楼主 #1 2019-03-10 15:14:27 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,441

- 积分: 9202

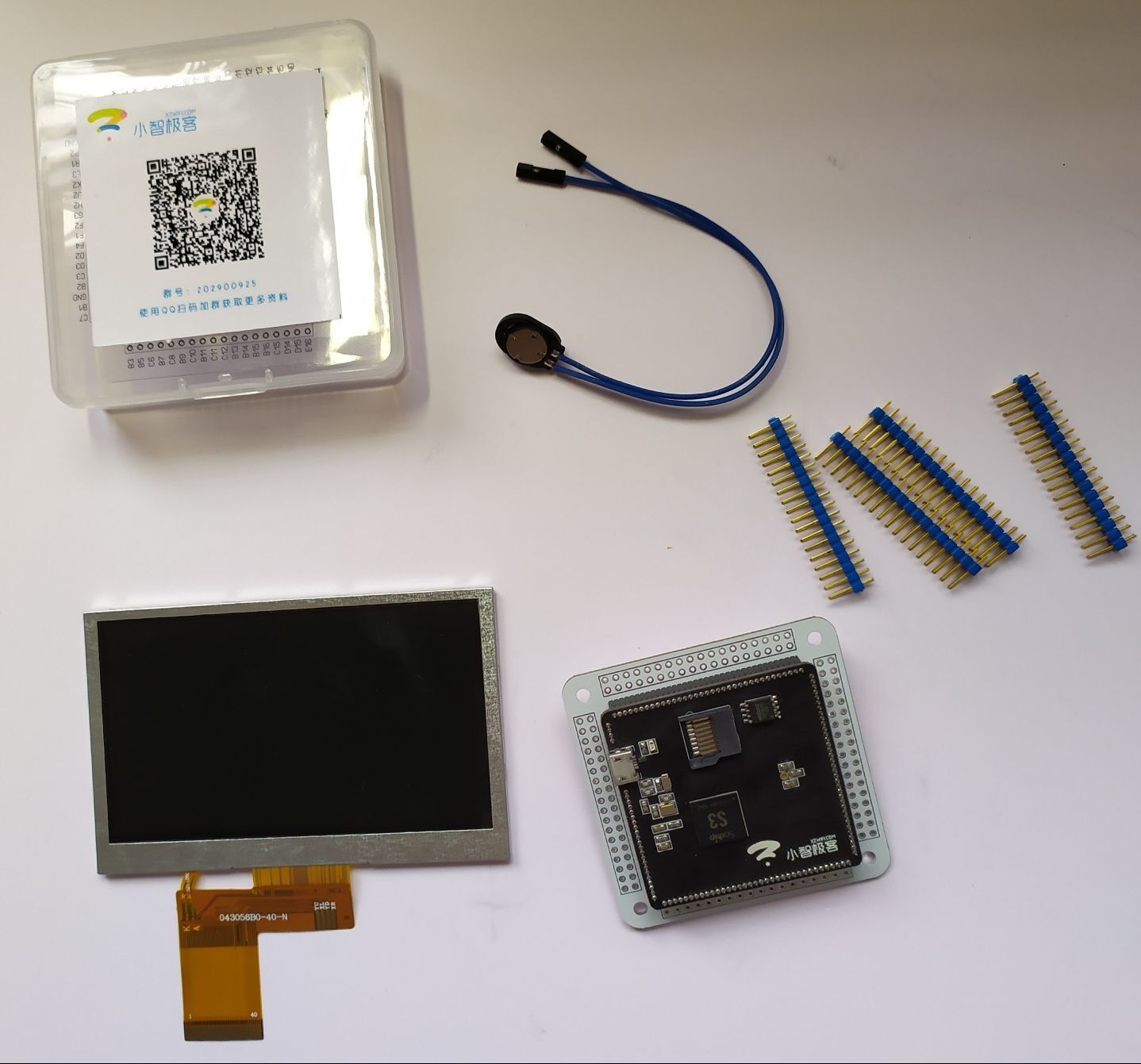

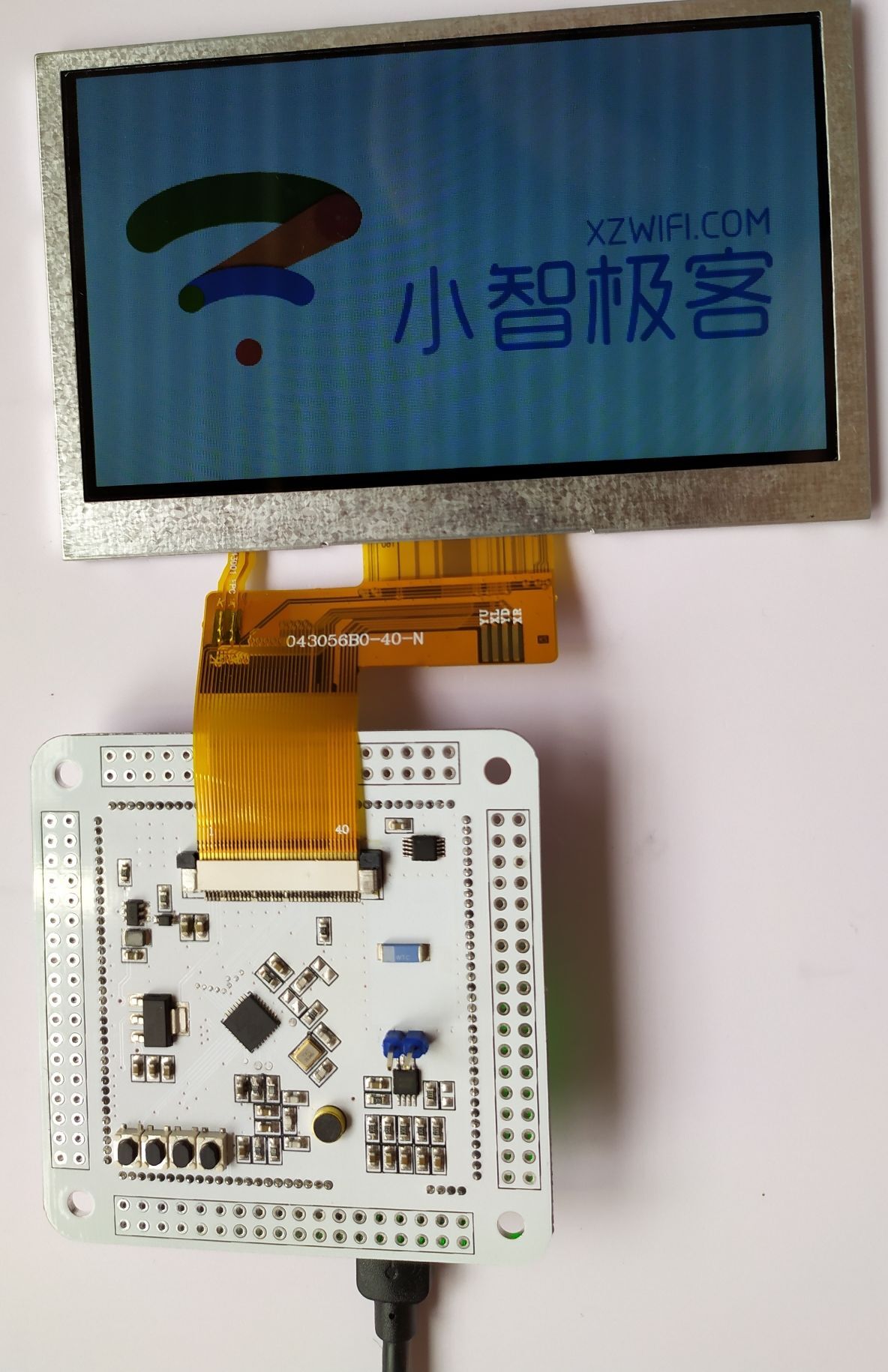

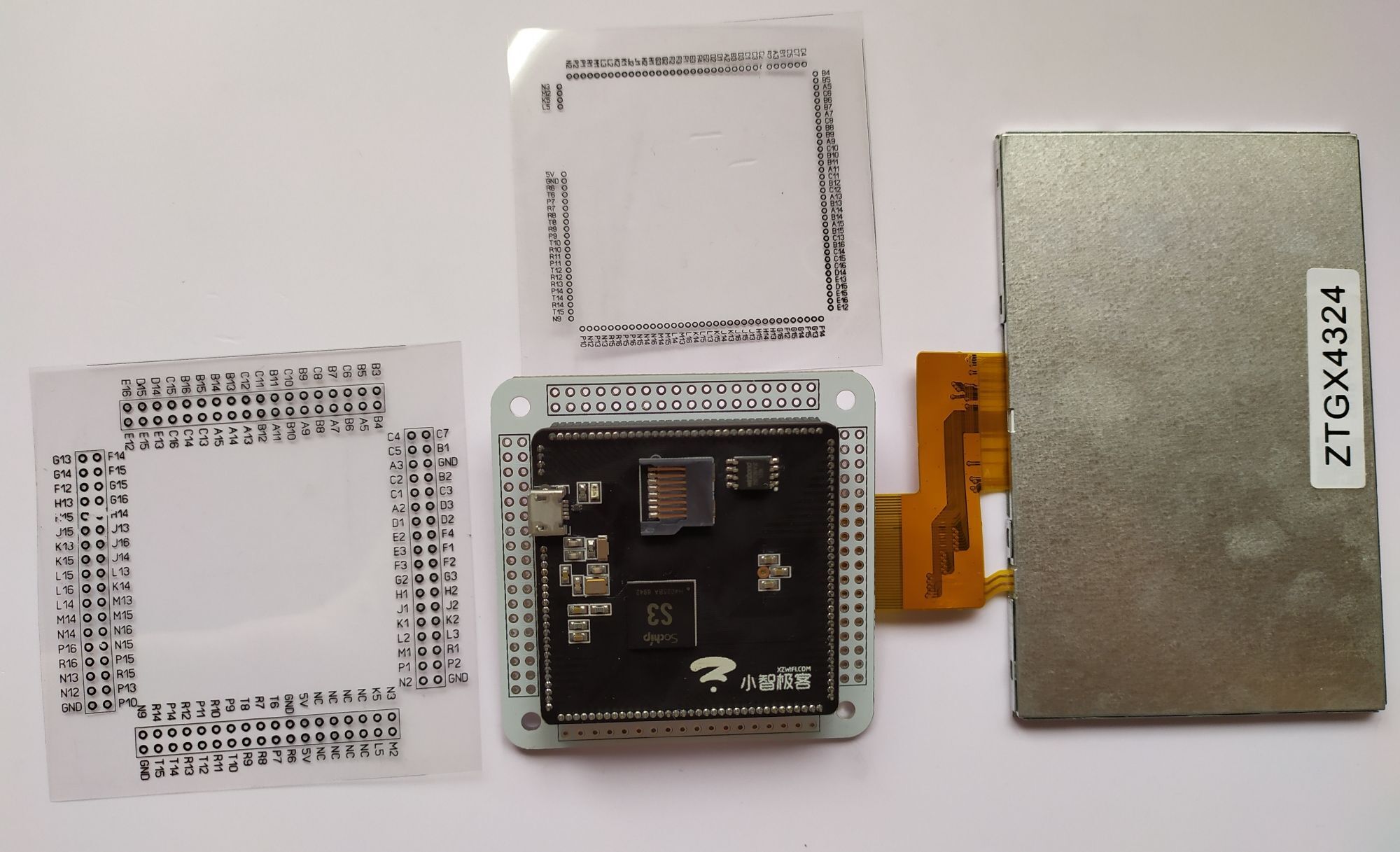

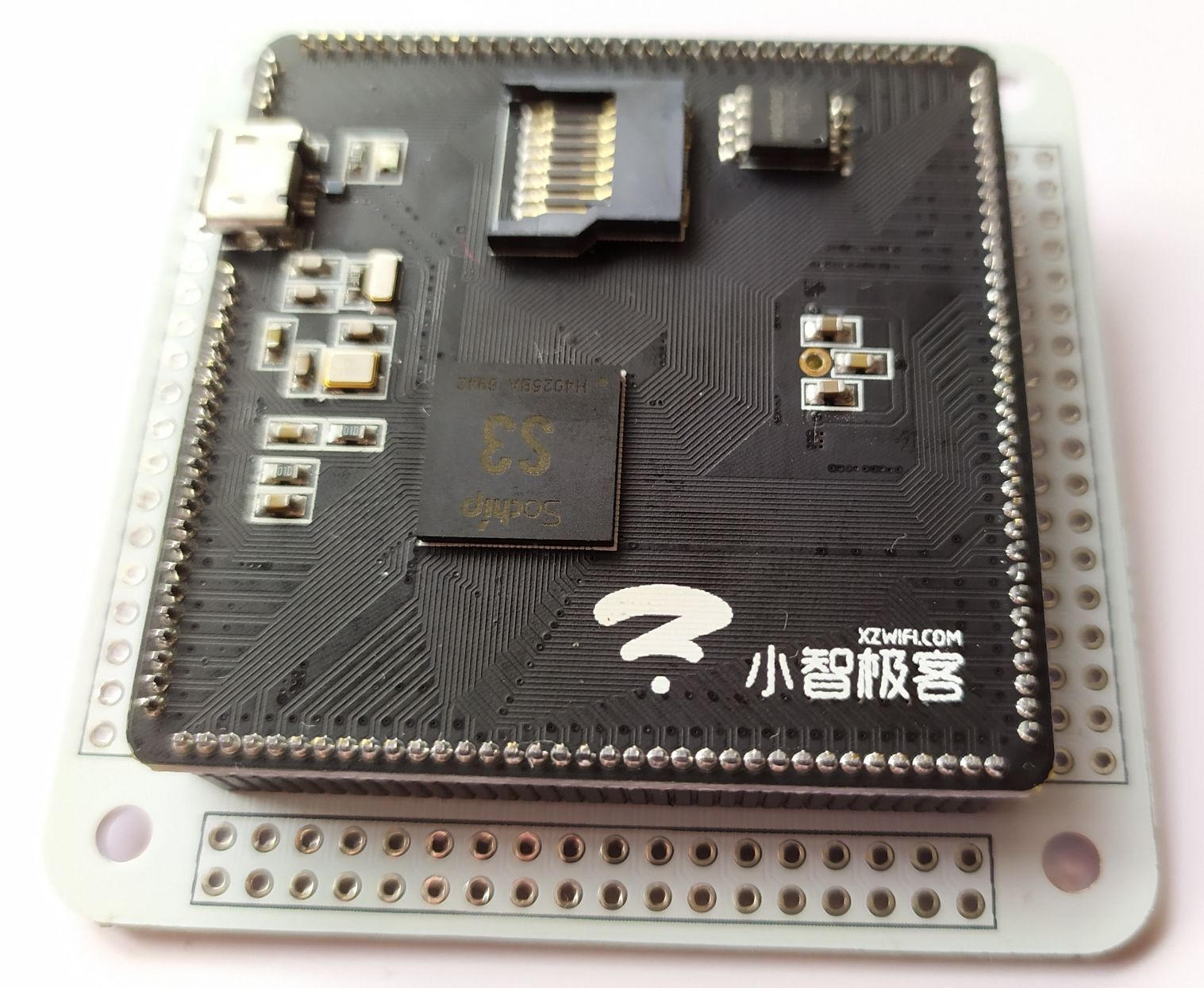

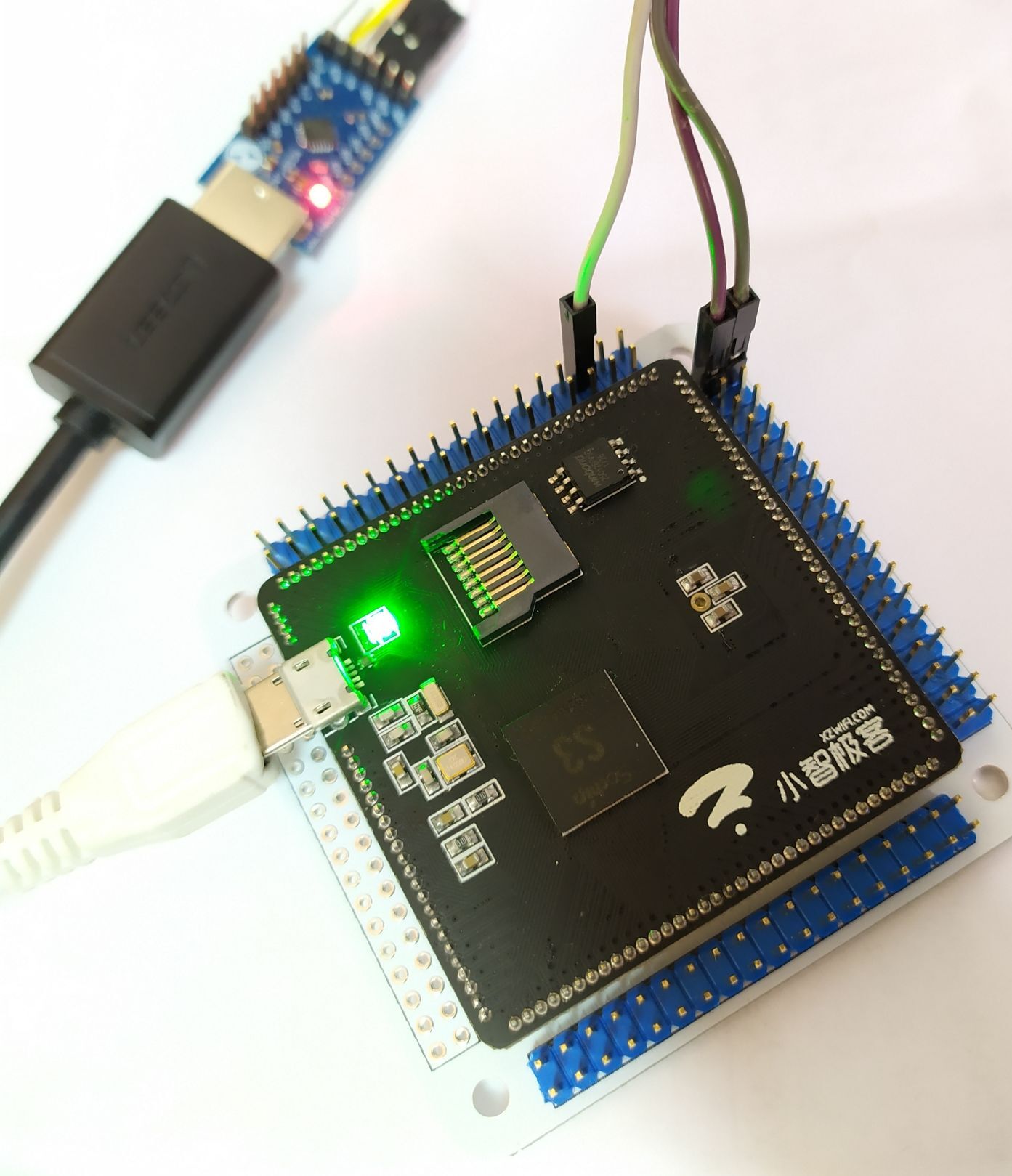

感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

购买链接:

小智极客 索智 全志 S3 核心板 开发板Linux系统: https://item.taobao.com/item.htm?id=588502966831

小智极客 索智/全志S3全功能底板: https://item.taobao.com/item.htm?id=588722094008

全志/索智S3芯片零售,内置128MB DDR3内存: https://item.taobao.com/item.htm?id=588754350002

QQ交流群: 202900925

全志V3s手册V1.0: Allwinner_V3s_Datasheet_V1.0.pdf

全志S3手册V0.2: Allwinner_S3_Datasheet_V0_2.pdf (索智S3手册)

参考链接: 编译索智(Sochip) S3 SDK (zeta)

2019-04-08 更新:

-------------------------------------------------

固件下载(主线uboot + 主线 linux 4.13): XiaoZhi_S3_Simple_V1_Pack_20190408.7z

2019-04-10 更新:

-------------------------------------------------

固件下载(主线uboot + 主线 linux 4.13)uart0, uart2两个版本: XiaoZhi_S3_Simple_V1_Pack_20190410.7z

源码地址: https://github.com/qq516333132/u-boot/tree/XiaoZhi_S3_Simple_V1

离线

楼主 #2 2019-03-10 15:15:47 分享评论

楼主 #3 2019-03-10 15:15:49 分享评论

楼主 #4 2019-03-10 15:15:51 分享评论

楼主 #5 2019-03-10 15:15:53 分享评论

楼主 #6 2019-03-10 15:15:55 分享评论

楼主 #7 2019-03-10 16:13:48 分享评论

#8 2019-03-10 16:23:12 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,140

- 积分: 1092.5

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

动作真快,比mango还先出了哈

离线

#9 2019-03-10 16:25:22 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,140

- 积分: 1092.5

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

有一点不明白,为啥都升级了ddr2,手册上还是说只支持1024的LCD

离线

#10 2019-03-10 16:30:30 分享评论

- 山无棱

- 会员

- 注册时间: 2017-10-23

- 已发帖子: 116

- 积分: 116

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

有一点不明白,为啥都升级了ddr2,手册上还是说只支持1024的LCD

也就是说分辨率和内存带宽有关系?

离线

#11 2019-03-10 16:32:36 分享评论

- mango

- 会员

- 所在地: 芒果派1

- 注册时间: 2017-12-02

- 已发帖子: 781

- 积分: 727

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

狂顶,改天拍一个过来玩。

我们的S3板子还得等段时间,在和seeed一起搞个全球首发的秘密项目,压力太大。

歪朵拉开源硬件: https://widora.cn

淘宝: https://widora.taobao.com/

离线

楼主 #12 2019-03-10 16:35:04 分享评论

#13 2019-03-10 17:12:02 分享评论

- 小智科技

- 会员

- 注册时间: 2019-03-10

- 已发帖子: 92

- 积分: 83

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

购买链接:

小智极客 索智 全志 S3 核心板 开发板Linux系统: https://item.taobao.com/item.htm?id=588502966831

小智极客 索智/全志S3全功能底板: https://item.taobao.com/item.htm?id=588722094008

全志/索智S3芯片零售,内置128MB DDR3内存: https://item.taobao.com/item.htm?id=588754350002

QQ交流群: 202900925

感谢晕哥以及晕哥平台的大力支持~ ![]()

离线

#14 2019-03-10 17:18:09 分享评论

- 小智科技

- 会员

- 注册时间: 2019-03-10

- 已发帖子: 92

- 积分: 83

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

狂顶,改天拍一个过来玩。

我们的S3板子还得等段时间,在和seeed一起搞个全球首发的秘密项目,压力太大。

谢谢芒果哥的支持原来买过widora bit系列很好用

离线

#15 2019-03-10 18:51:21 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,140

- 积分: 1092.5

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

mango 说:狂顶,改天拍一个过来玩。

我们的S3板子还得等段时间,在和seeed一起搞个全球首发的秘密项目,压力太大。坐等秘密项目被公开。

我猜是新版k210。。。期待

离线

#16 2019-03-10 19:05:45 分享评论

- mango

- 会员

- 所在地: 芒果派1

- 注册时间: 2017-12-02

- 已发帖子: 781

- 积分: 727

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

晕哥 说:mango 说:狂顶,改天拍一个过来玩。

我们的S3板子还得等段时间,在和seeed一起搞个全球首发的秘密项目,压力太大。坐等秘密项目被公开。

我猜是新版k210。。。期待

不是

歪朵拉开源硬件: https://widora.cn

淘宝: https://widora.taobao.com/

离线

#17 2019-03-11 17:15:25 分享评论

- dgtg

- 会员

- 注册时间: 2017-11-08

- 已发帖子: 275

- 积分: 229.5

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

关注一下!买个来耍耍...

离线

楼主 #18 2019-03-11 17:19:49 分享评论

楼主 #19 2019-03-11 18:11:03 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,441

- 积分: 9202

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

把荔枝派的 u-boot 弄到 S3 跑跑:

参考链接: https://whycan.cn/t_561.html

1. 克隆源码: git clone https://github.com/Lichee-Pi/u-boot.git -b v3s-spi-experimental

2. ARCH=arm CROSS_COMPILE=arm-linux-gnueabihf- make LicheePi_Zero_defconfig (默认)

3. 修改 arch/arm/mach-sunxi/dram_sun8i_h3.c:

#ifdef CONFIG_SUNXI_H3_DRAM_DDR2

u8 bank_bits;

#endif

改为:

u8 bank_bits;

4. 修改 board/sunxi/Kconfig

删除第 138 行:

select SUNXI_H3_DRAM_DDR2

5. .config 文件 删除以下行: CONFIG_SUNXI_H3_DRAM_DDR2

可以用 sunxi-fel 烧录到 S3 板子,

调试串口是 PB8, PB9 也就是 示意图上面 B6, C6

离线

#20 2019-03-11 20:00:16 分享评论

- 小智科技

- 会员

- 注册时间: 2019-03-10

- 已发帖子: 92

- 积分: 83

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

把荔枝派的 u-boot 弄到 S3 跑跑:

参考链接: https://whycan.cn/t_561.html

1. 克隆源码: git clone https://github.com/Lichee-Pi/u-boot.git -b v3s-spi-experimental

2. ARCH=arm CROSS_COMPILE=arm-linux-gnueabihf- make LicheePi_Zero_defconfig (默认)

3. 修改 arch/arm/mach-sunxi/dram_sun8i_h3.c:

#ifdef CONFIG_SUNXI_H3_DRAM_DDR2

u8 bank_bits;

#endif改为:

u8 bank_bits;

4. 修改 board/sunxi/Kconfig

删除第 138 行:select SUNXI_H3_DRAM_DDR2

5. .config 文件 删除以下行: CONFIG_SUNXI_H3_DRAM_DDR2

可以用 sunxi-fel 烧录到 S3 板子,

调试串口是 PB8, PB9 也就是 示意图上面 B6, C6

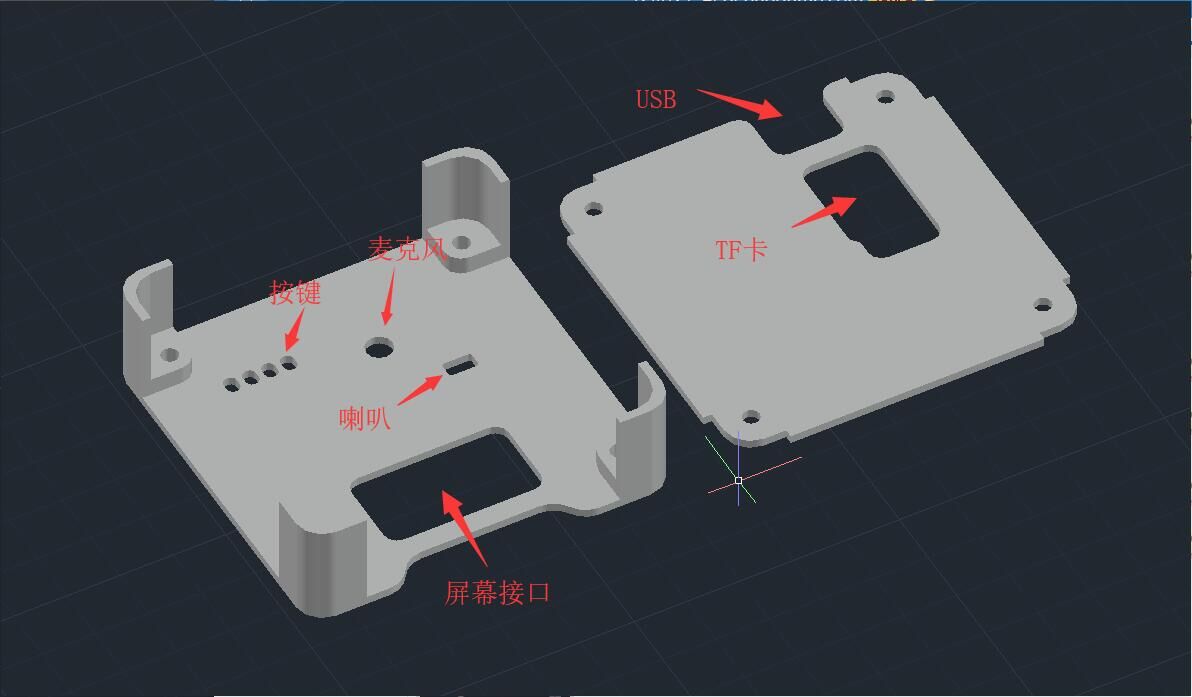

谢晕哥又带来了更多的玩法,今晚建模做个外壳 ![]()

离线

楼主 #21 2019-03-11 23:10:40 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,441

- 积分: 9202

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

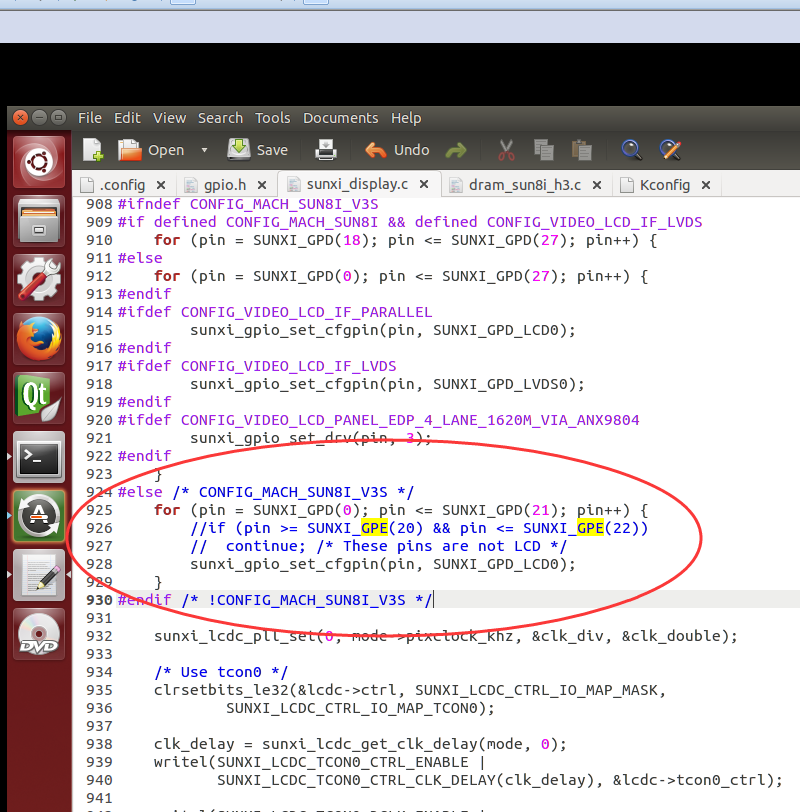

修改 drivers/video/sunxi_display.c

for (pin = SUNXI_GPE(0); pin <= SUNXI_GPE(24); pin++) {

if (pin >= SUNXI_GPE(20) && pin <= SUNXI_GPE(22))

continue; /* These pins are not LCD */

sunxi_gpio_set_cfgpin(pin, SUN8I_V3S_GPE_LCD);

}

改为:

for (pin = SUNXI_GPD(0); pin <= SUNXI_GPD(21); pin++) {

sunxi_gpio_set_cfgpin(pin, SUNXI_GPD_LCD0);

}

可以点亮 LCD 屏了!

离线

#22 2019-03-12 10:58:05 分享评论

- Ken

- 会员

- 注册时间: 2019-01-06

- 已发帖子: 59

- 积分: 54

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

S3的SDK能实现视频h.264的解码吗?

离线

#23 2019-03-12 11:18:21 分享评论

- Ken

- 会员

- 注册时间: 2019-01-06

- 已发帖子: 59

- 积分: 54

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

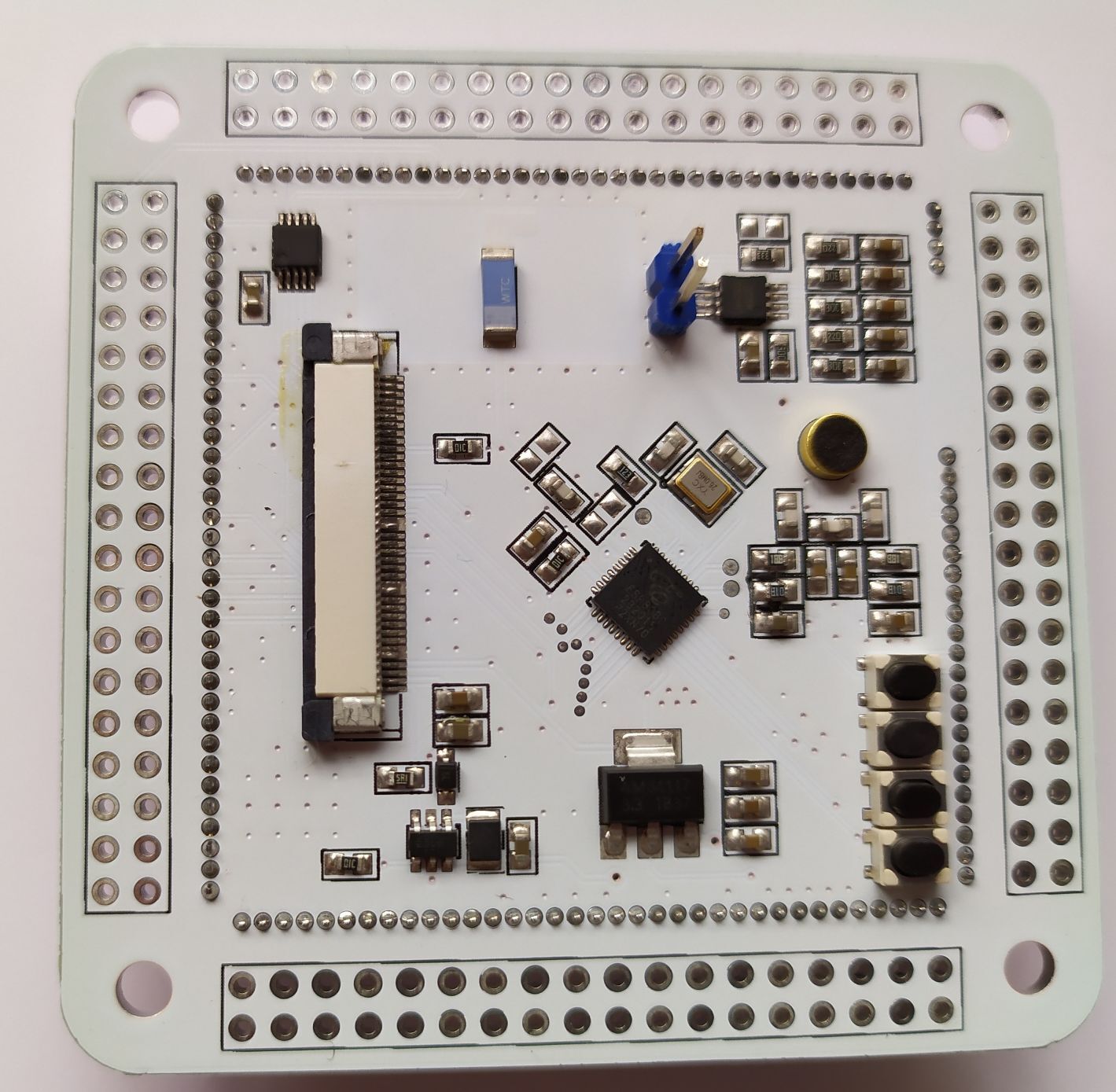

晕哥照片里的那个白色板是焊接好的全功能底板吗?店里现售的空底板是没有这些器件的吗?

离线

#24 2019-03-12 12:35:51 分享评论

- 小智科技

- 会员

- 注册时间: 2019-03-10

- 已发帖子: 92

- 积分: 83

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

晕哥照片里的那个白色板是焊接好的全功能底板吗?店里现售的空底板是没有这些器件的吗?

照片里白色的是全功能底板,全功能底板还有3天到货。

离线

#25 2019-03-12 13:13:46 分享评论

- Ken

- 会员

- 注册时间: 2019-01-06

- 已发帖子: 59

- 积分: 54

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

@小智科技,这个SDK能实现视频h.264的解码吗?

离线

#26 2019-03-12 13:23:34 分享评论

- 小智科技

- 会员

- 注册时间: 2019-03-10

- 已发帖子: 92

- 积分: 83

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

@小智科技,这个SDK能实现视频h.264的解码吗?

可以按照群内资料编译好发我测试一下。。。我电脑被虚拟机撑爆了。。。

离线

#27 2019-03-12 14:23:50 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,140

- 积分: 1092.5

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

为啥核心板这么大这么空?另外,这个核心板是否提供软件支持,比如驱动都适配好,能播视频,能接摄像头等

离线

#28 2019-03-12 15:26:42 分享评论

- 小智科技

- 会员

- 注册时间: 2019-03-10

- 已发帖子: 92

- 积分: 83

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

为啥核心板这么大这么空?另外,这个核心板是否提供软件支持,比如驱动都适配好,能播视频,能接摄像头等

核心板仅有5CM*5CM的大小,比银行卡还小,如果再小接口将无法全部引出,全志SDK大部分驱动都有。

离线

#29 2019-03-12 23:43:08 分享评论

- 小叶子

- 会员

- 注册时间: 2019-03-12

- 已发帖子: 1

- 积分: 1

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

刚用上,非常不错

离线

楼主 #30 2019-03-13 08:43:01 分享评论

#31 2019-03-22 10:26:37 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

有外壳,不错

离线

#32 2019-03-26 10:28:09 分享评论

- 雷龙发展q2852826868

- 会员

- 所在地: 深圳

- 注册时间: 2018-12-10

- 已发帖子: 157

- 积分: 157

- 个人网站

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

这个,真是厉害了。

CS品牌SD NAND , ATO 小容量SLC/SPI NAND/MCP. T:13691982107,Q:2852826868

离线

楼主 #33 2019-04-08 08:51:08 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,441

- 积分: 9202

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

安装 arm gcc 浮点数工具链:

sudo apt-get install gcc-arm-linux-gnueabihf

编译 S3 u-boot 流程:

git clone https://github.com/qq516333132/u-boot.git -b XiaoZhi_S3_Simple_V1

###启用 4.3 寸 配置 ###

ARCH=arm CROSS_COMPILE=arm-linux-gnueabihf- make XiaoZhi_S3_Simple_V1_480x272LCD_defconfig###启用 5.0 寸 配置 ###

ARCH=arm CROSS_COMPILE=arm-linux-gnueabihf- make XiaoZhi_S3_Simple_V1_800x480LCD_defconfig###编译###

ARCH=arm CROSS_COMPILE=arm-linux-gnueabihf- make

修改记录:

https://github.com/qq516333132/u-boot/commits/XiaoZhi_S3_Simple_V1

https://github.com/qq516333132/u-boot/commit/404c4f2d1a8c88c8db338111173683043d3ba6cf

https://github.com/qq516333132/u-boot/commit/c14c5d029f10bf6a365a7f128b57ec0deb8b176b

https://github.com/qq516333132/u-boot/commit/b63ce45082d5b2762dbdb0d90000319c45ab06e2

diff 文件:

root@test4:/opt/u-boot# git diff dd6e8740dc2dc24d64c6ee62250330a174b16607 b63ce45082d5b2762dbdb0d90000319c45ab06e2

diff --git a/arch/arm/dts/Makefile b/arch/arm/dts/Makefile

index 469dd71..24ac190 100644

--- a/arch/arm/dts/Makefile

+++ b/arch/arm/dts/Makefile

@@ -282,6 +282,8 @@ dtb-$(CONFIG_MACH_SUN8I_H3) += \

sun8i-h3-nanopi-neo.dtb

dtb-$(CONFIG_MACH_SUN8I_V3S) += \

sun8i-v3s-licheepi-zero.dtb

+dtb-$(CONFIG_MACH_SUN8I_S3) += \

+ sun8i-v3s-licheepi-zero.dtb

dtb-$(CONFIG_MACH_SUN50I) += \

sun50i-a64-pine64-plus.dtb \

sun50i-a64-pine64.dtb

diff --git a/arch/arm/include/asm/arch-sunxi/clock_sun6i.h b/arch/arm/include/asm/arch-sunxi/clock_sun6i.h

index 5bbc869..6aadac8 100644

--- a/arch/arm/include/asm/arch-sunxi/clock_sun6i.h

+++ b/arch/arm/include/asm/arch-sunxi/clock_sun6i.h

@@ -451,7 +451,7 @@ struct sunxi_ccm_reg {

/* CCM bits common to all Display Engine 2.0 clock ctrl regs */

#define CCM_DE2_CTRL_M(n) ((((n) - 1) & 0xf) << 0)

#define CCM_DE2_CTRL_PLL_MASK (3 << 24)

-#ifndef CONFIG_MACH_SUN8I_V3S

+#if !defined(CONFIG_MACH_SUN8I_V3S) && !defined(CONFIG_MACH_SUN8I_S3)

#define CCM_DE2_CTRL_PLL6_2X (0 << 24)

#define CCM_DE2_CTRL_PLL10 (1 << 24)

#else

diff --git a/arch/arm/include/asm/arch-sunxi/pwm.h b/arch/arm/include/asm/arch-sunxi/pwm.h

index c83ca37..f061383 100644

--- a/arch/arm/include/asm/arch-sunxi/pwm.h

+++ b/arch/arm/include/asm/arch-sunxi/pwm.h

@@ -31,7 +31,7 @@

#define SUNXI_PWM_MUX SUN8I_GPH_PWM

#endif

-#if defined CONFIG_MACH_SUN8I_V3S

+#if defined CONFIG_MACH_SUN8I_V3S || defined CONFIG_MACH_SUN8I_S3

#define SUNXI_PWM_PIN0 SUNXI_GPB(4)

#define SUNXI_PWM_MUX SUN8I_V3S_GPB_PWM

#endif

diff --git a/arch/arm/mach-sunxi/board.c b/arch/arm/mach-sunxi/board.c

index 7a55ee3..b463653 100644

--- a/arch/arm/mach-sunxi/board.c

+++ b/arch/arm/mach-sunxi/board.c

@@ -110,7 +110,7 @@ static int gpio_init(void)

sunxi_gpio_set_cfgpin(SUNXI_GPB(9), SUN8I_A83T_GPB_UART0);

sunxi_gpio_set_cfgpin(SUNXI_GPB(10), SUN8I_A83T_GPB_UART0);

sunxi_gpio_set_pull(SUNXI_GPB(10), SUNXI_GPIO_PULL_UP);

-#elif CONFIG_CONS_INDEX == 1 && defined(CONFIG_MACH_SUN8I_V3S)

+#elif CONFIG_CONS_INDEX == 1 && (defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3))

sunxi_gpio_set_cfgpin(SUNXI_GPB(8), SUN8I_V3S_GPB_UART0);

sunxi_gpio_set_cfgpin(SUNXI_GPB(9), SUN8I_V3S_GPB_UART0);

sunxi_gpio_set_pull(SUNXI_GPB(9), SUNXI_GPIO_PULL_UP);

diff --git a/arch/arm/mach-sunxi/cpu_info.c b/arch/arm/mach-sunxi/cpu_info.c

index 15f1e0e..34bcb5e 100644

--- a/arch/arm/mach-sunxi/cpu_info.c

+++ b/arch/arm/mach-sunxi/cpu_info.c

@@ -87,7 +87,7 @@ int print_cpuinfo(void)

printf("CPU: Allwinner A83T (SUN8I %04x)\n", sunxi_get_sram_id());

#elif defined CONFIG_MACH_SUN8I_H3

printf("CPU: Allwinner H3 (SUN8I %04x)\n", sunxi_get_sram_id());

-#elif defined CONFIG_MACH_SUN8I_V3S

+#elif defined CONFIG_MACH_SUN8I_V3S || defined CONFIG_MACH_SUN8I_S3

printf("CPU: Allwinner V3s (SUN8I %04x)\n", sunxi_get_sram_id());

#elif defined CONFIG_MACH_SUN9I

puts("CPU: Allwinner A80 (SUN9I)\n");

diff --git a/arch/arm/mach-sunxi/dram_sun8i_h3.c b/arch/arm/mach-sunxi/dram_sun8i_h3.c

index a48320e..ec220f2 100644

--- a/arch/arm/mach-sunxi/dram_sun8i_h3.c

+++ b/arch/arm/mach-sunxi/dram_sun8i_h3.c

@@ -22,9 +22,9 @@ struct dram_para {

u8 bus_width;

u8 dual_rank;

u8 row_bits;

-#ifdef CONFIG_SUNXI_H3_DRAM_DDR2

+//#ifdef CONFIG_SUNXI_H3_DRAM_DDR2

u8 bank_bits;

-#endif

+//#endif

};

static inline int ns_to_t(int nanoseconds)

diff --git a/board/sunxi/Kconfig b/board/sunxi/Kconfig

index a451f47..4437c01 100644

--- a/board/sunxi/Kconfig

+++ b/board/sunxi/Kconfig

@@ -139,6 +139,17 @@ config MACH_SUN8I_V3S

select SUNXI_DE2

select ARMV7_BOOT_SEC_DEFAULT if OLD_SUNXI_KERNEL_COMPAT

+config MACH_SUN8I_S3

+ bool "sun8i (Allwinner S3)"

+ select CPU_V7

+ select CPU_V7_HAS_NONSEC

+ select CPU_V7_HAS_VIRT

+ select SUNXI_GEN_SUN6I

+ select SUPPORT_SPL

+ select SUNXI_H3_DW_DRAM

+ select SUNXI_DE2

+ select ARMV7_BOOT_SEC_DEFAULT if OLD_SUNXI_KERNEL_COMPAT

+

config MACH_SUN9I

bool "sun9i (Allwinner A80)"

select CPU_V7

@@ -155,7 +166,7 @@ endchoice

# The sun8i SoCs share a lot, this helps to avoid a lot of "if A23 || A33"

config MACH_SUN8I

bool

- default y if MACH_SUN8I_A23 || MACH_SUN8I_A33 || MACH_SUN8I_H3 || MACH_SUN8I_A83T || MACH_SUN8I_V3S

+ default y if MACH_SUN8I_A23 || MACH_SUN8I_A33 || MACH_SUN8I_H3 || MACH_SUN8I_A83T || MACH_SUN8I_V3S || MACH_SUN8I_S3

config DRAM_TYPE

int "sunxi dram type"

diff --git a/configs/XiaoZhi_S3_Simple_V1_480x272LCD_defconfig b/configs/XiaoZhi_S3_Simple_V1_480x272LCD_defconfig

new file mode 100644

index 0000000..7192ee7

--- /dev/null

+++ b/configs/XiaoZhi_S3_Simple_V1_480x272LCD_defconfig

@@ -0,0 +1,27 @@

+CONFIG_ARM=y

+CONFIG_ARCH_SUNXI=y

+# CONFIG_ARMV7_NONSEC is not set

+CONFIG_MACH_SUN8I_S3=y

+CONFIG_DRAM_CLK=360

+CONFIG_DRAM_ZQ=14779

+CONFIG_VIDEO_LCD_MODE="x:480,y:272,depth:18,pclk_khz:10000,le:42,ri:8,up:11,lo:4,hs:1,vs:1,sync:3,vmode:0"CONFIG_VIDEO_LCD_MODE="x:480,y:272,depth:18,pclk_khz:10000,le:42,ri:8,up:11,lo:4,hs:1,vs:1,sync:3,vmode:0"CONFIG_VIDEO_LCD_MODE="x:480,y:272,depth:18,pclk_khz:10000,le:42,ri:8,up:11,lo:4,hs:1,vs:1,sync:3,vmode:0"CONFIG_VIDEO_LCD_MODE="x:480,y:272,depth:18,pclk_khz:10000,le:42,ri:8,up:11,lo:4,hs:1,vs:1,sync:3,vmode:0"CONFIG_VIDEO_LCD_MODE="x:480,y:272,depth:18,pclk_khz:10000,le:42,ri:8,up:11,lo:4,hs:1,vs:1,sync:3,vmode:0"

+CONFIG_VIDEO_LCD_BL_PWM="PB4"

+# CONFIG_VIDEO_LCD_BL_PWM_ACTIVE_LOW is not set

+CONFIG_DEFAULT_DEVICE_TREE="sun8i-v3s-licheepi-zero"

+# CONFIG_CONSOLE_MUX is not set

+CONFIG_SPL=y

+CONFIG_CMD_BOOTMENU=y

+# CONFIG_CMD_IMLS is not set

+CONFIG_CMD_MEMINFO=y

+# CONFIG_CMD_FLASH is not set

+CONFIG_CMD_SF=y

+CONFIG_CMD_SPI=y

+# CONFIG_CMD_FPGA is not set

+CONFIG_DM_SPI_FLASH=y

+CONFIG_SPI_FLASH=y

+CONFIG_SPI_FLASH_WINBOND=y

+CONFIG_SPL_SPI_SUNXI=y

+# CONFIG_NETDEVICES is not set

+CONFIG_DM_SPI=y

+CONFIG_SUNXI_SPI=y

+CONFIG_OF_LIBFDT_OVERLAY=y

diff --git a/configs/XiaoZhi_S3_Simple_V1_800x480LCD_defconfig b/configs/XiaoZhi_S3_Simple_V1_800x480LCD_defconfig

new file mode 100644

index 0000000..53245de

--- /dev/null

+++ b/configs/XiaoZhi_S3_Simple_V1_800x480LCD_defconfig

@@ -0,0 +1,27 @@

+CONFIG_ARM=y

+CONFIG_ARCH_SUNXI=y

+# CONFIG_ARMV7_NONSEC is not set

+CONFIG_MACH_SUN8I_S3=y

+CONFIG_DRAM_CLK=360

+CONFIG_DRAM_ZQ=14779

+CONFIG_VIDEO_LCD_MODE="x:800,y:480,depth:18,pclk_khz:33000,le:87,ri:40,up:31,lo:13,hs:1,vs:1,sync:3,vmode:0"

+CONFIG_VIDEO_LCD_BL_PWM="PB4"

+# CONFIG_VIDEO_LCD_BL_PWM_ACTIVE_LOW is not set

+CONFIG_DEFAULT_DEVICE_TREE="sun8i-v3s-licheepi-zero"

+# CONFIG_CONSOLE_MUX is not set

+CONFIG_SPL=y

+CONFIG_CMD_BOOTMENU=y

+# CONFIG_CMD_IMLS is not set

+CONFIG_CMD_MEMINFO=y

+# CONFIG_CMD_FLASH is not set

+CONFIG_CMD_SF=y

+CONFIG_CMD_SPI=y

+# CONFIG_CMD_FPGA is not set

+CONFIG_DM_SPI_FLASH=y

+CONFIG_SPI_FLASH=y

+CONFIG_SPI_FLASH_WINBOND=y

+CONFIG_SPL_SPI_SUNXI=y

+# CONFIG_NETDEVICES is not set

+CONFIG_DM_SPI=y

+CONFIG_SUNXI_SPI=y

+CONFIG_OF_LIBFDT_OVERLAY=y

diff --git a/drivers/video/sunxi_display.c b/drivers/video/sunxi_display.c

index 7049a3c..06ccb01 100644

--- a/drivers/video/sunxi_display.c

+++ b/drivers/video/sunxi_display.c

@@ -525,7 +525,7 @@ static void sunxi_composer_init(void)

struct sunxi_ccm_reg * const ccm =

(struct sunxi_ccm_reg *)SUNXI_CCM_BASE;

-#ifndef CONFIG_MACH_SUN8I_V3S

+#if !defined(CONFIG_MACH_SUN8I_V3S) && !defined(CONFIG_MACH_SUN8I_S3)

clock_set_pll10(432000000);

/* Set DE parent to pll10 */

@@ -905,7 +905,7 @@ static void sunxi_lcdc_tcon0_mode_set(const struct ctfb_res_modes *mode,

(struct sunxi_lcdc_reg *)SUNXI_LCD0_BASE;

int bp, clk_delay, clk_div, clk_double, pin, total, val;

-#ifndef CONFIG_MACH_SUN8I_V3S

+#if !defined(CONFIG_MACH_SUN8I_V3S) && !defined(CONFIG_MACH_SUN8I_S3)

#if defined CONFIG_MACH_SUN8I && defined CONFIG_VIDEO_LCD_IF_LVDS

for (pin = SUNXI_GPD(18); pin <= SUNXI_GPD(27); pin++) {

#else

@@ -921,13 +921,17 @@ static void sunxi_lcdc_tcon0_mode_set(const struct ctfb_res_modes *mode,

sunxi_gpio_set_drv(pin, 3);

#endif

}

-#else /* CONFIG_MACH_SUN8I_V3S */

+#elif defined CONFIG_MACH_SUN8I_V3S

for (pin = SUNXI_GPE(0); pin <= SUNXI_GPE(24); pin++) {

if (pin >= SUNXI_GPE(20) && pin <= SUNXI_GPE(22))

continue; /* These pins are not LCD */

sunxi_gpio_set_cfgpin(pin, SUN8I_V3S_GPE_LCD);

}

-#endif /* !CONFIG_MACH_SUN8I_V3S */

+#elif defined CONFIG_MACH_SUN8I_S3

+ for (pin = SUNXI_GPD(0); pin <= SUNXI_GPD(21); pin++) {

+ sunxi_gpio_set_cfgpin(pin, SUNXI_GPD_LCD0);

+ }

+#endif

sunxi_lcdc_pll_set(0, mode->pixclock_khz, &clk_div, &clk_double);

diff --git a/include/configs/sun8i.h b/include/configs/sun8i.h

index 6ac42ac..b8454ba 100644

--- a/include/configs/sun8i.h

+++ b/include/configs/sun8i.h

@@ -21,7 +21,7 @@

#define CONFIG_SUNXI_USB_PHYS 4

#elif defined CONFIG_MACH_SUN8I_A83T

#define CONFIG_SUNXI_USB_PHYS 3

-#elif defined CONFIG_MACH_SUN8I_V3S

+#elif (defined CONFIG_MACH_SUN8I_V3S) || (defined CONFIG_MACH_SUN8I_S3)

#define CONFIG_SUNXI_USB_PHYS 1

#else

#define CONFIG_SUNXI_USB_PHYS 2

diff --git a/include/configs/sunxi-common.h b/include/configs/sunxi-common.h

index fcecd0b..2874cef 100644

--- a/include/configs/sunxi-common.h

+++ b/include/configs/sunxi-common.h

@@ -77,7 +77,7 @@

#define CONFIG_SYS_SDRAM_BASE 0x40000000

#define CONFIG_SYS_LOAD_ADDR 0x41000000 /* default load address */

/* V3s do not have enough memory to place code at 0x4a000000 */

-#ifndef CONFIG_MACH_SUN8I_V3S

+#if !defined(CONFIG_MACH_SUN8I_V3S) && !defined(CONFIG_MACH_SUN8I_S3)

#define CONFIG_SYS_TEXT_BASE 0x4a000000

#else

#define CONFIG_SYS_TEXT_BASE 0x42e00000

@@ -153,7 +153,7 @@

#define CONFIG_SYS_MMC_MAX_DEVICE 4

#endif

-#ifndef CONFIG_MACH_SUN8I_V3S

+#if !defined(CONFIG_MACH_SUN8I_V3S) && !defined(CONFIG_MACH_SUN8I_S3)

/* 64MB of malloc() pool */

#define CONFIG_SYS_MALLOC_LEN (CONFIG_ENV_SIZE + (64 << 20))

#else

@@ -303,7 +303,7 @@ extern int soft_i2c_gpio_scl;

* The amount of RAM to keep free at the top of RAM when relocating u-boot,

* to use as framebuffer. This must be a multiple of 4096.

*/

-#ifndef CONFIG_MACH_SUN8I_V3S

+#if !defined(CONFIG_MACH_SUN8I_V3S) && !defined(CONFIG_MACH_SUN8I_S3)

#define CONFIG_SUNXI_MAX_FB_SIZE (16 << 20)

#else

#define CONFIG_SUNXI_MAX_FB_SIZE (2 << 20)

@@ -410,7 +410,7 @@ extern int soft_i2c_gpio_scl;

* 32M uncompressed kernel, 16M compressed kernel, 1M fdt,

* 1M script, 1M pxe and the ramdisk at the end.

*/

-#ifndef CONFIG_MACH_SUN8I_V3S

+#if !defined(CONFIG_MACH_SUN8I_V3S) && !defined(CONFIG_MACH_SUN8I_S3)

#define BOOTM_SIZE __stringify(0xa000000)

#define KERNEL_ADDR_R __stringify(SDRAM_OFFSET(2000000))

#define FDT_ADDR_R __stringify(SDRAM_OFFSET(3000000))

@@ -440,7 +440,7 @@ extern int soft_i2c_gpio_scl;

"pxefile_addr_r=" PXEFILE_ADDR_R "\0" \

"ramdisk_addr_r=" RAMDISK_ADDR_R "\0"

-#ifndef CONFIG_MACH_SUN8I_V3S

+#if !defined(CONFIG_MACH_SUN8I_V3S) && !defined(CONFIG_MACH_SUN8I_S3)

#define DFU_ALT_INFO_RAM \

"dfu_alt_info_ram=" \

"kernel ram " KERNEL_ADDR_R " 0x1000000;" \离线

#34 2019-04-08 12:54:44 分享评论

- jw__liu

- 会员

- 注册时间: 2019-01-18

- 已发帖子: 40

- 积分: 40

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

占沙发了

离线

楼主 #35 2019-04-08 15:17:29 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,441

- 积分: 9202

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

https://github.com/qq516333132/u-boot/commits/XiaoZhi_S3_Simple_V1_BootCmdArgs

https://github.com/qq516333132/u-boot/commit/b9f440d625d727205970e93aace9639e7b23605f

https://github.com/qq516333132/u-boot/blob/XiaoZhi_S3_Simple_V1_BootCmdArgs/include/configs/sun8i.h

新建了一个 XiaoZhi_S3_Simple_V1_BootCmdArgs 分支,

在 include/configs/sun8i.h 添加 :

#undef CONFIG_BOOTCOMMAND

#undef CONFIG_BOOTARGS

#ifndef CONFIG_BOOTCOMMAND

#define CONFIG_BOOTCOMMAND "sf probe 0 50000000;sf read 0x41800000 0x100000 0x4000;sf read 0x41000000 0x110000 0x500000; bootz 0x41000000 - 0x41800000"

#endif

#ifndef CONFIG_BOOTARGS

#define CONFIG_BOOTARGS "console=ttyS0,115200 earlyprintk panic=5 rootwait mtdparts=spi32766.0:992k(uboot)ro,32k(env)ro,64k(dtb)ro,5M(kernel)ro,-(rootfs) root=31:04 rw rootfstype=jffs2"

#endifzImage 和 rootfs 按照 V3s 的套路编译生成即可。

固件下载(主线uboot + 主线 linux 4.13): XiaoZhi_S3_Simple_V1_Pack_20190408.7z

离线

楼主 #36 2019-04-08 17:42:51 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,441

- 积分: 9202

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

https://github.com/Lichee-Pi/u-boot/commits/v3s-spi-experimental/common/Kconfig

https://github.com/Lichee-Pi/u-boot/commits/nano-v2018.01/common/Kconfig

原来是因为合并的版本不同, 导致 荔枝派 V3s 和 f1c100s 的 u-boot 表现有差异,

f1c100s 的 u-boot 可以通过 menuconfig 配置 bootargs 和 bootcmd,

而 V3s 的不可以。

离线

#37 2019-04-12 22:37:14 分享评论

- thor_yu

- 会员

- 注册时间: 2018-10-12

- 已发帖子: 20

- 积分: 5

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

各位大佬,S3 zeta的SDK怎么没看到有H264的编解码demo啊?

哪位调过S3的硬件编解码?可以直接UVC输入吗?

离线

#38 2019-04-13 08:20:30 分享评论

- smartcar

- 会员

- 注册时间: 2018-02-19

- 已发帖子: 735

- 积分: 735

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

各位大佬,S3 zeta的SDK怎么没看到有H264的编解码demo啊?

哪位调过S3的硬件编解码?可以直接UVC输入吗?

理论上可行, 我在 zeta sdk 也没有找到demo, 或许可以问下全志或者索智, 看他们能不能提供demo或者技术支持。

离线

#39 2019-04-18 19:39:22 分享评论

- zhenfanhei

- 会员

- 注册时间: 2018-01-18

- 已发帖子: 326

- 积分: 246

- 个人网站

离线

楼主 #40 2019-04-18 21:12:32 分享评论

#41 2019-04-19 00:40:16 分享评论

- zhenfanhei

- 会员

- 注册时间: 2018-01-18

- 已发帖子: 326

- 积分: 246

- 个人网站

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

那问下他有没,但如果不好扩散估计也够呛,买了也只能自个用

离线

#42 2019-04-19 07:37:12 分享评论

- kaokao

- 会员

- 注册时间: 2018-06-06

- 已发帖子: 30

- 积分: 30

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

果然小巧精致,漂亮大方!

离线

#43 2019-04-25 15:27:13 分享评论

- yytyu

- 会员

- 注册时间: 2018-11-01

- 已发帖子: 35

- 积分: 19

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

请问下S3 sdk包 运行频率是多少,内存带宽是多少位的

离线

楼主 #44 2019-04-25 16:07:18 分享评论

#45 2019-05-09 11:44:53 分享评论

- oldersu

- 会员

- 注册时间: 2019-05-09

- 已发帖子: 50

- 积分: 50

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

漂亮

离线

#46 2019-05-09 11:46:45 分享评论

- oldersu

- 会员

- 注册时间: 2019-05-09

- 已发帖子: 50

- 积分: 50

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

s3是啥芯片,第一次听说,有相关介绍吗?

离线

#47 2019-05-15 10:58:55 分享评论

- as86455011

- 会员

- 注册时间: 2018-11-20

- 已发帖子: 33

- 积分: 4

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

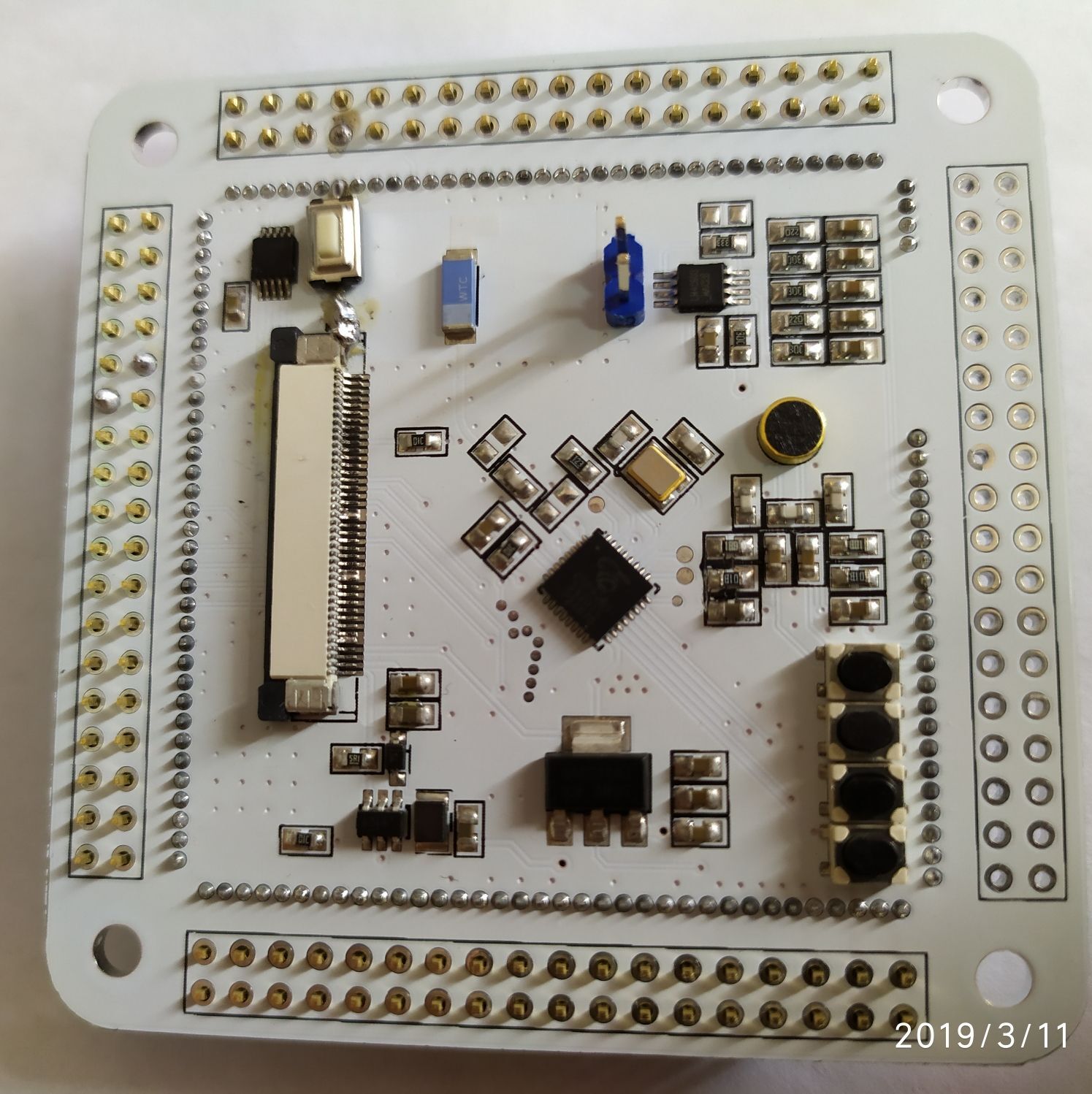

https://whycan.cn/files/members/3/QQ20190311175226.jpg

焊上按键,烧录方便多了。

https://whycan.cn/files/members/3/QQ20190311164816.jpg

焊上排针, 串口输出正常。

用 sunxi-fel 测试烧录, 也正常。

请教一下,这个fel模式是通过哪个管脚进入的?

离线

楼主 #48 2019-05-15 11:05:13 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,441

- 积分: 9202

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

晕哥 说:https://whycan.cn/files/members/3/QQ20190311175226.jpg

焊上按键,烧录方便多了。

https://whycan.cn/files/members/3/QQ20190311164816.jpg

焊上排针, 串口输出正常。

用 sunxi-fel 测试烧录, 也正常。

请教一下,这个fel模式是通过哪个管脚进入的?

1. 不插TF卡 或 TF卡不能启动系统, 那短路 SPI FLASH 的 CLK 引脚到 GND, 再插入USB线即可。

2. 制作一个特殊的 TF卡: https://whycan.cn/t_2429.html

制作一个特殊的TF卡系统, 插入即进入 fel, 这样不用短路也能烧录:

wget https://github.com/linux-sunxi/sunxi-tools/raw/master/bin/fel-sdboot.sunxi

dd if=fel-sdboot.sunxi of=/dev/sdX bs=1024 seek=8 ####sdX替换成你的TF卡实际磁盘设备

强烈建议用第二种, 省得去插线拔线。

离线

#49 2019-05-26 14:25:14 分享评论

- kkzhong

- 会员

- 注册时间: 2017-11-15

- 已发帖子: 7

- 积分: 7

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

有一点不明白,为啥都升级了ddr2,手册上还是说只支持1024的LCD

显示模块部分已经设计好了,只改了封装和DDR,自然分辨率不会有变化

中科世为HMI 方案 FlyThing OS

https://developer.flythings.cn

联系电话 13728931930

离线

#50 2019-07-06 17:03:56 分享评论

- allen

- 会员

- 注册时间: 2019-07-06

- 已发帖子: 2

- 积分: 2

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

晕哥 说:购买链接:

小智极客 索智 全志 S3 核心板 开发板Linux系统: https://item.taobao.com/item.htm?id=588502966831

小智极客 索智/全志S3全功能底板: https://item.taobao.com/item.htm?id=588722094008

全志/索智S3芯片零售,内置128MB DDR3内存: https://item.taobao.com/item.htm?id=588754350002

QQ交流群: 202900925

感谢晕哥以及晕哥平台的大力支持~

已购买,即将开启S3神奇之旅

离线

#51 2019-07-27 09:14:59 分享评论

- awoyzc

- 会员

- 注册时间: 2019-07-27

- 已发帖子: 1

- 积分: 1

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

没得卖了。谁有卖我一个呗

离线

楼主 #53 2019-10-14 09:20:41 分享评论

#54 2019-11-12 11:37:09 分享评论

- silvereyes

- 会员

- 注册时间: 2018-08-27

- 已发帖子: 14

- 积分: 4

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

这个zeta哪里能下载啊?

离线

#55 2019-11-12 13:35:11 分享评论

- 小智科技

- 会员

- 注册时间: 2019-03-10

- 已发帖子: 92

- 积分: 83

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

这个zeta哪里能下载啊?

上面有QQ群号,群文件里有

离线

#56 2019-11-12 13:35:42 分享评论

- 小智科技

- 会员

- 注册时间: 2019-03-10

- 已发帖子: 92

- 积分: 83

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

没得卖了。谁有卖我一个呗

新S3开发板购买连接 https://item.taobao.com/item.htm?id=607207528669

最近编辑记录 小智科技 (2019-11-12 13:36:29)

离线

#57 2019-11-12 13:36:17 分享评论

- 小智科技

- 会员

- 注册时间: 2019-03-10

- 已发帖子: 92

- 积分: 83

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

@小智科技, @晕哥,这个项目挺好的啊。小智极客,淘宝链接,咋下架了啊。老弟?

这个挺不错的啊,不公开卖是把?

离线

#58 2019-11-12 13:37:33 分享评论

- 小智科技

- 会员

- 注册时间: 2019-03-10

- 已发帖子: 92

- 积分: 83

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

@晕哥 麻烦晕哥把帖子的购买链接更新一下,谢谢哈~

离线

#59 2019-11-17 17:22:43 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,140

- 积分: 1092.5

Re: 感谢小智极客赠送的全志/索智S3开发板样品!小巧精致,漂亮大方! (多图预警)

买了新板子,请问有对应主线源码吗?晕哥用的是是索智的SDK吧,

离线

楼主 #60 2019-11-17 17:34:33 分享评论

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发