楼主 #1 2019-03-27 17:25:24 分享评论

- yangzl

- 会员

- 注册时间: 2019-03-27

- 已发帖子: 36

- 积分: 36

有关全志V3s硬件电路上的关于SPI flash的问题

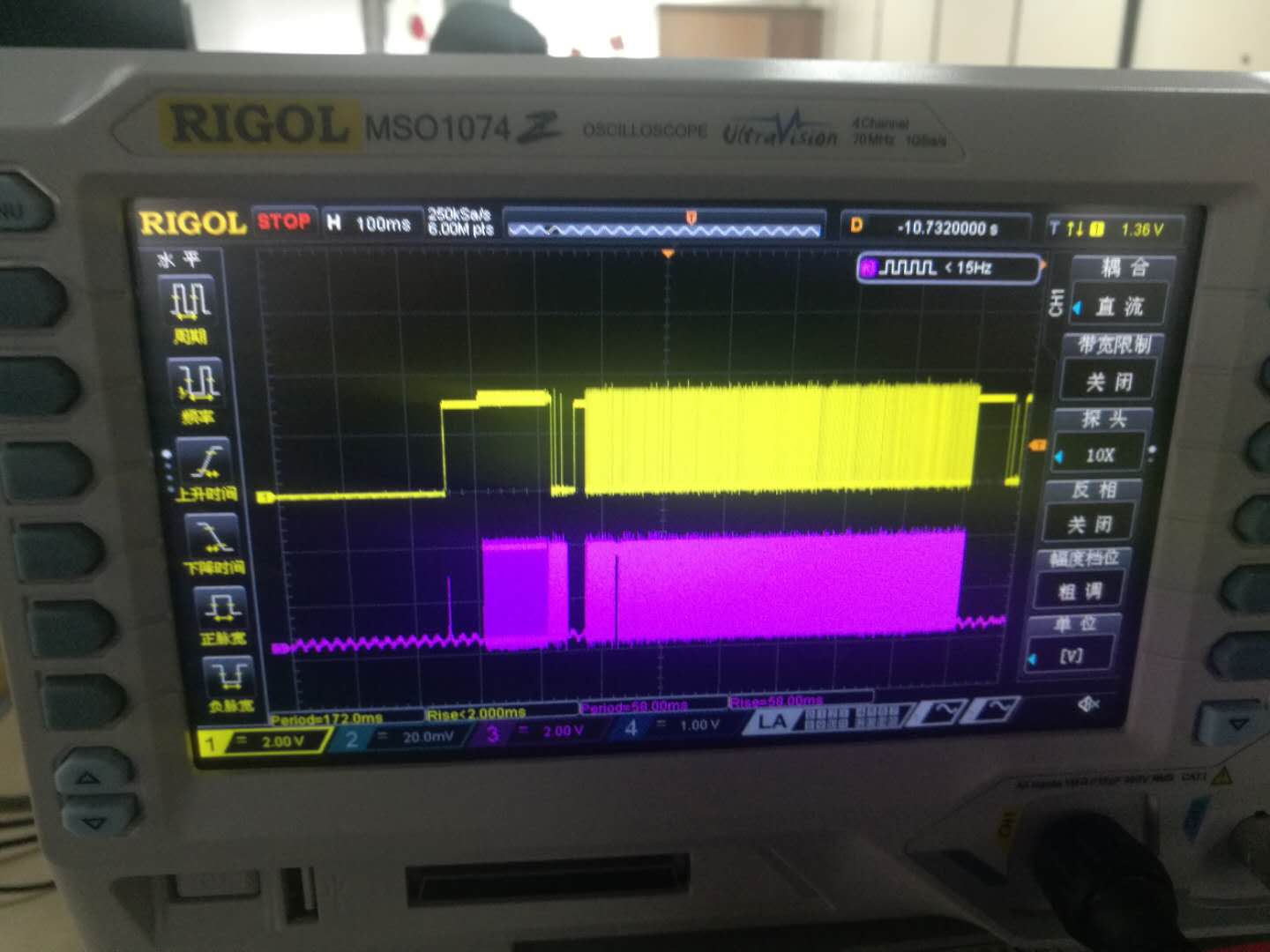

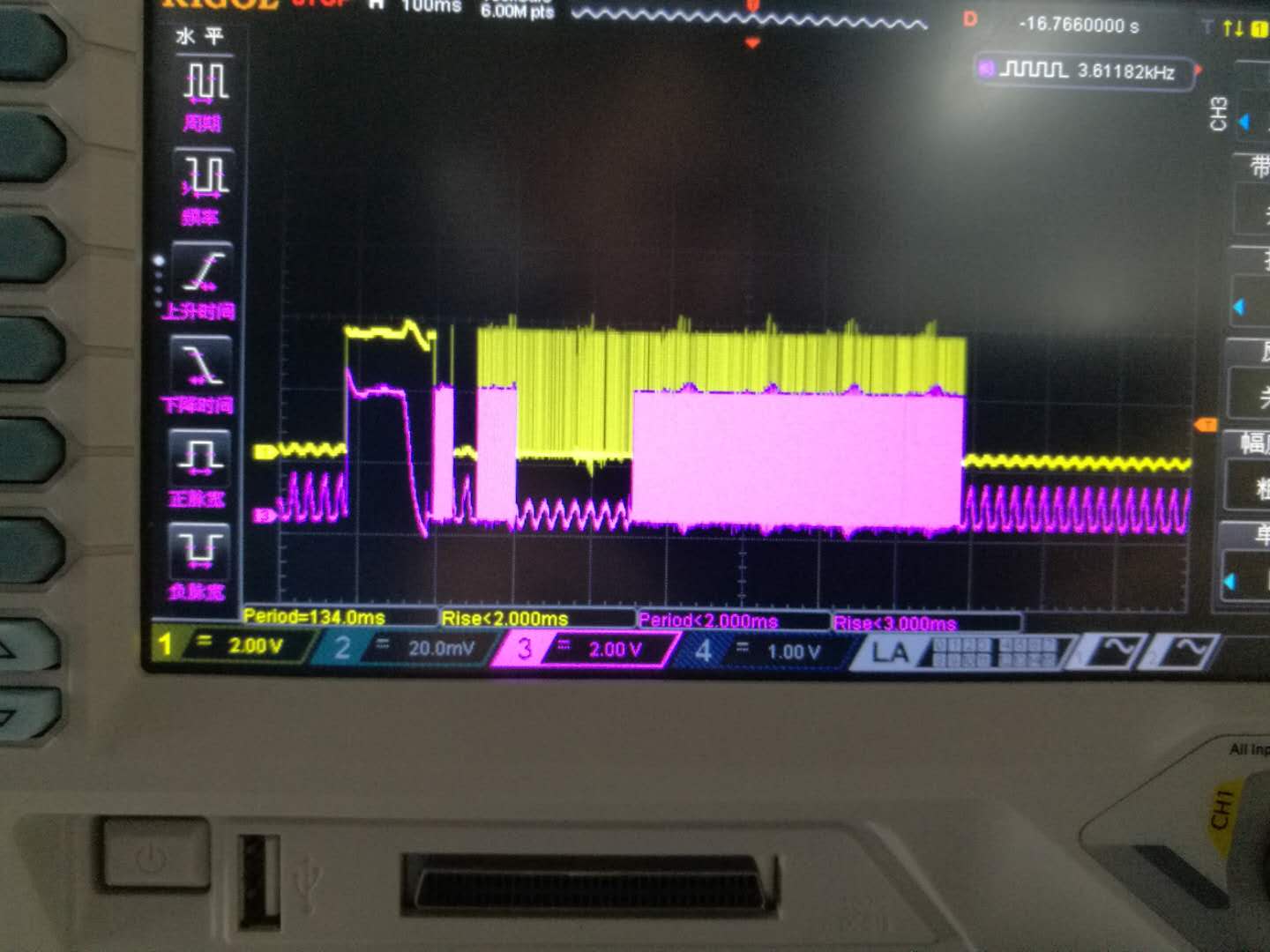

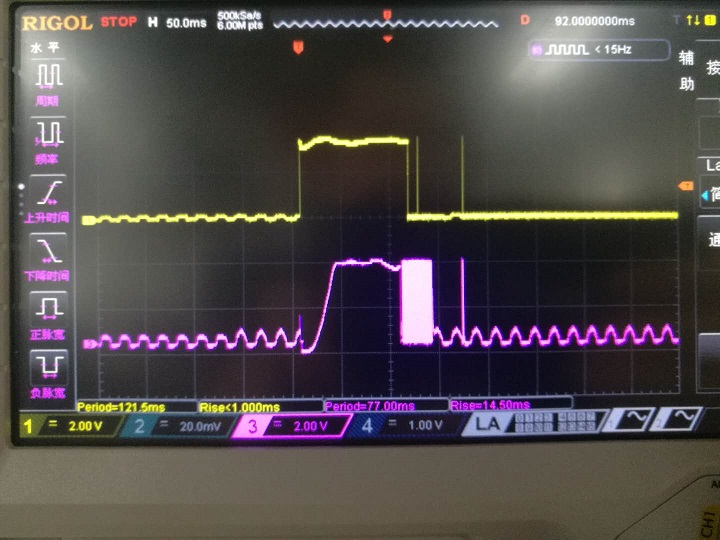

我在lichee zero开发板上完成了SPI flash固件编译生成,在开发板上也可以正常运行,而后将固件烧录到自制的开发板中,发现无法正常启动,而后接上SPI引脚观察引脚波形,发现uboot未读取成功,不知道是SPI引脚与芯片直连就可以还是需要中间添加其他配件。具体的波形如下图

这是荔枝派开发板上读取uboot的MOSI和MISO的波形。

这是自制开发板上读取uboot的MOSI和MISO的波形。

想问硬件上要怎么连接才能正常读取

离线

楼主 #2 2019-03-27 17:37:54 分享评论

- yangzl

- 会员

- 注册时间: 2019-03-27

- 已发帖子: 36

- 积分: 36

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

硬件上现在是芯片SPI引脚和flash是直连的,中间没有任何配件,很奇怪的是可以通过USB烧写固件,也验证了烧写成功,但是芯片无法从SPI读取到这个uboot固件,有人知道这应该怎么解决吗?万分感谢!

离线

楼主 #4 2019-03-27 18:49:58 分享评论

- yangzl

- 会员

- 注册时间: 2019-03-27

- 已发帖子: 36

- 积分: 36

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

你是如何确定 u-boot 没有启动成功的? 是用示波器确定? 还是用串口输出确定?

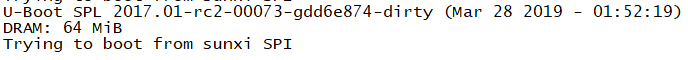

刚刚再次确认了一下,这一段是自制开发板上用示波器显示读取UBOOT的区域,然后就没有继续读取dtb、kernal,串口只打印了“”这一个符号,这个uboot固件在荔枝派上能正常运行串口0打印。

因为在示波器上读取两者之间波形不一致,以及串口只打印了“”这一个符号所以觉得uboot没有启动成功。

请问这个问题可能是出在哪里?谢谢回复

离线

#7 2019-03-28 09:38:50 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

如果串口引脚用的和荔枝派一样的话,直接调换两个flash看看

离线

楼主 #8 2019-03-28 10:59:49 分享评论

- yangzl

- 会员

- 注册时间: 2019-03-27

- 已发帖子: 36

- 积分: 36

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

既然能烧录,说明硬件问题应该不大,至少能启动spl (boot0)才对,spl时串口是有输出的。

还是检查有没有弄错串口

三组电压都是检查过没有问题的。

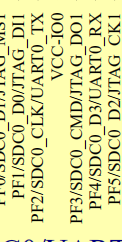

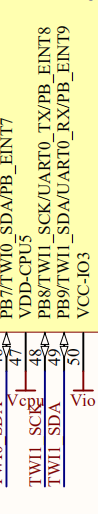

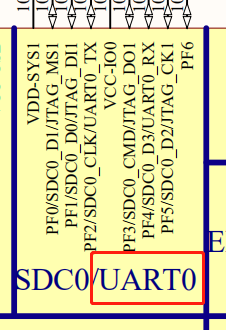

仔细检查了一下串口,发现原理图里面有两个串口0的引脚,PB和PF,之前看到原理图就直接把芯片上方的PF引脚当成串口0了,看到uboot里配置的串口0PB引脚输出,待会尝试重新编译一下固件烧写进去

然后之前换了块芯片USB调试现在就出问题了。。。。我晕。。。硬件上也没有短路看不出什么问题,电脑显示设备描述符出错,只能换个芯片重新焊试试了,未完待续.......

最近编辑记录 yangzl (2019-03-28 11:00:14)

离线

#9 2019-03-28 11:07:15 分享评论

- 超级萌新

- 会员

- 注册时间: 2018-05-04

- 已发帖子: 408

- 积分: 407

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

我记得 荔枝派zero 默认串口是 PB8,PB9

离线

楼主 #10 2019-03-28 11:13:07 分享评论

- yangzl

- 会员

- 注册时间: 2019-03-27

- 已发帖子: 36

- 积分: 36

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

我记得 荔枝派zero 默认串口是 PB8,PB9

一个大大的UART0在上面,谁又能想到.......

离线

楼主 #11 2019-03-28 12:02:28 分享评论

- yangzl

- 会员

- 注册时间: 2019-03-27

- 已发帖子: 36

- 积分: 36

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

既然能烧录,说明硬件问题应该不大,至少能启动spl (boot0)才对,spl时串口是有输出的。

还是检查有没有弄错串口

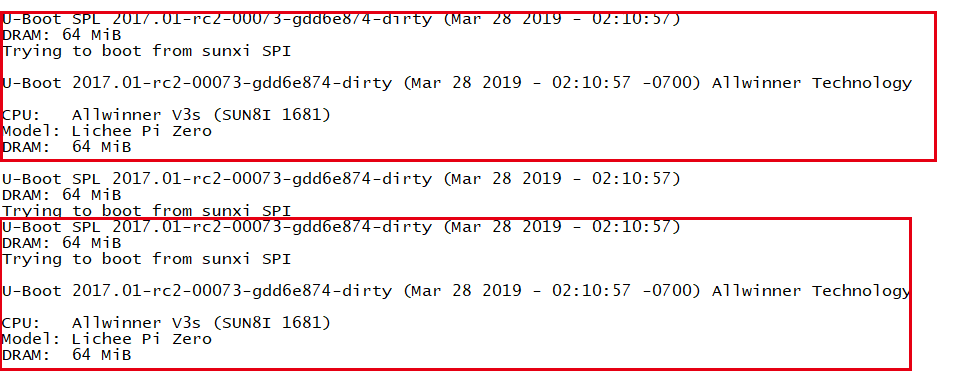

USB调试串口已经可以烧写了,然后我修改了sun8i-v3s.dtsi里的PB8、PB9为PF2、PF4,重新编译,烧录进去后

发现还是如上图没有任何输出,是否还能有其他方法确认uboot启动正常?感谢回复

离线

楼主 #13 2019-03-28 14:20:20 分享评论

- yangzl

- 会员

- 注册时间: 2019-03-27

- 已发帖子: 36

- 积分: 36

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

@yangzl 先接 PB8, PB9 看是否有输出, 再谋划改代码吧。

尝试过将原有可用的固件烧写进去,用示波器查看PB8和PB9的电平输出,没有丝毫波动,应该是uboot并没有启动成功吧

离线

#14 2019-03-28 14:34:10 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,437

- 积分: 9202

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

晕哥 说:@yangzl 先接 PB8, PB9 看是否有输出, 再谋划改代码吧。

尝试过将原有可用的固件烧写进去,用示波器查看PB8和PB9的电平输出,没有丝毫波动,应该是uboot并没有启动成功吧

注意: sunxi-fel 烧录的时候 不需要再短路 spi 的引脚了

sunxi-fel 没有校验机制, 到之后也不知道有没有写进去, 写进去的对不对,

你不接 flash, 他一样能告诉你写入成功。

sunxi-fel 的 read 功能貌似也有问题, 读的数据不对。

接逻辑分析仪或者 USB串口模块试一试.

至少能启动 u-boot 最开始的 spl(boot0),

这里有几行串口输出。

最后, 你交换一下 荔枝派(能正常启动的板子)的flash测试。

离线

楼主 #15 2019-03-28 16:13:41 分享评论

- yangzl

- 会员

- 注册时间: 2019-03-27

- 已发帖子: 36

- 积分: 36

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

yangzl 说:晕哥 说:@yangzl 先接 PB8, PB9 看是否有输出, 再谋划改代码吧。

尝试过将原有可用的固件烧写进去,用示波器查看PB8和PB9的电平输出,没有丝毫波动,应该是uboot并没有启动成功吧

注意: sunxi-fel 烧录的时候 不需要再短路 spi 的引脚了

sunxi-fel 没有校验机制, 到之后也不知道有没有写进去, 写进去的对不对,

你不接 flash, 他一样能告诉你写入成功。sunxi-fel 的 read 功能貌似也有问题, 读的数据不对。

接逻辑分析仪或者 USB串口模块试一试.

至少能启动 u-boot 最开始的 spl(boot0),

这里有几行串口输出。最后, 你交换一下 荔枝派(能正常启动的板子)的flash测试。

在使用sunxi-fel烧录前都会使用“sunxi-fei spiflash-info”命令确认能否读取到flash芯片信息后再进行烧写,短接SPI引脚使用镊子短接,识别到就松开了。

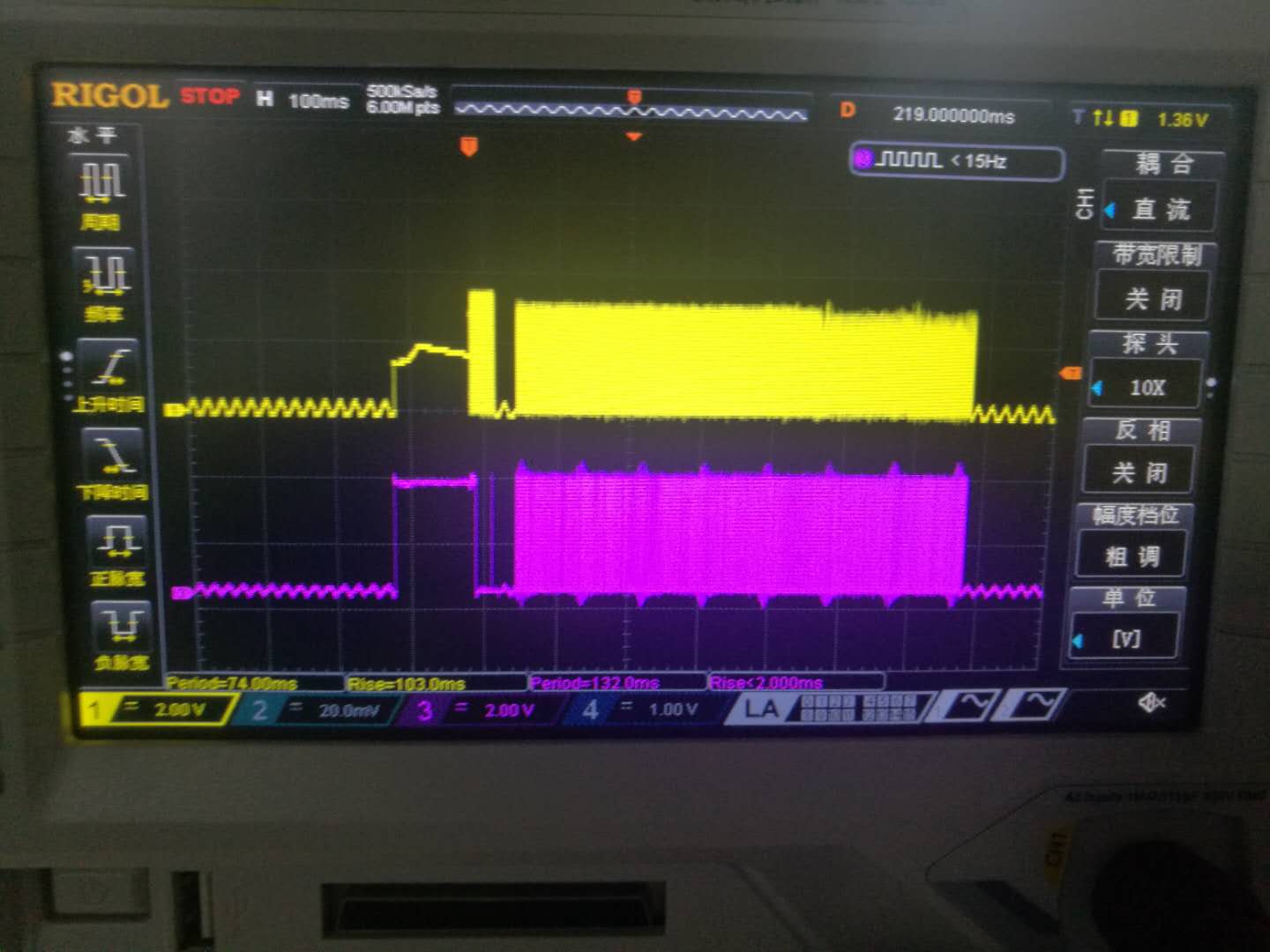

然后在确认荔枝派开发板上的固件可以正常串口输出后,把两块板子的flash更换,结果发现SPI引脚都没有读取了,如图。

黄线DO,紫线是DI。

之前一块flash在荔枝派上重新烧写并检测能用,再更换回去,还是如上图......

我的内心好绝望。。。

感谢回复

最近编辑记录 yangzl (2019-03-28 16:14:50)

离线

#16 2019-03-28 16:26:11 分享评论

- jimmy

- 会员

- 注册时间: 2017-10-29

- 已发帖子: 316

- 积分: 315

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

这个 SPI 读 Flash 的 boot0 操作, 是 BROM 完成的,

这时候只在 SRAM 里面操作, 并没有涉及到 DRAM 的操作,

所以越看越奇怪。

交换过去的荔枝派板子, SPI 波形正常?

离线

楼主 #17 2019-03-28 16:58:25 分享评论

- yangzl

- 会员

- 注册时间: 2019-03-27

- 已发帖子: 36

- 积分: 36

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

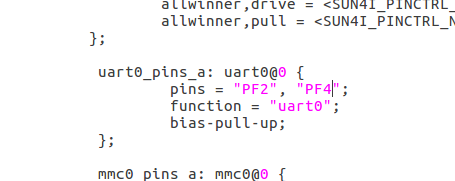

发现了原理图和实物有些差异,把线直接引出后现在有串口打印了

然后没有进行下一步了

离线

楼主 #19 2019-03-28 17:16:53 分享评论

- yangzl

- 会员

- 注册时间: 2019-03-27

- 已发帖子: 36

- 积分: 36

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

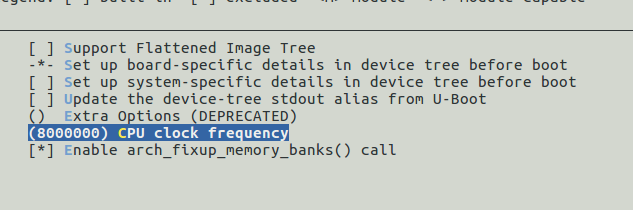

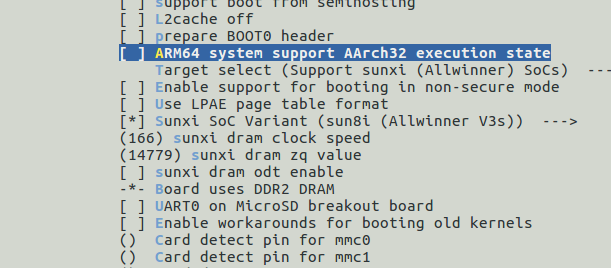

感觉有点是 板子布线问题,试一试在 uboot 把 dram和cpu主频都降下来,

分别降为: 166Mhz,800Mhz

重新编译试一试

尝试了一下,更改了下面两个参数

每次串口输出信息不同,下图

感谢回复

离线

楼主 #21 2019-03-28 17:27:15 分享评论

- yangzl

- 会员

- 注册时间: 2019-03-27

- 已发帖子: 36

- 积分: 36

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

这两次可能是 spl 和 uboot 两次报出来的信息。

现在还没有启动?

没有没有,现在到那个红色框范围就停止了,使用的固件明明是荔枝派可以使用的(挠头)

离线

#22 2019-03-28 17:43:24 分享评论

- jimmy

- 会员

- 注册时间: 2017-10-29

- 已发帖子: 316

- 积分: 315

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

是不是按晕哥套路改了之后, 比17楼有进步?

能启动到 u-boot ?

离线

楼主 #23 2019-03-28 18:00:01 分享评论

- yangzl

- 会员

- 注册时间: 2019-03-27

- 已发帖子: 36

- 积分: 36

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

是不是按晕哥套路改了之后, 比17楼有进步?

能启动到 u-boot ?

是的,踏出了一小步,也就这样设置才能读出uboot,下面示波器图看出来了,但是uboot并没有继续往下走了

离线

楼主 #25 2019-03-29 11:53:05 分享评论

- yangzl

- 会员

- 注册时间: 2019-03-27

- 已发帖子: 36

- 积分: 36

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

看样子,有可能频率还得降下来才行

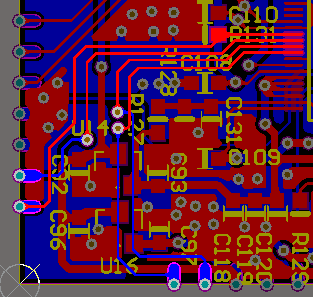

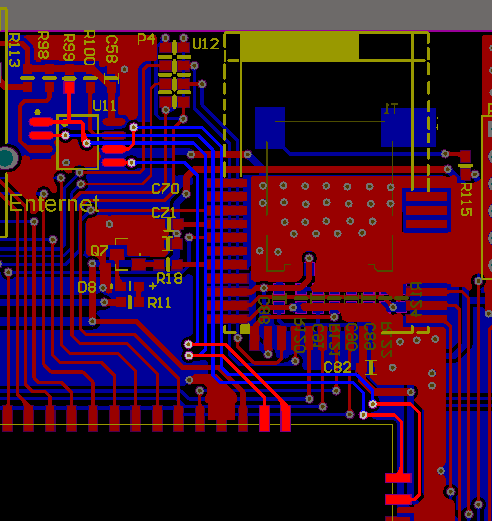

如果说主频要降频运行的话,那应该是硬件设计的问题吧

硬件设计是底板+核心板的设计,图上高亮部分是芯片连接FLASH的地方,芯片的三组电压都正常德华,会不会是flash离芯片太远导致的问题呢?

感谢回复

最近编辑记录 yangzl (2019-03-29 11:55:37)

离线

#26 2019-03-29 13:38:22 分享评论

- 天边那朵白云

- 会员

- 注册时间: 2019-03-18

- 已发帖子: 16

- 积分: 16

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

1. 检查 1.2V, 1.8V, 看是否波纹过大, 可以加大电容或 dcdc的电感。

2. 调低 SPI 频率, 调到 10Mhz 以下试一试。

离线

楼主 #27 2019-03-29 14:33:32 分享评论

- yangzl

- 会员

- 注册时间: 2019-03-27

- 已发帖子: 36

- 积分: 36

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

1. 检查 1.2V, 1.8V, 看是否波纹过大, 可以加大电容或 dcdc的电感。

2. 调低 SPI 频率, 调到 10Mhz 以下试一试。

spi频率具体在哪里可以调低?

感谢回复

离线

#28 2019-03-29 15:01:40 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,437

- 积分: 9202

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

这个 60000000 就是 spi 的频率:

sf probe 0 60000000; sf read 0x80c00000 0x70000 0x10000; sf read 0x80008000 0x80000 0x400000; bootz 0x80008000 - 0x80c00000

离线

楼主 #29 2019-04-01 17:24:54 分享评论

- yangzl

- 会员

- 注册时间: 2019-03-27

- 已发帖子: 36

- 积分: 36

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

开启内核的时候,1.2V拉扯电流太多,导致压降突然下降,导致一次0.4V的下降,持续十几ms,导致内核不能正常启动;现把手上两个LDO并联解决了;后期更换LDO。

离线

#30 2019-04-01 17:57:42 分享评论

- smartcar

- 会员

- 注册时间: 2018-02-19

- 已发帖子: 735

- 积分: 735

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

开启内核的时候,1.2V拉扯电流太多,导致压降突然下降,导致一次0.4V的下降,持续十几ms,导致内核不能正常启动;现把手上两个LDO并联解决了;后期更换LDO。

那么多参考电路,你竟然选了LDO, 可能也可以,但是你得加个很大很大的电容。

离线

#31 2024-01-22 15:13:52 分享评论

- dsp2000

- 会员

- 注册时间: 2024-01-21

- 已发帖子: 29

- 积分: 4

Re: 有关全志V3s硬件电路上的关于SPI flash的问题

用DC/DC会比较好

离线

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发