楼主 #1 2018-04-09 14:57:59 分享评论

- tom

- 会员

- 注册时间: 2018-03-14

- 已发帖子: 128

- 积分: 122.5

N32926 Capture驱动

新塘SDK的Capture驱动支持的Sensor代码均为V4L1的接口,有没有哪位大侠做成V4L2接口的?有没有相关移植经验可以借鉴?

离线

楼主 #3 2018-04-09 17:21:44 分享评论

- tom

- 会员

- 注册时间: 2018-03-14

- 已发帖子: 128

- 积分: 122.5

Re: N32926 Capture驱动

目前网络上多数测试程序都是V4L2接口的,想改为该接口,方便调试。

我的需求是,前端sensor给的标清图像到Capture端口,驱动要自己做,因此想有一个比较成熟的应用程序配合调试驱动。 这条路看来不好走通了,只能在现有的sensor驱动上面进行改动,配合新塘的例子vin_demo一起调试

离线

#4 2018-04-09 22:10:01 分享评论

- awfans

- 会员

- 注册时间: 2018-04-03

- 已发帖子: 264

- 积分: 264

Re: N32926 Capture驱动

要把驱动从V4L改成V4L2应该是一个不小的工程, 建议还是改应用吧.

离线

楼主 #5 2018-04-20 10:59:48 分享评论

- tom

- 会员

- 注册时间: 2018-03-14

- 已发帖子: 128

- 积分: 122.5

Re: N32926 Capture驱动

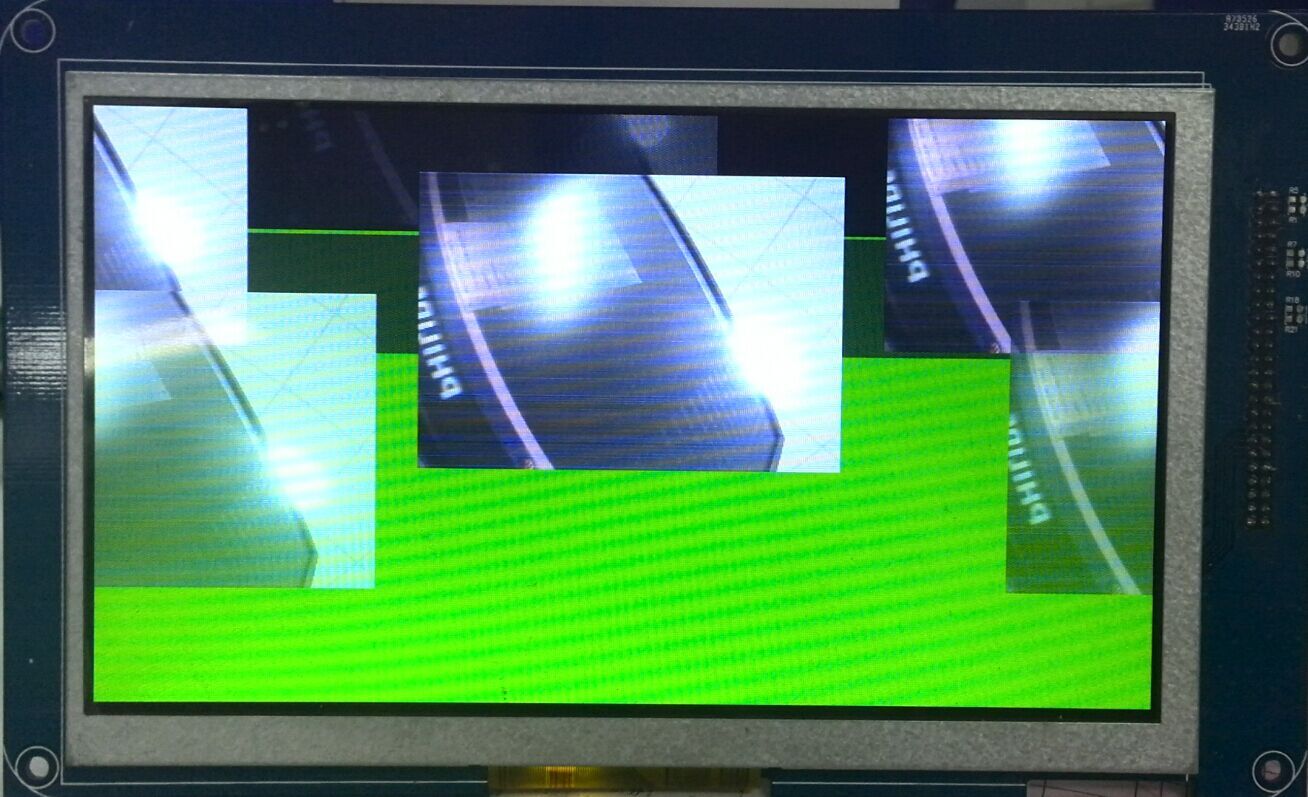

采集端口分为packet和Planar两个通道进入内存,目前Planar通道正常了,Packet通道通过VPOST预览不对。

VPSOT的分辨率设置为720*576(TV分辨率),采集分辨率为640*480,这种情况下,应用程序调用ioctl(VIDIOCSWIN)设置预览窗口,该ioctl对应的设置函数为static unsigned int vin_ioctl_set_overlay_window(struct file *file,unsigned int cmd,void *arg),

该函数主要操作就是设置Packet基地址和output frame pixel stride寄存器。

为了让图像通过Framebuffer直接显示。我的理解是,由于行方向分辨率不同,为了让图像正常显示,Packet数据包的DMA硬件,应当是每行跳跃720个像素,然后存储到内存, SetStride函数应该就是完成这个功能,这样的话,图像在内存中就不是连续的了,不止理解是否有误?

离线

#6 2018-04-20 11:43:20 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,442

- 积分: 9202

Re: N32926 Capture驱动

采集端口分为packet和Planar两个通道进入内存,目前Planar通道正常了,Packet通道通过VPOST预览不对。

VPSOT的分辨率设置为720*576(TV分辨率),采集分辨率为640*480,这种情况下,应用程序调用ioctl(VIDIOCSWIN)设置预览窗口,该ioctl对应的设置函数为static unsigned int vin_ioctl_set_overlay_window(struct file *file,unsigned int cmd,void *arg),

该函数主要操作就是设置Packet基地址和output frame pixel stride寄存器。

为了让图像通过Framebuffer直接显示。我的理解是,由于行方向分辨率不同,为了让图像正常显示,Packet数据包的DMA硬件,应当是每行跳跃720个像素,然后存储到内存, SetStride函数应该就是完成这个功能,这样的话,图像在内存中就不是连续的了,不止理解是否有误?

这个题目难度太大,邀请了好几个朋友都不会。

离线

楼主 #7 2018-04-20 13:32:53 分享评论

- tom

- 会员

- 注册时间: 2018-03-14

- 已发帖子: 128

- 积分: 122.5

Re: N32926 Capture驱动

感谢版主关注。这个问题确实比较麻烦,需要理解Capture和VPOST两个模块的工作原理。nuvoton提供的手册,只有寄存器定义,没有原理描述,我也只能根据寄存器,揣测原理。

我显示的图像大体都对,我现在判断问题可能出在视频输入的三缓冲和显示输出的缓冲地址的配合上面

离线

#8 2018-04-20 13:43:58 分享评论

- goodgoodstudy

- 会员

- 注册时间: 2017-09-15

- 已发帖子: 61

- 积分: 61

Re: N32926 Capture驱动

没有看太明白,新唐提供的vin_demo不能实现什么功能呢?你是想基于vin做什么改进?嵌入到自己的应用?

离线

楼主 #9 2018-04-20 14:24:36 分享评论

- tom

- 会员

- 注册时间: 2018-03-14

- 已发帖子: 128

- 积分: 122.5

Re: N32926 Capture驱动

没有看太明白,新唐提供的vin_demo不能实现什么功能呢?你是想基于vin做什么改进?嵌入到自己的应用?

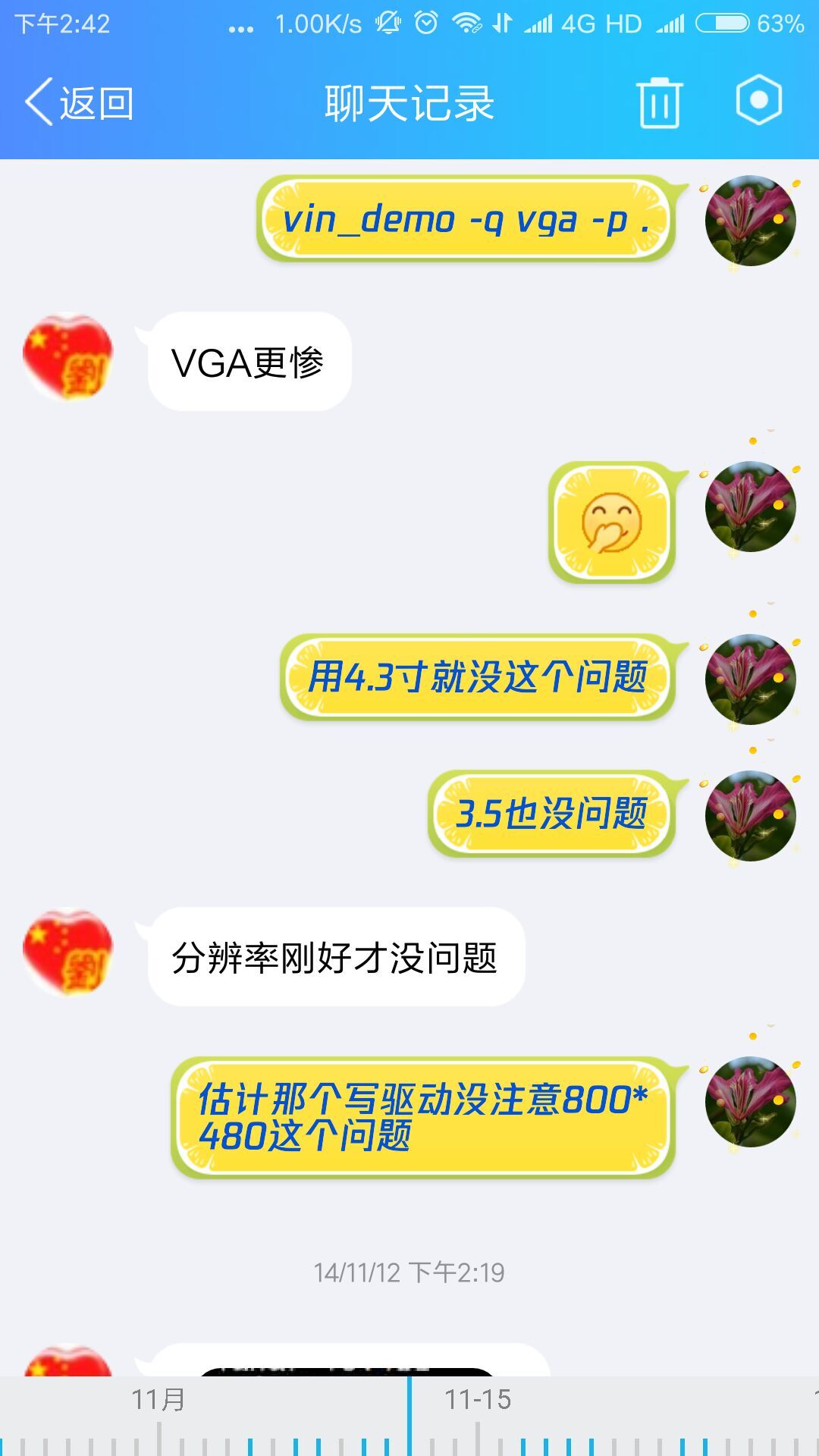

vin_demo 在输入输出分辨率都相同的时候,是正确的。我现在显示分辨率设置为720,输入分辨率为640,显示就不准确了,有可能是我的姿势不对哦。。。

PS,输入 输出驱动我都有改动,满足我的系统的输入输出分辨率、时序要求。

离线

楼主 #11 2018-04-20 14:51:11 分享评论

- tom

- 会员

- 注册时间: 2018-03-14

- 已发帖子: 128

- 积分: 122.5

Re: N32926 Capture驱动

是这个问题。可能我的分辨率和你这个有区别,现象不完全相同。我目前用的TV输出,分辨率改到720*576了。

离线

楼主 #13 2018-04-20 15:05:42 分享评论

- tom

- 会员

- 注册时间: 2018-03-14

- 已发帖子: 128

- 积分: 122.5

Re: N32926 Capture驱动

不是什么高科技,如能解决,可以分享给大家。如果其他人凑巧有类似硬件碰到该问题,可以试试,是否有普遍性

离线

楼主 #14 2018-04-20 16:32:45 分享评论

- tom

- 会员

- 注册时间: 2018-03-14

- 已发帖子: 128

- 积分: 122.5

Re: N32926 Capture驱动

解决了。。。。自己使用的问题,吐血。。。 没有合适的资料完全是自己瞎琢磨呀

内核配置的时候,需要将图像预览尺寸设置为FB的尺寸。 当尺寸设置小了,将该区域映射为FB的地址,显然会有图像重叠。

前面关于Capture 机制的分析也没问题

离线

#16 2018-05-05 14:14:36 分享评论

- dgtg

- 会员

- 注册时间: 2017-11-08

- 已发帖子: 275

- 积分: 229.5

Re: N32926 Capture驱动

请问一下楼主,capture是什么信号源?是sensor还是TV decoder ?

离线

楼主 #17 2018-05-08 22:19:06 分享评论

- tom

- 会员

- 注册时间: 2018-03-14

- 已发帖子: 128

- 积分: 122.5

Re: N32926 Capture驱动

请问一下楼主,capture是什么信号源?是sensor还是TV decoder ?

我用fpga模拟的sensor时序 tv解码应该类似,不过一般是隔行的了

离线

#18 2020-08-13 16:40:06 分享评论

- szchen2006

- 会员

- 注册时间: 2019-10-09

- 已发帖子: 216

- 积分: 166.5

Re: N32926 Capture驱动

学习了!

离线

#19 2020-08-13 16:47:14 分享评论

- szchen2006

- 会员

- 注册时间: 2019-10-09

- 已发帖子: 216

- 积分: 166.5

Re: N32926 Capture驱动

请教一下,V4L1接口的信号线怎样定义的?V4L2呢?谢谢你不吝赐教!

离线

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发