楼主 # 2022-12-24 18:48:54 分享评论

- stm32f407

- 会员

- 注册时间: 2022-10-20

- 已发帖子: 7

- 积分: 23

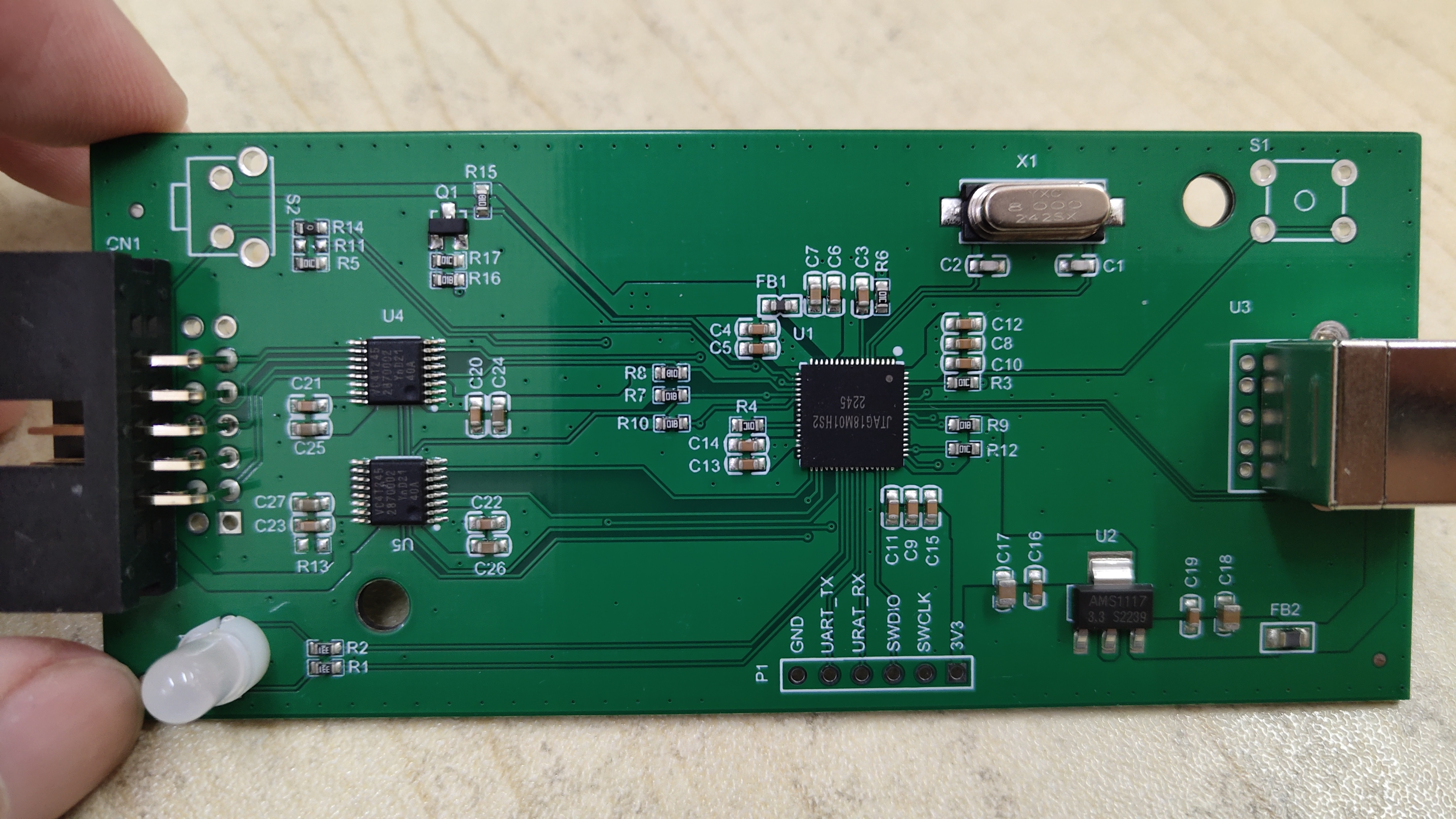

拆解了一块USB Blaser II,内部芯片方案令人好奇

一开始以为是用的68013+FPGA的方案制作的USB Blaster II,但是拆开以后发现里面的主芯片只有一个,然后是电平转换芯片。

其中主芯片的丝印被磨掉,然后看具体的接口像是用的带有高速USB的ARM芯片,然后模拟USB Blaster II的协议,然后把命令转换成对应的JTAG接口操作,再通过电平转换芯片与外部连接。

所以,问题来了,里面用的主控是啥?

论坛里有大佬能科普下这是什么方案么?

离线

#1 2022-12-25 00:14:02 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 拆解了一块USB Blaser II,内部芯片方案令人好奇

有没有一种可能,里面不是ARM的核心呢🤣

离线

#2 2022-12-25 07:49:11 分享评论

- echo

- 会员

- 注册时间: 2020-04-16

- 已发帖子: 364

- 积分: 370.5

Re: 拆解了一块USB Blaser II,内部芯片方案令人好奇

随便一个带USB的单片机就可以搞定,比如CH552

离线

楼主 #3 2022-12-25 09:51:11 分享评论

- stm32f407

- 会员

- 注册时间: 2022-10-20

- 已发帖子: 7

- 积分: 23

Re: 拆解了一块USB Blaser II,内部芯片方案令人好奇

随便一个带USB的单片机就可以搞定,比如CH552

这个我能理解您说的意思,确实随便用一个带USB的单片机都能搞定。但是这个是模拟了USB Blaster II,相比于一般的FullSpeed提升到了HighSpeed,速度上也更快了,每一个USB数据包也从64Bytes提升到了512Bytes。

我感觉像是一个带有HighSpeed USB的单片机实现的,然后把接收到的数据内部模拟产生JTAG协议。

离线

#4 2022-12-26 09:33:21 分享评论

- echo

- 会员

- 注册时间: 2020-04-16

- 已发帖子: 364

- 积分: 370.5

Re: 拆解了一块USB Blaser II,内部芯片方案令人好奇

@stm32f407

在这里USBHS并没有什么意义,12M的USBFS充分优化以后足够用了。就好比你在国道上开一辆F1赛车,并不比买菜车更好。

离线

#5 2022-12-26 11:00:56 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 拆解了一块USB Blaser II,内部芯片方案令人好奇

论坛好多 CH552 方案的

离线

#6 2022-12-26 11:10:17 分享评论

- david

- 会员

- 注册时间: 2018-03-05

- 已发帖子: 397

- 积分: 328.5

Re: 拆解了一块USB Blaser II,内部芯片方案令人好奇

说明你用的fpga还不够大 ;-)

离线

#7 2022-12-26 13:11:50 分享评论

- DENHJD

- 会员

- 注册时间: 2017-12-24

- 已发帖子: 42

- 积分: 141.5

Re: 拆解了一块USB Blaser II,内部芯片方案令人好奇

有没有可能这是RiscV呢 ![]()

如果没错的话应该是CH32V307WCU6

最近编辑记录 DENHJD (2022-12-26 13:12:10)

离线

楼主 #8 2022-12-26 17:38:02 分享评论

- stm32f407

- 会员

- 注册时间: 2022-10-20

- 已发帖子: 7

- 积分: 23

Re: 拆解了一块USB Blaser II,内部芯片方案令人好奇

@stm32f407

在这里USBHS并没有什么意义,12M的USBFS充分优化以后足够用了。就好比你在国道上开一辆F1赛车,并不比买菜车更好。

大佬,您好,您的工作让我深深感到敬佩,能够得到您的回复也很荣幸,但是我没有贬低USBFS的意思。我在使用Stratix V系列的FPGA时候,对比过速度上的区别,II代的USBHS的TCK时钟频率可以到24M,不管怎么说都比FS要快,尤其是在固化的时候,我用I代要等很久才行,换成II代有了很大的改善。然后就自己也买了一个Blaster II,因为对此感到了一些好奇,买了一个后顺便拆开看看别人是怎么做的,然后把里面的电路板照片分享了出来。

最近编辑记录 stm32f407 (2022-12-26 18:18:51)

离线

楼主 #9 2022-12-26 17:43:06 分享评论

- stm32f407

- 会员

- 注册时间: 2022-10-20

- 已发帖子: 7

- 积分: 23

Re: 拆解了一块USB Blaser II,内部芯片方案令人好奇

有没有可能这是RiscV呢

如果没错的话应该是CH32V307WCU6

不亏是大佬,我对比了下手册上的引脚,几乎可以99%确定是这个型号,感谢大佬提供的思路。

离线

#10 2022-12-26 19:47:46 分享评论

- david

- 会员

- 注册时间: 2018-03-05

- 已发帖子: 397

- 积分: 328.5

Re: 拆解了一块USB Blaser II,内部芯片方案令人好奇

这颗市面上好像都是LQFP的

离线

#11 2022-12-26 19:52:35 分享评论

- david

- 会员

- 注册时间: 2018-03-05

- 已发帖子: 397

- 积分: 328.5

Re: 拆解了一块USB Blaser II,内部芯片方案令人好奇

离线

#12 2022-12-27 09:42:12 分享评论

- echo

- 会员

- 注册时间: 2020-04-16

- 已发帖子: 364

- 积分: 370.5

Re: 拆解了一块USB Blaser II,内部芯片方案令人好奇

@stm32f407

也许是你的I代太差了而已。USB那边你再快,JTAG这边也受限于硬件SPI的极限速度,更何况有些场景比如AS下载无法利用硬件SPI来加速,软件IO速度会更慢。TCK频率越高稳定性也越差,并不是越高越好。480M的USBHS用在这里完全是大炮轰蚊子。其实cy7c68013版本的usb-blaster就是USBHS,然而它是速度最慢的usb-blaster。

最近编辑记录 echo (2022-12-27 09:54:13)

离线

楼主 #13 2022-12-27 13:31:06 分享评论

- stm32f407

- 会员

- 注册时间: 2022-10-20

- 已发帖子: 7

- 积分: 23

Re: 拆解了一块USB Blaser II,内部芯片方案令人好奇

@echo

是这么个道理,正常来说I代的速度如果优化好了,也可以得到很好的性能。使用USBHS不仅需要USB接口的支持,同时也受限于SPI的速度,最多也只能说HS能够提供大于12M的数据传输带宽,但是也没能到理论上的480M速度,最多也只能到24M左右,性能提升有限。

离线

楼主 #14 2022-12-27 13:58:53 分享评论

- stm32f407

- 会员

- 注册时间: 2022-10-20

- 已发帖子: 7

- 积分: 23

Re: 拆解了一块USB Blaser II,内部芯片方案令人好奇

感谢您提供的链接,我好像看懂USB Blaster的工作原理了。

离线

#15 2022-12-28 12:33:43 分享评论

- mars4zhu

- 会员

- 注册时间: 2019-06-05

- 已发帖子: 5

- 积分: 5

Re: 拆解了一块USB Blaser II,内部芯片方案令人好奇

QFN68封装,

晶振引脚是5/6

UART_TX/RX引脚是44/45

SWDIO、SWCLK引脚是48、52(推测)

USB是61/62

寂寞哥提示不是ARM核心,带USB高速PHY的,那就是WCH的CH32V307了。

离线

#16 2025-12-15 21:30:18 分享评论

- BVK17

- 会员

- 注册时间: 2024-01-17

- 已发帖子: 4

- 积分: 99

Re: 拆解了一块USB Blaser II,内部芯片方案令人好奇

@stm32f407

能沁恒的调试器读一下芯片型号试试

离线

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发