楼主 # 2023-02-18 04:26:41 分享评论

- Simn

- 会员

- 注册时间: 2021-12-16

- 已发帖子: 33

- 积分: 3

F1C200S SPI->ST7789

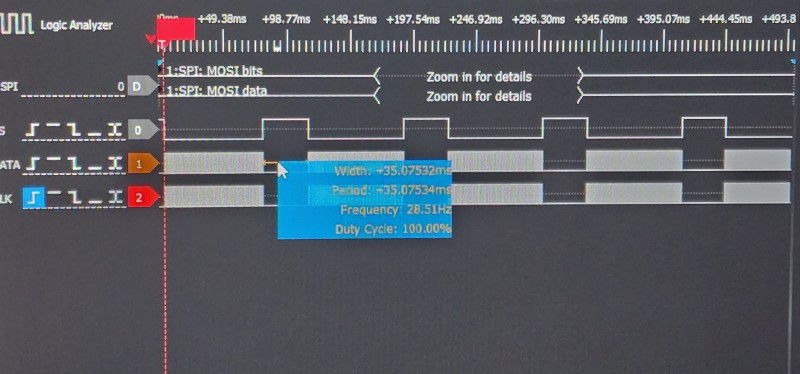

需要帮助。 传输 SPI FIFO 数据时遇到问题,每 64 字节加载一次会使传输延迟 35 毫秒。 如何不间断地传输数据?

离线

#1 2023-02-18 09:17:55 分享评论

- dykxjh

- 会员

- 注册时间: 2020-03-25

- 已发帖子: 189

- 积分: 149

Re: F1C200S SPI->ST7789

代码贴出来看看 啊

离线

楼主 #2 2023-02-18 15:43:15 分享评论

- Simn

- 会员

- 注册时间: 2021-12-16

- 已发帖子: 33

- 积分: 3

Re: F1C200S SPI->ST7789

代码贴出来看看 啊

void spi_write(unsigned char *buffer, int length)

{

int i;

int cnt;

while(length)

{

if(length <= 64)

cnt = length;

else

cnt = 64;

//number of bytes burst

*SPI0_MBC = cnt;

//number of bytes to transmit

*SPI0_MTC = cnt;

*SPI0_BCC = cnt;

//Load FIFO

for(i=0;i<cnt;++i)

*SPI0_TXD_BYTE = *buffer++;

//Start

*SPI0_TCR |= SPI_TCR_XCH_START;

length -= cnt;

while(*SPI0_TCR & SPI_TCR_XCH_START);

*SPI0_FCR |= SPI_FCR_RX_FIFO_RST;

while(*SPI0_FCR & SPI_FCR_RX_FIFO_RST);

}

}void LCD_Fill(uint16_t Color)

{

uint16_t i, j;

for (i = 0; i < LCD_WIDTH; i++)

for (j = 0; j < LCD_HEIGHT; j++)

{

*(volatile uint16_t *) (disp_buf + j * LCD_WIDTH + i) = Color;

}

SetAddressWindow(0, 0, LCD_WIDTH - 1, LCD_HEIGHT - 1);

spi_write(disp_buf,LCD_WIDTH * LCD_HEIGHT*2);

}离线

#3 2023-02-18 20:25:31 分享评论

- dykxjh

- 会员

- 注册时间: 2020-03-25

- 已发帖子: 189

- 积分: 149

Re: F1C200S SPI->ST7789

改成DMA传输不香吗

最近编辑记录 dykxjh (2023-02-18 20:25:43)

离线

楼主 #4 2023-02-20 02:47:41 分享评论

- Simn

- 会员

- 注册时间: 2021-12-16

- 已发帖子: 33

- 积分: 3

Re: F1C200S SPI->ST7789

改成DMA传输不香吗

我不明白如何启动 DMA->SPI。 有如何做到这一点的例子吗?

离线

楼主 #5 2023-02-24 23:33:26 分享评论

- Simn

- 会员

- 注册时间: 2021-12-16

- 已发帖子: 33

- 积分: 3

Re: F1C200S SPI->ST7789

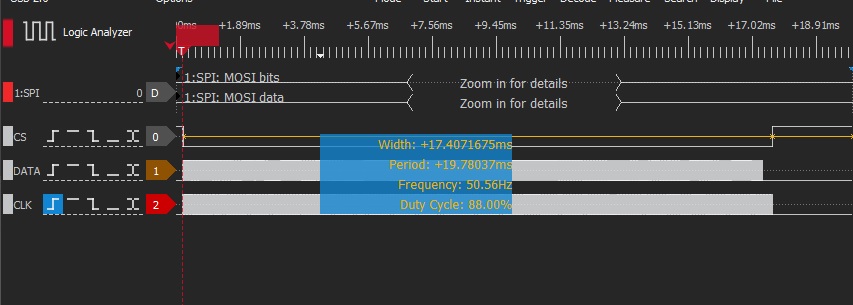

配置 DMA SPI 再次出现问题。 发送前 64 个字节,然后挂起 while(NDMA0->CR & NDMA_CFG_BUSY_STATUS)SPI1_RXD_BYTE;问题是什么?

https://whycan.com/t_3405.html

NDMA0->CR = NDMA_CFG_DRQ_SPI1_TX |

NDMA_CFG_DRQ_SDRAM_MEMORY |

NDMA_CFG_ADDRESS_IO_MODE |

NDMA_CFG_WAIT_STATE2;

NDMA0->SAR =&disp_buf;

NDMA0->DAR = SPI1_TXD_BYTE;

*SPI1_FCR = SPI_FCR_RF_RST |

SPI_FCR_TX_FIFO_RST |

SPI_FCR_TF_DRQ_EN |

SPI_FCR_TX_TRIG_LEV_64 |

SPI_FCR_RX_FIFO_RST |

SPI_FCR_RX_TRIG_LEV_1;void flushDMA()

{

*SPI1_MBC = *SPI1_MTC = *SPI1_BCC = NDMA0->BCR = 170*320*2;

NDMA0->CR |=NDMA_CFG_LOADING;

*SPI1_TCR &= ~SPI_TCR_SS_LEVEL_HIGH;

*SPI1_TCR |= SPI_TCR_XCH_START;

while(NDMA0->CR & NDMA_CFG_BUSY_STATUS) SPI1_RXD_BYTE;

*SPI1_ISR |= SPI_ISR_TC;

while(!(*SPI1_ISR&SPI_ISR_TC)SPI1_RXD_BYTE;

*SPI1_TCR |= SPI_TCR_SS_LEVEL_HIGH;

}离线

#6 2023-02-25 09:43:27 分享评论

- dykxjh

- 会员

- 注册时间: 2020-03-25

- 已发帖子: 189

- 积分: 149

Re: F1C200S SPI->ST7789

是不是接收FIFO满了,数据没有及时取走? 可以配置忽略接收FIFO状态

离线

楼主 #7 2023-02-26 00:58:52 分享评论

- Simn

- 会员

- 注册时间: 2021-12-16

- 已发帖子: 33

- 积分: 3

Re: F1C200S SPI->ST7789

是不是接收FIFO满了,数据没有及时取走? 可以配置忽略接收FIFO状态

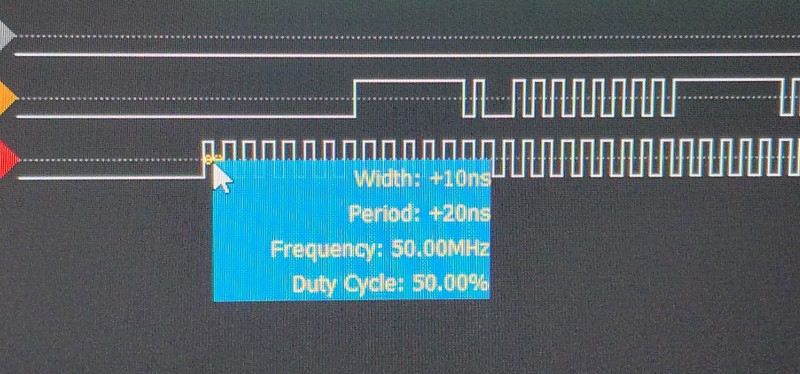

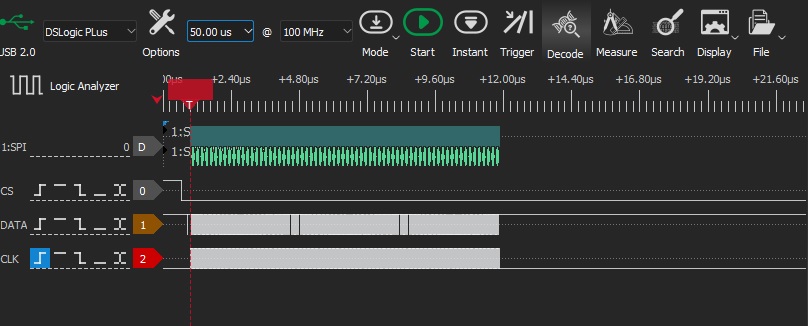

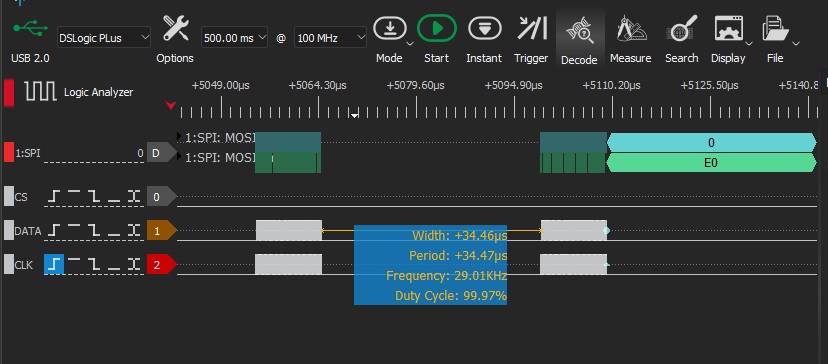

是的,这确实是 RX FIFO 溢出感谢您的提示。 但主要问题仍然存在,每个 64B 都有 34uS 的暂停。 我不明白为什么,关于 DMA 功能的信息很少

离线

楼主 #8 2023-02-28 01:41:52 分享评论

- Simn

- 会员

- 注册时间: 2021-12-16

- 已发帖子: 33

- 积分: 3

Re: F1C200S SPI->ST7789

终于问题解决了。 现在我需要设置一个 DMA 中断并删除 dma 完成等待函数“while(NDMA0->CR & NDMA_CFG_BUSY_STATUS)*SPI1_FCR |= SPI_FCR_RX_FIFO_RST;”

离线

#9 2023-03-08 15:29:31 分享评论

- gary

- 会员

- 注册时间: 2018-05-30

- 已发帖子: 54

- 积分: 8.5

Re: F1C200S SPI->ST7789

直接用MCU I8080接口的屏就行了

离线

#10 2024-03-01 22:02:53 分享评论

Re: F1C200S SPI->ST7789

终于问题解决了。 现在我需要设置一个 DMA 中断并删除 dma 完成等待函数“while(NDMA0->CR & NDMA_CFG_BUSY_STATUS)*SPI1_FCR |= SPI_FCR_RX_FIFO_RST;”https://whycan.com/files/members/7990/dma3.jpghttps://whycan.com/files/members/7990/spi.mp4

楼主请教怎么解决SPI传输中间暂停问题的?

离线

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发