- 首页

- » 搜索

- » shuimogezi 发表的帖子

页次: 1

#1 全志 SOC » 基于linux 内核版本6.1-RC6的F1C200S配置RGB 565 LCD显示屏调试 » 2022-11-26 23:40:29

- shuimogezi

- 回复: 1

目前遇到的问题如下:

按照linux4.14版本内核的设备树配置了6.1的LCD部分。但是使用的是drm方式,但是会提示如下错误:

[ 0.814794] panel-simple panel: supply power not found, using dummy regulator

[ 0.815406] ------------[ cut here ]------------

[ 0.815435] WARNING: CPU: 0 PID: 1 at drivers/gpu/drm/panel/panel-simple.c:623 panel_simple_probe+0x578/0x6dc

[ 0.815539] Modules linked in:

[ 0.815566] CPU: 0 PID: 1 Comm: swapper Not tainted 6.1.0-rc6-licheepi-nano #6

[ 0.815598] Hardware name: Allwinner suniv Family

[ 0.815632] unwind_backtrace from show_stack+0x10/0x14

[ 0.815722] show_stack from dump_stack_lvl+0x28/0x30

[ 0.815785] dump_stack_lvl from __warn+0xdc/0xf4

[ 0.815823] __warn from warn_slowpath_fmt+0xa8/0xb8

[ 0.815860] warn_slowpath_fmt from panel_simple_probe+0x578/0x6dc

[ 0.815918] panel_simple_probe from platform_probe+0x58/0xb8

[ 0.815974] platform_probe from really_probe+0xc4/0x2ac

[ 0.816042] really_probe from __driver_probe_device+0x80/0xe4

[ 0.816106] __driver_probe_device from driver_probe_device+0x30/0xdc

[ 0.816172] driver_probe_device from __driver_attach+0x8c/0x110

[ 0.816238] __driver_attach from bus_for_each_dev+0x70/0xb4

[ 0.816303] bus_for_each_dev from bus_add_driver+0x158/0x1ec

[ 0.816362] bus_add_driver from driver_register+0x74/0x10c

[ 0.816429] driver_register from panel_simple_init+0x10/0x48

[ 0.816505] panel_simple_init from do_one_initcall+0x48/0x240

[ 0.816562] do_one_initcall from kernel_init_freeable+0x180/0x1fc

[ 0.816638] kernel_init_freeable from kernel_init+0x10/0x130

[ 0.816690] kernel_init from ret_from_fork+0x14/0x2c

[ 0.816726] Exception stack(0xc480dfb0 to 0xc480dff8)

[ 0.816761] dfa0: 00000000 00000000 00000000 00000000

[ 0.816796] dfc0: 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000

[ 0.816826] dfe0: 00000000 00000000 00000000 00000000 00000013 00000000

[ 0.816844] ---[ end trace 0000000000000000 ]---

设备树如下:

<suniv-f1c100s.dtsi>:

// SPDX-License-Identifier: (GPL-2.0+ OR X11)

/*

* Copyright 2018 Icenowy Zheng <icenowy@aosc.io>

* Copyright 2018 Mesih Kilinc <mesihkilinc@gmail.com>

*/

#include <dt-bindings/clock/suniv-ccu-f1c100s.h>

#include <dt-bindings/reset/suniv-ccu-f1c100s.h>

/ {

#address-cells = <1>;

#size-cells = <1>;

interrupt-parent = <&intc>;

clocks {

osc24M: clk-24M {

#clock-cells = <0>;

compatible = "fixed-clock";

clock-frequency = <24000000>;

clock-output-names = "osc24M";

};

osc32k: clk-32k {

#clock-cells = <0>;

compatible = "fixed-clock";

clock-frequency = <32768>;

clock-output-names = "osc32k";

};

};

cpus {

// #address-cells = <1>;

#address-cells = <0>;

#size-cells = <0>;

cpu@0 {

compatible = "arm,arm926ej-s";

device_type = "cpu";

// reg = <0x0>;

};

};

de: display-engine {

compatible = "allwinner,suniv-f1c100s-display-engine";

allwinner,pipelines = <&fe0>;

status = "disabled";

};

soc {

compatible = "simple-bus";

#address-cells = <1>;

#size-cells = <1>;

ranges;

sram-controller@1c00000 {

compatible = "allwinner,suniv-f1c100s-system-control",

"allwinner,sun4i-a10-system-control",

"allwinner,sun4i-a10-sram-controller";

reg = <0x01c00000 0x30>;

#address-cells = <1>;

#size-cells = <1>;

ranges;

sram_d: sram@10000 {

compatible = "mmio-sram";

reg = <0x00010000 0x1000>;

#address-cells = <1>;

#size-cells = <1>;

ranges = <0 0x00010000 0x1000>;

otg_sram: sram-section@0 {

compatible = "allwinner,suniv-f1c100s-sram-d",

"allwinner,sun4i-a10-sram-d";

reg = <0x0000 0x1000>;

status = "disabled";

};

};

};

spi0: spi@1c05000 {

compatible = "allwinner,suniv-f1c100s-spi",

"allwinner,sun8i-h3-spi";

reg = <0x01c05000 0x1000>;

interrupts = <10>;

clocks = <&ccu CLK_BUS_SPI0>, <&ccu CLK_BUS_SPI0>;

clock-names = "ahb", "mod";

resets = <&ccu RST_BUS_SPI0>;

status = "disabled";

num-cs = <1>;

#address-cells = <1>;

#size-cells = <0>;

};

spi1: spi@1c06000 {

compatible = "allwinner,suniv-f1c100s-spi",

"allwinner,sun8i-h3-spi";

reg = <0x01c06000 0x1000>;

interrupts = <11>;

clocks = <&ccu CLK_BUS_SPI1>, <&ccu CLK_BUS_SPI1>;

clock-names = "ahb", "mod";

resets = <&ccu RST_BUS_SPI1>;

status = "disabled";

num-cs = <1>;

#address-cells = <1>;

#size-cells = <0>;

};

tcon0: lcd-controller@1c0c000 {

compatible = "allwinner,suniv-f1c100s-tcon";

reg = <0x01c0c000 0x1000>;

interrupts = <29>;

clocks = <&ccu CLK_BUS_LCD>,

<&ccu CLK_TCON>;

clock-names = "ahb",

"tcon-ch0";

clock-output-names = "tcon-pixel-clock";

resets = <&ccu RST_BUS_LCD>;

reset-names = "lcd";

status = "disabled";

ports {

#address-cells = <1>;

#size-cells = <0>;

tcon0_in: port@0 {

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

tcon0_in_be0: endpoint@0 {

reg = <0>;

remote-endpoint = <&be0_out_tcon0>;

};

};

tcon0_out: port@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

};

};

};

mmc0: mmc@1c0f000 {

compatible = "allwinner,suniv-f1c100s-mmc",

"allwinner,sun7i-a20-mmc";

reg = <0x01c0f000 0x1000>;

clocks = <&ccu CLK_BUS_MMC0>,

<&ccu CLK_MMC0>,

<&ccu CLK_MMC0_OUTPUT>,

<&ccu CLK_MMC0_SAMPLE>;

clock-names = "ahb", "mmc", "output", "sample";

resets = <&ccu RST_BUS_MMC0>;

reset-names = "ahb";

interrupts = <23>;

pinctrl-names = "default";

pinctrl-0 = <&mmc0_pins>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

mmc1: mmc@1c10000 {

compatible = "allwinner,suniv-f1c100s-mmc",

"allwinner,sun7i-a20-mmc";

reg = <0x01c10000 0x1000>;

clocks = <&ccu CLK_BUS_MMC1>,

<&ccu CLK_MMC1>,

<&ccu CLK_MMC1_OUTPUT>,

<&ccu CLK_MMC1_SAMPLE>;

clock-names = "ahb", "mmc", "output", "sample";

resets = <&ccu RST_BUS_MMC1>;

reset-names = "ahb";

interrupts = <24>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

ccu: clock@1c20000 {

compatible = "allwinner,suniv-f1c100s-ccu";

reg = <0x01c20000 0x400>;

clocks = <&osc24M>, <&osc32k>;

clock-names = "hosc", "losc";

#clock-cells = <1>;

#reset-cells = <1>;

};

intc: interrupt-controller@1c20400 {

compatible = "allwinner,suniv-f1c100s-ic";

reg = <0x01c20400 0x400>;

interrupt-controller;

#interrupt-cells = <1>;

};

pio: pinctrl@1c20800 {

compatible = "allwinner,suniv-f1c100s-pinctrl";

reg = <0x01c20800 0x400>;

interrupts = <38>, <39>, <40>;

clocks = <&ccu CLK_BUS_PIO>, <&osc24M>, <&osc32k>;

clock-names = "apb", "hosc", "losc";

gpio-controller;

interrupt-controller;

#interrupt-cells = <3>;

#gpio-cells = <3>;

mmc0_pins: mmc0-pins {

pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5";

function = "mmc0";

drive-strength = <30>;

};

spi0_pc_pins: spi0-pc-pins {

pins = "PC0", "PC1", "PC2", "PC3";

function = "spi0";

};

uart0_pe_pins: uart0-pe-pins {

pins = "PE0", "PE1";

function = "uart0";

};

uart1_pa_pins: uart1-pa-pins {

pins = "PA2", "PA3";

function = "uart1";

};

lcd_rgb666_pins: lcd-rgb666-pins {

pins = "PD0", "PD1", "PD2", "PD3", "PD4",

"PD5", "PD6", "PD7", "PD8", "PD9",

"PD10", "PD11", "PD12", "PD13", "PD14",

"PD15", "PD16", "PD17", "PD18", "PD19",

"PD20", "PD21";

function = "lcd";

};

};

timer@1c20c00 {

compatible = "allwinner,suniv-f1c100s-timer";

reg = <0x01c20c00 0x90>;

interrupts = <13>, <14>, <15>;

clocks = <&osc24M>;

};

wdt: watchdog@1c20ca0 {

compatible = "allwinner,suniv-f1c100s-wdt",

"allwinner,sun6i-a31-wdt";

reg = <0x01c20ca0 0x20>;

interrupts = <16>;

clocks = <&osc32k>;

};

uart0: serial@1c25000 {

compatible = "snps,dw-apb-uart";

reg = <0x01c25000 0x400>;

interrupts = <1>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_BUS_UART0>;

resets = <&ccu RST_BUS_UART0>;

status = "disabled";

};

uart1: serial@1c25400 {

compatible = "snps,dw-apb-uart";

reg = <0x01c25400 0x400>;

interrupts = <2>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_BUS_UART1>;

resets = <&ccu RST_BUS_UART1>;

status = "disabled";

};

uart2: serial@1c25800 {

compatible = "snps,dw-apb-uart";

reg = <0x01c25800 0x400>;

interrupts = <3>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_BUS_UART2>;

resets = <&ccu RST_BUS_UART2>;

status = "disabled";

};

usb_otg: usb@1c13000 {

compatible = "allwinner,suniv-musb";

reg = <0x01c13000 0x0400>;

clocks = <&ccu CLK_BUS_OTG>;

resets = <&ccu RST_BUS_OTG>;

interrupts = <26>;

interrupt-names = "mc";

phys = <&usbphy 0>;

phy-names = "usb";

extcon = <&usbphy 0>;

allwinner,sram = <&otg_sram 1>;

status = "disabled";

};

usbphy: phy@1c13400 {

compatible = "allwinner,suniv-usb-phy";

reg = <0x01c13400 0x10>;

reg-names = "phy_ctrl";

clocks = <&ccu CLK_USB_PHY0>;

clock-names = "usb0_phy";

resets = <&ccu RST_USB_PHY0>;

reset-names = "usb0_reset";

#phy-cells = <1>;

status = "disabled";

};

fe0: display-frontend@1e00000 {

compatible = "allwinner,suniv-f1c100s-display-frontend";

reg = <0x01e00000 0x20000>;

interrupts = <30>;

clocks = <&ccu CLK_BUS_DE_FE>, <&ccu CLK_DE_FE>,

<&ccu CLK_DRAM_DE_FE>;

clock-names = "ahb", "mod",

"ram";

resets = <&ccu RST_BUS_DE_FE>;

status = "disabled";

ports {

#address-cells = <1>;

#size-cells = <0>;

fe0_out: port@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

fe0_out_be0: endpoint@0 {

reg = <0>;

remote-endpoint = <&be0_in_fe0>;

};

};

};

};

be0: display-backend@1e60000 {

compatible = "allwinner,suniv-f1c100s-display-backend";

reg = <0x01e60000 0x10000>;

reg-names = "be";

interrupts = <31>;

clocks = <&ccu CLK_BUS_DE_BE>, <&ccu CLK_DE_BE>,

<&ccu CLK_DRAM_DE_BE>;

clock-names = "ahb", "mod",

"ram";

resets = <&ccu RST_BUS_DE_BE>;

reset-names = "be";

assigned-clocks = <&ccu CLK_DE_BE>;

assigned-clock-rates = <300000000>;

ports {

#address-cells = <1>;

#size-cells = <0>;

be0_in: port@0 {

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

be0_in_fe0: endpoint@0 {

reg = <0>;

remote-endpoint = <&fe0_out_be0>;

};

};

be0_out: port@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

be0_out_tcon0: endpoint@0 {

reg = <0>;

remote-endpoint = <&tcon0_in_be0>;

};

};

};

};

};

};

<suniv-f1c100s-licheepip-nano.dts>:

// SPDX-License-Identifier: (GPL-2.0+ OR X11)

/*

* Copyright 2018 Icenowy Zheng <icenowy@aosc.io>

*/

/dts-v1/;

#include "suniv-f1c100s.dtsi"

#include <dt-bindings/gpio/gpio.h>

/ {

model = "Lichee Pi Nano";

compatible = "licheepi,licheepi-nano", "allwinner,suniv-f1c100s";

aliases {

mmc0 = &mmc0;

serial1 = &uart1;

spi0 = &spi0;

};

chosen {

stdout-path = "serial1:115200n8";

};

reg_vcc3v3: vcc3v3 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3";

regulator-min-microvolt = <3300000>;

regulator-max-microvolt = <3300000>;

};

};

&mmc0 {

broken-cd;

bus-width = <4>;

disable-wp;

status = "okay";

vmmc-supply = <®_vcc3v3>;

};

&spi0 {

pinctrl-names = "default";

pinctrl-0 = <&spi0_pc_pins>;

status = "okay";

flash@0 {

#address-cells = <1>;

#size-cells = <1>;

compatible = "winbond,w25q128", "jedec,spi-nor";

reg = <0>;

spi-max-frequency = <40000000>;

};

};

&uart0 {

pinctrl-names = "default";

pinctrl-0 = <&uart0_pe_pins>;

status = "okay";

};

&uart1 {

pinctrl-names = "default";

pinctrl-0 = <&uart1_pa_pins>;

status = "okay";

};

&otg_sram {

status = "okay";

};

&usb_otg {

dr_mode = "otg";

status = "okay";

};

&usbphy {

usb0_id_det-gpio = <&pio 4 2 GPIO_ACTIVE_HIGH>; /* PE2 */

status = "okay";

};

<suniv-f1c100s-licheepi-nano-with-lcd.dts>:

/*

* Copyright (C) 2018 Icenowy Zheng <icenowy@aosc.io>

*

* SPDX-License-Identifier: (GPL-2.0+ OR X11)

*/

#include "suniv-f1c100s-licheepi-nano.dts"

/ {

panel: panel {

compatible = "ampire,am-480272h3tmqw-t01h", "simple-panel";

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

#address-cells = <1>;

#size-cells = <0>;

panel_input: endpoint@0 {

reg = <0>;

remote-endpoint = <&tcon0_out_lcd>;

};

};

};

};

&be0 {

status = "okay";

};

&de {

status = "okay";

};

&tcon0 {

pinctrl-names = "default";

pinctrl-0 = <&lcd_rgb666_pins>;

status = "okay";

};

&tcon0_out {

tcon0_out_lcd: endpoint@0 {

reg = <0>;

remote-endpoint = <&panel_input>;

};

};

#2 Re: Cortex M0/M3/M4/M7 » 2.通过LWIP协议栈使用学习http,tcp,网卡之间的关系. » 2022-10-14 09:16:51

楼主,请问下这个slipif又在windows下的测试方法吗?

#3 哇酷地摊(跳蚤市场) » NUC977(64MB DDR版本)一共10片,330元人民币出,顺丰包邮,有人要吗? » 2022-10-12 11:14:25

- shuimogezi

- 回复: 0

10片闲置的NUC977 ARM9处理器,330源10片一起出,有人要吗?要的加我Q:819277784.

#4 Re: 全志 SOC » [开源项目-记录贴]扔掉你手中的开发板,跟我来自制基于F1C100s/F1C200s的M5Pi吧! » 2022-10-12 10:28:15

楼主这个电容屏特别喜庆,能否贴上购买链接看看?

#5 Re: 全志 SOC » 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出 » 2022-01-26 23:24:32

问下,用的这个工程打样的板子回来了,贴的32MB的QSPI FLASH,很大概率的时候经常擦除flash失败导致新固件有很多时候写不进去,请问是怎么回事?

#6 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » lvgl7重复调用lv_img_set_src后造成系统(RTOS)死机 » 2022-01-05 13:30:54

@达克罗德

我的问题已经解决了,在上面评论中,我自己做的回复,另外对LVGL内存使用的监控(采用串口打印LVGL动态内存使用情况)也很重要,如果LVGL内存临界的话,也会出现死机或者其他的问题。

#7 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » lvgl7重复调用lv_img_set_src后造成系统(RTOS)死机 » 2022-01-05 13:28:07

@达克罗德

你说的和我操作的情况不一样,首先,我没有在两个线程中操作GUI,也没有在调用UI Handle的线程中独立操作GUI,而是在GUI提供的回调接口中操作的。所以不存在抢占的问题。而且是间隔5秒执行一次GUI回调(LVGL提供的多任务回调注册接口)。

#8 Re: 全志 SOC » DKTool F1C100s/F1C200s专用工具 哇酷网特别版,20201221正式发布!!!! » 2022-01-04 11:33:32

下载了,支持32MB的spi flash 烧录吗?

#9 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » lvgl7重复调用lv_img_set_src后造成系统(RTOS)死机 » 2022-01-04 11:18:01

问题已解决,2个地方:

1:在wifi断开连接后,不应该继续调用esp_wifi_sta_get_ap_info函数来获取AP信息。

2:最后发现NXP的gui builder创建的工程控件布置不知什么时候都错乱了(之前没有错乱,可能是拷贝.guiguider文件并直接修改导致的,虽然显示正常,但是父级子级关系乱了,重新改过来,摆正关系后,正常)

#10 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » lvgl7重复调用lv_img_set_src后造成系统(RTOS)死机 » 2021-12-29 14:49:39

@一篮子bug

首先,我是使用的lvgl自带的任务函数创建的一个任务显示操作的任务,并没有在2个线程中操作lvgl相关的函数之类的,所以这个排除了,而且我也尝试过使用lv_obj_del(立即删除对象)和lv_obj_async_del(下个周期删除对象),结果还是会死机。

#11 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » lvgl7重复调用lv_img_set_src后造成系统(RTOS)死机 » 2021-12-29 08:20:19

如果可以的话,建议把代码发出来看一看

void task_gui_process_disptileview_cb(lv_task_t *task)

{

static uint8_t var_buff[64] = {0};

static wifi_ap_record_t ap_record_t = {0};

lv_ui *ui = task->user_data;

memset(var_buff,0x00,64);

memcpy(var_buff,"hello",5);

lv_label_set_text(ui->screen1_date_time, (char *)var_buff);

esp_wifi_sta_get_ap_info(&ap_record_t);

if(ap_record_t.rssi <= -100)

{

lv_img_set_src(ui->screen1_img_wifi,&_wifi_zero_alpha_18x16);

}

else if((-100 < ap_record_t.rssi)&&(ap_record_t.rssi <= -80))

{

lv_img_set_src(ui->screen1_img_wifi,&_wifi_one_alpha_18x16);

}

else if((-80 < ap_record_t.rssi)&&(ap_record_t.rssi <= -70))

{

lv_img_set_src(ui->screen1_img_wifi,&_wifi_two_alpha_18x16);

}

else if((-70 < ap_record_t.rssi)&&(ap_record_t.rssi < 0))

{

lv_img_set_src(ui->screen1_img_wifi,&_wifi_three_alpha_18x16);

}

else

{

lv_img_set_src(ui->screen1_img_wifi,&_WIFI_13_alpha_18x16);

}

}

#12 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » lvgl7重复调用lv_img_set_src后造成系统(RTOS)死机 » 2021-12-28 23:27:08

用memcpy试试

不好意思,那个是回帖子贴源码时删减不当造成的(memset和memcpy删减),这个memset的问题可以忽略,目前是重复调用lv_img_set_src会死机。

如果吧这句话(lv_img_set_src)屏蔽,ESP8266重新断开wifi连接后,不会死机,设备可以正常运行;当调用lv_img-set_src时,同样的操作设备会死机。

#13 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » lvgl7重复调用lv_img_set_src后造成系统(RTOS)死机 » 2021-12-28 23:23:20

C标准库的:void *memset(void *dest, int c, size_t count);

楼主的用法:memset(var_buff,"hello lvgl",64);

memset不是这样用的吧?难道是私有memset?

不好意思,那个是因为贴本网站上源码,删减一些没用的源码时不小心删错的,memset和memcpy两个删重组了,这个问题可以忽略。目前是重复调用lv_img_set_src的时候会造成死机。

#14 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » lvgl7重复调用lv_img_set_src后造成系统(RTOS)死机 » 2021-12-27 18:03:00

你是不是每次设置的时候都重新创建了一个img对象,导致ram溢出了?

我也尝试使用lv_obj_del删除img对象,然后再重新创建,发现结果还是一样的。

#15 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » lvgl7重复调用lv_img_set_src后造成系统(RTOS)死机 » 2021-12-27 17:34:44

- shuimogezi

- 回复: 14

这几天玩ESP8266,并且移植了LVGL(LVGL版本是V7.10.1),通过lvgl的图片显示功能,每隔5秒切换一张图片,图片使用NXP的GUI Builder直接生成的保存到ROM里面,通过调用lv_img_set_src实现图片的切换,经过一段时间测试,会发现反复调用这个函数后会死机,屏蔽掉后系统运行正常。运行平台:ESP8266。有知道的小伙伴帮忙答疑一下。

#16 Re: ESP32/ESP8266 » ESP32DOWD外扩ESP-PSRAM64H不识别的问题 » 2021-06-24 09:39:44

解决了,说出来也很尴尬,由于板卡时间过于久远没碰了,都忘记了,当时没有焊接PSRAM的时候顺带着PSRAM的clk引脚串联的电阻R5也一起没焊接,后来用示波器测信号时发现的,补上了R5电阻就可以正常识别和通过MMU使用PSRAM了...

#17 ESP32/ESP8266 » ESP32DOWD外扩ESP-PSRAM64H不识别的问题 » 2021-06-23 09:46:26

- shuimogezi

- 回复: 9

最近又重新拾起了ESP32,一年前疫情期间闲着没事自己画的板卡,ESP型号用的双核EPS32DOWD,主频最高240MH在,外扩了8MB的QSPI FLASH和预留了一个PSRAM,前两天买了几片ESP-PSRAM64H(支持3.3V供电,最高时钟133MHz),就想起了我的ESP32板子,于是焊接上了,但是再menuconfig里面配置了SPI RAM,却不被识别,请教下朋友们有没有知道原因的?

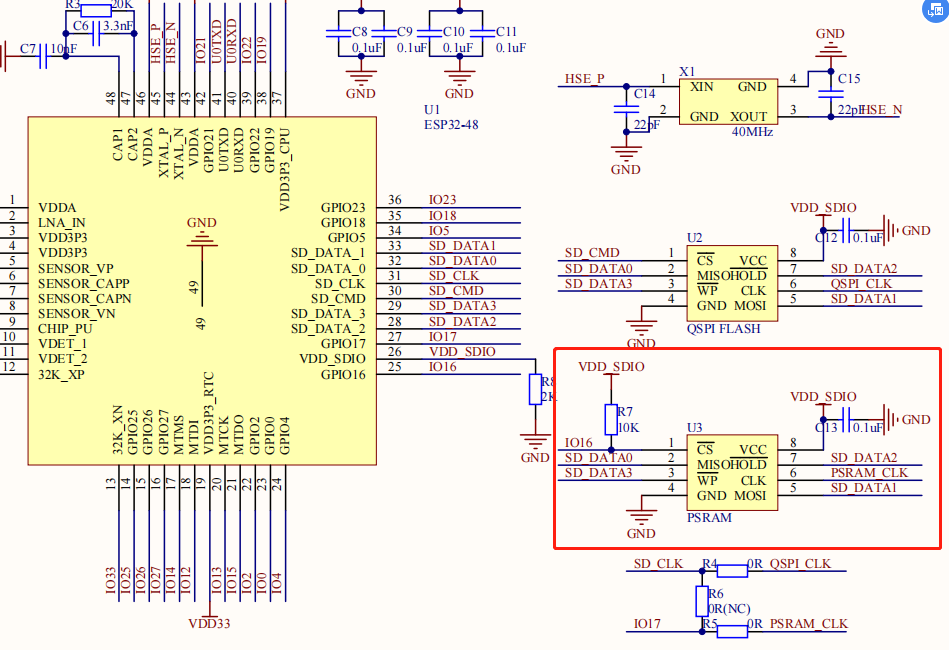

1.原理图(R6为NC,没有焊接):

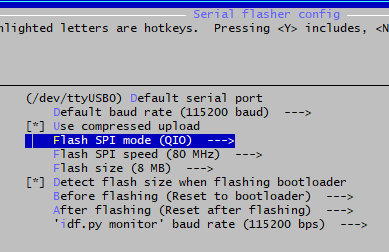

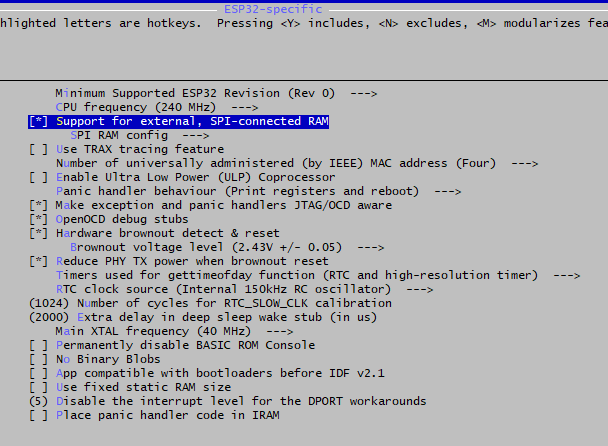

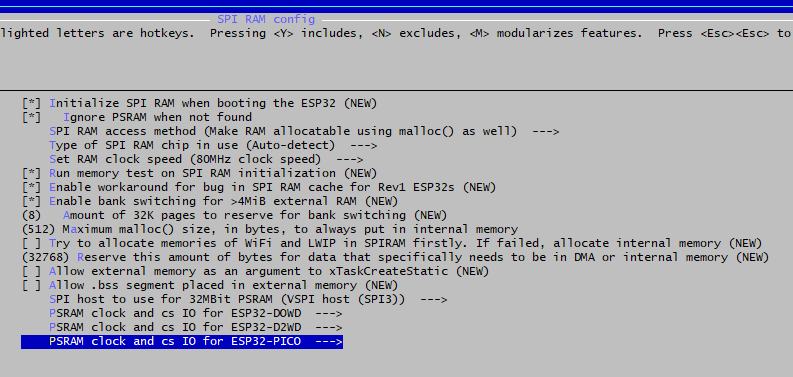

2:menuconfig

(1):qspi flash 配置(QIO)

(2):spi ram 配置

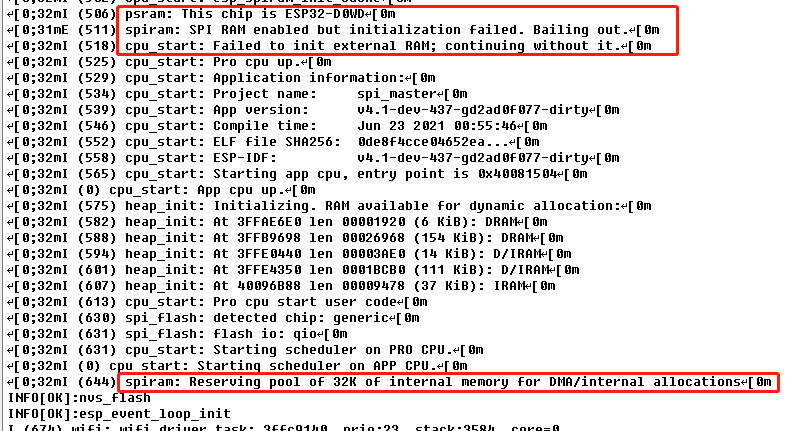

3:系统启动的log信息(红框信息提示SPI RAM初始化失败)

#18 Re: Cortex M0/M3/M4/M7 » 晒一下树莓派Pico同时驱动两个8080屏幕的效果,99Hz无压力 » 2021-06-12 10:22:35

汇编写的吗?

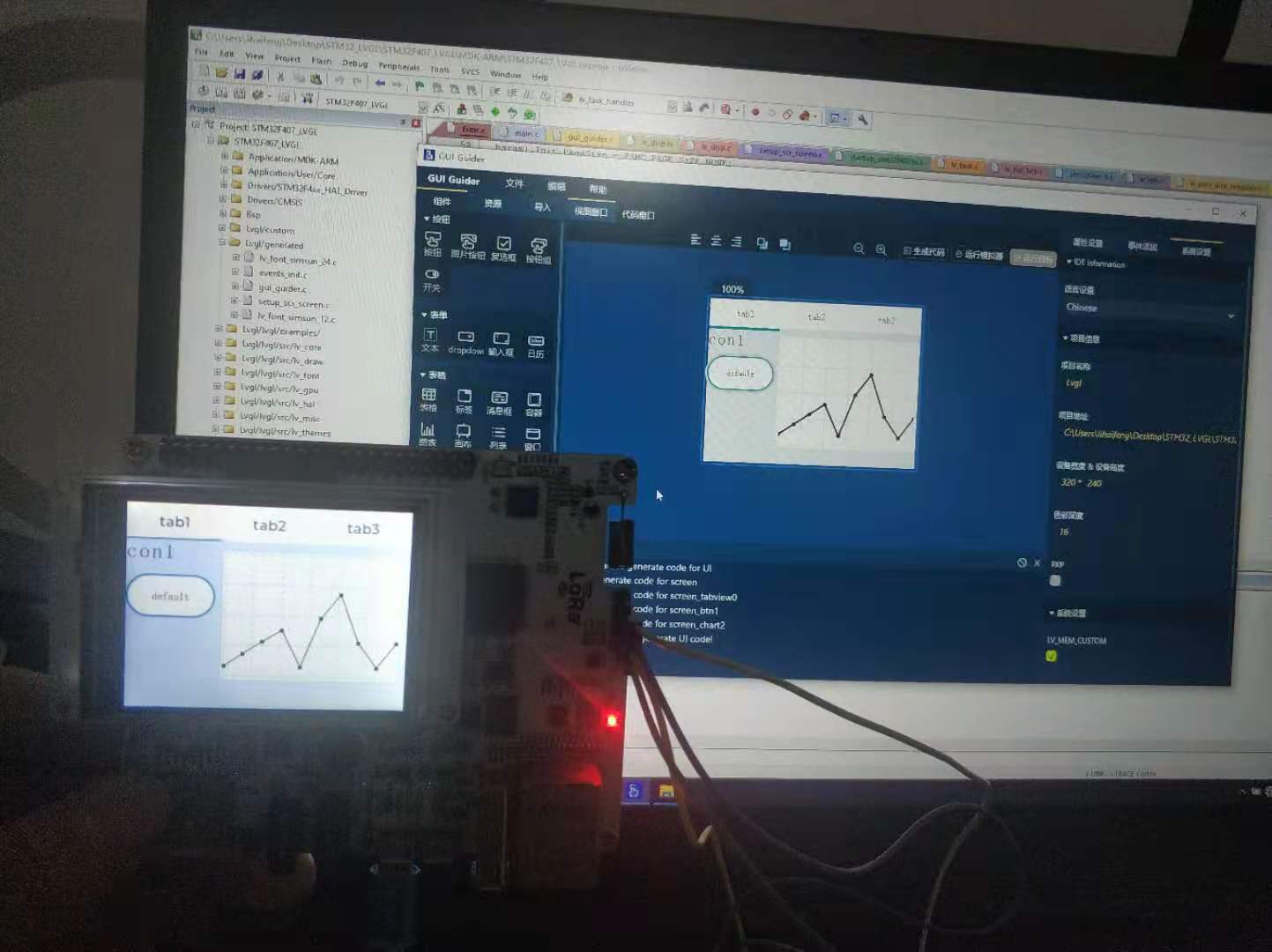

#19 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » NXP出了个LVGL界面设计器 ---- Gui-Guider-Setup-1.0.0-GA.exe » 2021-06-01 15:24:08

已经移植到裸机STM32F4上面去了,非常方便

#20 Re: 全志 SOC » 新作F1C200S,百分之百开源,新年礼物开箱!!! » 2021-01-25 10:06:51

楼主现在都验证通过了吗?

#21 Re: 全志 SOC » 开源全志V3S 两层板PCB 支持OV7725 OV2640摄像头 » 2021-01-25 10:04:08

楼主好,从github上下载的原理图打开什么都没有,PCB是正常的

#22 Re: 全志 SOC » 开源自己画的H3四层板打板只要50块 » 2021-01-05 10:44:30

很棒,感谢楼主,这个板卡经过测试了吗?DDR速度能到多少

#23 全志 SOC » STM32F429移植uboot » 2020-12-22 10:14:05

- shuimogezi

- 回复: 3

(第一次在挖坑论坛上发表,有些功能还不熟悉,请见谅,嘿嘿)

一、准备工作

1:gcc交叉编译器源码:gcc-arm-none-eabi-5_4-2016q3-20160926-linux.tar.bz2

2:uboot源码:u-boot-2016.03.tar.bz2

3:kernel源码:linux-4.13.12.tar.xz

4:rootfs源码:Stm32_mini_rootfs.cpio.bz2

(说明:以上文件均可百度搜到,暂时没有贴上直接的下载链接)

二、安装gcc交叉编译工具

1:将gcc交叉编译工具解压

$ tar xjvf gcc-arm-none-eabi-5_4-2016q3-20160926-linux.tar.bz2

2:修改环境变量,将gcc编译器路径添加到环境变量中

$ vim ~/.bashrc

在文件的最后一行添加gcc路径(your_gcc_path:指自己的gcc解压路径,因每个人的解压位置不同而不同)

export PATH=$PATH:/your_gcc_path/bin

使环境变量生效:stm32$ source ~/.bashrc

查看gcc是否添加成功:arm-none-eabi-gcc -v

如果出现gcc版本信息,说明已经添加成功并且生效了:

三、编译uboot

1:解压uboot源码

$ tar xjvf u-boot-2016.03.tar.bz2

2:匹配自己的硬件(https://github.com/huayuguo/uboot-stm32h743_eth/blob/uboot201811-stm32h7/build.sh)

进入u-boot-2016.03文件夹,首先要修改系统时钟,默认是8MHz外部晶振,我这里用的是24Mhz的,所以需要先修改成24MHz,源码路径在:

u-boot-2016.03/include/configs/stm32f429-discovery.h

u-boot-2016.03/arch/arm/mach-stm32/stm32f4/clock.c

这两个地方修改好之后,系统时钟源就已经配置好了(我这里配置的系统时钟是180MHz,外部高速晶振24MHz)

然后继续修改外部FMC总线,要修改成和自己的硬件一致,不然后面会直接影响kernel的加载。具体修改如下:

找到初始化FMC总线的文件路径:u-boot-2016.03/board/st/stm32f429-discovery/stm32f429-discovery.c

修改FMC引脚和时钟:

串口默认是PA9和PA10,正好和我的一样,这里就不做修改了。

如果想修改的话,路径是:arch/arm/include/asm/arch-stm32f4/gpio.h

到此位置uboot的修改基本完成了,下年就是开始准备编译了。

3:生成u-boot.bin

清除操作:$ make mrproper

配置默认选项:$ make stm32f429-discovery_defconfig

成成.config文件:$ make menuconfig,打开后如果不需要修改可以直接退出,目的是为了生成.config配置信息

执行命令:$ make ARCH=arm CROSS_COMPILE=arm-none-eabi-

编译完成后,生成的u-boot.bin就是我们要下载到STM32F429中的uboot程序,下载地址为:0x08000000

#24 Re: 全志 SOC » 分享F1C100S的TVD源码,TVIN0接CVBS摄像头采集数据显示到LCD屏 » 2020-12-22 09:57:21

很好的东西,已经做了一个一摸一样的板子出来了,准备玩一下

#25 Re: 全志 SOC » 还在加班加点画F1C100s/F1C200s PCB吗,widora tiny200 PCB已经开源了 » 2020-11-15 00:35:24

漂亮,多谢分享

#26 Re: ST/STM8/STM8S/STM8L » STM32H750+lvgl » 2020-07-05 01:10:49

STM32H750外接QSPI PSRAM没有用,因为STM32H70的QSPI目前只支持内存映射,用于存储代码,替代内存flash

#27 Re: DOPI开源摄像头(HI3516/HI3518) » DOPI EV200 SDK 开源啦!快来下载 Q群 735884031 » 2020-07-05 00:55:53

正准备学习这个呢,很不错的资料,感谢楼主

页次: 1

- 首页

- » 搜索

- » shuimogezi 发表的帖子

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发