- 首页

- » 搜索

- » stm32f407 发表的帖子

页次: 1

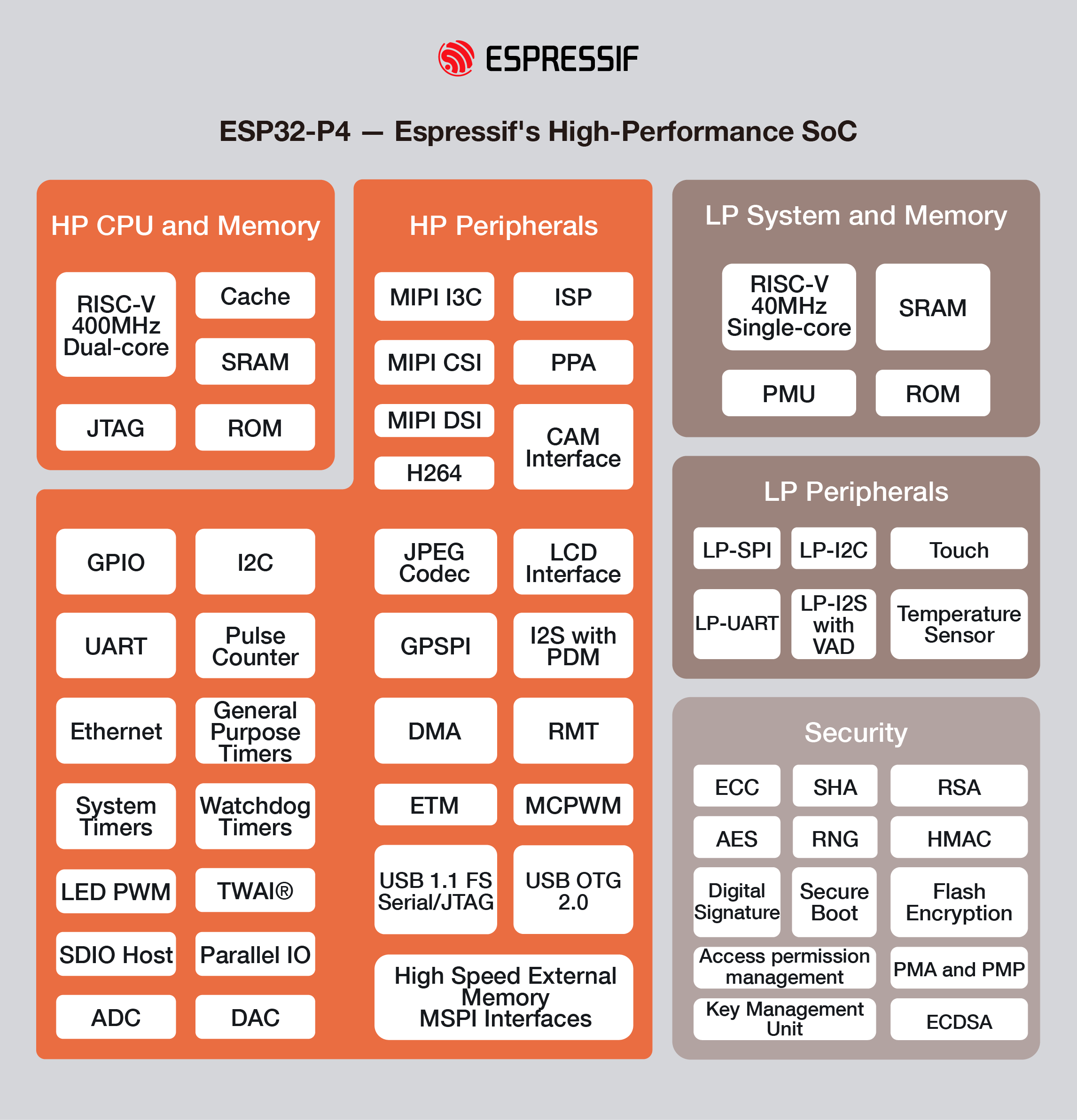

#1 Re: ESP32/ESP8266 » 乐鑫要发的新芯片esp32-P4 » 2023-01-09 21:50:42

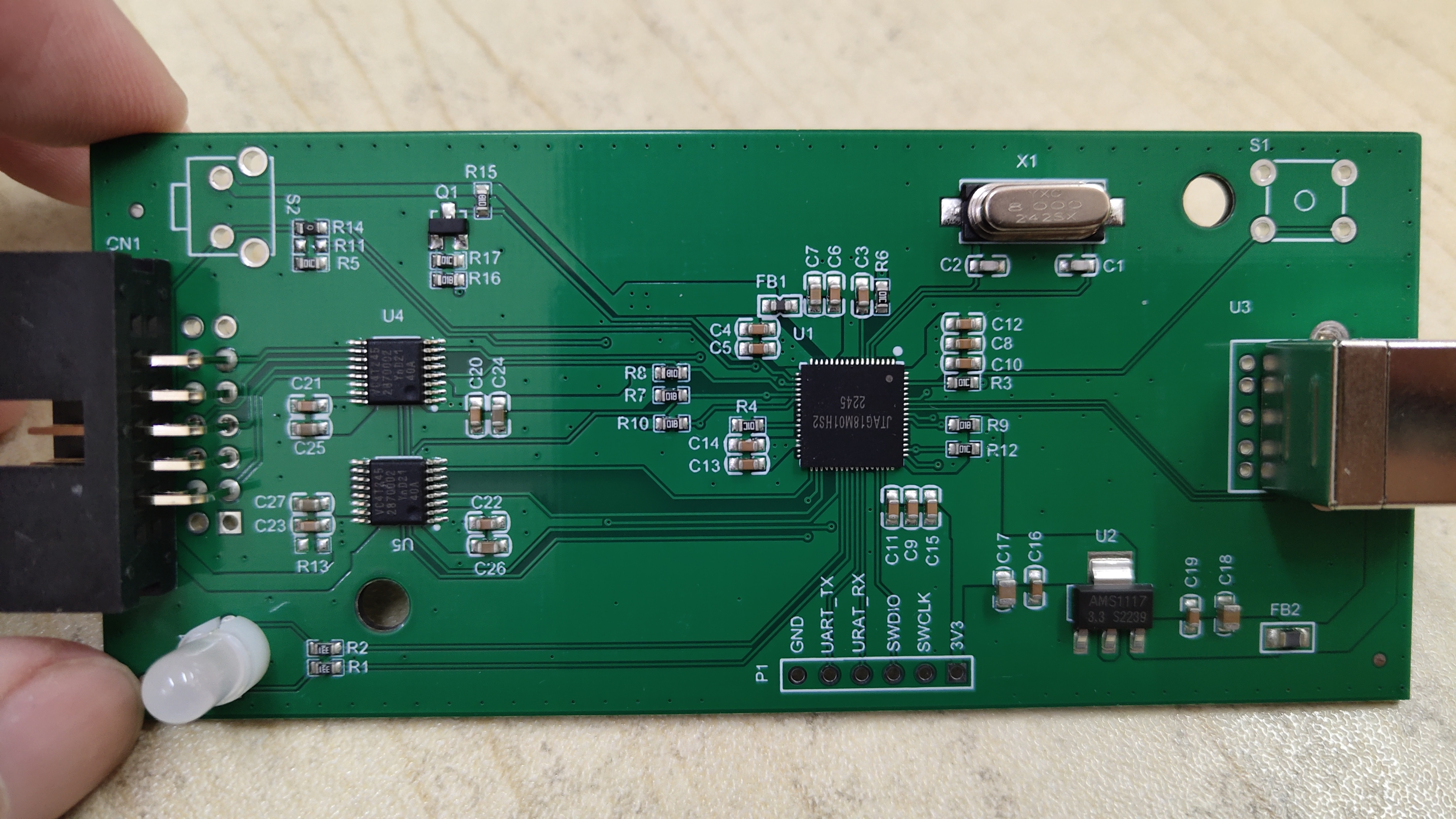

#2 Re: Xilinx/Altera/FPGA/CPLD/Verilog » 拆解了一块USB Blaser II,内部芯片方案令人好奇 » 2022-12-27 13:58:53

david 说:

感谢您提供的链接,我好像看懂USB Blaster的工作原理了。

#5 Re: Xilinx/Altera/FPGA/CPLD/Verilog » 拆解了一块USB Blaser II,内部芯片方案令人好奇 » 2022-12-26 17:38:02

echo 说:

@stm32f407

在这里USBHS并没有什么意义,12M的USBFS充分优化以后足够用了。就好比你在国道上开一辆F1赛车,并不比买菜车更好。

大佬,您好,您的工作让我深深感到敬佩,能够得到您的回复也很荣幸,但是我没有贬低USBFS的意思。我在使用Stratix V系列的FPGA时候,对比过速度上的区别,II代的USBHS的TCK时钟频率可以到24M,不管怎么说都比FS要快,尤其是在固化的时候,我用I代要等很久才行,换成II代有了很大的改善。然后就自己也买了一个Blaster II,因为对此感到了一些好奇,买了一个后顺便拆开看看别人是怎么做的,然后把里面的电路板照片分享了出来。

页次: 1

- 首页

- » 搜索

- » stm32f407 发表的帖子

感谢为中文互联网持续输出优质内容的各位老铁们。

QQ: 516333132, 微信(wechat): whycan_cn (哇酷网/挖坑网/填坑网) service@whycan.cn

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发