- 首页

- » 搜索

- » laplace 发表的帖子

页次: 1

#2 Re: 全志 SOC » 制作F1C100S开发板,开源 » 2022-01-04 10:04:56

#6 Re: SigmaStar/SSD201/SSD202/SSD212 » SSD201/SSD202D/双屏同显/MP4/MKV/FLV/RMVB/MOV/AVI,4K播放,已量产,出货~出货~出货~ » 2021-12-30 17:24:54

#7 Re: 全志 SOC » 大佬们救救我,自己画的荔枝派出问题 » 2021-12-30 17:07:52

#8 Re: 全志 SOC » 制作F1C100S开发板,开源 » 2021-12-29 23:57:40

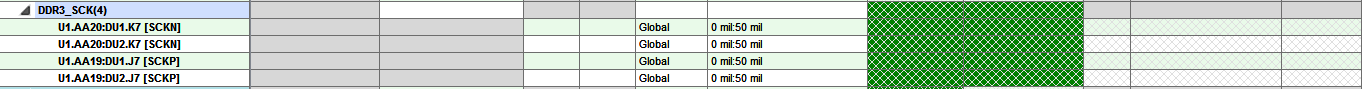

#9 全志 SOC » 制作F1C100S开发板,开源 » 2021-12-23 22:44:13

- laplace

- 回复: 8

才画完板子不久,焊接完毕,学着编译了uboot、Linux和根文件系统。

虽然已经有很多大佬开源了,但是看到晕哥的白嫖帖子,DNA直接躁动了。。。

这个板子预留了:

1组I2C

SPI0、SPI1,SPI1通过排针引出,后接了一个SPI lcd座子,SPI0用于SPI FLASH

一个耳机

ADC按键、两个GPIO按键、4个LED(流水灯)

引出了CVBS一级麦克风等

一个USBHUB,可以有两个USB

一个RGB666的接口,我通过GM8285C把RGB转成LVDS了,主要是我只有6位LVDS屏幕

PCB格式是ALLEGRO 17.2

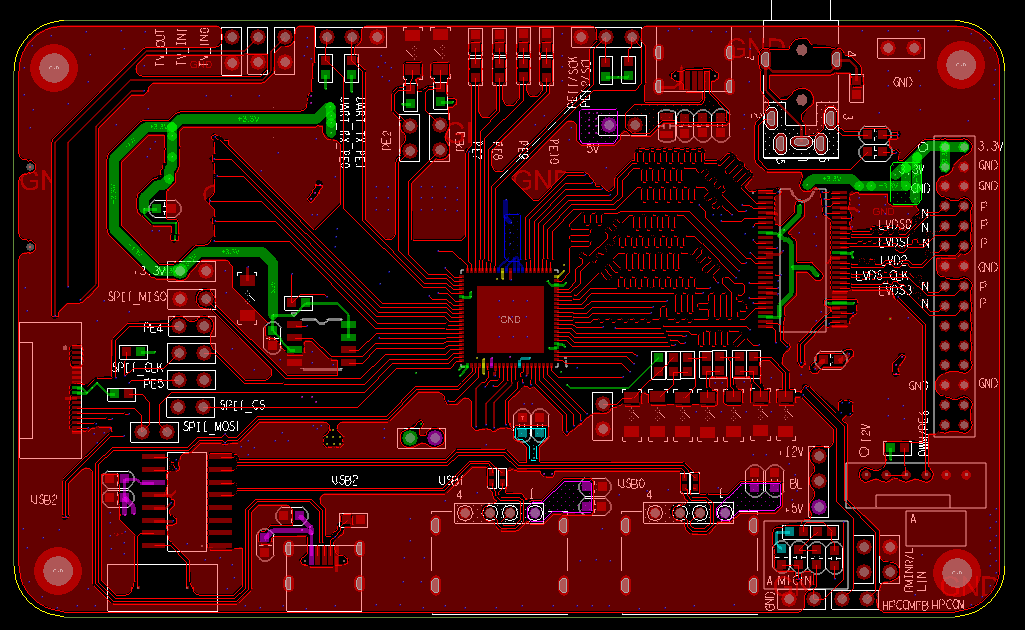

TOP层

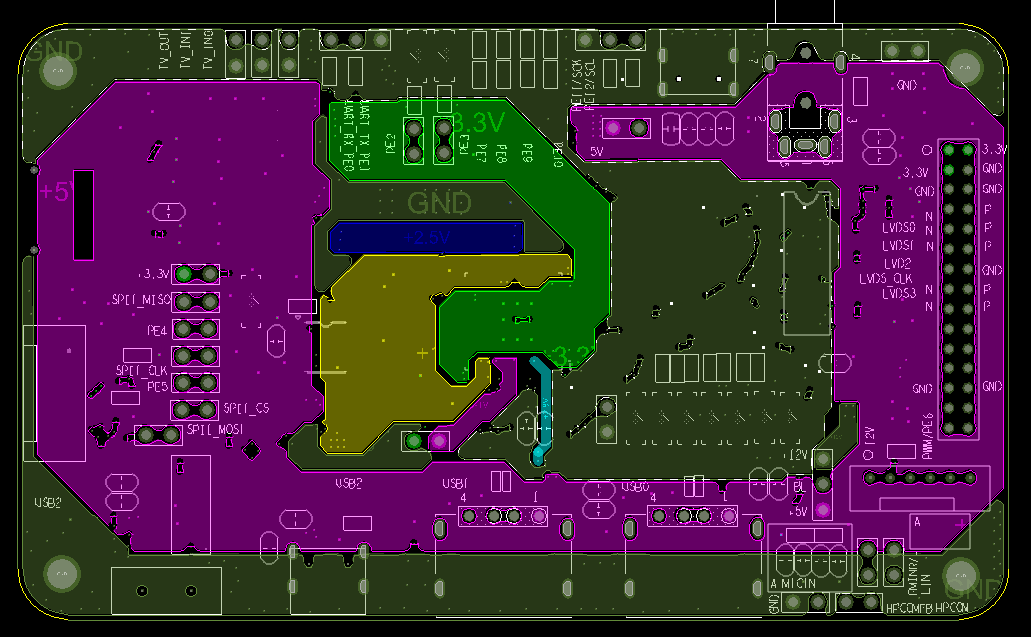

POWER03层

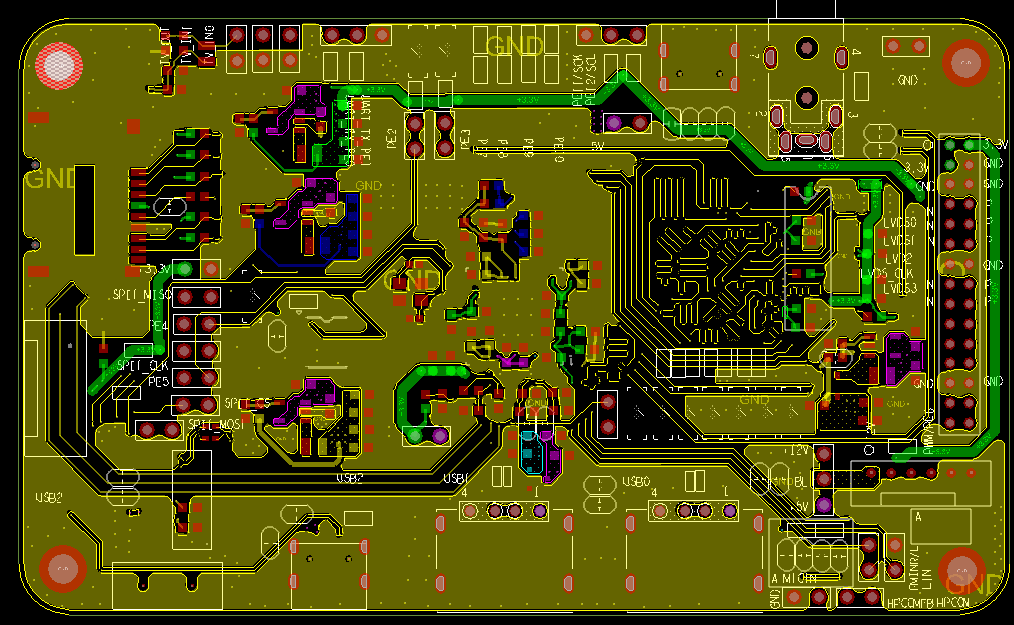

BOTTOM层

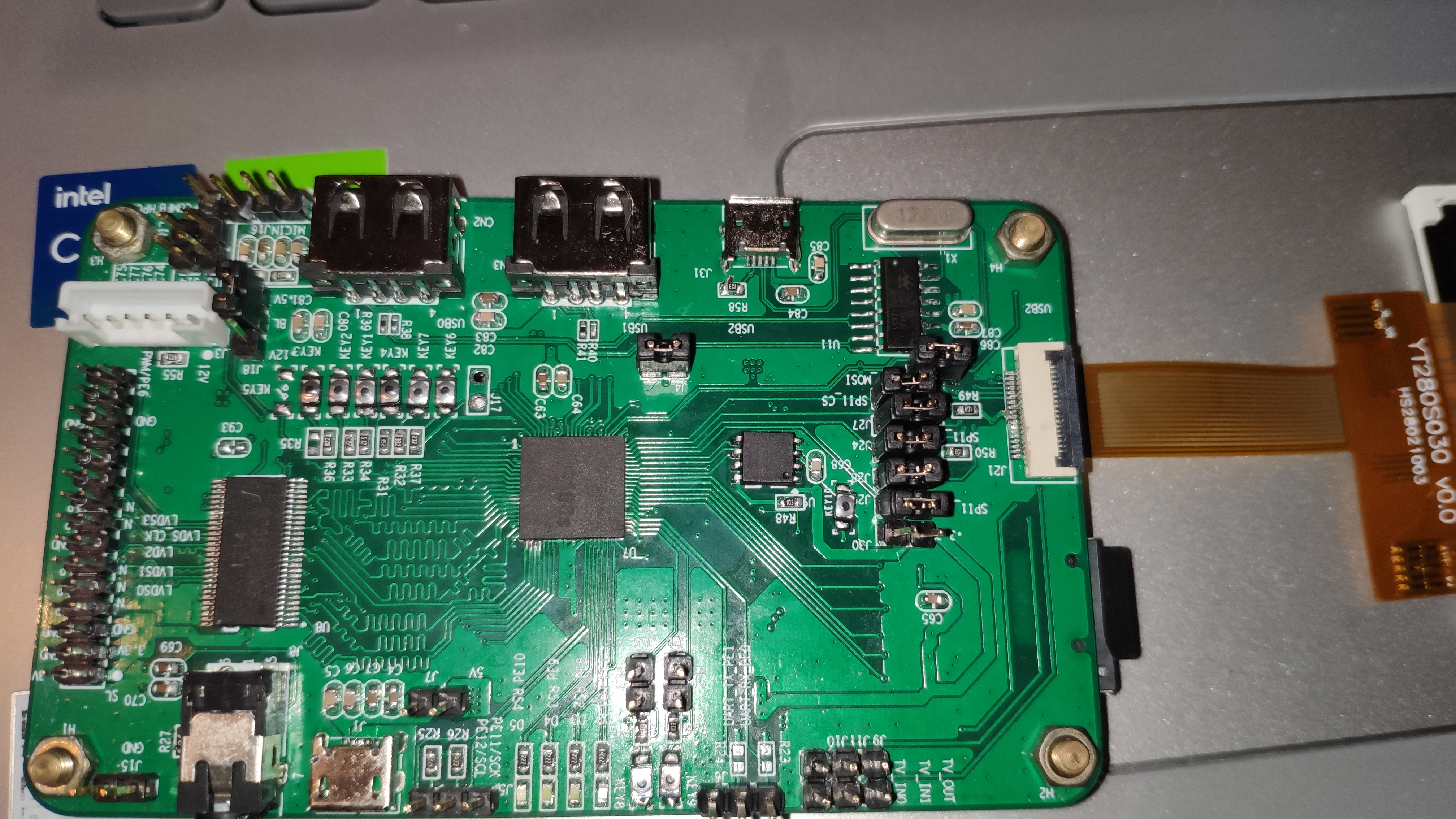

板子大小:6cm*10cm 嘉立创打板0元

这个板子画得很随意,大家多多包涵

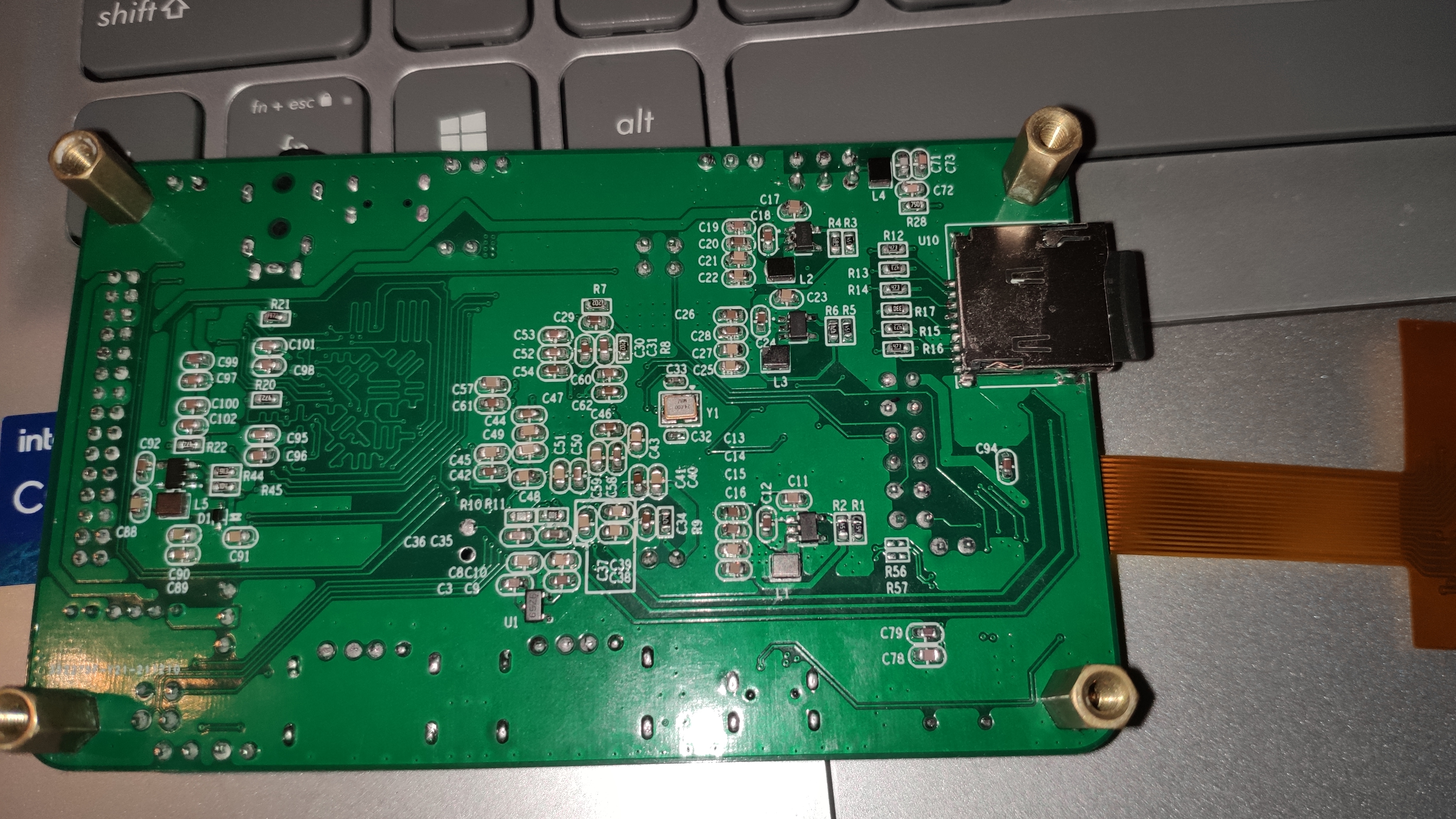

焊接完后

目前已经跑起来了,现在还在搞开机logo,现在SPI LCD颜色不对,还没找到原因,还要继续搞.jpg)

这个贴别感谢墨云的帖子、教程以及问题解答。

还有一点就是F1C100S的焊盘我做短了,特别不好焊接,兄弟们可以参考其他大佬的封装

这里贴上原理图和PCB

F1C100S.zip

#10 Re: 全志 SOC » 不雷同开源送两片,可选 D1/ D1s/ V3x/XR806/XR829/XR32/R11【长期有效】, F1C200s/V3s暂停 » 2021-12-23 08:35:23

#11 Re: 全志 SOC » 小白自制Linux开发板(F1C200s)整理系列,持续更新中 » 2021-12-20 12:40:12

楼主 我编译Linux系统,按照你的步骤,但是最后uboot没有识别到系统,可以请你帮忙看看吗?小白,不太懂

U-Boot SPL 2018.01-05679-g013ca457fd-dirty (Dec 18 2021 - 06:00:26)

DRAM: 32 MiB

Trying to boot from MMC1

U-Boot 2018.01-05679-g013ca457fd-dirty (Dec 18 2021 - 06:00:26 -0500) Allwinner Technology

CPU: Allwinner F Series (SUNIV)

Model: QL's f1c100s

DRAM: 32 MiB

MMC: SUNXI SD/MMC: 0

*** Warning - bad CRC, using default environment

In: serial@1c25000

Out: serial@1c25000

Err: serial@1c25000

Net: No ethernet found.

starting USB...

No controllers found

Hit any key to stop autoboot: 0

switch to partitions #0, OK

mmc0 is current device

Scanning mmc 0:1...

reading /suniv-f1c100s-licheepi-nano.dtb

3607 bytes read in 27 ms (129.9 KiB/s)

starting USB...

No controllers found

USB is stopped. Please issue 'usb start' first.

starting USB...

No controllers found

No ethernet found.

missing environment variable: pxeuuid

missing environment variable: bootfile

Retrieving file: pxelinux.cfg/00000000

No ethernet found.

missing environment variable: bootfile

Retrieving file: pxelinux.cfg/0000000

No ethernet found.

missing environment variable: bootfile

Retrieving file: pxelinux.cfg/000000

No ethernet found.

missing environment variable: bootfile

Retrieving file: pxelinux.cfg/00000

No ethernet found.

missing environment variable: bootfile

Retrieving file: pxelinux.cfg/0000

No ethernet found.

missing environment variable: bootfile

Retrieving file: pxelinux.cfg/000

No ethernet found.

missing environment variable: bootfile

Retrieving file: pxelinux.cfg/00

No ethernet found.

missing environment variable: bootfile

Retrieving file: pxelinux.cfg/0

No ethernet found.

missing environment variable: bootfile

Retrieving file: pxelinux.cfg/default-arm-sunxi

No ethernet found.

missing environment variable: bootfile

Retrieving file: pxelinux.cfg/default-arm

No ethernet found.

missing environment variable: bootfile

Retrieving file: pxelinux.cfg/default

No ethernet found.

Config file not found

starting USB...

No controllers found

No ethernet found.

No ethernet found.

=>

另外 你在编译系统时有什么配置吗 我看你没有写 我就用没改 然后系统是直接复制到BOOT文件夹下的

#17 全志 SOC » 全志H3四层板制作分享,从开始学allegro 到完成第一块高速板 » 2021-05-22 13:27:02

- laplace

- 回复: 44

自己学习了allegro,一直想画一块板子,自己画原理图,自己layout,然后打板出来,最后让linux跑起来,最后学一点linux,在论坛看到了大佬们的H3,我也想尝试下。

首先我找到了H3官方资料(吴川斌那里下的),这样原理图设计就有参考了,比较快。然后就是画PCB。

配置方面:USB*2

HDMI

耳机

按键*1

1个自定义LED 学习linux点灯用,哈哈哈

1个MPU6050的陀螺仪 进一步学习linux驱动使用

DDR3 512M *2

EMMC 5.0

WIFI

TF卡

PCB采用4层板,嘉立创打板,jlc2312结构。

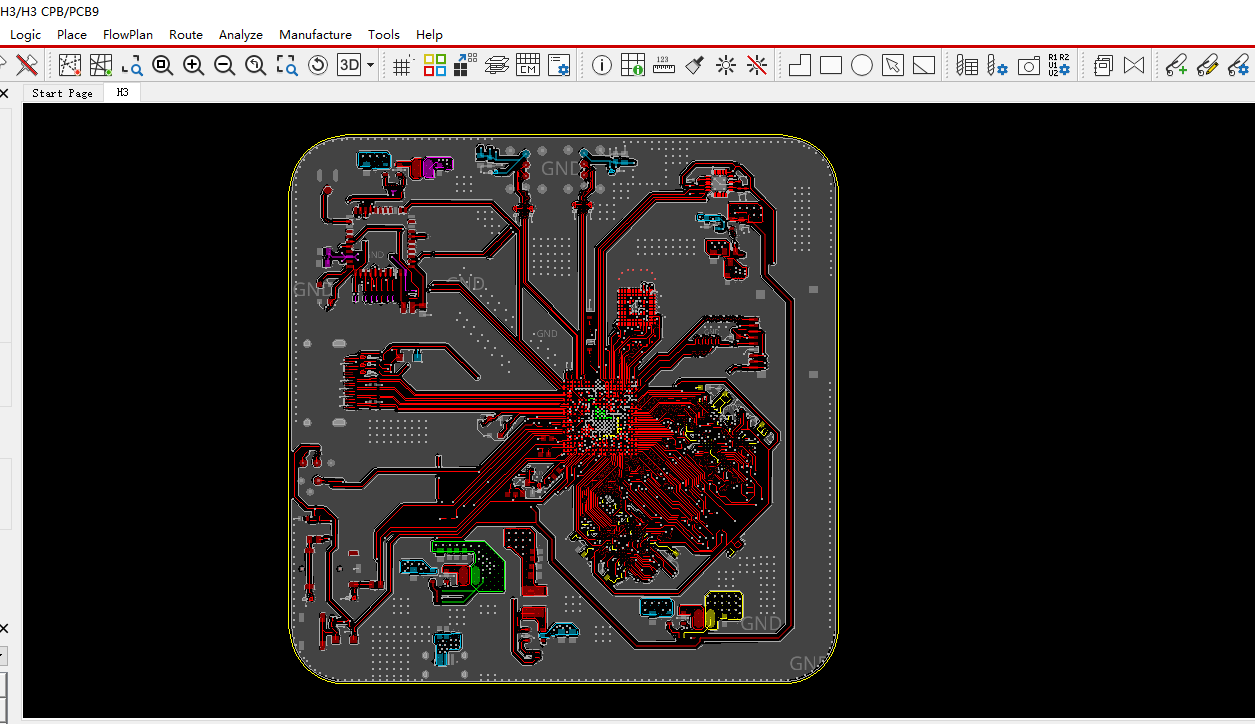

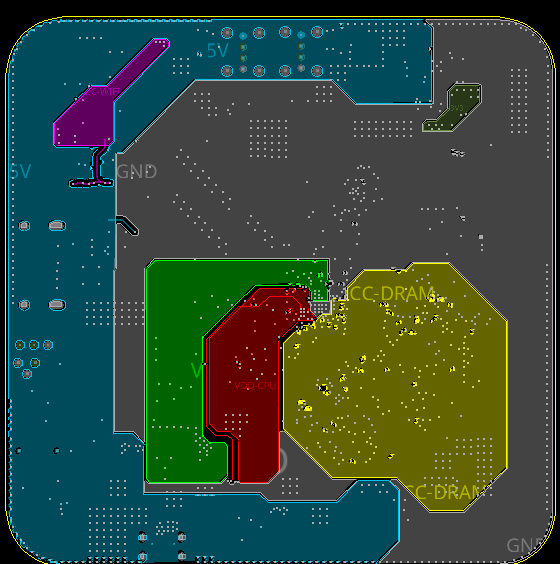

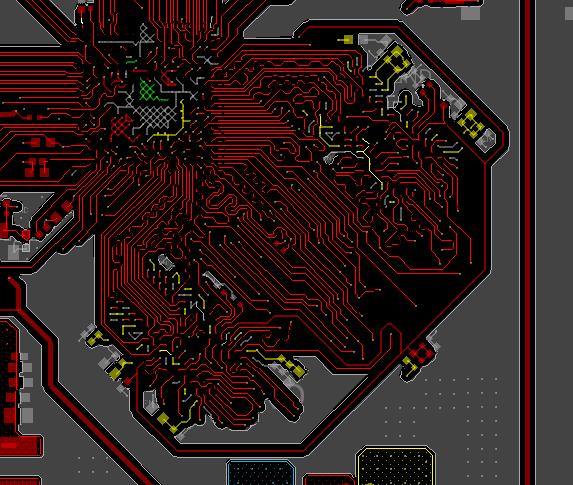

画完的板子:

TOP层

GND02层

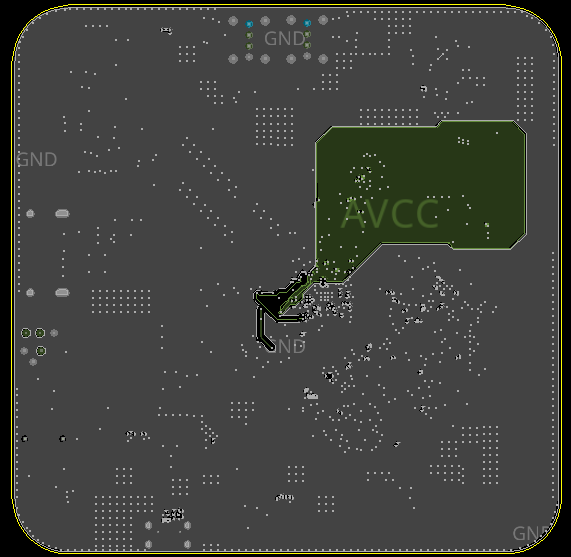

POWER03层电源分割

BOTTOM层

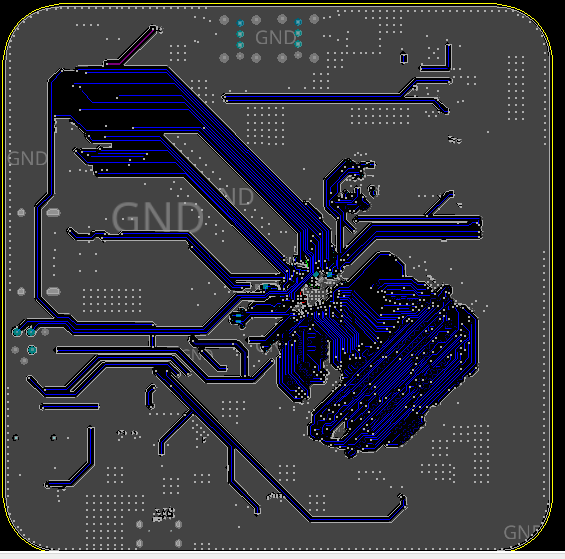

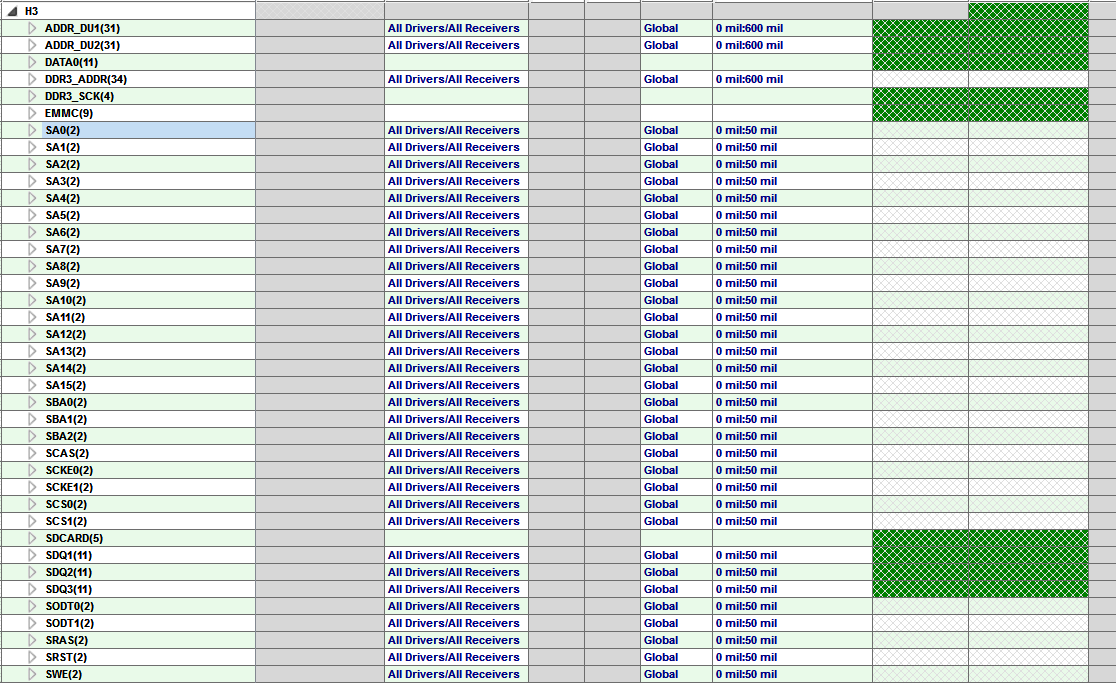

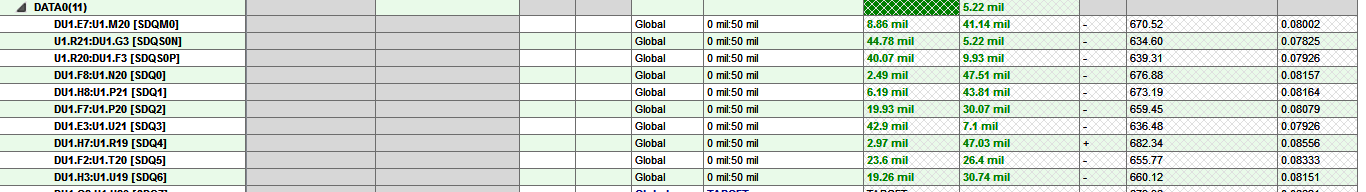

首先说说DDR3部分,T拓扑,在嘉立创打板50欧姆线宽为5.78mil,这使得布线比较紧凑,就没有满足3W原则,走的2倍线宽。

参考原厂DEMO:

不同地址线之间等长600mil,同一网络等长50mil

数据线组内等长50mil

时钟等长50mil

DDR3 TOP面走线:

走线比较乱,线间距比较小,主要是线宽有点大

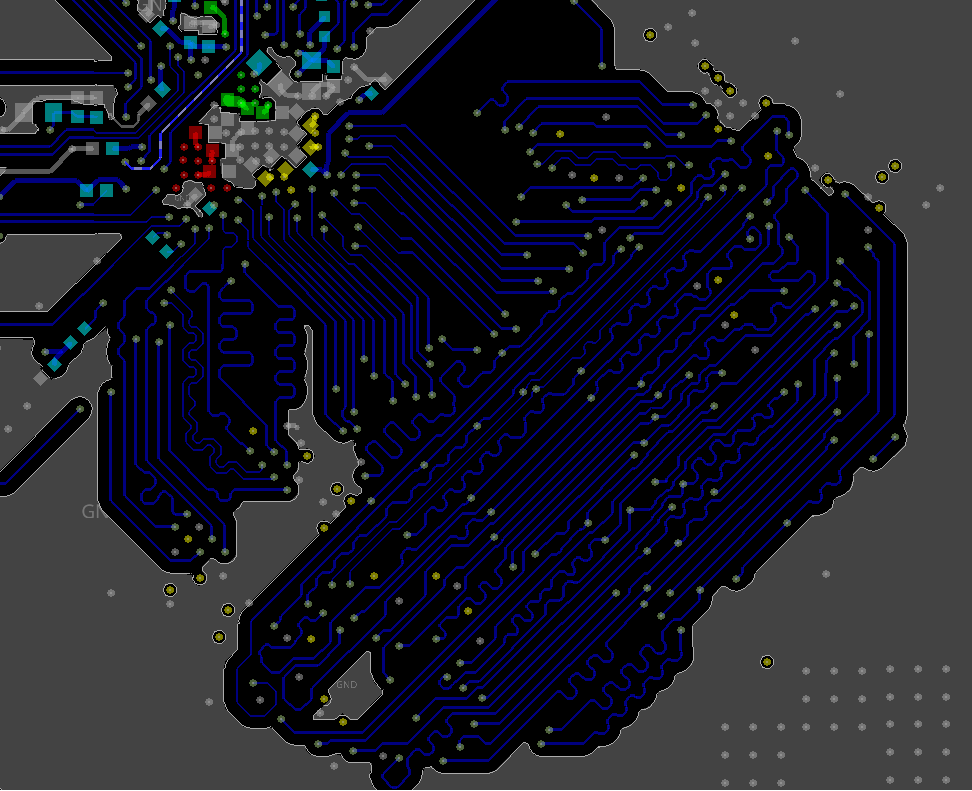

DDR3 BOTTM面走线:

为了等长也是走得一团乱

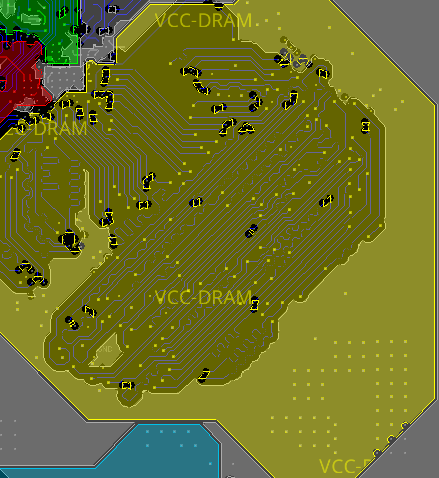

内层保证平面完整:

TOP层参考GND02层

BOTTM层参考VCC_dram:

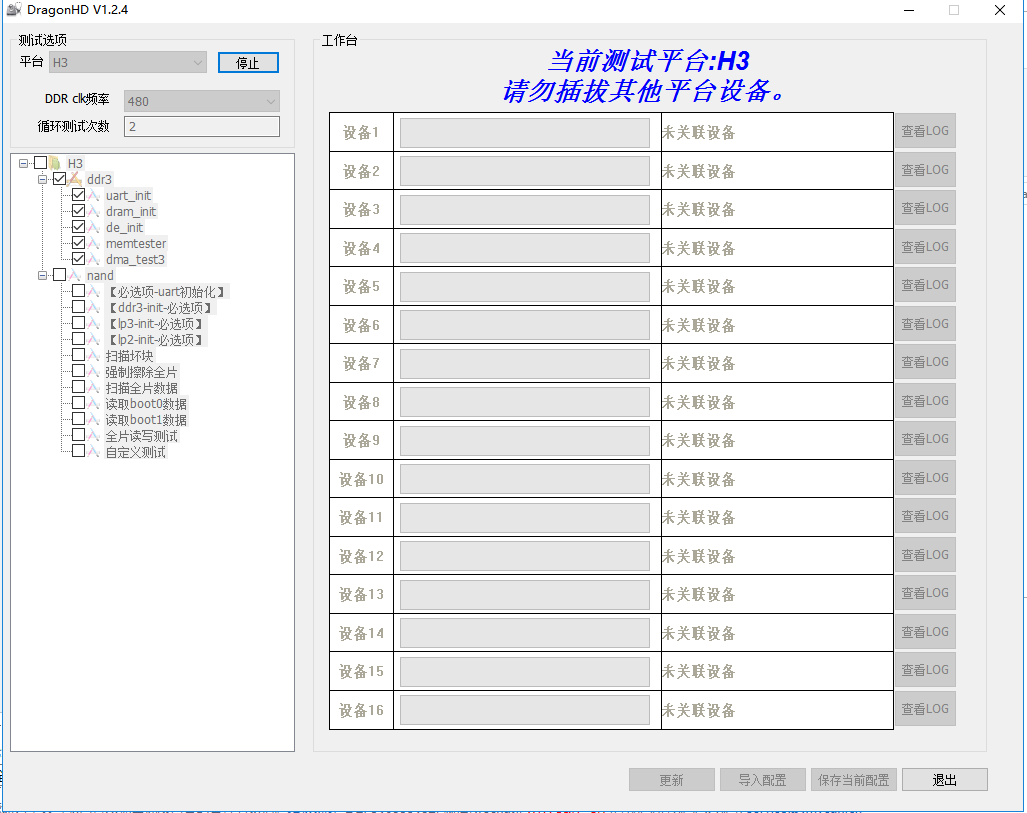

我今天使用DragonHD测试DDR3,我接的USB0,不知道为什么,没有任何反应,点了启动一直是下面这样:

恳求大佬们给我讲下这个软件怎么用的,是不是还需要什么驱动啊,我现在一头雾水。

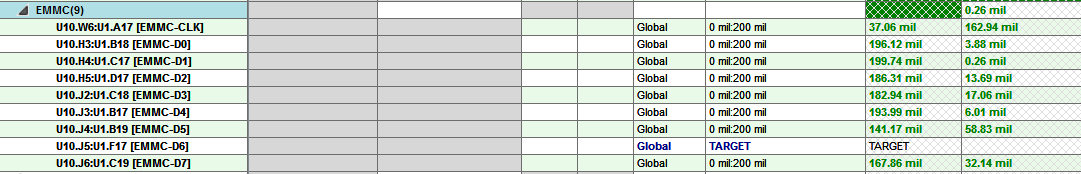

EMMC:

EMMC就做的200mil等长,现在还没使用EMMC

参考GND02层 VCC_IO_3.3V,保证平面完整。

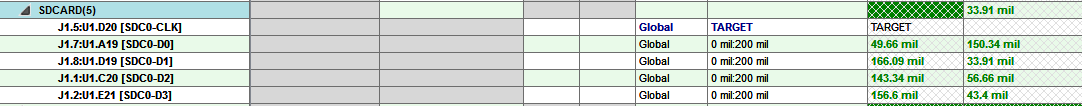

tf卡也是200mil等长:

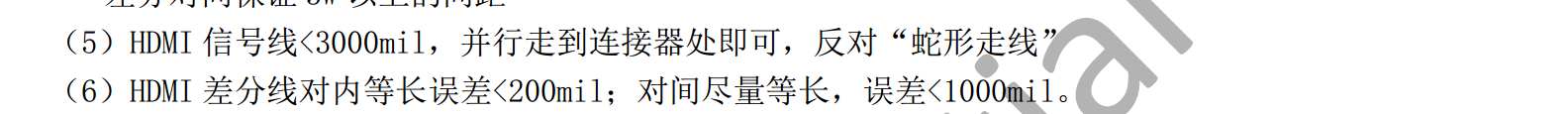

HDMI:

hdmi原厂要求不走蛇形线,等长要求宽松,直线拉通就是了,比较简单。

USB 对内5mil

最大的问题是在wifi-sdio上:

首先走线乱,其次就是数据线参考平面跨分割了,当时没注意到,缺乏经验。

板子布局:

板子大致布局我觉得没有问题,但是整个板子的线都很凌乱,没有横七竖八的美观,所以布局还需很大改进。

然后就是打板,嘉立创jlc2313结构打板有点慢,板子到手总共用了10天。

然后就是焊焊焊,目前还没焊完,只有周末有时间,平时加班也比较多,焊得也比较丑,哈哈哈哈

由于我自己不懂linux,所以也使用的是友善之壁的固件,醋酸胶布下面是一个散热片,真的比较烫:

使用debian

先写到这,自己先慢慢学习linux,希望能学会,希望大佬们也能多给我一些建议,特别是PCB Layout上的缺陷与不足,我好及时改进,也是非常难得的学习机会。

最后,后面可能会问到一些linux软件方面的问题,希望大佬们多多帮忙解答,爱你们,么么哒!!

附件(allegro 17.4):

H3.zip

#18 Re: 全志 SOC » 开源自己画的H3四层板打板只要50块 » 2021-03-05 16:50:13

页次: 1

- 首页

- » 搜索

- » laplace 发表的帖子

东莞哇酷科技有限公司开发