- 首页

- » 搜索

- » achinwoo 发表的帖子

页次: 1

#3 Re: 全志 SOC » T113的福利,分享一个关于T113 SPL以及rt-thread驱动适配的开源仓库 » 2024-10-21 12:15:22

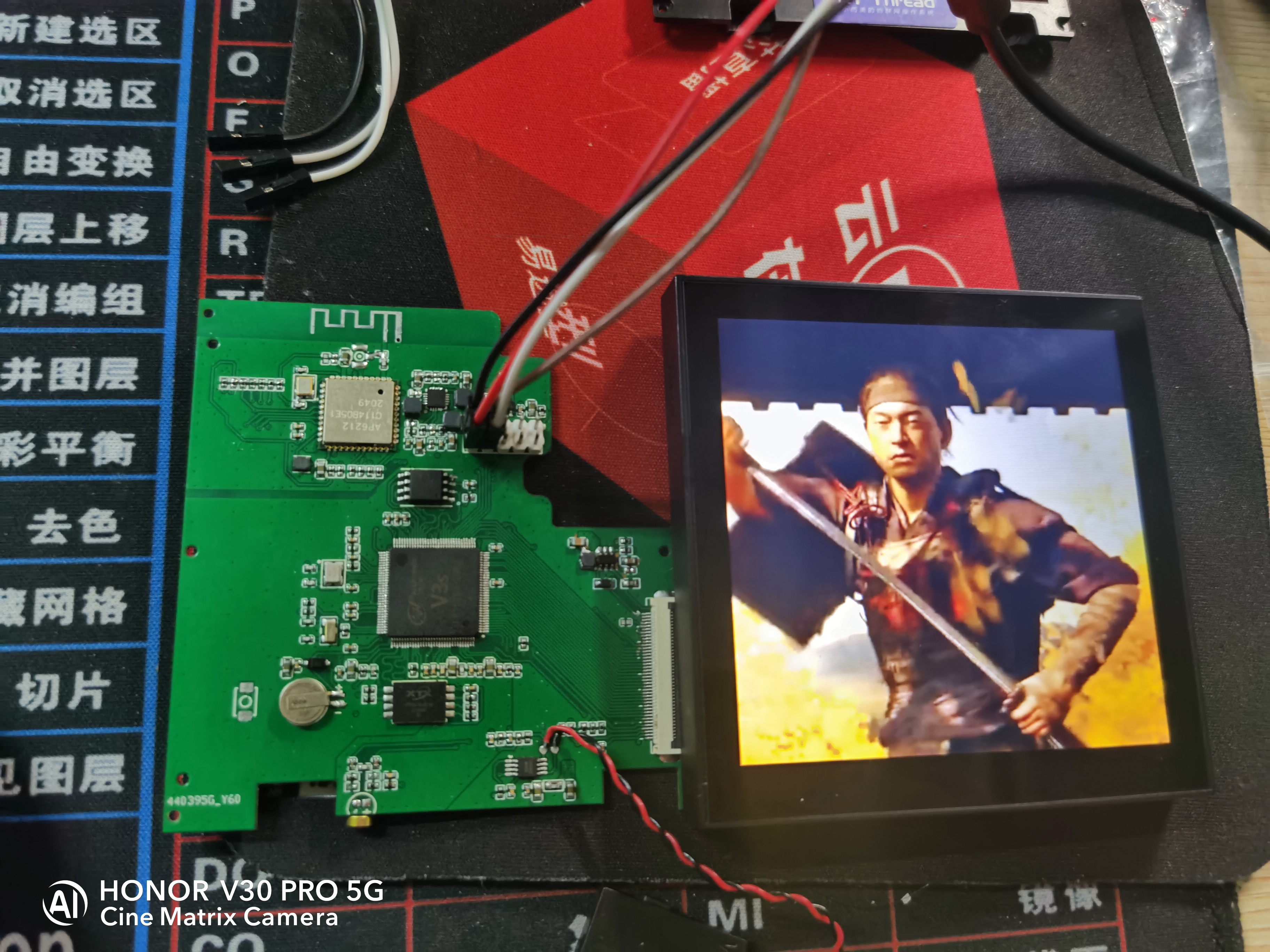

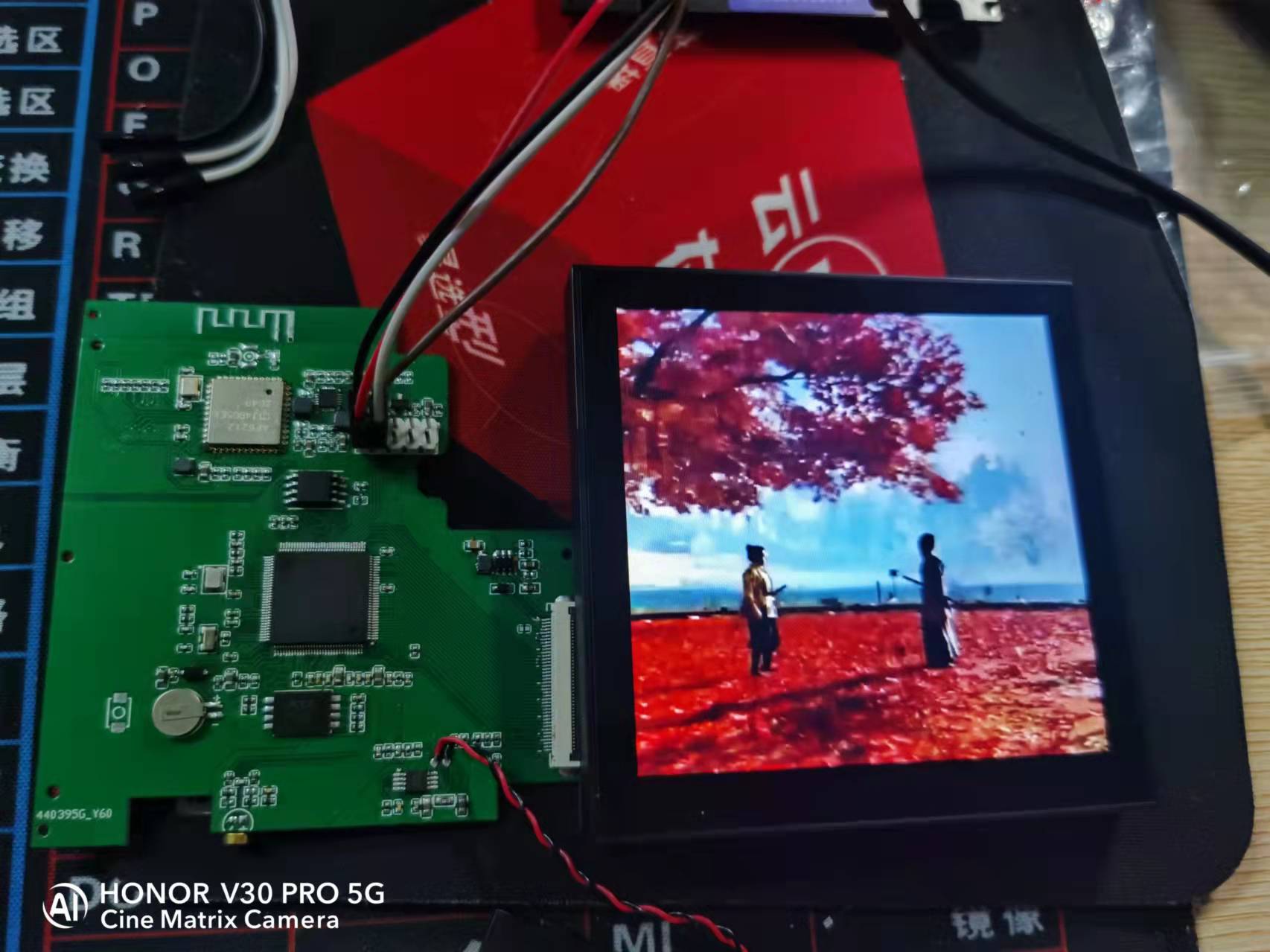

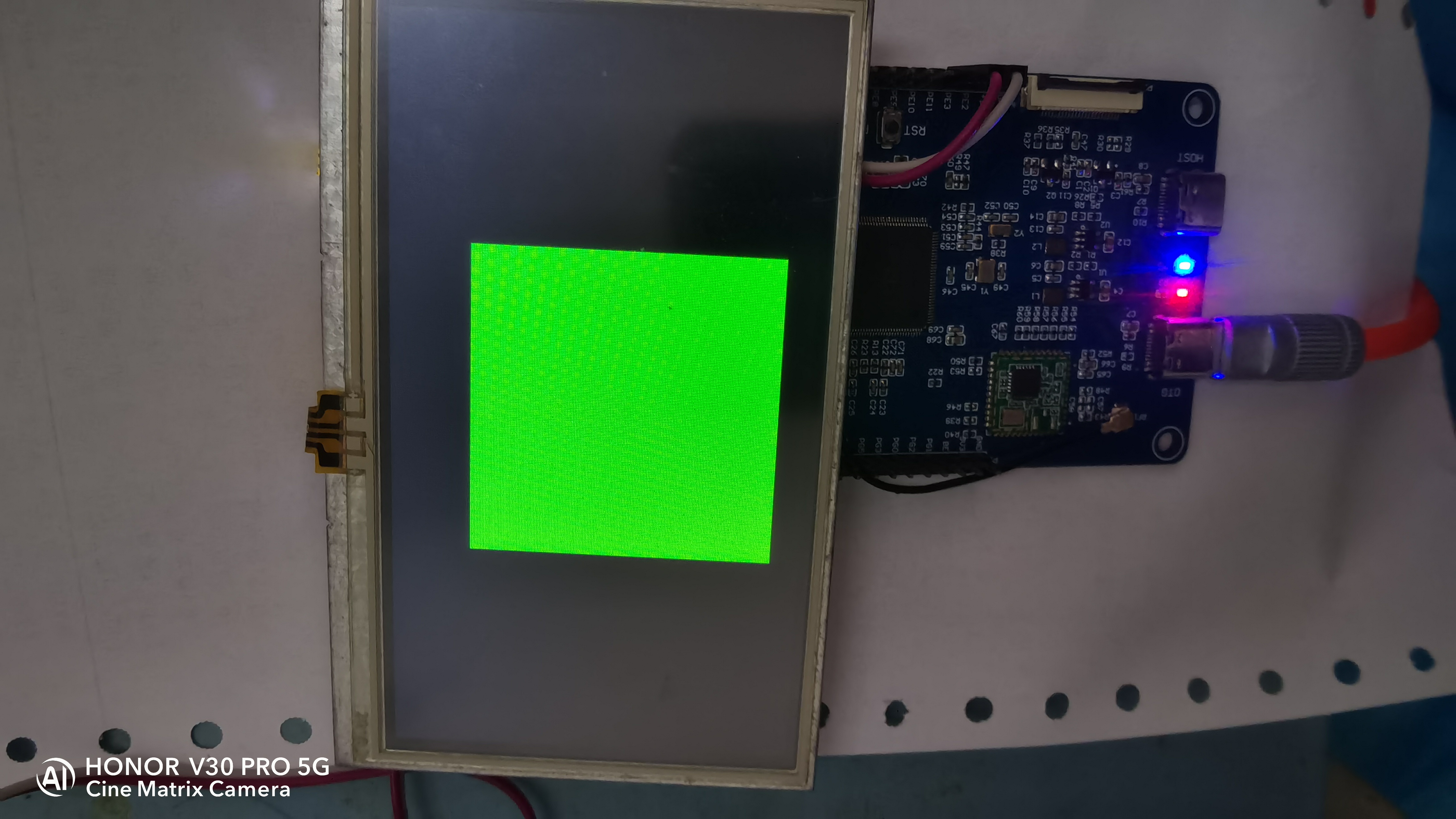

LCD驱动,寄存器方式

秋风冷飕飕,回家路途更新了lcd驱动,添加了drv_lcd.c, reg_de.h, reg_tcon.h文件,撸寄存器方式实现,特点固件体积小,适配其他分辨率LCD需要修改如下代码即可:

_panel = &lcd_config;

#define DEFAULT_LCD_CONFIG {\

width:480,\

height:272,\

bits_pixel:18,\

timing:\

{\

pixel_clock_hz:10000000,\

h_front_porch:8,\

h_back_porch:43,\

h_sync_len:4,\

v_front_porch:8,\

v_back_porch:12,\

v_sync_len:4,\

h_sync_active:0,\

v_sync_active:0,\

den_active:1,\

clk_active:0\

},\

swap_flag:0,\

ctp_flag:0\

}测试命令

lcd_draw_point 240 120

附带编译的固件

boot-with-pt16M_UART2.zip

#5 全志 SOC » T113的福利,分享一个关于T113 SPL以及rt-thread驱动适配的开源仓库 » 2024-10-18 22:27:37

- achinwoo

- 回复: 5

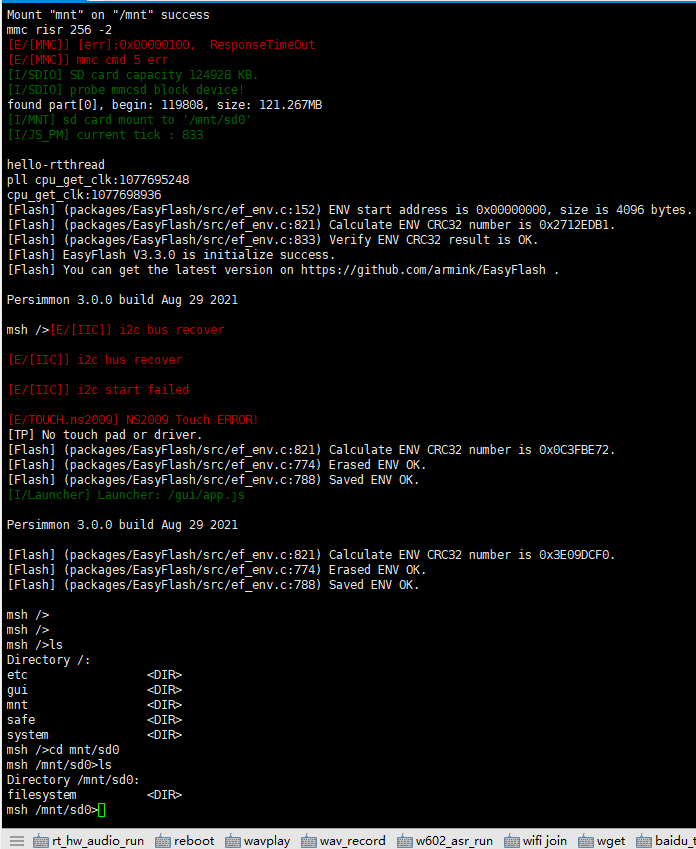

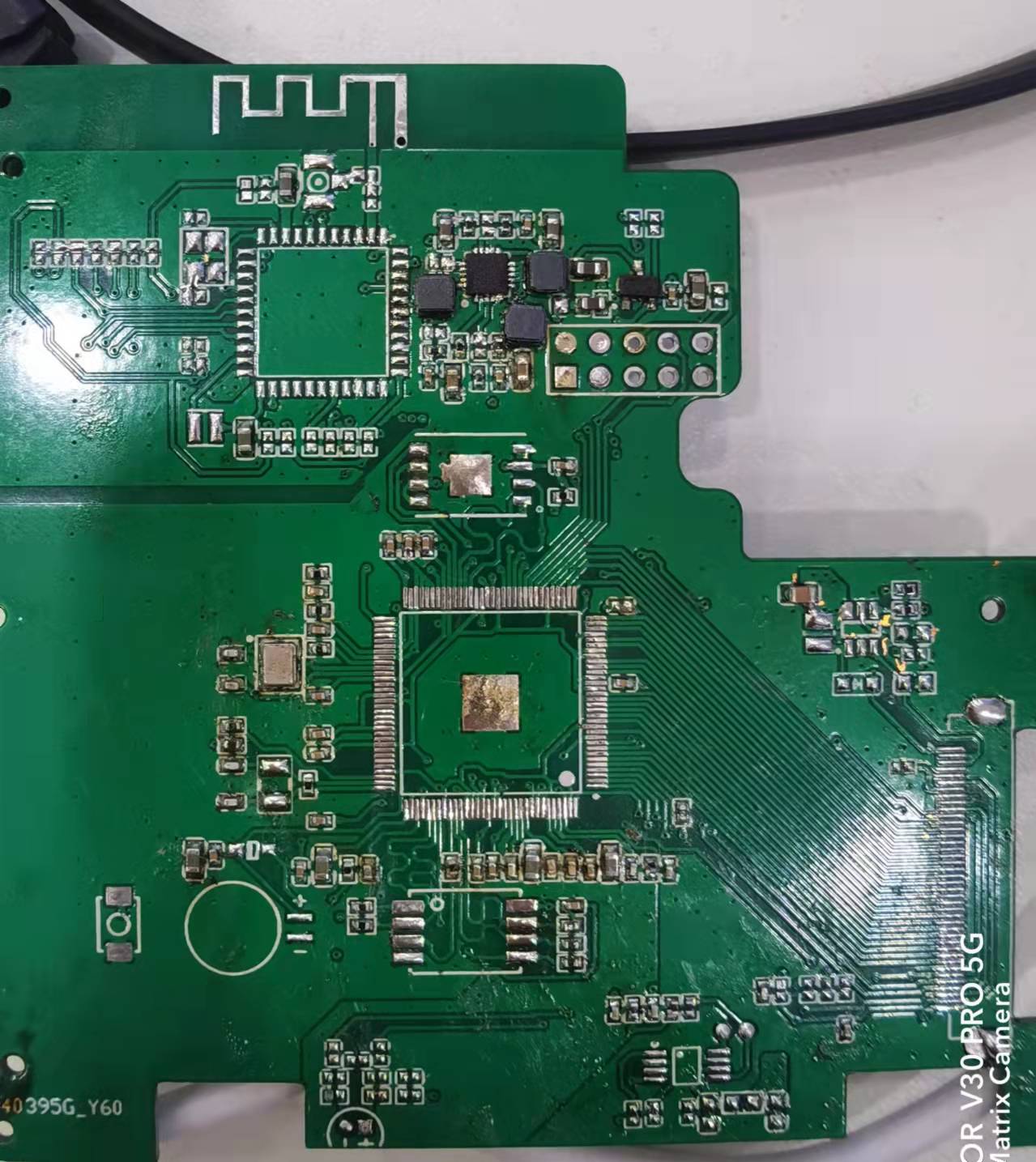

看到rt-thread适配了riscv d1 d1s的bsp,适配了基于hal的驱动,发现T113与D1 pin to pin兼容,所以感觉外设驱动不大,可以提高效率,减小工作量,所以有移植rt-thread的念头,目前已经扣出基于XBOOT大佬的驱动,适配了SPL,引导bootloader,目前已经测试通过,可以引导,很快更新仓库,有感兴趣的小伙伴一起研究!目前仓库更新了spl,bootloader,以及uart,gpio,watchdog驱动,适配了reboot测试完毕稳定后更新上来。目前所有测试基于MQ电路一致的硬件

仓库地址

https://gitee.com/achinwoo/t113-rt-thread-spl-bootloader-hal

万里长征第一步,T113的SPL实现

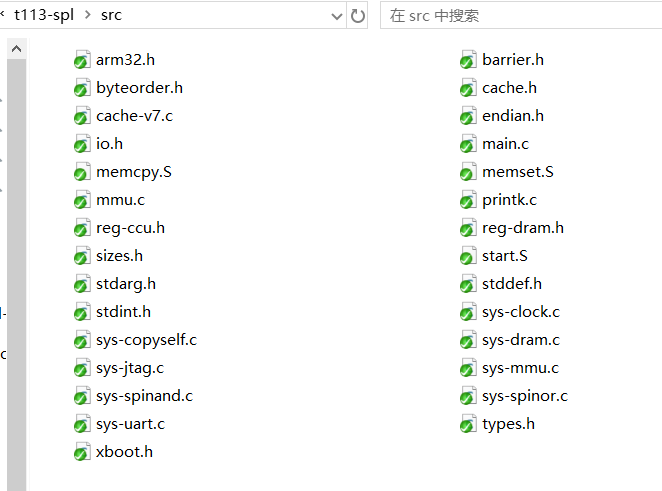

1.1 拷贝Xboot路径\xboot\src\arch\arm32\mach-t113s3的驱动代码,如下图所示

1.2 添加mksunxi.c工具,该工具负责计算sum,文件长度按照8K对齐方式,配置引导介质boot_media,比如spinor,spinand,sdmmc启动信息,添加到头中,占用64字节长度,详细阅读改代码,比较简单,容易理解。目前只适配了spinor启动。

添加scons脚本SConstruct,SConscript,

```

SConscript('./mksunxi/SConscript')

SConscript('./SConscript')

```

1.3 修改start.S汇编代码,修改之前代码

```

.align 5

undefined_instruction:

sub lr, lr, #4

save_regs

bl arm32_do_undefined_instruction

restore_regs

.align 5

software_interrupt:

sub lr, lr, #4

save_regs

bl arm32_do_software_interrupt

restore_regs

.align 5

prefetch_abort:

sub lr, lr, #4

save_regs

bl arm32_do_prefetch_abort

restore_regs

.align 5

data_abort:

sub lr, lr, #8

save_regs

bl arm32_do_data_abort

restore_regs

.align 5

not_used:

b .

.align 5

irq:

sub lr, lr, #4

save_regs

bl arm32_do_irq

restore_regs

.align 5

fiq:

sub lr, lr, #4

save_regs

bl arm32_do_fiq

restore_regs

修改之后代码

1.4 编译方法,win环境下scons命令即可,编译的log信息

1.5 产生一个固件名’sunxi-spl.bin’,通过xfel烧录到0地址即可

1.6 烧录后启动的信息,表明SPL成功运行,下步制作bootloader,未完持续….

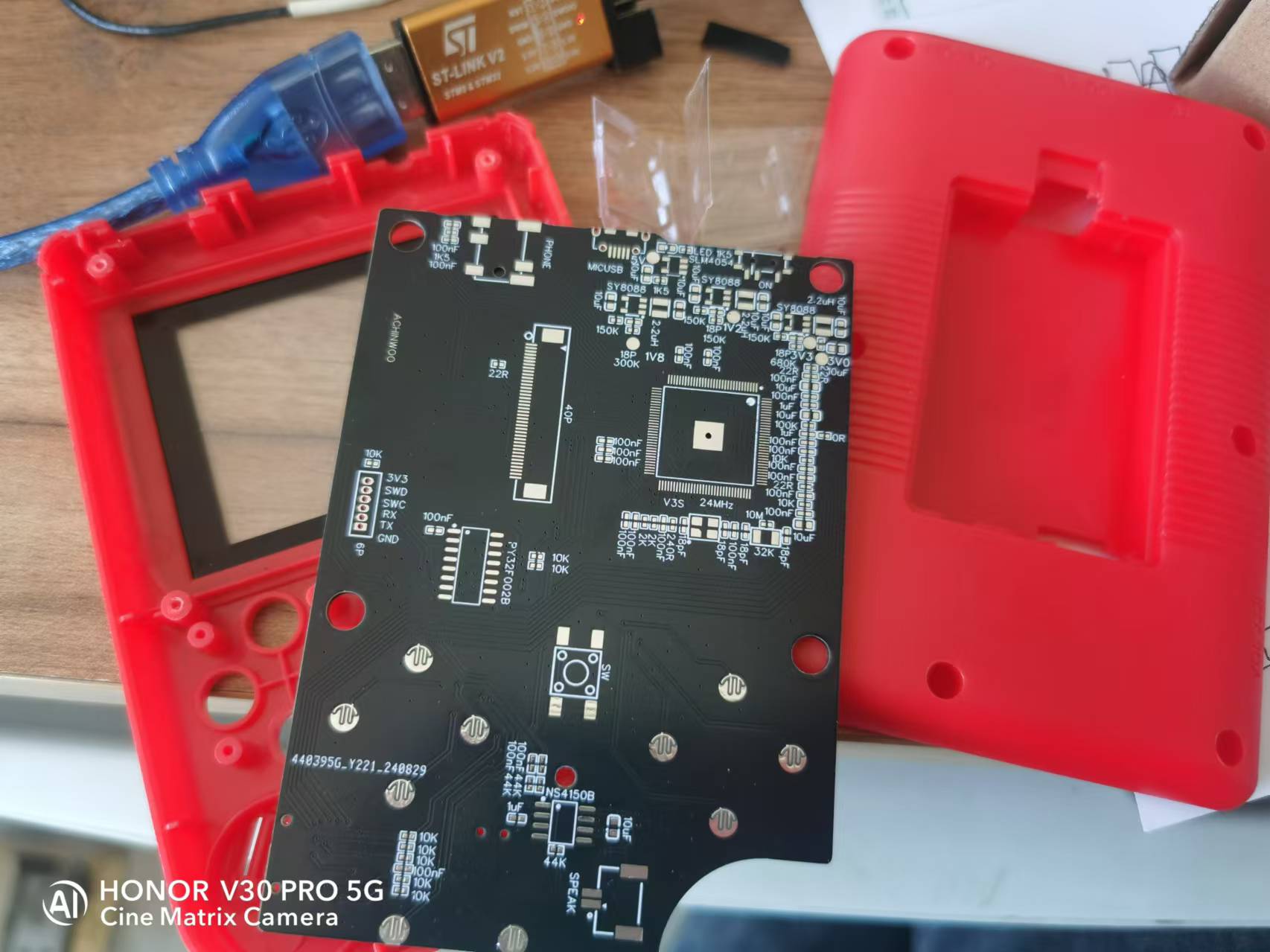

#6 Re: 全志 SOC » v3s 掌机 参考FUNKEY » 2024-09-02 13:01:03

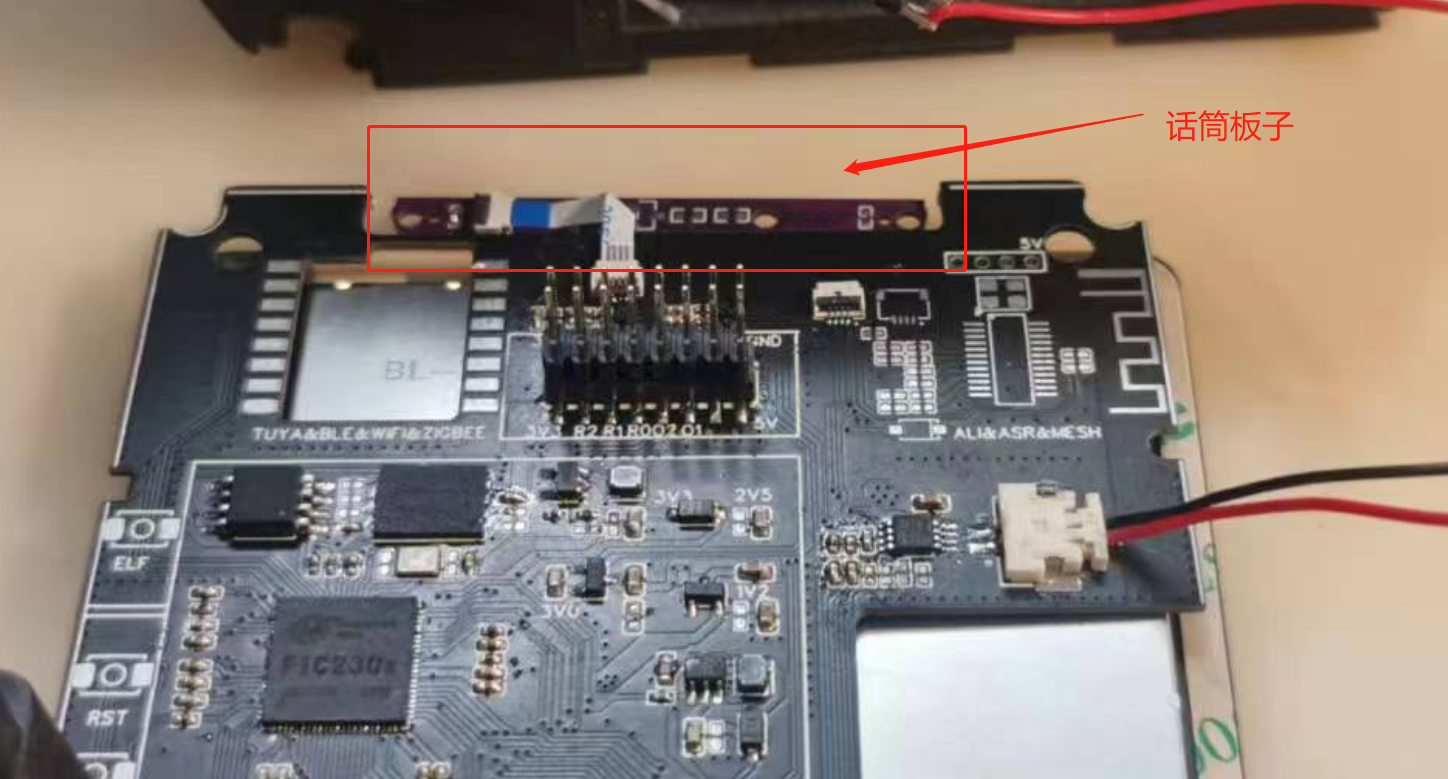

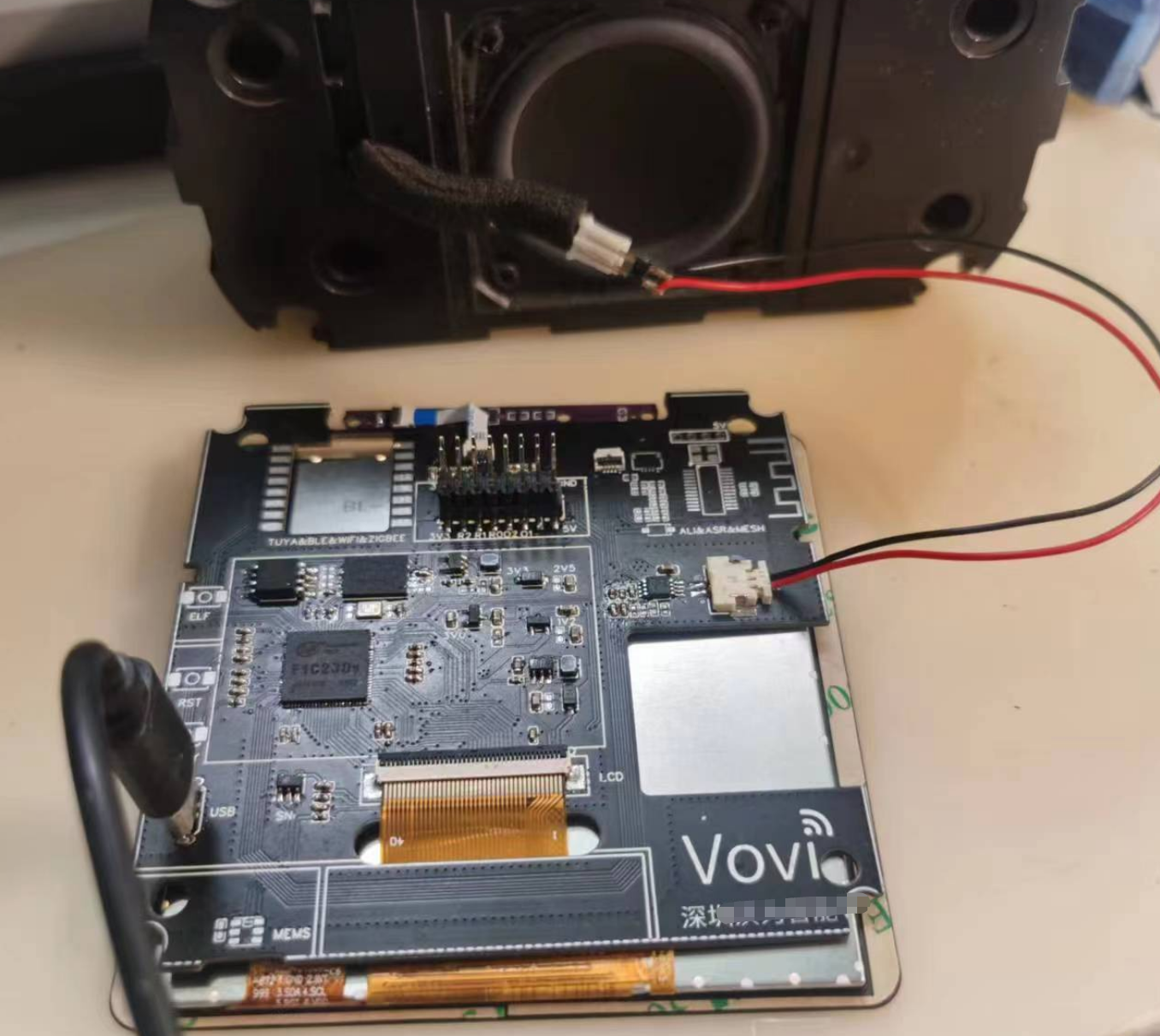

#7 Re: 全志 SOC » F1C100内置语音识别算法的测试 » 2023-08-11 13:03:37

#8 Re: 全志 SOC » F1C100内置语音识别算法的测试 » 2023-08-11 13:01:01

#11 哇酷地摊(跳蚤市场) » 杰理移植LVGL » 2022-11-30 09:57:47

#12 Re: 全志 SOC » 不雷同开源送两片,可选 D1/ D1s/ V3x/XR806/XR829/XR32/R11【长期有效】, F1C200s/V3s暂停 » 2022-01-22 20:11:01

#13 Re: 全志 SOC » 不雷同开源送两片,可选 D1/ D1s/ V3x/XR806/XR829/XR32/R11【长期有效】, F1C200s/V3s暂停 » 2022-01-20 00:41:28

#14 Re: 全志 SOC » 不雷同开源送两片,可选 D1/ D1s/ V3x/XR806/XR829/XR32/R11【长期有效】, F1C200s/V3s暂停 » 2022-01-19 13:45:37

#15 Re: 全志 SOC » 不雷同开源送两片,可选 D1/ D1s/ V3x/XR806/XR829/XR32/R11【长期有效】, F1C200s/V3s暂停 » 2022-01-17 09:04:26

#16 Re: 全志 SOC » 开源V3x 项目,立创EDA格式。 » 2022-01-09 23:47:27

#17 Re: 全志 SOC » 开源V3x 项目,立创EDA格式。 » 2022-01-09 22:34:16

#18 Re: 全志 SOC » 不雷同开源送两片,可选 D1/ D1s/ V3x/XR806/XR829/XR32/R11【长期有效】, F1C200s/V3s暂停 » 2022-01-09 21:59:15

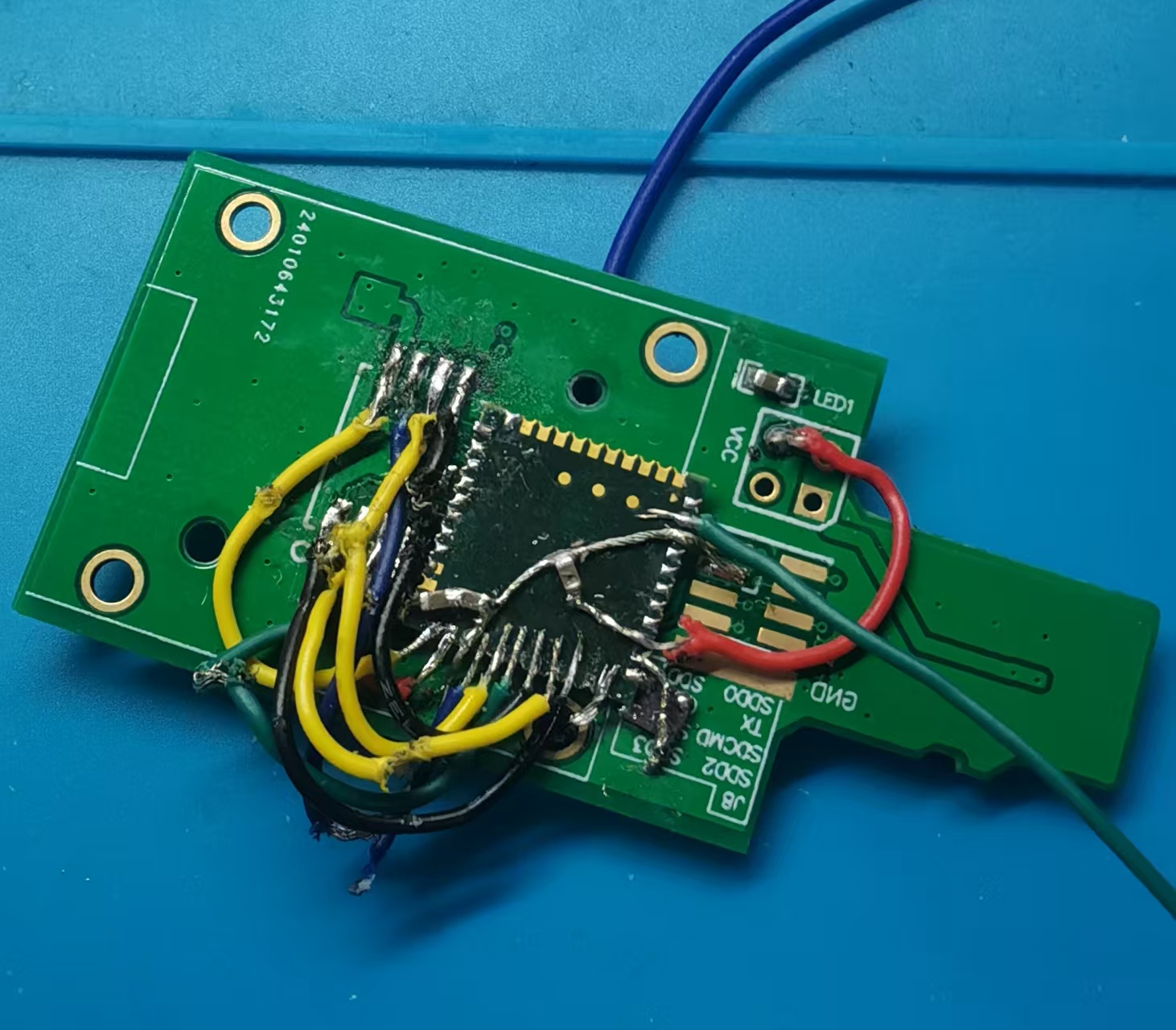

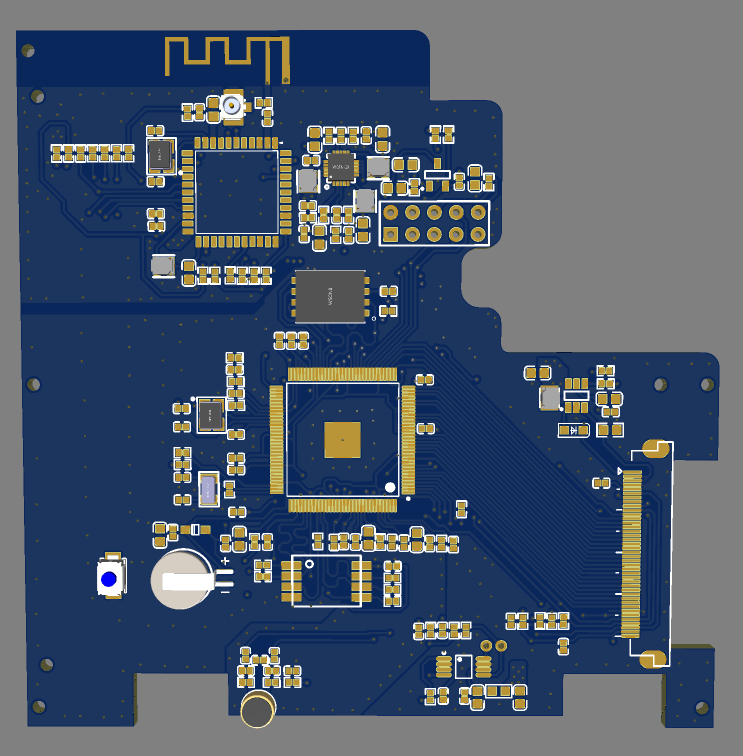

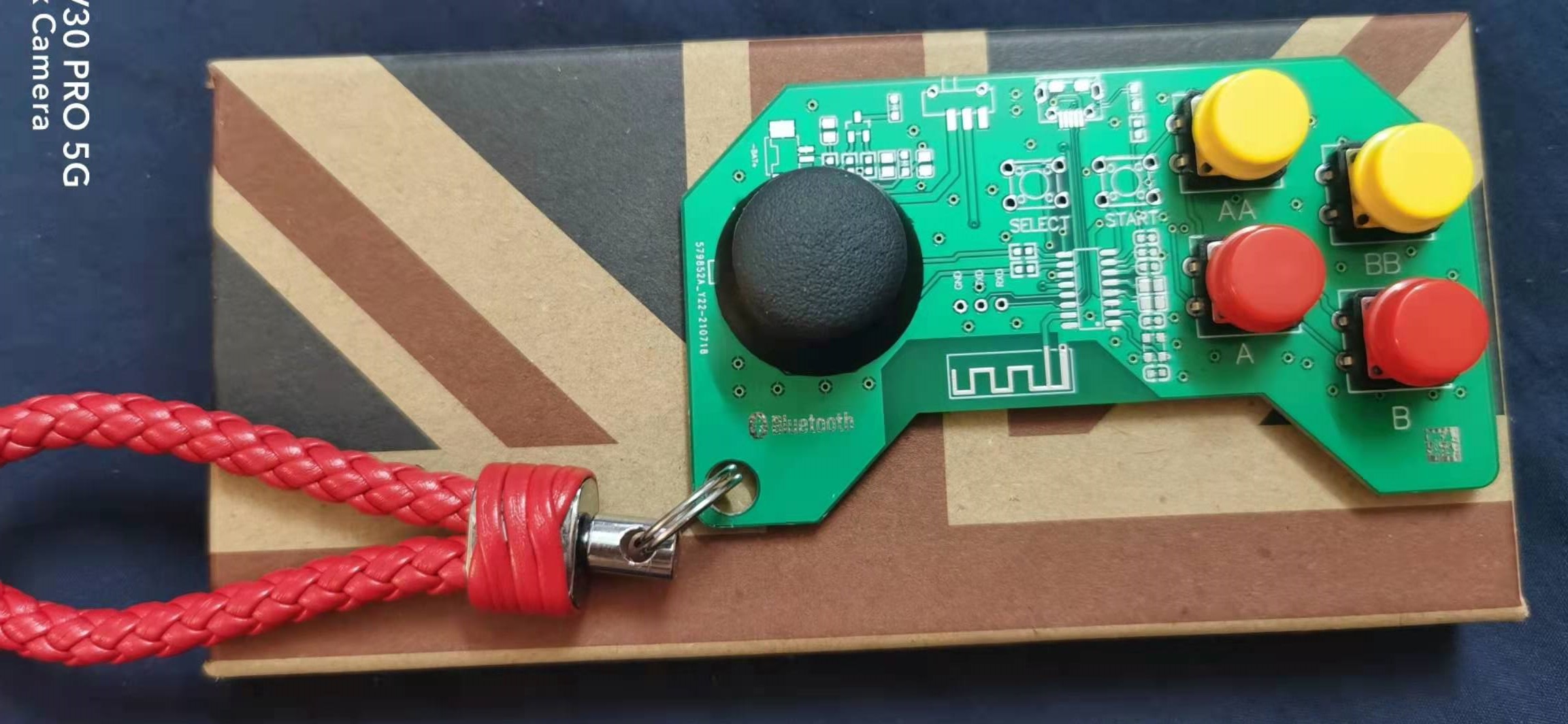

#20 司徒开源 » 动手DIY蓝牙手柄 » 2021-07-26 23:47:23

- achinwoo

- 回复: 8

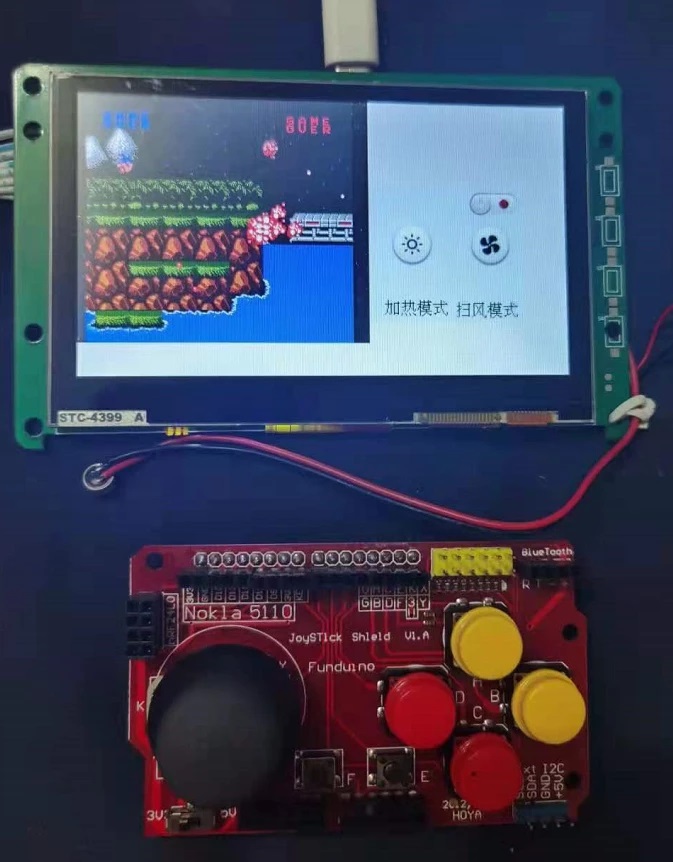

近期在调试市面一款RW007模块的BLE部分,于是想制作一个蓝牙游戏手柄,玩一下游戏模拟器,找回童年的乐趣!

设计雏形,购买一块开发板,然后杜邦线连接,发现问题,有点费手!插针TMD扎手啦。

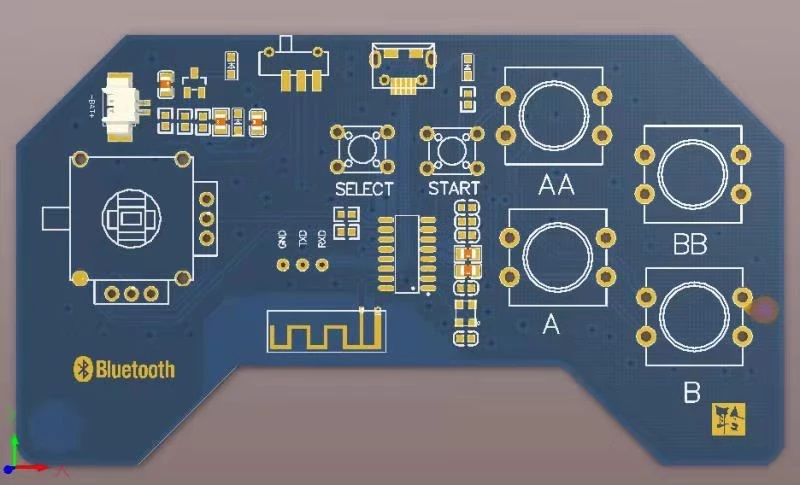

果断放弃,免费PCB打样中,重新设计一款。

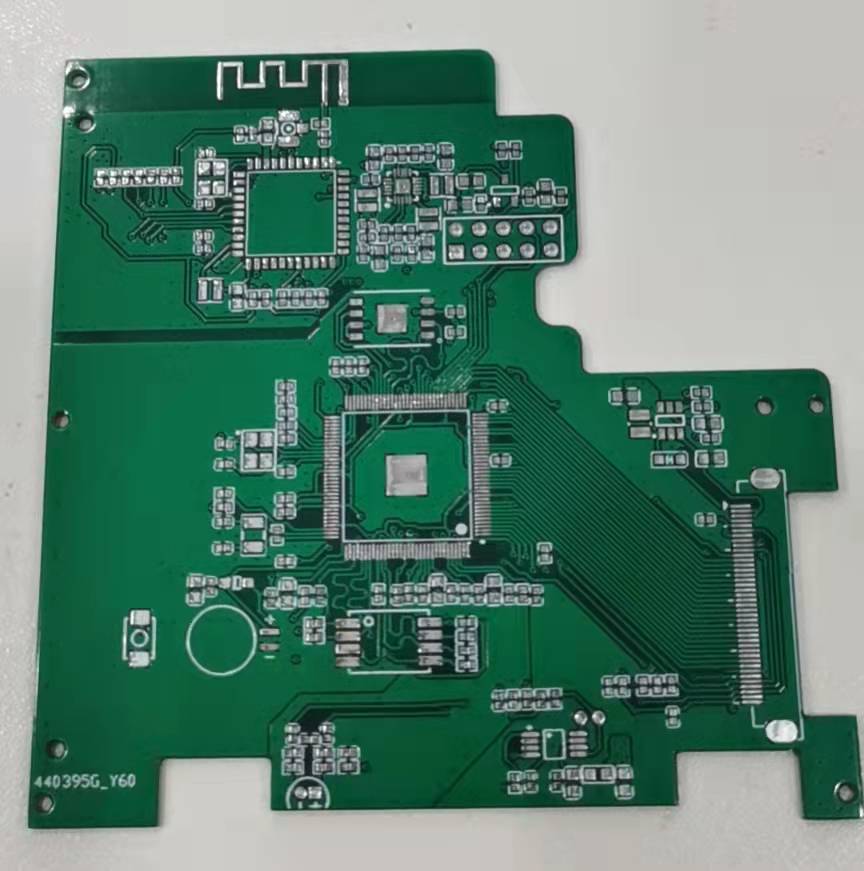

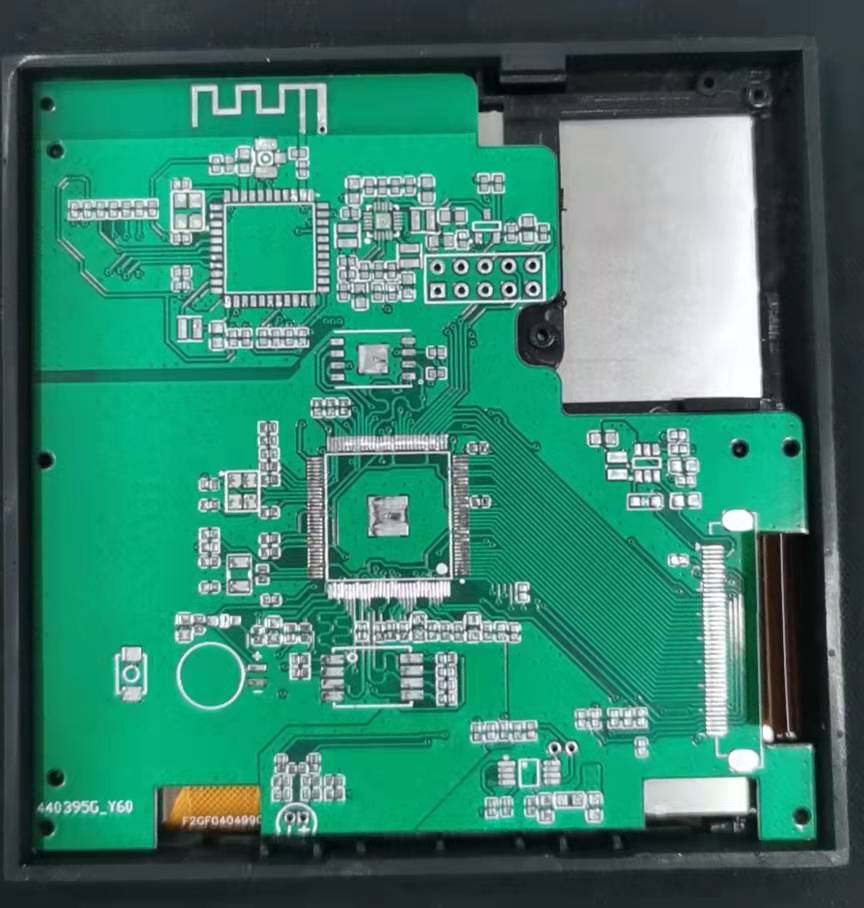

PCB到了,还没来及焊接,先上个谍照吧!

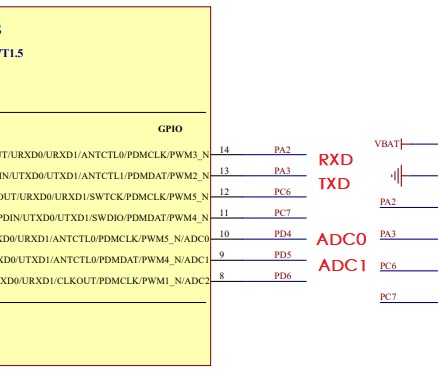

主控芯片信息

| 参数 | 叙述 |

| ------ | ------ |

| 型号 | FR8012乞丐版 |

| 版本 | 蓝牙5.1 |

| 内核 | cortex-m3 |

| 时钟频率 | 48Mhz |

| RAM | 48K |

| FLASH | 256KB |

| 封装 | SOP-16 |

| 系统 | rt-thread 民间移植版 |

技术难题

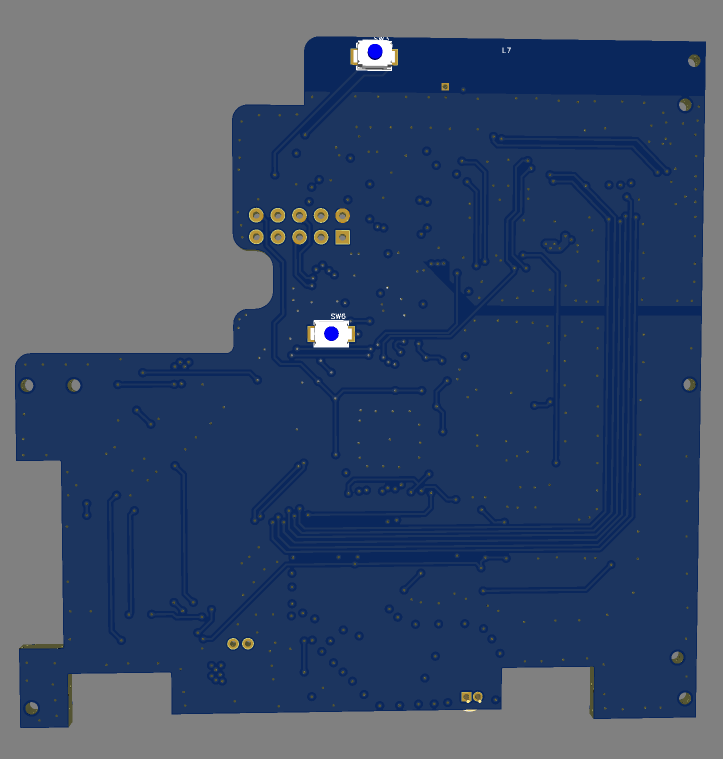

这个蓝牙游戏手柄,其实蓝牙通讯,如何匹配倒没有花费很多的精力,或许因为通讯那部分比较成熟,拿过来使用就可以了。另外得到了大佬的指导,顺利的调通了无线通讯协议部分。主要遇到的难点是引脚不够,比较紧张。如图:

1 PA2,PA3烧写调试,无法做按键输入使用。PASS。

2 采用ADCKEY方式,分析因为手柄支持组合按键,该方案pass。

3 剩下5个引脚,其中PD4,PD5做摇杆ADC通道采集使用,只剩下3个GPIO了,PC6,PC7,PD5.如果对地设计按键,只能设计3个了.

4 游戏手柄除去4个方向键,目测还有select,start,A,B,AA(连发),BB(连发)6个键值。

4 有点脑瓜疼!谁让我们用的是SOP-16封装呢?想办法,办法总比困难多。这3个GPIO分别ADC0,ADC1做矩阵,时分复用能否可行?

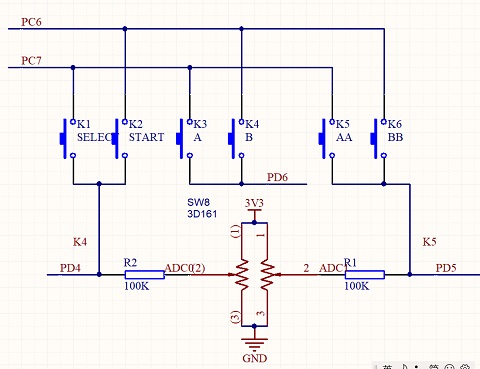

5 细思量后发现一个极其恐怖的问题,手柄是支持组合按键的,如果玩家方向键与A键同时按下,会发生很严重的过流问题。是坚决不能允许的。

6 串联限流隔离电阻,解决了问题。

工作原理

1 先将5个引脚关闭上拉,配置输入方向,配置ADC0,ADC1,获取4个方向数值。adc关闭转换结束。

2 将5个引脚配置GPIO,并且上拉有效。

2.1 配置PD4方向为输出,并且输出0.

2.2 分别读取PC6,PC7引脚电平值,作为SELECT,START键值.

2.3 配置PD4方向输入,上拉有效,配置PD5方向输出,并且输出0

2.4 分别读取PC6,PC7引脚电平值,作为AA(连发),BB(连发)键值.

2.6 配置PD5方向输入,上拉有效,配置PD6方向输出,并且输出0

2.7 分别读取PC6,PC7引脚电平值,作为A,B键值.

2.8 配置PD6方向输入,上拉有效。J结束。焊接成品,可以同时支持2个手柄PK啦!

PK的视频,

页次: 1

- 首页

- » 搜索

- » achinwoo 发表的帖子

东莞哇酷科技有限公司开发