楼主 # 2022-02-07 17:34:55 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

本工作在本站大佬 @ljbfly 的工作基础上改进而来

详细见帖子:CH552 版 CMSIS-DAP v2 https://whycan.com/t_3732.html

基本大框架没有动,使用汇编优化了SWD时序,高速提供IO模拟的SWD时序,也提供一个硬件SPI的尝鲜。

完全重写C+汇编混和优化了虚拟串口部分,有效减小串口丢包,发送中断问题,提高效率

只使用v2版本的免驱动bulk模式,不兼容V1版本的hid,提供一个虚拟串口

目前空间占用,rom用了7k多,ram基本都榨干了,xram全部是缓存,iram剩余字节数也不多

开源代码、编译好的固件、PCB工程获取途径:https://github.com/posystorage/CH55x_HS_DAP-Link-v2

优化思路参考了 @metro大佬的工作,参见:

【重开旧坑】8051上的CMSIS-DAP调试器——TinyDAP开发过程记录 https://whycan.com/t_6114.html

晒一下CH558跑的CMSIS-DAP v2调试器,下载速度可以达到70KB/s(Flash)和300KB/s(SRAM) https://whycan.com/t_3766.html

和@metro大佬比起来,本人的目标是实现高速的SWD优化,暂时不打算涉猎JTAG\SWO\文件拖拽下载\兼容HID等这些功能,主要应用方向是做板载调试器(例如使用CH552E实现串口+SWD),在开发板上非常方便的调试芯片,减少接线

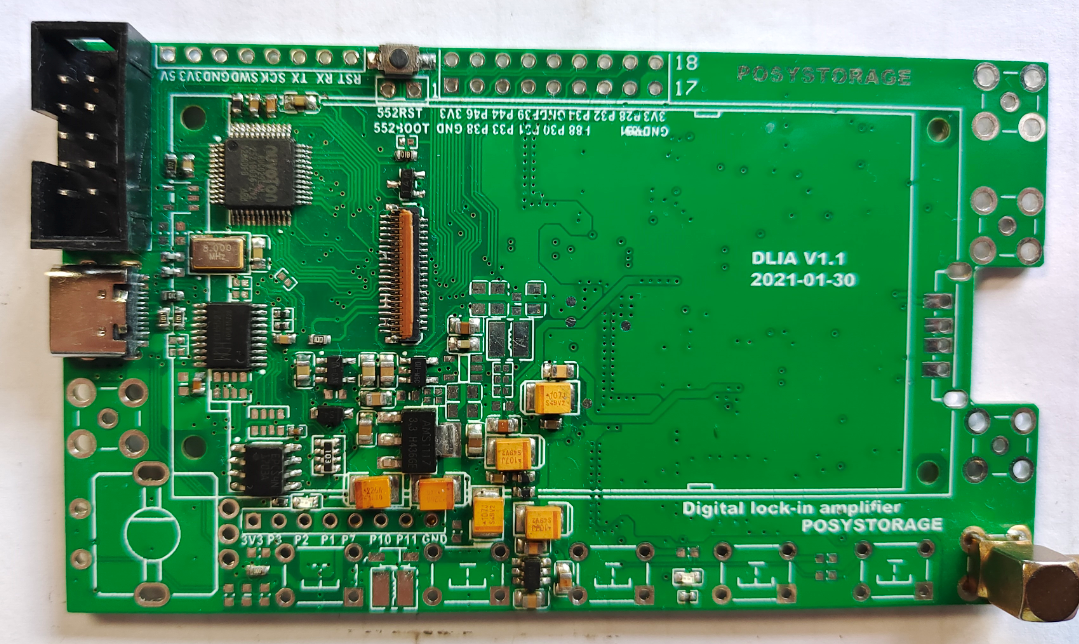

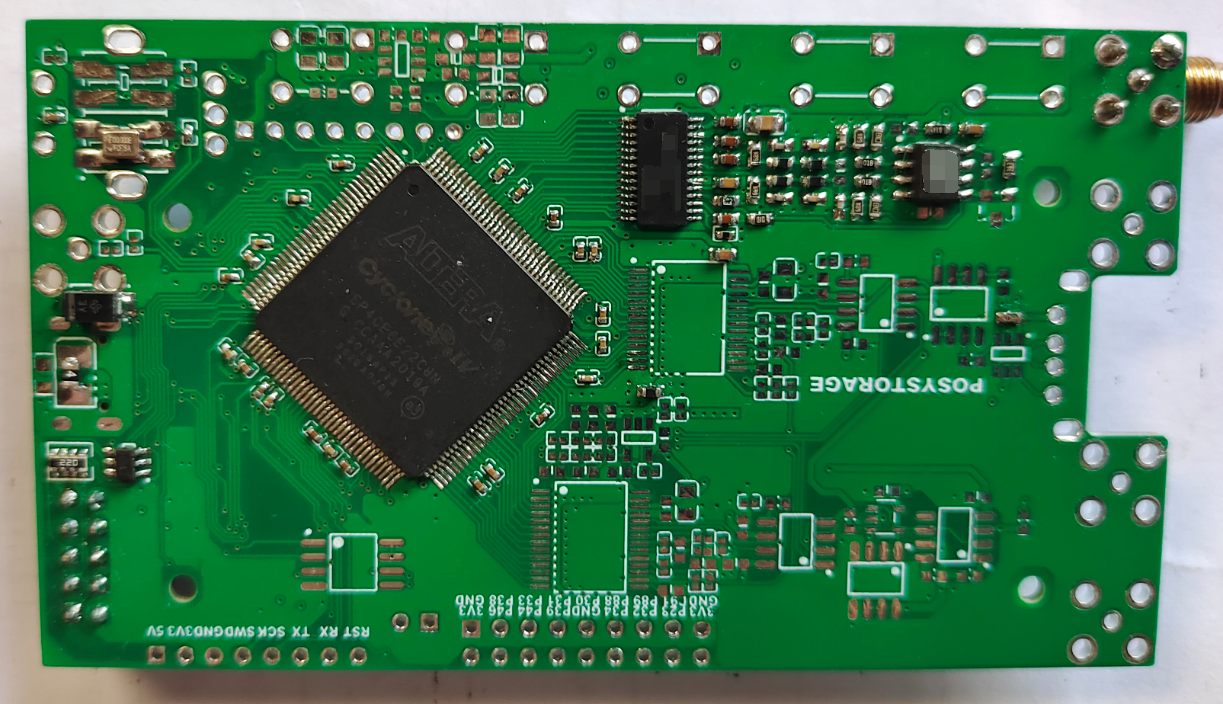

比如说挖坑的这个做数字锁相放大器的板子,由CH552负责通讯+SWD调试单片机+JTAG调试FPGA,全部集成。当然这坑啥时候能填完又是另说了。

回归正题

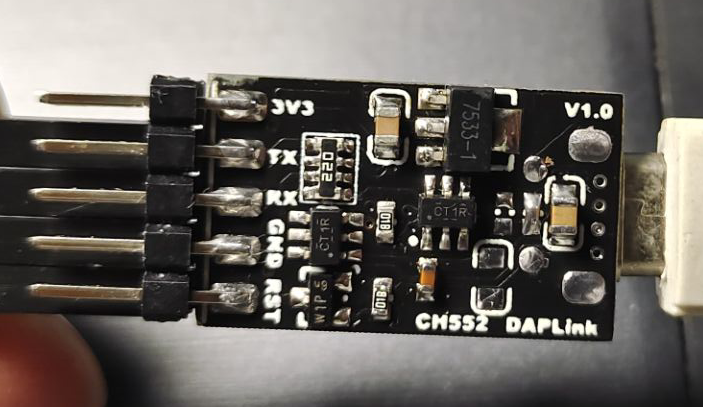

硬件实现 我这个板子可以选3.3V供电或者5V,我考虑的是选5V可以跑24M主频(实测32M也稳定可跑),然后IO电平用两颗1T45转换成3.3V,顺便负责SWDIO的换向,板子体积非常小。

如果是板载调试器的话,用3.3V供电跑16M也还是足矣,可以节约不少外围。

@ljbfly大佬编写的代码是全C实现的,由于编译器问题,SWD底层部分在频繁的搬数据,时序效果看起来占空比非常高,而且SWD输入的时候直接使用推挽读取(让我一开始非常迷惑),实测下来有的单片机如果SWD脚驱动不强的话可能兼容性不太好。

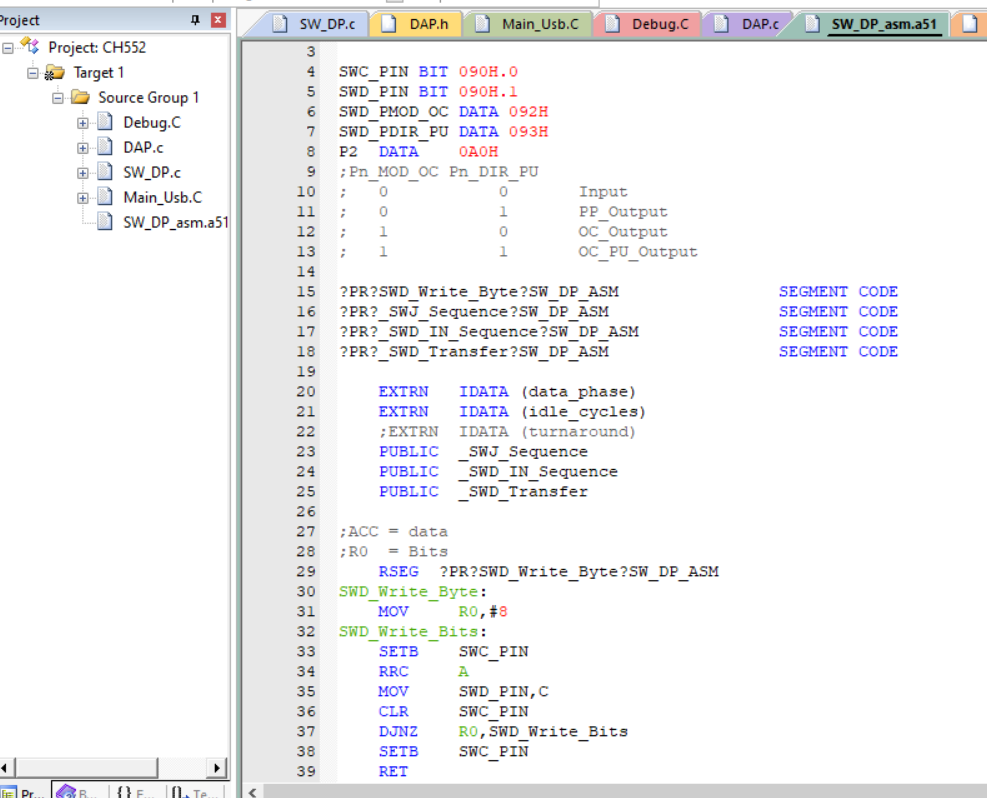

所以整个SWD时序创建了一个汇编文件,全部用汇编优化。网上写的8051如何C和汇编混合编程,也是写的乱七八糟的,互相抄来抄去,东拼西凑。我研究了好久才让这玩意稳定工作()可能还是因为太菜了吧

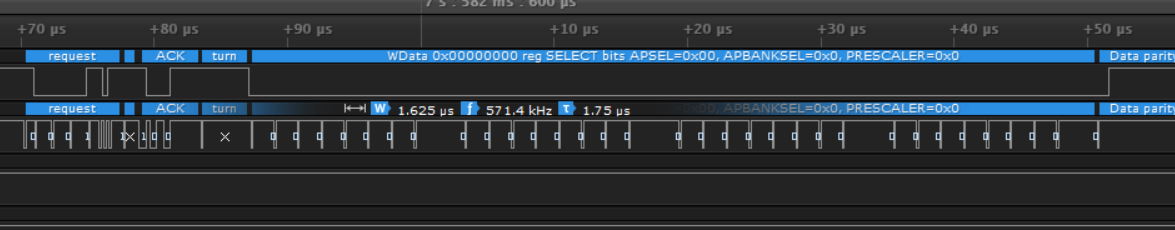

优化后 经过计算软IO模拟的话,12个处理器周期可以刷一个SWD时钟,3.3V下16M主频时钟1.66M,5V下24M主频时钟2M.

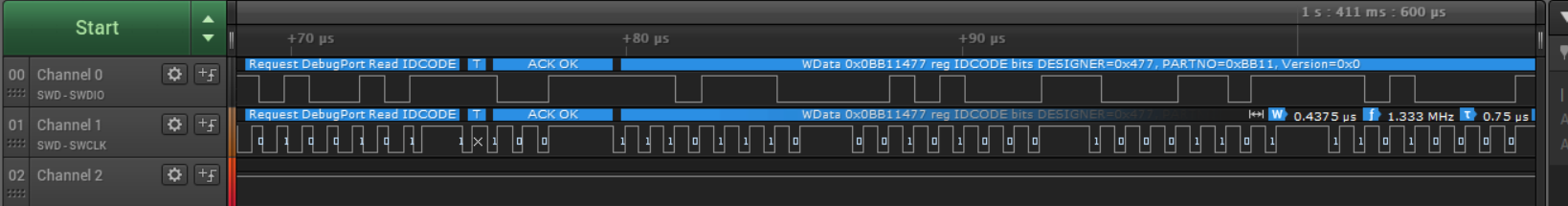

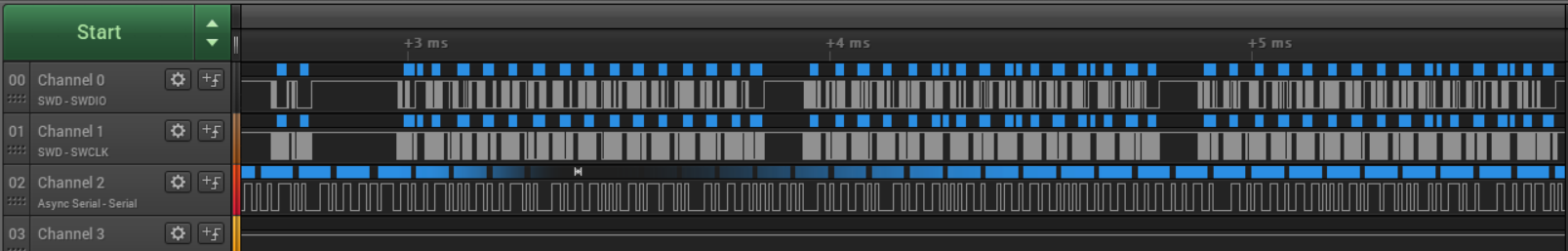

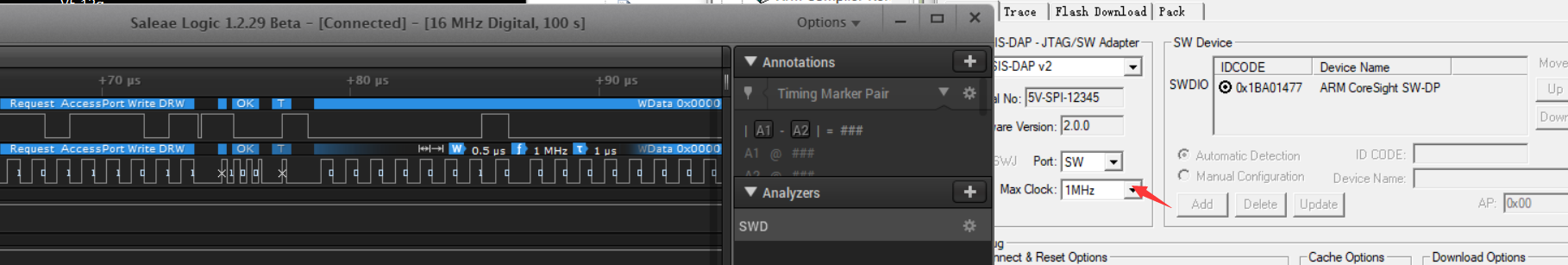

3.3V下IO模拟读取时序:

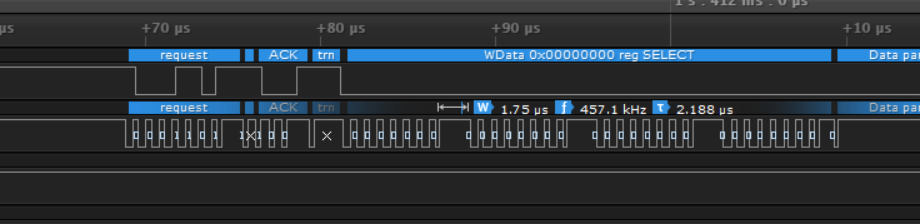

3.3V下IO模拟写时序:

16M主频下看起来SWD接口的占空比比较大,实际研究后,间隔时间五分之二是ch552在处理,五分之三是上位机比较慢,上位机驱动不改的话,下位机处理DAP指令还是有不少的优化空间(从xram倒腾数据过程非常多),不过考虑到我头发有限,目前就暂时不弄了。

串口优化:原版的串口驱动只能说叫有,但是基本没什么优化,串口发送是cpu在硬等,数据量一大就丢包。目前优化后使用256字节的xram做串口发送大fifo,(这样的好处是写入写出指针用8位刚好可以,处理fifo的满和空非常简单),串口接收由于usb带宽远高于串口,所以用64字节缓存足矣,收到串口数据只要有usb端点空闲就直接丢给usb(基本上1-2个字节就会发一次),总体没什么压力。

发送大于256字节的串口数据,usb会发四次包直到缓存塞满。usb发包的时候确实会打断串口中断,以后可以优化以下用中断嵌套,使得串口优先级更高。

但是fifo的处理涉及到可能会两个中断同时访问,还需要掉些头发。

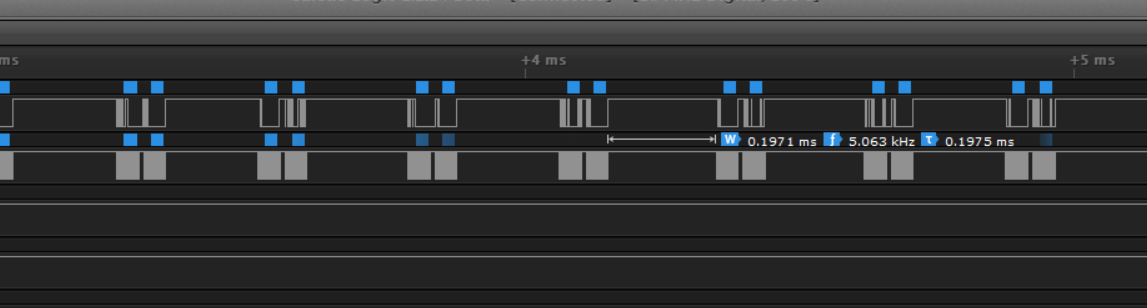

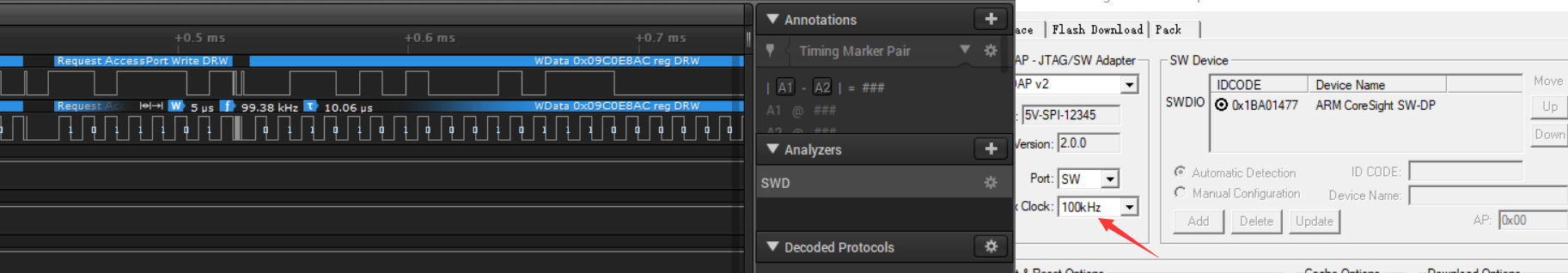

可以看到swd和串口一起工作的时候的状态,波特率干到500000

如果没有要复杂处理的usb中断,swd是不影响串口的

降低波特率到115200

硬件spi优化

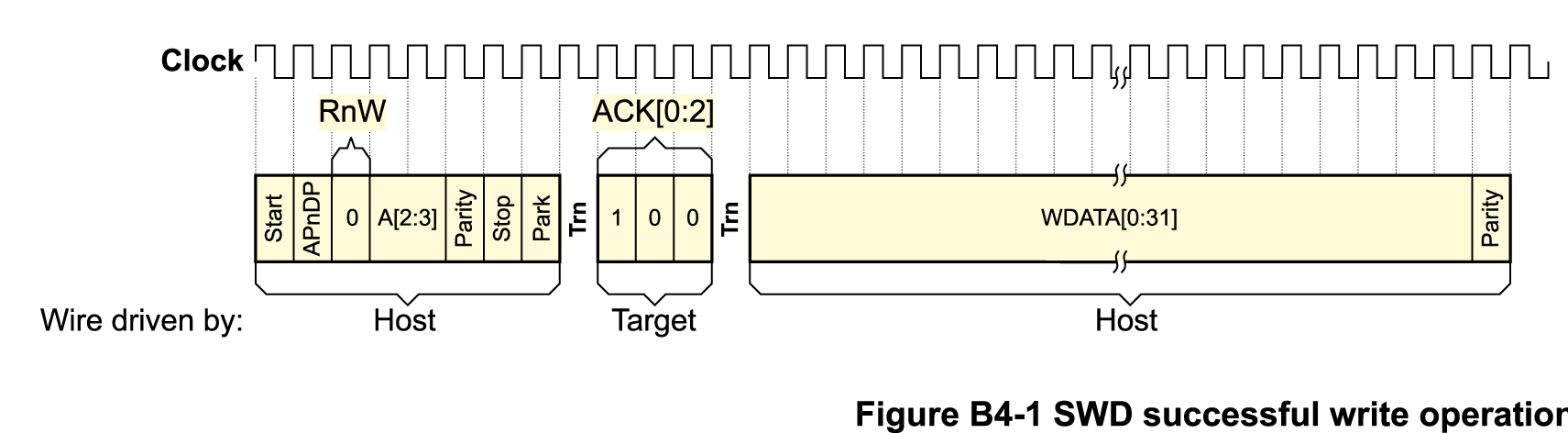

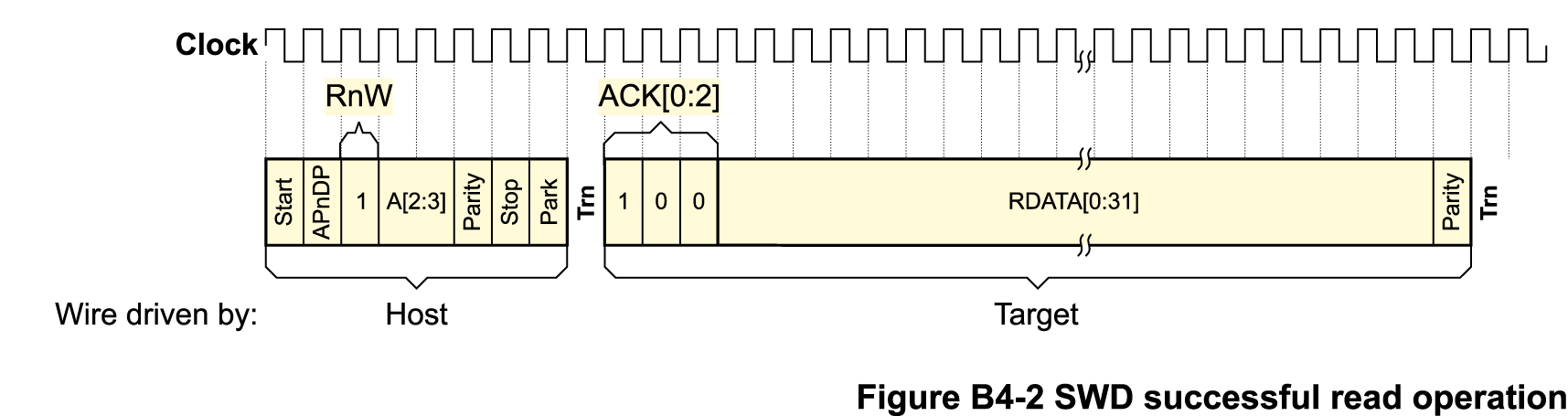

使用硬件spi刷写swd部分的固定字节。8-bit的command和32bit的数据可以直接切换到spi刷

优化占比可以达到(8+32)/(8+5+32+1)≈87%

既然用了spi 就可以调速度,以5V下跑24M主频为例,swd速度可调100KHz~12MHz,当然只调节spi刷的部分,软件部分改不了的。

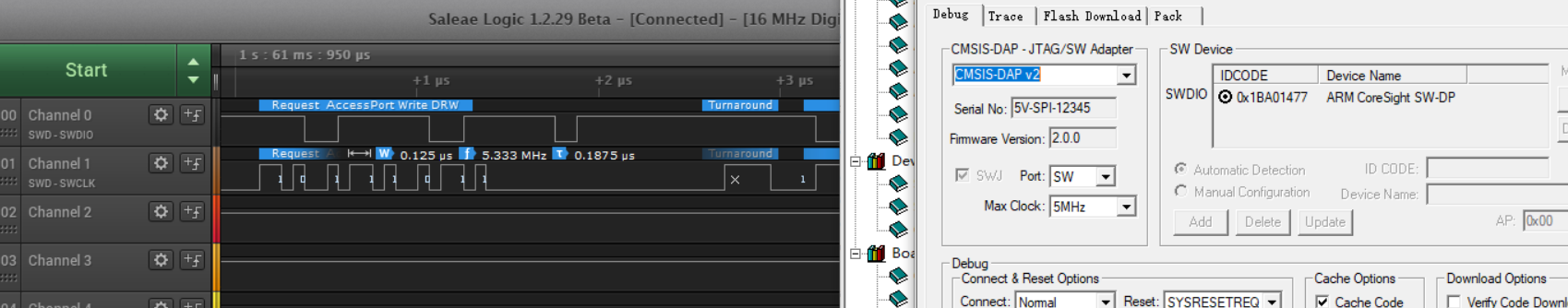

100K

1M

实际上是6M,12M逻辑分析仪抓不到了,但是也可以正常通讯。我还玩了下主频32M跑鸡血16M时钟,也没什么问题。

开源了PCB工程文件和电路图,代码开源了软件模拟io,因为spi硬件刷新的我测下来兼容性并不是太好,有点挑MCU,有时候会莫名其妙报错,所以我回头在研究研究,就先不拿出来献丑了。提供几个编译好的固件大家可以试试。

欢迎找bug,提交改进意见~

禁止用于商业用途

离线

#1 2022-02-07 18:24:16 分享评论

- mousebat04

- 会员

- 注册时间: 2020-04-26

- 已发帖子: 10

- 积分: 10

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬牛哇!简直造福人类。希望后面越来越好用。

另外问下,CH551是不是装不上这个固件?

离线

楼主 #2 2022-02-07 18:31:41 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬牛哇!简直造福人类。希望后面越来越好用。

另外问下,CH551是不是装不上这个固件?

我没做限制,大小才8K,没用串口1,应该是没问题

离线

#3 2022-02-07 19:20:38 分享评论

- pla155

- 会员

- 注册时间: 2020-01-05

- 已发帖子: 3

- 积分: 3

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬造福人类

学习一下,顶起。

离线

#4 2022-02-07 19:32:01 分享评论

- LingMao

- 会员

- 注册时间: 2020-03-21

- 已发帖子: 1

- 积分: 1

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬又一力作,前来资瓷下。

用CH552E的话,成本更低体积更小了。

离线

#5 2022-02-07 22:13:43 分享评论

- llinjupt

- 会员

- 注册时间: 2020-12-21

- 已发帖子: 93

- 积分: 163

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

支持,CH552用于做板载调试器成本低,DAPLink的JTAG调试FPGA?这个需要上位机支持吧,还是说自己在调试器中实现FPGA的一套JTAG协议?

离线

楼主 #6 2022-02-08 01:47:20 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

支持,CH552用于做板载调试器成本低,DAPLink的JTAG调试FPGA?这个需要上位机支持吧,还是说自己在调试器中实现FPGA的一套JTAG协议?

切换使用不就行了 usbblaster+daplink 用按键一键切换

离线

#7 2022-02-11 16:23:04 分享评论

- Chin

- 会员

- 注册时间: 2020-10-19

- 已发帖子: 61

- 积分: 39

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

我的天,都是大佬!一套成本得多少?

离线

楼主 #8 2022-02-12 22:09:55 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

我的天,都是大佬!一套成本得多少?

不超过10元 这个芯片很便宜的(特别是涨价前)

离线

楼主 #10 2022-02-14 18:29:54 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬太强了!手里有几片多年前立创撸的CH554T,看DS说554只是比552/1多了USB Host功能,是不是也可以搞这玩意儿

可以用 都一样的

离线

#11 2022-02-14 20:32:51 分享评论

- echo

- 会员

- 注册时间: 2020-04-16

- 已发帖子: 364

- 积分: 370.5

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

CH552性能上限太低了,而且现在也并不便宜

离线

#12 2022-02-17 14:58:50 分享评论

- taotieren

- 会员

- 注册时间: 2020-05-19

- 已发帖子: 117

- 积分: 152

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

有计划支持 rs-flash 吗?

离线

楼主 #13 2022-02-19 00:41:39 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

CH552性能上限太低了,而且现在也并不便宜

ch552e ssop10封装的还是很香的,在开发板上板载一个 得到串口+swd

离线

楼主 #14 2022-02-22 00:46:54 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

有计划支持 rs-flash 吗?

请问这是什么东西 没听说过

离线

#15 2022-02-22 15:29:33 分享评论

- 234336283

- 会员

- 注册时间: 2021-03-05

- 已发帖子: 8

- 积分: 8

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

简单实用,速度不知道实际下载体验什么样,特别是下载大程序或H750外部Qflash

离线

#16 2022-02-22 21:03:33 分享评论

- taotieren

- 会员

- 注册时间: 2020-05-19

- 已发帖子: 117

- 积分: 152

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

taotieren 说:有计划支持 rs-flash 吗?

请问这是什么东西 没听说过

https://github.com/probe-rs/cargo-flash

https://github.com/probe-rs/probe-rs

离线

#17 2022-02-22 22:18:28 分享评论

- echo

- 会员

- 注册时间: 2020-04-16

- 已发帖子: 364

- 积分: 370.5

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

echo 说:CH552性能上限太低了,而且现在也并不便宜

ch552e ssop10封装的还是很香的,在开发板上板载一个 得到串口+swd

我的FPGA开发板用CH552T做板载usb-blaster,可以给FPGA省下一个有源晶振。

离线

楼主 #18 2022-02-23 13:10:43 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

posystorage 说:taotieren 说:有计划支持 rs-flash 吗?

请问这是什么东西 没听说过

https://github.com/probe-rs/cargo-flash

https://github.com/probe-rs/probe-rs

我简单看了下,有点没太看懂,这个不就是个上位机软件吗?

离线

#20 2022-03-02 09:54:50 分享评论

- taotieren

- 会员

- 注册时间: 2020-05-19

- 已发帖子: 117

- 积分: 152

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

@posystorage

这个是开源出来的原理图和 PCB:https://github.com/probe-rs/hs-probe

probe-rs 是使用 rust 来调试 嵌入式硬件的固件,cargo-flash 是上位机,

离线

#21 2022-03-02 22:07:33 分享评论

- bigbat

- 会员

- 注册时间: 2022-01-30

- 已发帖子: 71

- 积分: 21

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

这个CH552是51内核的芯片吗

离线

#22 2022-03-07 09:44:40 分享评论

- kingsley_ch

- 会员

- 注册时间: 2020-08-15

- 已发帖子: 2

- 积分: 2

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

膜拜大佬一下,之前我也想折腾,但是总感觉51用的怪怪的.

顺便说下,wch最近出了不少144M主频内置USB高速PHY的mcu, 做这玩意,岂不是爽多了.

之前问了下最下他们网站那个高速的最低配的版本CH32V305,说要8块多,估计批量能便宜一些.

最近编辑记录 kingsley_ch (2022-03-07 09:53:31)

离线

#23 2022-03-07 11:33:23 分享评论

- gddddd

- 会员

- 注册时间: 2020-03-27

- 已发帖子: 30

- 积分: 30

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

mousebat04 说:大佬牛哇!简直造福人类。希望后面越来越好用。

另外问下,CH551是不是装不上这个固件?我没做限制,大小才8K,没用串口1,应该是没问题

CH551的XRAM只有512B,直接使用不行。试着改了一下XRAM的绝对地址和减小定义,编译后用不了,主要感觉程序中有有些和XRAM相关的使用地址是绑定的我没改到。

posystorage大佬方便出一版本内存精简版吗,适配一下CH551可好?

离线

#24 2022-03-07 16:13:37 分享评论

- echo

- 会员

- 注册时间: 2020-04-16

- 已发帖子: 364

- 积分: 370.5

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

@gddddd

512kB 的XRAM憋屈得很,而且CH551都停产了

离线

楼主 #25 2022-03-11 02:16:17 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

@gddddd

可能是因为有些是汇编代码 受影响吧?我回头有空看看

离线

#26 2022-03-15 00:07:31 分享评论

- wh201906

- 会员

- 注册时间: 2021-12-09

- 已发帖子: 50

- 积分: 50

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

请问,如果用SPI的话,是需要用2线半双工模式来作为SWDIO口吗?或者用其它方法来解决双向的问题?

离线

楼主 #27 2022-03-21 12:19:28 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

请问,如果用SPI的话,是需要用2线半双工模式来作为SWDIO口吗?或者用其它方法来解决双向的问题?

用的全双工SPI,将两个IO并起来用。ch552的半双工SPI有问题,速度提不到最快

离线

#28 2022-04-16 16:41:37 分享评论

- Meski

- 会员

- 注册时间: 2022-04-16

- 已发帖子: 2

- 积分: 2

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬,我试着复刻了一下pcb,发现了一个矛盾的地方,readme中提示P1.6和P1.7需要并联,但是在原理图中P1.6又和P1.5通过一个0欧电阻相连,甚是疑惑,是我什么地方存在理解错误吗,希望能够得到解答,感谢。

离线

楼主 #29 2022-04-17 01:25:14 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬,我试着复刻了一下pcb,发现了一个矛盾的地方,readme中提示P1.6和P1.7需要并联,但是在原理图中P1.6又和P1.5通过一个0欧电阻相连,甚是疑惑,是我什么地方存在理解错误吗,希望能够得到解答,感谢。

readme 写错了 按原理图为准

离线

#30 2022-04-25 17:44:27 分享评论

- JZH1996

- 会员

- 注册时间: 2019-09-25

- 已发帖子: 9

- 积分: 15

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

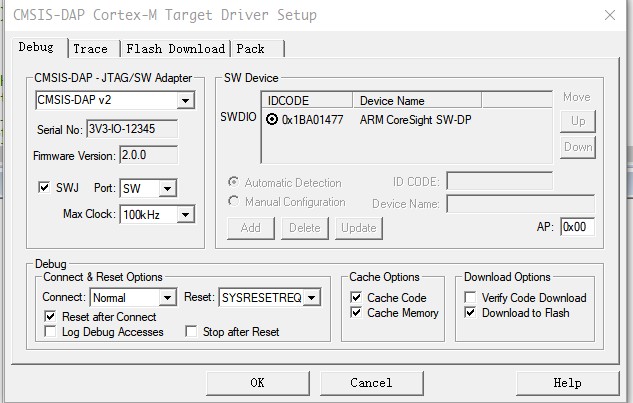

大佬,我烧了你编译出来的固件,设备管理器里面能看到一个串口和一个CMSIS-DAP V2设备,但是Keil里面检测不到,想问一下是需要装专门的驱动还是对Keil版本有要求啊,我的Keil是5.23版本

离线

楼主 #31 2022-04-26 00:14:45 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬,我烧了你编译出来的固件,设备管理器里面能看到一个串口和一个CMSIS-DAP V2设备,但是Keil里面检测不到,想问一下是需要装专门的驱动还是对Keil版本有要求啊,我的Keil是5.23版本

keil版本太老了 识别不到v2版本的daplink 升级下keil

或者替换这个dll文件 在Keil_mdk_c51\ARM\BIN下

CMSIS_DAP.zip

离线

#32 2022-05-02 13:54:50 分享评论

- 冷月烟

- 会员

- 注册时间: 2020-07-06

- 已发帖子: 40

- 积分: 47.5

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬,这个编译的固件试了一下,串口不稳定啊,3.3V供电,115200波特率,串口接受误码很厉害

离线

#33 2022-05-02 21:57:29 分享评论

- Meski

- 会员

- 注册时间: 2022-04-16

- 已发帖子: 2

- 积分: 2

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬,我做完了,但是碰到一些小问题,我是采用了5VIO的方案,然后用SN74LVC1T45DCKR转为3.3VIO,电脑和Keil能够识别出Daplink设备,但是显示SWD/JTAG Communication Failure,也找不到设备ID,然后我怀疑电平转换可能不太行,确认我的SWD接口支持5V电平输入后拆掉了电平转换,直接飞线到CLK和DIO的排针,ID读出来了,但是却显示Cannot Load Flash Programming Algorithm,尝试换电脑或者降低下载速率还是未能解决,还麻烦您如果有时间能够分析一下可能的原因,感激不尽。

离线

#34 2022-05-03 00:11:06 分享评论

- health

- 会员

- 注册时间: 2021-02-23

- 已发帖子: 31

- 积分: 50.5

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬,这个编译的固件试了一下,串口不稳定啊,3.3V供电,115200波特率,串口接受误码很厉害

3.3V供电产生不了115200bps波特率啊。

离线

楼主 #35 2022-05-03 03:55:36 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬,这个编译的固件试了一下,串口不稳定啊,3.3V供电,115200波特率,串口接受误码很厉害

3.3V下主频只有16MHz,跑115200波特率偏差非常大的

Fsys / 16 / 波特率

波特率应该111111

离线

楼主 #36 2022-05-03 03:56:27 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

@Meski

Cannot Load Flash Programming Algorithm这个是你keil设置问题,和daplink没关系 这个是没有设置下载算法

离线

#37 2022-05-23 16:45:57 分享评论

- jk

- 会员

- 注册时间: 2022-05-23

- 已发帖子: 2

- 积分: 2

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬,我也跟着复刻了一下,5V供电,串口和下载都可以,就是debug调试不行,是我设置问题,还是这个固件没有完善debug功能呢?

离线

#38 2022-05-23 18:21:39 分享评论

- jk

- 会员

- 注册时间: 2022-05-23

- 已发帖子: 2

- 积分: 2

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬,又发现一个新问题,下载小文件正常,下载大文件(比如14K)的程序,会提示校验出错

离线

#39 2022-05-27 10:15:18 分享评论

- Vans000

- 会员

- 注册时间: 2022-01-04

- 已发帖子: 10

- 积分: 5

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

现在使用下来烧录应该没有问题,但是串口感觉不是很稳定,丢数据比较严重

离线

#40 2022-06-16 17:37:05 分享评论

- nick_zm

- 会员

- 注册时间: 2022-06-16

- 已发帖子: 2

- 积分: 2

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

感谢共享源码,众里寻他千百度,带来全不费工夫

离线

#41 2022-06-26 16:12:54 分享评论

- jdsuchen

- 会员

- 注册时间: 2022-06-19

- 已发帖子: 2

- 积分: 2

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

感谢分享,做了一个,速度很快,用UnionPRG读取STM32F030C8T6耗时1秒,WCH-LINK耗时9秒

离线

#43 2022-06-28 16:22:30 分享评论

- jdsuchen

- 会员

- 注册时间: 2022-06-19

- 已发帖子: 2

- 积分: 2

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

试了下STM32F407VET6有点问题,偶尔连上一次,也调试不了,WCH-LINK也是同样的问题

Info : Listening on port 6666 for tcl connections

Info : Listening on port 4444 for telnet connections

Info : Using CMSIS-DAPv2 interface with VID:PID=0x0d28:0x0204, serial=5V0-IO-12345

Info : CMSIS-DAP: SWD Supported

Info : CMSIS-DAP: FW Version = 2.0.0

Info : CMSIS-DAP: Interface Initialised (SWD)

Info : SWCLK/TCK = 1 SWDIO/TMS = 1 TDI = 0 TDO = 0 nTRST = 0 nRESET = 1

Info : CMSIS-DAP: Interface ready

Info : clock speed 10000 kHz

Error: Error connecting DP: cannot read IDR

离线

#44 2022-06-28 21:23:19 分享评论

- 上海航芯市场

- 会员

- 注册时间: 2022-06-23

- 已发帖子: 44

- 积分: 139

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

利用航芯带HS USB的ACH512制作的DAP-Link已经上架whycan淘宝店

https://item.taobao.com/item.htm?spm=a1z10.3-c-s.w4002-24455499472.11.77c6526cEQ21jK&id=677891191502

原厂会配合whycan长期平价(30RMB以内)供应DAP-Link

串口921600波特率,下载480KB固件到ACM32FP4,速度对比:

其他70+RMB的daplink: 16s

ACH512-dap: 14.5s

SWD下载63KB固件到ACM32FP4,速度对比:

其他70+RMB的daplink-10M: 3.6s

ACH512-dap-10M: 5s

最近编辑记录 上海航芯市场 (2022-06-28 21:25:16)

离线

#46 2022-07-18 22:59:30 分享评论

- cuit4017

- 会员

- 注册时间: 2022-07-18

- 已发帖子: 1

- 积分: 1

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

感谢分享,做了一个,速度很快,用UnionPRG读取STM32F030C8T6耗时1秒,WCH-LINK耗时9秒

https://whycan.com/files/members/9626/微信图片_20220626161156.jpg

你这个开源么,想打个typec口的。

离线

#47 2022-07-20 17:23:15 分享评论

- Vans000

- 会员

- 注册时间: 2022-01-04

- 已发帖子: 10

- 积分: 5

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬 很强啊 我也在用ljbfly的代码 发现里面用的是串口1 打板回来发现串口1在3.3V供电情况误码太大了

离线

#48 2022-08-02 20:08:37 分享评论

- xiao_fang

- 会员

- 注册时间: 2022-08-02

- 已发帖子: 4

- 积分: 5

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

感谢楼主分享的源码,我这几天正在学习usb,计划把它移植到CH583上,下一步使用蓝牙做一个无线的DAP。

离线

楼主 #49 2022-08-11 00:51:05 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

感谢楼主分享的源码,我这几天正在学习usb,计划把它移植到CH583上,下一步使用蓝牙做一个无线的DAP。

支持你,SWD速度优化建议你重写官方原装的SWD时序代码

离线

#50 2022-08-28 11:13:06 分享评论

- EListen

- 会员

- 注册时间: 2021-08-25

- 已发帖子: 3

- 积分: 33

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

发现个问题楼主代码中给端点1端点2端点3分配了64*4 即256字节的buffer

UINT8X Ep0Buffer[THIS_ENDP0_SIZE] _at_ 0x0000; //端点0 OUT&IN缓冲区,必须是偶地址

UINT8X Ep1BufferO[THIS_ENDP0_SIZE] _at_ 0x0040; //端点1 OUT双缓冲区,必须是偶地址 Not Change!!!!!!

UINT8X Ep1BufferI[THIS_ENDP0_SIZE] _at_ 0x0080; //端点1 IN双缓冲区,必须是偶地址 Not Change!!!!!!

//100,140,180,1C0

UINT8X Ep2BufferO[4 * THIS_ENDP0_SIZE] _at_ 0x00C0; //端点2 OUT双缓冲区,必须是偶地址

//200,240,280,2C0

UINT8X Ep3BufferI[4 * THIS_ENDP0_SIZE] _at_ 0x01C0; //端点3 IN双缓冲区,必须是偶地址但到了实际的配置 全部都是单缓的配置

UEP2_DMA = Ep2BufferO; //端点2数据传输地址

UEP3_DMA = Ep3BufferI; //端点2数据传输地址

UEP2_3_MOD |= (bUEP3_TX_EN | bUEP2_RX_EN); //端点2发送接收使能

UEP2_3_MOD &= ~(bUEP2_BUF_MOD | bUEP3_BUF_MOD); //端点2收发各64字节缓冲区

UEP2_CTRL = bUEP_AUTO_TOG | UEP_T_RES_NAK | UEP_R_RES_ACK; //端点2自动翻转同步标志位,IN事务返回NAK,OUT返回ACK

UEP3_CTRL = bUEP_AUTO_TOG | UEP_T_RES_NAK | UEP_R_RES_NAK; //端点3自动翻转同步标志位,IN事务返回NAK,OUT返回NACK如果没有对手册对错的话 加上端点1的配置 按照现在实际的全单缓配置可以省下来512字节的外部ram

另外好像是配置的了端点4 但是实际的端点初始化的时候却禁止了 这块我还在检查

离线

楼主 #51 2022-08-28 17:22:33 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

@EListen

端点2和3应该是串口缓存buff,使用256字节空间做fifo的,你看下汇编部分就会发现

离线

#52 2022-08-28 18:08:18 分享评论

- EListen

- 会员

- 注册时间: 2021-08-25

- 已发帖子: 3

- 积分: 33

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

@EListen

端点2和3应该是串口缓存buff,使用256字节空间做fifo的,你看下汇编部分就会发现

我如果没有理解错 你应该是单独开辟了缓冲区 而且指定了段地址

混用usb buff 和 串口buff 还是比较危险的吧

UINT8X Ep0Buffer[THIS_ENDP0_SIZE] _at_ 0x0000; //端点0 OUT&IN缓冲区,必须是偶地址

UINT8X Ep1BufferO[THIS_ENDP0_SIZE] _at_ 0x0040; //端点1 OUT双缓冲区,必须是偶地址 Not Change!!!!!!

UINT8X Ep1BufferI[THIS_ENDP0_SIZE] _at_ 0x0080; //端点1 IN双缓冲区,必须是偶地址 Not Change!!!!!!

//100,140,180,1C0

UINT8X Ep2BufferO[4 * THIS_ENDP0_SIZE] _at_ 0x0100; //端点2 OUT双缓冲区,必须是偶地址

//200,240,280,2C0

UINT8X Ep3BufferI[4 * THIS_ENDP0_SIZE] _at_ 0x0200; //端点3 IN双缓冲区,必须是偶地址

UINT8I UART_RX_Data_Buff[ENDP1_SIZE];

UINT8X UART_TX_Data_Buff[256]_at_ 0x0300;我自己是打算重写ch552的daplink的 想加入rtx51tiny的系统 看的比较仔细吧 你看一下应该是可以砍掉不少给usb的缓冲区

离线

楼主 #53 2022-08-29 11:40:33 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

@EListen

时间长了 有点忘了。我看了下 是这样的

EP1缓存是串口用的缓冲,收发各使用了64字节

Main_Usb.C

UINT8X Ep1BufferO[THIS_ENDP0_SIZE] _at_ 0x0040; //端点1 OUT双缓冲区,必须是偶地址 Not Change!!!!!!

UINT8X Ep1BufferI[THIS_ENDP0_SIZE] _at_ 0x0080; //端点1 IN双缓冲区,必须是偶地址 Not Change!!!!!!串口文件下有两个缓存,在内部的是RX缓存,64字节,在外部的是TX缓存,256字节

Uart.c

UINT8I UART_RX_Data_Buff[ENDP1_SIZE];

UINT8X UART_TX_Data_Buff[256]_at_ 0x0300;void UART_Get_USB_Data(UINT8 Nums)负责把Ep1BufferO搬到发送fifo UART_TX_Data_Buff里面

void memcpy_TXBUFF_USBBUFF(UINT8 data_len)负责把UART_RX_Data_Buff搬到Ep1BufferI

串口这部分的buff是没混用的

EP2是PC下发DAP数据给CH552

这里的缓存是这样用的,写满了就直接+64

Main_Usb.C

case UIS_TOKEN_OUT | 2: //endpoint 2# 端点批量下传 DAP-CMD

if (U_TOG_OK) // 不同步的数据包将丢弃

{

Ep2Oi += 64;

UEP2_DMA_L = Ep2Oi;

}

break;EP3也是同理,好了直接换缓存,这样不用一直等USB

Main_Usb.C

if (Endp3Busy != 1 && Ep3Ii != Ep3Io)

{

Endp3Busy = 1;

UEP3_T_LEN = Ep3Is[0];//Ep3Io>>6];

UEP3_DMA_L = Ep3Io;

UEP3_CTRL = UEP3_CTRL & ~MASK_UEP_T_RES | UEP_T_RES_ACK; //有数据时上传数据并应答ACK

Ep3Io += 64;

}这里有FIFO缓存的使用

DAP.c

void DAP_Thread(void)

{

UINT8I num;

if (Ep2Oi != Ep2Oo)

{

PUINT8 req = &Ep2BufferO[Ep2Oo];

PUINT8 res = &Ep3BufferI[Ep3Ii];

Ep2Oo += 64;

........

Ep3Is[0]/*(Ep3Ii>>6)]*/ = num + 1;

Ep3Ii += 64;

}

}离线

#54 2022-08-30 18:36:43 分享评论

- abgelehnt

- 会员

- 注册时间: 2022-05-01

- 已发帖子: 10

- 积分: 110

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

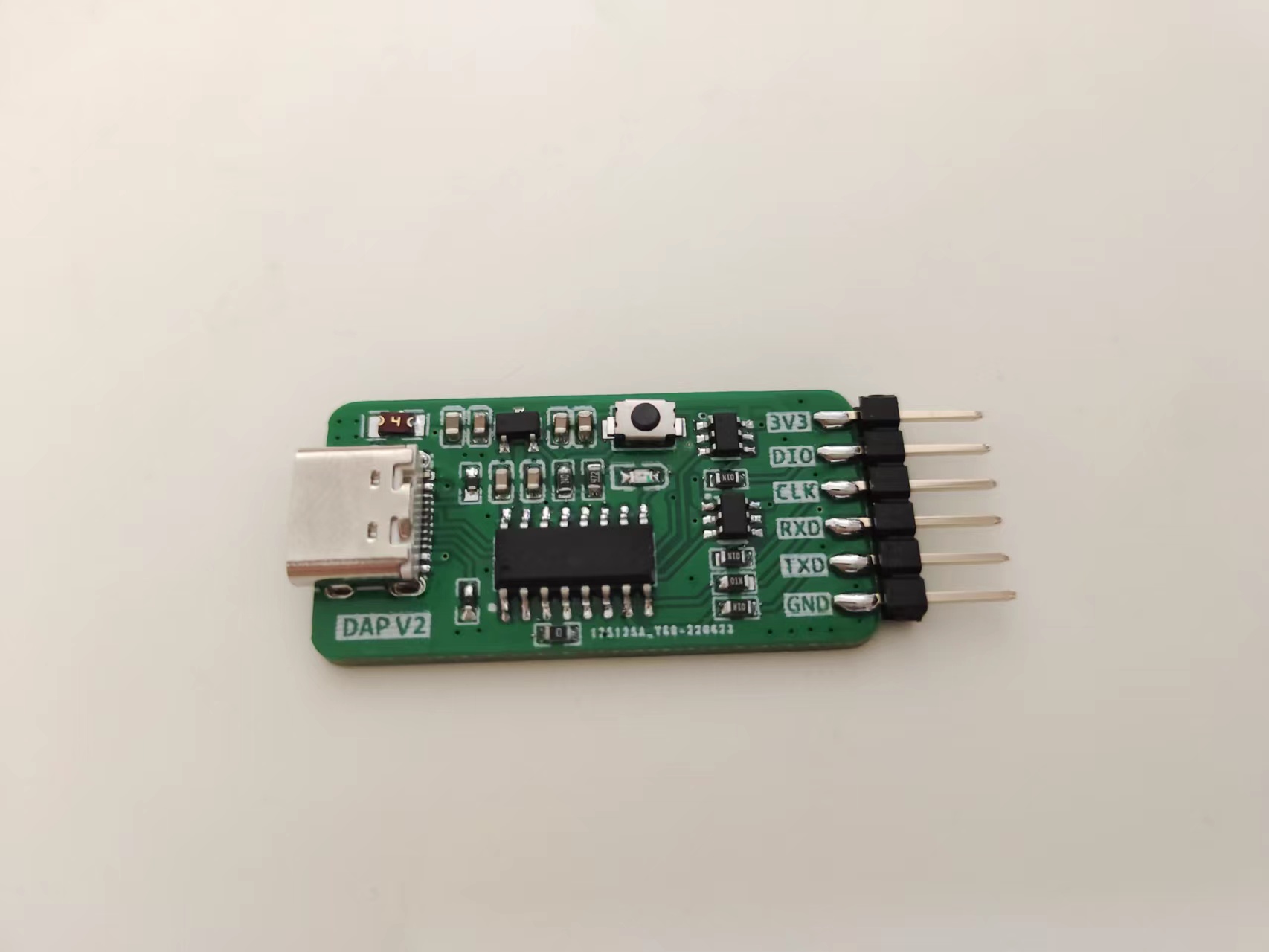

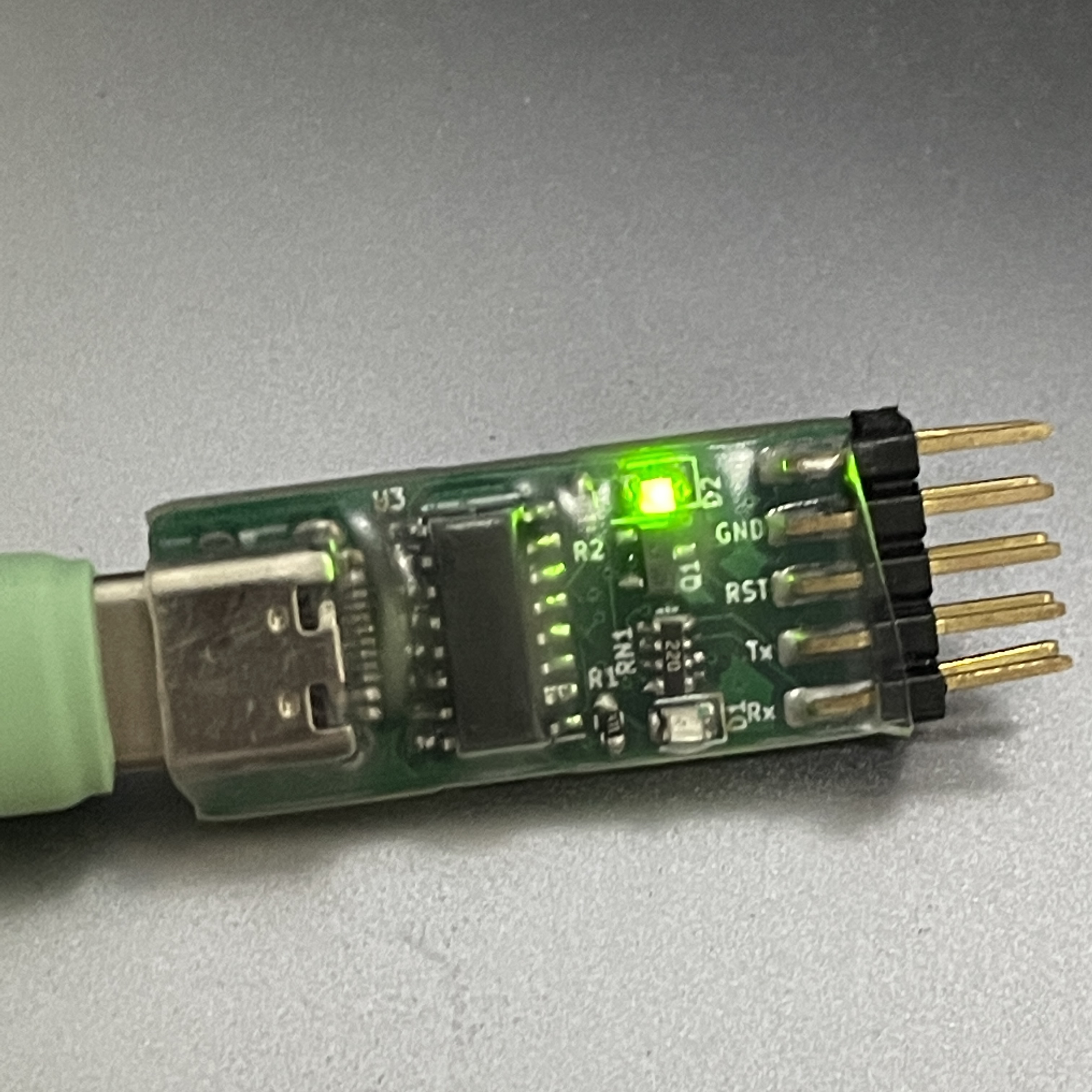

感谢分享,做了一个typec版本的 ![]()

离线

#55 2022-08-30 18:50:33 分享评论

- EListen

- 会员

- 注册时间: 2021-08-25

- 已发帖子: 3

- 积分: 33

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

@posystorage

抱歉 看到dap那边调用是理解了这个buffer的设置 不过这些buffer设置有些混乱 另外dap真的需要收发各256字节的buffer吗 我目前打算用usb外设支持的双buffer模式尝试一下 感觉应该是够用的

离线

#56 2022-09-02 19:17:24 分享评论

- abgelehnt

- 会员

- 注册时间: 2022-05-01

- 已发帖子: 10

- 积分: 110

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

我感觉是不需要这么大的buffer的,楼主这么写应该是为了汇编好写 直接DPH固定了

不过这XRAM不用白不用对吧hhh

离线

楼主 #57 2022-09-04 04:11:42 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

我感觉是不需要这么大的buffer的,楼主这么写应该是为了汇编好写 直接DPH固定了

不过这XRAM不用白不用对吧hhh

哈哈 被你发现了 就是汇编偷懒 你说得对,而且这部分代码还是之前在别的工程上用的 我直接搬过来偷懒了

离线

#58 2022-11-17 22:27:41 分享评论

- 815794369

- 会员

- 注册时间: 2020-02-16

- 已发帖子: 10

- 积分: 23.5

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

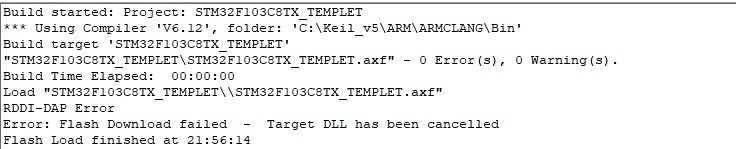

实际测试了下 在3.3V环境下不是很稳定,10次下载9次失败,失败之后报错如下,需要将ch552和stm32都断开再连接才能下载。请大佬帮忙看下

离线

#59 2022-11-17 22:57:26 分享评论

- 815794369

- 会员

- 注册时间: 2020-02-16

- 已发帖子: 10

- 积分: 23.5

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

实际测试发现将目标板子的3.3V和ch552的电源连接就好了。具体原因很蒙蔽

离线

楼主 #60 2022-11-18 01:58:22 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

@815794369

这么点信息不足以分析出问题在哪里,这个要抓包swd+usb才容易看出来。话说你测试了5V情况下能稳定工作吗?

离线

#61 2022-11-22 19:22:27 分享评论

- 815794369

- 会员

- 注册时间: 2020-02-16

- 已发帖子: 10

- 积分: 23.5

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

没有测试5V的 我的板子上没画1T45

离线

#62 2022-11-22 19:25:30 分享评论

- 815794369

- 会员

- 注册时间: 2020-02-16

- 已发帖子: 10

- 积分: 23.5

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

看到这个帖子下面(https://whycan.com/t_6042.html),有大佬说“

另外nerdralph回报说CH552用杜邦线连接HK32F是不可以用的。原因是振铃太大,时钟错误。CH552不能控制压摆率,所以SWD中间应该串一个50-150Ohm电阻做匹配,来消除振铃。

”

我在swd上串联了一个100R的电阻,实际测试发现下载故障率小了很多,但是不能Debug。会报"Cannot access target Shutting down debug session"

离线

楼主 #63 2022-11-22 20:22:58 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

@815794369

振铃我觉得主要是杜邦线不好,以及接地屏蔽不完善造成的,建议不要撕开杜邦线

离线

#64 2023-06-02 16:57:38 分享评论

- foticing

- 会员

- 注册时间: 2023-06-02

- 已发帖子: 1

- 积分: 1

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

CH552下载不了STM32的是什么情况

离线

楼主 #65 2023-06-02 17:09:30 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

CH552下载不了STM32的是什么情况

我这边测试是可以的 你要不看看低速下行不行

离线

#66 2023-06-25 23:17:15 分享评论

- andyxu

- 会员

- 注册时间: 2023-06-25

- 已发帖子: 1

- 积分: 1

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

@posystorage 楼主楼主 在单独接下载器没有接32的时候 在Keil中检测下载器状态的时候 debugger settings里的 有出现RDDI-DAP Error的情况不

离线

楼主 #67 2023-07-03 12:28:39 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

@posystorage 楼主楼主 在单独接下载器没有接32的时候 在Keil中检测下载器状态的时候 debugger settings里的 有出现RDDI-DAP Error的情况不

发个截图看看。另外 接stm32的时候能用吗?

离线

#70 2024-01-03 23:02:38 分享评论

- flex-A

- 会员

- 注册时间: 2019-08-27

- 已发帖子: 51

- 积分: 146.5

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬威武,ch551/552的资源够用的话,是不是也能拿cy7c68013/cbm9002这种芯片弄一个下载器?

离线

楼主 #71 2024-01-04 02:13:26 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬威武,ch551/552的资源够用的话,是不是也能拿cy7c68013/cbm9002这种芯片弄一个下载器?

我估计可以?

离线

#72 2024-01-04 08:52:17 分享评论

- mcujishu

- 会员

- 注册时间: 2024-01-03

- 已发帖子: 4

- 积分: 4

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

CH552哪里有源码例子

离线

#73 2024-01-18 11:46:48 分享评论

- Mox_Q

- 会员

- 注册时间: 2023-09-05

- 已发帖子: 1

- 积分: 1

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

大佬能添加一下debug的功能嘛:D

离线

#74 2024-01-19 11:05:05 分享评论

- zydl123

- 会员

- 注册时间: 2022-10-22

- 已发帖子: 3

- 积分: 3

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

ch552我也做过几种,DAPLink的JTAG调试FPGA?不

离线

楼主 #75 2024-05-19 00:24:34 分享评论

- posystorage

- 会员

- 注册时间: 2018-05-06

- 已发帖子: 173

- 积分: 539

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

有大佬进行了更新,解决了一些bug,可以看这里

https://oshwhub.com/jdsuchen/ch552-cmsis-dap

离线

#77 2025-01-17 22:03:18 分享评论

- zeroL

- 会员

- 注册时间: 2025-01-17

- 已发帖子: 2

- 积分: 2

Re: 开源CH551/2实现的汇编优化高速DAP-Link (CMSIS-DAP v2)

老哥我使用STM32F103的daplink开源代码,想去掉bl程序,直接使用if程序,在if程序中注释掉了地址赋值,发现程序会死在GPIO初始化中的定时器,现在不知道怎么办,我想学习这个开源的daplink源码并移植成freerrtos,现在卡在这一步麻烦老哥指点一下我。

离线

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发