- 首页

- » 全志 SOC

- » 这个电路好魔幻, 是如何工作的?

楼主 # 2024-01-21 03:12:35 分享评论

- musich

- 会员

- 注册时间: 2018-04-17

- 已发帖子: 259

- 积分: 291

这个电路好魔幻, 是如何工作的?

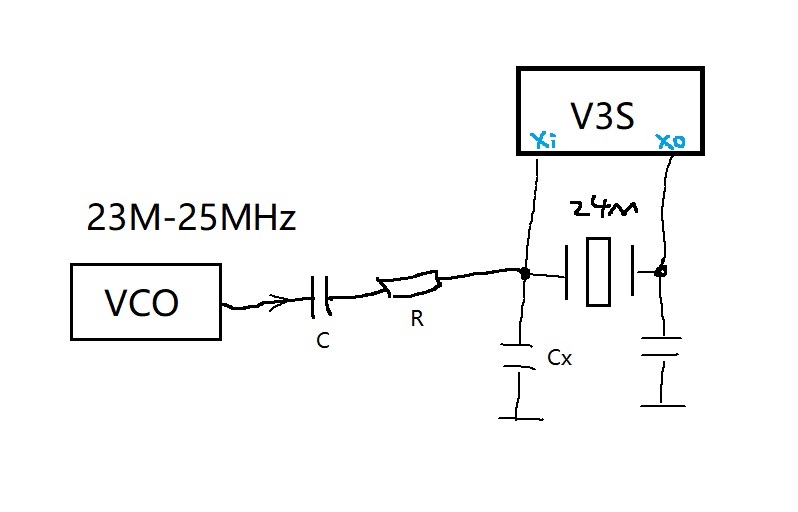

这个V3s时钟电路, 看了好久也没明白, 原电路是用在一个音频测试设备上的.

24M晶体, 再外接一个时钟源, 对原24M能有什么影响呢?

离线

楼主 #1 2024-01-21 03:17:23 分享评论

- musich

- 会员

- 注册时间: 2018-04-17

- 已发帖子: 259

- 积分: 291

Re: 这个电路好魔幻, 是如何工作的?

24M晶体, 再外接一个时钟源, 这么做,

难道可以混频? 还是可以微调频率? 这是可以自动切换到外接时钟源?

改变24M时钟源,内部DDR刷新就变了,系统不会奔溃了吗?

离线

楼主 #5 2024-01-22 03:38:50 分享评论

- musich

- 会员

- 注册时间: 2018-04-17

- 已发帖子: 259

- 积分: 291

Re: 这个电路好魔幻, 是如何工作的?

david 说:

实物两款时钟都接了么 还是就电路图上画了两个

元件都贴全了, 不是二选一.

离线

楼主 #7 2024-01-23 12:01:53 分享评论

- musich

- 会员

- 注册时间: 2018-04-17

- 已发帖子: 259

- 积分: 291

Re: 这个电路好魔幻, 是如何工作的?

david 说:

那就要看谁的信号强了 设计的时候二选一 贴片厂全贴的情况也是有的

有道理, 这是一个类似SDR接收机里面的电路,

搜了一下得到结果是, 可以防谐波干扰,提高接收机灵敏度.

离线

- 首页

- » 全志 SOC

- » 这个电路好魔幻, 是如何工作的?

感谢为中文互联网持续输出优质内容的各位老铁们。

QQ: 516333132, 微信(wechat): whycan_cn (哇酷网/挖坑网/填坑网) service@whycan.cn

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发