楼主 #1 2019-10-04 16:45:35 分享评论

- augyy

- 会员

- 注册时间: 2019-01-29

- 已发帖子: 46

- 积分: 46

全志A33 UART baudrate 921600 問題!!

現在我把A33 UART2 波特率設定為921600, 但是出來波特率是761904.

同時我找到sunxi-uart.c file 裡要改apb2div. 請問那裡設定?

离线

楼主 #3 2019-10-04 17:16:26 分享评论

- augyy

- 会员

- 注册时间: 2019-01-29

- 已发帖子: 46

- 积分: 46

Re: 全志A33 UART baudrate 921600 問題!!

用logic analyzer 望 output data. 所以知道波特率大約761904.

同時試過把設波特率定為 1500000, 是無問題!!

离线

楼主 #6 2019-10-09 16:05:29 分享评论

- augyy

- 会员

- 注册时间: 2019-01-29

- 已发帖子: 46

- 积分: 46

Re: 全志A33 UART baudrate 921600 問題!!

会不会是逻辑分析仪的最大频率不够?

逻辑分析仪频率應該足夠,因為可看到1500000频率

离线

楼主 #8 2019-10-10 15:43:26 分享评论

- augyy

- 会员

- 注册时间: 2019-01-29

- 已发帖子: 46

- 积分: 46

Re: 全志A33 UART baudrate 921600 問題!!

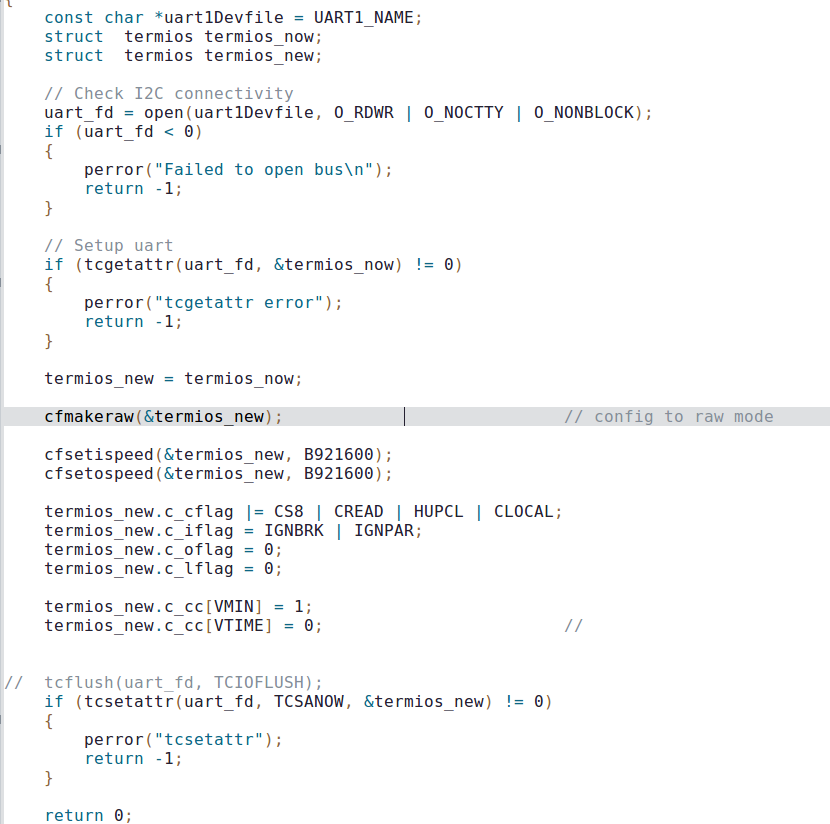

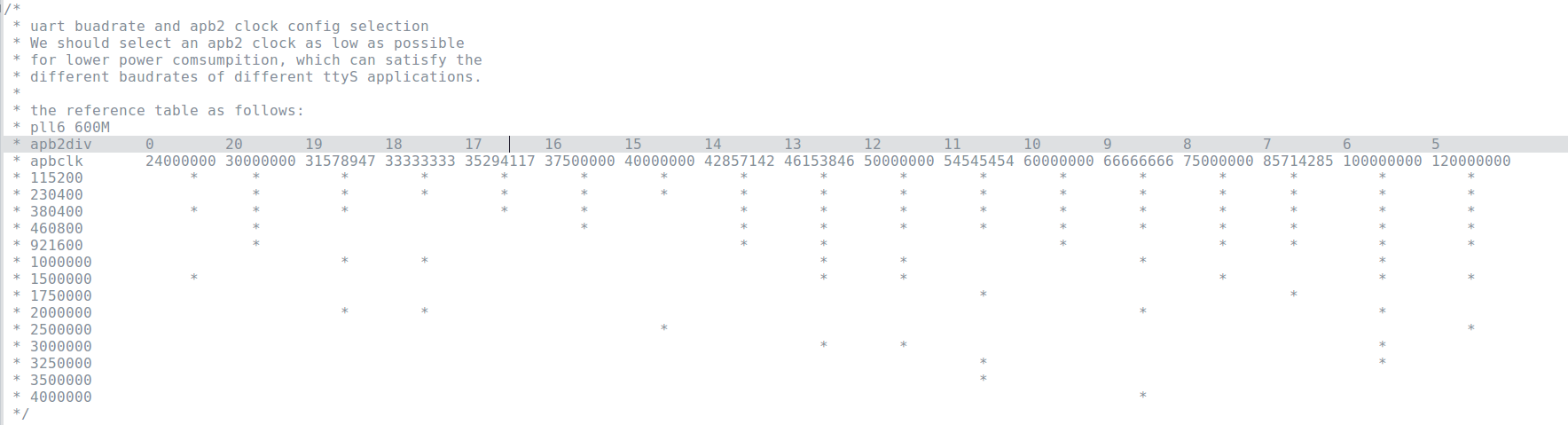

apb2时钟默认是OSC24M,时钟源应该使用PLL6,修改uboot时钟初始化的代码就行

24000000/16/921600=1.6276,向上取整,实际波特率24000000/16/2=750000,应该是这样augyy 说:阿黄 说:会不会是逻辑分析仪的最大频率不够?

逻辑分析仪频率應該足夠,因為可看到1500000频率

https://whycan.cn/files/members/1429/CONFIG_SYS_NS16550_CLK.png

是否直接把CONFIG_SYS_NS16550_CLK 為 (30000000) ?

离线

楼主 #10 2019-10-10 17:01:32 分享评论

- augyy

- 会员

- 注册时间: 2019-01-29

- 已发帖子: 46

- 积分: 46

Re: 全志A33 UART baudrate 921600 問題!!

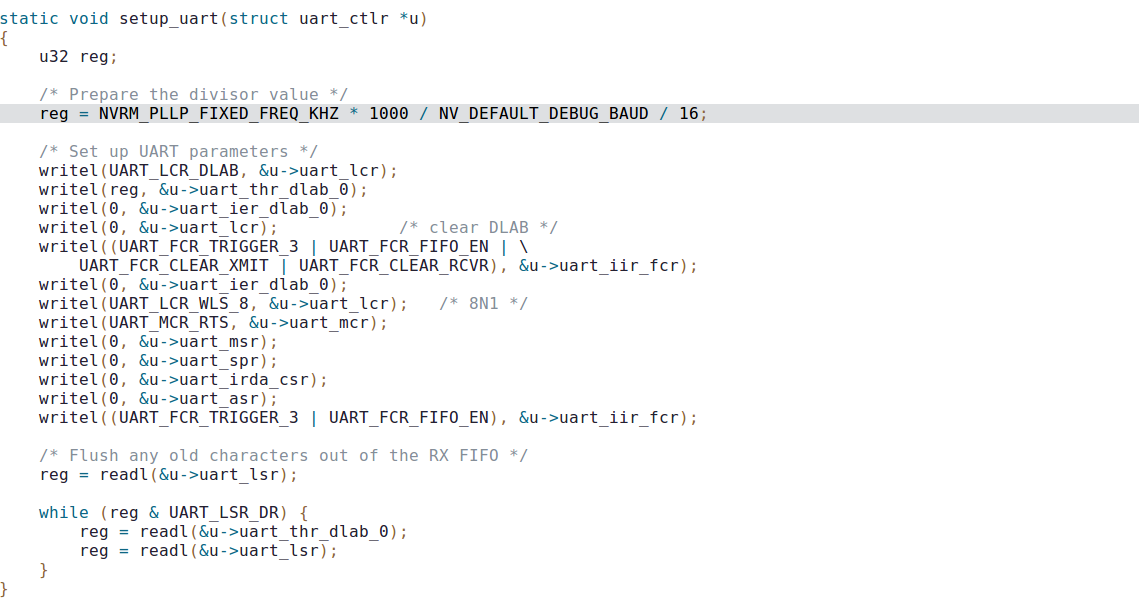

只找到board.c 同 serial_tegra2.c 文件

是否改setup_uart(..) function

reg = NVRM_PLLP_FIXED_FREQ_KHZ * 1000 / NV_DEFAULT_DEBUF_BAUD / 16 的

16 為 20 or 其他?

最近编辑记录 augyy (2019-10-10 17:12:43)

离线

楼主 #12 2019-10-17 17:18:05 分享评论

- augyy

- 会员

- 注册时间: 2019-01-29

- 已发帖子: 46

- 积分: 46

Re: 全志A33 UART baudrate 921600 問題!!

我用u-boot-2011.09 版本的. 同sun8iw5p1.h

最近编辑记录 augyy (2019-10-17 17:18:49)

离线

楼主 #14 2019-10-25 11:30:33 分享评论

- augyy

- 会员

- 注册时间: 2019-01-29

- 已发帖子: 46

- 积分: 46

Re: 全志A33 UART baudrate 921600 問題!!

出到921600波特率了. 謝謝!!

离线

楼主 #16 2019-10-25 12:02:07 分享评论

- augyy

- 会员

- 注册时间: 2019-01-29

- 已发帖子: 46

- 积分: 46

Re: 全志A33 UART baudrate 921600 問題!!

augyy 说:出到921600波特率了. 謝謝!!

请问怎么做到的呢?

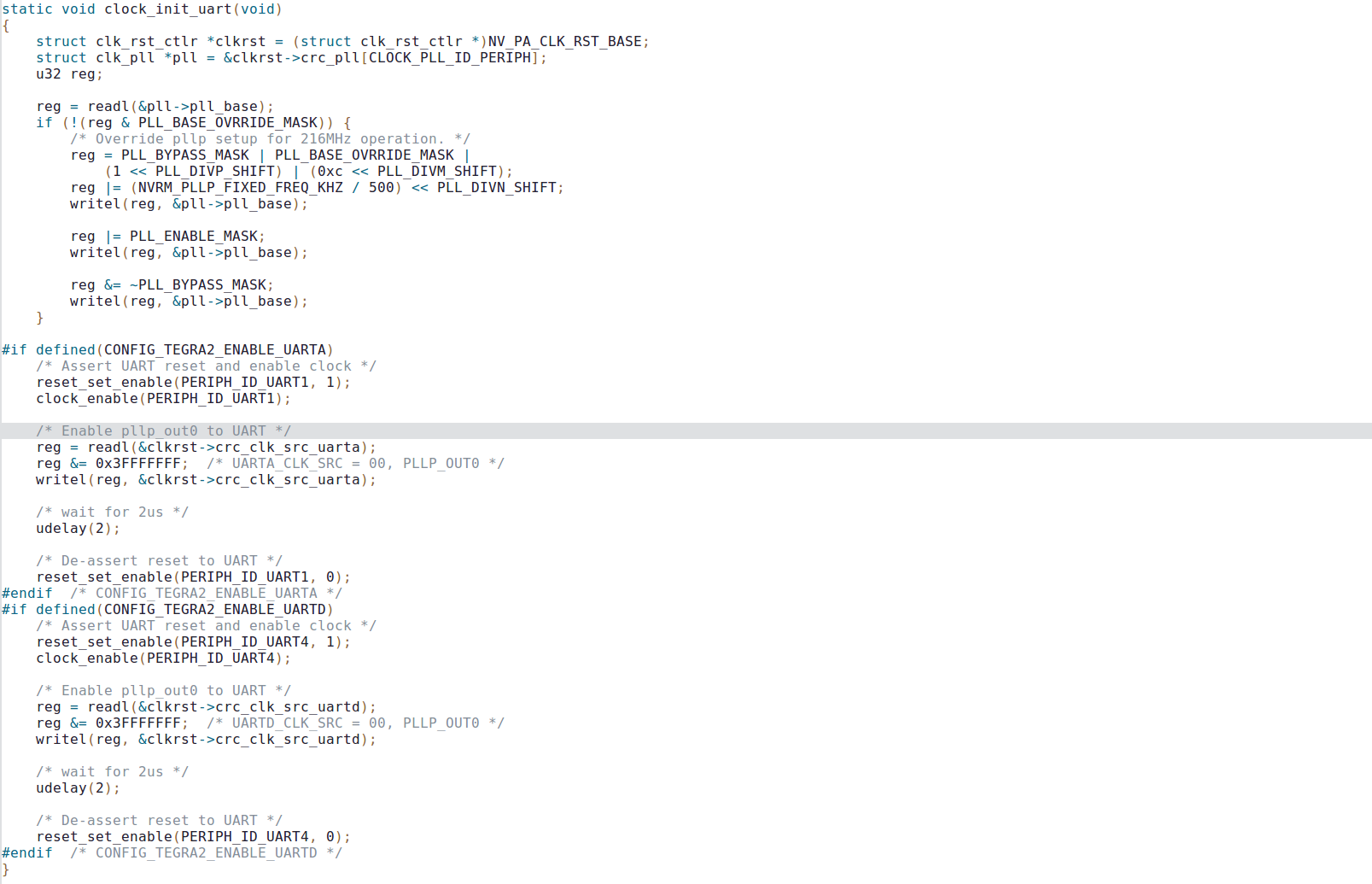

Linus-SDK/dragonboard/brandy/u-boot-2011.09/arch/arm/cpu/armv7/sun8iw5/clock.c

int sunxi_clock_set_corepll(xxx) 加 :

reg_val = readl(CCM_APB2_CLK_CTRL);

reg_val &= ~((0x03 << 24) | (0x.03 << 16) | (0x1f << 0);

reg_val |= (0x02 << 24) | (0x07 << 0);

writel(reg_val, CCM_APB2_CLK_CTRL);

int sunxi_clock_get_apb2(void) 改:

//return 24;

return 600;

之後起 brandy/ 行 ./build.sh -p sun8iw5p1

离线

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发