楼主 #1 2020-01-21 12:28:22 分享评论

- staunchheart

- 会员

- 注册时间: 2019-12-17

- 已发帖子: 232

- 积分: 190

50PIN 1024*600踩坑及后续的一种可能

https://whycan.cn/t_2135.html

参考大佬的贴子,我也调能了50pin 1024*600的屏,但中间并不顺利。本来想直接在后面回贴的,但考虑到其实有朋友也遇到同样的问题,却不问也不发贴;比如坐在QQ群后排的一位同学,感谢他的帮助。我的屏和板都是别人公司的,没有原理图也没有资料,而他的有,而且他也遇到了同样的问题。

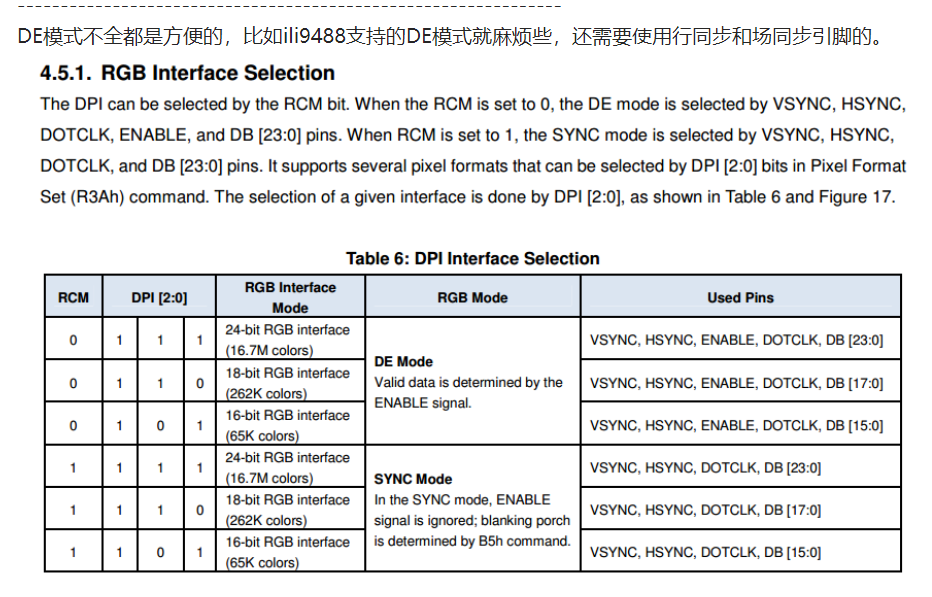

坑的位置是,达克罗德 大老用的是晕哥的转接板,这个板的mode引脚是置空的。而我们的板是设计时就在板上50PIN的,因为50PIN的屏一般都比较大,而大屏一般都用DE模式,所以我们的板上MODE是高电平。也就是说必需进入DE模式。

查看屏的手册,有的屏有这个说明。有的没有

Note 1: DE/SYNC mode select. Normally pull high.

When select DE mode, MODE=”1”, VS and HS must pull high.

When select SYNC mode, MODE= ”0”, DE must be grounded.

就是说MODE为1是VS \HS 必需高。

所以对应的

.h_sync_active = 1,

.v_sync_active = 1,

奇怪的是我的板

.den_active = 1,

.clk_active = 1,

必需这样才能行。

离线

楼主 #2 2020-01-21 12:31:41 分享评论

- staunchheart

- 会员

- 注册时间: 2019-12-17

- 已发帖子: 232

- 积分: 190

Re: 50PIN 1024*600踩坑及后续的一种可能

再接着说另一个坑。。在没有改

write32(F1C100S_CCU_BASE + CCU_PLL_VIDEO_CTRL, 0x81004103);

前,如果用480*800的50PIN 7寸屏,MODE为高时,会出现一个有意思的事。

198000000/33300000=5.9 在XBoot中,因为申明为int64,所以得到6,而我用RTT,GCC编译的,得到的是5.

这一点点差别就是黑屏与正常使用的问题,

所以write32(F1C100S_CCU_BASE + CCU_PLL_VIDEO_CTRL, 0x81004103);这个是必需改。

然后我去查资料,如果VS AND HS必需为PULL HIGH, 是否意味着 ,在设计电路时将这两个脚拉高,就可以空出两个IO用呢。

离线

楼主 #3 2020-01-21 12:34:17 分享评论

- staunchheart

- 会员

- 注册时间: 2019-12-17

- 已发帖子: 232

- 积分: 190

Re: 50PIN 1024*600踩坑及后续的一种可能

水贴了,,拆开说,有积分的。。。

查到资料说,很多屏都是这样的,只要将HS与VS拉高就可以了。因为我这个屏没法试,所以我希望有群友可以试试。

有晕哥哪个转接板的朋友应该更加方便试。

我做的测试是

fb_f1c100s_cfg_gpios(GPIO_PORT_D, GPIO_PIN_0, 20, IO_FUN_1, PULL_DISABLE, DRV_LEVEL_3);

fb_f1c100s_cfg_gpios(GPIO_PORT_D, GPIO_PIN_20, 22, IO_OUTPUT, PULL_UP, DRV_LEVEL_3);

将D20,D21不复用为HS VS ,当作普通的IO,上拉,经测试手上这块屏是可以的。

希望朋友们也测试一下,这样是否可以省出两个IO来?

离线

楼主 #6 2020-01-21 17:05:58 分享评论

- staunchheart

- 会员

- 注册时间: 2019-12-17

- 已发帖子: 232

- 积分: 190

Re: 50PIN 1024*600踩坑及后续的一种可能

TKS 老大。如果项目选型确定后,可以省出一个IO用也是不错的。

F1C100S的IO口太少了。

离线

楼主 #8 2020-01-21 17:27:39 分享评论

- staunchheart

- 会员

- 注册时间: 2019-12-17

- 已发帖子: 232

- 积分: 190

Re: 50PIN 1024*600踩坑及后续的一种可能

我还是有些不明白。

强行解释一波的话,就是可能老的产品需要三个同时。

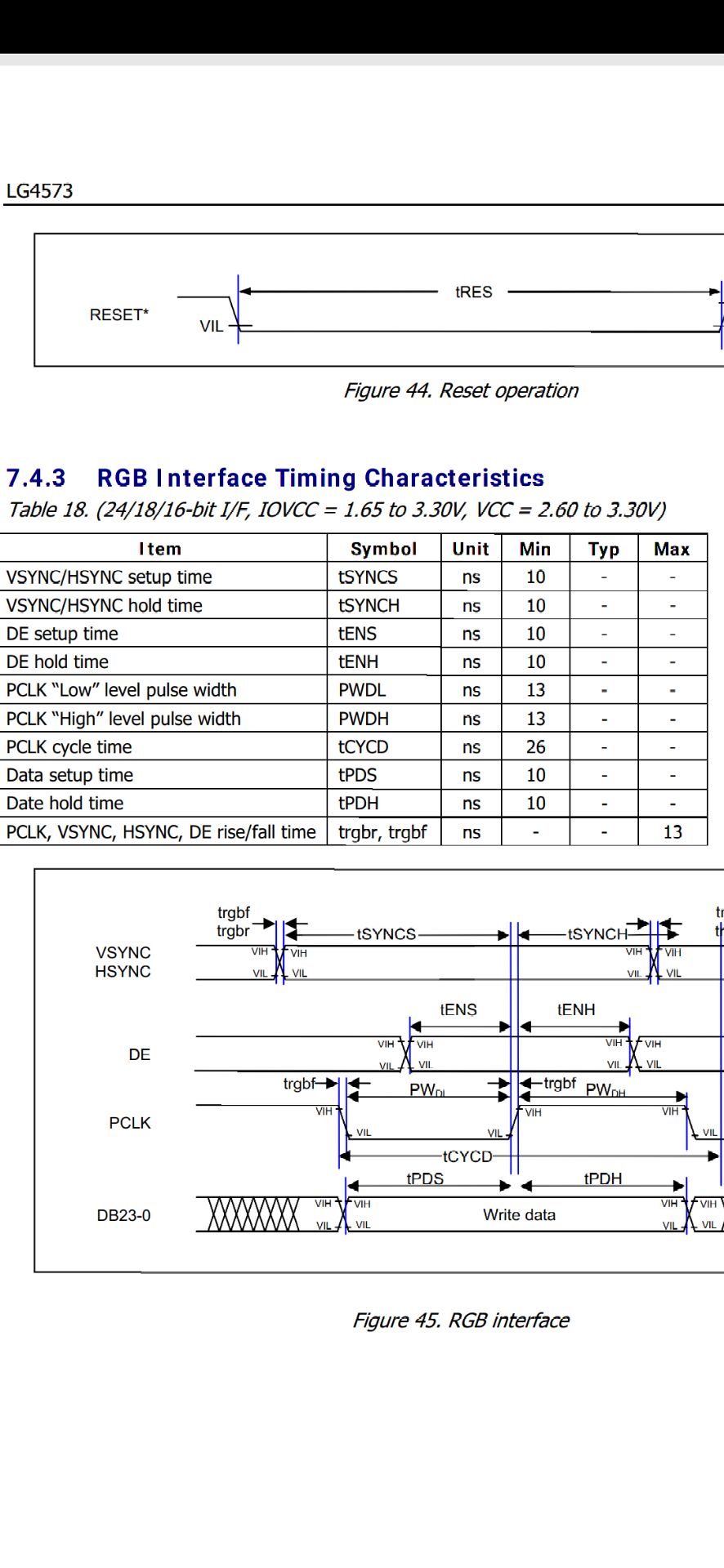

因为DE模式好像是后面才有的。

这个是群里小伙伴发给我的他用的屏的手册截图。问题太基础他们不好意思问,我也看不太懂。

离线

楼主 #11 2020-01-21 17:43:24 分享评论

- staunchheart

- 会员

- 注册时间: 2019-12-17

- 已发帖子: 232

- 积分: 190

Re: 50PIN 1024*600踩坑及后续的一种可能

总结起来的意思是:

1、DE模式,将VSYNC/HSYNC当作普通IO用是可以的,将VSYNC/HSYNC用电路拉高就好了。

2、VH模式下,将DE脚用电路接地,将DE脚本以复用为普通IO,也是可行的。

3、以上两种需要在屏选型时确认,并不是市面上随意买一块都可以这样用。所以最好还是电路上留下跳线来选择。

最近编辑记录 staunchheart (2020-01-21 17:43:34)

离线

楼主 #14 2020-04-10 11:35:34 分享评论

- staunchheart

- 会员

- 注册时间: 2019-12-17

- 已发帖子: 232

- 积分: 190

Re: 50PIN 1024*600踩坑及后续的一种可能

everlink wrote:

楼主好,我做了一个40PIN转60PIN的板子,打算驱动一块DE mode的屏,还没有搞定

请教楼主,能分享些经验吗

能不能分享谢代码或者BIN

多谢。

参考

https://whycan.cn/t_3538.html

https://gitee.com/zhangheyang/f1c100s_rt-thread

这里有RTT的代码,如果只想调试屏幕,本站的裸机程序带了屏幕显示,可能更适合你参考。

代码少,功能独立,容易找到要修改的地方。

离线

东莞哇酷科技有限公司开发