楼主 # 2023-03-15 10:02:04 分享评论

- LIVPO

- 会员

- 注册时间: 2022-10-09

- 已发帖子: 22

- 积分: 302

R128可以在FreeRTOS下查看并更改RISC-V、ARM、DSP三个CPU核的默认运行频率了

1.主题

FreeRTOS_R128_如何查看并更改各CPU核的默认运行频率

2.问题背景

硬件:R128

软件:FreeRTOS

在日常开发过程中,需要评估各CPU核的默认运行频率,有时候需要降低默认运行频率来降低功耗,有时候又需要提升默认运行频率来增加算力。

那么如何从查看并更改R128上各CPU核的默认运行频率?

3.解决办法

查看各CPU核默认运行频率

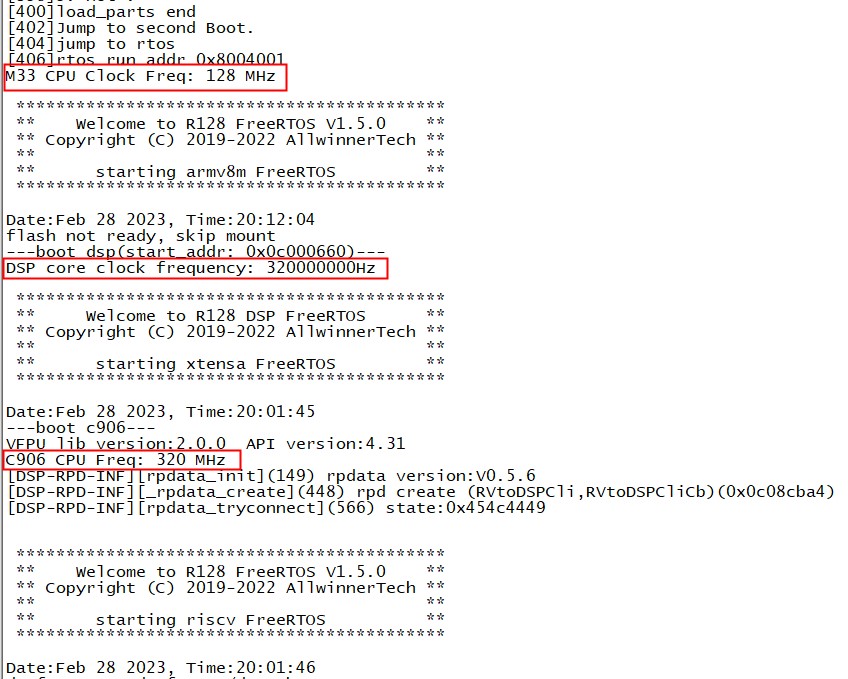

默认启动各个CPU核时会打印对应CPU核的运行频率,如下图所示:

更改各CPU核默认运行频率方法

由于R128中各CPU核的默认运行频率是M33核上的代码配置的,因此只需修改M33核的代码即可。

具体步骤为:

首先通过执行crtos命令切换到rtos代码目录,rtos代码目录路径为:lichee/rtos

然后修改文件arch/arm/armv8m/sun20iw2p1/sun20i.c里设置相关时钟频率的地方

M33核

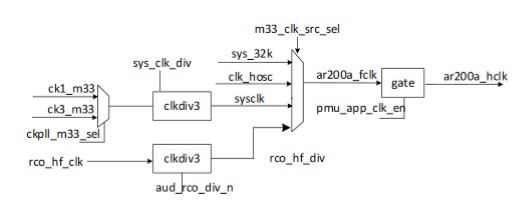

M33核相关时钟硬件如下图:

目前SDK中M33核时钟ar200a_hclk的来源为:DPLL1输出时钟经过第一个分频器输出ck1_m33时钟,然后通过第二个分频器输出sysclk钟,最后通过一个多路选择器输出ar200a_hclk。

DPLL1输出时钟的频率已经确定为1920M,因此要修改M33核的时钟,则只需要修改这2个分频器的分频值即可。

由于SDK中默认将第一个分频器的分频值定为5(此分频器的分频值取值范围为4-8),也即ck1_m33时钟频率为1920/5=384M,而第二个分频器的分频值取值范围为1-16,因此如果要修改的M33核时钟频率在24M到384M之间且可以被384M整除,则只需要修改第2个分频器的分频值,例如将M33核默认运行频率修改为128M,则只需修改宏AR200A_FREQ即可,如下所示:

diff --git a/arch/arm/armv8m/sun20iw2p1/sun20i.c b/arch/arm/armv8m/sun20iw2p1/sun20i.c

index 9b8c1cb1..c09444fc 100755

--- a/arch/arm/armv8m/sun20iw2p1/sun20i.c

+++ b/arch/arm/armv8m/sun20iw2p1/sun20i.c

@@ -445,7 +445,7 @@ static void rcosc_init(void)

#define DPLL1_FREQ (1920000000)

#define DPLL2_FREQ (1920000000)

#define DPLL3_FREQ (1600000000)

-#define AR200A_FREQ ( 192000000)

+#define AR200A_FREQ ( 128000000)

#define DEVICE_FREQ ( 192000000)

static int sys_clk_init(void)

{若要修改的M33核时钟频率不满足上述条件,则需要同时修改函数ar200a_clk_set里设置ck1_m33时钟频率的地方,例如修改ck1_m33时钟为240M(1920/8=240M):

diff --git a/arch/arm/armv8m/sun20iw2p1/sun20i.c b/arch/arm/armv8m/sun20iw2p1/sun20i.c

index 9b8c1cb1..29b71137 100755

--- a/arch/arm/armv8m/sun20iw2p1/sun20i.c

+++ b/arch/arm/armv8m/sun20iw2p1/sun20i.c

@@ -190,7 +190,7 @@ static int ar200a_clk_set(u32 freq)

/*fixed 384M*/

//sr32(CCMU_AON_BASE+0xa4, 0, 3, 0x3);

//0x4004c4a4: 0x8080000b

- ret = hal_clk_set_rate(clk_ck1_m33, 384000000);

+ ret = hal_clk_set_rate(clk_ck1_m33, 240000000);

if (HAL_CLK_STATUS_OK != ret) {

ret = -1;

goto err2;C906核

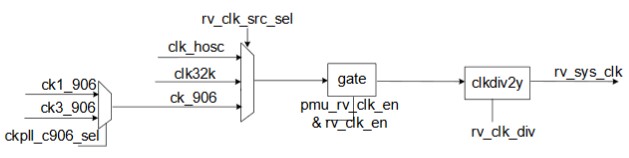

C906核相关时钟硬件如下图:

目前SDK中C906核时钟rv_sys_clk的来源为:DPLL1输出时钟经过第一个分频器输出ck1_906时钟,然后通过第二个分频器输出rv_sys_clk时钟。

DPLL1输出时钟的频率已经确定为1920M,因此要修改C906核的时钟,则只需要修改这2个分频器的分频值即可,第一个分频器的分频值可取2、2.5、3、4、7,第二个分频器的分频值可取1、2、4、8。

例如将C906核默认运行频率修改为320M,需要修改sun20i_boot_c906函数中2处设置频率的地方,:

diff --git a/arch/arm/armv8m/sun20iw2p1/sun20i.c b/arch/arm/armv8m/sun20iw2p1/sun20i.c

index 9b8c1cb1..5798657b 100755

--- a/arch/arm/armv8m/sun20iw2p1/sun20i.c

+++ b/arch/arm/armv8m/sun20iw2p1/sun20i.c

@@ -596,7 +596,7 @@ int sun20i_boot_c906(void)

//set clk_ck1_c906 clk to 480M

//sr32(CCMU_AON_BASE+0xa4, 4, 3, 0x1);

- ret = hal_clk_set_rate(clk_ck1_c906, 480000000);

+ ret = hal_clk_set_rate(clk_ck1_c906, 640000000);

if (HAL_CLK_STATUS_OK != ret) {

ret = -1;

goto err2;

@@ -632,7 +632,7 @@ int sun20i_boot_c906(void)

//set clk_ck_c906_div to 480000000;

//sr32(CCMU_BASE+0x064, 0, 2, 0x0);

clk_c906_div = hal_clock_get(HAL_SUNXI_CCU, CLK_RISCV_DIV);

- ret = hal_clk_set_rate(clk_c906_div, 480000000);

+ ret = hal_clk_set_rate(clk_c906_div, 320000000);

if (HAL_CLK_STATUS_OK != ret) {

ret = -1;

goto err6;PS:由于第一个分频器无法输出320M时钟,故先配置第一个分频器输出640M的ck1_c906时钟,然后由第二个分频器再进行2分频,从而得到320M的C906核时钟。

DSP核

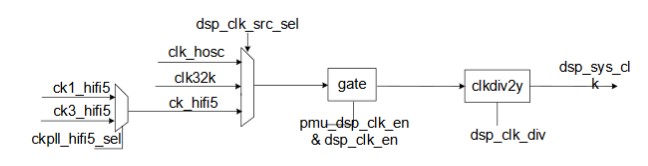

DSP核相关时钟硬件如下图:

目前SDK中DSP核时钟dsp_sys_clk的来源为:DPLL3输出时钟经过第一个分频器输出ck3_hifi5时钟,然后通过第二个分频器输出dsp_sys_clk时钟。

DPLL3输出时钟的频率已经确定为1600M,因此要修改DSP核的时钟,则只需要修改这2个分频器的分频值即可,第一个分频器的分频值可取3、4、5、6、7,第二个分频器的分频值可取1、2、4、8。

例如将DSP核默认运行频率修改为320M,只需修改宏DSP_CORE_CLOCK_FREQ即可,:

diff --git a/arch/arm/armv8m/sun20iw2p1/sun20i.c b/arch/arm/armv8m/sun20iw2p1/sun20i.c

index 9b8c1cb1..97d03ad7 100755

--- a/arch/arm/armv8m/sun20iw2p1/sun20i.c

+++ b/arch/arm/armv8m/sun20iw2p1/sun20i.c

@@ -703,7 +703,7 @@ err1:

#if defined(CONFIG_ARCH_ARMV8M_DEFAULT_BOOT_DSP) || defined(CONFIG_COMMAND_BOOT_DSP) \

|| defined(CONFIG_PM_SUBSYS_DSP_SUPPORT)

-#define DSP_CORE_CLOCK_FREQ (400000000)

+#define DSP_CORE_CLOCK_FREQ (320000000)

#define DSP_LDO_WORK_VOLT (1200) //400M@1.2V, 274M@1.1V

int __sun20i_boot_dsp_with_start_addr(uint32_t dsp_start_addr)

{另外目前SDK代码中第一个分频器和第二个分频都配置成了相同的频率,若第一个分频器无法直接输出想要设置的频率,则需要分别将2个分频器配置成不同的输出频率。例如将DSP核默认运行频率修改为200M,第一个分频器最低输出时钟频率为1600/7=228.57M,无法直接输出200M,因此需要先配置第一个分频器输出400M的ck3_hifi5时钟,然后由第二个分频器进行2分频从而得到200M的dsp_sys_clk时钟,主要修改如下所示:

diff --git a/arch/arm/armv8m/sun20iw2p1/sun20i.c b/arch/arm/armv8m/sun20iw2p1/sun20i.c

index 9b8c1cb1..53f6828a 100755

--- a/arch/arm/armv8m/sun20iw2p1/sun20i.c

+++ b/arch/arm/armv8m/sun20iw2p1/sun20i.c

@@ -703,7 +703,7 @@ err1:

#if defined(CONFIG_ARCH_ARMV8M_DEFAULT_BOOT_DSP) || defined(CONFIG_COMMAND_BOOT_DSP) \

|| defined(CONFIG_PM_SUBSYS_DSP_SUPPORT)

-#define DSP_CORE_CLOCK_FREQ (400000000)

+#define DSP_CORE_CLOCK_FREQ (200000000)

#define DSP_LDO_WORK_VOLT (1200) //400M@1.2V, 274M@1.1V

int __sun20i_boot_dsp_with_start_addr(uint32_t dsp_start_addr)

{

@@ -752,7 +752,7 @@ int __sun20i_boot_dsp_with_start_addr(uint32_t dsp_start_addr)

//set clk_ck3_hifi5 clk to 400M

//sr32(CCMU_AON_BASE+0xa8, 8, 3, 0x3);

- ret = hal_clk_set_rate(clk_ck3_hifi5, DSP_CORE_CLOCK_FREQ);

+ ret = hal_clk_set_rate(clk_ck3_hifi5, 400000000);

if (HAL_CLK_STATUS_OK != ret) {

ret = -1;

goto err2;修改完成后重新编译M33核固件,因为R128中各CPU核的默认运行频率是M33核上的代码配置的。

可先执行lunch_rtos选择对应方案的M33核,然后再执行mrtos编译以及执行pack命令打包固件。

下图是修改M33核频率为128M、C906核频率为320M、DSP核频率为320M后的效果:

离线

楼主 #4 2023-03-15 14:36:37 分享评论

- LIVPO

- 会员

- 注册时间: 2022-10-09

- 已发帖子: 22

- 积分: 302

Re: R128可以在FreeRTOS下查看并更改RISC-V、ARM、DSP三个CPU核的默认运行频率了

r128的c906最大能到多少,d1h好像也是c906架构频率可以1g左右

从爆料看是C906 600 MHz,DSP 400 MHz,M33 240 MHz这样

离线

楼主 #5 2023-03-15 14:38:05 分享评论

- LIVPO

- 会员

- 注册时间: 2022-10-09

- 已发帖子: 22

- 积分: 302

Re: R128可以在FreeRTOS下查看并更改RISC-V、ARM、DSP三个CPU核的默认运行频率了

芯片可以购买了吗

据说快了,芯片能不能卖,晕哥肯定会有一手消息

离线

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发