楼主 #1 2018-07-20 16:28:34 分享评论

- awfans

- 会员

- 注册时间: 2018-04-03

- 已发帖子: 264

- 积分: 264

请问 荔枝派zero V3s主线u-boot 如何修改默认的串口为uart2(PB0/PB1) ?

git clone https://github.com/Lichee-Pi/u-boot.git -b v3s-spi-experimental

代码是上面这里下载到的.

默认是从 PB8,PB9 这组 UART0 输出的,

我现在想改到 PB0, PB1 这组 UART2 输出,

应该如何做到呢?

以下由 @哇酷小二 2021-02-10 添加

------------------------------------

相关链接:

荔枝派zero V3S u-boot调试信息从UART1(PE21/PE22)输出没有成功,还遗留什么没有修改? (修改成功,方案在8楼)

http://whycan.com/t_1624.html

离线

楼主 #2 2018-07-20 17:47:45 分享评论

- awfans

- 会员

- 注册时间: 2018-04-03

- 已发帖子: 264

- 积分: 264

Re: 请问 荔枝派zero V3s主线u-boot 如何修改默认的串口为uart2(PB0/PB1) ?

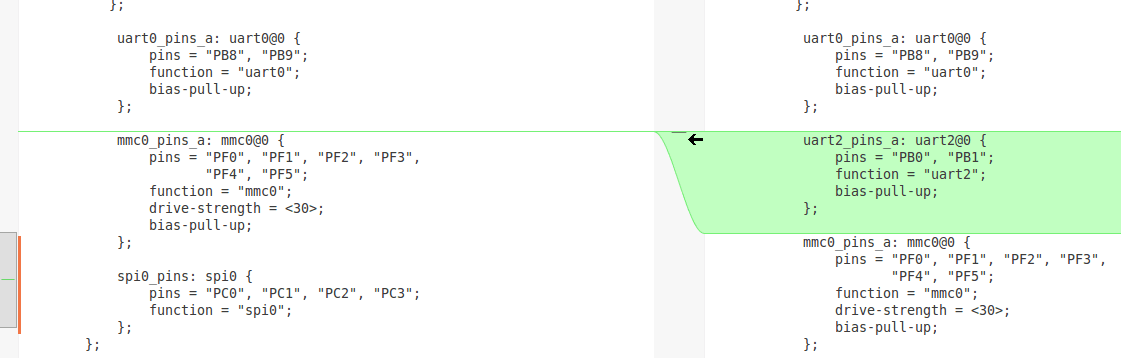

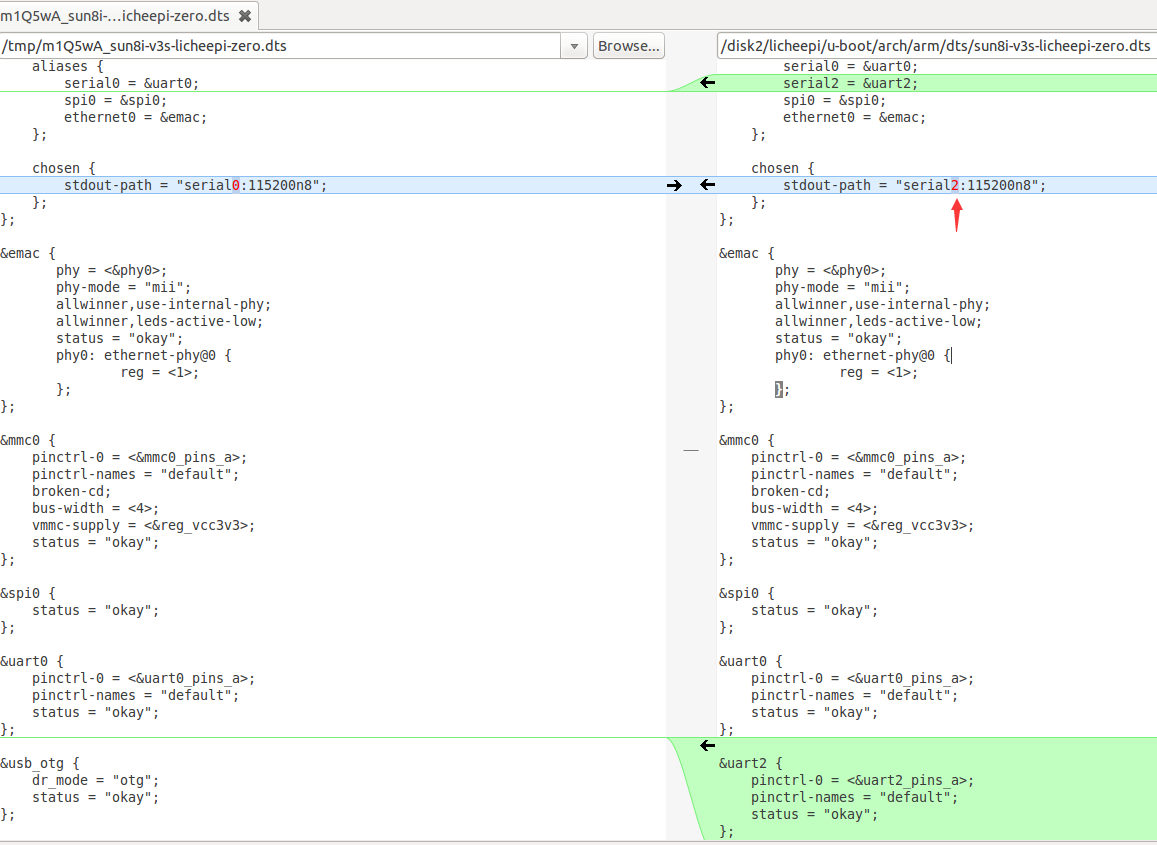

修改了这两个文件:

modified: arch/arm/dts/sun8i-v3s-licheepi-zero.dts

/*

* Copyright (C) 2016 Icenowy Zheng <icenowy@aosc.xyz>

*

* This file is dual-licensed: you can use it either under the terms

* of the GPL or the X11 license, at your option. Note that this dual

* licensing only applies to this file, and not this project as a

* whole.

*

* a) This file is free software; you can redistribute it and/or

* modify it under the terms of the GNU General Public License as

* published by the Free Software Foundation; either version 2 of the

* License, or (at your option) any later version.

*

* This file is distributed in the hope that it will be useful,

* but WITHOUT ANY WARRANTY; without even the implied warranty of

* MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

* GNU General Public License for more details.

*

* Or, alternatively,

*

* b) Permission is hereby granted, free of charge, to any person

* obtaining a copy of this software and associated documentation

* files (the "Software"), to deal in the Software without

* restriction, including without limitation the rights to use,

* copy, modify, merge, publish, distribute, sublicense, and/or

* sell copies of the Software, and to permit persons to whom the

* Software is furnished to do so, subject to the following

* conditions:

*

* The above copyright notice and this permission notice shall be

* included in all copies or substantial portions of the Software.

*

* THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND,

* EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES

* OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND

* NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT

* HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY,

* WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING

* FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR

* OTHER DEALINGS IN THE SOFTWARE.

*/

/dts-v1/;

#include "sun8i-v3s.dtsi"

#include "sunxi-common-regulators.dtsi"

/ {

model = "Lichee Pi Zero";

compatible = "licheepi,licheepi-zero", "allwinner,sun8i-v3s";

aliases {

serial0 = &uart0;

serial2 = &uart2;

spi0 = &spi0;

ethernet0 = &emac;

};

chosen {

stdout-path = "serial2:115200n8";

};

};

&emac {

phy = <&phy0>;

phy-mode = "mii";

allwinner,use-internal-phy;

allwinner,leds-active-low;

status = "okay";

phy0: ethernet-phy@0 {

reg = <1>;

};

};

&mmc0 {

pinctrl-0 = <&mmc0_pins_a>;

pinctrl-names = "default";

broken-cd;

bus-width = <4>;

vmmc-supply = <®_vcc3v3>;

status = "okay";

};

&spi0 {

status = "okay";

};

&uart0 {

pinctrl-0 = <&uart0_pins_a>;

pinctrl-names = "default";

status = "okay";

};

&uart2 {

pinctrl-0 = <&uart2_pins_a>;

pinctrl-names = "default";

status = "okay";

};

&usb_otg {

dr_mode = "otg";

status = "okay";

};

&usbphy {

usb0_id_det-gpio = <&pio 5 6 GPIO_ACTIVE_HIGH>;

status = "okay";

};modified: arch/arm/dts/sun8i-v3s.dtsi

/*

* Copyright (C) 2016 Icenowy Zheng <icenowy@aosc.xyz>

*

* This file is dual-licensed: you can use it either under the terms

* of the GPL or the X11 license, at your option. Note that this dual

* licensing only applies to this file, and not this project as a

* whole.

*

* a) This file is free software; you can redistribute it and/or

* modify it under the terms of the GNU General Public License as

* published by the Free Software Foundation; either version 2 of the

* License, or (at your option) any later version.

*

* This file is distributed in the hope that it will be useful,

* but WITHOUT ANY WARRANTY; without even the implied warranty of

* MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

* GNU General Public License for more details.

*

* Or, alternatively,

*

* b) Permission is hereby granted, free of charge, to any person

* obtaining a copy of this software and associated documentation

* files (the "Software"), to deal in the Software without

* restriction, including without limitation the rights to use,

* copy, modify, merge, publish, distribute, sublicense, and/or

* sell copies of the Software, and to permit persons to whom the

* Software is furnished to do so, subject to the following

* conditions:

*

* The above copyright notice and this permission notice shall be

* included in all copies or substantial portions of the Software.

*

* THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND,

* EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES

* OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND

* NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT

* HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY,

* WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING

* FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR

* OTHER DEALINGS IN THE SOFTWARE.

*/

#include <dt-bindings/clock/sun8i-v3s-ccu.h>

#include <dt-bindings/reset/sun8i-v3s-ccu.h>

#include <dt-bindings/interrupt-controller/arm-gic.h>

#include <dt-bindings/pinctrl/sun4i-a10.h>

/ {

#address-cells = <1>;

#size-cells = <1>;

interrupt-parent = <&gic>;

cpus {

#address-cells = <1>;

#size-cells = <0>;

cpu@0 {

compatible = "arm,cortex-a7";

device_type = "cpu";

reg = <0>;

clocks = <&ccu CLK_CPU>;

};

};

timer {

compatible = "arm,armv7-timer";

interrupts = <GIC_PPI 13 (GIC_CPU_MASK_SIMPLE(4) | IRQ_TYPE_LEVEL_LOW)>,

<GIC_PPI 14 (GIC_CPU_MASK_SIMPLE(4) | IRQ_TYPE_LEVEL_LOW)>,

<GIC_PPI 11 (GIC_CPU_MASK_SIMPLE(4) | IRQ_TYPE_LEVEL_LOW)>,

<GIC_PPI 10 (GIC_CPU_MASK_SIMPLE(4) | IRQ_TYPE_LEVEL_LOW)>;

};

clocks {

#address-cells = <1>;

#size-cells = <1>;

ranges;

osc24M: osc24M_clk {

#clock-cells = <0>;

compatible = "fixed-clock";

clock-frequency = <24000000>;

clock-output-names = "osc24M";

};

osc32k: osc32k_clk {

#clock-cells = <0>;

compatible = "fixed-clock";

clock-frequency = <32768>;

clock-output-names = "osc32k";

};

};

soc {

compatible = "simple-bus";

#address-cells = <1>;

#size-cells = <1>;

ranges;

dma: dma-controller@01c02000 {

compatible = "allwinner,sun8i-v3s-dma";

reg = <0x01c02000 0x1000>;

interrupts = <GIC_SPI 50 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_BUS_DMA>;

resets = <&ccu RST_BUS_DMA>;

#dma-cells = <1>;

};

syscon: syscon@01c00000 {

compatible = "allwinner,sun8i-h3-syscon","syscon";

reg = <0x01c00000 0x34>;

};

mmc0: mmc@01c0f000 {

compatible = "allwinner,sun7i-a20-mmc";

reg = <0x01c0f000 0x1000>;

clocks = <&ccu CLK_BUS_MMC0>,

<&ccu CLK_MMC0>,

<&ccu CLK_MMC0_OUTPUT>,

<&ccu CLK_MMC0_SAMPLE>;

clock-names = "ahb",

"mmc",

"output",

"sample";

resets = <&ccu RST_BUS_MMC0>;

reset-names = "ahb";

interrupts = <GIC_SPI 60 IRQ_TYPE_LEVEL_HIGH>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

mmc1: mmc@01c10000 {

compatible = "allwinner,sun7i-a20-mmc";

reg = <0x01c10000 0x1000>;

clocks = <&ccu CLK_BUS_MMC1>,

<&ccu CLK_MMC1>,

<&ccu CLK_MMC1_OUTPUT>,

<&ccu CLK_MMC1_SAMPLE>;

clock-names = "ahb",

"mmc",

"output",

"sample";

resets = <&ccu RST_BUS_MMC1>;

reset-names = "ahb";

interrupts = <GIC_SPI 61 IRQ_TYPE_LEVEL_HIGH>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

mmc2: mmc@01c11000 {

compatible = "allwinner,sun7i-a20-mmc";

reg = <0x01c11000 0x1000>;

clocks = <&ccu CLK_BUS_MMC2>,

<&ccu CLK_MMC2>,

<&ccu CLK_MMC2_OUTPUT>,

<&ccu CLK_MMC2_SAMPLE>;

clock-names = "ahb",

"mmc",

"output",

"sample";

resets = <&ccu RST_BUS_MMC2>;

reset-names = "ahb";

interrupts = <GIC_SPI 62 IRQ_TYPE_LEVEL_HIGH>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

usb_otg: usb@01c19000 {

compatible = "allwinner,sun8i-h3-musb";

reg = <0x01c19000 0x0400>;

clocks = <&ccu CLK_BUS_OTG>;

resets = <&ccu RST_BUS_OTG>;

interrupts = <GIC_SPI 71 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "mc";

phys = <&usbphy 0>;

phy-names = "usb";

extcon = <&usbphy 0>;

status = "disabled";

};

usbphy: phy@01c19400 {

compatible = "allwinner,sun8i-v3s-usb-phy";

reg = <0x01c19400 0x2c>,

<0x01c1a800 0x4>;

reg-names = "phy_ctrl",

"pmu0";

clocks = <&ccu CLK_USB_PHY0>;

clock-names = "usb0_phy";

resets = <&ccu RST_USB_PHY0>;

reset-names = "usb0_reset";

status = "disabled";

#phy-cells = <1>;

};

ccu: clock@01c20000 {

compatible = "allwinner,sun8i-v3s-ccu";

reg = <0x01c20000 0x400>;

clocks = <&osc24M>, <&osc32k>;

clock-names = "hosc", "losc";

#clock-cells = <1>;

#reset-cells = <1>;

};

rtc: rtc@01c20400 {

compatible = "allwinner,sun6i-a31-rtc";

reg = <0x01c20400 0x54>;

interrupts = <GIC_SPI 40 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 41 IRQ_TYPE_LEVEL_HIGH>;

};

pio: pinctrl@01c20800 {

compatible = "allwinner,sun8i-v3s-pinctrl";

reg = <0x01c20800 0x400>;

interrupts = <GIC_SPI 15 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 17 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_BUS_PIO>, <&osc24M>, <&osc32k>;

clock-names = "apb", "hosc", "losc";

gpio-controller;

#gpio-cells = <3>;

interrupt-controller;

#interrupt-cells = <3>;

emac_rgmii_pins: emac0@0 {

allwinner,pins = "PD0", "PD1", "PD2", "PD3",

"PD4", "PD5", "PD7",

"PD8", "PD9", "PD10",

"PD12", "PD13", "PD15",

"PD16", "PD17";

allwinner,function = "emac";

allwinner,drive = <SUN4I_PINCTRL_40_MA>;

allwinner,pull = <SUN4I_PINCTRL_NO_PULL>;

};

uart0_pins_a: uart0@0 {

pins = "PB8", "PB9";

function = "uart0";

bias-pull-up;

};

uart2_pins_a: uart2@0 {

pins = "PB0", "PB1";

function = "uart2";

bias-pull-up;

};

mmc0_pins_a: mmc0@0 {

pins = "PF0", "PF1", "PF2", "PF3",

"PF4", "PF5";

function = "mmc0";

drive-strength = <30>;

bias-pull-up;

};

spi0_pins: spi0 {

pins = "PC0", "PC1", "PC2", "PC3";

function = "spi0";

};

};

timer@01c20c00 {

compatible = "allwinner,sun4i-a10-timer";

reg = <0x01c20c00 0xa0>;

interrupts = <GIC_SPI 18 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 19 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&osc24M>;

};

wdt0: watchdog@01c20ca0 {

compatible = "allwinner,sun6i-a31-wdt";

reg = <0x01c20ca0 0x20>;

interrupts = <GIC_SPI 25 IRQ_TYPE_LEVEL_HIGH>;

};

uart0: serial@01c28000 {

compatible = "snps,dw-apb-uart";

reg = <0x01c28000 0x400>;

interrupts = <GIC_SPI 0 IRQ_TYPE_LEVEL_HIGH>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_BUS_UART0>;

resets = <&ccu RST_BUS_UART0>;

status = "disabled";

};

uart1: serial@01c28400 {

compatible = "snps,dw-apb-uart";

reg = <0x01c28400 0x400>;

interrupts = <GIC_SPI 1 IRQ_TYPE_LEVEL_HIGH>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_BUS_UART1>;

resets = <&ccu RST_BUS_UART1>;

status = "disabled";

};

uart2: serial@01c28800 {

compatible = "snps,dw-apb-uart";

reg = <0x01c28800 0x400>;

interrupts = <GIC_SPI 2 IRQ_TYPE_LEVEL_HIGH>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_BUS_UART2>;

resets = <&ccu RST_BUS_UART2>;

status = "disabled";

};

spi0: spi@1c68000 {

compatible = "allwinner,sun8i-h3-spi";

reg = <0x01c68000 0x1000>;

interrupts = <GIC_SPI 65 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&ccu CLK_BUS_SPI0>, <&ccu CLK_SPI0>;

clock-names = "ahb", "mod";

pinctrl-names = "default";

pinctrl-0 = <&spi0_pins>;

resets = <&ccu RST_BUS_SPI0>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

emac: ethernet@1c30000 {

compatible = "allwinner,sun8i-h3-emac";

reg = <0x01c30000 0x104>, <0x01c00030 0x4>;

reg-names = "emac", "syscon";

interrupts = <GIC_SPI 82 IRQ_TYPE_LEVEL_HIGH>;

resets = <&ccu RST_BUS_EMAC>, <&ccu RST_BUS_EPHY>;

reset-names = "ahb", "ephy";

clocks = <&ccu CLK_BUS_EMAC>, <&ccu CLK_BUS_EPHY>;

clock-names = "ahb", "ephy";

#address-cells = <1>;

#size-cells = <0>;

status = "disabled";

};

gic: interrupt-controller@01c81000 {

compatible = "arm,cortex-a7-gic", "arm,cortex-a15-gic";

reg = <0x01c81000 0x1000>,

<0x01c82000 0x1000>,

<0x01c84000 0x2000>,

<0x01c86000 0x2000>;

interrupt-controller;

#interrupt-cells = <3>;

interrupts = <GIC_PPI 9 (GIC_CPU_MASK_SIMPLE(4) | IRQ_TYPE_LEVEL_HIGH)>;

};

};

};但是发现串口2并没有数据输出.

离线

楼主 #4 2018-07-20 22:42:15 分享评论

- awfans

- 会员

- 注册时间: 2018-04-03

- 已发帖子: 264

- 积分: 264

Re: 请问 荔枝派zero V3s主线u-boot 如何修改默认的串口为uart2(PB0/PB1) ?

根据晕哥提示的修改, 接上串口 UART2 有显示,感觉只是spl 起来了,u-boot并没有启动:

U-Boot SPL 2017.01-rc2-00073-gdd6e874-dirty (Jul 20 2018 - 22:31:29)

DRAM: 64 MiB

Trying to boot from sunxi SPI

离线

楼主 #5 2018-07-21 10:08:03 分享评论

- awfans

- 会员

- 注册时间: 2018-04-03

- 已发帖子: 264

- 积分: 264

Re: 请问 荔枝派zero V3s主线u-boot 如何修改默认的串口为uart2(PB0/PB1) ?

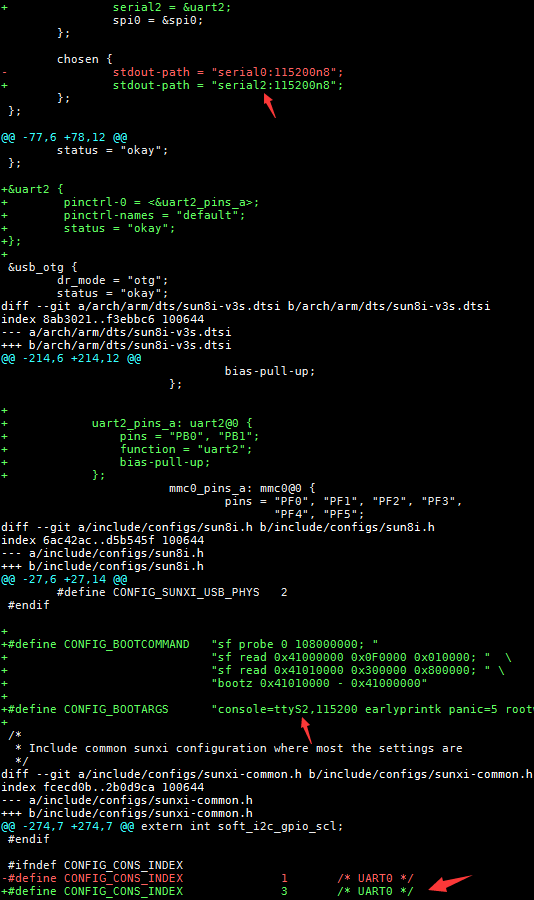

diff --git a/arch/arm/dts/sun8i-v3s-licheepi-zero.dts b/arch/arm/dts/sun8i-v3s-licheepi-zero.dts

index 3aec3eb..14376f1 100644

--- a/arch/arm/dts/sun8i-v3s-licheepi-zero.dts

+++ b/arch/arm/dts/sun8i-v3s-licheepi-zero.dts

@@ -50,11 +50,12 @@

aliases {

serial0 = &uart0;

+ serial2 = &uart2;

spi0 = &spi0;

};

chosen {

- stdout-path = "serial0:115200n8";

+ stdout-path = "serial2:115200n8";

};

};

@@ -77,6 +78,12 @@

status = "okay";

};

+&uart2 {

+ pinctrl-0 = <&uart2_pins_a>;

+ pinctrl-names = "default";

+ status = "okay";

+};

+

&usb_otg {

dr_mode = "otg";

status = "okay";

diff --git a/arch/arm/dts/sun8i-v3s.dtsi b/arch/arm/dts/sun8i-v3s.dtsi

index 8ab3021..f3ebbc6 100644

--- a/arch/arm/dts/sun8i-v3s.dtsi

+++ b/arch/arm/dts/sun8i-v3s.dtsi

@@ -214,6 +214,12 @@

bias-pull-up;

};

+

+ uart2_pins_a: uart2@0 {

+ pins = "PB0", "PB1";

+ function = "uart2";

+ bias-pull-up;

+ };

mmc0_pins_a: mmc0@0 {

pins = "PF0", "PF1", "PF2", "PF3",

"PF4", "PF5";

diff --git a/include/configs/sun8i.h b/include/configs/sun8i.h

index 6ac42ac..d5b545f 100644

--- a/include/configs/sun8i.h

+++ b/include/configs/sun8i.h

@@ -27,6 +27,14 @@

#define CONFIG_SUNXI_USB_PHYS 2

#endif

+

+#define CONFIG_BOOTCOMMAND "sf probe 0 108000000; " \

+ "sf read 0x41000000 0x0F0000 0x010000; " \

+ "sf read 0x41010000 0x300000 0x800000; " \

+ "bootz 0x41010000 - 0x41000000"

+

+#define CONFIG_BOOTARGS "console=ttyS2,115200 earlyprintk panic=5 rootwait mtdparts=spi32766.0:960k(uboot),64k(dtb),1M(background),1M(animation),8M(kernel),-(appendfs) root=/dev/ram0 rdinit=/init vt.global_cursor_default=0"

+

/*

* Include common sunxi configuration where most the settings are

*/

diff --git a/include/configs/sunxi-common.h b/include/configs/sunxi-common.h

index fcecd0b..2b0d9ca 100644

--- a/include/configs/sunxi-common.h

+++ b/include/configs/sunxi-common.h

@@ -274,7 +274,7 @@ extern int soft_i2c_gpio_scl;

#endif

#ifndef CONFIG_CONS_INDEX

-#define CONFIG_CONS_INDEX 1 /* UART0 */

+#define CONFIG_CONS_INDEX 3 /* UART0 */

#endif

#ifdef CONFIG_REQUIRE_SERIAL_CONSOLEU-Boot 2017.01-rc2-00073-gdd6e874-dirty (Jul 21 2018 - 09:56:51 +0800) Allwinner Technology

CPU: Allwinner V3s (SUN8I 1681)

Model: Lichee Pi Zero

DRAM: 64 MiB

MMC: SUNXI SD/MMC: 0

SF: Detected mx25l12805 with page size 256 Bytes, erase size 64 KiB, total 16 MiB

*** Warning - bad CRC, using default environment

Setting up a 800x480 lcd console (overscan 0x0)

dotclock: 33000kHz = 33000kHz: (1 * 3MHz * 66) / 6

In: serial@01c28800

Out: serial@01c28800

Err: serial@01c28800

Net: No ethernet found.

starting USB...

No controllers found

Hit any key to stop autoboot: 2 1 0

SF: Detected mx25l12805 with page size 256 Bytes, erase size 64 KiB, total 16 MiB

device 0 offset 0x100000, size 0x10000

SF: 65536 bytes @ 0x100000 Read: OK

device 0 offset 0x110000, size 0x600000

SF: 6291456 bytes @ 0x110000 Read: OK

=> uboot 终于启动了.

最近编辑记录 awfans (2018-07-21 10:15:02)

离线

感谢为中文互联网持续输出优质内容的各位老铁们。

QQ: 516333132, 微信(wechat): whycan_cn (哇酷网/挖坑网/填坑网) service@whycan.cn