楼主 # 2022-07-12 09:08:08 分享评论

众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

出发点:需要做个可扩展的控制器,类似PLC,IO点不够可以增加扩展模块来扩充IO,没有485等串口,可以增加扩展模块来扩充。

西门子 PLC图片如下:

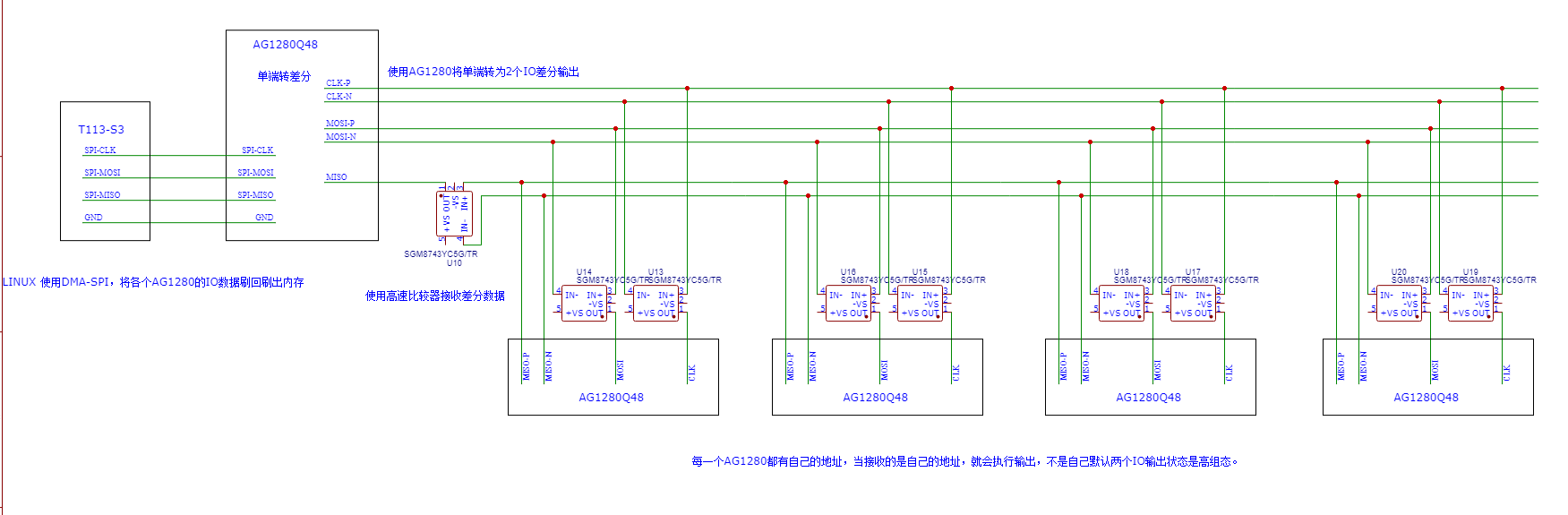

CPU主控打算用全志T113系列,

考虑扩展模块上芯片不会用太高端,所以只能从UART、SPI、I2C、RS485、CAN这类的去考虑,

1、需要多从机

2、需要高速

3、需要远距离抗干扰,比如CPU挂10个扩展模块,线长都出去了半米了。

综合考虑,T113处选择SPI接口,

使用将SPI改为3线,使用CLK、MOSI、MISO

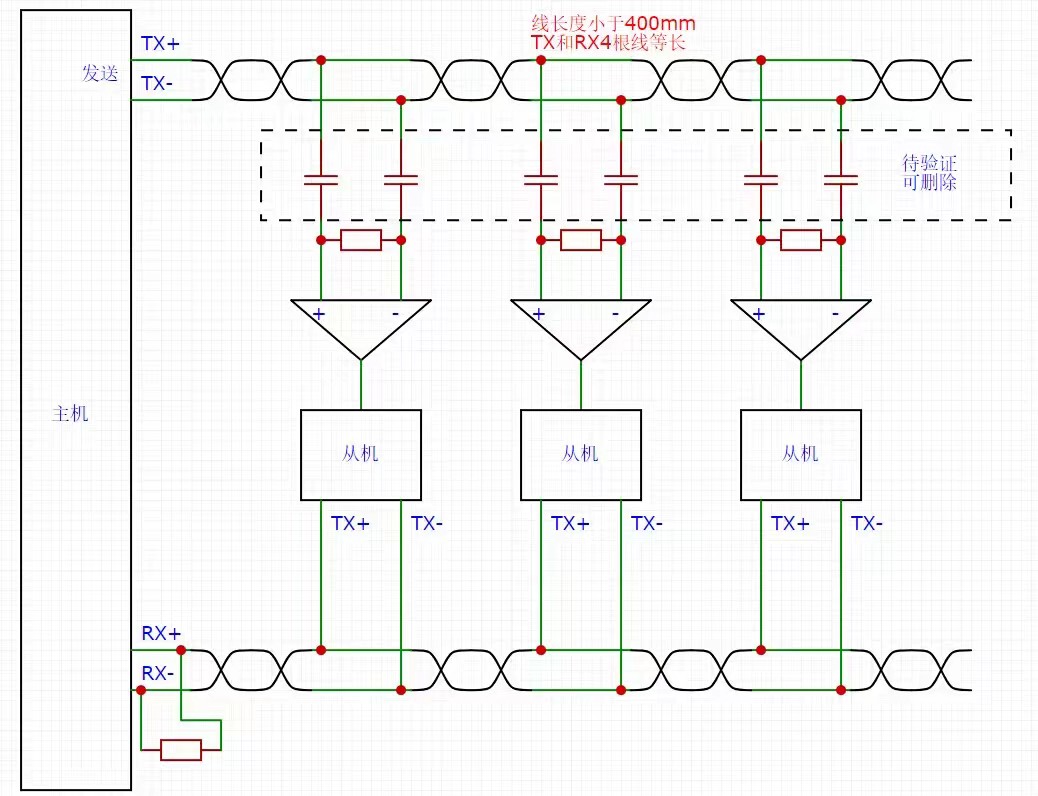

考虑远距离传输的抗干扰性,将3根信号线变为差分信号。

T113连接CPLD,CPLD将单端信号变为两个端口输出,来模拟差分线。

在接收端,使用高速比较器进行接收数据,市面在售的7ns比较器比较便宜。

增加总线的地址机制,每个从设备都有地址,当收到自己地址的数据需要发送时才会进行发送,否则发送为高阻态。

下面是初版设计原理图,

离线

楼主 #1 2022-07-12 09:11:27 分享评论

楼主 #7 2022-07-12 14:44:43 分享评论

楼主 #8 2022-07-12 14:45:29 分享评论

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

SN65LVDS049 这个应该正好

http://www.ti.com/cn/lit/gpn/sn65lvds049

我看了TI的lvds类转换芯片,价格比较贵,所以排除了。

离线

楼主 #9 2022-07-12 14:51:03 分享评论

楼主 #10 2022-07-12 14:51:47 分享评论

楼主 #13 2022-07-12 16:02:05 分享评论

楼主 #20 2022-07-13 12:51:58 分享评论

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

多谢大佬分享,是个参考项!

离线

楼主 #21 2022-07-13 12:56:01 分享评论

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

@阿黄

我之前使用485芯片来延长SPI总线,挂接HC595/HC165,线越长,相位偏移,走形便越厉害。

如果器件传输延迟低,SPI CLK不要太高,感觉没问题。

大佬能详细讲讲,吗?

你是用的RS485芯片对SPI进行延长,

也就是MOSI和CLK用了两个485芯片,

在设备HC595端也放了两个485芯片进行接收,

转出来的CLK和MOSI相位对不上吗?

单向发送也有相位偏移的问题吗?

我的从机器件打算用CPLD做,响应时间应该挺快的。

我其实有往100M跑的打算

离线

楼主 #22 2022-07-13 12:59:10 分享评论

楼主 #24 2022-07-13 17:58:24 分享评论

楼主 #26 2022-07-13 22:25:44 分享评论

楼主 #30 2022-07-14 08:50:25 分享评论

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

迪卡 说:大家还有什么建议和想法?这周我再总结一下,画下改进后的【迪卡总线】

已了解台达plc用的spi,已了解西门子背板总线用的无cs的spi,即全双工i2c。你这距离要多远 多高的速率 延迟啥要求

前面说了个大概,最远距离半米吧,上面挂接多个从设备。

速率需求就是主机发出控制某个IO的命令或是读取某个IO的状态,时间小于1us吧,先这样暂时定一个。

假设读取一个IO状态连发送带接收需要32bit的数据,那么32bit宽裕点算,按50bit算,获取IO状态用时按小于1us.

那么时钟频率最少需要50MHz

离线