楼主 #1 2020-04-02 23:02:54 分享评论

#2 2020-04-03 09:35:12 分享评论

- zzm24

- 会员

- 注册时间: 2018-05-07

- 已发帖子: 127

- 积分: 94

Re: F1C100S使用主线uboot如何更改默认终端串口

suniv.dtsi

line124

uart0_pins_a: uart-pins-pe {

pins = "PE0", "PE1";

function = "uart0";

};

uart1_pins_a: uart-pins-pa {

pins = "PA2", "PA3";

function = "uart1";

};

u-boot\arch\arm\mach-sunxi\board.c

line86

#elif CONFIG_CONS_INDEX == 2 && defined(CONFIG_MACH_SUNIV)

sunxi_gpio_set_cfgpin(SUNXI_GPA(2), SUNIV_GPE_UART0);

sunxi_gpio_set_cfgpin(SUNXI_GPA(3), SUNIV_GPE_UART0);

sunxi_gpio_set_pull(SUNXI_GPA(3), SUNXI_GPIO_PULL_UP);

之前花了一点时间改了一下,希望帮得上忙

离线

#3 2020-04-03 11:27:59 分享评论

- ubuntu

- 会员

- 注册时间: 2020-03-30

- 已发帖子: 329

- 积分: 307

Re: F1C100S使用主线uboot如何更改默认终端串口

这个文件 include/configs/suniv.h 还得加上:

#define CONFIG_CONS_INDEX 1 //UART0

#define CONFIG_CONS_INDEX 2 //UART1

#define CONFIG_CONS_INDEX 3 //UART2

离线

#4 2020-04-03 11:41:37 分享评论

- ubuntu

- 会员

- 注册时间: 2020-03-30

- 已发帖子: 329

- 积分: 307

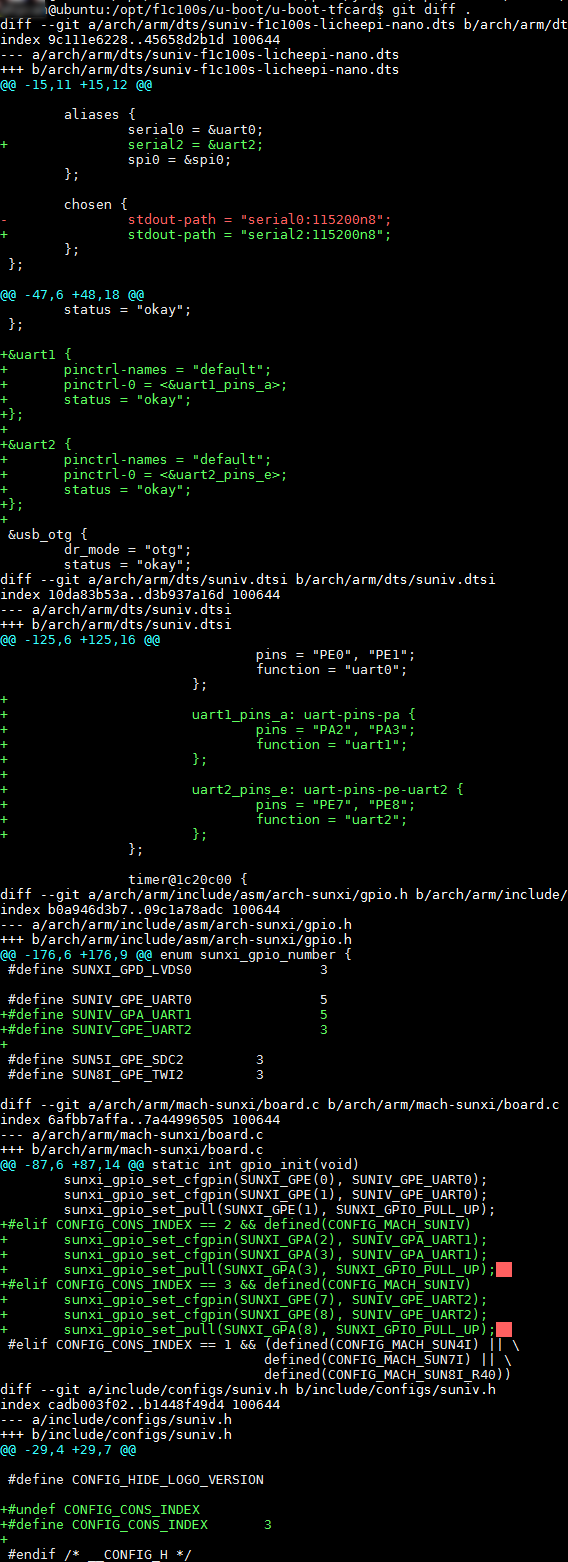

Re: F1C100S使用主线uboot如何更改默认终端串口

diff --git a/arch/arm/dts/suniv.dtsi b/arch/arm/dts/suniv.dtsi

index 10da83b53a..9dd95f38e1 100644

--- a/arch/arm/dts/suniv.dtsi

+++ b/arch/arm/dts/suniv.dtsi

@@ -125,6 +125,16 @@

pins = "PE0", "PE1";

function = "uart0";

};

+

+ uart1_pins_a: uart-pins-pa {

+ pins = "PA2", "PA3";

+ function = "uart1";

+ };

+

+ uart2_pins_a: uart-pins-pe-uart2 {

+ pins = "PE7", "PE8";

+ function = "uart2";

+ };

};

timer@1c20c00 {

diff --git a/arch/arm/include/asm/arch-sunxi/gpio.h b/arch/arm/include/asm/arch-sunxi/gpio.h

index b0a946d3b7..09c1a78adc 100644

--- a/arch/arm/include/asm/arch-sunxi/gpio.h

+++ b/arch/arm/include/asm/arch-sunxi/gpio.h

@@ -176,6 +176,9 @@ enum sunxi_gpio_number {

#define SUNXI_GPD_LVDS0 3

#define SUNIV_GPE_UART0 5

+#define SUNIV_GPA_UART1 5

+#define SUNIV_GPE_UART2 3

+

#define SUN5I_GPE_SDC2 3

#define SUN8I_GPE_TWI2 3

diff --git a/arch/arm/mach-sunxi/board.c b/arch/arm/mach-sunxi/board.c

index 6afbb7affa..7a44996505 100644

--- a/arch/arm/mach-sunxi/board.c

+++ b/arch/arm/mach-sunxi/board.c

@@ -87,6 +87,14 @@ static int gpio_init(void)

sunxi_gpio_set_cfgpin(SUNXI_GPE(0), SUNIV_GPE_UART0);

sunxi_gpio_set_cfgpin(SUNXI_GPE(1), SUNIV_GPE_UART0);

sunxi_gpio_set_pull(SUNXI_GPE(1), SUNXI_GPIO_PULL_UP);

+#elif CONFIG_CONS_INDEX == 2 && defined(CONFIG_MACH_SUNIV)

+ sunxi_gpio_set_cfgpin(SUNXI_GPA(2), SUNIV_GPA_UART1);

+ sunxi_gpio_set_cfgpin(SUNXI_GPA(3), SUNIV_GPA_UART1);

+ sunxi_gpio_set_pull(SUNXI_GPA(3), SUNXI_GPIO_PULL_UP);

+#elif CONFIG_CONS_INDEX == 3 && defined(CONFIG_MACH_SUNIV)

+ sunxi_gpio_set_cfgpin(SUNXI_GPE(7), SUNIV_GPE_UART2);

+ sunxi_gpio_set_cfgpin(SUNXI_GPE(8), SUNIV_GPE_UART2);

+ sunxi_gpio_set_pull(SUNXI_GPA(8), SUNXI_GPIO_PULL_UP);

#elif CONFIG_CONS_INDEX == 1 && (defined(CONFIG_MACH_SUN4I) || \

defined(CONFIG_MACH_SUN7I) || \

defined(CONFIG_MACH_SUN8I_R40))

diff --git a/include/configs/suniv.h b/include/configs/suniv.h

index cadb003f02..b1448f49d4 100644

--- a/include/configs/suniv.h

+++ b/include/configs/suniv.h

@@ -29,4 +29,7 @@

#define CONFIG_HIDE_LOGO_VERSION

+#undef CONFIG_CONS_INDEX

+#define CONFIG_CONS_INDEX 3

+

#endif /* __CONFIG_H */从 UART2(PE7/PE8)输出, 刚刚改完, 还没测试呢, 可能有坑。

离线

#5 2020-04-03 15:22:13 分享评论

- ubuntu

- 会员

- 注册时间: 2020-03-30

- 已发帖子: 329

- 积分: 307

Re: F1C100S使用主线uboot如何更改默认终端串口

#define CONFIG_CONS_INDEX 1 //UART0

#define CONFIG_CONS_INDEX 2 //UART1

#define CONFIG_CONS_INDEX 3 //UART2

改这个只能影响u-boot 的 spl 串口输出, 如果u-boot输出还得改 dts 文件:

diff --git a/arch/arm/dts/suniv-f1c100s-licheepi-nano.dts b/arch/arm/dts/suniv-f1c100s-licheepi-nano.dts

index 9c111e6228..45658d2b1d 100644

--- a/arch/arm/dts/suniv-f1c100s-licheepi-nano.dts

+++ b/arch/arm/dts/suniv-f1c100s-licheepi-nano.dts

@@ -15,11 +15,12 @@

aliases {

serial0 = &uart0;

+ serial2 = &uart2;

spi0 = &spi0;

};

chosen {

- stdout-path = "serial0:115200n8";

+ stdout-path = "serial2:115200n8";

};

};

@@ -47,6 +48,18 @@

status = "okay";

};

+&uart1 {

+ pinctrl-names = "default";

+ pinctrl-0 = <&uart1_pins_a>;

+ status = "okay";

+};

+

+&uart2 {

+ pinctrl-names = "default";

+ pinctrl-0 = <&uart2_pins_e>;

+ status = "okay";

+};

+

&usb_otg {

dr_mode = "otg";

status = "okay";

diff --git a/arch/arm/dts/suniv.dtsi b/arch/arm/dts/suniv.dtsi

index 10da83b53a..d3b937a16d 100644

--- a/arch/arm/dts/suniv.dtsi

+++ b/arch/arm/dts/suniv.dtsi

@@ -125,6 +125,16 @@

pins = "PE0", "PE1";

function = "uart0";

};

+

+ uart1_pins_a: uart-pins-pa {

+ pins = "PA2", "PA3";

+ function = "uart1";

+ };

+

+ uart2_pins_e: uart-pins-pe-uart2 {

+ pins = "PE7", "PE8";

+ function = "uart2";

+ };

};

timer@1c20c00 {

diff --git a/arch/arm/include/asm/arch-sunxi/gpio.h b/arch/arm/include/asm/arch-sunxi/gpio.h

index b0a946d3b7..09c1a78adc 100644

--- a/arch/arm/include/asm/arch-sunxi/gpio.h

+++ b/arch/arm/include/asm/arch-sunxi/gpio.h

@@ -176,6 +176,9 @@ enum sunxi_gpio_number {

#define SUNXI_GPD_LVDS0 3

#define SUNIV_GPE_UART0 5

+#define SUNIV_GPA_UART1 5

+#define SUNIV_GPE_UART2 3

+

#define SUN5I_GPE_SDC2 3

#define SUN8I_GPE_TWI2 3

diff --git a/arch/arm/mach-sunxi/board.c b/arch/arm/mach-sunxi/board.c

index 6afbb7affa..7a44996505 100644

--- a/arch/arm/mach-sunxi/board.c

+++ b/arch/arm/mach-sunxi/board.c

@@ -87,6 +87,14 @@ static int gpio_init(void)

sunxi_gpio_set_cfgpin(SUNXI_GPE(0), SUNIV_GPE_UART0);

sunxi_gpio_set_cfgpin(SUNXI_GPE(1), SUNIV_GPE_UART0);

sunxi_gpio_set_pull(SUNXI_GPE(1), SUNXI_GPIO_PULL_UP);

+#elif CONFIG_CONS_INDEX == 2 && defined(CONFIG_MACH_SUNIV)

+ sunxi_gpio_set_cfgpin(SUNXI_GPA(2), SUNIV_GPA_UART1);

+ sunxi_gpio_set_cfgpin(SUNXI_GPA(3), SUNIV_GPA_UART1);

+ sunxi_gpio_set_pull(SUNXI_GPA(3), SUNXI_GPIO_PULL_UP);

+#elif CONFIG_CONS_INDEX == 3 && defined(CONFIG_MACH_SUNIV)

+ sunxi_gpio_set_cfgpin(SUNXI_GPE(7), SUNIV_GPE_UART2);

+ sunxi_gpio_set_cfgpin(SUNXI_GPE(8), SUNIV_GPE_UART2);

+ sunxi_gpio_set_pull(SUNXI_GPA(8), SUNXI_GPIO_PULL_UP);

#elif CONFIG_CONS_INDEX == 1 && (defined(CONFIG_MACH_SUN4I) || \

defined(CONFIG_MACH_SUN7I) || \

defined(CONFIG_MACH_SUN8I_R40))

diff --git a/include/configs/suniv.h b/include/configs/suniv.h

index cadb003f02..b1448f49d4 100644

--- a/include/configs/suniv.h

+++ b/include/configs/suniv.h

@@ -29,4 +29,7 @@

#define CONFIG_HIDE_LOGO_VERSION

+#undef CONFIG_CONS_INDEX

+#define CONFIG_CONS_INDEX 3

+

从 UART2(PE7/PE8)输出搞定!

离线

楼主 #6 2020-04-03 21:47:09 分享评论

楼主 #7 2020-04-03 22:09:10 分享评论

#8 2020-04-16 15:52:13 分享评论

- lihanchao90

- 会员

- 注册时间: 2020-04-06

- 已发帖子: 1

- 积分: 1

Re: F1C100S使用主线uboot如何更改默认终端串口

和u-boot 类似修改dts

diff --git a/arch/arm/boot/dts/suniv-f1c100s-licheepi-nano.dts b/arch/arm/boot/dts/suniv-f1c100s-licheepi-nano.dts

index f46e190..c31e4ea 100644

--- a/arch/arm/boot/dts/suniv-f1c100s-licheepi-nano.dts

+++ b/arch/arm/boot/dts/suniv-f1c100s-licheepi-nano.dts

@@ -7,7 +7,8 @@

#include "suniv-f1c100s.dtsi"

#include <dt-bindings/gpio/gpio.h>

-

+#include <dt-bindings/input/input.h>

+#include <dt-bindings/interrupt-controller/irq.h>

/ {

model = "Lichee Pi Nano";

compatible = "licheepi,licheepi-nano", "allwinner,suniv-f1c100s",

@@ -15,11 +16,12 @@

aliases {

serial0 = &uart0;

+ serial1 = &uart1;

spi0 = &spi0;

};

chosen {

- stdout-path = "serial0:115200n8";

+ stdout-path = "serial1:115200n8";

};

panel: panel {

@@ -67,13 +69,52 @@

pinctrl-names = "default";

pinctrl-0 = <&spi0_pins_a>;

status = "okay";

-

- flash@0 {

+ spi-max-frequency = <50000000>;

+ flash: w25q128@0 {

#address-cells = <1>;

#size-cells = <1>;

compatible = "winbond,w25q128", "jedec,spi-nor";

reg = <0>;

- spi-max-frequency = <40000000>;

+ spi-max-frequency = <50000000>;

+ partitions {

+ compatible = "fixed-partitions";

+ #address-cells = <1>;

+ #size-cells = <1>;

+

+ partition@0 {

+ label = "u-boot";

+ reg = <0x000000 0x100000>;

+ read-only;

+ };

+

+ partition@100000 {

+ label = "dtb";

+ reg = <0x100000 0x10000>;

+ read-only;

+ };

+

+ partition@110000 {

+ label = "kernel";

+ reg = <0x110000 0x400000>;

+ read-only;

+ };

+

+ partition@510000 {

+ label = "rootfs";

+ reg = <0x510000 0xAF0000>;

+ };

+ };

+ };

+};

+

+&i2c0 {

+ pinctrl-0 = <&i2c0_pins>;

+ pinctrl-names = "default";

+ status = "okay";

+

+ ns2009: ns2009@48 {

+ compatible = "nsiway,ns2009";

+ reg = <0x48>;

};

};

@@ -95,7 +136,11 @@

pinctrl-0 = <&uart0_pins_a>;

status = "okay";

};

-

+&uart1 {

+ pinctrl-names = "default";

+ pinctrl-0 = <&uart1_pins_a>;

+ status = "okay";

+};

&usb_otg {

dr_mode = "otg";

status = "okay";

diff --git a/arch/arm/boot/dts/suniv.dtsi b/arch/arm/boot/dts/suniv.dtsi

index ee600cd..d0d2fc7 100644

--- a/arch/arm/boot/dts/suniv.dtsi

+++ b/arch/arm/boot/dts/suniv.dtsi

@@ -228,12 +228,18 @@

"PD20", "PD21";

function = "lcd";

};

-

+ i2c0_pins: i2c0 {

+ pins = "PD12", "PD0";

+ function = "i2c0";

+ };

uart0_pins_a: uart-pins-pe {

pins = "PE0", "PE1";

function = "uart0";

};

-

+ uart1_pins_a: uart-pins-pa {

+ pins = "PA2", "PA3";

+ function = "uart1";

+ };

mmc0_pins: mmc0-pins {

pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5";

function = "mmc0";

@@ -284,6 +290,18 @@

resets = <&ccu RST_BUS_UART2>;

status = "disabled";

};

+ i2c0: i2c@1c27000 {

+ compatible = "allwinner,sun6i-a31-i2c";

+ reg = <0x01C27000 0x400>;

+ interrupts = <7>;

+ clocks = <&ccu CLK_BUS_I2C0>;

+ resets = <&ccu RST_BUS_I2C0>;

+ pinctrl-names = "default";

+ pinctrl-0 = <&i2c0_pins>;

+ status = "disabled";

+ #address-cells = <1>;

+ #size-cells = <0>;

+ };

usb_otg: usb@1c13000 {

compatible = "allwinner,suniv-musb";

diff --git a/drivers/mtd/spi-nor/spi-nor.c b/drivers/mtd/spi-nor/spi-nor.c

index bc266f7..99dc551 100644

--- a/drivers/mtd/spi-nor/spi-nor.c

+++ b/drivers/mtd/spi-nor/spi-nor.c

@@ -1182,7 +1182,7 @@ static const struct flash_info spi_nor_ids[] = {

},

{ "w25q80", INFO(0xef5014, 0, 64 * 1024, 16, SECT_4K) },

{ "w25q80bl", INFO(0xef4014, 0, 64 * 1024, 16, SECT_4K) },

- { "w25q128", INFO(0xef4018, 0, 64 * 1024, 256, SECT_4K) },

+ { "w25q128", INFO(0xef4018, 0, 64 * 1024, 256, 0) },

{ "w25q256", INFO(0xef4019, 0, 64 * 1024, 512, SECT_4K | SPI_NOR_DUAL_READ | SPI_NOR_QUAD_READ) },

{ "w25m512jv", INFO(0xef7119, 0, 64 * 1024, 1024,

SECT_4K | SPI_NOR_QUAD_READ | SPI_NOR_DUAL_READ) }, 离线

#9 2020-04-17 11:23:33 分享评论

- MK-2020

- 会员

- 注册时间: 2020-01-02

- 已发帖子: 51

- 积分: 46

Re: F1C100S使用主线uboot如何更改默认终端串口

U-BOOT改好了,参数好像会直接传递到内核,所以内核那边是不需要去改的。只停在start kernel可能是原来传递的是ttyS0,你没改到ttyS1.

离线

#10 2021-11-29 20:17:21 分享评论

- somnus

- 会员

- 注册时间: 2021-11-29

- 已发帖子: 17

- 积分: 2

Re: F1C100S使用主线uboot如何更改默认终端串口

离线

- 不通过:其他

#11 2021-11-30 12:25:38 分享评论

- zh_tao518

- 会员

- 注册时间: 2021-04-17

- 已发帖子: 6

- 积分: 1

Re: F1C100S使用主线uboot如何更改默认终端串口

U-BOOT改好了,参数好像会直接传递到内核,所以内核那边是不需要去改的。只停在start kernel可能是原来传递的是ttyS0,你没改到ttyS1.

应该是正解

离线

#12 2022-03-17 15:48:24 分享评论

- Sam

- 会员

- 注册时间: 2019-12-06

- 已发帖子: 55

- 积分: 50

Re: F1C100S使用主线uboot如何更改默认终端串口

@迪卡

能分享下教程么?我想我串口2打印日志,BSP LINUX3.10 修改fex文件和uboot都不好使,现在想用主线UBOOT引导BSP来实现,但是不知道怎么实现

离线

#14 2023-12-22 13:54:26 分享评论

- wei

- 会员

- 注册时间: 2023-08-24

- 已发帖子: 1

- 积分: 1

Re: F1C100S使用主线uboot如何更改默认终端串口

只更改rootfs中的/etc/inittab里的还是不行,只停在start kernel

后来解决了吗

离线

#15 2024-03-02 23:22:56 分享评论

- future

- 会员

- 注册时间: 2021-11-28

- 已发帖子: 49

- 积分: 26

Re: F1C100S使用主线uboot如何更改默认终端串口

楼主可以整理一下主线u-boot修改的步骤吗。

离线

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发