楼主 #1 2020-04-21 12:08:04 分享评论

- aodzip

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 130

- 积分: 100

Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

白嫖: https://github.com/aodzip/u-boot/tree/Allwinner-S3

可能是S3目前最好用的u-boot了

支持LCD,支持以太网,支持USB Gadget

LCD演示:

Fastboot演示:

./fel-flash.sh

sunxi-fel -p uboot output/images/u-boot-sunxi-with-spl.bin

fastboot oem format

fastboot flash loader output/images/u-boot-sunxi-with-spl.bin

fastboot flash esp output/images/boot.vfat

fastboot flash system output/images/rootfs.ext4

fastboot reboot以下是 @哇酷小二 2020-04-30 整理的修改记录:

-------------------------------------------------

https://github.com/u-boot/u-boot/commit/e4837da7828293ea49abc579f939c0f5c4b127c3

git diff e4837da7828293ea49abc579f939c0f5c4b127c3 c8aac3e1734b87c2800c05fd5428f3aae8d8ae73 > ~/uboot_s3_aodzip.diff

diff --git a/Kconfig b/Kconfig

index 8bae87e3f6..cc625d0253 100644

--- a/Kconfig

+++ b/Kconfig

@@ -589,9 +589,9 @@ config HAVE_SYS_TEXT_BASE

config SYS_TEXT_BASE

depends on HAVE_SYS_TEXT_BASE

default 0x80800000 if ARCH_OMAP2PLUS || ARCH_K3

- default 0x4a000000 if ARCH_SUNXI && !MACH_SUN9I && !MACH_SUN8I_V3S

+ default 0x4a000000 if ARCH_SUNXI && !MACH_SUN9I && (!MACH_SUN8I_V3S || !MACH_SUN8I_S3)

default 0x2a000000 if ARCH_SUNXI && MACH_SUN9I

- default 0x42e00000 if ARCH_SUNXI && MACH_SUN8I_V3S

+ default 0x42e00000 if ARCH_SUNXI && (MACH_SUN8I_V3S || MACH_SUN8I_S3)

hex "Text Base"

help

The address in memory that U-Boot will be running from, initially.

diff --git a/arch/arm/dts/Makefile b/arch/arm/dts/Makefile

index bb979550c4..bbe1887623 100644

--- a/arch/arm/dts/Makefile

+++ b/arch/arm/dts/Makefile

@@ -546,7 +546,9 @@ dtb-$(CONFIG_MACH_SUN8I_R40) += \

sun8i-r40-bananapi-m2-ultra.dtb \

sun8i-v40-bananapi-m2-berry.dtb

dtb-$(CONFIG_MACH_SUN8I_V3S) += \

- sun8i-v3s-licheepi-zero.dtb

+ sun8i-v3s-licheepi-zero.dtb

+dtb-$(CONFIG_MACH_SUN8I_S3) += \

+ sun8i-s3-generic.dtb

dtb-$(CONFIG_MACH_SUN50I_H5) += \

sun50i-h5-bananapi-m2-plus.dtb \

sun50i-h5-emlid-neutis-n5-devboard.dtb \

diff --git a/arch/arm/dts/sun8i-s3-generic.dts b/arch/arm/dts/sun8i-s3-generic.dts

new file mode 100644

index 0000000000..c1aac3d5d4

--- /dev/null

+++ b/arch/arm/dts/sun8i-s3-generic.dts

@@ -0,0 +1,135 @@

+/*

+ * Copyright (C) 2020 Aodzip <aodzip@gmail.com>

+ *

+ * This file is dual-licensed: you can use it either under the terms

+ * of the GPL or the X11 license, at your option. Note that this dual

+ * licensing only applies to this file, and not this project as a

+ * whole.

+ *

+ * a) This file is free software; you can redistribute it and/or

+ * modify it under the terms of the GNU General Public License as

+ * published by the Free Software Foundation; either version 2 of the

+ * License, or (at your option) any later version.

+ *

+ * This file is distributed in the hope that it will be useful,

+ * but WITHOUT ANY WARRANTY; without even the implied warranty of

+ * MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

+ * GNU General Public License for more details.

+ *

+ * Or, alternatively,

+ *

+ * b) Permission is hereby granted, free of charge, to any person

+ * obtaining a copy of this software and associated documentation

+ * files (the "Software"), to deal in the Software without

+ * restriction, including without limitation the rights to use,

+ * copy, modify, merge, publish, distribute, sublicense, and/or

+ * sell copies of the Software, and to permit persons to whom the

+ * Software is furnished to do so, subject to the following

+ * conditions:

+ *

+ * The above copyright notice and this permission notice shall be

+ * included in all copies or substantial portions of the Software.

+ *

+ * THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND,

+ * EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES

+ * OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND

+ * NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT

+ * HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY,

+ * WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING

+ * FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR

+ * OTHER DEALINGS IN THE SOFTWARE.

+ */

+

+/dts-v1/;

+#include "sun8i-s3.dtsi"

+#include "sunxi-common-regulators.dtsi"

+

+/ {

+ model = "Allwinner S3 Generic Device";

+ compatible = "allwinner,sun8i-s3";

+

+ aliases {

+ serial0 = &uart0;

+ };

+

+ chosen {

+ stdout-path = "serial0:115200n8";

+ };

+

+ backlight: backlight {

+ compatible = "pwm-backlight";

+ pwms = <&pwm 0 50000 0>;

+ brightness-levels = <0 2 4 8 16 32 64 128 255>;

+ default-brightness-level = <8>;

+ };

+

+ panel-rgb@0 {

+ compatible = "simple-panel";

+ backlight = <&backlight>;

+

+ display-timings {

+ timing@0 {

+ clock-frequency = <50000000>;

+ hactive = <480>;

+ vactive = <272>;

+ hfront-porch = <2>;

+ hback-porch = <2>;

+ hsync-len = <41>;

+ vfront-porch = <2>;

+ vback-porch = <2>;

+ vsync-len = <10>;

+ hsync-active = <0>;

+ vsync-active = <0>;

+ de-active = <0>;

+ pixelclk-active = <1>;

+ };

+ };

+ };

+};

+

+&emac {

+ phy-handle = <&int_mii_phy>;

+ phy-mode = "mii";

+ allwinner,use-internal-phy;

+ status = "okay";

+};

+

+&mmc0 {

+ bus-width = <4>;

+ status = "okay";

+};

+

+&mmc2 {

+ non-removable;

+ max-speed = <20000000>;

+ bus-width = <8>;

+ status = "okay";

+};

+

+&spi0 {

+ status = "disabled";

+};

+

+&uart0 {

+ status = "okay";

+};

+

+&usb_otg {

+ status = "okay";

+};

+

+&usbphy {

+ status = "okay";

+};

+

+&ehci0 {

+ status = "okay";

+};

+

+&ohci0 {

+ status = "okay";

+};

+

+&pwm {

+ status = "okay";

+};

diff --git a/arch/arm/dts/sun8i-s3.dtsi b/arch/arm/dts/sun8i-s3.dtsi

new file mode 100644

index 0000000000..282aadff11

--- /dev/null

+++ b/arch/arm/dts/sun8i-s3.dtsi

@@ -0,0 +1,157 @@

+/*

+ * Copyright (C) 2020 Aodzip <aodzip@gmail.com>

+ *

+ * This file is dual-licensed: you can use it either under the terms

+ * of the GPL or the X11 license, at your option. Note that this dual

+ * licensing only applies to this file, and not this project as a

+ * whole.

+ *

+ * a) This file is free software; you can redistribute it and/or

+ * modify it under the terms of the GNU General Public License as

+ * published by the Free Software Foundation; either version 2 of the

+ * License, or (at your option) any later version.

+ *

+ * This file is distributed in the hope that it will be useful,

+ * but WITHOUT ANY WARRANTY; without even the implied warranty of

+ * MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

+ * GNU General Public License for more details.

+ *

+ * Or, alternatively,

+ *

+ * b) Permission is hereby granted, free of charge, to any person

+ * obtaining a copy of this software and associated documentation

+ * files (the "Software"), to deal in the Software without

+ * restriction, including without limitation the rights to use,

+ * copy, modify, merge, publish, distribute, sublicense, and/or

+ * sell copies of the Software, and to permit persons to whom the

+ * Software is furnished to do so, subject to the following

+ * conditions:

+ *

+ * The above copyright notice and this permission notice shall be

+ * included in all copies or substantial portions of the Software.

+ *

+ * THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND,

+ * EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES

+ * OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND

+ * NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT

+ * HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY,

+ * WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING

+ * FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR

+ * OTHER DEALINGS IN THE SOFTWARE.

+ */

+/dts-v1/;

+#include "sun8i-v3s.dtsi"

+#include "sunxi-common-regulators.dtsi"

+#include <dt-bindings/input/input.h>

+

+/ {

+ #address-cells = <1>;

+ #size-cells = <1>;

+ interrupt-parent = <&gic>;

+

+ soc {

+ compatible = "simple-bus";

+ #address-cells = <1>;

+ #size-cells = <1>;

+ ranges;

+

+ syscon: syscon@1c00000 {

+ compatible = "allwinner,sun8i-v3s-system-controller", "allwinner,sun8i-h3-system-control", "syscon";

+ reg = <0x01c00000 0x1000>;

+ };

+

+ emac: ethernet@1c30000 {

+ compatible = "allwinner,sun8i-h3-emac";

+ syscon = <&syscon>;

+ reg = <0x01c30000 0x10000>;

+ interrupts = <GIC_SPI 82 IRQ_TYPE_LEVEL_HIGH>;

+ interrupt-names = "macirq";

+ resets = <&ccu RST_BUS_EMAC>;

+ reset-names = "stmmaceth";

+ clocks = <&ccu CLK_BUS_EMAC>;

+ clock-names = "stmmaceth";

+ status = "disabled";

+

+ mdio: mdio {

+ #address-cells = <1>;

+ #size-cells = <0>;

+ compatible = "snps,dwmac-mdio";

+ };

+

+ mdio-mux {

+ compatible = "allwinner,sun8i-h3-mdio-mux";

+ #address-cells = <1>;

+ #size-cells = <0>;

+

+ mdio-parent-bus = <&mdio>;

+ /* Only one MDIO is usable at the time */

+ internal_mdio: mdio@1 {

+ compatible = "allwinner,sun8i-h3-mdio-internal";

+ reg = <1>;

+ #address-cells = <1>;

+ #size-cells = <0>;

+

+ int_mii_phy: ethernet-phy@1 {

+ compatible = "ethernet-phy-ieee802.3-c22";

+ reg = <1>;

+ clocks = <&ccu CLK_BUS_EPHY>;

+ resets = <&ccu RST_BUS_EPHY>;

+ };

+ };

+

+ external_mdio: mdio@2 {

+ reg = <2>;

+ #address-cells = <1>;

+ #size-cells = <0>;

+ };

+ };

+ };

+

+ ehci0: usb@01c1a000 {

+ compatible = "allwinner,sun8i-v3s-ehci", "generic-ehci";

+ reg = <0x01c1a000 0x100>;

+ interrupts = <GIC_SPI 72 IRQ_TYPE_LEVEL_HIGH>;

+ clocks = <&ccu CLK_BUS_EHCI0>, <&ccu CLK_BUS_OHCI0>;

+ resets = <&ccu RST_BUS_EHCI0>, <&ccu RST_BUS_OHCI0>;

+ status = "disabled";

+ };

+

+ ohci0: usb@01c1a400 {

+ compatible = "allwinner,sun8i-v3s-ohci", "generic-ohci";

+ reg = <0x01c1a400 0x100>;

+ interrupts = <GIC_SPI 73 IRQ_TYPE_LEVEL_HIGH>;

+ clocks = <&ccu CLK_BUS_EHCI0>, <&ccu CLK_BUS_OHCI0>, <&ccu CLK_USB_OHCI0>;

+ resets = <&ccu RST_BUS_EHCI0>, <&ccu RST_BUS_OHCI0>;

+ status = "disabled";

+ };

+

+ spi0: spi@1c68000 {

+ compatible = "allwinner,sun8i-h3-spi";

+ reg = <0x01c68000 0x1000>;

+ interrupts = <GIC_SPI 65 IRQ_TYPE_LEVEL_HIGH>;

+ clocks = <&ccu CLK_BUS_SPI0>, <&ccu CLK_SPI0>;

+ clock-names = "ahb", "mod";

+ resets = <&ccu RST_BUS_SPI0>;

+ status = "disabled";

+ #address-cells = <1>;

+ #size-cells = <0>;

+ };

+

+ pwm: pwm@1c21400 {

+ compatible = "allwinner,sun5i-a13-pwm";

+ reg = <0x01c21400 0x8>;

+ clocks = <&osc24M>;

+ #pwm-cells = <3>;

+ status = "disabled";

+ };

+ };

+};

+

+&usb_otg {

+ phys = <&usbphy>;

+ extcon = <&usbphy>;

+};

+

+&usbphy {

+ #phy-cells = <0>;

+};

diff --git a/arch/arm/include/asm/arch-sunxi/clock_sun6i.h b/arch/arm/include/asm/arch-sunxi/clock_sun6i.h

index ee387127f3..8001a81b8f 100644

--- a/arch/arm/include/asm/arch-sunxi/clock_sun6i.h

+++ b/arch/arm/include/asm/arch-sunxi/clock_sun6i.h

@@ -333,9 +333,14 @@ struct sunxi_ccm_reg {

#define AHB_GATE_OFFSET_LCD1 5

#define AHB_GATE_OFFSET_LCD0 4

#else

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

+#define AHB_GATE_OFFSET_LCD1 5

+#define AHB_GATE_OFFSET_LCD0 4

+#else

#define AHB_GATE_OFFSET_LCD1 4

#define AHB_GATE_OFFSET_LCD0 3

#endif

+#endif

#define CCM_NAND_CTRL_M(x) ((x) - 1)

#define CCM_NAND_CTRL_N(x) ((x) << 16)

@@ -480,9 +485,14 @@ struct sunxi_ccm_reg {

#define AHB_RESET_OFFSET_LCD1 5

#define AHB_RESET_OFFSET_LCD0 4

#else

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

+#define AHB_RESET_OFFSET_LCD1 5

+#define AHB_RESET_OFFSET_LCD0 4

+#else

#define AHB_RESET_OFFSET_LCD1 4

#define AHB_RESET_OFFSET_LCD0 3

#endif

+#endif

/* ahb_reset2 offsets */

#define AHB_RESET_OFFSET_EPHY 2

@@ -508,7 +518,12 @@ struct sunxi_ccm_reg {

/* CCM bits common to all Display Engine 2.0 clock ctrl regs */

#define CCM_DE2_CTRL_M(n) ((((n) - 1) & 0xf) << 0)

#define CCM_DE2_CTRL_PLL_MASK (3 << 24)

+

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

+#define CCM_DE2_CTRL_PLL6_2X (2 << 24)

+#else

#define CCM_DE2_CTRL_PLL6_2X (0 << 24)

+#endif

#define CCM_DE2_CTRL_PLL10 (1 << 24)

#define CCM_DE2_CTRL_GATE (0x1 << 31)

diff --git a/arch/arm/include/asm/arch-sunxi/display2.h b/arch/arm/include/asm/arch-sunxi/display2.h

index 7202d2756c..ad3a81dbde 100644

--- a/arch/arm/include/asm/arch-sunxi/display2.h

+++ b/arch/arm/include/asm/arch-sunxi/display2.h

@@ -137,4 +137,12 @@ struct de_csc {

#define SUNXI_DE2_WH(w, h) (((h - 1) << 16) | (w - 1))

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

+ #define SUNXI_DE2_MUX_CHAN_SZ_COUNT 2

+ #define SUNXI_DE2_BLD_ROUTE 2

+#else

+ #define SUNXI_DE2_MUX_CHAN_SZ_COUNT 1

+ #define SUNXI_DE2_BLD_ROUTE 1

+#endif

+

#endif /* _SUNXI_DISPLAY2_H */

diff --git a/arch/arm/mach-sunxi/Kconfig b/arch/arm/mach-sunxi/Kconfig

index be0822bfb7..b7cb87a98f 100644

--- a/arch/arm/mach-sunxi/Kconfig

+++ b/arch/arm/mach-sunxi/Kconfig

@@ -262,7 +262,18 @@ config MACH_SUN8I_V3S

select SUNXI_DRAM_DW

select SUNXI_DRAM_DW_16BIT

select SUPPORT_SPL

- select ARMV7_BOOT_SEC_DEFAULT if OLD_SUNXI_KERNEL_COMPAT

+

+config MACH_SUN8I_S3

+ bool "sun8i (Allwinner S3)"

+ select CPU_V7A

+ select CPU_V7_HAS_NONSEC

+ select CPU_V7_HAS_VIRT

+ select ARCH_SUPPORT_PSCI

+ select SUNXI_GEN_SUN6I

+ select SUNXI_DRAM_DW

+ select SUNXI_DRAM_DW_16BIT

+ select SUPPORT_SPL

+ select SUNXI_DE2

config MACH_SUN9I

bool "sun9i (Allwinner A80)"

@@ -321,6 +332,7 @@ config MACH_SUN8I

default y if MACH_SUNXI_H3_H5

default y if MACH_SUN8I_R40

default y if MACH_SUN8I_V3S

+ default y if MACH_SUN8I_S3

config RESERVE_ALLWINNER_BOOT0_HEADER

bool "reserve space for Allwinner boot0 header"

@@ -437,7 +449,7 @@ config DRAM_ZQ

default 123 if MACH_SUN4I || MACH_SUN5I || MACH_SUN6I || \

MACH_SUN8I_A23 || MACH_SUN8I_A33 || MACH_SUN8I_A83T

default 127 if MACH_SUN7I

- default 14779 if MACH_SUN8I_V3S

+ default 14779 if MACH_SUN8I_V3S || MACH_SUN8I_S3

default 3881979 if MACH_SUNXI_H3_H5 || MACH_SUN8I_R40 || MACH_SUN50I_H6

default 4145117 if MACH_SUN9I

default 3881915 if MACH_SUN50I

@@ -755,6 +767,7 @@ config VIDEO_SUNXI

depends on !MACH_SUNXI_H3_H5

depends on !MACH_SUN8I_R40

depends on !MACH_SUN8I_V3S

+ depends on !MACH_SUN8I_S3

depends on !MACH_SUN9I

depends on !MACH_SUN50I

depends on !MACH_SUN50I_H6

diff --git a/arch/arm/mach-sunxi/board.c b/arch/arm/mach-sunxi/board.c

index b487b265af..6aa28bbc3c 100644

--- a/arch/arm/mach-sunxi/board.c

+++ b/arch/arm/mach-sunxi/board.c

@@ -117,7 +117,7 @@ static int gpio_init(void)

sunxi_gpio_set_cfgpin(SUNXI_GPB(9), SUN8I_A83T_GPB_UART0);

sunxi_gpio_set_cfgpin(SUNXI_GPB(10), SUN8I_A83T_GPB_UART0);

sunxi_gpio_set_pull(SUNXI_GPB(10), SUNXI_GPIO_PULL_UP);

-#elif CONFIG_CONS_INDEX == 1 && defined(CONFIG_MACH_SUN8I_V3S)

+#elif CONFIG_CONS_INDEX == 1 && (defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3))

sunxi_gpio_set_cfgpin(SUNXI_GPB(8), SUN8I_V3S_GPB_UART0);

sunxi_gpio_set_cfgpin(SUNXI_GPB(9), SUN8I_V3S_GPB_UART0);

sunxi_gpio_set_pull(SUNXI_GPB(9), SUNXI_GPIO_PULL_UP);

diff --git a/arch/arm/mach-sunxi/cpu_info.c b/arch/arm/mach-sunxi/cpu_info.c

index ae4745bfec..060fbfc8a9 100644

--- a/arch/arm/mach-sunxi/cpu_info.c

+++ b/arch/arm/mach-sunxi/cpu_info.c

@@ -90,6 +90,8 @@ int print_cpuinfo(void)

printf("CPU: Allwinner R40 (SUN8I %04x)\n", sunxi_get_sram_id());

#elif defined CONFIG_MACH_SUN8I_V3S

printf("CPU: Allwinner V3s (SUN8I %04x)\n", sunxi_get_sram_id());

+#elif defined CONFIG_MACH_SUN8I_S3

+ printf("CPU: Allwinner S3 (SUN8I %04x)\n", sunxi_get_sram_id());

#elif defined CONFIG_MACH_SUN9I

puts("CPU: Allwinner A80 (SUN9I)\n");

#elif defined CONFIG_MACH_SUN50I

diff --git a/arch/arm/mach-sunxi/dram_sunxi_dw.c b/arch/arm/mach-sunxi/dram_sunxi_dw.c

index 85e7a1874e..43db624d8b 100644

--- a/arch/arm/mach-sunxi/dram_sunxi_dw.c

+++ b/arch/arm/mach-sunxi/dram_sunxi_dw.c

@@ -727,6 +727,9 @@ unsigned long sunxi_dram_init(void)

#elif defined(CONFIG_MACH_SUN8I_V3S)

/* TODO: set delays and mbus priority for V3s */

uint16_t socid = SOCID_H3;

+#elif defined(CONFIG_MACH_SUN8I_S3)

+ /* TODO: set delays and mbus priority for S3 */

+ uint16_t socid = SOCID_H3;

#elif defined(CONFIG_MACH_SUN50I)

uint16_t socid = SOCID_A64;

#elif defined(CONFIG_MACH_SUN50I_H5)

diff --git a/board/sunxi/board.c b/board/sunxi/board.c

index 6afea6ef42..769530412b 100644

--- a/board/sunxi/board.c

+++ b/board/sunxi/board.c

@@ -40,6 +40,7 @@

#include <spl.h>

#include <sy8106a.h>

#include <asm/setup.h>

+#include <splash.h>

#if defined CONFIG_VIDEO_LCD_PANEL_I2C && !(defined CONFIG_SPL_BUILD)

/* So that we can use pin names in Kconfig and sunxi_name_to_gpio() */

@@ -501,6 +502,13 @@ static void mmc_pinmux_setup(int sdc)

sunxi_gpio_set_pull(SUNXI_GPC(24), SUNXI_GPIO_PULL_UP);

sunxi_gpio_set_drv(SUNXI_GPC(24), 2);

#elif defined(CONFIG_MACH_SUN8I) || defined(CONFIG_MACH_SUN50I)

+#ifdef CONFIG_MACH_SUN8I_S3

+ for (pin = SUNXI_GPC(0); pin <= SUNXI_GPC(10); pin++) {

+ sunxi_gpio_set_cfgpin(pin, 2);

+ sunxi_gpio_set_pull(pin, SUNXI_GPIO_PULL_UP);

+ sunxi_gpio_set_drv(pin, 2);

+ }

+#else

/* SDC2: PC5-PC6, PC8-PC16 */

for (pin = SUNXI_GPC(5); pin <= SUNXI_GPC(6); pin++) {

sunxi_gpio_set_cfgpin(pin, SUNXI_GPC_SDC2);

@@ -513,6 +521,7 @@ static void mmc_pinmux_setup(int sdc)

sunxi_gpio_set_pull(pin, SUNXI_GPIO_PULL_UP);

sunxi_gpio_set_drv(pin, 2);

}

+#endif

#elif defined(CONFIG_MACH_SUN50I_H6)

/* SDC2: PC4-PC14 */

for (pin = SUNXI_GPC(4); pin <= SUNXI_GPC(14); pin++) {

@@ -916,3 +925,41 @@ int board_fit_config_name_match(const char *name)

return strcmp(name, cmp_str);

}

#endif

+

+#ifdef CONFIG_SPLASH_SCREEN

+static struct splash_location sunxi_splash_locations[] = {

+ {

+ .name = "mmc0_fs",

+ .storage = SPLASH_STORAGE_MMC,

+ .flags = SPLASH_STORAGE_FS,

+ .devpart = "0:1",

+ },

+ {

+ .name = "mmc1_fs",

+ .storage = SPLASH_STORAGE_MMC,

+ .flags = SPLASH_STORAGE_FS,

+ .devpart = "1:1",

+ },

+};

+

+int splash_screen_prepare(void)

+{

+ return splash_source_load(sunxi_splash_locations,

+ ARRAY_SIZE(sunxi_splash_locations));

+}

+

+int initr_env_dynamic_default(void)

+{

+ uint boot = sunxi_get_boot_device();

+ switch (boot) {

+ case BOOT_DEVICE_MMC1:

+ env_set("splashsource", "mmc0_fs");

+ break;

+ case BOOT_DEVICE_MMC2:

+ env_set("splashsource", "mmc1_fs");

+ break;

+ }

+ return 0;

+}

+

+#endif

diff --git a/common/board_r.c b/common/board_r.c

index 0bbeaa7594..949169895d 100644

--- a/common/board_r.c

+++ b/common/board_r.c

@@ -777,6 +777,9 @@ static init_fnc_t init_sequence_r[] = {

initr_mmc,

#endif

initr_env,

+#ifdef CONFIG_ENV_DYNAMIC_DEFAULT

+ initr_env_dynamic_default,

+#endif

#ifdef CONFIG_SYS_BOOTPARAMS_LEN

initr_malloc_bootparams,

#endif

diff --git a/configs/allwinner_s3_generic_defconfig b/configs/allwinner_s3_generic_defconfig

new file mode 100644

index 0000000000..2c368215ed

--- /dev/null

+++ b/configs/allwinner_s3_generic_defconfig

@@ -0,0 +1,54 @@

+CONFIG_ARM=y

+CONFIG_ARCH_SUNXI=y

+CONFIG_MACH_SUN8I_S3=y

+

+CONFIG_DEFAULT_DEVICE_TREE="sun8i-s3-generic"

+CONFIG_SPL=y

+CONFIG_CMD_BOOTMENU=y

+CONFIG_CMD_MEMINFO=y

+CONFIG_BOOTDELAY=0

+

+CONFIG_NETDEVICES=y

+CONFIG_SUN8I_EMAC=y

+CONFIG_NET_RANDOM_ETHADDR=y

+

+CONFIG_DM_SPI=y

+CONFIG_SUNXI_SPI=y

+

+CONFIG_MMC=y

+CONFIG_MMC_SUNXI_SLOT_EXTRA=2

+CONFIG_MMC0_CD_PIN="PF6"

+

+CONFIG_CMD_BMP=y

+CONFIG_VIDEO_BPP8=y

+CONFIG_VIDEO_SIMPLE=y

+CONFIG_VIDEO_DT_SIMPLEFB=y

+

+CONFIG_DM_REGULATOR=y

+CONFIG_REGULATOR_PWM=y

+CONFIG_DM_PWM=y

+CONFIG_PWM_SUNXI=y

+CONFIG_BACKLIGHT_PWM=y

+

+CONFIG_USB_GADGET_VBUS_DRAW=250

+

+CONFIG_USB_MUSB_GADGET=y

+CONFIG_USB_MUSB_SUNXI=y

+CONFIG_USB_MUSB_DISABLE_BULK_COMBINE_SPLIT=y

+CONFIG_USB_MUSB_PIO_ONLY=y

+CONFIG_USB_STORAGE=y

+

+CONFIG_PHY=y

+CONFIG_PHY_SUN4I_USB=y

+

+CONFIG_USB_EHCI_HCD=y

+CONFIG_USB_EHCI_GENERIC=y

+CONFIG_USB_OHCI_HCD=y

+CONFIG_USB_OHCI_GENERIC=y

+

+CONFIG_CMD_USB_MASS_STORAGE=y

+

+CONFIG_CMD_FASTBOOT=y

+CONFIG_FASTBOOT_FLASH_MMC=y

+CONFIG_FASTBOOT_FLASH_MMC_DEV=1

+CONFIG_FASTBOOT_CMD_OEM_FORMAT=y

diff --git a/drivers/clk/sunxi/Kconfig b/drivers/clk/sunxi/Kconfig

index 5ff101b993..c48717bbbc 100644

--- a/drivers/clk/sunxi/Kconfig

+++ b/drivers/clk/sunxi/Kconfig

@@ -52,11 +52,11 @@ config CLK_SUN8I_R40

on Allwinner R40 SoC.

config CLK_SUN8I_V3S

- bool "Clock driver for Allwinner V3S"

- default MACH_SUN8I_V3S

+ bool "Clock driver for Allwinner V3S/S3"

+ default MACH_SUN8I_V3S || MACH_SUN8I_S3

help

This enables common clock driver support for platforms based

- on Allwinner V3S SoC.

+ on Allwinner V3S/S3 SoC.

config CLK_SUN9I_A80

bool "Clock driver for Allwinner A80"

diff --git a/drivers/clk/sunxi/clk_v3s.c b/drivers/clk/sunxi/clk_v3s.c

index 789ac72026..2101efd11f 100644

--- a/drivers/clk/sunxi/clk_v3s.c

+++ b/drivers/clk/sunxi/clk_v3s.c

@@ -16,16 +16,22 @@ static struct ccu_clk_gate v3s_gates[] = {

[CLK_BUS_MMC0] = GATE(0x060, BIT(8)),

[CLK_BUS_MMC1] = GATE(0x060, BIT(9)),

[CLK_BUS_MMC2] = GATE(0x060, BIT(10)),

+ [CLK_BUS_EMAC] = GATE(0x060, BIT(17)),

[CLK_BUS_SPI0] = GATE(0x060, BIT(20)),

[CLK_BUS_OTG] = GATE(0x060, BIT(24)),

+ [CLK_BUS_EHCI0] = GATE(0x060, BIT(26)),

+ [CLK_BUS_OHCI0] = GATE(0x060, BIT(29)),

[CLK_BUS_UART0] = GATE(0x06c, BIT(16)),

[CLK_BUS_UART1] = GATE(0x06c, BIT(17)),

[CLK_BUS_UART2] = GATE(0x06c, BIT(18)),

+ [CLK_BUS_EPHY] = GATE(0x070, BIT(0)),

+

[CLK_SPI0] = GATE(0x0a0, BIT(31)),

- [CLK_USB_PHY0] = GATE(0x0cc, BIT(8)),

+ [CLK_USB_PHY0] = GATE(0x0cc, BIT(8)),

+ [CLK_USB_OHCI0] = GATE(0x0cc, BIT(16)),

};

static struct ccu_reset v3s_resets[] = {

@@ -34,8 +40,13 @@ static struct ccu_reset v3s_resets[] = {

[RST_BUS_MMC0] = RESET(0x2c0, BIT(8)),

[RST_BUS_MMC1] = RESET(0x2c0, BIT(9)),

[RST_BUS_MMC2] = RESET(0x2c0, BIT(10)),

+ [RST_BUS_EMAC] = RESET(0x2c0, BIT(17)),

[RST_BUS_SPI0] = RESET(0x2c0, BIT(20)),

[RST_BUS_OTG] = RESET(0x2c0, BIT(24)),

+ [RST_BUS_EHCI0] = RESET(0x2c0, BIT(26)),

+ [RST_BUS_OHCI0] = RESET(0x2c0, BIT(29)),

+

+ [RST_BUS_EPHY] = RESET(0x2c8, BIT(2)),

[RST_BUS_UART0] = RESET(0x2d8, BIT(16)),

[RST_BUS_UART1] = RESET(0x2d8, BIT(17)),

diff --git a/drivers/mmc/sunxi_mmc.c b/drivers/mmc/sunxi_mmc.c

index 9f426661c4..20a622dd2e 100644

--- a/drivers/mmc/sunxi_mmc.c

+++ b/drivers/mmc/sunxi_mmc.c

@@ -628,7 +628,7 @@ static int sunxi_mmc_probe(struct udevice *dev)

cfg->b_max = CONFIG_SYS_MMC_MAX_BLK_COUNT;

cfg->f_min = 400000;

- cfg->f_max = 52000000;

+ cfg->f_max = dev_read_u32_default(dev, "max-speed", 52000000);

priv->reg = (void *)dev_read_addr(dev);

priv->variant =

diff --git a/drivers/pwm/sunxi_pwm.c b/drivers/pwm/sunxi_pwm.c

index 8a55e4f461..154a5290ce 100644

--- a/drivers/pwm/sunxi_pwm.c

+++ b/drivers/pwm/sunxi_pwm.c

@@ -47,6 +47,9 @@ static int sunxi_pwm_config_pinmux(void)

{

#ifdef CONFIG_MACH_SUN50I

sunxi_gpio_set_cfgpin(SUNXI_GPD(22), SUNXI_GPD_PWM);

+#endif

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

+ sunxi_gpio_set_cfgpin(SUNXI_GPB(4), SUN4I_GPB_PWM);

#endif

return 0;

}

diff --git a/drivers/usb/musb-new/musb_core.c b/drivers/usb/musb-new/musb_core.c

index f678aa4826..2574a6fd4b 100644

--- a/drivers/usb/musb-new/musb_core.c

+++ b/drivers/usb/musb-new/musb_core.c

@@ -1875,6 +1875,7 @@ allocate_instance(struct device *dev,

musb->controller = dev;

+ musb->dyn_fifo = config->dyn_fifo;

return musb;

}

diff --git a/drivers/video/sunxi/sunxi_de2.c b/drivers/video/sunxi/sunxi_de2.c

index 8333ddc44c..13be7a11e0 100644

--- a/drivers/video/sunxi/sunxi_de2.c

+++ b/drivers/video/sunxi/sunxi_de2.c

@@ -23,12 +23,21 @@

DECLARE_GLOBAL_DATA_PTR;

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

+enum {

+ /* Maximum LCD size we support */

+ LCD_MAX_WIDTH = 1024,

+ LCD_MAX_HEIGHT = 768,

+ LCD_MAX_LOG2_BPP = VIDEO_BPP32,

+};

+#else

enum {

/* Maximum LCD size we support */

LCD_MAX_WIDTH = 3840,

LCD_MAX_HEIGHT = 2160,

LCD_MAX_LOG2_BPP = VIDEO_BPP32,

};

+#endif

static void sunxi_de2_composer_init(void)

{

@@ -43,13 +52,19 @@ static void sunxi_de2_composer_init(void)

reg_value &= ~(0x01 << 24);

writel(reg_value, SUNXI_SRAMC_BASE + 0x04);

#endif

-

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

+ unsigned int hz = 300000000;

+ int pll = clock_get_pll6() * 2;

+ int div = 1;

+ while ((pll / div) > hz)

+ div++;

+ writel(CCM_DE2_CTRL_GATE | CCM_DE2_CTRL_PLL6_2X | CCM_DE2_CTRL_M(div), &ccm->de_clk_cfg);

+#else

clock_set_pll10(432000000);

-

/* Set DE parent to pll10 */

clrsetbits_le32(&ccm->de_clk_cfg, CCM_DE2_CTRL_PLL_MASK,

CCM_DE2_CTRL_PLL10);

-

+#endif

/* Set ahb gating to pass */

setbits_le32(&ccm->ahb_reset1_cfg, 1 << AHB_RESET_OFFSET_DE);

setbits_le32(&ccm->ahb_gate1, 1 << AHB_GATE_OFFSET_DE);

@@ -74,14 +89,13 @@ static void sunxi_de2_mode_set(int mux, const struct display_timing *mode,

struct de_ui * const de_ui_regs =

(struct de_ui *)(de_mux_base +

SUNXI_DE2_MUX_CHAN_REGS +

- SUNXI_DE2_MUX_CHAN_SZ * 1);

+ SUNXI_DE2_MUX_CHAN_SZ * SUNXI_DE2_MUX_CHAN_SZ_COUNT);

struct de_csc * const de_csc_regs =

(struct de_csc *)(de_mux_base +

SUNXI_DE2_MUX_DCSC_REGS);

u32 size = SUNXI_DE2_WH(mode->hactive.typ, mode->vactive.typ);

int channel;

u32 format;

-

/* enable clock */

#ifdef CONFIG_MACH_SUN8I_H3

setbits_le32(&de_clk_regs->rst_cfg, (mux == 0) ? 1 : 4);

@@ -108,13 +122,12 @@ static void sunxi_de2_mode_set(int mux, const struct display_timing *mode,

writel(0x00000101, &de_bld_regs->fcolor_ctl);

- writel(1, &de_bld_regs->route);

+ writel(SUNXI_DE2_BLD_ROUTE, &de_bld_regs->route);

writel(0, &de_bld_regs->premultiply);

writel(0xff000000, &de_bld_regs->bkcolor);

writel(0x03010301, &de_bld_regs->bld_mode[0]);

-

writel(size, &de_bld_regs->output_size);

writel(mode->flags & DISPLAY_FLAGS_INTERLACED ? 2 : 0,

&de_bld_regs->out_ctl);

diff --git a/drivers/video/sunxi/sunxi_dw_hdmi.c b/drivers/video/sunxi/sunxi_dw_hdmi.c

index c87c919a52..949b41732e 100644

--- a/drivers/video/sunxi/sunxi_dw_hdmi.c

+++ b/drivers/video/sunxi/sunxi_dw_hdmi.c

@@ -395,6 +395,8 @@ U_BOOT_DRIVER(sunxi_dw_hdmi) = {

.priv_auto_alloc_size = sizeof(struct sunxi_dw_hdmi_priv),

};

+#if !defined(CONFIG_MACH_SUN8I_V3S) && !defined(CONFIG_MACH_SUN8I_S3)

U_BOOT_DEVICE(sunxi_dw_hdmi) = {

.name = "sunxi_dw_hdmi"

};

+#endif

diff --git a/drivers/video/sunxi/sunxi_lcd.c b/drivers/video/sunxi/sunxi_lcd.c

index 619f5892f5..bc0a782a1c 100644

--- a/drivers/video/sunxi/sunxi_lcd.c

+++ b/drivers/video/sunxi/sunxi_lcd.c

@@ -24,7 +24,7 @@ struct sunxi_lcd_priv {

static void sunxi_lcdc_config_pinmux(void)

{

-#ifdef CONFIG_MACH_SUN50I

+#if defined(CONFIG_MACH_SUN50I) || defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

int pin;

for (pin = SUNXI_GPD(0); pin <= SUNXI_GPD(21); pin++) {

@@ -144,7 +144,7 @@ U_BOOT_DRIVER(sunxi_lcd) = {

.priv_auto_alloc_size = sizeof(struct sunxi_lcd_priv),

};

-#ifdef CONFIG_MACH_SUN50I

+#if defined(CONFIG_MACH_SUN50I) || defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

U_BOOT_DEVICE(sunxi_lcd) = {

.name = "sunxi_lcd"

};

diff --git a/include/configs/sunxi-common.h b/include/configs/sunxi-common.h

index 0ef289fd64..da3080cc32 100644

--- a/include/configs/sunxi-common.h

+++ b/include/configs/sunxi-common.h

@@ -144,12 +144,12 @@

#define CONFIG_SYS_MMC_MAX_DEVICE 4

#endif

-#ifndef CONFIG_MACH_SUN8I_V3S

-/* 64MB of malloc() pool */

-#define CONFIG_SYS_MALLOC_LEN (CONFIG_ENV_SIZE + (64 << 20))

-#else

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

/* 2MB of malloc() pool */

#define CONFIG_SYS_MALLOC_LEN (CONFIG_ENV_SIZE + (2 << 20))

+#else

+/* 64MB of malloc() pool */

+#define CONFIG_SYS_MALLOC_LEN (CONFIG_ENV_SIZE + (64 << 20))

#endif

/*

@@ -301,19 +301,8 @@ extern int soft_i2c_gpio_scl;

#define RAMDISK_ADDR_R __stringify(SDRAM_OFFSET(FE00000))

#else

-/*

- * 160M RAM (256M minimum minus 64MB heap + 32MB for u-boot, stack, fb, etc.

- * 32M uncompressed kernel, 16M compressed kernel, 1M fdt,

- * 1M script, 1M pxe and the ramdisk at the end.

- */

-#ifndef CONFIG_MACH_SUN8I_V3S

-#define BOOTM_SIZE __stringify(0xa000000)

-#define KERNEL_ADDR_R __stringify(SDRAM_OFFSET(2000000))

-#define FDT_ADDR_R __stringify(SDRAM_OFFSET(3000000))

-#define SCRIPT_ADDR_R __stringify(SDRAM_OFFSET(3100000))

-#define PXEFILE_ADDR_R __stringify(SDRAM_OFFSET(3200000))

-#define RAMDISK_ADDR_R __stringify(SDRAM_OFFSET(3300000))

-#else

+

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

/*

* 64M RAM minus 2MB heap + 16MB for u-boot, stack, fb, etc.

* 16M uncompressed kernel, 8M compressed kernel, 1M fdt,

@@ -325,6 +314,18 @@ extern int soft_i2c_gpio_scl;

#define SCRIPT_ADDR_R __stringify(SDRAM_OFFSET(1900000))

#define PXEFILE_ADDR_R __stringify(SDRAM_OFFSET(1A00000))

#define RAMDISK_ADDR_R __stringify(SDRAM_OFFSET(1B00000))

+#else

+/*

+ * 160M RAM (256M minimum minus 64MB heap + 32MB for u-boot, stack, fb, etc.

+ * 32M uncompressed kernel, 16M compressed kernel, 1M fdt,

+ * 1M script, 1M pxe and the ramdisk at the end.

+ */

+#define BOOTM_SIZE __stringify(0xa000000)

+#define KERNEL_ADDR_R __stringify(SDRAM_OFFSET(2000000))

+#define FDT_ADDR_R __stringify(SDRAM_OFFSET(3000000))

+#define SCRIPT_ADDR_R __stringify(SDRAM_OFFSET(3100000))

+#define PXEFILE_ADDR_R __stringify(SDRAM_OFFSET(3200000))

+#define RAMDISK_ADDR_R __stringify(SDRAM_OFFSET(3300000))

#endif

#endif

@@ -427,6 +428,14 @@ extern int soft_i2c_gpio_scl;

#include <config_distro_bootcmd.h>

+#ifdef CONFIG_CMD_FASTBOOT

+#define FASTBOOT_SETTINGS \

+ "boot_targets=fel mmc_auto usb0 fastboot\0" \

+ "bootcmd_fastboot=fastboot usb 0\0"

+#else

+#define FASTBOOT_SETTINGS

+#endif

+

#ifdef CONFIG_USB_KEYBOARD

#define CONSOLE_STDIN_SETTINGS \

"preboot=usb start\0" \

@@ -436,11 +445,25 @@ extern int soft_i2c_gpio_scl;

"stdin=serial\0"

#endif

+#ifdef CONFIG_DM_VIDEO

+#define CONFIG_VIDEO_BMP_RLE8

+#define CONFIG_BMP_16BPP

+#define CONFIG_BMP_24BPP

+#define CONFIG_BMP_32BPP

+#define CONFIG_SPLASH_SCREEN

+#define CONFIG_SPLASH_SOURCE

+#define SPLASHIMAGE_ENV_SETTINGS "splashimage=" __stringify(SDRAM_OFFSET(2000000)) "\0"

+#define CONFIG_ENV_DYNAMIC_DEFAULT

+#else

+#define SPLASHIMAGE_ENV_SETTINGS

+#endif

+

#ifdef CONFIG_VIDEO

#define CONSOLE_STDOUT_SETTINGS \

"stdout=serial,vga\0" \

"stderr=serial,vga\0"

-#elif CONFIG_DM_VIDEO

+#else

+#if CONFIG_DM_VIDEO && !defined(CONFIG_SPLASH_SCREEN)

#define CONSOLE_STDOUT_SETTINGS \

"stdout=serial,vidconsole\0" \

"stderr=serial,vidconsole\0"

@@ -449,6 +472,7 @@ extern int soft_i2c_gpio_scl;

"stdout=serial\0" \

"stderr=serial\0"

#endif

+#endif

#ifdef CONFIG_MTDIDS_DEFAULT

#define SUNXI_MTDIDS_DEFAULT \

@@ -464,11 +488,18 @@ extern int soft_i2c_gpio_scl;

#define SUNXI_MTDPARTS_DEFAULT

#endif

+#if defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

+#define PARTS_DEFAULT \

+ "name=loader,start=8k,size=1024k;" \

+ "name=esp,size=16M,bootable,uuid=${uuid_gpt_esp};" \

+ "name=system,size=-,uuid=${uuid_gpt_system};"

+#else

#define PARTS_DEFAULT \

"name=loader1,start=8k,size=32k,uuid=${uuid_gpt_loader1};" \

"name=loader2,size=984k,uuid=${uuid_gpt_loader2};" \

"name=esp,size=128M,bootable,uuid=${uuid_gpt_esp};" \

"name=system,size=-,uuid=${uuid_gpt_system};"

+#endif

#define UUID_GPT_ESP "c12a7328-f81f-11d2-ba4b-00a0c93ec93b"

@@ -490,6 +521,7 @@ extern int soft_i2c_gpio_scl;

#define CONFIG_EXTRA_ENV_SETTINGS \

CONSOLE_ENV_SETTINGS \

+ SPLASHIMAGE_ENV_SETTINGS \

MEM_LAYOUT_ENV_SETTINGS \

DFU_ALT_INFO_RAM \

"fdtfile=" FDTFILE "\0" \

@@ -500,10 +532,12 @@ extern int soft_i2c_gpio_scl;

"uuid_gpt_system=" UUID_GPT_SYSTEM "\0" \

"partitions=" PARTS_DEFAULT "\0" \

BOOTCMD_SUNXI_COMPAT \

- BOOTENV

+ BOOTENV \

+ FASTBOOT_SETTINGS

#else /* ifndef CONFIG_SPL_BUILD */

#define CONFIG_EXTRA_ENV_SETTINGS

#endif

#endif /* _SUNXI_COMMON_CONFIG_H */

+

diff --git a/include/init.h b/include/init.h

index 2a33a3fd1e..95bb92f51c 100644

--- a/include/init.h

+++ b/include/init.h

@@ -203,6 +203,7 @@ int update_flash_size(int flash_size);

int arch_early_init_r(void);

void pci_init(void);

int misc_init_r(void);

+int initr_env_dynamic_default(void);

#if defined(CONFIG_VID)

int init_func_vid(void);

#endif

diff --git a/scripts/config_whitelist.txt b/scripts/config_whitelist.txt

index 6908431d03..b3414bb3a0 100644

--- a/scripts/config_whitelist.txt

+++ b/scripts/config_whitelist.txt

@@ -426,6 +426,7 @@ CONFIG_ENV_ADDR_FLEX

CONFIG_ENV_CALLBACK_LIST_DEFAULT

CONFIG_ENV_CALLBACK_LIST_STATIC

CONFIG_ENV_COMMON_BOOT

+CONFIG_ENV_DYNAMIC_DEFAULT

CONFIG_ENV_EEPROM_IS_ON_I2C

CONFIG_ENV_FLAGS_LIST_DEFAULT

CONFIG_ENV_FLAGS_LIST_STATIC离线

#2 2020-04-21 12:15:10 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,140

- 积分: 1092.5

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

是安卓那个fastboot工具吗?这个工具好用

离线

楼主 #3 2020-04-21 12:15:42 分享评论

- aodzip

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 130

- 积分: 100

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

是安卓那个fastboot工具吗?这个工具好用

是的,就是Android的fastboot

生产力级别的u-boot

最近编辑记录 aodzip (2020-04-21 12:16:16)

离线

#4 2020-04-21 12:56:31 分享评论

- yytyu

- 会员

- 注册时间: 2018-11-01

- 已发帖子: 35

- 积分: 19

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

谢谢分享!

离线

#5 2020-04-21 16:59:47 分享评论

- xingjxuan

- 会员

- 注册时间: 2020-04-07

- 已发帖子: 7

- 积分: 7

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

这个好,fastboot可以用的话就刚刚的了,uboot生产力加倍~~

离线

#6 2020-04-21 17:52:53 分享评论

- shaoxi2010

- 会员

- 注册时间: 2019-06-13

- 已发帖子: 398

- 积分: 337

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

给力阿,之前研究了很久DE2死活没调通,还是大佬厉害啊

离线

#7 2020-04-21 23:42:04 分享评论

- AaronHo

- 会员

- 注册时间: 2020-03-08

- 已发帖子: 13

- 积分: 13

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

!!!不错,这是我见过的最完美的uboot了。很硬核啊!!!

之前尝试编fastboot,无奈错误不少啊。

显示无忧~

网络无忧~

USB无忧~

刷机无忧~

大佬!!给力!!

离线

#8 2020-04-22 20:43:41 分享评论

- liuchangyin

- 会员

- 注册时间: 2020-03-17

- 已发帖子: 204

- 积分: 199

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

不知道视频编解码怎么样?要是这个完全解决了,那要无敌啊

离线

楼主 #9 2020-04-24 10:24:16 分享评论

- aodzip

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 130

- 积分: 100

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

给SDC2加了时钟降速功能,为了兼容某些品牌SD NAND自己上报能跑50M结果真跑了50M存储控制器直接死机的问题。

离线

楼主 #10 2020-04-24 10:24:54 分享评论

- aodzip

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 130

- 积分: 100

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

不知道视频编解码怎么样?要是这个完全解决了,那要无敌啊

这个不是uboot该考虑的事哈哈。

离线

#11 2020-04-24 10:34:00 分享评论

- ytm2020

- 会员

- 注册时间: 2020-04-24

- 已发帖子: 6

- 积分: 7

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

不错,有新的u-boot 支持,有多大?

离线

#12 2020-04-24 10:39:27 分享评论

- 龙折翼

- 会员

- 注册时间: 2020-04-24

- 已发帖子: 9

- 积分: 9

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

感觉uboot加上LCD显示没有太大用,最多显示一下开机logo就行了

离线

楼主 #13 2020-04-24 10:42:58 分享评论

- aodzip

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 130

- 积分: 100

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

感觉uboot加上LCD显示没有太大用,最多显示一下开机logo就行了

就是显示logo用的,不然你在kernel完全加载之前会白屏很长一段时间,用户体验差(除非你Kernel在几百毫秒内就能启动完成

离线

#14 2020-04-27 14:52:11 分享评论

- Daniel

- 会员

- 注册时间: 2020-04-27

- 已发帖子: 5

- 积分: 5

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

这个在其他全志平台能用吗,比如 H3 和 H6

离线

楼主 #15 2020-04-27 14:55:28 分享评论

- aodzip

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 130

- 积分: 100

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

这个在其他全志平台能用吗,比如 H3 和 H6

不能直接用,可以参考我的commit去修改

离线

#16 2020-04-27 15:13:40 分享评论

- Daniel

- 会员

- 注册时间: 2020-04-27

- 已发帖子: 5

- 积分: 5

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

谢谢,fastboot 是用 apt 安装的吗,还是使用全志提供的那个二进制程序。

离线

楼主 #17 2020-04-27 15:17:00 分享评论

- aodzip

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 130

- 积分: 100

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

谢谢,fastboot 是用 apt 安装的吗,还是使用全志提供的那个二进制程序。

apt装的就可以,兼容的是标准的fastboot

离线

#18 2020-04-27 15:22:53 分享评论

- Daniel

- 会员

- 注册时间: 2020-04-27

- 已发帖子: 5

- 积分: 5

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

谢谢,还有个问题要请教下,这个烧到 EMMC 和 TF 都支持了吗?

离线

楼主 #19 2020-04-27 15:24:22 分享评论

- aodzip

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 130

- 积分: 100

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

谢谢,还有个问题要请教下,这个烧到 EMMC 和 TF 都支持了吗?

都支持

离线

#20 2020-04-27 15:27:22 分享评论

- Daniel

- 会员

- 注册时间: 2020-04-27

- 已发帖子: 5

- 积分: 5

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

都支持

Nice,太棒了

离线

#21 2020-04-27 15:43:37 分享评论

- Daniel

- 会员

- 注册时间: 2020-04-27

- 已发帖子: 5

- 积分: 5

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

Allwinner mUSB OTG (Peripheral)

Net: phy interface0

eth0: ethernet@1c30000

Warning: usb_ether MAC addresses don't match:

Address in ROM is de:ad:be:ef:00:01

Address in environment is 12:81:3e:a8:58:d8

, eth1: usb_ether

starting USB...

Bus usb@1c1a000: USB EHCI 1.00

Bus usb@1c1a400: USB OHCI 1.0

Bus usb@1c1b000: USB EHCI 1.00

Bus usb@1c1b400: USB OHCI 1.0

Bus usb@1c1c000: USB EHCI 1.00

Bus usb@1c1c400: USB OHCI 1.0

Bus usb@1c1d000: USB EHCI 1.00

Bus usb@1c1d400: USB OHCI 1.0

scanning bus usb@1c1a000 for devices... 1 USB Device(s) found

scanning bus usb@1c1a400 for devices... 1 USB Device(s) found

scanning bus usb@1c1b000 for devices... 1 USB Device(s) found

scanning bus usb@1c1b400 for devices... 1 USB Device(s) found

scanning bus usb@1c1c000 for devices... 1 USB Device(s) found

scanning bus usb@1c1c400 for devices... 1 USB Device(s) found

scanning bus usb@1c1d000 for devices... 1 USB Device(s) found

scanning bus usb@1c1d400 for devices... 1 USB Device(s) found

scanning usb for storage devices... 0 Storage Device(s) found

Hit any key to stop autoboot: 0

switch to partitions #0, OK

mmc1(part 0) is current device

** Unrecognized filesystem type **

MMC: no card present

Device 0: unknown device

musb-hdrc: peripheral reset irq lost!我在 H3 上试下了,串口这个提示信息和你截图的一样

但是我在 Ubuntu PC 中使用 sudo fastboot devices 检测不到设备,一直提示

$ sudo fastboot oem

< waiting for device >

现在是不是Ubuntu Pc 的 fastboot 的配置有问题

如果板子log停在 musb-hdrc: peripheral reset irq lost! 这里,是不是说明板子那边配置应该已经正常了,谢谢!

最近编辑记录 Daniel (2020-04-27 15:44:17)

离线

楼主 #22 2020-04-27 15:48:55 分享评论

- aodzip

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 130

- 积分: 100

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

Allwinner mUSB OTG (Peripheral)

Net: phy interface0

eth0: ethernet@1c30000

Warning: usb_ether MAC addresses don't match:

....

如果板子log停在 musb-hdrc: peripheral reset irq lost! 这里,是不是说明板子那边配置应该已经正常了,谢谢!

H3我不了解具体情况,我这个代码里存在部分专门为S3做的适配,H3用很可能出BUG。可能具体的一些调整操作要你自己来做了。

fastboot不认看看dmesg中有没有枚举设备,如果没有的话可能就有点麻烦

离线

#23 2020-04-27 15:53:18 分享评论

- Daniel

- 会员

- 注册时间: 2020-04-27

- 已发帖子: 5

- 积分: 5

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

谢谢,看来是我 fastboot 配置的问题,用全志的 fastboot 可以识别并操作

$ sudo ./fastboot devices

02c001813ea858d8 fastboot

$ sudo ./fastboot oem format

...

OKAY [ 0.008s]

finished. total time: 0.008s

离线

#24 2020-04-27 16:38:19 分享评论

- zhang235hai

- 会员

- 注册时间: 2020-04-06

- 已发帖子: 212

- 积分: 165

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

这个不是uboot该考虑的事哈哈。

要让控制台的信息输出到4.3寸液晶屏,需要做哪些设置呢?

也就是可以脱离台式机电脑操作荔枝派zero

离线

#25 2020-04-27 16:46:45 分享评论

- shunshn

- 会员

- 注册时间: 2020-04-13

- 已发帖子: 15

- 积分: 15

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

V3s可以使用吗?努力学习arm + linux系统中。。。。。。

离线

#26 2020-05-04 15:01:54 分享评论

- 拉轰的脚踏车

- 会员

- 注册时间: 2020-03-20

- 已发帖子: 288

- 积分: 222

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

V3s可以使用吗?努力学习arm + linux系统中。。。。。。

可以用,

arch/arm/mach-sunxi/Kconfig 要添加一行 V3s 才能编译通过:

config MACH_SUN8I_V3S

bool "sun8i (Allwinner V3s)"

select CPU_V7A

select CPU_V7_HAS_NONSEC

select CPU_V7_HAS_VIRT

select ARCH_SUPPORT_PSCI

select SUNXI_GEN_SUN6I

select SUNXI_DRAM_DW

select SUNXI_DRAM_DW_16BIT

select SUPPORT_SPL

select SUNXI_DE2config MACH_SUN8I_S3

bool "sun8i (Allwinner S3)"

select CPU_V7A

select CPU_V7_HAS_NONSEC

select CPU_V7_HAS_VIRT

select ARCH_SUPPORT_PSCI

select SUNXI_GEN_SUN6I

select SUNXI_DRAM_DW

select SUNXI_DRAM_DW_16BIT

select SUPPORT_SPL

select SUNXI_DE2

离线

#27 2020-05-04 16:10:06 分享评论

- 流氓兔

- 会员

- 注册时间: 2020-02-01

- 已发帖子: 121

- 积分: 109.5

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

好像不支持 SPI FLASH, 大佬可以把这个代码合并进去吗?

https://github.com/Lichee-Pi/u-boot/commits/v3s-spi-experimental

离线

#28 2020-05-04 21:35:25 分享评论

- god

- 会员

- 注册时间: 2019-10-04

- 已发帖子: 10

- 积分: 10

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

支持adozip,支持fastboot!

离线

#29 2020-05-06 11:54:53 分享评论

- dylan

- 会员

- 注册时间: 2020-05-06

- 已发帖子: 5

- 积分: 5

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

能支持wifi吗,有调过ap6212的没有

离线

楼主 #30 2020-05-06 12:18:32 分享评论

- aodzip

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 130

- 积分: 100

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

好像不支持 SPI FLASH, 大佬可以把这个代码合并进去吗?

https://github.com/Lichee-Pi/u-boot/commits/v3s-spi-experimental

等我有能测试SPI设备的时候再搞

离线

楼主 #31 2020-05-06 12:19:04 分享评论

- aodzip

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 130

- 积分: 100

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

能支持wifi吗,有调过ap6212的没有

为啥要支持Wi-Fi啊,大概是什么应用场景

离线

#32 2020-05-31 09:34:19 分享评论

- 房地产

- 会员

- 注册时间: 2020-03-02

- 已发帖子: 27

- 积分: 27

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

这个可以用到f1c100s上吗?

离线

#33 2020-06-02 10:09:42 分享评论

- twig

- 会员

- 注册时间: 2020-01-06

- 已发帖子: 3

- 积分: 3

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

这个好。

离线

#34 2020-10-14 15:32:02 分享评论

- 拉轰的脚踏车

- 会员

- 注册时间: 2020-03-20

- 已发帖子: 288

- 积分: 222

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

感谢楼主, V3s u-boot USB运行成功

离线

#35 2020-10-17 16:16:39 分享评论

- 路人甲

- 会员

- 注册时间: 2017-09-07

- 已发帖子: 202

- 积分: 199.5

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

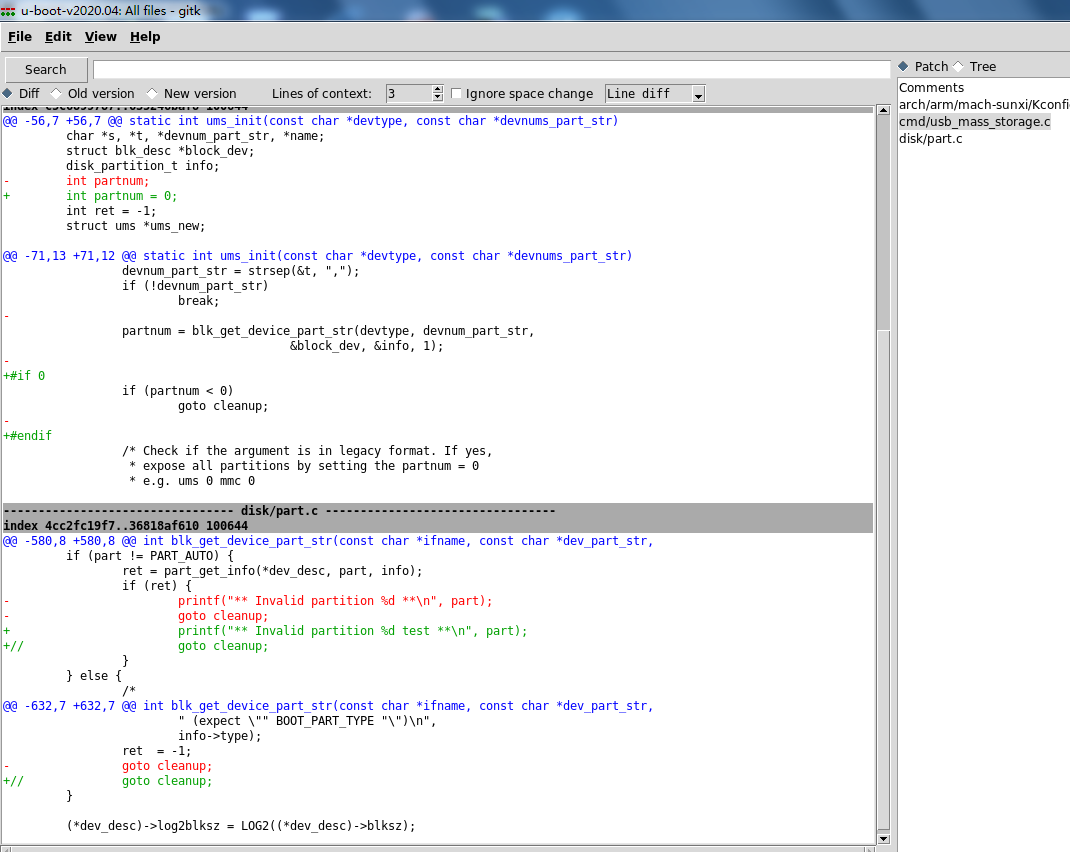

请问楼主如果TF有两个分区,执行ums命令:

=> ums 0 mmc 0

** Invalid partition 1 **

会出现这个错误, 应该怎么破?

离线

#36 2020-10-17 17:06:13 分享评论

- 路人甲

- 会员

- 注册时间: 2017-09-07

- 已发帖子: 202

- 积分: 199.5

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

请问楼主如果TF有两个分区,执行ums命令:

=> ums 0 mmc 0

** Invalid partition 1 **会出现这个错误, 应该怎么破?

把这个判断强行屏蔽起来就好了

diff --git a/arch/arm/mach-sunxi/Kconfig b/arch/arm/mach-sunxi/Kconfig

index b7cb87a98f..3a46b14b05 100644

--- a/arch/arm/mach-sunxi/Kconfig

+++ b/arch/arm/mach-sunxi/Kconfig

@@ -262,6 +262,7 @@ config MACH_SUN8I_V3S

select SUNXI_DRAM_DW

select SUNXI_DRAM_DW_16BIT

select SUPPORT_SPL

+ select SUNXI_DE2

config MACH_SUN8I_S3

bool "sun8i (Allwinner S3)"

diff --git a/cmd/usb_mass_storage.c b/cmd/usb_mass_storage.c

index c5c6899787..635246baf8 100644

--- a/cmd/usb_mass_storage.c

+++ b/cmd/usb_mass_storage.c

@@ -56,7 +56,7 @@ static int ums_init(const char *devtype, const char *devnums_part_str)

char *s, *t, *devnum_part_str, *name;

struct blk_desc *block_dev;

disk_partition_t info;

- int partnum;

+ int partnum = 0;

int ret = -1;

struct ums *ums_new;

@@ -71,13 +71,12 @@ static int ums_init(const char *devtype, const char *devnums_part_str)

devnum_part_str = strsep(&t, ",");

if (!devnum_part_str)

break;

-

partnum = blk_get_device_part_str(devtype, devnum_part_str,

&block_dev, &info, 1);

-

+#if 0

if (partnum < 0)

goto cleanup;

-

+#endif

/* Check if the argument is in legacy format. If yes,

* expose all partitions by setting the partnum = 0

* e.g. ums 0 mmc 0

diff --git a/disk/part.c b/disk/part.c

index 4cc2fc19f7..36818af610 100644

--- a/disk/part.c

+++ b/disk/part.c

@@ -580,8 +580,8 @@ int blk_get_device_part_str(const char *ifname, const char *dev_part_str,

if (part != PART_AUTO) {

ret = part_get_info(*dev_desc, part, info);

if (ret) {

- printf("** Invalid partition %d **\n", part);

- goto cleanup;

+ printf("** Invalid partition %d test **\n", part);

+// goto cleanup;

}

} else {

/*

@@ -632,7 +632,7 @@ int blk_get_device_part_str(const char *ifname, const char *dev_part_str,

" (expect \"" BOOT_PART_TYPE "\")\n",

info->type);

ret = -1;

- goto cleanup;

+// goto cleanup;

}

(*dev_desc)->log2blksz = LOG2((*dev_desc)->blksz);

离线

#37 2020-11-04 17:33:22 分享评论

- 孤星泪

- 会员

- 注册时间: 2020-03-18

- 已发帖子: 235

- 积分: 231

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

奇怪,我的荔枝派跑起来其它功能都正常,但是屏幕背光没有显示。

离线

#38 2020-11-23 15:03:53 分享评论

- avb

- 会员

- 注册时间: 2020-02-22

- 已发帖子: 2

- 积分: 2

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

One problem with this u-boot - it overwrites loaded splash image with uboot version string.

离线

#39 2021-03-21 22:34:20 分享评论

- 马前卒

- 会员

- 注册时间: 2020-08-08

- 已发帖子: 60

- 积分: 57

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

奇怪,我的荔枝派跑起来其它功能都正常,但是屏幕背光没有显示。

我的也是没有背光, 这就尴尬了, 看代码好像是 dts 驱动pwm0 (PB4) 实现的, 荔枝派的原理图也是这么接, 可是就是不亮.

离线

#40 2021-03-21 23:31:04 分享评论

- whyabc666

- 封禁

- 注册时间: 2019-12-12

- 已发帖子: 378

- 积分: 365

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

dylan 说:能支持wifi吗,有调过ap6212的没有

为啥要支持Wi-Fi啊,大概是什么应用场景

AP6212是什么级别的WiFi?有阉割吗?

离线

#41 2021-03-21 23:44:45 分享评论

- 马前卒

- 会员

- 注册时间: 2020-08-08

- 已发帖子: 60

- 积分: 57

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

孤星泪 说:奇怪,我的荔枝派跑起来其它功能都正常,但是屏幕背光没有显示。

我的也是没有背光, 这就尴尬了, 看代码好像是 dts 驱动pwm0 (PB4) 实现的, 荔枝派的原理图也是这么接, 可是就是不亮.

修改这个文件: drivers/video/sunxi/sunxi_lcd.c

static void sunxi_lcdc_config_pinmux(void)

{

#if defined(CONFIG_MACH_SUN50I) || defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3)

int pin;

#if defined(CONFIG_MACH_SUN8I_V3S)

#define SUN8I_V3S_GPE_LCD 3

for (pin = SUNXI_GPE(0); pin <= SUNXI_GPE(24); pin++) {

if (pin >= SUNXI_GPE(20) && pin <= SUNXI_GPE(22))

continue; /* These pins are not LCD */

sunxi_gpio_set_cfgpin(pin, SUN8I_V3S_GPE_LCD);

}

printf("init v3s gpio e for lcd\n");

#elif defined(CONFIG_MACH_SUN8I_S3)

for (pin = SUNXI_GPD(0); pin <= SUNXI_GPD(21); pin++) {

sunxi_gpio_set_cfgpin(pin, SUNXI_GPD_LCD0);

sunxi_gpio_set_drv(pin, 3);

}

printf("init s3 gpio e for lcd\n");

#endif

#endif

}然后命令行运行:

fatload usb 0:1 0x43000000 800x480.bmp;bmp display 0x43000000 0 0

屏幕有反应了, 但是显示还不正常.

离线

#42 2021-04-28 11:12:19 分享评论

- wilik

- 会员

- 注册时间: 2021-04-14

- 已发帖子: 2

- 积分: 1.5

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

为什么从 S3 的datasheet里面找不到 DE2 相关的寄存器相关信息呢?

离线

#43 2021-04-30 09:54:55 分享评论

- MTLINUX

- 会员

- 注册时间: 2019-10-21

- 已发帖子: 29

- 积分: 1.5

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

马前卒 说:孤星泪 说:奇怪,我的荔枝派跑起来其它功能都正常,但是屏幕背光没有显示。

我的也是没有背光, 这就尴尬了, 看代码好像是 dts 驱动pwm0 (PB4) 实现的, 荔枝派的原理图也是这么接, 可是就是不亮.

修改这个文件: drivers/video/sunxi/sunxi_lcd.c

static void sunxi_lcdc_config_pinmux(void) { #if defined(CONFIG_MACH_SUN50I) || defined(CONFIG_MACH_SUN8I_V3S) || defined(CONFIG_MACH_SUN8I_S3) int pin; #if defined(CONFIG_MACH_SUN8I_V3S) #define SUN8I_V3S_GPE_LCD 3 for (pin = SUNXI_GPE(0); pin <= SUNXI_GPE(24); pin++) { if (pin >= SUNXI_GPE(20) && pin <= SUNXI_GPE(22)) continue; /* These pins are not LCD */ sunxi_gpio_set_cfgpin(pin, SUN8I_V3S_GPE_LCD); } printf("init v3s gpio e for lcd\n"); #elif defined(CONFIG_MACH_SUN8I_S3) for (pin = SUNXI_GPD(0); pin <= SUNXI_GPD(21); pin++) { sunxi_gpio_set_cfgpin(pin, SUNXI_GPD_LCD0); sunxi_gpio_set_drv(pin, 3); } printf("init s3 gpio e for lcd\n"); #endif #endif }然后命令行运行:

fatload usb 0:1 0x43000000 800x480.bmp;bmp display 0x43000000 0 0

屏幕有反应了, 但是显示还不正常.

v3s 修改设备树里lcd的参数,图片能显示正常。

但uboot启动时lcd还是没亮的,另外U盘也不支持;

离线

#44 2021-04-30 22:52:27 分享评论

- microxp

- 会员

- 注册时间: 2021-04-27

- 已发帖子: 76

- 积分: 124

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

感谢白嫖

离线

#45 2021-05-12 16:23:59 分享评论

- yangshuwei

- 会员

- 注册时间: 2020-03-22

- 已发帖子: 138

- 积分: 70

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

大佬,用你的uboot启动内核出现下面错误,需要做哪些设置呢

[ 1.862149] Kernel panic - not syncing: VFS: Unable to mount root fs on unknown-block(0,0)

[ 1.870417] CPU: 0 PID: 1 Comm: swapper/0 Not tainted 5.1.0 #26

[ 1.876332] Hardware name: Allwinner sun8i Family

[ 1.881076] [<c010ece0>] (unwind_backtrace) from [<c010b76c>] (show_stack+0x10/0x14)

[ 1.888831] [<c010b76c>] (show_stack) from [<c075ee50>] (dump_stack+0x84/0x98)

[ 1.896062] [<c075ee50>] (dump_stack) from [<c011dba4>] (panic+0x110/0x2b8)

[ 1.903032] [<c011dba4>] (panic) from [<c0a0130c>] (mount_block_root+0x1a0/0x288)

[ 1.910521] [<c0a0130c>] (mount_block_root) from [<c0a01538>] (mount_root+0x144/0x160)

[ 1.918442] [<c0a01538>] (mount_root) from [<c0a016a4>] (prepare_namespace+0x150/0x194)

[ 1.926452] [<c0a016a4>] (prepare_namespace) from [<c07773c8>] (kernel_init+0x8/0x10c)

[ 1.934376] [<c07773c8>] (kernel_init) from [<c01010e8>] (ret_from_fork+0x14/0x2c)

[ 1.941944] Exception stack(0xc6833fb0 to 0xc6833ff8)

[ 1.946997] 3fa0: 00000000 00000000 00000000 00000000

[ 1.955177] 3fc0: 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000

[ 1.963353] 3fe0: 00000000 00000000 00000000 00000000 00000013 00000000

[ 1.969981] ---[ end Kernel panic - not syncing: VFS: Unable to mount root fs on unknown-block(0,0) ]---感谢感谢

离线

#46 2021-05-12 17:37:05 分享评论

- unturned3

- 会员

- 注册时间: 2020-07-01

- 已发帖子: 272

- 积分: 301

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

大佬,用你的uboot启动内核出现下面错误,需要做哪些设置呢

好像有些重要信息被你截取掉了……发一下完整的log吧。

感觉一般 unable to mount rootfs 都是 kernel 没配置好的问题,和 u-boot 可能没关系?

最近编辑记录 unturned3 (2021-05-12 17:37:29)

离线

#47 2021-05-12 17:40:50 分享评论

- yangshuwei

- 会员

- 注册时间: 2020-03-22

- 已发帖子: 138

- 积分: 70

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

yangshuwei 说:大佬,用你的uboot启动内核出现下面错误,需要做哪些设置呢

好像有些重要信息被你截取掉了……发一下完整的log吧。

感觉一般 unable to mount rootfs 都是 kernel 没配置好的问题,和 u-boot 可能没关系?

U-Boot SPL 2020.04-00497-gc8aac3e-dirty (May 12 2021 - 17:32:37 +0800)

DRAM: 128 MiB

Trying to boot from FEL

U-Boot 2020.04-00497-gc8aac3e-dirty (May 12 2021 - 17:32:37 +0800) Allwinner Technology

CPU: Allwinner S3 (SUN8I 1681)

Model: Allwinner S3 Generic Device

DRAM: 128 MiB

MMC: mmc@01c0f000: 0, mmc@01c11000: 1

Loading Environment from FAT... Card did not respond to voltage select!

Error (-2): cannot determine file size

In: serial

Out: serial

Err: serial

Allwinner mUSB OTG (Peripheral)

Net: phy interface0

Warning: ethernet@1c30000 (eth0) using random MAC address - 02:60:b1:57:c3:3c

eth0: ethernet@1c30000

Warning: usb_ether using MAC address from ROM

, eth1: usb_ether

starting USB...

Bus usb@01c1a000: USB EHCI 1.00

Bus usb@01c1a400: USB OHCI 1.0

scanning bus usb@01c1a000 for devices... 1 USB Device(s) found

scanning bus usb@01c1a400 for devices... 1 USB Device(s) found

scanning usb for storage devices... 0 Storage Device(s) found

Hit any key to stop autoboot: 0

4672328 bytes read in 215 ms (20.7 MiB/s)

14088 bytes read in 3 ms (4.5 MiB/s)

## Flattened Device Tree blob at 41800000

Booting using the fdt blob at 0x41800000

Loading Device Tree to 42df9000, end 42dff707 ... OK

Starting kernel ...

[ 0.000000] Booting Linux on physical CPU 0x0

[ 0.000000] Linux version 5.1.0 (root@debian8) (gcc version 6.4.1 20170707 (Linaro GCC 6.4-2017.08)) #26 SMP Tue Jun 18 13:58:52 HKT 2019

[ 0.000000] CPU: ARMv7 Processor [410fc075] revision 5 (ARMv7), cr=10c5387d

[ 0.000000] CPU: div instructions available: patching division code

[ 0.000000] CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache

[ 0.000000] OF: fdt: Machine model: hqembed s3 lcd050ips

[ 0.000000] Memory policy: Data cache writealloc

[ 0.000000] cma: Reserved 16 MiB at 0x47000000

[ 0.000000] percpu: Embedded 16 pages/cpu s34572 r8192 d22772 u65536

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 32512

[ 0.000000] Kernel command line:

[ 0.000000] Dentry cache hash table entries: 16384 (order: 4, 65536 bytes)

[ 0.000000] Inode-cache hash table entries: 8192 (order: 3, 32768 bytes)

[ 0.000000] Memory: 102556K/131072K available (7168K kernel code, 326K rwdata, 1712K rodata, 1024K init, 253K bss, 12132K reserved, 16384K cma-reserved, 0K highmem)

[ 0.000000] SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=1, Nodes=1

[ 0.000000] rcu: Hierarchical RCU implementation.

[ 0.000000] rcu: RCU restricting CPUs from NR_CPUS=8 to nr_cpu_ids=1.

[ 0.000000] rcu: RCU calculated value of scheduler-enlistment delay is 10 jiffies.

[ 0.000000] rcu: Adjusting geometry for rcu_fanout_leaf=16, nr_cpu_ids=1

[ 0.000000] NR_IRQS: 16, nr_irqs: 16, preallocated irqs: 16

[ 0.000000] random: get_random_bytes called from start_kernel+0x2a0/0x42c with crng_init=0

[ 0.000000] arch_timer: cp15 timer(s) running at 24.00MHz (virt).

[ 0.000000] clocksource: arch_sys_counter: mask: 0xffffffffffffff max_cycles: 0x588fe9dc0, max_idle_ns: 440795202592 ns

[ 0.000008] sched_clock: 56 bits at 24MHz, resolution 41ns, wraps every 4398046511097ns

[ 0.000020] Switching to timer-based delay loop, resolution 41ns

[ 0.000212] clocksource: timer: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 79635851949 ns

[ 0.000451] Console: colour dummy device 80x30

[ 0.000721] printk: console [tty0] enabled

[ 0.000775] Calibrating delay loop (skipped), value calculated using timer frequency.. 48.00 BogoMIPS (lpj=240000)

[ 0.000804] pid_max: default: 32768 minimum: 301

[ 0.001008] Mount-cache hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.001040] Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.001795] *** VALIDATE proc ***

[ 0.002040] *** VALIDATE cgroup1 ***

[ 0.002071] *** VALIDATE cgroup2 ***

[ 0.002097] CPU: Testing write buffer coherency: ok

[ 0.002634] /cpus/cpu@0 missing clock-frequency property

[ 0.002682] CPU0: thread -1, cpu 0, socket 0, mpidr 80000000

[ 0.003564] Setting up static identity map for 0x40100000 - 0x40100060

[ 0.003818] rcu: Hierarchical SRCU implementation.

[ 0.004425] smp: Bringing up secondary CPUs ...

[ 0.004470] smp: Brought up 1 node, 1 CPU

[ 0.004488] SMP: Total of 1 processors activated (48.00 BogoMIPS).

[ 0.004504] CPU: All CPU(s) started in SVC mode.

[ 0.005443] devtmpfs: initialized

[ 0.009381] VFP support v0.3: implementor 41 architecture 2 part 30 variant 7 rev 5

[ 0.009719] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604462750000 ns

[ 0.009774] futex hash table entries: 256 (order: 2, 16384 bytes)

[ 0.010780] pinctrl core: initialized pinctrl subsystem

[ 0.012139] NET: Registered protocol family 16

[ 0.013672] DMA: preallocated 256 KiB pool for atomic coherent allocations

[ 0.014892] hw-breakpoint: found 5 (+1 reserved) breakpoint and 4 watchpoint registers.

[ 0.014940] hw-breakpoint: maximum watchpoint size is 8 bytes.

[ 0.044538] SCSI subsystem initialized

[ 0.044865] usbcore: registered new interface driver usbfs

[ 0.044954] usbcore: registered new interface driver hub

[ 0.045084] usbcore: registered new device driver usb

[ 0.045368] media: Linux media interface: v0.10

[ 0.045430] videodev: Linux video capture interface: v2.00

[ 0.045495] pps_core: LinuxPPS API ver. 1 registered

[ 0.045512] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it>

[ 0.045558] PTP clock support registered

[ 0.045857] Advanced Linux Sound Architecture Driver Initialized.

[ 0.046569] Bluetooth: Core ver 2.22

[ 0.046687] NET: Registered protocol family 31

[ 0.046708] Bluetooth: HCI device and connection manager initialized

[ 0.046740] Bluetooth: HCI socket layer initialized

[ 0.046759] Bluetooth: L2CAP socket layer initialized

[ 0.046799] Bluetooth: SCO socket layer initialized

[ 0.047685] clocksource: Switched to clocksource arch_sys_counter

[ 0.060511] NET: Registered protocol family 2

[ 0.061276] tcp_listen_portaddr_hash hash table entries: 512 (order: 0, 6144 bytes)

[ 0.061343] TCP established hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.061388] TCP bind hash table entries: 1024 (order: 1, 8192 bytes)

[ 0.061419] TCP: Hash tables configured (established 1024 bind 1024)

[ 0.061592] UDP hash table entries: 256 (order: 1, 8192 bytes)

[ 0.061662] UDP-Lite hash table entries: 256 (order: 1, 8192 bytes)

[ 0.061934] NET: Registered protocol family 1

[ 0.062963] RPC: Registered named UNIX socket transport module.

[ 0.063014] RPC: Registered udp transport module.

[ 0.063027] RPC: Registered tcp transport module.

[ 0.063039] RPC: Registered tcp NFSv4.1 backchannel transport module.

[ 0.065572] Initialise system trusted keyrings

[ 0.066040] workingset: timestamp_bits=30 max_order=15 bucket_order=0

[ 0.074652] NFS: Registering the id_resolver key type

[ 0.074732] Key type id_resolver registered

[ 0.074747] Key type id_legacy registered

[ 0.074822] Key type asymmetric registered

[ 0.074839] Asymmetric key parser 'x509' registered

[ 0.074923] Block layer SCSI generic (bsg) driver version 0.4 loaded (major 247)

[ 0.074949] io scheduler mq-deadline registered

[ 0.074963] io scheduler kyber registered

[ 0.080848] sun8i-v3s-pinctrl 1c20800.pinctrl: initialized sunXi PIO driver

[ 0.155292] Serial: 8250/16550 driver, 8 ports, IRQ sharing disabled

[ 0.157957] sun8i-v3s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pb not found, using dummy regulator

[ 0.179495] 1c28000.serial: ttyS0 at MMIO 0x1c28000 (irq = 38, base_baud = 1500000) is a U6_16550A

[ 0.753955] printk: console [ttyS0] enabled

[ 0.758879] sun8i-v3s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pg not found, using dummy regulator

[ 0.790342] 1c28400.serial: ttyS1 at MMIO 0x1c28400 (irq = 39, base_baud = 1500000) is a U6_16550A

[ 0.821347] 1c28800.serial: ttyS2 at MMIO 0x1c28800 (irq = 40, base_baud = 1500000) is a U6_16550A

[ 0.855012] libphy: Fixed MDIO Bus: probed

[ 0.859295] CAN device driver interface

[ 0.863756] dwmac-sun8i 1c30000.ethernet: PTP uses main clock

[ 0.869683] dwmac-sun8i 1c30000.ethernet: No regulator found

[ 0.876005] dwmac-sun8i 1c30000.ethernet: Current syscon value is not the default 148000 (expect 38000)

[ 0.885544] dwmac-sun8i 1c30000.ethernet: No HW DMA feature register supported

[ 0.892806] dwmac-sun8i 1c30000.ethernet: RX Checksum Offload Engine supported

[ 0.900052] dwmac-sun8i 1c30000.ethernet: COE Type 2

[ 0.905020] dwmac-sun8i 1c30000.ethernet: TX Checksum insertion supported

[ 0.911824] dwmac-sun8i 1c30000.ethernet: Normal descriptors

[ 0.917484] dwmac-sun8i 1c30000.ethernet: Chain mode enabled

[ 0.923178] dwmac-sun8i 1c30000.ethernet (unnamed net_device) (uninitialized): device MAC address 36:c2:66:0a:5f:7a

[ 0.933876] libphy: stmmac: probed

[ 0.938114] dwmac-sun8i 1c30000.ethernet: Found internal PHY node

[ 0.944460] libphy: mdio_mux: probed

[ 0.948171] dwmac-sun8i 1c30000.ethernet: Switch mux to internal PHY

[ 0.954543] dwmac-sun8i 1c30000.ethernet: Powering internal PHY

[ 0.961791] libphy: mdio_mux: probed

[ 0.965874] ehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver

[ 0.972550] ehci-platform: EHCI generic platform driver

[ 0.978149] ehci-platform 1c1a000.usb: EHCI Host Controller

[ 0.983805] ehci-platform 1c1a000.usb: new USB bus registered, assigned bus number 1

[ 0.992111] ehci-platform 1c1a000.usb: irq 28, io mem 0x01c1a000

[ 1.027683] ehci-platform 1c1a000.usb: USB 2.0 started, EHCI 1.00

[ 1.035006] hub 1-0:1.0: USB hub found

[ 1.039016] hub 1-0:1.0: 1 port detected

[ 1.043749] ohci_hcd: USB 1.1 'Open' Host Controller (OHCI) Driver

[ 1.050119] ohci-platform: OHCI generic platform driver

[ 1.055717] ohci-platform 1c1a400.usb: Generic Platform OHCI controller

[ 1.062469] ohci-platform 1c1a400.usb: new USB bus registered, assigned bus number 2

[ 1.070696] ohci-platform 1c1a400.usb: irq 29, io mem 0x01c1a400

[ 1.142865] hub 2-0:1.0: USB hub found

[ 1.146738] hub 2-0:1.0: 1 port detected

[ 1.152098] usbcore: registered new interface driver usb-storage

[ 1.158451] usbcore: registered new interface driver usbserial_generic

[ 1.165041] usbserial: USB Serial support registered for generic

[ 1.171705] usb_phy_generic usb_phy_generic.0.auto: usb_phy_generic.0.auto supply vcc not found, using dummy regulator

[ 1.183336] musb-hdrc musb-hdrc.1.auto: MUSB HDRC host driver

[ 1.189218] musb-hdrc musb-hdrc.1.auto: new USB bus registered, assigned bus number 3

[ 1.198518] hub 3-0:1.0: USB hub found

[ 1.202389] hub 3-0:1.0: 1 port detected

[ 1.207877] dummy_hcd dummy_hcd.0: USB Host+Gadget Emulator, driver 02 May 2005

[ 1.215239] dummy_hcd dummy_hcd.0: Dummy host controller

[ 1.220622] dummy_hcd dummy_hcd.0: new USB bus registered, assigned bus number 4

[ 1.229237] hub 4-0:1.0: USB hub found

[ 1.233118] hub 4-0:1.0: 1 port detected

[ 1.239053] input: 1c22800.lradc as /devices/platform/soc/1c22800.lradc/input/input0

[ 1.248397] sun6i-rtc 1c20400.rtc: registered as rtc0

[ 1.253482] sun6i-rtc 1c20400.rtc: RTC enabled

[ 1.258258] i2c /dev entries driver

[ 1.263490] sun8i-v3s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pe not found, using dummy regulator

[ 1.276934] sunxi-wdt 1c20ca0.watchdog: Watchdog enabled (timeout=16 sec, nowayout=0)

[ 1.285075] Bluetooth: HCI UART driver ver 2.3

[ 1.289586] Bluetooth: HCI UART protocol H4 registered

[ 1.295735] sun8i-v3s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pf not found, using dummy regulator

[ 1.307099] sunxi-mmc 1c0f000.mmc: Got CD GPIO

[ 1.337314] sunxi-mmc 1c0f000.mmc: initialized, max. request size: 16384 KB

[ 1.346235] sunxi-mmc 1c10000.mmc: allocated mmc-pwrseq

[ 1.376139] sunxi-mmc 1c10000.mmc: initialized, max. request size: 16384 KB

[ 1.383490] sun8i-v3s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pc not found, using dummy regulator

[ 1.404163] mmc0: host does not support reading read-only switch, assuming write-enable

[ 1.417189] mmc0: new high speed SDHC card at address aaaa

[ 1.423216] sunxi-mmc 1c11000.mmc: initialized, max. request size: 16384 KB

[ 1.431901] usbcore: registered new interface driver usbhid

[ 1.437506] usbhid: USB HID core driver

[ 1.444127] mmcblk0: mmc0:aaaa SC16G 14.8 GiB

[ 1.452638] sun4i-codec 1c22c00.codec: ASoC: codec-analog@01c23000 not registered

[ 1.460378] sun4i-codec 1c22c00.codec: Failed to register our card

[ 1.467001] mmcblk0: p1 p2

[ 1.473302] NET: Registered protocol family 17

[ 1.477970] can: controller area network core (rev 20170425 abi 9)

[ 1.484306] NET: Registered protocol family 29

[ 1.488826] can: raw protocol (rev 20170425)

[ 1.493105] can: broadcast manager protocol (rev 20170425 t)

[ 1.498798] can: netlink gateway (rev 20170425) max_hops=1

[ 1.504648] Key type dns_resolver registered

[ 1.509035] Registering SWP/SWPB emulation handler

[ 1.514404] mmc1: new high speed SDIO card at address 0001

[ 1.521203] Loading compiled-in X.509 certificates

[ 1.534613] sun4i-codec 1c22c00.codec: Codec <-> 1c22c00.codec mapping ok

[ 1.543405] sun6i-rtc 1c20400.rtc: setting system clock to 1970-01-01T03:47:00 UTC (13620)

[ 1.552055] cfg80211: Loading compiled-in X.509 certificates for regulatory database

[ 1.563844] cfg80211: Loaded X.509 cert 'sforshee: 00b28ddf47aef9cea7'

[ 1.570681] vcc5v0: disabling

[ 1.573672] ALSA device list:

[ 1.576645] #0: V3s Audio Codec

[ 1.580931] platform regulatory.0: Direct firmware load for regulatory.db failed with error -2

[ 1.589710] cfg80211: failed to load regulatory.db

[ 1.595277] VFS: Cannot open root device "(null)" or unknown-block(0,0): error -6

[ 1.602946] Please append a correct "root=" boot option; here are the available partitions:

[ 1.611360] b300 15558144 mmcblk0

[ 1.611365] driver: mmcblk

[ 1.618197] b301 51200 mmcblk0p1 33c8c247-01

[ 1.618199]

[ 1.625003] b302 15505408 mmcblk0p2 33c8c247-02

[ 1.625005]

[ 1.631830] Kernel panic - not syncing: VFS: Unable to mount root fs on unknown-block(0,0)

[ 1.640098] CPU: 0 PID: 1 Comm: swapper/0 Not tainted 5.1.0 #26

[ 1.646013] Hardware name: Allwinner sun8i Family

[ 1.650756] [<c010ece0>] (unwind_backtrace) from [<c010b76c>] (show_stack+0x10/0x14)

[ 1.658511] [<c010b76c>] (show_stack) from [<c075ee50>] (dump_stack+0x84/0x98)

[ 1.665743] [<c075ee50>] (dump_stack) from [<c011dba4>] (panic+0x110/0x2b8)

[ 1.672714] [<c011dba4>] (panic) from [<c0a0130c>] (mount_block_root+0x1a0/0x288)

[ 1.680203] [<c0a0130c>] (mount_block_root) from [<c0a01538>] (mount_root+0x144/0x160)

[ 1.688123] [<c0a01538>] (mount_root) from [<c0a016a4>] (prepare_namespace+0x150/0x194)

[ 1.696133] [<c0a016a4>] (prepare_namespace) from [<c07773c8>] (kernel_init+0x8/0x10c)

[ 1.704055] [<c07773c8>] (kernel_init) from [<c01010e8>] (ret_from_fork+0x14/0x2c)

[ 1.711625] Exception stack(0xc6833fb0 to 0xc6833ff8)

[ 1.716678] 3fa0: 00000000 00000000 00000000 00000000

[ 1.724857] 3fc0: 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000

[ 1.733034] 3fe0: 00000000 00000000 00000000 00000000 00000013 00000000

[ 1.739662] ---[ end Kernel panic - not syncing: VFS: Unable to mount root fs on unknown-block(0,0) ]---离线

#48 2021-07-16 14:30:02 分享评论

- xiaohui

- 会员

- 注册时间: 2019-01-15

- 已发帖子: 259

- 积分: 122.5

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

大佬牛皮啊,超感谢大佬的贡献

离线

#49 2021-09-01 17:19:57 分享评论

- ubuntu

- 会员

- 注册时间: 2020-03-30

- 已发帖子: 332

- 积分: 310

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

奇怪,我的背光也亮不起来。

离线

#50 2021-09-01 22:01:23 分享评论

- tigger

- Moderator

- 注册时间: 2021-06-18

- 已发帖子: 172

- 积分: 111

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

奇怪,我的背光也亮不起来。

以前玩过,pwm感觉是有bug,用uboot命令行

gpio set pb4

就可以点亮屏幕。

离线

#51 2021-09-15 15:39:33 分享评论

- qianfan

- 会员

- 注册时间: 2019-11-29

- 已发帖子: 38

- 积分: 106.5

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

fastboot oem format这个学到了, 真好用

离线

#52 2021-10-07 12:20:57 分享评论

- 奔跑的孩子

- 会员

- 注册时间: 2021-01-28

- 已发帖子: 51

- 积分: 31.5

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

流氓兔 说:好像不支持 SPI FLASH, 大佬可以把这个代码合并进去吗?

https://github.com/Lichee-Pi/u-boot/commits/v3s-spi-experimental

等我有能测试SPI设备的时候再搞

基本全了,只差SPI FLASH

离线

#53 2022-05-05 01:30:25 分享评论

- screep

- 会员

- 注册时间: 2022-04-28

- 已发帖子: 2

- 积分: 22

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

大家好你们好!

你能帮我设置连接到 S3 MCU PD0-PD21 端口的 LCD 显示器吗? 我已经克隆了这个存储库,但是 LCD 引脚上没有任何活动。 我应该检查什么才能确定,液晶显示器没问题。 硬件看起来不错。

先感谢您

期待您的回复。

离线

#54 2022-05-05 08:45:44 分享评论

离线

#55 2022-05-05 12:10:02 分享评论

- screep

- 会员

- 注册时间: 2022-04-28

- 已发帖子: 2

- 积分: 22

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

@哇酷小二

不,这些引脚上没有任何活动。

离线

#56 2022-07-27 12:44:09 分享评论

- ronz

- 会员

- 注册时间: 2021-11-19

- 已发帖子: 31

- 积分: 11

Re: Allwinner S3 u-boot 2020.04 (DisplayEngine2 + Fastboot线刷)

大佬,我好奇你的开机logo实现了吗?不知道能不能运行

离线

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发