楼主 # 2022-07-12 09:08:08 分享评论

众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

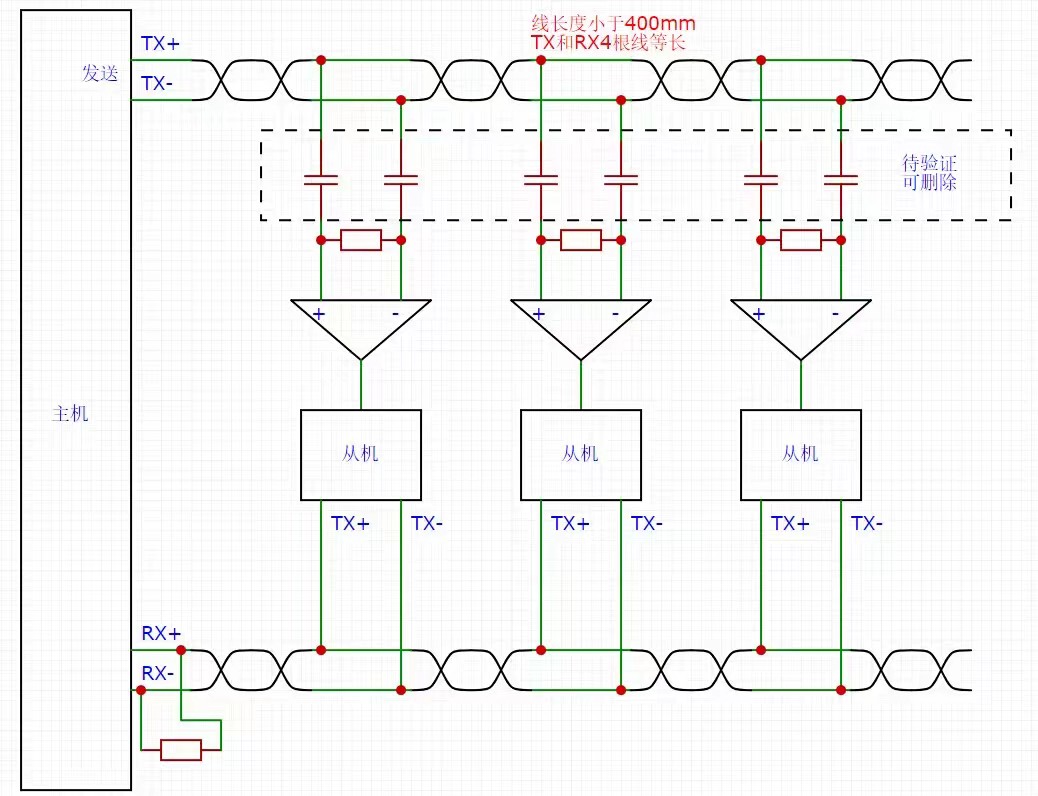

出发点:需要做个可扩展的控制器,类似PLC,IO点不够可以增加扩展模块来扩充IO,没有485等串口,可以增加扩展模块来扩充。

西门子 PLC图片如下:

CPU主控打算用全志T113系列,

考虑扩展模块上芯片不会用太高端,所以只能从UART、SPI、I2C、RS485、CAN这类的去考虑,

1、需要多从机

2、需要高速

3、需要远距离抗干扰,比如CPU挂10个扩展模块,线长都出去了半米了。

综合考虑,T113处选择SPI接口,

使用将SPI改为3线,使用CLK、MOSI、MISO

考虑远距离传输的抗干扰性,将3根信号线变为差分信号。

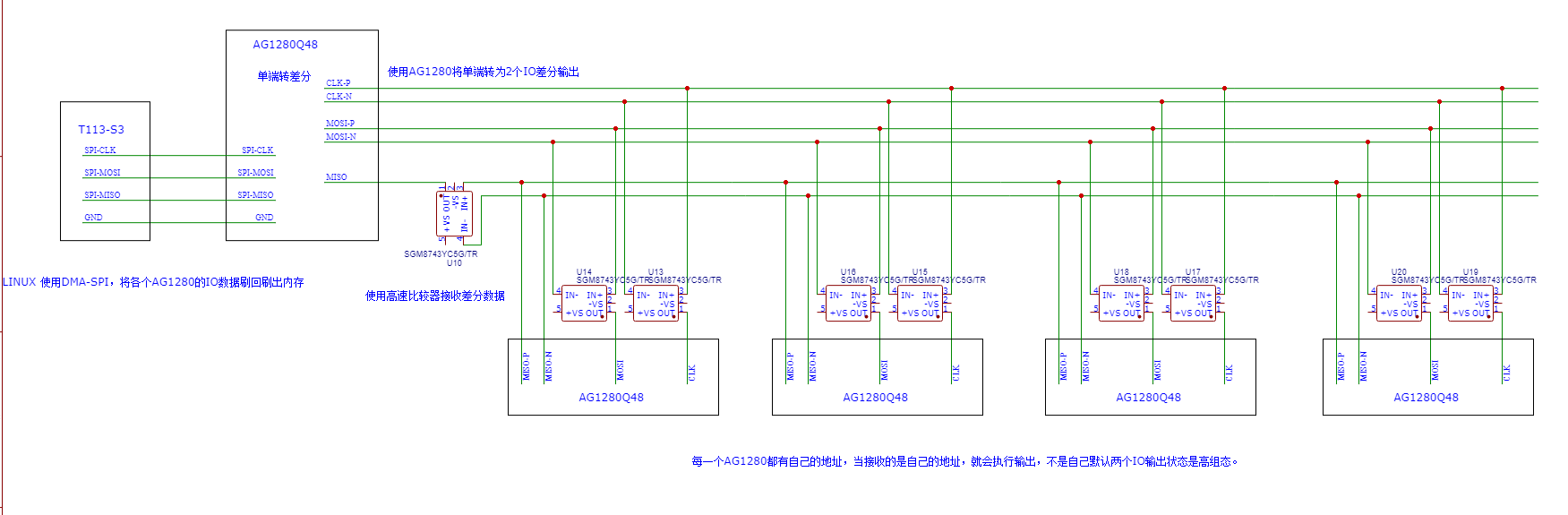

T113连接CPLD,CPLD将单端信号变为两个端口输出,来模拟差分线。

在接收端,使用高速比较器进行接收数据,市面在售的7ns比较器比较便宜。

增加总线的地址机制,每个从设备都有地址,当收到自己地址的数据需要发送时才会进行发送,否则发送为高阻态。

下面是初版设计原理图,

离线

楼主 #1 2022-07-12 09:11:27 分享评论

#2 2022-07-12 13:44:07 分享评论

- jiaowoxiaolu

- 会员

- 注册时间: 2021-08-27

- 已发帖子: 48

- 积分: 64

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

cpld不需要吧,直接用max485芯片或者mcp2551这类转一下就行了,专门转差分就用一颗CPLD大材小用了

离线

#3 2022-07-12 13:52:14 分享评论

- jiaowoxiaolu

- 会员

- 注册时间: 2021-08-27

- 已发帖子: 48

- 积分: 64

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

SN65LVDS049 这个应该正好

http://www.ti.com/cn/lit/gpn/sn65lvds049

离线

#4 2022-07-12 13:54:20 分享评论

- le062

- 会员

- 注册时间: 2019-02-07

- 已发帖子: 75

- 积分: 65.5

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

既然上了CPLD,直接把从机串联呗。

上电后,主机从0开始发地址,从机若无地址,则应答,若有地址则发给下一个从机,进而完成自动地址配发。

运行时,CPLD的串联延迟可以做到很低,所以也不会影响速率,而且还能起到中继效果,规避了信号完整性问题。

离线

#5 2022-07-12 13:56:27 分享评论

- le062

- 会员

- 注册时间: 2019-02-07

- 已发帖子: 75

- 积分: 65.5

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

补充下,串联方案对于SPI这种同步信号可能不合适,CLK与MISO容易出现同步问题。更适合串口类的异步信号

离线

#6 2022-07-12 14:31:43 分享评论

- Gentlepig

- 会员

- 注册时间: 2018-10-24

- 已发帖子: 1,409

- 积分: 1373.5

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

为何MISO不也用差分信号呢?

还有,想请教下,想这种从机串联方式,从机的单片机供电是不是也需要从这样的总线上采呢?如果是的话,总线上直接传输单片机需要的5V或3.3V,电压会不稳定吧?

以前拆过一个台达的PLC及扩展模块,貌似就是采用的SPI扩展,不过貌似没有改成差分信号。

最近编辑记录 Gentlepig (2022-07-12 14:32:42)

离线

楼主 #7 2022-07-12 14:44:43 分享评论

楼主 #8 2022-07-12 14:45:29 分享评论

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

SN65LVDS049 这个应该正好

http://www.ti.com/cn/lit/gpn/sn65lvds049

我看了TI的lvds类转换芯片,价格比较贵,所以排除了。

离线

楼主 #9 2022-07-12 14:51:03 分享评论

楼主 #10 2022-07-12 14:51:47 分享评论

#11 2022-07-12 15:27:14 分享评论

- 1847123212

- 会员

- 注册时间: 2019-11-21

- 已发帖子: 70

- 积分: 46

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

如果没记错的话,这个方案我们已经有专利了

离线

#12 2022-07-12 15:52:44 分享评论

- 阿黄

- 会员

- 注册时间: 2018-10-03

- 已发帖子: 299

- 积分: 134

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

不考虑CAN吗?

离线

楼主 #13 2022-07-12 16:02:05 分享评论

#14 2022-07-12 23:38:10 分享评论

- tpu

- 会员

- 注册时间: 2020-06-15

- 已发帖子: 40

- 积分: 42.5

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

离线

#15 2022-07-13 07:32:20 分享评论

- 阿黄

- 会员

- 注册时间: 2018-10-03

- 已发帖子: 299

- 积分: 134

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

@Gentlepig

MISO和MOSI都用差分了,MISO是soc输入端,不是输出。

多谢信息分享,台达用的spi,

考虑稳定性,所以我加差分。扩展模块的核心供电可以从总线上取,但输出不从总线上取,扩展模块需要外供电。

单向发送肯定没问题,但接收数据时,CLK和MISO的相位并不一致,因为CLK是主机端发出,而MISO是从机端发出。是降低速度还是做延迟补偿?

离线

#18 2022-07-13 10:25:32 分享评论

- 阿黄

- 会员

- 注册时间: 2018-10-03

- 已发帖子: 299

- 积分: 134

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

我的箱内总线都用I2C了,便宜。

T113要是支持CAN-FD就好了

## 箱内通讯总线

- I2C✅

- 速率尚可

- 怕干扰(可屏蔽)

- 485❌

- 速率略高

- 要收发器

- CAN❌

- 速度较高

- 要收发器(还挺贵)

CAN收发器还好,TJA1042T/1J也只要5块钱左右, 同样I2C做板间总线,也需要加总线驱动芯片来吧

离线

#19 2022-07-13 10:27:14 分享评论

- 阿黄

- 会员

- 注册时间: 2018-10-03

- 已发帖子: 299

- 积分: 134

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

@阿黄

我之前使用485芯片来延长SPI总线,挂接HC595/HC165,线越长,相位偏移,走形便越厉害。

如果器件传输延迟低,SPI CLK不要太高,感觉没问题。

如果挂多个从机,不同距离的从机,相位偏移也不同,还必须要区别对待- -

离线

楼主 #20 2022-07-13 12:51:58 分享评论

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

多谢大佬分享,是个参考项!

离线

楼主 #21 2022-07-13 12:56:01 分享评论

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

@阿黄

我之前使用485芯片来延长SPI总线,挂接HC595/HC165,线越长,相位偏移,走形便越厉害。

如果器件传输延迟低,SPI CLK不要太高,感觉没问题。

大佬能详细讲讲,吗?

你是用的RS485芯片对SPI进行延长,

也就是MOSI和CLK用了两个485芯片,

在设备HC595端也放了两个485芯片进行接收,

转出来的CLK和MOSI相位对不上吗?

单向发送也有相位偏移的问题吗?

我的从机器件打算用CPLD做,响应时间应该挺快的。

我其实有往100M跑的打算

离线

楼主 #22 2022-07-13 12:59:10 分享评论

#23 2022-07-13 15:04:35 分享评论

- yobbo

- 会员

- 注册时间: 2019-12-09

- 已发帖子: 83

- 积分: 181.5

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

做过类似的,已经稳定量产,如果主机到模块的长度不定,这种方案很有可能出问题,就是clk和miso的同步问题,已经踩过坑了。

实际使用方案是用了两种:

一种是利用cpld进行一个读取字节的延时;(也测试了一种,上电后先进行主机和从机模块的握手,根据握手时间进行速度调整,后面软件优化一直有问题,废弃了)

另一种就是利用两个spi端口进行通讯,主机和从机都有单独的clk;

离线

楼主 #24 2022-07-13 17:58:24 分享评论

楼主 #26 2022-07-13 22:25:44 分享评论

#27 2022-07-13 23:21:18 分享评论

- david

- 会员

- 注册时间: 2018-03-05

- 已发帖子: 397

- 积分: 328.5

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

都用1280了 做个协议转换 用8/10编码不是更省事

离线

#28 2022-07-13 23:23:09 分享评论

- david

- 会员

- 注册时间: 2018-03-05

- 已发帖子: 397

- 积分: 328.5

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

如果没记错的话,这个方案我们已经有专利了

专利号是啥?

离线

#29 2022-07-13 23:24:18 分享评论

- david

- 会员

- 注册时间: 2018-03-05

- 已发帖子: 397

- 积分: 328.5

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

大家还有什么建议和想法?这周我再总结一下,画下改进后的【迪卡总线】

已了解台达plc用的spi,已了解西门子背板总线用的无cs的spi,即全双工i2c。

你这距离要多远 多高的速率 延迟啥要求

离线

楼主 #30 2022-07-14 08:50:25 分享评论

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

迪卡 说:大家还有什么建议和想法?这周我再总结一下,画下改进后的【迪卡总线】

已了解台达plc用的spi,已了解西门子背板总线用的无cs的spi,即全双工i2c。你这距离要多远 多高的速率 延迟啥要求

前面说了个大概,最远距离半米吧,上面挂接多个从设备。

速率需求就是主机发出控制某个IO的命令或是读取某个IO的状态,时间小于1us吧,先这样暂时定一个。

假设读取一个IO状态连发送带接收需要32bit的数据,那么32bit宽裕点算,按50bit算,获取IO状态用时按小于1us.

那么时钟频率最少需要50MHz

离线

#31 2022-07-14 11:15:20 分享评论

- mengxp

- 会员

- 注册时间: 2021-10-07

- 已发帖子: 68

- 积分: 152

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

@迪卡

你主机要是用linux怕是远远达不到这个要求。

离线

#32 2022-07-14 12:26:49 分享评论

- Gentlepig

- 会员

- 注册时间: 2018-10-24

- 已发帖子: 1,409

- 积分: 1373.5

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

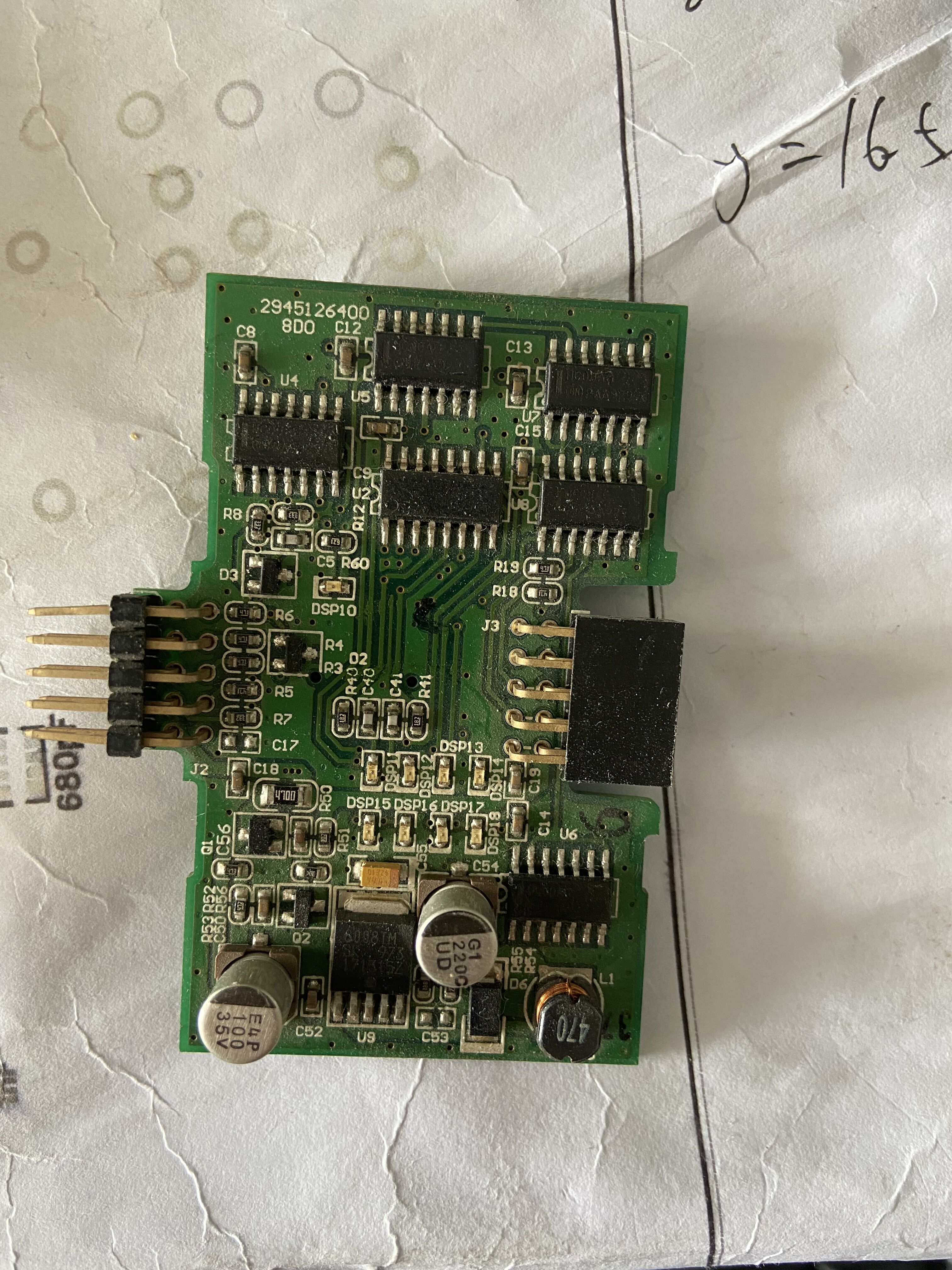

可以看到右侧带针的那个端子,是接到主机的。

看丝印,依次是:

C2-CLK C1-SDI

C3-SDO GND

C4-LATCH GND

C5-DE BOOT

C6-CS +24V

左侧接下一个模组的端子的丝印:

N_C1 N_C2

GND N_C3

GND N_C4

ITS N_C5

估计是24V N_C6

最近编辑记录 Gentlepig (2022-07-15 09:46:41)

离线

#33 2022-07-14 13:19:46 分享评论

- Gentlepig

- 会员

- 注册时间: 2018-10-24

- 已发帖子: 1,409

- 积分: 1373.5

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

当时画了一半的原理图。CD4094是将数据转为8位并口通过端子连到了下面的IO板,8个输出。

SPI如何传到下一级,没搞明白。尤其是DE,LATCH,BOOT这几个引脚的作用。

--------------------------------------

板子上有个24V转5V电路,靠近这部分也有个74HC00,感觉boot管脚和这部分有关。

上个楼层中的顶视图里,中间考上的那个是4094芯片,右上角是74HC08,其余全是74HC00。

最近编辑记录 Gentlepig (2022-07-14 13:28:53)

离线

楼主 #35 2022-07-15 21:23:41 分享评论

楼主 #36 2022-07-16 20:19:50 分享评论

楼主 #37 2022-07-16 20:24:15 分享评论

#38 2022-07-16 21:34:08 分享评论

- grantho

- 会员

- 注册时间: 2020-03-21

- 已发帖子: 71

- 积分: 2.5

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

要接的线有点多了

离线

楼主 #39 2022-07-16 21:47:59 分享评论

#40 2022-07-16 23:21:54 分享评论

- wurst

- 会员

- 注册时间: 2019-09-20

- 已发帖子: 7

- 积分: 2

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

以前做个类似的产品,主模块+N个扩展模块。采用SPI+N个片选。每个模块内置总线驱动器,片选采用递推方式,自动自增。

离线

楼主 #41 2022-07-17 11:30:21 分享评论

#42 2022-07-17 19:39:18 分享评论

- echo

- 会员

- 注册时间: 2020-04-16

- 已发帖子: 364

- 积分: 370.5

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

ADI(LINEAR)的BMS AFE芯片,用的isoSPI接口,就是干这个的。也有独立的芯片将SPI接口转isoSPI,型号LTC6820

最近编辑记录 echo (2022-07-17 19:41:09)

离线

楼主 #43 2022-07-18 11:58:20 分享评论

楼主 #44 2022-07-19 21:48:09 分享评论

#45 2022-07-20 01:25:36 分享评论

- david

- 会员

- 注册时间: 2018-03-05

- 已发帖子: 397

- 积分: 328.5

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

这种并联差分总线 应该只需要在终端做终结

离线

#46 2022-07-20 08:26:23 分享评论

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

https://whycan.com/files/members/1228/bf17a44ca6a9711dd2e93423cb844b6.png

这个电路是我比较倾向的。

在上电时,MUX都会打到终端电阻位置,

这样只有离CPU单元最近的模块能被访问到,就可以依次进行地址赋值。

我感觉原理是没有问题了,但往往这种自定义的设计,会因为开发时间久,测试不方便,成本不够低,不好落地。

离线

楼主 #47 2022-07-20 12:57:55 分享评论

#48 2025-02-11 16:11:03 分享评论

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

@迪卡

@LinjieGuo

@yobbo

spi 时钟延迟的问题,一般是半个周期为单位调整,一个周期步进太大,小于半个周期硬件不好实现

我写过一遍文章,免协商固定半个周期,不用增加等待字节,实现简单,含 verilog 实现代码:

离线

#50 2025-03-14 16:16:38 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】

@迪卡

对哦,为什么不用网口

离线

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发