#5 全志 SOC » t113 到底怎样才能将jtag引脚从pf重映射到pe啊? » 2025-07-08 16:06:18

- zm

- 回复: 6

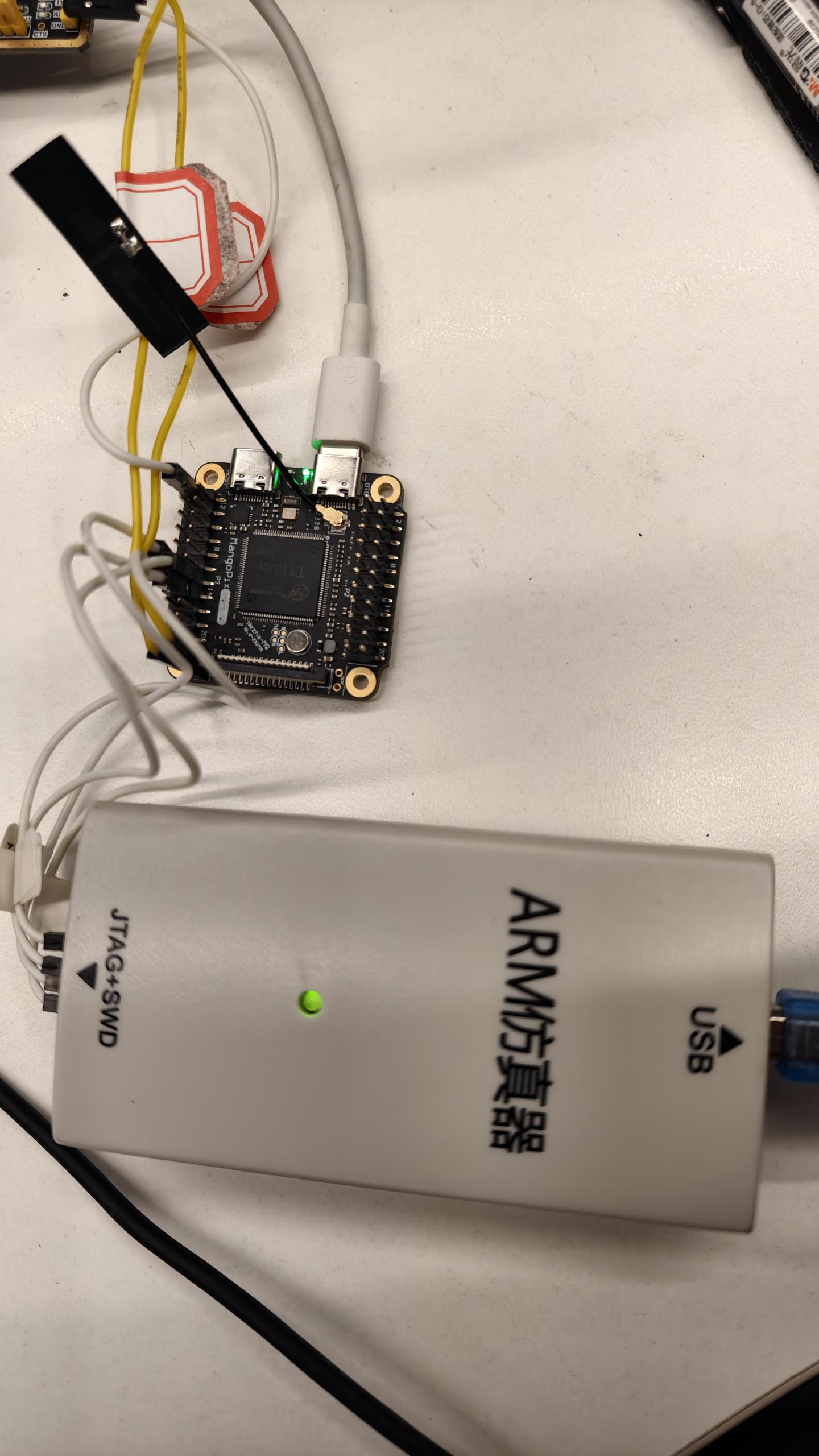

最近一直在研究openocd + jlink方式调试t113裸机,

目前t113s3 如果使用sd0引脚作为jtag引脚的话,看下面的打印应该算是连上了。

C:\msys64\mingw64\bin>openocd.exe -f t113s3-mangguo.cfg -f t113s3.cfg -d -s E:\资料\T113S3\

Open On-Chip Debugger 0.12.0

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

User : 3 3 options.c:52 configuration_output_handler(): debug_level: 3

User : 4 5 options.c:52 configuration_output_handler():

Debug: 5 7 configuration.c:33 add_script_search_dir(): adding E:\资料\T113S3\

Debug: 6 9 options.c:233 add_default_dirs(): bindir=D:/a/msys64/mingw64/bin

Debug: 7 11 options.c:234 add_default_dirs(): pkgdatadir=D:/a/msys64/mingw64/share/openocd

Debug: 8 13 options.c:235 add_default_dirs(): exepath=C:/msys64/mingw64/bin

Debug: 9 15 options.c:236 add_default_dirs(): bin2data=../share/openocd

Debug: 10 17 configuration.c:33 add_script_search_dir(): adding C:/Users/17204/AppData/Roaming/OpenOCD

Debug: 11 19 configuration.c:33 add_script_search_dir(): adding C:/msys64/mingw64/bin/../share/openocd/site

Debug: 12 24 configuration.c:33 add_script_search_dir(): adding C:/msys64/mingw64/bin/../share/openocd/scripts

Debug: 13 26 command.c:155 script_debug(): command - ocd_find t113s3-mangguo.cfg

Debug: 14 28 configuration.c:88 find_file(): found E:\资料\T113S3\/t113s3-mangguo.cfg

Debug: 15 31 command.c:155 script_debug(): command - ocd_find interface/jlink.cfg

Debug: 16 33 configuration.c:88 find_file(): found C:/msys64/mingw64/bin/../share/openocd/scripts/interface/jlink.cfg

Debug: 17 36 command.c:155 script_debug(): command - adapter driver jlink

Debug: 18 39 command.c:155 script_debug(): command - adapter speed 1000

Debug: 19 41 adapter.c:251 adapter_config_khz(): handle adapter khz

Debug: 20 42 adapter.c:215 adapter_khz_to_speed(): convert khz to adapter specific speed value

Debug: 21 45 adapter.c:215 adapter_khz_to_speed(): convert khz to adapter specific speed value

Debug: 22 47 command.c:155 script_debug(): command - transport select jtag

User : 23 49 options.c:52 configuration_output_handler(): jtagUser : 24 50 options.c:52 configuration_output_handler():

Debug: 25 51 command.c:155 script_debug(): command - ocd_find t113s3.cfg

Debug: 26 55 configuration.c:88 find_file(): found E:\资料\T113S3\/t113s3.cfg

Debug: 27 57 command.c:155 script_debug(): command - reset_config none srst_pulls_trst

Debug: 28 59 command.c:155 script_debug(): command - jtag newtap t113s3 cpu -irlen 4 -ircapture 0x01 -irmask 0x0f -expected-id 0x5ba00477

Debug: 29 62 tcl.c:557 jim_newtap_cmd(): Creating New Tap, Chip: t113s3, Tap: cpu, Dotted: t113s3.cpu, 8 params

Debug: 30 65 tcl.c:582 jim_newtap_cmd(): Processing option: -irlen

Debug: 31 67 tcl.c:582 jim_newtap_cmd(): Processing option: -ircapture

Debug: 32 70 tcl.c:582 jim_newtap_cmd(): Processing option: -irmask

Debug: 33 72 tcl.c:582 jim_newtap_cmd(): Processing option: -expected-id

Debug: 34 74 core.c:1474 jtag_tap_init(): Created Tap: t113s3.cpu @ abs position 0, irlen 4, capture: 0x1 mask: 0xf

Debug: 35 76 command.c:155 script_debug(): command - dap create t113s3.dap -chain-position t113s3.cpu

Debug: 36 79 command.c:155 script_debug(): command - target create t113s3.cpu cortex_a -dap t113s3.dap

Info : 37 82 server.c:297 add_service(): Listening on port 6666 for tcl connections

Info : 38 85 server.c:297 add_service(): Listening on port 4444 for telnet connections

Debug: 39 88 command.c:155 script_debug(): command - init

Debug: 40 89 command.c:155 script_debug(): command - target init

Debug: 41 91 command.c:155 script_debug(): command - target names

Debug: 42 92 command.c:155 script_debug(): command - t113s3.cpu cget -event gdb-flash-erase-start

Debug: 43 95 command.c:155 script_debug(): command - t113s3.cpu configure -event gdb-flash-erase-start reset init

Debug: 44 97 command.c:155 script_debug(): command - t113s3.cpu cget -event gdb-flash-write-end

Debug: 45 102 command.c:155 script_debug(): command - t113s3.cpu configure -event gdb-flash-write-end reset halt

Debug: 46 105 command.c:155 script_debug(): command - t113s3.cpu cget -event gdb-attach

Debug: 47 107 command.c:155 script_debug(): command - t113s3.cpu configure -event gdb-attach halt 1000

Debug: 48 110 target.c:1657 handle_target_init_command(): Initializing targets...

Debug: 49 111 semihosting_common.c:109 semihosting_common_init():

Debug: 50 114 jlink.c:635 jlink_init(): Using libjaylink 0.4.0 (compiled with 0.4.0)

Debug: 51 130 jlink.c:514 jaylink_log_handler(): Found device (VID:PID = 1366:0105, bus:address = 002:055)

Debug: 52 133 jlink.c:514 jaylink_log_handler(): Device: USB address = 0

Debug: 53 135 jlink.c:514 jaylink_log_handler(): Device: Serial number = 4294967295

Debug: 54 137 jlink.c:514 jaylink_log_handler(): Allocating new device instance

Debug: 55 139 jlink.c:514 jaylink_log_handler(): Found 1 USB device(s)

Debug: 56 141 jlink.c:514 jaylink_log_handler(): Trying to open device (bus:address = 002:055)

Debug: 57 143 jlink.c:514 jaylink_log_handler(): Using endpoint 83 (IN) and 02 (OUT)

Debug: 58 147 jlink.c:514 jaylink_log_handler(): Device opened successfully

Info : 66 149 jlink.c:707 jlink_init(): J-Link V1n compiled Feb 13 2023 17:39:21

Info : 79 152 jlink.c:748 jlink_init(): Hardware version: 11.00

Info : 88 153 jlink.c:789 jlink_init(): VTarget = 3.321 V

Debug: 94 155 jlink.c:514 jaylink_log_handler(): Last read operation left 16 bytes in the buffer

Debug: 104 158 jlink.c:942 jlink_reset(): TRST: 0, SRST: 0

Debug: 124 174 adapter.c:215 adapter_khz_to_speed(): convert khz to adapter specific speed value

Debug: 125 178 adapter.c:219 adapter_khz_to_speed(): have adapter set up

Debug: 132 180 adapter.c:215 adapter_khz_to_speed(): convert khz to adapter specific speed value

Debug: 133 183 adapter.c:219 adapter_khz_to_speed(): have adapter set up

Info : 134 185 adapter.c:179 adapter_init(): clock speed 1000 kHz

Debug: 135 187 openocd.c:134 handle_init_command(): Debug Adapter init complete

Debug: 136 191 command.c:155 script_debug(): command - transport init

Debug: 137 193 transport.c:219 handle_transport_init(): handle_transport_init

Debug: 138 195 jlink.c:942 jlink_reset(): TRST: 0, SRST: 0

Debug: 143 196 core.c:830 jtag_add_reset(): SRST line released

Debug: 144 198 core.c:855 jtag_add_reset(): TRST line released

Debug: 145 199 core.c:328 jtag_call_event_callbacks(): jtag event: TAP reset

Debug: 146 201 command.c:155 script_debug(): command - jtag arp_init

Debug: 147 203 core.c:1509 jtag_init_inner(): Init JTAG chain

Debug: 148 207 core.c:328 jtag_call_event_callbacks(): jtag event: TAP reset

Debug: 158 209 core.c:1234 jtag_examine_chain(): DR scan interrogation for IDCODE/BYPASS

Debug: 159 212 core.c:328 jtag_call_event_callbacks(): jtag event: TAP reset

Info : 169 215 core.c:1133 jtag_examine_chain_display(): JTAG tap: t113s3.cpu tap/device found: 0x5ba00477 (mfg: 0x23b (ARM Ltd), part: 0xba00, ver: 0x5)

Debug: 170 219 core.c:1364 jtag_validate_ircapture(): IR capture validation scan

Debug: 180 222 core.c:1421 jtag_validate_ircapture(): t113s3.cpu: IR capture 0x01

Debug: 181 224 command.c:155 script_debug(): command - dap init

Debug: 182 226 arm_dap.c:97 dap_init_all(): Initializing all DAPs ...

Debug: 183 228 arm_dap.c:121 dap_init_all(): DAP t113s3.cpu configured by default to use ADIv5 protocol

Debug: 184 230 arm_adi_v5.c:679 dap_dp_init(): t113s3.dap

Debug: 185 232 arm_adi_v5.c:711 dap_dp_init(): DAP: wait CDBGPWRUPACK

Debug: 186 233 arm_adi_v5.h:638 dap_dp_poll_register(): DAP: poll 4, mask 0x20000000, value 0x20000000

Debug: 205 239 arm_adi_v5.c:719 dap_dp_init(): DAP: wait CSYSPWRUPACK

Debug: 206 241 arm_adi_v5.h:638 dap_dp_poll_register(): DAP: poll 4, mask 0x80000000, value 0x80000000

Debug: 243 244 openocd.c:151 handle_init_command(): Examining targets...

Debug: 244 246 target.c:1843 target_call_event_callbacks(): target event 19 (examine-start) for core t113s3.cpu

Debug: 245 250 arm_adi_v5.c:1095 dap_get_ap(): refcount AP#0x0 get 1

Debug: 264 253 arm_adi_v5.c:1120 dap_put_ap(): refcount AP#0x0 put 0

Debug: 265 255 arm_adi_v5.c:1095 dap_get_ap(): refcount AP#0x1 get 1

Debug: 284 258 arm_adi_v5.c:1038 dap_find_get_ap(): Found MEM-AP APB2 or APB3 at AP index: 1 (IDR=0x44770002)

Debug: 321 263 arm_adi_v5.c:825 mem_ap_init(): MEM_AP Packed Transfers: disabled

Debug: 322 267 arm_adi_v5.c:836 mem_ap_init(): MEM_AP CFG: large data 0, long address 0, big-endian 0

Debug: 323 270 cortex_a.c:2901 cortex_a_examine_first(): t113s3.cpu's dbgbase is not set, trying to detect using the ROM table

Debug: 576 308 arm_adi_v5.c:2200 dap_lookup_cs_component(): CS lookup found at 0x81410000

Debug: 577 313 cortex_a.c:2911 cortex_a_examine_first(): Detected core 0 dbgbase: 0x81410000

Debug: 614 318 cortex_a.c:2934 cortex_a_examine_first(): didr = 0x3515f005

Debug: 615 320 cortex_a.c:2935 cortex_a_examine_first(): cpuid = 0x410fc075

Debug: 634 324 cortex_a.c:2944 cortex_a_examine_first(): target->coreid 0 DBGPRSR 0x2b

Debug: 635 327 cortex_a.c:2953 cortex_a_examine_first(): target->coreid 0 was reset!

Debug: 654 330 cortex_a.c:2960 cortex_a_examine_first(): target->coreid 0 DBGOSLSR 0xa

Debug: 655 332 cortex_a.c:2966 cortex_a_examine_first(): target->coreid 0 OSLock set! Trying to unlock

Debug: 710 337 cortex_a.c:2991 cortex_a_examine_first(): target->coreid 0 has security extensions

Debug: 711 341 cortex_a.c:2996 cortex_a_examine_first(): target->coreid 0 has virtualization extensions

Info : 712 344 arm_dpm.c:1100 arm_dpm_setup(): t113s3.cpu: hardware has 6 breakpoints, 4 watchpoints

Debug: 713 347 cortex_a.c:595 cortex_a_bpwp_disable(): A: bpwp disable, cr 81410140

Debug: 732 350 cortex_a.c:595 cortex_a_bpwp_disable(): A: bpwp disable, cr 81410144

Debug: 751 353 cortex_a.c:595 cortex_a_bpwp_disable(): A: bpwp disable, cr 81410148

Debug: 770 357 cortex_a.c:595 cortex_a_bpwp_disable(): A: bpwp disable, cr 8141014c

Debug: 789 361 cortex_a.c:595 cortex_a_bpwp_disable(): A: bpwp disable, cr 81410150

Debug: 808 364 cortex_a.c:595 cortex_a_bpwp_disable(): A: bpwp disable, cr 81410154

Debug: 827 367 cortex_a.c:595 cortex_a_bpwp_disable(): A: bpwp disable, cr 814101c0

Debug: 846 371 cortex_a.c:595 cortex_a_bpwp_disable(): A: bpwp disable, cr 814101c4

Debug: 865 375 cortex_a.c:595 cortex_a_bpwp_disable(): A: bpwp disable, cr 814101c8

Debug: 884 378 cortex_a.c:595 cortex_a_bpwp_disable(): A: bpwp disable, cr 814101cc

Debug: 903 381 cortex_a.c:3030 cortex_a_examine_first(): Configured 6 hw breakpoints

Debug: 904 383 cortex_a.c:3044 cortex_a_examine_first(): Configured 4 hw watchpoints

Debug: 977 391 target.c:1843 target_call_event_callbacks(): target event 21 (examine-end) for core t113s3.cpu

Debug: 978 394 command.c:155 script_debug(): command - flash init

Debug: 979 395 tcl.c:1375 handle_flash_init_command(): Initializing flash devices...

Debug: 980 397 command.c:155 script_debug(): command - nand init

Debug: 981 399 tcl.c:487 handle_nand_init_command(): Initializing NAND devices...

Debug: 982 402 command.c:155 script_debug(): command - pld init

Debug: 983 404 pld.c:194 handle_pld_init_command(): Initializing PLDs...

Debug: 984 407 command.c:155 script_debug(): command - tpiu init

Info : 985 409 gdb_server.c:3791 gdb_target_start(): starting gdb server for t113s3.cpu on 3333

Info : 986 412 server.c:297 add_service(): Listening on port 3333 for gdb connections环境:MQ芒果派; JLINKV11 ;openocev0.12.0

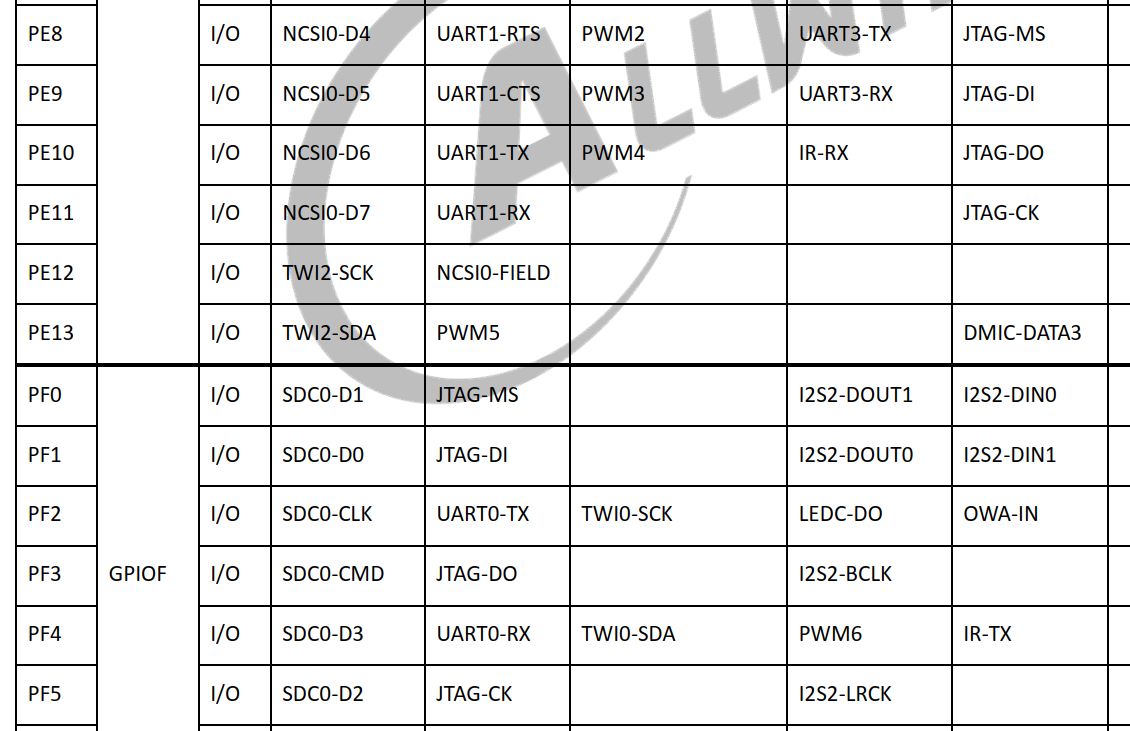

但是由于我想将sd卡用起来,所以想将t113的jtag引脚重映射成pe8 pe9 pe10 pe11。

datasheet明确说了jtag引脚是可以重映射成pe引脚的

尝试步骤:

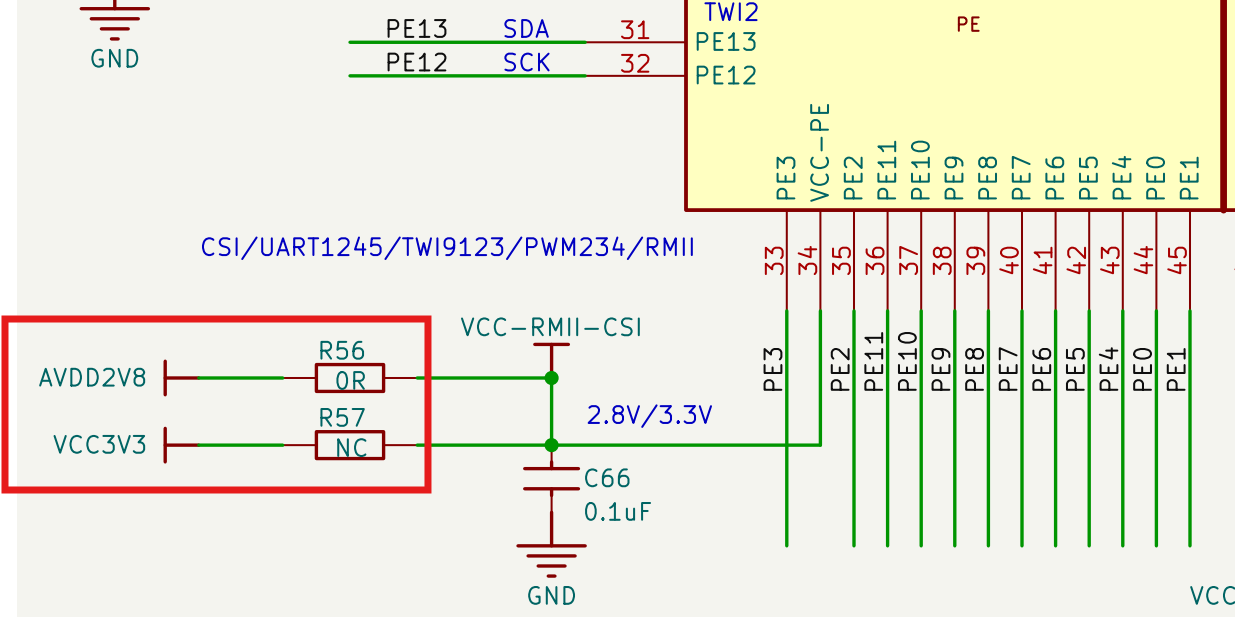

1.电平问题

可能jtag的电平需要3.3v,所以我将电阻R56扣下来焊到了R57处,使PE引脚输出3.3v

2.重写xfel payload

xfel可以直接设置jtag,发现xfel的jtag配置默认使用pf引脚,于是重新改写了jtag的payload

payloads/r528_t113/jtag/source/sys-jtag.c

#include <xboot.h>

void sys_jtag_init(void)

{

virtual_addr_t addr;

u32_t val;

/* Config GPIOF0, GPIOF1, GPIOF3 and GPIOF5 to JTAG mode */

addr = 0x020000f0 + 0x00;

val = read32(addr);

val &= ~(0xf << ((0 & 0x7) << 2));

val |= ((0x3 & 0xf) << ((0 & 0x7) << 2));

write32(addr, val);

val = read32(addr);

val &= ~(0xf << ((1 & 0x7) << 2));

val |= ((0x3 & 0xf) << ((1 & 0x7) << 2));

write32(addr, val);

val = read32(addr);

val &= ~(0xf << ((3 & 0x7) << 2));

val |= ((0x3 & 0xf) << ((3 & 0x7) << 2));

write32(addr, val);

val = read32(addr);

val &= ~(0xf << ((5 & 0x7) << 2));

val |= ((0x3 & 0xf) << ((5 & 0x7) << 2));

write32(addr, val);

}

void sys_jtag_init2(void)

{

virtual_addr_t addr;

u32_t val;

/* Config GPIOE8, GPIOE9, GPIOE10 and GPIOE11 to JTAG mode

MS DI DO CK*/

addr = 0x020000c4 + 0x00;

val = read32(addr);

val &= ~(0xf << (((8-8) & 0x7) << 2));

val |= ((0x6 & 0xf) << (((8-8) & 0x7) << 2));

write32(addr, val);

val = read32(addr);

val &= ~(0xf << (((9-8) & 0x7) << 2));

val |= ((0x6 & 0xf) << (((9-8) & 0x7) << 2));

write32(addr, val);

val = read32(addr);

val &= ~(0xf << (((10-8) & 0x7) << 2));

val |= ((0x6 & 0xf) << (((10-8) & 0x7) << 2));

write32(addr, val);

val = read32(addr);

val &= ~(0xf << (((11-8) & 0x7) << 2));

val |= ((0x6 & 0xf) << (((11-8) & 0x7) << 2));

write32(addr, val);

} payloads/r528_t113/jtag/source/start.S

/*

* start.S

*

* Copyright(c) 2007-2021 Jianjun Jiang <8192542@qq.com>

* Official site: http://xboot.org

* Mobile phone: +86-18665388956

* QQ: 8192542

*

* Permission is hereby granted, free of charge, to any person obtaining a copy

* of this software and associated documentation files (the "Software"), to deal

* in the Software without restriction, including without limitation the rights

* to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

* copies of the Software, and to permit persons to whom the Software is

* furnished to do so, subject to the following conditions:

*

* The above copyright notice and this permission notice shall be included in all

* copies or substantial portions of the Software.

*

* THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

* IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

* FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

* AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

* LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

* OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE

* SOFTWARE.

*

*/

.global _start

_start:

mov r0, #0

mcr p15, 0, r0, c8, c7, 0

mcr p15, 0, r0, c7, c5, 0

mcr p15, 0, r0, c7, c5, 6

mcr p15, 0, r0, c7, c10, 4

mcr p15, 0, r0, c7, c5, 4

b reset

reset:

ldr r0, =0x00047fe0

str sp, [r0, #0]

str lr, [r0, #4]

mrs lr, cpsr

str lr, [r0, #8]

mrc p15, 0, lr, c1, c0, 0

str lr, [r0, #12]

mrc p15, 0, lr, c12, c0, 0

str lr, [r0, #16]

mrc p15, 0, lr, c1, c0, 0

str lr, [r0, #20]

bl sys_jtag_init2

ldr r0, =0x00047fe0

ldr sp, [r0, #0]

ldr lr, [r0, #4]

ldr r1, [r0, #20]

mcr p15, 0, r1, c1, c0, 0

ldr r1, [r0, #16]

mcr p15, 0, r1, c12, c0, 0

ldr r1, [r0, #12]

mcr p15, 0, r1, c1, c0, 0

ldr r1, [r0, #8]

msr cpsr, r1

bx lr进入jtag目录,编译,生成bin文件,再将bin文件翻译成数组,修改chips/r528_t113.c文件下chip_jtag函数中的payload数组,重新编译xfel,make install。

测试:

xfel ddr t113-s3

xfel jtag输出报错:

Error: 169 227 core.c:1122 jtag_examine_chain_check(): JTAG scan chain interrogation failed: all zeroes

Error: 170 234 core.c:1124 jtag_examine_chain_check(): Check JTAG interface, timings, target power, etc.

Error: 171 237 core.c:1554 jtag_init_inner(): Trying to use configured scan chain anyway...

完整日志:

C:\msys64\mingw64\bin>openocd.exe -f t113s3-mangguo.cfg -f t113s3.cfg -d -s E:\资料\T113S3\

Open On-Chip Debugger 0.12.0

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

User : 3 3 options.c:52 configuration_output_handler(): debug_level: 3

User : 4 5 options.c:52 configuration_output_handler():

Debug: 5 7 configuration.c:33 add_script_search_dir(): adding E:\资料\T113S3\

Debug: 6 10 options.c:233 add_default_dirs(): bindir=D:/a/msys64/mingw64/bin

Debug: 7 12 options.c:234 add_default_dirs(): pkgdatadir=D:/a/msys64/mingw64/share/openocd

Debug: 8 14 options.c:235 add_default_dirs(): exepath=C:/msys64/mingw64/bin

Debug: 9 16 options.c:236 add_default_dirs(): bin2data=../share/openocd

Debug: 10 18 configuration.c:33 add_script_search_dir(): adding C:/Users/17204/AppData/Roaming/OpenOCD

Debug: 11 22 configuration.c:33 add_script_search_dir(): adding C:/msys64/mingw64/bin/../share/openocd/site

Debug: 12 26 configuration.c:33 add_script_search_dir(): adding C:/msys64/mingw64/bin/../share/openocd/scripts

Debug: 13 29 command.c:155 script_debug(): command - ocd_find t113s3-mangguo.cfg

Debug: 14 31 configuration.c:88 find_file(): found E:\资料\T113S3\/t113s3-mangguo.cfg

Debug: 15 37 command.c:155 script_debug(): command - ocd_find interface/jlink.cfg

Debug: 16 40 configuration.c:88 find_file(): found C:/msys64/mingw64/bin/../share/openocd/scripts/interface/jlink.cfg

Debug: 17 45 command.c:155 script_debug(): command - adapter driver jlink

Debug: 18 47 command.c:155 script_debug(): command - adapter speed 1000

Debug: 19 50 adapter.c:251 adapter_config_khz(): handle adapter khz

Debug: 20 52 adapter.c:215 adapter_khz_to_speed(): convert khz to adapter specific speed value

Debug: 21 54 adapter.c:215 adapter_khz_to_speed(): convert khz to adapter specific speed value

Debug: 22 57 command.c:155 script_debug(): command - transport select jtag

User : 23 61 options.c:52 configuration_output_handler(): jtagUser : 24 63 options.c:52 configuration_output_handler():

Debug: 25 65 command.c:155 script_debug(): command - ocd_find t113s3.cfg

Debug: 26 68 configuration.c:88 find_file(): found E:\资料\T113S3\/t113s3.cfg

Debug: 27 70 command.c:155 script_debug(): command - reset_config none srst_pulls_trst

Debug: 28 72 command.c:155 script_debug(): command - jtag newtap t113s3 cpu -irlen 4 -ircapture 0x01 -irmask 0x0f -expected-id 0x5ba00477

Debug: 29 78 tcl.c:557 jim_newtap_cmd(): Creating New Tap, Chip: t113s3, Tap: cpu, Dotted: t113s3.cpu, 8 params

Debug: 30 82 tcl.c:582 jim_newtap_cmd(): Processing option: -irlen

Debug: 31 83 tcl.c:582 jim_newtap_cmd(): Processing option: -ircapture

Debug: 32 85 tcl.c:582 jim_newtap_cmd(): Processing option: -irmask

Debug: 33 87 tcl.c:582 jim_newtap_cmd(): Processing option: -expected-id

Debug: 34 89 core.c:1474 jtag_tap_init(): Created Tap: t113s3.cpu @ abs position 0, irlen 4, capture: 0x1 mask: 0xf

Debug: 35 93 command.c:155 script_debug(): command - dap create t113s3.dap -chain-position t113s3.cpu

Debug: 36 98 command.c:155 script_debug(): command - target create t113s3.cpu cortex_a -dap t113s3.dap

Info : 37 101 server.c:297 add_service(): Listening on port 6666 for tcl connections

Info : 38 103 server.c:297 add_service(): Listening on port 4444 for telnet connections

Debug: 39 105 command.c:155 script_debug(): command - init

Debug: 40 107 command.c:155 script_debug(): command - target init

Debug: 41 110 command.c:155 script_debug(): command - target names

Debug: 42 112 command.c:155 script_debug(): command - t113s3.cpu cget -event gdb-flash-erase-start

Debug: 43 114 command.c:155 script_debug(): command - t113s3.cpu configure -event gdb-flash-erase-start reset init

Debug: 44 117 command.c:155 script_debug(): command - t113s3.cpu cget -event gdb-flash-write-end

Debug: 45 119 command.c:155 script_debug(): command - t113s3.cpu configure -event gdb-flash-write-end reset halt

Debug: 46 122 command.c:155 script_debug(): command - t113s3.cpu cget -event gdb-attach

Debug: 47 126 command.c:155 script_debug(): command - t113s3.cpu configure -event gdb-attach halt 1000

Debug: 48 129 target.c:1657 handle_target_init_command(): Initializing targets...

Debug: 49 131 semihosting_common.c:109 semihosting_common_init():

Debug: 50 133 jlink.c:635 jlink_init(): Using libjaylink 0.4.0 (compiled with 0.4.0)

Debug: 51 149 jlink.c:514 jaylink_log_handler(): Found device (VID:PID = 1366:0105, bus:address = 002:055)

Debug: 52 152 jlink.c:514 jaylink_log_handler(): Device: USB address = 0

Debug: 53 154 jlink.c:514 jaylink_log_handler(): Device: Serial number = 4294967295

Debug: 54 158 jlink.c:514 jaylink_log_handler(): Allocating new device instance

Debug: 55 160 jlink.c:514 jaylink_log_handler(): Found 1 USB device(s)

Debug: 56 162 jlink.c:514 jaylink_log_handler(): Trying to open device (bus:address = 002:055)

Debug: 57 164 jlink.c:514 jaylink_log_handler(): Using endpoint 83 (IN) and 02 (OUT)

Debug: 58 167 jlink.c:514 jaylink_log_handler(): Device opened successfully

Info : 66 169 jlink.c:707 jlink_init(): J-Link V1n compiled Feb 13 2023 17:39:21

Info : 79 173 jlink.c:748 jlink_init(): Hardware version: 11.00

Info : 88 175 jlink.c:789 jlink_init(): VTarget = 3.322 V

Debug: 94 176 jlink.c:514 jaylink_log_handler(): Last read operation left 16 bytes in the buffer

Debug: 104 179 jlink.c:942 jlink_reset(): TRST: 0, SRST: 0

Debug: 124 185 adapter.c:215 adapter_khz_to_speed(): convert khz to adapter specific speed value

Debug: 125 188 adapter.c:219 adapter_khz_to_speed(): have adapter set up

Debug: 132 190 adapter.c:215 adapter_khz_to_speed(): convert khz to adapter specific speed value

Debug: 133 193 adapter.c:219 adapter_khz_to_speed(): have adapter set up

Info : 134 195 adapter.c:179 adapter_init(): clock speed 1000 kHz

Debug: 135 196 openocd.c:134 handle_init_command(): Debug Adapter init complete

Debug: 136 198 command.c:155 script_debug(): command - transport init

Debug: 137 202 transport.c:219 handle_transport_init(): handle_transport_init

Debug: 138 204 jlink.c:942 jlink_reset(): TRST: 0, SRST: 0

Debug: 143 206 core.c:830 jtag_add_reset(): SRST line released

Debug: 144 208 core.c:855 jtag_add_reset(): TRST line released

Debug: 145 210 core.c:328 jtag_call_event_callbacks(): jtag event: TAP reset

Debug: 146 212 command.c:155 script_debug(): command - jtag arp_init

Debug: 147 216 core.c:1509 jtag_init_inner(): Init JTAG chain

Debug: 148 219 core.c:328 jtag_call_event_callbacks(): jtag event: TAP reset

Debug: 158 222 core.c:1234 jtag_examine_chain(): DR scan interrogation for IDCODE/BYPASS

Debug: 159 224 core.c:328 jtag_call_event_callbacks(): jtag event: TAP reset

Error: 169 227 core.c:1122 jtag_examine_chain_check(): JTAG scan chain interrogation failed: all zeroes

Error: 170 234 core.c:1124 jtag_examine_chain_check(): Check JTAG interface, timings, target power, etc.

Error: 171 237 core.c:1554 jtag_init_inner(): Trying to use configured scan chain anyway...

Debug: 172 239 core.c:1364 jtag_validate_ircapture(): IR capture validation scan

Error: 182 242 core.c:1413 jtag_validate_ircapture(): t113s3.cpu: IR capture error; saw 0x00 not 0x01

Debug: 183 248 core.c:328 jtag_call_event_callbacks(): jtag event: TAP reset

Warn : 193 252 core.c:1577 jtag_init_inner(): Bypassing JTAG setup events due to errors

Debug: 194 254 command.c:155 script_debug(): command - dap init

Debug: 195 256 arm_dap.c:97 dap_init_all(): Initializing all DAPs ...

Debug: 196 258 arm_dap.c:121 dap_init_all(): DAP t113s3.cpu configured by default to use ADIv5 protocol

Debug: 197 264 arm_adi_v5.c:679 dap_dp_init(): t113s3.dap

Debug: 198 266 arm_adi_v5.c:711 dap_dp_init(): DAP: wait CDBGPWRUPACK

Debug: 199 268 arm_adi_v5.h:638 dap_dp_poll_register(): DAP: poll 4, mask 0x20000000, value 0x20000000

Error: 209 271 adi_v5_jtag.c:446 jtagdp_overrun_check(): Invalid ACK (0) in DAP response

Debug: 219 274 command.c:544 run_command(): Command 'dap init' failed with error code -107

User : 220 280 command.c:608 command_run_line():

Debug: 221 281 command.c:544 run_command(): Command 'init' failed with error code -4

User : 222 283 command.c:608 command_run_line():

Debug: 223 285 target.c:2199 target_free_all_working_areas_restore(): freeing all working areas

Debug: 229 288 jlink.c:514 jaylink_log_handler(): Last read operation left 16 bytes in the buffer

Debug: 231 292 jlink.c:514 jaylink_log_handler(): Closing device (bus:address = 002:055)

Debug: 232 296 jlink.c:514 jaylink_log_handler(): Device closed successfully

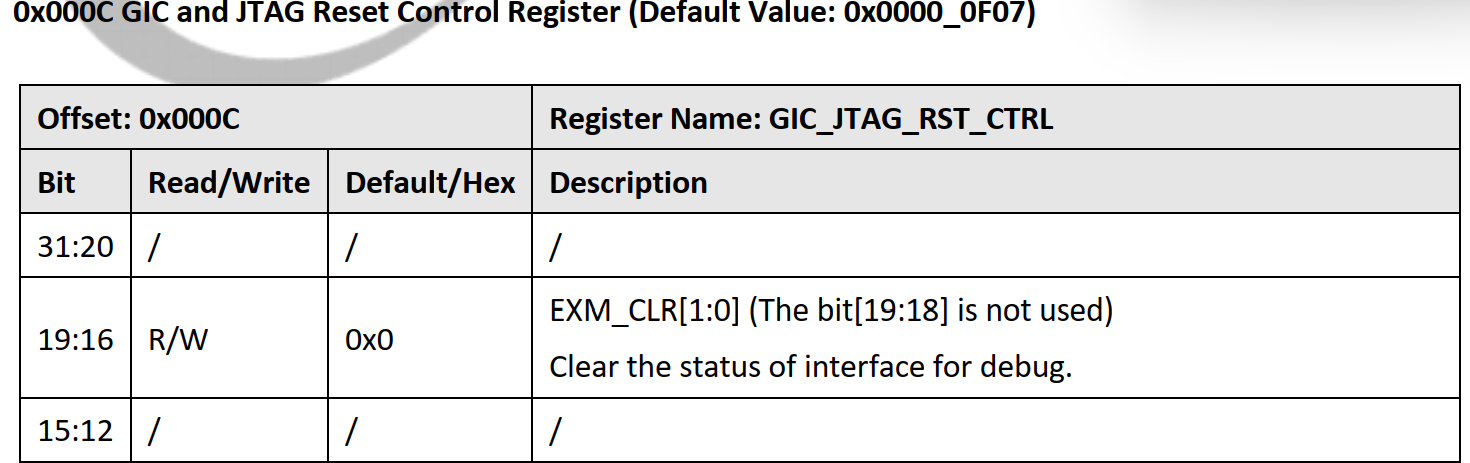

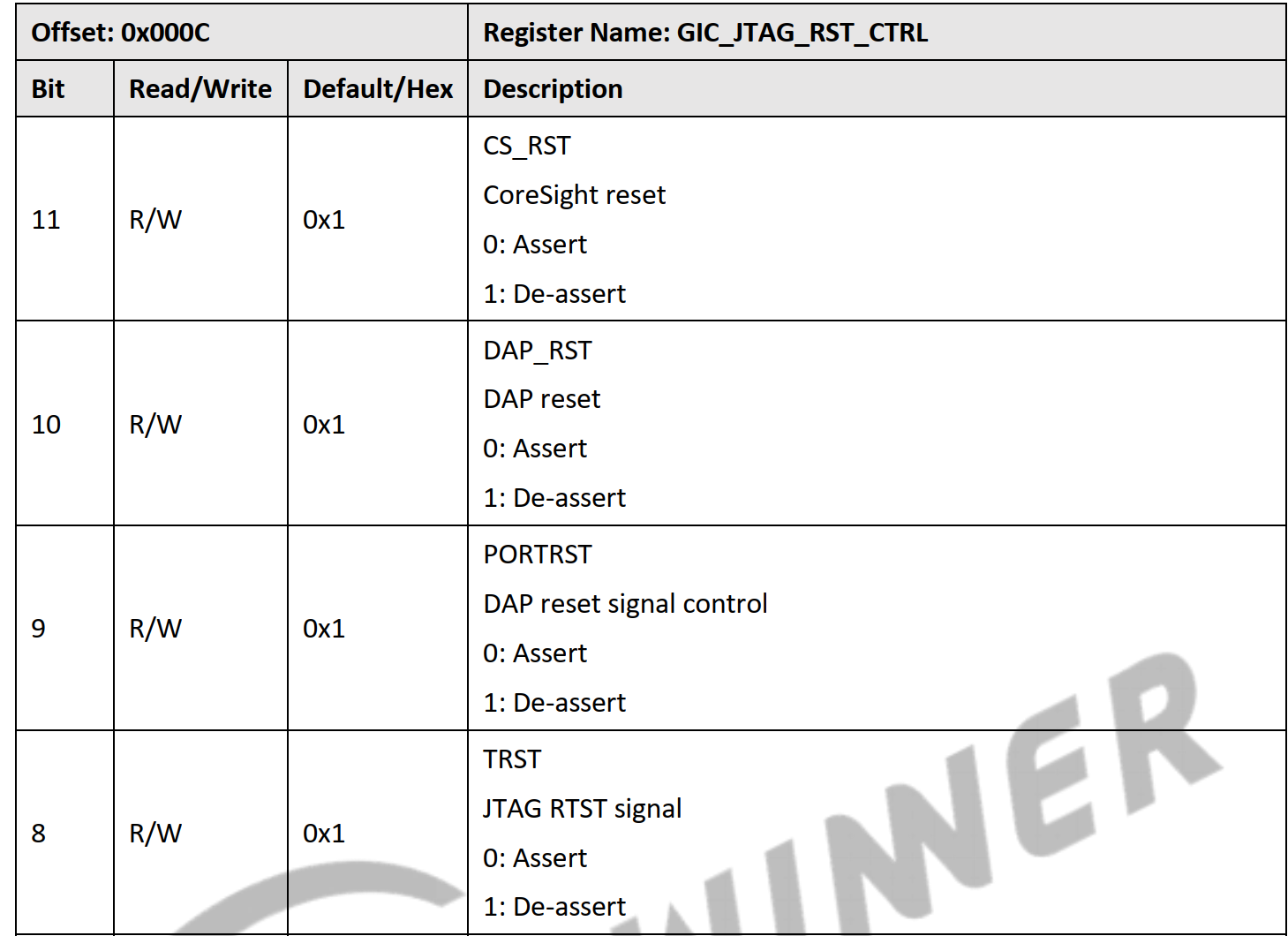

Debug: 233 299 jlink.c:514 jaylink_log_handler(): Device destroyed (bus:address = 002:055)最后,又查看trm手册,是不是jtag需要重新复位一下,于是又操作了GIC_JTAG_RST_CTRL寄存器进行了jtag复位

,最终还是报错,依旧是相同的原因

Error: 169 227 core.c:1122 jtag_examine_chain_check(): JTAG scan chain interrogation failed: all zeroes

Error: 170 234 core.c:1124 jtag_examine_chain_check(): Check JTAG interface, timings, target power, etc.

Error: 171 237 core.c:1554 jtag_init_inner(): Trying to use configured scan chain anyway...

有没有大佬给指条明路啊?

#6 Re: 全志 SOC » T113的OpenOCD在线调试的坑 » 2025-07-03 18:07:30

#8 Re: 全志 SOC » 搞了一个T113S3裸机代码(copy xboot和awboot),遇到定时器中断一直触发不了。。。 » 2024-04-11 16:40:10

lyy wrote:

@evilbinary 我现在是参考的本版的一个iar工程弄的,可以仿真调试,但是看了你的程序,没看懂中断流程,不知道该怎么对照着改IAR工程

我没有使用IAR,但流程都差不多,工程我放在gitee仓库了,目前没实现啥功能,只是移植了freertos,可以跑任务,想要参考的话可以看看

https://gitee.com/zmzone/mangzai_freertos_kit/tree/master/

#9 Re: 全志 SOC » 搞了一个T113S3裸机代码(copy xboot和awboot),遇到定时器中断一直触发不了。。。 » 2024-01-12 14:23:21

freertos 初步移植成功,用的freertos版本是10.0.0,目前只验证了多任务运行,运行正常!

[I] AWBoot r51 starting...

[D] DRAM BOOT DRIVE INFO: V0.24

[D] DRAM CLK = 792 MHz

[D] DRAM Type = 3 (2:DDR2,3:DDR3)

[D] DRAMC read ODT off

[D] ZQ value = 0x12e

[D] DDR efuse: 0xa

[D] chip id efuse: 0x6000

[D] single rank and full DQ

[D] DDR efuse: 0xa

[D] chip id efuse: 0x6000

[D] rank 0 row = 13

[D] para->dram_para1 = 0x10d2

[D] rank 0 bank = 8

[D] para->dram_para1 = 0x10d2

[D] rank 0 page size = 2 KB

[D] para->dram_para1 = 0x10d2

[D] DRAM ODT value: 0x42

[D] DDR efuse: 0xa

[D] chip id efuse: 0x6000

[D] DRAM: size = 128MB

[D] DRAM: simple test OK

[D] DMA: init

[T] DMA: test 0x44000000 ====> 0x44800000, len 512KB

[T] DMA: provide channel 0

[D] DMA: test OK in 59ms

[T] SPI: parent_clk=600MHz, div=3, n=1, m=3

[T] SPI: CDR2 - n = 0

[T] SPI: clock div=0

[D] SPI: set clock asked=100MHz actual=100MHz mclk=200MHz

[T] DMA: provide channel 0

[T] SPI: tsfr mode=0 tx=1 rx=0

[T] SPI: ISR=0x1032

[T] SPI: tsfr mode=0 tx=1 rx=1

[T] SPI: ISR=0x1033

[T] SPI: tsfr mode=0 tx=1 rx=4

[T] SPI: ISR=0x1033

[I] SPI-NOR: MFR:0xEF DEV:0x4019

[T] SPI: tsfr mode=1 tx=5 rx=2097152

[T] SPI: ISR=0x1037

[I] SPI NOR: READ USER BIN TIME:89785uS

[I] ------BootLoader Jump Successed-----------

[D] welcome to T113s3

[D] CLK: CPU PLL=PLL_CPU FREQ=1200MHz

[D] CLK: PLL_peri (2X)=1200MHz, (1X)=600MHz, (800M)=800MHz

[D] CLK: PLL_ddr=1584MHz

[D] timer0 irq is enable

[D] i am task0

[D] i am task2

[D] i am task1

[D] i am task0

[D] i am task2

[D] i am task1

[D] i am task0

[D] i am task2

[D] i am task1

[D] i am task0

[D] i am task2

[D] i am task1

[D] i am task0

[D] i am task2

[D] i am task1

[D] i am task0

[D] i am task2

[D] i am task1

[D] i am task0

[D] i am task2

[D] i am task1后续打算研究一下t113s3的在线调试,想用openocd估计又是一个大坑~

#10 Re: 全志 SOC » 搞了一个T113S3裸机代码(copy xboot和awboot),遇到定时器中断一直触发不了。。。 » 2024-01-10 10:45:01

总算搞定中断了,发现还是前面gic初始化出问题了,哎,心累 ![]()

dram start

dram init ok

welcome to T113s3

[D] CLK: CPU PLL=PLL_CPU FREQ=1200MHz

[D] CLK: PLL_peri (2X)=1200MHz, (1X)=600MHz, (800M)=800MHz

[D] CLK: PLL_ddr=1584MHz

now run in security

sys tick handler get

sys tick handler get

sys tick handler get

sys tick handler get

sys tick handler get

sys tick handler get

sys tick handler get

sys tick handler get

sys tick handler get

sys tick handler get

sys tick handler get

sys tick handler get

sys tick handler get下面开始移植freertos,开搞!!

#11 Re: 全志 SOC » T113-S3主线Linux支持方案(基于TF卡,包含串口修改) » 2024-01-05 17:19:54

[I] AWBoot r6164 starting...

[D] DRAM BOOT DRIVE INFO: V0.24

[D] DRAM CLK = 792 MHz

[D] DRAM Type = 3 (2:DDR2,3:DDR3)

[D] DRAMC read ODT off

[D] ZQ value = 0x2f

[D] DDR efuse: 0xa

[D] chip id efuse: 0x6000

[D] single rank and full DQ

[D] DDR efuse: 0xa

[D] chip id efuse: 0x6000

[D] rank 0 row = 13

[D] para->dram_para1 = 0x10d2

[D] rank 0 bank = 8

[D] para->dram_para1 = 0x10d2

[D] rank 0 page size = 2 KB

[D] para->dram_para1 = 0x10d2

[D] DRAM ODT value: 0x42

[D] DDR efuse: 0xa

[D] chip id efuse: 0x6000

[D] DRAM: size = 128MB

[D] DRAM: simple test OK

[I] SMHC: sdhci0 controller v50310 initialized

[D] SMHC: capacity 31.3GB

[I] SHMC: SD card detected

[D] SDMMC: speedtest 512KB in 27ms at 19418KB/S

[I] FATFS: cache: 67108864 bytes in 2048 chunks

[D] FATFS: mount OK

[I] FATFS: read sun8i-t113-mangopi-dual.dtb addr=44000000

[D] FATFS: read in 5ms at 4.56MB/S

[I] FATFS: read zImage addr=44800000

[D] FATFS: read in 376ms at 13.11MB/S

[D] FATFS: unmount OK

[D] FATFS: done in 410ms

[I] booting linux...

[ 0.000000] Booting Linux on physical CPU 0x0

[ 0.000000] Linux version 6.0.1-gd7d8c971c9c5-dirty (ubuntu@ubuntu1804) (arm-none-linux-gnueabihf-gcc (GNU Toolchain for the A-profile Architecture 10.3-2021.07 (arm-10.29)) 10.3.1 20210621, GNU ld (GNU Toolchain for the A-profile Architecture 10.3-2021.07 (arm-10.29)) 2.36.1.20210621) #2 SMP Fri Jan 5 02:05:12 EST 2024

[ 0.000000] CPU: ARMv7 Processor [410fc075] revision 5 (ARMv7), cr=10c5387d

[ 0.000000] CPU: div instructions available: patching division code

[ 0.000000] CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache

[ 0.000000] OF: fdt: Machine model: MangoPi MQ-Dual

[ 0.000000] Memory policy: Data cache writealloc

[ 0.000000] cma: Failed to reserve 72 MiB

[ 0.000000] Zone ranges:

[ 0.000000] Normal [mem 0x0000000040000000-0x0000000047ffffff]

[ 0.000000] HighMem empty

[ 0.000000] Movable zone start for each node

[ 0.000000] Early memory node ranges

[ 0.000000] node 0: [mem 0x0000000040000000-0x0000000047ffffff]

[ 0.000000] Initmem setup node 0 [mem 0x0000000040000000-0x0000000047ffffff]

[ 0.000000] percpu: Embedded 11 pages/cpu s15508 r8192 d21356 u45056

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 32512

[ 0.000000] Kernel command line: mem=128M cma=72M root=/dev/mmcblk0p2 init=/sbin/init rootwait console=tty0 console=ttyS0,115200

[ 0.000000] Dentry cache hash table entries: 16384 (order: 4, 65536 bytes, linear)

[ 0.000000] Inode-cache hash table entries: 8192 (order: 3, 32768 bytes, linear)

[ 0.000000] mem auto-init: stack:off, heap alloc:off, heap free:off

[ 0.000000] Memory: 116236K/131072K available (8192K kernel code, 942K rwdata, 2092K rodata, 1024K init, 263K bss, 14836K reserved, 0K cma-reserved, 0K highmem)

[ 0.000000] SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=2, Nodes=1

[ 0.000000] rcu: Hierarchical RCU implementation.

[ 0.000000] rcu: RCU restricting CPUs from NR_CPUS=8 to nr_cpu_ids=2.

[ 0.000000] rcu: RCU calculated value of scheduler-enlistment delay is 10 jiffies.

[ 0.000000] rcu: Adjusting geometry for rcu_fanout_leaf=16, nr_cpu_ids=2

[ 0.000000] NR_IRQS: 16, nr_irqs: 16, preallocated irqs: 16

[ 0.000000] rcu: srcu_init: Setting srcu_struct sizes based on contention.

[ 0.000000] arch_timer: cp15 timer(s) running at 24.00MHz (phys).

[ 0.000000] clocksource: arch_sys_counter: mask: 0xffffffffffffff max_cycles: 0x588fe9dc0, max_idle_ns: 440795202592 ns

[ 0.000001] sched_clock: 56 bits at 24MHz, resolution 41ns, wraps every 4398046511097ns

[ 0.000012] Switching to timer-based delay loop, resolution 41ns

[ 0.000193] clocksource: timer: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 79635851949 ns

[ 0.000688] Console: colour dummy device 80x30

[ 0.001005] printk: console [tty0] enabled

[ 0.001048] Calibrating delay loop (skipped), value calculated using timer frequency.. 48.00 BogoMIPS (lpj=240000)

[ 0.001078] pid_max: default: 32768 minimum: 301

[ 0.001234] Mount-cache hash table entries: 1024 (order: 0, 4096 bytes, linear)

[ 0.001268] Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes, linear)

[ 0.001811] CPU: Testing write buffer coherency: ok

[ 0.002137] /cpus/cpu@0 missing clock-frequency property

[ 0.002189] /cpus/cpu@1 missing clock-frequency property

[ 0.002209] CPU0: thread -1, cpu 0, socket 0, mpidr 80000000

[ 0.002969] Setting up static identity map for 0x40100000 - 0x40100060

[ 0.003140] rcu: Hierarchical SRCU implementation.

[ 0.003159] rcu: Max phase no-delay instances is 1000.

[ 0.003682] smp: Bringing up secondary CPUs ...

[ 0.004393] CPU1: thread -1, cpu 1, socket 0, mpidr 80000001

[ 0.004514] smp: Brought up 1 node, 2 CPUs

[ 0.004557] SMP: Total of 2 processors activated (96.00 BogoMIPS).

[ 0.004574] CPU: All CPU(s) started in SVC mode.

[ 0.005094] devtmpfs: initialized

[ 0.009148] VFP support v0.3: implementor 41 architecture 2 part 30 variant 7 rev 5

[ 0.009372] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604462750000 ns

[ 0.009414] futex hash table entries: 512 (order: 3, 32768 bytes, linear)

[ 0.009566] pinctrl core: initialized pinctrl subsystem

[ 0.010871] NET: Registered PF_NETLINK/PF_ROUTE protocol family

[ 0.011180] DMA: preallocated 256 KiB pool for atomic coherent allocations

[ 0.011964] thermal_sys: Registered thermal governor 'step_wise'

[ 0.012201] hw-breakpoint: found 5 (+1 reserved) breakpoint and 4 watchpoint registers.

[ 0.012250] hw-breakpoint: maximum watchpoint size is 8 bytes.

[ 0.019770] platform 5460000.tcon-top: Fixing up cyclic dependency with 5200000.mixer

[ 0.019877] platform 5460000.tcon-top: Fixing up cyclic dependency with 5100000.mixer

[ 0.020253] platform 5461000.lcd-controller: Fixing up cyclic dependency with 5460000.tcon-top

[ 0.020635] platform 5470000.lcd-controller: Fixing up cyclic dependency with 5604000.tv-encoder

[ 0.020726] platform 5470000.lcd-controller: Fixing up cyclic dependency with 5460000.tcon-top

[ 0.021497] platform 7090000.rtc: Fixing up cyclic dependency with 7010000.clock-controller

[ 0.031379] SCSI subsystem initialized

[ 0.031878] usbcore: registered new interface driver usbfs

[ 0.031937] usbcore: registered new interface driver hub

[ 0.031987] usbcore: registered new device driver usb

[ 0.032200] mc: Linux media interface: v0.10

[ 0.032257] videodev: Linux video capture interface: v2.00

[ 0.032339] pps_core: LinuxPPS API ver. 1 registered

[ 0.032356] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it>

[ 0.032387] PTP clock support registered

[ 0.032821] Advanced Linux Sound Architecture Driver Initialized.

[ 0.033988] clocksource: Switched to clocksource arch_sys_counter

[ 0.041554] NET: Registered PF_INET protocol family

[ 0.041781] IP idents hash table entries: 2048 (order: 2, 16384 bytes, linear)

[ 0.042324] tcp_listen_portaddr_hash hash table entries: 512 (order: 0, 4096 bytes, linear)

[ 0.042372] Table-perturb hash table entries: 65536 (order: 6, 262144 bytes, linear)

[ 0.042395] TCP established hash table entries: 1024 (order: 0, 4096 bytes, linear)

[ 0.042424] TCP bind hash table entries: 1024 (order: 1, 8192 bytes, linear)

[ 0.042454] TCP: Hash tables configured (established 1024 bind 1024)

[ 0.042548] UDP hash table entries: 256 (order: 1, 8192 bytes, linear)

[ 0.042595] UDP-Lite hash table entries: 256 (order: 1, 8192 bytes, linear)

[ 0.042760] NET: Registered PF_UNIX/PF_LOCAL protocol family

[ 0.043304] RPC: Registered named UNIX socket transport module.

[ 0.043346] RPC: Registered udp transport module.

[ 0.043359] RPC: Registered tcp transport module.

[ 0.043371] RPC: Registered tcp NFSv4.1 backchannel transport module.

[ 0.044470] Initialise system trusted keyrings

[ 0.044768] workingset: timestamp_bits=30 max_order=15 bucket_order=0

[ 0.049500] NFS: Registering the id_resolver key type

[ 0.049592] Key type id_resolver registered

[ 0.049608] Key type id_legacy registered

[ 0.049657] Key type asymmetric registered

[ 0.049671] Asymmetric key parser 'x509' registered

[ 0.049813] Block layer SCSI generic (bsg) driver version 0.4 loaded (major 246)

[ 0.049838] io scheduler mq-deadline registered

[ 0.049851] io scheduler kyber registered

[ 0.105846] Serial: 8250/16550 driver, 8 ports, IRQ sharing disabled

[ 0.115337] CAN device driver interface

[ 0.116088] ehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver

[ 0.116115] ehci-platform: EHCI generic platform driver

[ 0.116255] ohci_hcd: USB 1.1 'Open' Host Controller (OHCI) Driver

[ 0.116288] ohci-platform: OHCI generic platform driver

[ 0.118701] sun6i-rtc 7090000.rtc: registered as rtc0

[ 0.118848] sun6i-rtc 7090000.rtc: setting system clock to 1970-01-02T00:26:48 UTC (88008)

[ 0.119003] sun6i-rtc 7090000.rtc: RTC enabled

[ 0.119351] i2c_dev: i2c /dev entries driver

[ 0.121104] sunxi-wdt 20500a0.watchdog: Watchdog enabled (timeout=16 sec, nowayout=0)

[ 0.122268] sun8i-ce 3040000.crypto: Set mod clock to 300000000 (300 Mhz) from 400000000 (400 Mhz)

[ 0.122628] sun8i-ce 3040000.crypto: will run requests pump with realtime priority

[ 0.122833] sun8i-ce 3040000.crypto: will run requests pump with realtime priority

[ 0.122988] sun8i-ce 3040000.crypto: will run requests pump with realtime priority

[ 0.123132] sun8i-ce 3040000.crypto: will run requests pump with realtime priority

[ 0.123238] sun8i-ce 3040000.crypto: Register cbc(aes)

[ 0.123272] sun8i-ce 3040000.crypto: Register ecb(aes)

[ 0.123292] sun8i-ce 3040000.crypto: Register cbc(des3_ede)

[ 0.123311] sun8i-ce 3040000.crypto: Register ecb(des3_ede)

[ 0.123349] sun8i-ce 3040000.crypto: CryptoEngine Die ID 0

[ 0.124270] usbcore: registered new interface driver usbhid

[ 0.124303] usbhid: USB HID core driver

[ 0.126913] NET: Registered PF_PACKET protocol family

[ 0.126969] can: controller area network core

[ 0.127047] NET: Registered PF_CAN protocol family

[ 0.127066] can: raw protocol

[ 0.127080] can: broadcast manager protocol

[ 0.127096] can: netlink gateway - max_hops=1

[ 0.127292] Key type dns_resolver registered

[ 0.127392] Registering SWP/SWPB emulation handler

[ 0.127509] Loading compiled-in X.509 certificates

[ 0.145500] sun20i-d1-pinctrl 2000000.pinctrl: initialized sunXi PIO driver

[ 0.146729] printk: console [ttyS0] disabled

[ 0.167029] 2500000.serial: ttyS0 at MMIO 0x2500000 (irq = 231, base_baud = 1500000) is a 16550A

[ 1.024542] printk: console [ttyS0] enabled

[ 1.050535] 2500400.serial: ttyS1 at MMIO 0x2500400 (irq = 232, base_baud = 1500000) is a 16550A

[ 1.080993] 2501400.serial: ttyS5 at MMIO 0x2501400 (irq = 233, base_baud = 1500000) is a 16550A

[ 1.091842] phy phy-4100400.phy.0: Changing dr_mode to 1

[ 1.092957] usb_phy_generic usb_phy_generic.1.auto: dummy supplies not allowed for exclusive requests

[ 1.097242] ehci-platform 4101000.usb: EHCI Host Controller

[ 1.106989] musb-hdrc musb-hdrc.2.auto: MUSB HDRC host driver

[ 1.112012] ehci-platform 4101000.usb: new USB bus registered, assigned bus number 1

[ 1.117774] musb-hdrc musb-hdrc.2.auto: new USB bus registered, assigned bus number 2

[ 1.118548] hub 2-0:1.0: USB hub found

[ 1.125647] ehci-platform 4101000.usb: irq 234, io mem 0x04101000

[ 1.133409] hub 2-0:1.0: 1 port detected

[ 1.148079] ehci-platform 4200000.usb: EHCI Host Controller

[ 1.153704] ehci-platform 4200000.usb: new USB bus registered, assigned bus number 3

[ 1.161599] ehci-platform 4200000.usb: irq 236, io mem 0x04200000

[ 1.165698] ohci-platform 4200400.usb: Generic Platform OHCI controller

[ 1.167811] ehci-platform 4101000.usb: USB 2.0 started, EHCI 1.00

[ 1.174363] ohci-platform 4200400.usb: new USB bus registered, assigned bus number 4

[ 1.188339] ohci-platform 4200400.usb: irq 238, io mem 0x04200400

[ 1.188599] hub 1-0:1.0: USB hub found

[ 1.198400] hub 1-0:1.0: 1 port detected

[ 1.202061] sunxi-mmc 4020000.mmc: Got CD GPIO

[ 1.204038] ehci-platform 4200000.usb: USB 2.0 started, EHCI 1.00

[ 1.213570] ALSA device list:

[ 1.216623] No soundcards found.

[ 1.220762] sunxi-mmc 4021000.mmc: allocated mmc-pwrseq

[ 1.226790] hub 3-0:1.0: USB hub found

[ 1.230607] hub 3-0:1.0: 1 port detected

[ 1.234985] sunxi-mmc 4020000.mmc: initialized, max. request size: 2048 KB, uses new timings mode

[ 1.251381] sunxi-mmc 4021000.mmc: initialized, max. request size: 2048 KB, uses new timings mode

[ 1.268605] sunxi-mmc 4021000.mmc: card claims to support voltages below defined range

[ 1.268682] hub 4-0:1.0: USB hub found

[ 1.280411] hub 4-0:1.0: 1 port detected

[ 1.296327] mmc1: new high speed SDIO card at address 0001

[ 1.320603] mmc0: new high speed SDHC card at address 0001

[ 1.327003] mmcblk0: mmc0:0001 SD32G 29.1 GiB

[ 1.334080] mmcblk0: p1

[ 1.354077] ohci-platform 4101400.usb: Generic Platform OHCI controller

[ 1.360746] ohci-platform 4101400.usb: new USB bus registered, assigned bus number 5

[ 1.368675] ohci-platform 4101400.usb: irq 237, io mem 0x04101400

[ 1.448679] hub 5-0:1.0: USB hub found

[ 1.452488] hub 5-0:1.0: 1 port detected

[ 1.457665] /dev/root: Can't open blockdev

[ 1.461805] VFS: Cannot open root device "mmcblk0p2" or unknown-block(179,2): error -6

[ 1.469764] Please append a correct "root=" boot option; here are the available partitions:

[ 1.478143] b300 30534656 mmcblk0

[ 1.478152] driver: mmcblk

[ 1.484977] b301 8387584 mmcblk0p1 a76cc5e4-01

[ 1.484986]

[ 1.491795] Kernel panic - not syncing: VFS: Unable to mount root fs on unknown-block(179,2)

[ 1.500235] CPU: 1 PID: 1 Comm: swapper/0 Not tainted 6.0.1-gd7d8c971c9c5-dirty #2

[ 1.507808] Hardware name: Generic DT based system

[ 1.512609] unwind_backtrace from show_stack+0x10/0x14

[ 1.517851] show_stack from dump_stack_lvl+0x40/0x4c

[ 1.522913] dump_stack_lvl from panic+0x100/0x304

[ 1.527717] panic from mount_block_root+0x15c/0x1f8

[ 1.532696] mount_block_root from prepare_namespace+0x150/0x18c

[ 1.538713] prepare_namespace from kernel_init+0x18/0x12c

[ 1.544211] kernel_init from ret_from_fork+0x14/0x2c

[ 1.549274] Exception stack(0xc8815fb0 to 0xc8815ff8)

[ 1.554330] 5fa0: 00000000 00000000 00000000 00000000

[ 1.562510] 5fc0: 00000000 00000000 00000000 00000000 00000000 00000000 00000000 00000000

[ 1.570689] 5fe0: 00000000 00000000 00000000 00000000 00000013 00000000

[ 1.577308] CPU0: stopping

[ 1.580016] CPU: 0 PID: 0 Comm: swapper/0 Not tainted 6.0.1-gd7d8c971c9c5-dirty #2

[ 1.587577] Hardware name: Generic DT based system

[ 1.592363] unwind_backtrace from show_stack+0x10/0x14

[ 1.597589] show_stack from dump_stack_lvl+0x40/0x4c

[ 1.602640] dump_stack_lvl from do_handle_IPI+0xec/0x124

[ 1.608038] do_handle_IPI from ipi_handler+0x18/0x20

[ 1.613089] ipi_handler from handle_percpu_devid_irq+0x78/0x13c

[ 1.619096] handle_percpu_devid_irq from generic_handle_domain_irq+0x28/0x38

[ 1.626230] generic_handle_domain_irq from gic_handle_irq+0x74/0x88

[ 1.632584] gic_handle_irq from generic_handle_arch_irq+0x34/0x44

[ 1.638765] generic_handle_arch_irq from __irq_svc+0x88/0xb0

[ 1.644509] Exception stack(0xc0d01f10 to 0xc0d01f58)

[ 1.649556] 1f00: 00000005 00000000 000014a1 c0115ee0

[ 1.657723] 1f20: 00000000 c0d04f0c c0d080c0 c0d04f54 c0de6b04 c0a390e8 00000001 00000000

[ 1.665890] 1f40: 00000118 c0d01f60 c01072a0 c01072a4 60000013 ffffffff

[ 1.672495] __irq_svc from arch_cpu_idle+0x38/0x3c

[ 1.677374] arch_cpu_idle from default_idle_call+0x24/0x34

[ 1.682947] default_idle_call from do_idle+0xb8/0x124

[ 1.688085] do_idle from cpu_startup_entry+0x18/0x1c

[ 1.693134] cpu_startup_entry from rest_init+0xa8/0xac

[ 1.698351] rest_init from arch_post_acpi_subsys_init+0x0/0x8

[ 1.704375] ---[ end Kernel panic - not syncing: VFS: Unable to mount root fs on unknown-block(179,2) ]---我只放了dtb和zImage,这个报错是因为没有文件系统的原因吗?楼主能出一个制作文件系统的贴子吗?想学习一下

#12 Re: 全志 SOC » 成功在T113-S3上跑了第一个裸机程序 » 2024-01-04 17:11:15

#13 全志 SOC » 搞了一个T113S3裸机代码(copy xboot和awboot),遇到定时器中断一直触发不了。。。 » 2024-01-02 17:21:05

- zm

- 回复: 20

手上有一块t113-s3 麻雀开发板,自己焊了norflash(怕nand flash出现坏块搞不定。。。),想试试能不能自己移植freertos在t113上跑,先打算实现裸机正常运行和中断正常运行。目前可以正常的打印,定时器也正常计数,就是无法触发中断,本人小白,花了一段时间,实在找不出问题,只能把源码贴出来了,希望有大佬帮忙看看。。

log:

dram start

dram init ok

welcome to T113s3

now run in security

[D] CLK: CPU PLL=PLL_CPU FREQ=1200MHz

[D] CLK: PLL_peri (2X)=1200MHz, (1X)=600MHz, (800M)=800MHz

[D] CLK: PLL_ddr=1584MHz

gic_base address is 0x3020000

gic irqs supported is 224

0) current val = 0

1) current val = 22779507

2) current val = 21555507

3) current val = 20331507

4) current val = 19107507

5) current val = 17883507

6) current val = 16659507

7) current val = 15435507

8) current val = 14211506

9) current val = 12987506

10) current val = 11763507

11) current val = 10539507

12) current val = 9315507

13) current val = 8091507

14) current val = 6867506

15) current val = 5643506

16) current val = 4419507

17) current val = 3195507

18) current val = 1971507

19) current val = 747506

20) current val = 23523507#include "debug.h"

#include "arch_timer/arch_timer.h"

#include "timer/timer.h"

#include "gic400/gic400.h"

#include "gic400/t113_irq.h"

#include "t113_clk/sunxi_clk.h"

#include "arm32.h"

#include "bit_ops.h"

static void timer0_irq_handler(void * data);

static void timer1_irq_handler(void * data);

int main(void)

{

u32 cur_val = 0;

u32 scr;

message("welcome to T113s3\r\n");

scr = arm32_read_scr_ns();

if(GET_BIT(scr,0))//获取SCR.NS位,如果是0则是安全模式,如果是1则是非安全模式

{

message("now run in non_security\r\n");

}

else

{

message("now run in security\r\n");

}

sunxi_clk_dump();

start_gic();

register_irq(T113_IRQ_TIMER1,timer1_irq_handler,NULL,(30 << 3),3);

start_ms_timer(TIMER1,1000);

int i = 0;

while(1)

{

cur_val = get_current_timer_value(TIMER1);

message("%d) current val = %d \r\n",i,cur_val);

mdelay(50);

i ++;

}

}

static void timer0_irq_handler(void * data)

{

//清中断

clear_timern_irq(TIMER0);

message("timer0 irq get \r\n");

}

static void timer1_irq_handler(void * data)

{

//清中断

clear_timern_irq(TIMER1);

message("timer1 irq get \r\n");

}GIC部分代码:

#include "gic400/gic400.h"

#include "gic400/t113_irq.h"

#include "io.h"

#include "smp.h"

#include "debug.h"

enum {

DIST_CTRL = 0x1000,

DIST_CTR = 0x1004,

DIST_IIDR = 0X1008,

DIST_IGROUPRn = 0x1080,

DIST_ENABLE_SET = 0x1100,

DIST_ENABLE_CLEAR = 0x1180,

DIST_PENDING_SET = 0x1200,

DIST_PENDING_CLEAR = 0x1280,

DIST_ACTIVE_BIT = 0x1300,

DIST_PRI = 0x1400,

DIST_TARGET = 0x1800,

DIST_CONFIG = 0x1c00,

DIST_SOFTINT = 0x1f00,

CPU_CTRL = 0x2000,

CPU_PRIMASK = 0x2004,

CPU_BINPOINT = 0x2008,

CPU_INTACK = 0x200c,

CPU_EOI = 0x2010,

CPU_RUNNINGPRI = 0x2014,

CPU_HIGHPRI = 0x2018,

}GIC_REG_NUM;

#define FGicPs_PRIORITY_OFFSET_CALC(InterruptID) \

((u32)DIST_PRI + (((InterruptID)/4U) * 4U))

#define FGicPs_INT_CFG_OFFSET_CALC(InterruptID) \

((u32)DIST_CONFIG + (((InterruptID)/16U) * 4U))

u32 read_gicd_pri(int int_id)

{

return read32(T113_GIC_400_BASE + FGicPs_PRIORITY_OFFSET_CALC(int_id));

}

void write_gicd_pri(int int_id, u32 val)

{

write32(T113_GIC_400_BASE + FGicPs_PRIORITY_OFFSET_CALC(int_id),val);

}

u32 read_gicd_cfg(int int_id)

{

return read32(T113_GIC_400_BASE + FGicPs_INT_CFG_OFFSET_CALC(int_id));

}

void write_gicd_cfg(int int_id, u32 val)

{

write32(T113_GIC_400_BASE + FGicPs_INT_CFG_OFFSET_CALC(int_id),val);

}

#if 0

static inline uint32_t arm32_get_gic_base(void)

{

uint32_t value;

__asm__ __volatile__(

"mrc p15, 4, %0, c15, c0, 0"

: "=r" (value)

:

: "memory");

return value;

}

#endif

void gic400_dist_init(void)

{

u32_t gic_irqs;

u32_t cpumask;

u32_t gic_base = T113_GIC_400_BASE;

int i;

message("gic_base address is 0x%x \r\n",gic_base);

write32(gic_base + DIST_CTRL, 0x0);

/*

* Find out how many interrupts are supported.

* The GIC only supports up to 1020 interrupt sources.

*/

gic_irqs = read32(gic_base + DIST_CTR) & 0x1f;

gic_irqs = (gic_irqs + 1) * 32;

message("gic irqs supported is %d \r\n",gic_irqs);

if(gic_irqs > 1020)

gic_irqs = 1020;

/*

* Set all global interrupts to this CPU only.

*/

cpumask = 1 << smp_processor_id();

cpumask |= cpumask << 8;

cpumask |= cpumask << 16;

for(i = 32; i < gic_irqs; i += 4)

write32(gic_base + DIST_TARGET + (i / 4 )* 4, cpumask);

/*

* Set all global interrupts to be level triggered, active low.

*/

for(i = 32; i < gic_irqs; i += 16)

write32(gic_base + DIST_CONFIG + (i /16) * 4 , 0);

/*

* Set priority on all global interrupts.

*/

for(i = 32; i < gic_irqs; i += 4)

write32(gic_base + DIST_PRI + (i / 4) * 4, 0xa0a0a0a0);

/*

* Disable all interrupts, leave the SGI and PPI alone

* as these enables are banked registers.

*/

for(i = 32; i < gic_irqs; i += 32)

write32(gic_base + DIST_ENABLE_CLEAR + (i / 32) * 4, 0xffffffff);

//将所有中断设为group0

for(i = 32 ; i < gic_irqs; i += 32)

write32(gic_base + DIST_IGROUPRn + (i / 32) * 4, 0x0);

write32(gic_base + DIST_CTRL, 0x1);

}

void gic400_cpu_init(void)

{

int i;

u32_t gic_base = T113_GIC_400_BASE;

/*

* Deal with the banked SGI and PPI interrupts - enable all

* SGI interrupts, ensure all PPI interrupts are disabled.

*/

write32(gic_base + DIST_ENABLE_CLEAR, 0xffff0000);

write32(gic_base + DIST_ENABLE_SET, 0x0000ffff);

/*

* Set priority on SGI and PPI interrupts

*/

for(i = 0; i < 32; i += 4)

write32(gic_base + DIST_PRI + ( i / 4 ) * 4, 0xa0a0a0a0);

write32(gic_base + CPU_PRIMASK, 0xf0);

write32(gic_base + CPU_CTRL, 0x1);

}

void irq_gic400_enable(int irq) //unmask对应中断

{

write32(T113_GIC_400_BASE + DIST_ENABLE_SET + (irq / 32) * 4, 1 << (irq % 32));

}

void irq_gic400_disable(int irq)//mask对应中断

{

write32(T113_GIC_400_BASE + DIST_ENABLE_CLEAR + (irq / 32) * 4, 1 << (irq % 32));

}

void irq_gic400_settype(void)

{

}

void irq_gic400_dispatch(void)//处理中断后清除中断标志

{

int irq = read32(T113_GIC_400_BASE + CPU_INTACK) & 0x3ff;

irq_gic400_disable(irq);

do_handler(irq);

write32(T113_GIC_400_BASE + CPU_EOI, irq);//清除中断

irq_gic400_enable(irq);

}

void gic_interrupt_handle_exception(void* regs)

{

irq_gic400_dispatch();

}

void start_gic(void)

{

gic400_dist_init();

gic400_cpu_init();

}register_irq:

bool_t register_irq(int irq,void (*func)(void *), void * data, u8 Priority, u8 trigger)

{

u32 val;

u8 LocalPriority;

if(!func)

return FALSE;

if(irq_hanlder_arry[irq].func != null_interrupt_function)

return FALSE;

irq_hanlder_arry[irq].func = func;

irq_hanlder_arry[irq].data = data;

// val = read_gicd_pri(irq);

// LocalPriority = LocalPriority & (u8)(0x000000F8U);

// val &= ~(0x000000FFU << ((irq%4U)*8U));

// val |= (u32)LocalPriority << ((irq%4U)*8U);

// write_gicd_pri(irq,val);

// val = read_gicd_cfg(irq);

// val &= ~(0x00000003U << ((irq%16U)*2U));

// val |= (u32)trigger << ((irq%16U)*2U);

// write_gicd_cfg(irq,val);

irq_gic400_enable(irq);

arm32_interrupt_enable();

return TRUE;

}定时器部分

#include "timer/timer.h"

enum {

TMR_IRQ_EN_REG =0x0000 ,

TMR_IRQ_STA_REG =0x0004 ,

TMR0_CTRL_REG =0x0010 ,

TMR0_INTV_VALUE_REG =0x0014 ,

TMR0_CUR_VALUE_REG =0x0018,

TMR1_CTRL_REG =0x0020 ,

TMR1_INTV_VALUE_REG =0x0024,

TMR1_CUR_VALUE_REG =0x0028,

}TIMER_REG_OFFSET;

#define Timer_Periodic_mode 0

#define Timer_Single_mode 1

//a &= ~(数值<<每组位数*组编号) :将连续几位清零的方法

//数值表示一组中每个bit都是1的情况下的值,比如组位数是2,则数值就是11b所代表的值,即3

//组编号是给寄存器多少个bit为1组进行分组,组号从0开始

void timern_init(int timer_id, int timing_mode) //时钟频率为24000000/2

{

u32 addr,val;

if(timer_id == 0)

addr = TIMER_BASE + TMR0_CTRL_REG;

else

addr = TIMER_BASE + TMR1_CTRL_REG;

if(timing_mode == Timer_Periodic_mode)

val = (u32)0x14;

else

val = (u32)0x94;

write32(addr,val);

}

void set_timern_interval_value(int timer_id, u32 value)

{

u32 addr,val;

val = value;

if(timer_id == 0)

addr = TIMER_BASE + TMR0_INTV_VALUE_REG;

else

addr = TIMER_BASE + TMR1_INTV_VALUE_REG;

write32(addr,val);//设置间隔值

}

void load_timern_interval_value(int timer_id)

{

u32 addr,val;

if(timer_id == 0)

addr = TIMER_BASE + TMR0_CTRL_REG;

else

addr = TIMER_BASE + TMR1_CTRL_REG;

write32(addr, read32(addr)|(1<<1)); //Set the Reload bit

}

void start_timer(int timer_id)

{

u32 addr,val;

if(timer_id == 0)

addr = TIMER_BASE + TMR0_CTRL_REG;

else

addr = TIMER_BASE + TMR1_CTRL_REG;

val = read32(addr);

val |= (0x1 << 0);

write32(addr,val);

}

void start_ms_timer(int timer_id,u32 ms)

{

u32 value = (24000 * ms);

u32 addr;

enable_timern_irq(timer_id);

set_timern_interval_value(timer_id,value);

timern_init(timer_id, Timer_Periodic_mode);

load_timern_interval_value(timer_id);

if(timer_id == 0)

addr = TIMER_BASE + TMR0_CTRL_REG;

else

addr = TIMER_BASE + TMR1_CTRL_REG;

while((read32(addr)>>1)&1);

start_timer(timer_id);

}

void enable_timern_irq(int timer_id)

{

u32 addr,val;

addr = TIMER_BASE + TMR_IRQ_EN_REG;

if(timer_id == 0)

{

val = read32(addr);

val |= (1 << 0);

}

else

{

val = read32(addr);

val |= (1 << 1);

}

write32(addr,val);

addr = TIMER_BASE + TMR_IRQ_STA_REG;

if(timer_id == 0)

{

val = read32(addr);

val |= (1 << 0);

}

else

{

val = read32(addr);

val |= (1 << 1);

}

write32(addr,val);

}

void clear_timern_irq(int timer_id)

{

u32 addr,val;

addr = TIMER_BASE + TMR_IRQ_STA_REG;

if(timer_id == 0)

{

val = read32(addr);

if( (val & 0x01))

{

val |= (1 << 0);

}

}

else

{

val = read32(addr);

if((val & 0x2))

{

val |= (1 << 1);

}

}

write32(addr,val);

}

u32 get_current_timer_value(int timer_id)

{

u32 addr,val;

if(timer_id == 0)

addr = TIMER_BASE + TMR0_CUR_VALUE_REG;

else

addr = TIMER_BASE + TMR1_CUR_VALUE_REG;

val = read32(addr);

return val;

}完整代码工程似乎传不上了,有兴趣的可以私聊

#14 全志 SOC » xboot 跑在t113-s3上,是如何识别boot device的? » 2023-12-31 16:06:45

- zm

- 回复: 2

最近在研究xboot对于T113-S3的启动源码,有一点一直搞不明白,就是在sys-copyself.c中的get_boot_device函数,源码如下:

static int get_boot_device(void)

{

uint8_t s = *((volatile uint8_t *)(0x00020000 + 0x28));

if(s == 0x3)

{

sys_uart_putc('3');

return BOOT_DEVICE_SPINOR;

}

else if(s == 0x4)

{

sys_uart_putc('4');

return BOOT_DEVICE_SPINAND;

}

else if(s == 0x0)

{

sys_uart_putc('0');

return BOOT_DEVICE_SDCARD;

}

sys_uart_putc(s);

return BOOT_DEVICE_SPINOR;

}我还添加了打印,

log在下面:

xboot: /# 3

█████████████████████████████████

██ ▄▄▄▄▄ █▄ ▄▄▄█ █▀▄▀█ ▄▄▄▄▄ ██

██ █ █ ██▀▄▀ ▄▄▄ ▀ ▄ █ █ █ ██

██ █▄▄▄█ █ ▄▀ ▄▀▄▄▀█▀▄▀█ █▄▄▄█ ██

██▄▄▄▄▄▄▄█▄█ █▄█▄▀▄█ ▀▄█▄▄▄▄▄▄▄██

███ ▄▄▀▄▀▀█ ▄█▄▄▀▄█▀▄ ███ ██

██▀█▄▄█ ▄ ▀ ▄▄█▄▄▄█ ██ █ ▄█▄███

██▄█▄▀█▀▄█▄██▀▄ ▄▄ ▄▄ ▀▄▀▄▀▄▄▄ ██

██▀ ▀▄█ ▀ ▄▄█▀ ▀█▄█▄▀█▀▀▄▄ ███

██▀█▄ █▄▄██▄▀▀█▀▄▀█▄▀▀▄▀▀▄▀ ▄▄▀██

██ █▄█▄█▄▄▀ ▄▀▀█▄ ▄█▀▀█ ██ ██ ███

██▄█▄▄█▄▄█▀▀▀▄█▀ ▄▄▄▄▀ ▄▄▄ ▄▄▀██

██ ▄▄▄▄▄ █ ▀ ▀▀▄█ ▄█▄▄ █▄█ ██ ███

██ █ █ █ ▄▄▄▄▀ ▄▄ ▄█▄ ▄ ▄ ▄▀▀██

██ █▄▄▄█ █ ▀ ▄ █▄ ▄█ ▀▀▀▄█ ▄▄ ███

██▄▄▄▄▄▄▄██▄█▄▄▄▄█▄▄▄███▄█▄▄▄████

█████████████████████████████████

_ _

_ _ | |___ _____ _____ _| |_

\ \/ /| _ | _ | _ |_ _| (C) 2007-2023

) ( | |_| | |_| | |_| | | |____JIANJUN.JIANG__

/_/\_\|_____|_____|_____| |_____________________|

V3.0.0 (Dec 31 2023 - 02:44:20) - [mangopi][MangoPi-MQ Based On Allwinner T133-S3 SOC]

[ 0.000020]Probe device 'blk-romdisk.0' with blk-romdisk

[ 0.000800]Probe device 'ext-32k' with clk-fixed

[ 0.000810]Probe device 'rc-16m' with clk-fixed

[ 0.000820]Probe device 'dcxo24m' with clk-fixed我理解的0x00020000 + 0x28这个地方应该存放的是xboot.bin的开头的识别信息里platform information,我把mksunxi之后的xboot.bin给反汇编了(mksunxi中貌似也只是修改了_spl_size和checksum吧),根据反汇编:

00000000 <.data>:

0: ea00000e b 0x40

4: 4e4f4765 cdpmi 7, 4, cr4, cr15, cr5, {3}

8: 3054422e subscc r4, r4, lr, lsr #4

c: c019bd71 andsgt fp, r9, r1, ror sp

10: 0000c000 andeq ip, r0, r0

14: 00000030 andeq r0, r0, r0, lsr r0

18: 30303033 eorscc r3, r0, r3, lsr r0

1c: 00020000 andeq r0, r2, r0

20: 00020000 andeq r0, r2, r0

...

2c: 00302e34 eorseq r2, r0, r4, lsr lr

...

40: ea00000d b 0x7c

44: e59ff014 ldr pc, [pc, #20] ; 0x60

48: e59ff014 ldr pc, [pc, #20] ; 0x64

4c: e59ff014 ldr pc, [pc, #20] ; 0x68

50: e59ff014 ldr pc, [pc, #20] ; 0x6c

54: e59ff014 ldr pc, [pc, #20] ; 0x70

58: e59ff014 ldr pc, [pc, #20] ; 0x74

5c: e59ff014 ldr pc, [pc, #20] ; 0x78

60: 40000400 andmi r0, r0, r0, lsl #8

64: 400004c0 andmi r0, r0, r0, asr #9我发现,0x28处就是0啊,但实际打印出来却是0x3,但我一直找不到是在什么时候把0x00020000 + 0x28处的值改成0x3了,希望有大佬能解释一下。

东莞哇酷科技有限公司开发