- 首页

- » 搜索

- » ymh2008 发表的帖子

页次: 1

#1 Re: 全志 SOC » T113-i应用工业控制的一些设计优化 » 2025-01-08 14:09:14

#2 Re: 全志 SOC » T113-i应用工业控制的一些设计优化 » 2025-01-06 16:39:27

#3 Re: 全志 SOC » T113-i应用工业控制的一些设计优化 » 2025-01-06 16:35:22

#4 Re: 全志 SOC » T113-i应用工业控制的一些设计优化 » 2025-01-06 16:30:47

#5 全志 SOC » T113-i应用工业控制的一些设计优化 » 2025-01-03 16:51:52

- ymh2008

- 回复: 13

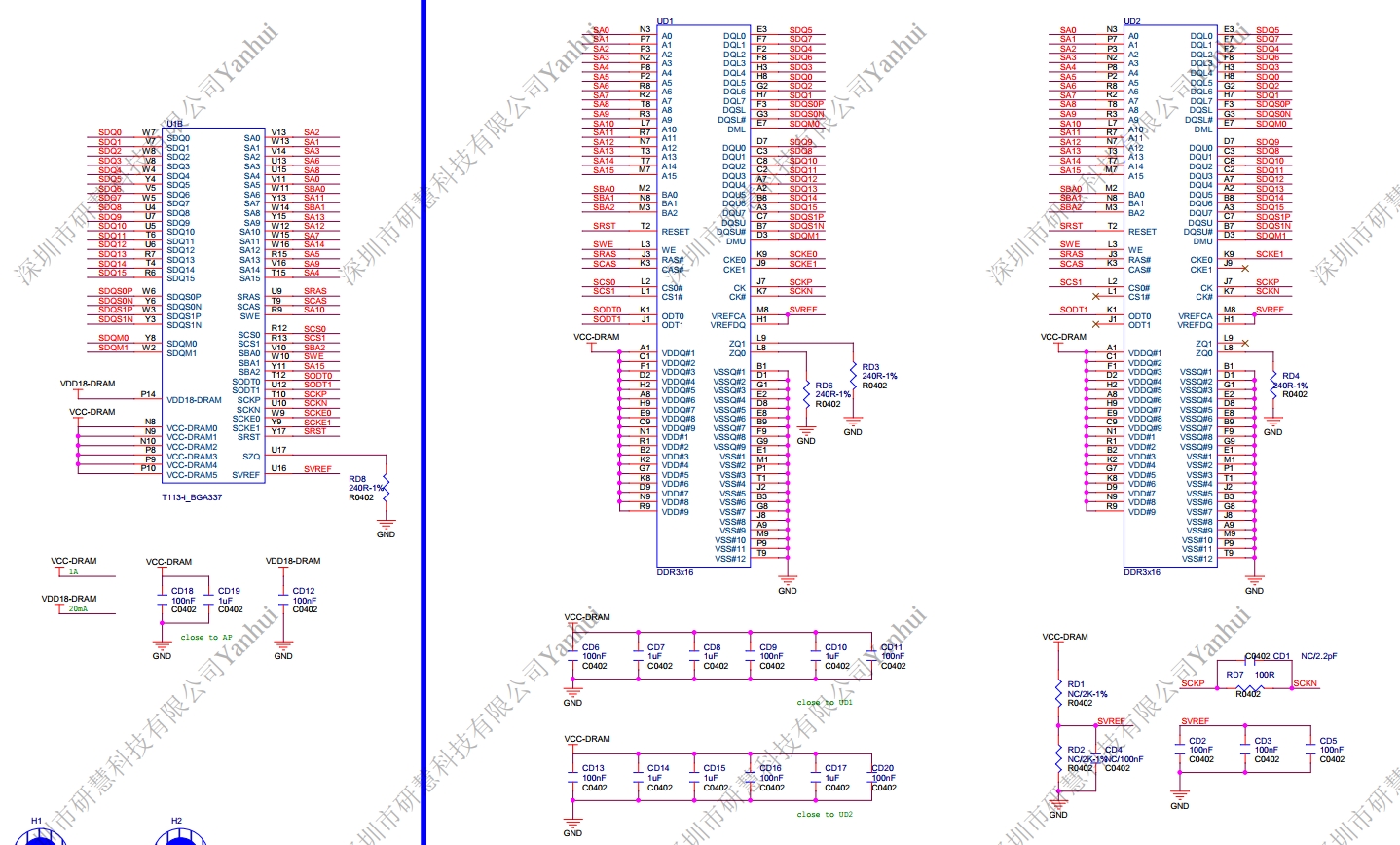

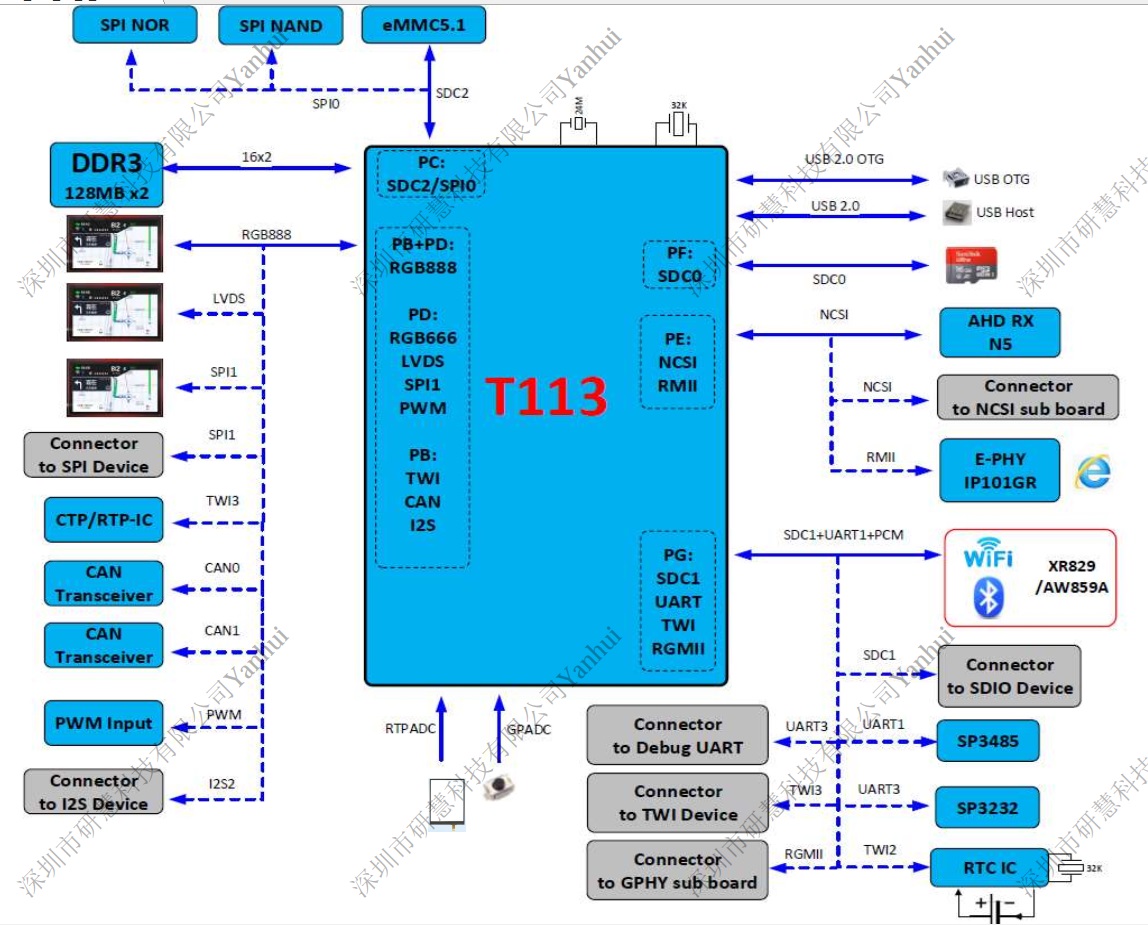

我这边将T113-i用于工业控制CPU,未用到显示、触屏、音频等接口,一些原理图设计可以优化供参考:

1、32KHz时钟,如果外部有单独的RTC芯片,T113的可以不用接晶振;

2、电源:VDD-CPU与VDD-SYS可以合路,用一个0.9V输出的DC-DC即可;

3、配1片DDR3时,VDD-DDR(1.5V)实测电流较小约0.1A,因此也可使用LDO供电;

4、1.8V AVCC要求1%精度,其实可以使用片上的LDO供电,其电流非常小,不会造成芯片功耗负担;

5、要求不高的场合DDR可以只使用一片,使用CS0的那片即可,注意地址线最好不要动线序要不然需要在驱动中做匹配;

#6 Re: 全志 SOC » 自制T113-I 核心板一次成功开机 » 2025-01-02 16:18:33

#7 Re: 全志 SOC » 自制T113-I 核心板一次成功开机 » 2025-01-02 16:15:33

#8 Re: 全志 SOC » 自制T113-I 核心板一次成功开机 » 2025-01-02 16:12:58

#9 Re: 全志 SOC » T113的QSPI通信速率问题 » 2025-01-02 16:09:08

#10 Re: 全志 SOC » T113-I ddr初始化失败[悬赏200块] » 2025-01-02 16:01:16

页次: 1

- 首页

- » 搜索

- » ymh2008 发表的帖子

感谢为中文互联网持续输出优质内容的各位老铁们。

QQ: 516333132, 微信(wechat): whycan_cn (哇酷网/挖坑网/填坑网) service@whycan.cn

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发