#2 Re: ST/STM8/STM8S/STM8L » 【求助】STM32H750外置下载算法 » 2024-07-27 21:37:48

自己改改

source [find interface/stlink.cfg]

set CHIPNAME stm32h750vbt6

# enable stmqspi

if {![info exists QUADSPI]} {

set QUADSPI 1

}

source [find target/stm32h7x.cfg]

# QUADSPI initialization

proc qspi_init { } {

global a

mmw 0x580244E0 0x000007FF 0 ;# RCC_AHB4ENR |= GPIOAEN-GPIOKEN (enable clocks)

mmw 0x580244D4 0x00004000 0 ;# RCC_AHB3ENR |= QSPIEN (enable clock)

sleep 1 ;# Wait for clock startup

# PB06:AF10:H, PB02:AF09:H, PD13:AF09:H, PD12:AF09:H, PD11:AF09:H, PE02:AF09:H

# Port B: PB06:AF10:H, PB02:AF09:H

mmw 0x58020400 0x00002020 0x00001010 ;# MODER

mmw 0x58020408 0x00002020 0x00001010 ;# OSPEEDR

mmw 0x5802040C 0x00000000 0x00003030 ;# PUPDR

mmw 0x58020420 0x0A000900 0x05000600 ;# AFRL

# Port D: PD13:AF09:H, PD12:AF09:H, PD11:AF09:H

mmw 0x58020C00 0x0A800000 0x05400000 ;# MODER

mmw 0x58020C08 0x0A800000 0x05400000 ;# OSPEEDR

mmw 0x58020C0C 0x00000000 0x0FC00000 ;# PUPDR

mmw 0x58020C24 0x00999000 0x00666000 ;# AFRH

# Port E: PE02:AF09:H

mmw 0x58021000 0x00000020 0x00000010 ;# MODER

mmw 0x58021008 0x00000020 0x00000010 ;# OSPEEDR

mmw 0x5802100C 0x00000000 0x00000030 ;# PUPDR

mmw 0x58021020 0x00000900 0x00000600 ;# AFRL

# correct FSIZE is 0x16, however, this causes trouble when

# reading the last bytes at end of bank in *memory mapped* mode

# for single flash mode w25q64jv

;# 010101010000000000000 0 011000

mww 0x52005000 0x05500018 ;# QUADSPI_CR: PRESCALER=5, APMS=1, FTHRES=1, FSEL=0, DFM=0, SSHIFT=1, TCEN=1

mww 0x52005004 0x00160500 ;# QUADSPI_DCR: FSIZE=0x16, CSHT=0x05, CKMODE=0

;# FSIZE flash的大小。

mww 0x52005030 0x00001000 ;# QUADSPI_LPTR: deactivate CS after 4096 clocks when FIFO is full

;# 11010000000000 10 010100000011

mww 0x52005014 0x0D002503 ;# QUADSPI_CCR: FMODE=0x3, DMODE=0x1, DCYC=0x0, ADSIZE=0x2, ADMODE=0x1, IMODE=0x1

mmw 0x52005000 0x00000001 0 ;# QUADSPI_CR: EN=1

# Exit QPI mode

#mmw 0x52005000 0x00000002 0 ;# QUADSPI_CR: ABORT=1

#mww 0x52005014 0x000003F5 ;# QUADSPI_CCR: FMODE=0x0, DMODE=0x0, DCYC=0x0, ADSIZE=0x0, ADMODE=0x0, IMODE=0x3, INSTR=Exit QPI

sleep 1

# reset flash

mmw 0x52005000 0x00000002 0 ;# QUADSPI_CR: ABORT=1

mww 0x52005014 0x00000166 ;# QUADSPI_CCR: FMODE=0x0, DMODE=0x0, DCYC=0x0, ADSIZE=0x0, ADMODE=0x0, IMODE=0x1, INSTR=0x66

mww 0x52005014 0x00000199 ;# QUADSPI_CCR: FMODE=0x0, DMODE=0x0, DCYC=0x0, ADSIZE=0x0, ADMODE=0x0, IMODE=0x1, INSTR=0x99

# memory-mapped read mode with 3-byte addresses

mmw 0x52005000 0x00000002 0 ;# QUADSPI_CR: ABORT=1

;# 11 11 0 00100 00 11 10 11 01 11101011

mww 0x52005014 0x0F10EDEB ;# QUADSPI_CCR: FMODE=0x3, DMODE=0x3, DCYC=0x4, ADSIZE=0x2, ADMODE=0x3, IMODE=0x1, INSTR=READ

;mww 0x52005014 0x0D002503

}

$_CHIPNAME.cpu0 configure -event reset-init {

global QUADSPI

mmw 0x52002000 0x00000004 0x0000000B ;# FLASH_ACR: 4 WS for 192 MHZ HCLK

mmw 0x58024400 0x00000001 0x00000018 ;# RCC_CR: HSIDIV=1, HSI on

mmw 0x58024410 0x10000000 0xEE000007 ;# RCC_CFGR: MCO2=system, MCO2PRE=8, HSI as system clock

mww 0x58024418 0x00000040 ;# RCC_D1CFGR: D1CPRE=1, D1PPRE=2, HPRE=1

mww 0x5802441C 0x00000440 ;# RCC_D2CFGR: D2PPRE2=2, D2PPRE1=2

mww 0x58024420 0x00000040 ;# RCC_D3CFGR: D3PPRE=2

mww 0x58024428 0x00000040 ;# RCC_PPLCKSELR: DIVM3=0, DIVM2=0, DIVM1=4, PLLSRC=HSI

mmw 0x5802442C 0x0001000C 0x00000002 ;# RCC_PLLCFGR: PLL1RGE=8MHz to 16MHz, PLL1VCOSEL=wide

mww 0x58024430 0x01070217 ;# RCC_PLL1DIVR: 192 MHz: DIVR1=2, DIVQ=8, DIVP1=2, DIVN1=24

mmw 0x58024400 0x01000000 0 ;# RCC_CR: PLL1ON=1

sleep 1

mmw 0x58024410 0x00000003 0 ;# RCC_CFGR: PLL1 as system clock

sleep 1

adapter speed 4000

if { $QUADSPI } {

qspi_init

}

}#4 Re: 全志 SOC » Windows裸机程序烧录工具,烧录到SD卡 » 2022-01-18 17:36:55

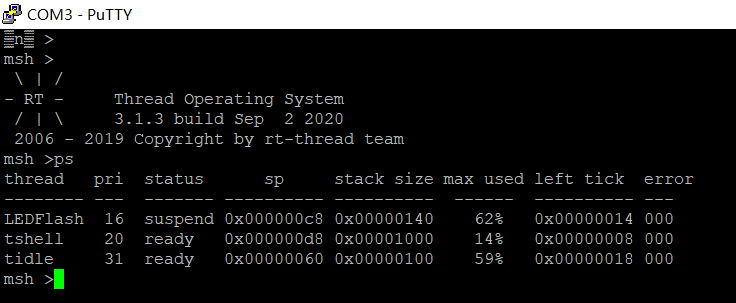

#8 Re: Cortex M0/M3/M4/M7 » 来一发rt-thread 用cmake 编译 » 2020-09-04 12:26:04

Gentlepig wrote:

请教下,msh功能打不开,有可能的原因是什么?

我的板子是gd32vf103c8,环境是vscoede+platformio,编译的是rtthread-nano,串口可以打印出启动信息,但是没有命令输入符。

使能了RTE_USING_FINSH。

在int finsh_system_init(void)函数里加了断点,结果运行仿真后,发现无法在这里停下。

#define RT_USING_FINSH

#define FINSH_THREAD_NAME "tshell"

#define FINSH_USING_HISTORY

#define FINSH_HISTORY_LINES 5

#define FINSH_USING_SYMTAB

#define FINSH_USING_DESCRIPTION

#define FINSH_THREAD_PRIORITY 20

#define FINSH_THREAD_STACK_SIZE 4096

#define FINSH_CMD_SIZE 80

#define FINSH_USING_MSH

#define FINSH_USING_MSH_DEFAULT

#define FINSH_USING_MSH_ONLY

#define FINSH_ARG_MAX 10#10 Cortex M0/M3/M4/M7 » 来一发rt-thread 用cmake 编译 » 2020-09-03 21:34:45

- 表慌张

- 回复: 7

业余爱好的我用不惯eclipse,遂改用clion+cmake+openocd,调试还没有搞定,目前搞了f407和f767两片板子,,,欢迎各位大佬指点。

f767_nano_OK.zip

f407_nano_t1_OK.7z

感谢为中文互联网持续输出优质内容的各位老铁们。

QQ: 516333132, 微信(wechat): whycan_cn (哇酷网/挖坑网/填坑网) service@whycan.cn

东莞哇酷科技有限公司开发

东莞哇酷科技有限公司开发