楼主 #1 2018-09-07 10:48:38 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,472

- 积分: 9202

f1c100s 官方bsp没有整合 电阻触摸屏(RTP)驱动, 现在在主线Linux上面找到驱动了

https://github.com/torvalds/linux/blob/master/drivers/input/touchscreen/sun4i-ts.c

/*

* Allwinner sunxi resistive touchscreen controller driver

*

* Copyright (C) 2013 - 2014 Hans de Goede <hdegoede@redhat.com>

*

* The hwmon parts are based on work by Corentin LABBE which is:

* Copyright (C) 2013 Corentin LABBE <clabbe.montjoie@gmail.com>

*

* This program is free software; you can redistribute it and/or modify

* it under the terms of the GNU General Public License as published by

* the Free Software Foundation; either version 2 of the License, or

* (at your option) any later version.

*

* This program is distributed in the hope that it will be useful,

* but WITHOUT ANY WARRANTY; without even the implied warranty of

* MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

* GNU General Public License for more details.

*/

/*

* The sun4i-ts controller is capable of detecting a second touch, but when a

* second touch is present then the accuracy becomes so bad the reported touch

* location is not useable.

*

* The original android driver contains some complicated heuristics using the

* aprox. distance between the 2 touches to see if the user is making a pinch

* open / close movement, and then reports emulated multi-touch events around

* the last touch coordinate (as the dual-touch coordinates are worthless).

*

* These kinds of heuristics are just asking for trouble (and don't belong

* in the kernel). So this driver offers straight forward, reliable single

* touch functionality only.

*

* s.a. A20 User Manual "1.15 TP" (Documentation/arm/sunxi/README)

* (looks like the description in the A20 User Manual v1.3 is better

* than the one in the A10 User Manual v.1.5)

*/

#include <linux/err.h>

#include <linux/hwmon.h>

#include <linux/thermal.h>

#include <linux/init.h>

#include <linux/input.h>

#include <linux/interrupt.h>

#include <linux/io.h>

#include <linux/module.h>

#include <linux/of_platform.h>

#include <linux/platform_device.h>

#include <linux/slab.h>

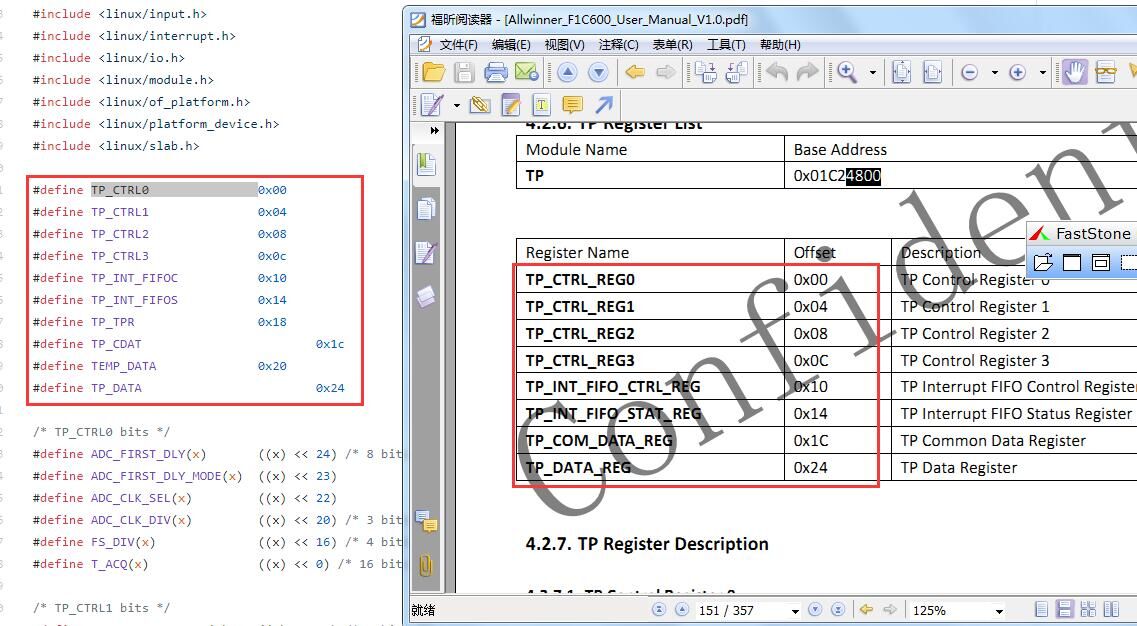

#define TP_CTRL0 0x00

#define TP_CTRL1 0x04

#define TP_CTRL2 0x08

#define TP_CTRL3 0x0c

#define TP_INT_FIFOC 0x10

#define TP_INT_FIFOS 0x14

#define TP_TPR 0x18

#define TP_CDAT 0x1c

#define TEMP_DATA 0x20

#define TP_DATA 0x24

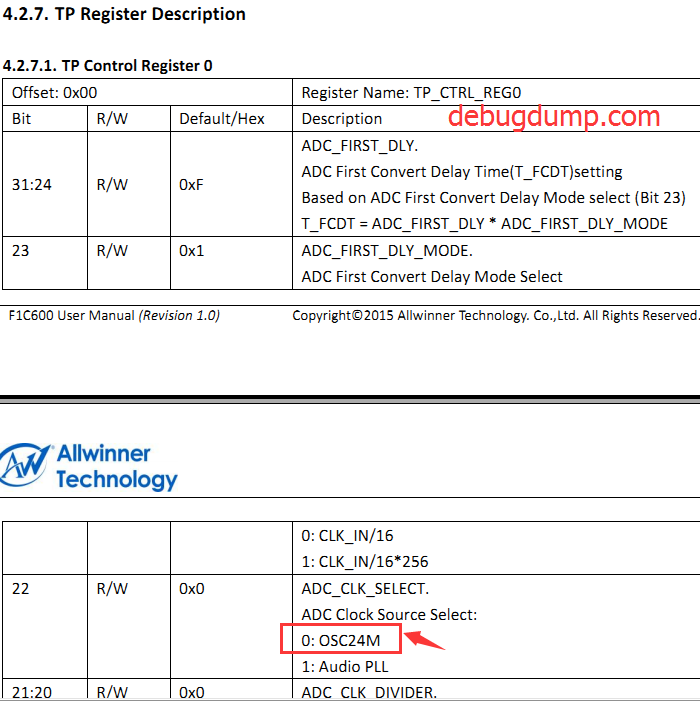

/* TP_CTRL0 bits */

#define ADC_FIRST_DLY(x) ((x) << 24) /* 8 bits */

#define ADC_FIRST_DLY_MODE(x) ((x) << 23)

#define ADC_CLK_SEL(x) ((x) << 22)

#define ADC_CLK_DIV(x) ((x) << 20) /* 3 bits */

#define FS_DIV(x) ((x) << 16) /* 4 bits */

#define T_ACQ(x) ((x) << 0) /* 16 bits */

/* TP_CTRL1 bits */

#define STYLUS_UP_DEBOUN(x) ((x) << 12) /* 8 bits */

#define STYLUS_UP_DEBOUN_EN(x) ((x) << 9)

#define TOUCH_PAN_CALI_EN(x) ((x) << 6)

#define TP_DUAL_EN(x) ((x) << 5)

#define TP_MODE_EN(x) ((x) << 4)

#define TP_ADC_SELECT(x) ((x) << 3)

#define ADC_CHAN_SELECT(x) ((x) << 0) /* 3 bits */

/* on sun6i, bits 3~6 are left shifted by 1 to 4~7 */

#define SUN6I_TP_MODE_EN(x) ((x) << 5)

/* TP_CTRL2 bits */

#define TP_SENSITIVE_ADJUST(x) ((x) << 28) /* 4 bits */

#define TP_MODE_SELECT(x) ((x) << 26) /* 2 bits */

#define PRE_MEA_EN(x) ((x) << 24)

#define PRE_MEA_THRE_CNT(x) ((x) << 0) /* 24 bits */

/* TP_CTRL3 bits */

#define FILTER_EN(x) ((x) << 2)

#define FILTER_TYPE(x) ((x) << 0) /* 2 bits */

/* TP_INT_FIFOC irq and fifo mask / control bits */

#define TEMP_IRQ_EN(x) ((x) << 18)

#define OVERRUN_IRQ_EN(x) ((x) << 17)

#define DATA_IRQ_EN(x) ((x) << 16)

#define TP_DATA_XY_CHANGE(x) ((x) << 13)

#define FIFO_TRIG(x) ((x) << 8) /* 5 bits */

#define DATA_DRQ_EN(x) ((x) << 7)

#define FIFO_FLUSH(x) ((x) << 4)

#define TP_UP_IRQ_EN(x) ((x) << 1)

#define TP_DOWN_IRQ_EN(x) ((x) << 0)

/* TP_INT_FIFOS irq and fifo status bits */

#define TEMP_DATA_PENDING BIT(18)

#define FIFO_OVERRUN_PENDING BIT(17)

#define FIFO_DATA_PENDING BIT(16)

#define TP_IDLE_FLG BIT(2)

#define TP_UP_PENDING BIT(1)

#define TP_DOWN_PENDING BIT(0)

/* TP_TPR bits */

#define TEMP_ENABLE(x) ((x) << 16)

#define TEMP_PERIOD(x) ((x) << 0) /* t = x * 256 * 16 / clkin */

struct sun4i_ts_data {

struct device *dev;

struct input_dev *input;

void __iomem *base;

unsigned int irq;

bool ignore_fifo_data;

int temp_data;

int temp_offset;

int temp_step;

};

static void sun4i_ts_irq_handle_input(struct sun4i_ts_data *ts, u32 reg_val)

{

u32 x, y;

if (reg_val & FIFO_DATA_PENDING) {

x = readl(ts->base + TP_DATA);

y = readl(ts->base + TP_DATA);

/* The 1st location reported after an up event is unreliable */

if (!ts->ignore_fifo_data) {

input_report_abs(ts->input, ABS_X, x);

input_report_abs(ts->input, ABS_Y, y);

/*

* The hardware has a separate down status bit, but

* that gets set before we get the first location,

* resulting in reporting a click on the old location.

*/

input_report_key(ts->input, BTN_TOUCH, 1);

input_sync(ts->input);

} else {

ts->ignore_fifo_data = false;

}

}

if (reg_val & TP_UP_PENDING) {

ts->ignore_fifo_data = true;

input_report_key(ts->input, BTN_TOUCH, 0);

input_sync(ts->input);

}

}

static irqreturn_t sun4i_ts_irq(int irq, void *dev_id)

{

struct sun4i_ts_data *ts = dev_id;

u32 reg_val;

reg_val = readl(ts->base + TP_INT_FIFOS);

if (reg_val & TEMP_DATA_PENDING)

ts->temp_data = readl(ts->base + TEMP_DATA);

if (ts->input)

sun4i_ts_irq_handle_input(ts, reg_val);

writel(reg_val, ts->base + TP_INT_FIFOS);

return IRQ_HANDLED;

}

static int sun4i_ts_open(struct input_dev *dev)

{

struct sun4i_ts_data *ts = input_get_drvdata(dev);

/* Flush, set trig level to 1, enable temp, data and up irqs */

writel(TEMP_IRQ_EN(1) | DATA_IRQ_EN(1) | FIFO_TRIG(1) | FIFO_FLUSH(1) |

TP_UP_IRQ_EN(1), ts->base + TP_INT_FIFOC);

return 0;

}

static void sun4i_ts_close(struct input_dev *dev)

{

struct sun4i_ts_data *ts = input_get_drvdata(dev);

/* Deactivate all input IRQs */

writel(TEMP_IRQ_EN(1), ts->base + TP_INT_FIFOC);

}

static int sun4i_get_temp(const struct sun4i_ts_data *ts, int *temp)

{

/* No temp_data until the first irq */

if (ts->temp_data == -1)

return -EAGAIN;

*temp = ts->temp_data * ts->temp_step - ts->temp_offset;

return 0;

}

static int sun4i_get_tz_temp(void *data, int *temp)

{

return sun4i_get_temp(data, temp);

}

static const struct thermal_zone_of_device_ops sun4i_ts_tz_ops = {

.get_temp = sun4i_get_tz_temp,

};

static ssize_t show_temp(struct device *dev, struct device_attribute *devattr,

char *buf)

{

struct sun4i_ts_data *ts = dev_get_drvdata(dev);

int temp;

int error;

error = sun4i_get_temp(ts, &temp);

if (error)

return error;

return sprintf(buf, "%d\n", temp);

}

static ssize_t show_temp_label(struct device *dev,

struct device_attribute *devattr, char *buf)

{

return sprintf(buf, "SoC temperature\n");

}

static DEVICE_ATTR(temp1_input, S_IRUGO, show_temp, NULL);

static DEVICE_ATTR(temp1_label, S_IRUGO, show_temp_label, NULL);

static struct attribute *sun4i_ts_attrs[] = {

&dev_attr_temp1_input.attr,

&dev_attr_temp1_label.attr,

NULL

};

ATTRIBUTE_GROUPS(sun4i_ts);

static int sun4i_ts_probe(struct platform_device *pdev)

{

struct sun4i_ts_data *ts;

struct device *dev = &pdev->dev;

struct device_node *np = dev->of_node;

struct device *hwmon;

int error;

u32 reg;

bool ts_attached;

u32 tp_sensitive_adjust = 15;

u32 filter_type = 1;

ts = devm_kzalloc(dev, sizeof(struct sun4i_ts_data), GFP_KERNEL);

if (!ts)

return -ENOMEM;

ts->dev = dev;

ts->ignore_fifo_data = true;

ts->temp_data = -1;

if (of_device_is_compatible(np, "allwinner,sun6i-a31-ts")) {

/* Allwinner SDK has temperature (C) = (value / 6) - 271 */

ts->temp_offset = 271000;

ts->temp_step = 167;

} else if (of_device_is_compatible(np, "allwinner,sun4i-a10-ts")) {

/*

* The A10 temperature sensor has quite a wide spread, these

* parameters are based on the averaging of the calibration

* results of 4 completely different boards, with a spread of

* temp_step from 0.096 - 0.170 and temp_offset from 176 - 331.

*/

ts->temp_offset = 257000;

ts->temp_step = 133;

} else {

/*

* The user manuals do not contain the formula for calculating

* the temperature. The formula used here is from the AXP209,

* which is designed by X-Powers, an affiliate of Allwinner:

*

* temperature (C) = (value * 0.1) - 144.7

*

* Allwinner does not have any documentation whatsoever for

* this hardware. Moreover, it is claimed that the sensor

* is inaccurate and cannot work properly.

*/

ts->temp_offset = 144700;

ts->temp_step = 100;

}

ts_attached = of_property_read_bool(np, "allwinner,ts-attached");

if (ts_attached) {

ts->input = devm_input_allocate_device(dev);

if (!ts->input)

return -ENOMEM;

ts->input->name = pdev->name;

ts->input->phys = "sun4i_ts/input0";

ts->input->open = sun4i_ts_open;

ts->input->close = sun4i_ts_close;

ts->input->id.bustype = BUS_HOST;

ts->input->id.vendor = 0x0001;

ts->input->id.product = 0x0001;

ts->input->id.version = 0x0100;

ts->input->evbit[0] = BIT(EV_SYN) | BIT(EV_KEY) | BIT(EV_ABS);

__set_bit(BTN_TOUCH, ts->input->keybit);

input_set_abs_params(ts->input, ABS_X, 0, 4095, 0, 0);

input_set_abs_params(ts->input, ABS_Y, 0, 4095, 0, 0);

input_set_drvdata(ts->input, ts);

}

ts->base = devm_ioremap_resource(dev,

platform_get_resource(pdev, IORESOURCE_MEM, 0));

if (IS_ERR(ts->base))

return PTR_ERR(ts->base);

ts->irq = platform_get_irq(pdev, 0);

error = devm_request_irq(dev, ts->irq, sun4i_ts_irq, 0, "sun4i-ts", ts);

if (error)

return error;

/*

* Select HOSC clk, clkin = clk / 6, adc samplefreq = clkin / 8192,

* t_acq = clkin / (16 * 64)

*/

writel(ADC_CLK_SEL(0) | ADC_CLK_DIV(2) | FS_DIV(7) | T_ACQ(63),

ts->base + TP_CTRL0);

/*

* tp_sensitive_adjust is an optional property

* tp_mode = 0 : only x and y coordinates, as we don't use dual touch

*/

of_property_read_u32(np, "allwinner,tp-sensitive-adjust",

&tp_sensitive_adjust);

writel(TP_SENSITIVE_ADJUST(tp_sensitive_adjust) | TP_MODE_SELECT(0),

ts->base + TP_CTRL2);

/*

* Enable median and averaging filter, optional property for

* filter type.

*/

of_property_read_u32(np, "allwinner,filter-type", &filter_type);

writel(FILTER_EN(1) | FILTER_TYPE(filter_type), ts->base + TP_CTRL3);

/* Enable temperature measurement, period 1953 (2 seconds) */

writel(TEMP_ENABLE(1) | TEMP_PERIOD(1953), ts->base + TP_TPR);

/*

* Set stylus up debounce to aprox 10 ms, enable debounce, and

* finally enable tp mode.

*/

reg = STYLUS_UP_DEBOUN(5) | STYLUS_UP_DEBOUN_EN(1);

if (of_device_is_compatible(np, "allwinner,sun6i-a31-ts"))

reg |= SUN6I_TP_MODE_EN(1);

else

reg |= TP_MODE_EN(1);

writel(reg, ts->base + TP_CTRL1);

/*

* The thermal core does not register hwmon devices for DT-based

* thermal zone sensors, such as this one.

*/

hwmon = devm_hwmon_device_register_with_groups(ts->dev, "sun4i_ts",

ts, sun4i_ts_groups);

if (IS_ERR(hwmon))

return PTR_ERR(hwmon);

devm_thermal_zone_of_sensor_register(ts->dev, 0, ts, &sun4i_ts_tz_ops);

writel(TEMP_IRQ_EN(1), ts->base + TP_INT_FIFOC);

if (ts_attached) {

error = input_register_device(ts->input);

if (error) {

writel(0, ts->base + TP_INT_FIFOC);

return error;

}

}

platform_set_drvdata(pdev, ts);

return 0;

}

static int sun4i_ts_remove(struct platform_device *pdev)

{

struct sun4i_ts_data *ts = platform_get_drvdata(pdev);

/* Explicit unregister to avoid open/close changing the imask later */

if (ts->input)

input_unregister_device(ts->input);

/* Deactivate all IRQs */

writel(0, ts->base + TP_INT_FIFOC);

return 0;

}

static const struct of_device_id sun4i_ts_of_match[] = {

{ .compatible = "allwinner,sun4i-a10-ts", },

{ .compatible = "allwinner,sun5i-a13-ts", },

{ .compatible = "allwinner,sun6i-a31-ts", },

{ /* sentinel */ }

};

MODULE_DEVICE_TABLE(of, sun4i_ts_of_match);

static struct platform_driver sun4i_ts_driver = {

.driver = {

.name = "sun4i-ts",

.of_match_table = of_match_ptr(sun4i_ts_of_match),

},

.probe = sun4i_ts_probe,

.remove = sun4i_ts_remove,

};

module_platform_driver(sun4i_ts_driver);

MODULE_DESCRIPTION("Allwinner sun4i resistive touchscreen controller driver");

MODULE_AUTHOR("Hans de Goede <hdegoede@redhat.com>");

MODULE_LICENSE("GPL");https://github.com/torvalds/linux/blob/master/arch/arm/boot/dts/sun4i-a10.dtsi

/*

* Copyright 2012 Stefan Roese

* Stefan Roese <sr@denx.de>

*

* This file is dual-licensed: you can use it either under the terms

* of the GPL or the X11 license, at your option. Note that this dual

* licensing only applies to this file, and not this project as a

* whole.

*

* a) This library is free software; you can redistribute it and/or

* modify it under the terms of the GNU General Public License as

* published by the Free Software Foundation; either version 2 of the

* License, or (at your option) any later version.

*

* This library is distributed in the hope that it will be useful,

* but WITHOUT ANY WARRANTY; without even the implied warranty of

* MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

* GNU General Public License for more details.

*

* Or, alternatively,

*

* b) Permission is hereby granted, free of charge, to any person

* obtaining a copy of this software and associated documentation

* files (the "Software"), to deal in the Software without

* restriction, including without limitation the rights to use,

* copy, modify, merge, publish, distribute, sublicense, and/or

* sell copies of the Software, and to permit persons to whom the

* Software is furnished to do so, subject to the following

* conditions:

*

* The above copyright notice and this permission notice shall be

* included in all copies or substantial portions of the Software.

*

* THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND,

* EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES

* OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND

* NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT

* HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY,

* WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING

* FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR

* OTHER DEALINGS IN THE SOFTWARE.

*/

#include <dt-bindings/thermal/thermal.h>

#include <dt-bindings/dma/sun4i-a10.h>

#include <dt-bindings/clock/sun4i-a10-ccu.h>

#include <dt-bindings/reset/sun4i-a10-ccu.h>

/ {

#address-cells = <1>;

#size-cells = <1>;

interrupt-parent = <&intc>;

aliases {

ethernet0 = &emac;

};

chosen {

#address-cells = <1>;

#size-cells = <1>;

ranges;

framebuffer-lcd0-hdmi {

compatible = "allwinner,simple-framebuffer",

"simple-framebuffer";

allwinner,pipeline = "de_be0-lcd0-hdmi";

clocks = <&ccu CLK_AHB_LCD0>, <&ccu CLK_AHB_HDMI0>,

<&ccu CLK_AHB_DE_BE0>, <&ccu CLK_DE_BE0>,

<&ccu CLK_TCON0_CH1>, <&ccu CLK_DRAM_DE_BE0>;

status = "disabled";

};

framebuffer-fe0-lcd0-hdmi {

compatible = "allwinner,simple-framebuffer",

"simple-framebuffer";

allwinner,pipeline = "de_fe0-de_be0-lcd0-hdmi";

clocks = <&ccu CLK_AHB_LCD0>, <&ccu CLK_AHB_HDMI0>,

<&ccu CLK_AHB_DE_BE0>, <&ccu CLK_AHB_DE_FE0>,

<&ccu CLK_DE_BE0>, <&ccu CLK_DE_FE0>,

<&ccu CLK_TCON0_CH1>, <&ccu CLK_HDMI>,

<&ccu CLK_DRAM_DE_FE0>, <&ccu CLK_DRAM_DE_BE0>;

status = "disabled";

};

framebuffer-fe0-lcd0 {

compatible = "allwinner,simple-framebuffer",

"simple-framebuffer";

allwinner,pipeline = "de_fe0-de_be0-lcd0";

clocks = <&ccu CLK_AHB_LCD0>, <&ccu CLK_AHB_DE_BE0>,

<&ccu CLK_AHB_DE_FE0>, <&ccu CLK_DE_BE0>,

<&ccu CLK_DE_FE0>, <&ccu CLK_TCON0_CH0>,

<&ccu CLK_DRAM_DE_FE0>, <&ccu CLK_DRAM_DE_BE0>;

status = "disabled";

};

framebuffer-fe0-lcd0-tve0 {

compatible = "allwinner,simple-framebuffer",

"simple-framebuffer";

allwinner,pipeline = "de_fe0-de_be0-lcd0-tve0";

clocks = <&ccu CLK_AHB_TVE0>, <&ccu CLK_AHB_LCD0>,

<&ccu CLK_AHB_DE_BE0>, <&ccu CLK_AHB_DE_FE0>,

<&ccu CLK_DE_BE0>, <&ccu CLK_DE_FE0>,

<&ccu CLK_TCON0_CH1>, <&ccu CLK_DRAM_TVE0>,

<&ccu CLK_DRAM_DE_FE0>, <&ccu CLK_DRAM_DE_BE0>;

status = "disabled";

};

};

cpus {

#address-cells = <1>;

#size-cells = <0>;

cpu0: cpu@0 {

device_type = "cpu";

compatible = "arm,cortex-a8";

reg = <0x0>;

clocks = <&ccu CLK_CPU>;

clock-latency = <244144>; /* 8 32k periods */

operating-points = <

/* kHz uV */

1008000 1400000

912000 1350000

864000 1300000

624000 1250000

>;

#cooling-cells = <2>;

};

};

thermal-zones {

cpu-thermal {

/* milliseconds */

polling-delay-passive = <250>;

polling-delay = <1000>;

thermal-sensors = <&rtp>;

cooling-maps {

map0 {

trip = <&cpu_alert0>;

cooling-device = <&cpu0 THERMAL_NO_LIMIT THERMAL_NO_LIMIT>;

};

};

trips {

cpu_alert0: cpu-alert0 {

/* milliCelsius */

temperature = <850000>;

hysteresis = <2000>;

type = "passive";

};

cpu_crit: cpu-crit {

/* milliCelsius */

temperature = <100000>;

hysteresis = <2000>;

type = "critical";

};

};

};

};

clocks {

#address-cells = <1>;

#size-cells = <1>;

ranges;

osc24M: clk-24M {

#clock-cells = <0>;

compatible = "fixed-clock";

clock-frequency = <24000000>;

clock-output-names = "osc24M";

};

osc32k: clk-32k {

#clock-cells = <0>;

compatible = "fixed-clock";

clock-frequency = <32768>;

clock-output-names = "osc32k";

};

};

de: display-engine {

compatible = "allwinner,sun4i-a10-display-engine";

allwinner,pipelines = <&fe0>, <&fe1>;

status = "disabled";

};

soc {

compatible = "simple-bus";

#address-cells = <1>;

#size-cells = <1>;

ranges;

system-control@1c00000 {

compatible = "allwinner,sun4i-a10-system-control";

reg = <0x01c00000 0x30>;

#address-cells = <1>;

#size-cells = <1>;

ranges;

sram_a: sram@0 {

compatible = "mmio-sram";

reg = <0x00000000 0xc000>;

#address-cells = <1>;

#size-cells = <1>;

ranges = <0 0x00000000 0xc000>;

emac_sram: sram-section@8000 {

compatible = "allwinner,sun4i-a10-sram-a3-a4";

reg = <0x8000 0x4000>;

status = "disabled";

};

};

sram_d: sram@10000 {

compatible = "mmio-sram";

reg = <0x00010000 0x1000>;

#address-cells = <1>;

#size-cells = <1>;

ranges = <0 0x00010000 0x1000>;

otg_sram: sram-section@0 {

compatible = "allwinner,sun4i-a10-sram-d";

reg = <0x0000 0x1000>;

status = "disabled";

};

};

};

dma: dma-controller@1c02000 {

compatible = "allwinner,sun4i-a10-dma";

reg = <0x01c02000 0x1000>;

interrupts = <27>;

clocks = <&ccu CLK_AHB_DMA>;

#dma-cells = <2>;

};

nfc: nand@1c03000 {

compatible = "allwinner,sun4i-a10-nand";

reg = <0x01c03000 0x1000>;

interrupts = <37>;

clocks = <&ccu CLK_AHB_NAND>, <&ccu CLK_NAND>;

clock-names = "ahb", "mod";

dmas = <&dma SUN4I_DMA_DEDICATED 3>;

dma-names = "rxtx";

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

spi0: spi@1c05000 {

compatible = "allwinner,sun4i-a10-spi";

reg = <0x01c05000 0x1000>;

interrupts = <10>;

clocks = <&ccu CLK_AHB_SPI0>, <&ccu CLK_SPI0>;

clock-names = "ahb", "mod";

dmas = <&dma SUN4I_DMA_DEDICATED 27>,

<&dma SUN4I_DMA_DEDICATED 26>;

dma-names = "rx", "tx";

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

spi1: spi@1c06000 {

compatible = "allwinner,sun4i-a10-spi";

reg = <0x01c06000 0x1000>;

interrupts = <11>;

clocks = <&ccu CLK_AHB_SPI1>, <&ccu CLK_SPI1>;

clock-names = "ahb", "mod";

dmas = <&dma SUN4I_DMA_DEDICATED 9>,

<&dma SUN4I_DMA_DEDICATED 8>;

dma-names = "rx", "tx";

pinctrl-names = "default";

pinctrl-0 = <&spi1_pins>, <&spi1_cs0_pin>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

emac: ethernet@1c0b000 {

compatible = "allwinner,sun4i-a10-emac";

reg = <0x01c0b000 0x1000>;

interrupts = <55>;

clocks = <&ccu CLK_AHB_EMAC>;

allwinner,sram = <&emac_sram 1>;

pinctrl-names = "default";

pinctrl-0 = <&emac_pins>;

status = "disabled";

};

mdio: mdio@1c0b080 {

compatible = "allwinner,sun4i-a10-mdio";

reg = <0x01c0b080 0x14>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

tcon0: lcd-controller@1c0c000 {

compatible = "allwinner,sun4i-a10-tcon";

reg = <0x01c0c000 0x1000>;

interrupts = <44>;

resets = <&ccu RST_TCON0>;

reset-names = "lcd";

clocks = <&ccu CLK_AHB_LCD0>,

<&ccu CLK_TCON0_CH0>,

<&ccu CLK_TCON0_CH1>;

clock-names = "ahb",

"tcon-ch0",

"tcon-ch1";

clock-output-names = "tcon0-pixel-clock";

dmas = <&dma SUN4I_DMA_DEDICATED 14>;

ports {

#address-cells = <1>;

#size-cells = <0>;

tcon0_in: port@0 {

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

tcon0_in_be0: endpoint@0 {

reg = <0>;

remote-endpoint = <&be0_out_tcon0>;

};

tcon0_in_be1: endpoint@1 {

reg = <1>;

remote-endpoint = <&be1_out_tcon0>;

};

};

tcon0_out: port@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

tcon0_out_hdmi: endpoint@1 {

reg = <1>;

remote-endpoint = <&hdmi_in_tcon0>;

allwinner,tcon-channel = <1>;

};

};

};

};

tcon1: lcd-controller@1c0d000 {

compatible = "allwinner,sun4i-a10-tcon";

reg = <0x01c0d000 0x1000>;

interrupts = <45>;

resets = <&ccu RST_TCON1>;

reset-names = "lcd";

clocks = <&ccu CLK_AHB_LCD1>,

<&ccu CLK_TCON1_CH0>,

<&ccu CLK_TCON1_CH1>;

clock-names = "ahb",

"tcon-ch0",

"tcon-ch1";

clock-output-names = "tcon1-pixel-clock";

dmas = <&dma SUN4I_DMA_DEDICATED 15>;

ports {

#address-cells = <1>;

#size-cells = <0>;

tcon1_in: port@0 {

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

tcon1_in_be0: endpoint@0 {

reg = <0>;

remote-endpoint = <&be0_out_tcon1>;

};

tcon1_in_be1: endpoint@1 {

reg = <1>;

remote-endpoint = <&be1_out_tcon1>;

};

};

tcon1_out: port@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

tcon1_out_hdmi: endpoint@1 {

reg = <1>;

remote-endpoint = <&hdmi_in_tcon1>;

allwinner,tcon-channel = <1>;

};

};

};

};

mmc0: mmc@1c0f000 {

compatible = "allwinner,sun4i-a10-mmc";

reg = <0x01c0f000 0x1000>;

clocks = <&ccu CLK_AHB_MMC0>, <&ccu CLK_MMC0>;

clock-names = "ahb", "mmc";

interrupts = <32>;

pinctrl-names = "default";

pinctrl-0 = <&mmc0_pins>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

mmc1: mmc@1c10000 {

compatible = "allwinner,sun4i-a10-mmc";

reg = <0x01c10000 0x1000>;

clocks = <&ccu CLK_AHB_MMC1>, <&ccu CLK_MMC1>;

clock-names = "ahb", "mmc";

interrupts = <33>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

mmc2: mmc@1c11000 {

compatible = "allwinner,sun4i-a10-mmc";

reg = <0x01c11000 0x1000>;

clocks = <&ccu CLK_AHB_MMC2>, <&ccu CLK_MMC2>;

clock-names = "ahb", "mmc";

interrupts = <34>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

mmc3: mmc@1c12000 {

compatible = "allwinner,sun4i-a10-mmc";

reg = <0x01c12000 0x1000>;

clocks = <&ccu CLK_AHB_MMC3>, <&ccu CLK_MMC3>;

clock-names = "ahb", "mmc";

interrupts = <35>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

usb_otg: usb@1c13000 {

compatible = "allwinner,sun4i-a10-musb";

reg = <0x01c13000 0x0400>;

clocks = <&ccu CLK_AHB_OTG>;

interrupts = <38>;

interrupt-names = "mc";

phys = <&usbphy 0>;

phy-names = "usb";

extcon = <&usbphy 0>;

allwinner,sram = <&otg_sram 1>;

status = "disabled";

};

usbphy: phy@1c13400 {

#phy-cells = <1>;

compatible = "allwinner,sun4i-a10-usb-phy";

reg = <0x01c13400 0x10 0x01c14800 0x4 0x01c1c800 0x4>;

reg-names = "phy_ctrl", "pmu1", "pmu2";

clocks = <&ccu CLK_USB_PHY>;

clock-names = "usb_phy";

resets = <&ccu RST_USB_PHY0>,

<&ccu RST_USB_PHY1>,

<&ccu RST_USB_PHY2>;

reset-names = "usb0_reset", "usb1_reset", "usb2_reset";

status = "disabled";

};

ehci0: usb@1c14000 {

compatible = "allwinner,sun4i-a10-ehci", "generic-ehci";

reg = <0x01c14000 0x100>;

interrupts = <39>;

clocks = <&ccu CLK_AHB_EHCI0>;

phys = <&usbphy 1>;

phy-names = "usb";

status = "disabled";

};

ohci0: usb@1c14400 {

compatible = "allwinner,sun4i-a10-ohci", "generic-ohci";

reg = <0x01c14400 0x100>;

interrupts = <64>;

clocks = <&ccu CLK_USB_OHCI0>, <&ccu CLK_AHB_OHCI0>;

phys = <&usbphy 1>;

phy-names = "usb";

status = "disabled";

};

crypto: crypto-engine@1c15000 {

compatible = "allwinner,sun4i-a10-crypto";

reg = <0x01c15000 0x1000>;

interrupts = <86>;

clocks = <&ccu CLK_AHB_SS>, <&ccu CLK_SS>;

clock-names = "ahb", "mod";

};

hdmi: hdmi@1c16000 {

compatible = "allwinner,sun4i-a10-hdmi";

reg = <0x01c16000 0x1000>;

interrupts = <58>;

clocks = <&ccu CLK_AHB_HDMI0>, <&ccu CLK_HDMI>,

<&ccu CLK_PLL_VIDEO0_2X>,

<&ccu CLK_PLL_VIDEO1_2X>;

clock-names = "ahb", "mod", "pll-0", "pll-1";

dmas = <&dma SUN4I_DMA_NORMAL 16>,

<&dma SUN4I_DMA_NORMAL 16>,

<&dma SUN4I_DMA_DEDICATED 24>;

dma-names = "ddc-tx", "ddc-rx", "audio-tx";

status = "disabled";

ports {

#address-cells = <1>;

#size-cells = <0>;

hdmi_in: port@0 {

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

hdmi_in_tcon0: endpoint@0 {

reg = <0>;

remote-endpoint = <&tcon0_out_hdmi>;

};

hdmi_in_tcon1: endpoint@1 {

reg = <1>;

remote-endpoint = <&tcon1_out_hdmi>;

};

};

hdmi_out: port@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

};

};

};

spi2: spi@1c17000 {

compatible = "allwinner,sun4i-a10-spi";

reg = <0x01c17000 0x1000>;

interrupts = <12>;

clocks = <&ccu CLK_AHB_SPI2>, <&ccu CLK_SPI2>;

clock-names = "ahb", "mod";

dmas = <&dma SUN4I_DMA_DEDICATED 29>,

<&dma SUN4I_DMA_DEDICATED 28>;

dma-names = "rx", "tx";

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

ahci: sata@1c18000 {

compatible = "allwinner,sun4i-a10-ahci";

reg = <0x01c18000 0x1000>;

interrupts = <56>;

clocks = <&ccu CLK_AHB_SATA>, <&ccu CLK_SATA>;

status = "disabled";

};

ehci1: usb@1c1c000 {

compatible = "allwinner,sun4i-a10-ehci", "generic-ehci";

reg = <0x01c1c000 0x100>;

interrupts = <40>;

clocks = <&ccu CLK_AHB_EHCI1>;

phys = <&usbphy 2>;

phy-names = "usb";

status = "disabled";

};

ohci1: usb@1c1c400 {

compatible = "allwinner,sun4i-a10-ohci", "generic-ohci";

reg = <0x01c1c400 0x100>;

interrupts = <65>;

clocks = <&ccu CLK_USB_OHCI1>, <&ccu CLK_AHB_OHCI1>;

phys = <&usbphy 2>;

phy-names = "usb";

status = "disabled";

};

spi3: spi@1c1f000 {

compatible = "allwinner,sun4i-a10-spi";

reg = <0x01c1f000 0x1000>;

interrupts = <50>;

clocks = <&ccu CLK_AHB_SPI3>, <&ccu CLK_SPI3>;

clock-names = "ahb", "mod";

dmas = <&dma SUN4I_DMA_DEDICATED 31>,

<&dma SUN4I_DMA_DEDICATED 30>;

dma-names = "rx", "tx";

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

ccu: clock@1c20000 {

compatible = "allwinner,sun4i-a10-ccu";

reg = <0x01c20000 0x400>;

clocks = <&osc24M>, <&osc32k>;

clock-names = "hosc", "losc";

#clock-cells = <1>;

#reset-cells = <1>;

};

intc: interrupt-controller@1c20400 {

compatible = "allwinner,sun4i-a10-ic";

reg = <0x01c20400 0x400>;

interrupt-controller;

#interrupt-cells = <1>;

};

pio: pinctrl@1c20800 {

compatible = "allwinner,sun4i-a10-pinctrl";

reg = <0x01c20800 0x400>;

interrupts = <28>;

clocks = <&ccu CLK_APB0_PIO>, <&osc24M>, <&osc32k>;

clock-names = "apb", "hosc", "losc";

gpio-controller;

interrupt-controller;

#interrupt-cells = <3>;

#gpio-cells = <3>;

can0_ph_pins: can0-ph-pins {

pins = "PH20", "PH21";

function = "can";

};

emac_pins: emac0-pins {

pins = "PA0", "PA1", "PA2",

"PA3", "PA4", "PA5", "PA6",

"PA7", "PA8", "PA9", "PA10",

"PA11", "PA12", "PA13", "PA14",

"PA15", "PA16";

function = "emac";

};

i2c0_pins: i2c0-pins {

pins = "PB0", "PB1";

function = "i2c0";

};

i2c1_pins: i2c1-pins {

pins = "PB18", "PB19";

function = "i2c1";

};

i2c2_pins: i2c2-pins {

pins = "PB20", "PB21";

function = "i2c2";

};

ir0_rx_pins: ir0-rx-pin {

pins = "PB4";

function = "ir0";

};

ir0_tx_pins: ir0-tx-pin {

pins = "PB3";

function = "ir0";

};

ir1_rx_pins: ir1-rx-pin {

pins = "PB23";

function = "ir1";

};

ir1_tx_pins: ir1-tx-pin {

pins = "PB22";

function = "ir1";

};

mmc0_pins: mmc0-pins {

pins = "PF0", "PF1", "PF2",

"PF3", "PF4", "PF5";

function = "mmc0";

drive-strength = <30>;

bias-pull-up;

};

ps2_ch0_pins: ps2-ch0-pins {

pins = "PI20", "PI21";

function = "ps2";

};

ps2_ch1_ph_pins: ps2-ch1-ph-pins {

pins = "PH12", "PH13";

function = "ps2";

};

pwm0_pin: pwm0-pin {

pins = "PB2";

function = "pwm";

};

pwm1_pin: pwm1-pin {

pins = "PI3";

function = "pwm";

};

spdif_tx_pin: spdif-tx-pin {

pins = "PB13";

function = "spdif";

bias-pull-up;

};

spi0_pi_pins: spi0-pi-pins {

pins = "PI11", "PI12", "PI13";

function = "spi0";

};

spi0_cs0_pi_pin: spi0-cs0-pi-pin {

pins = "PI10";

function = "spi0";

};

spi1_pins: spi1-pins {

pins = "PI17", "PI18", "PI19";

function = "spi1";

};

spi1_cs0_pin: spi1-cs0-pin {

pins = "PI16";

function = "spi1";

};

spi2_pb_pins: spi2-pb-pins {

pins = "PB15", "PB16", "PB17";

function = "spi2";

};

spi2_pc_pins: spi2-pc-pins {

pins = "PC20", "PC21", "PC22";

function = "spi2";

};

spi2_cs0_pb_pin: spi2-cs0-pb-pin {

pins = "PB14";

function = "spi2";

};

spi2_cs0_pc_pins: spi2-cs0-pc-pin {

pins = "PC19";

function = "spi2";

};

uart0_pb_pins: uart0-pb-pins {

pins = "PB22", "PB23";

function = "uart0";

};

uart0_pf_pins: uart0-pf-pins {

pins = "PF2", "PF4";

function = "uart0";

};

uart1_pins: uart1-pins {

pins = "PA10", "PA11";

function = "uart1";

};

};

timer@1c20c00 {

compatible = "allwinner,sun4i-a10-timer";

reg = <0x01c20c00 0x90>;

interrupts = <22>;

clocks = <&osc24M>;

};

wdt: watchdog@1c20c90 {

compatible = "allwinner,sun4i-a10-wdt";

reg = <0x01c20c90 0x10>;

};

rtc: rtc@1c20d00 {

compatible = "allwinner,sun4i-a10-rtc";

reg = <0x01c20d00 0x20>;

interrupts = <24>;

};

pwm: pwm@1c20e00 {

compatible = "allwinner,sun4i-a10-pwm";

reg = <0x01c20e00 0xc>;

clocks = <&osc24M>;

#pwm-cells = <3>;

status = "disabled";

};

spdif: spdif@1c21000 {

#sound-dai-cells = <0>;

compatible = "allwinner,sun4i-a10-spdif";

reg = <0x01c21000 0x400>;

interrupts = <13>;

clocks = <&ccu CLK_APB0_SPDIF>, <&ccu CLK_SPDIF>;

clock-names = "apb", "spdif";

dmas = <&dma SUN4I_DMA_NORMAL 2>,

<&dma SUN4I_DMA_NORMAL 2>;

dma-names = "rx", "tx";

status = "disabled";

};

ir0: ir@1c21800 {

compatible = "allwinner,sun4i-a10-ir";

clocks = <&ccu CLK_APB0_IR0>, <&ccu CLK_IR0>;

clock-names = "apb", "ir";

interrupts = <5>;

reg = <0x01c21800 0x40>;

status = "disabled";

};

ir1: ir@1c21c00 {

compatible = "allwinner,sun4i-a10-ir";

clocks = <&ccu CLK_APB0_IR1>, <&ccu CLK_IR1>;

clock-names = "apb", "ir";

interrupts = <6>;

reg = <0x01c21c00 0x40>;

status = "disabled";

};

i2s0: i2s@1c22400 {

#sound-dai-cells = <0>;

compatible = "allwinner,sun4i-a10-i2s";

reg = <0x01c22400 0x400>;

interrupts = <16>;

clocks = <&ccu CLK_APB0_I2S0>, <&ccu CLK_I2S0>;

clock-names = "apb", "mod";

dmas = <&dma SUN4I_DMA_NORMAL 3>,

<&dma SUN4I_DMA_NORMAL 3>;

dma-names = "rx", "tx";

status = "disabled";

};

lradc: lradc@1c22800 {

compatible = "allwinner,sun4i-a10-lradc-keys";

reg = <0x01c22800 0x100>;

interrupts = <31>;

status = "disabled";

};

codec: codec@1c22c00 {

#sound-dai-cells = <0>;

compatible = "allwinner,sun4i-a10-codec";

reg = <0x01c22c00 0x40>;

interrupts = <30>;

clocks = <&ccu CLK_APB0_CODEC>, <&ccu CLK_CODEC>;

clock-names = "apb", "codec";

dmas = <&dma SUN4I_DMA_NORMAL 19>,

<&dma SUN4I_DMA_NORMAL 19>;

dma-names = "rx", "tx";

status = "disabled";

};

sid: eeprom@1c23800 {

compatible = "allwinner,sun4i-a10-sid";

reg = <0x01c23800 0x10>;

};

rtp: rtp@1c25000 {

compatible = "allwinner,sun4i-a10-ts";

reg = <0x01c25000 0x100>;

interrupts = <29>;

#thermal-sensor-cells = <0>;

};

uart0: serial@1c28000 {

compatible = "snps,dw-apb-uart";

reg = <0x01c28000 0x400>;

interrupts = <1>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_APB1_UART0>;

status = "disabled";

};

uart1: serial@1c28400 {

compatible = "snps,dw-apb-uart";

reg = <0x01c28400 0x400>;

interrupts = <2>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_APB1_UART1>;

status = "disabled";

};

uart2: serial@1c28800 {

compatible = "snps,dw-apb-uart";

reg = <0x01c28800 0x400>;

interrupts = <3>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_APB1_UART2>;

status = "disabled";

};

uart3: serial@1c28c00 {

compatible = "snps,dw-apb-uart";

reg = <0x01c28c00 0x400>;

interrupts = <4>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_APB1_UART3>;

status = "disabled";

};

uart4: serial@1c29000 {

compatible = "snps,dw-apb-uart";

reg = <0x01c29000 0x400>;

interrupts = <17>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_APB1_UART4>;

status = "disabled";

};

uart5: serial@1c29400 {

compatible = "snps,dw-apb-uart";

reg = <0x01c29400 0x400>;

interrupts = <18>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_APB1_UART5>;

status = "disabled";

};

uart6: serial@1c29800 {

compatible = "snps,dw-apb-uart";

reg = <0x01c29800 0x400>;

interrupts = <19>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_APB1_UART6>;

status = "disabled";

};

uart7: serial@1c29c00 {

compatible = "snps,dw-apb-uart";

reg = <0x01c29c00 0x400>;

interrupts = <20>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_APB1_UART7>;

status = "disabled";

};

ps20: ps2@1c2a000 {

compatible = "allwinner,sun4i-a10-ps2";

reg = <0x01c2a000 0x400>;

interrupts = <62>;

clocks = <&ccu CLK_APB1_PS20>;

status = "disabled";

};

ps21: ps2@1c2a400 {

compatible = "allwinner,sun4i-a10-ps2";

reg = <0x01c2a400 0x400>;

interrupts = <63>;

clocks = <&ccu CLK_APB1_PS21>;

status = "disabled";

};

i2c0: i2c@1c2ac00 {

compatible = "allwinner,sun4i-a10-i2c";

reg = <0x01c2ac00 0x400>;

interrupts = <7>;

clocks = <&ccu CLK_APB1_I2C0>;

pinctrl-names = "default";

pinctrl-0 = <&i2c0_pins>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

i2c1: i2c@1c2b000 {

compatible = "allwinner,sun4i-a10-i2c";

reg = <0x01c2b000 0x400>;

interrupts = <8>;

clocks = <&ccu CLK_APB1_I2C1>;

pinctrl-names = "default";

pinctrl-0 = <&i2c1_pins>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

i2c2: i2c@1c2b400 {

compatible = "allwinner,sun4i-a10-i2c";

reg = <0x01c2b400 0x400>;

interrupts = <9>;

clocks = <&ccu CLK_APB1_I2C2>;

pinctrl-names = "default";

pinctrl-0 = <&i2c2_pins>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

can0: can@1c2bc00 {

compatible = "allwinner,sun4i-a10-can";

reg = <0x01c2bc00 0x400>;

interrupts = <26>;

clocks = <&ccu CLK_APB1_CAN>;

status = "disabled";

};

mali: gpu@1c40000 {

compatible = "allwinner,sun4i-a10-mali", "arm,mali-400";

reg = <0x01c40000 0x10000>;

interrupts = <69>,

<70>,

<71>,

<72>,

<73>;

interrupt-names = "gp",

"gpmmu",

"pp0",

"ppmmu0",

"pmu";

clocks = <&ccu CLK_AHB_GPU>, <&ccu CLK_GPU>;

clock-names = "bus", "core";

resets = <&ccu RST_GPU>;

assigned-clocks = <&ccu CLK_GPU>;

assigned-clock-rates = <384000000>;

};

fe0: display-frontend@1e00000 {

compatible = "allwinner,sun4i-a10-display-frontend";

reg = <0x01e00000 0x20000>;

interrupts = <47>;

clocks = <&ccu CLK_AHB_DE_FE0>, <&ccu CLK_DE_FE0>,

<&ccu CLK_DRAM_DE_FE0>;

clock-names = "ahb", "mod",

"ram";

resets = <&ccu RST_DE_FE0>;

ports {

#address-cells = <1>;

#size-cells = <0>;

fe0_out: port@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

fe0_out_be0: endpoint@0 {

reg = <0>;

remote-endpoint = <&be0_in_fe0>;

};

fe0_out_be1: endpoint@1 {

reg = <1>;

remote-endpoint = <&be1_in_fe0>;

};

};

};

};

fe1: display-frontend@1e20000 {

compatible = "allwinner,sun4i-a10-display-frontend";

reg = <0x01e20000 0x20000>;

interrupts = <48>;

clocks = <&ccu CLK_AHB_DE_FE1>, <&ccu CLK_DE_FE1>,

<&ccu CLK_DRAM_DE_FE1>;

clock-names = "ahb", "mod",

"ram";

resets = <&ccu RST_DE_FE1>;

ports {

#address-cells = <1>;

#size-cells = <0>;

fe1_out: port@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

fe1_out_be0: endpoint@0 {

reg = <0>;

remote-endpoint = <&be0_in_fe1>;

};

fe1_out_be1: endpoint@1 {

reg = <1>;

remote-endpoint = <&be1_in_fe1>;

};

};

};

};

be1: display-backend@1e40000 {

compatible = "allwinner,sun4i-a10-display-backend";

reg = <0x01e40000 0x10000>;

interrupts = <48>;

clocks = <&ccu CLK_AHB_DE_BE1>, <&ccu CLK_DE_BE1>,

<&ccu CLK_DRAM_DE_BE1>;

clock-names = "ahb", "mod",

"ram";

resets = <&ccu RST_DE_BE1>;

ports {

#address-cells = <1>;

#size-cells = <0>;

be1_in: port@0 {

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

be1_in_fe0: endpoint@0 {

reg = <0>;

remote-endpoint = <&fe0_out_be1>;

};

be1_in_fe1: endpoint@1 {

reg = <1>;

remote-endpoint = <&fe1_out_be1>;

};

};

be1_out: port@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

be1_out_tcon0: endpoint@0 {

reg = <0>;

remote-endpoint = <&tcon0_in_be1>;

};

be1_out_tcon1: endpoint@1 {

reg = <1>;

remote-endpoint = <&tcon1_in_be1>;

};

};

};

};

be0: display-backend@1e60000 {

compatible = "allwinner,sun4i-a10-display-backend";

reg = <0x01e60000 0x10000>;

interrupts = <47>;

clocks = <&ccu CLK_AHB_DE_BE0>, <&ccu CLK_DE_BE0>,

<&ccu CLK_DRAM_DE_BE0>;

clock-names = "ahb", "mod",

"ram";

resets = <&ccu RST_DE_BE0>;

ports {

#address-cells = <1>;

#size-cells = <0>;

be0_in: port@0 {

#address-cells = <1>;

#size-cells = <0>;

reg = <0>;

be0_in_fe0: endpoint@0 {

reg = <0>;

remote-endpoint = <&fe0_out_be0>;

};

be0_in_fe1: endpoint@1 {

reg = <1>;

remote-endpoint = <&fe1_out_be0>;

};

};

be0_out: port@1 {

#address-cells = <1>;

#size-cells = <0>;

reg = <1>;

be0_out_tcon0: endpoint@0 {

reg = <0>;

remote-endpoint = <&tcon0_in_be0>;

};

be0_out_tcon1: endpoint@1 {

reg = <1>;

remote-endpoint = <&tcon1_in_be0>;

};

};

};

};

};

};离线

楼主 #2 2018-09-07 10:49:37 分享评论

#3 2018-09-07 18:05:38 分享评论

- msr06rr

- 会员

- 所在地: 苏州

- 注册时间: 2018-01-11

- 已发帖子: 181

- 积分: 171.5

Re: f1c100s 官方bsp没有整合 电阻触摸屏(RTP)驱动, 现在在主线Linux上面找到驱动了

终于有电阻触摸驱动了,坐等晕哥手把手系列教程 ![]()

离线

楼主 #4 2018-09-08 09:31:22 分享评论

楼主 #5 2018-09-08 09:38:27 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,472

- 积分: 9202

离线

#6 2018-12-12 21:46:56 分享评论

- Peter

- 会员

- 注册时间: 2018-12-12

- 已发帖子: 36

- 积分: 36

Re: f1c100s 官方bsp没有整合 电阻触摸屏(RTP)驱动, 现在在主线Linux上面找到驱动了

大神,现在顶帖晚了吗:p ,这个A10的驱动可以直接添加到Licheepi Nano上吗

最近编辑记录 Peter (2018-12-12 21:47:44)

离线

楼主 #7 2018-12-12 22:10:44 分享评论

#8 2019-08-07 16:08:56 分享评论

- 傅伟清

- 会员

- 注册时间: 2019-07-17

- 已发帖子: 39

- 积分: 39

Re: f1c100s 官方bsp没有整合 电阻触摸屏(RTP)驱动, 现在在主线Linux上面找到驱动了

晕哥,这个Temp——data 0x20,手册里没有呀,不影响吗

离线

楼主 #9 2019-08-07 16:19:47 分享评论

#10 2019-09-06 23:12:56 分享评论

- nuvoton

- 会员

- 注册时间: 2019-06-17

- 已发帖子: 59

- 积分: 59

Re: f1c100s 官方bsp没有整合 电阻触摸屏(RTP)驱动, 现在在主线Linux上面找到驱动了

离线

#11 2020-11-13 00:51:26 分享评论

- mcd12

- 会员

- 注册时间: 2020-11-12

- 已发帖子: 2

- 积分: 2

Re: f1c100s 官方bsp没有整合 电阻触摸屏(RTP)驱动, 现在在主线Linux上面找到驱动了

嗨,大家好。 如何将内置电阻式触摸屏驱动程序(RTP)F1C100S移植到Rtthread littlevGL7.1。

离线

#12 2020-11-13 08:19:36 分享评论

- sea18c

- 会员

- 注册时间: 2019-08-05

- 已发帖子: 230

- 积分: 222.5

Re: f1c100s 官方bsp没有整合 电阻触摸屏(RTP)驱动, 现在在主线Linux上面找到驱动了

参考XBOOT的裸机程序就可以了

离线

#13 2020-11-13 16:04:04 分享评论

- mcd12

- 会员

- 注册时间: 2020-11-12

- 已发帖子: 2

- 积分: 2

Re: f1c100s 官方bsp没有整合 电阻触摸屏(RTP)驱动, 现在在主线Linux上面找到驱动了

你好。 谢谢,请输入代码或链接。 谢谢 sea18c.

离线

#14 2020-11-15 22:23:03 分享评论

- sea18c

- 会员

- 注册时间: 2019-08-05

- 已发帖子: 230

- 积分: 222.5

Re: f1c100s 官方bsp没有整合 电阻触摸屏(RTP)驱动, 现在在主线Linux上面找到驱动了

mcd12 wrote:

你好。 谢谢,请输入代码或链接。 谢谢 sea18c.

https://gitee.com/xboot/xboot/blob/master/src/arch/arm32/mach-f1c100s/driver/ts-f1c100s.c

离线

#15 2020-11-19 16:58:51 分享评论

- mcd12

- 会员

- 注册时间: 2020-11-12

- 已发帖子: 2

- 积分: 2

Re: f1c100s 官方bsp没有整合 电阻触摸屏(RTP)驱动, 现在在主线Linux上面找到驱动了

你好.谢谢亲爱的朋友sea18c.

离线

#16 2020-11-19 17:03:11 分享评论

- mcd12

- 会员

- 注册时间: 2020-11-12

- 已发帖子: 2

- 积分: 2

Re: f1c100s 官方bsp没有整合 电阻触摸屏(RTP)驱动, 现在在主线Linux上面找到驱动了

sea18c wrote:

mcd12 wrote:

你好。 谢谢,请输入代码或链接。 谢谢 sea18c.

https://gitee.com/xboot/xboot/blob/master/src/arch/arm32/mach-f1c100s/driver/ts-f1c100s.c

你好.请帮助我提供端口代码。

使用rt_hw_interrupt_install函数而不是request_irq函数,或者使用其他什么输入参数?

抱歉,我是否在新的RT-THREAD中这样问.

离线

#18 2020-11-19 21:31:11 分享评论

- mcd12

- 会员

- 注册时间: 2020-11-12

- 已发帖子: 2

- 积分: 2

Re: f1c100s 官方bsp没有整合 电阻触摸屏(RTP)驱动, 现在在主线Linux上面找到驱动了

aozima wrote:

#define TOUCHPANEL_INTERRUPT (20) rt_hw_interrupt_install(TOUCHPANEL_INTERRUPT, you_touch_handle, param, "touch");

你好. 亲爱的朋友aozima 感谢您解释参数结构并编写you_touch_handle函数吗?

离线

东莞哇酷科技有限公司开发