楼主 #1 2021-01-25 20:12:26 分享评论

- 丨晋丨

- 会员

- 注册时间: 2021-01-06

- 已发帖子: 20

- 积分: 170

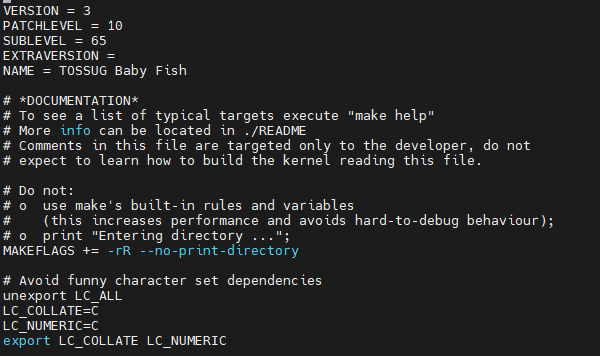

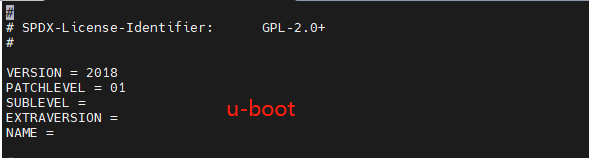

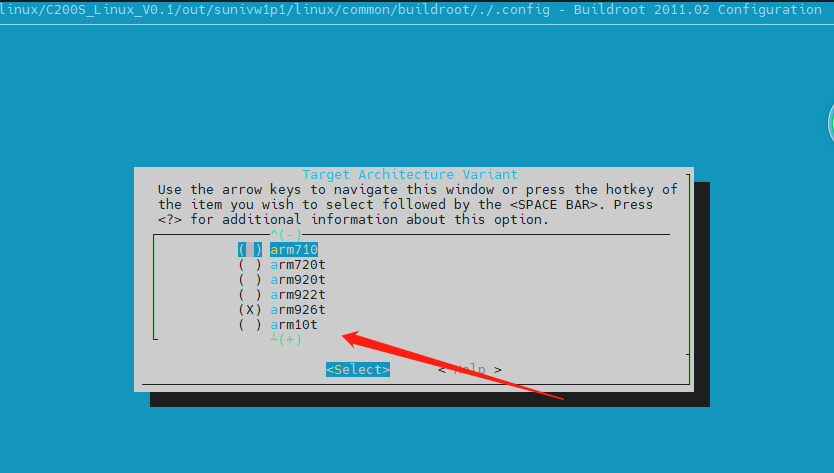

F1C100S/F1C200S主线uboot更改默认终端串口为uart1

买了芒果派的f1c200s板子,烧录nano的uboot无LOG输出,最终发现串口终端使用的是uart1,而nano的源码是使用的uart0。

找了很多资料,参考:https://whycan.com/t_1624.html修改u-boot源码uart1为终端输出,并打包成patch分享给大家使用。

补丁包:f1c100s-uboot串口1终端补丁包.zip

详细的修改步骤之前记录在CSDN了:全志F1C100S/F1C200S学习笔记(3)——主线uboot更改默认终端串口为uart1

补丁使用:

1、u-boot-uart1.patch 放在u-boot 同级目录

2、进入u-boot目录

3、执行patch -p1 < ../u-boot-uart1.patch

离线

楼主 #2 2021-01-25 20:21:06 分享评论

- 丨晋丨

- 会员

- 注册时间: 2021-01-06

- 已发帖子: 20

- 积分: 170

Re: F1C100S/F1C200S主线uboot更改默认终端串口为uart1

贴出修改内容:

1、 u-boot/arch/arm/dts/suniv-f1c100s-licheepi-nano.dts 17行:

/ {

model = "Lichee Pi Nano";

compatible = "licheepi,licheepi-nano", "allwinner,suniv-f1c100s",

"allwinner,suniv";

aliases {

serial0 = &uart0;

serial1 = &uart1;

spi0 = &spi0;

};

chosen {

stdout-path = "serial1:115200n8";

};

};

...

&uart1 {

pinctrl-names = "default";

pinctrl-0 = <&uart1_pins_a>;

status = "okay";

};离线

楼主 #3 2021-01-25 20:24:26 分享评论

- 丨晋丨

- 会员

- 注册时间: 2021-01-06

- 已发帖子: 20

- 积分: 170

Re: F1C100S/F1C200S主线uboot更改默认终端串口为uart1

2、 u-boot/arch/arm/dts/suniv.dtsi 124行:

pio: pinctrl@1c20800 {

compatible = "allwinner,suniv-pinctrl";

reg = <0x01c20800 0x400>;

interrupts = <38>, <39>, <40>;

clocks = <&ccu CLK_BUS_PIO>, <&osc24M>, <&osc32k>;

clock-names = "apb", "hosc", "losc";

gpio-controller;

interrupt-controller;

#interrupt-cells = <3>;

#gpio-cells = <3>;

spi0_pins_a: spi0-pins-pc {

pins = "PC0", "PC1", "PC2", "PC3";

function = "spi0";

};

uart0_pins_a: uart-pins-pe {

pins = "PE0", "PE1";

function = "uart0";

};

uart1_pins_a: uart-pins-pa {

pins = "PA2", "PA3";

function = "uart1";

};

};离线

楼主 #4 2021-01-25 20:27:41 分享评论

- 丨晋丨

- 会员

- 注册时间: 2021-01-06

- 已发帖子: 20

- 积分: 170

Re: F1C100S/F1C200S主线uboot更改默认终端串口为uart1

3、 /u-boot/arch/arm/include/asm/arch-sunxi/gpio.h 146行:

#define SUNXI_GPA_EMAC 2

#define SUNIV_GPA_UART1 54、 u-boot/include/configs/suniv.h 17行:

#include <configs/sunxi-common.h>

#undef CONFIG_CONS_INDEX

#define CONFIG_CONS_INDEX 2 //UART1

#endif /* __CONFIG_H */5、 u-boot/arch/arm/mach-sunxi/board.c 86行:

#elif CONFIG_CONS_INDEX == 1 && defined(CONFIG_MACH_SUNIV)

sunxi_gpio_set_cfgpin(SUNXI_GPE(0), SUNIV_GPE_UART0);

sunxi_gpio_set_cfgpin(SUNXI_GPE(1), SUNIV_GPE_UART0);

sunxi_gpio_set_pull(SUNXI_GPE(1), SUNXI_GPIO_PULL_UP);

#elif CONFIG_CONS_INDEX == 2 && defined(CONFIG_MACH_SUNIV)

sunxi_gpio_set_cfgpin(SUNXI_GPA(2), SUNIV_GPA_UART1);

sunxi_gpio_set_cfgpin(SUNXI_GPA(3), SUNIV_GPA_UART1);

sunxi_gpio_set_pull(SUNXI_GPA(3), SUNXI_GPIO_PULL_UP);离线

#5 2022-03-11 16:05:37 分享评论

- wakerze

- 会员

- 注册时间: 2022-02-28

- 已发帖子: 9

- 积分: 4

Re: F1C100S/F1C200S主线uboot更改默认终端串口为uart1

最近正好需要把串口从uart0换到uart1,前来学习学习

离线

#6 2022-03-17 16:50:02 分享评论

- Sam

- 会员

- 注册时间: 2019-12-06

- 已发帖子: 55

- 积分: 50

Re: F1C100S/F1C200S主线uboot更改默认终端串口为uart1

@丨晋丨

参考链接:https://blog.csdn.net/p1279030826/article/details/113116927

我的调试串口是UART2,F1C100S PE7,PE8

根据参考链接与手册修改了

1./u-boot/arch/arm/include/asm/arch-sunxi/gpio.h 146行

#define SUNIV_GPE_UART2 32.u-boot/arch/arm/mach-sunxi/board.c 86行:

#elif CONFIG_CONS_INDEX == 2 && defined(CONFIG_MACH_SUNIV)

sunxi_gpio_set_cfgpin(SUNXI_GPE(7), SUNIV_GPE_UART2);

sunxi_gpio_set_cfgpin(SUNXI_GPE(8), SUNIV_GPE_UART2);

sunxi_gpio_set_pull(SUNXI_GPE(7), SUNXI_GPIO_PULL_UP);3.u-boot/include/configs/suniv.h17行

#define CONFIG_CONS_INDEX 24.u-boot/include/configs/sunxi-common.h 276行

#elif CONFIG_CONS_INDEX == 2 && defined(CONFIG_MACH_SUNIV)

#define OF_STDOUT_PATH "/soc@01c00000/serial@01c28400:115200"修改后,编译正常

LD spl/u-boot-spl

OBJCOPY spl/u-boot-spl-nodtb.bin

COPY spl/u-boot-spl.bin

MKSUNXI spl/sunxi-spl.bin

OBJCOPY u-boot-nodtb.bin

CAT u-boot-dtb.bin

COPY u-boot.bin

MKIMAGE u-boot.img

COPY u-boot.dtb

BINMAN u-boot-sunxi-with-spl.bin

OBJCOPY u-boot.srec

SYM u-boot.sym

MKIMAGE u-boot-dtb.img

CHK include/config.h

CFG u-boot.cfg烧录到nor 的零地址

./sunxi-fel -p spiflash-write 0x000000 u-boot-sunxi-with-spl.bin启动 串口还是没有任何输出:(

离线

#7 2022-03-17 17:26:26 分享评论

- Sam

- 会员

- 注册时间: 2019-12-06

- 已发帖子: 55

- 积分: 50

Re: F1C100S/F1C200S主线uboot更改默认终端串口为uart1

@Sam

再附一个 BSP生成的dtb文件,反编译成dts:

/dts-v1/;

/memreserve/ 0x0000000081000000 0x0000000000010000;

/ {

model = "sunivw1p1";

compatible = "arm,sunivw1p1", "arm,suniw1p1";

interrupt-parent = <0x1>;

#address-cells = <0x2>;

#size-cells = <0x2>;

clocks {

compatible = "allwinner,sunxi-clk-init";

device_type = "clocks";

#address-cells = <0x2>;

#size-cells = <0x2>;

ranges;

reg = <0x0 0x1c20000 0x0 0x2d0>;

losc {

#clock-cells = <0x0>;

compatible = "allwinner,fixed-clock";

clock-frequency = <0x8000>;

clock-output-names = "losc";

};

hosc {

#clock-cells = <0x0>;

compatible = "allwinner,fixed-clock";

clock-frequency = <0x16e3600>;

clock-output-names = "hosc";

linux,phandle = <0x11>;

phandle = <0x11>;

};

pll_cpu {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-pll-clock";

lock-mode = "none";

assigned-clock-rates = <0x1f78a400>;

clock-output-names = "pll_cpu";

};

pll_audio {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-pll-clock";

lock-mode = "none";

clock-output-names = "pll_audio";

linux,phandle = <0x2>;

phandle = <0x2>;

};

pll_video {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-pll-clock";

lock-mode = "none";

assigned-clock-rates = <0x11b3dc40>;

clock-output-names = "pll_video";

linux,phandle = <0x3>;

phandle = <0x3>;

};

pll_ve {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-pll-clock";

lock-mode = "none";

clock-output-names = "pll_ve";

linux,phandle = <0x6>;

phandle = <0x6>;

};

pll_ddr {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-pll-clock";

lock-mode = "none";

assigned-clock-rates = <0x1298be00>;

clock-output-names = "pll_ddr";

};

pll_periph {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-pll-clock";

lock-mode = "none";

clock-output-names = "pll_periph";

linux,phandle = <0x4>;

phandle = <0x4>;

};

pll_audiox8 {

#clock-cells = <0x0>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x2>;

clock-mult = <0x8>;

clock-div = <0x1>;

clock-output-names = "pll_audiox8";

};

pll_audiox4 {

#clock-cells = <0x0>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x2>;

clock-mult = <0x8>;

clock-div = <0x2>;

clock-output-names = "pll_audiox4";

};

pll_audiox2 {

#clock-cells = <0x0>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x2>;

clock-mult = <0x8>;

clock-div = <0x4>;

clock-output-names = "pll_audiox2";

};

pll_videox2 {

#clock-cells = <0x0>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x3>;

clock-mult = <0x2>;

clock-div = <0x1>;

clock-output-names = "pll_videox2";

};

pll_periphx2 {

#clock-cells = <0x0>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x4>;

clock-mult = <0x2>;

clock-div = <0x1>;

clock-output-names = "pll_periphx2";

};

cpu {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "cpu";

};

pll_periphahb {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "pll_periphahb";

};

ahb1 {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "ahb1";

};

apb1 {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "apb1";

};

sdmmc0_mod {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "sdmmc0_mod";

linux,phandle = <0x27>;

phandle = <0x27>;

};

sdmmc0_bus {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "sdmmc0_bus";

linux,phandle = <0x28>;

phandle = <0x28>;

};

sdmmc0_rst {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "sdmmc0_rst";

linux,phandle = <0x29>;

phandle = <0x29>;

};

sdmmc1_mod {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "sdmmc1_mod";

linux,phandle = <0x2c>;

phandle = <0x2c>;

};

sdmmc1_bus {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "sdmmc1_bus";

linux,phandle = <0x2d>;

phandle = <0x2d>;

};

sdmmc1_rst {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "sdmmc1_rst";

linux,phandle = <0x2e>;

phandle = <0x2e>;

};

spi0 {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "spi0";

linux,phandle = <0x1e>;

phandle = <0x1e>;

};

spi1 {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "spi1";

linux,phandle = <0x23>;

phandle = <0x23>;

};

usbphy0 {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "usbphy0";

linux,phandle = <0x39>;

phandle = <0x39>;

};

usbotg {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "usbotg";

linux,phandle = <0x3a>;

phandle = <0x3a>;

};

audio {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "audio";

linux,phandle = <0x3b>;

phandle = <0x3b>;

};

avs {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "avs";

};

codec {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "codec";

linux,phandle = <0x42>;

phandle = <0x42>;

};

spdif {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "spdif";

linux,phandle = <0x3f>;

phandle = <0x3f>;

};

debe {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "debe";

linux,phandle = <0x32>;

phandle = <0x32>;

};

defe {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "defe";

linux,phandle = <0x31>;

phandle = <0x31>;

};

tcon {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "tcon";

linux,phandle = <0x34>;

phandle = <0x34>;

};

deinterlace {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "deinterlace";

linux,phandle = <0x33>;

phandle = <0x33>;

};

tve_clk2 {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "tve_clk2";

};

tve_clk1 {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "tve_clk1";

};

tvd {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "tvd";

};

csi_m {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "csi_m";

linux,phandle = <0x35>;

phandle = <0x35>;

};

ve {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "ve";

linux,phandle = <0x7>;

phandle = <0x7>;

};

sdram {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "sdram";

};

dma {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "dma";

linux,phandle = <0x5>;

phandle = <0x5>;

};

uart0 {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "uart0";

linux,phandle = <0x8>;

phandle = <0x8>;

};

uart1 {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "uart1";

linux,phandle = <0xb>;

phandle = <0xb>;

};

uart2 {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "uart2";

linux,phandle = <0xe>;

phandle = <0xe>;

};

twi0 {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "twi0";

linux,phandle = <0x15>;

phandle = <0x15>;

};

twi1 {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "twi1";

linux,phandle = <0x18>;

phandle = <0x18>;

};

twi2 {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "twi2";

linux,phandle = <0x1b>;

phandle = <0x1b>;

};

rsb {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "rsb";

};

cir {

#clock-cells = <0x0>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "cir";

linux,phandle = <0x12>;

phandle = <0x12>;

};

};

soc {

compatible = "simple-bus";

#address-cells = <0x2>;

#size-cells = <0x2>;

device_type = "soc";

ranges;

pinctrl@01c20800 {

compatible = "allwinner,sunivw1p1-pinctrl";

reg = <0x0 0x1c20800 0x0 0x400>;

interrupts = <0x26 0x27 0x28>;

device_type = "pio";

gpio-controller;

interrupt-controller;

#interrupt-cells = <0x2>;

#size-cells = <0x0>;

#gpio-cells = <0x6>;

linux,phandle = <0x38>;

phandle = <0x38>;

vdevice@0 {

allwinner,pins = "PC0", "PC1";

allwinner,function = "vdevice";

allwinner,muxsel = <0x4>;

allwinner,drive = <0x1>;

allwinner,pull = <0x1>;

};

uart0@1 {

allwinner,pins = "PF2", "PF4";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x7>;

allwinner,drive = <0x1>;

allwinner,pull = <0x1>;

linux,phandle = <0xa>;

phandle = <0xa>;

};

uart1@1 {

allwinner,pins = "PA3", "PA2", "PA1", "PA0";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x7>;

allwinner,drive = <0x1>;

allwinner,pull = <0x1>;

linux,phandle = <0xd>;

phandle = <0xd>;

};

uart2@1 {

allwinner,pins = "PE7", "PE8", "PE9", "PE10";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x7>;

allwinner,drive = <0x1>;

allwinner,pull = <0x1>;

linux,phandle = <0x10>;

phandle = <0x10>;

};

twi0@1 {

allwinner,pins = "PD12", "PD0";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x7>;

allwinner,drive = <0x1>;

allwinner,pull = <0x0>;

linux,phandle = <0x17>;

phandle = <0x17>;

};

twi1@1 {

allwinner,pins = "PB0", "PB1";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x7>;

allwinner,drive = <0x1>;

allwinner,pull = <0x0>;

linux,phandle = <0x1a>;

phandle = <0x1a>;

};

twi2@1 {

allwinner,pins = "PE0", "PE1";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x7>;

allwinner,drive = <0x1>;

allwinner,pull = <0x0>;

linux,phandle = <0x1d>;

phandle = <0x1d>;

};

spi0@2 {

allwinner,pins = "PC0", "PC1", "PC2", "PC3";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x7>;

allwinner,drive = <0x1>;

allwinner,pull = <0x0>;

linux,phandle = <0x21>;

phandle = <0x21>;

};

spi1@0 {

allwinner,pins = "PB1", "PB3", "PB2";

allwinner,pname = "spi1_mosi", "spi1_miso", "spi1_sclk";

allwinner,function = "spi1";

allwinner,muxsel = <0x6>;

allwinner,drive = <0x1>;

allwinner,pull = <0x0>;

linux,phandle = <0x24>;

phandle = <0x24>;

};

spi1@1 {

allwinner,pins = "PB0";

allwinner,pname = "spi1_cs0";

allwinner,function = "spi1";

allwinner,muxsel = <0x6>;

allwinner,drive = <0x1>;

allwinner,pull = <0x1>;

linux,phandle = <0x25>;

phandle = <0x25>;

};

spi1@2 {

allwinner,pins = "PB0", "PB1", "PB2", "PB3";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x7>;

allwinner,drive = <0x1>;

allwinner,pull = <0x0>;

linux,phandle = <0x26>;

phandle = <0x26>;

};

csi0@0 {

allwinner,pins = "PE0", "PE1", "PE2", "PE3", "PE4", "PE5", "PE6", "PE7", "PE8", "PE9", "PE10";

allwinner,pname = "csi0_hsync", "csi0_vsync", "csi0_pck", "csi0_d0", "csi0_d1", "csi0_d2", "csi0_d3", "csi0_d4", "csi0_d5", "csi0_d6", "csi0_d7";

allwinner,function = "csi0";

allwinner,muxsel = <0x2>;

allwinner,drive = <0x1>;

allwinner,pull = <0x0>;

allwinner,data = <0x0>;

linux,phandle = <0x36>;

phandle = <0x36>;

};

csi0_sleep@0 {

allwinner,pins = "PE0", "PE1", "PE2", "PE3", "PE4", "PE5", "PE6", "PE7", "PE8", "PE9", "PE10";

allwinner,pname = "csi0_hsync", "csi0_vsync", "csi0_pck", "csi0_d0", "csi0_d1", "csi0_d2", "csi0_d3", "csi0_d4", "csi0_d5", "csi0_d6", "csi0_d7";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x7>;

allwinner,drive = <0x1>;

allwinner,pull = <0x0>;

allwinner,data = <0x0>;

linux,phandle = <0x37>;

phandle = <0x37>;

};

sdc0@1 {

allwinner,pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x7>;

allwinner,drive = <0x1>;

allwinner,pull = <0x1>;

linux,phandle = <0x2b>;

phandle = <0x2b>;

};

sdc1@1 {

allwinner,pins = "PC0", "PC1", "PC2";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x7>;

allwinner,drive = <0x1>;

allwinner,pull = <0x1>;

linux,phandle = <0x30>;

phandle = <0x30>;

};

daudio0@0 {

allwinner,pins = "PE3", "PE4", "PE5", "PE6";

allwinner,function = "iis0";

allwinner,muxsel = <0x4>;

allwinner,drive = <0x1>;

allwinner,pull = <0x0>;

linux,phandle = <0x3c>;

phandle = <0x3c>;

};

daudio0@1 {

allwinner,pins = "PD7";

allwinner,function = "iis0";

allwinner,muxsel = <0x3>;

allwinner,drive = <0x1>;

allwinner,pull = <0x0>;

linux,phandle = <0x3d>;

phandle = <0x3d>;

};

daudio0_sleep@0 {

allwinner,pins = "PE3", "PE4", "PE5", "PE6", "PE12";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x7>;

allwinner,drive = <0x1>;

allwinner,pull = <0x0>;

linux,phandle = <0x3e>;

phandle = <0x3e>;

};

spdif@0 {

allwinner,pins = "PD17";

allwinner,function = "spdif0";

allwinner,muxsel = <0x3>;

allwinner,drive = <0x1>;

allwinner,pull = <0x0>;

linux,phandle = <0x40>;

phandle = <0x40>;

};

spdif_sleep@0 {

allwinner,pins = "PD17";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x7>;

allwinner,drive = <0x1>;

allwinner,pull = <0x0>;

linux,phandle = <0x41>;

phandle = <0x41>;

};

cir@0 {

allwinner,pins = "PE11";

allwinner,function = "cir";

allwinner,muxsel = <0x4>;

allwinner,drive = <0x1>;

allwinner,pull = <0x0>;

linux,phandle = <0x13>;

phandle = <0x13>;

};

cir_sleep@0 {

allwinner,pins = "PE11";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x7>;

allwinner,drive = <0x1>;

allwinner,pull = <0x0>;

linux,phandle = <0x14>;

phandle = <0x14>;

};

card0_boot_para@0 {

linux,phandle = <0x47>;

phandle = <0x47>;

allwinner,pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5";

allwinner,function = "card0_boot_para";

allwinner,pname = "sdc_d1", "sdc_d0", "sdc_clk", "sdc_cmd", "sdc_d3", "sdc_d2";

allwinner,muxsel = <0x2>;

allwinner,pull = <0x1>;

allwinner,drive = <0x2>;

allwinner,data = <0xffffffff>;

};

card2_boot_para@0 {

linux,phandle = <0x48>;

phandle = <0x48>;

allwinner,pins = "PC5", "PC6", "PC8", "PC9", "PC10", "PC11", "PC12", "PC13", "PC14", "PC15", "PC16", "PC1";

allwinner,function = "card2_boot_para";

allwinner,pname = "sdc_clk", "sdc_cmd", "sdc_d0", "sdc_d1", "sdc_d2", "sdc_d3", "sdc_d4", "sdc_d5", "sdc_d6", "sdc_d7", "sdc_emmc_rst", "sdc_ds";

allwinner,muxsel = <0x3>;

allwinner,pull = <0x1>;

allwinner,drive = <0x3>;

allwinner,data = <0xffffffff>;

};

twi_para@0 {

linux,phandle = <0x49>;

phandle = <0x49>;

allwinner,pins = "PD12", "PD0";

allwinner,function = "twi_para";

allwinner,pname = "twi_scl", "twi_sda";

allwinner,muxsel = <0x3>;

allwinner,pull = <0xffffffff>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

uart_para@0 {

linux,phandle = <0x4a>;

phandle = <0x4a>;

allwinner,pins = "PE7", "PE8";

allwinner,function = "uart_para";

allwinner,pname = "uart_debug_tx", "uart_debug_rx";

allwinner,muxsel = <0x3>;

allwinner,pull = <0x1>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

force_uart_para@0 {

linux,phandle = <0x4b>;

phandle = <0x4b>;

allwinner,pins = "PE7", "PE8";

allwinner,function = "force_uart_para";

allwinner,pname = "force_uart__tx", "force_uart__rx";

allwinner,muxsel = <0x3>;

allwinner,pull = <0x1>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

jtag_para@0 {

linux,phandle = <0x4c>;

phandle = <0x4c>;

allwinner,pins = "PH9", "PH10", "PH11", "PH12";

allwinner,function = "jtag_para";

allwinner,pname = "jtag_ms", "jtag_ck", "jtag_do", "jtag_di";

allwinner,muxsel = <0x3>;

allwinner,pull = <0xffffffff>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

twi0@0 {

linux,phandle = <0x4d>;

phandle = <0x4d>;

allwinner,pins = "PD12", "PD0";

allwinner,function = "twi0";

allwinner,pname = "twi0_scl", "twi0_sda";

allwinner,muxsel = <0x3>;

allwinner,pull = <0xffffffff>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

twi1@0 {

linux,phandle = <0x4e>;

phandle = <0x4e>;

allwinner,pins = "PB0", "PB1";

allwinner,function = "twi1";

allwinner,pname = "twi1_scl", "twi1_sda";

allwinner,muxsel = <0x2>;

allwinner,pull = <0xffffffff>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

twi2@0 {

linux,phandle = <0x4f>;

phandle = <0x4f>;

allwinner,pins = "PE0", "PE1";

allwinner,function = "twi2";

allwinner,pname = "twi2_scl", "twi2_sda";

allwinner,muxsel = <0x4>;

allwinner,pull = <0xffffffff>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

uart0@0 {

linux,phandle = <0x50>;

phandle = <0x50>;

allwinner,pins = "PF2", "PF4";

allwinner,function = "uart0";

allwinner,pname = "uart0_tx", "uart0_rx";

allwinner,muxsel = <0x3>;

allwinner,pull = <0x1>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

uart1@0 {

linux,phandle = <0x51>;

phandle = <0x51>;

allwinner,pins = "PA2", "PA3";

allwinner,function = "uart1";

allwinner,pname = "uart1_tx", "uart1_rx";

allwinner,muxsel = <0x5>;

allwinner,pull = <0x1>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

uart2@0 {

linux,phandle = <0x52>;

phandle = <0x52>;

allwinner,pins = "PE7", "PE8";

allwinner,function = "uart2";

allwinner,pname = "uart1_tx", "uart1_rx";

allwinner,muxsel = <0x3>;

allwinner,pull = <0x1>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

spi0@0 {

linux,phandle = <0x53>;

phandle = <0x53>;

allwinner,pins = "PC1";

allwinner,function = "spi0";

allwinner,pname = "spi0_cs0";

allwinner,muxsel = <0x2>;

allwinner,pull = <0x1>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

spi0@1 {

linux,phandle = <0x54>;

phandle = <0x54>;

allwinner,pins = "PC0", "PC3", "PC2";

allwinner,function = "spi0";

allwinner,pname = "spi0_sclk", "spi0_mosi", "spi0_miso";

allwinner,muxsel = <0x2>;

allwinner,pull = <0xffffffff>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

nand0@0 {

linux,phandle = <0x55>;

phandle = <0x55>;

allwinner,pins = "PC0", "PC1", "PC2", "PC4", "PC6", "PC7", "PC8", "PC9", "PC10", "PC11", "PC12", "PC13", "PC14";

allwinner,function = "nand0";

allwinner,pname = "nand0_we", "nand0_ale", "nand0_cle", "nand0_nre", "nand0_d0", "nand0_d1", "nand0_d2", "nand0_d3", "nand0_d4", "nand0_d5", "nand0_d6", "nand0_d7", "nand0_ndqs";

allwinner,muxsel = <0x2>;

allwinner,pull = <0x0>;

allwinner,drive = <0x1>;

allwinner,data = <0xffffffff>;

};

nand0@1 {

linux,phandle = <0x56>;

phandle = <0x56>;

allwinner,pins = "PC3", "PC5";

allwinner,function = "nand0";

allwinner,pname = "nand0_ce0", "nand0_rb0";

allwinner,muxsel = <0x2>;

allwinner,pull = <0x1>;

allwinner,drive = <0x1>;

allwinner,data = <0xffffffff>;

};

lcd0@0 {

linux,phandle = <0x57>;

phandle = <0x57>;

allwinner,pins = "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD8", "PD9", "PD10", "PD11", "PD13", "PD14", "PD15", "PD16", "PD17", "PD18", "PD19";

allwinner,function = "lcd0";

allwinner,pname = "lcdd3", "lcdd4", "lcdd5", "lcdd6", "lcdd7", "lcdd10", "lcdd11", "lcdd12", "lcdd13", "lcdd14", "lcdd15", "lcdd19", "lcdd20", "lcdd21", "lcdd22", "lcdd23", "lcdclk", "lcdde";

allwinner,muxsel = <0x2>;

allwinner,pull = <0x0>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

pwm0_para@0 {

linux,phandle = <0x58>;

phandle = <0x58>;

allwinner,pins = "PH0";

allwinner,function = "pwm0_para";

allwinner,pname = "pwm_positive";

allwinner,muxsel = <0x2>;

allwinner,pull = <0x0>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

pwm1_para@0 {

linux,phandle = <0x59>;

phandle = <0x59>;

allwinner,pins = "PH1";

allwinner,function = "pwm1_para";

allwinner,pname = "pwm_positive";

allwinner,muxsel = <0x2>;

allwinner,pull = <0x0>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

vip0@0 {

linux,phandle = <0x5a>;

phandle = <0x5a>;

allwinner,pins = "PE0", "PE2", "PE3", "PE4", "PE5", "PE6", "PE7", "PE8", "PE9", "PE10", "PE11", "PE12", "PE13";

allwinner,function = "vip0";

allwinner,pname = "vip0_csi_pck", "vip0_csi_hsync", "vip0_csi_vsync", "vip0_csi_d0", "vip0_csi_d1", "vip0_csi_d2", "vip0_csi_d3", "vip0_csi_d4", "vip0_csi_d5", "vip0_csi_d6", "vip0_csi_d7", "vip_csi_sck", "vip_csi_sda";

allwinner,muxsel = <0x2>;

allwinner,pull = <0xffffffff>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

vip0@1 {

linux,phandle = <0x5b>;

phandle = <0x5b>;

allwinner,pins = "PE1";

allwinner,function = "vip0";

allwinner,pname = "vip0_csi_mck";

allwinner,muxsel = <0x2>;

allwinner,pull = <0x0>;

allwinner,drive = <0x1>;

allwinner,data = <0x0>;

};

sdc0@0 {

linux,phandle = <0x5c>;

phandle = <0x5c>;

allwinner,pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5";

allwinner,function = "sdc0";

allwinner,pname = "sdc0_d1", "sdc0_d0", "sdc0_clk", "sdc0_cmd", "sdc0_d3", "sdc0_d2";

allwinner,muxsel = <0x2>;

allwinner,pull = <0x1>;

allwinner,drive = <0x2>;

allwinner,data = <0xffffffff>;

};

sdc1@0 {

linux,phandle = <0x5d>;

phandle = <0x5d>;

allwinner,pins = "PC0", "PC1", "PC2";

allwinner,function = "sdc1";

allwinner,pname = "sdc1_clk", "sdc1_cmd", "sdc1_d0";

allwinner,muxsel = <0x3>;

allwinner,pull = <0x1>;

allwinner,drive = <0x2>;

allwinner,data = <0xffffffff>;

};

Vdevice@0 {

linux,phandle = <0x5e>;

phandle = <0x5e>;

allwinner,pins = "PB1", "PB2";

allwinner,function = "Vdevice";

allwinner,pname = "Vdevice_0", "Vdevice_1";

allwinner,muxsel = <0x4>;

allwinner,pull = <0x1>;

allwinner,drive = <0x2>;

allwinner,data = <0xffffffff>;

};

};

dma-controller@01c02000 {

compatible = "allwinner,suniv-dma";

reg = <0x0 0x1c02000 0x0 0x1000>;

interrupts = <0x12>;

clocks = <0x5>;

#dma-cells = <0x2>;

linux,phandle = <0x22>;

phandle = <0x22>;

};

timer@1c20c00 {

compatible = "allwinner,sunxi-timer";

device_type = "timer";

reg = <0x0 0x1c20c00 0x0 0x90>;

interrupts = <0xd>;

clock-frequency = <0x16e3600>;

timer-prescale = <0x10>;

};

ve@01c0e000 {

compatible = "allwinner,sunxi-cedar-ve";

reg = <0x0 0x1c0e000 0x0 0x1000 0x0 0x1c00000 0x0 0x3000 0x0 0x1c20000 0x0 0x800>;

interrupts = <0x22>;

clocks = <0x6 0x7>;

};

uart@01c25000 {

compatible = "allwinner,suniv-uart";

device_type = "uart0";

reg = <0x0 0x1c25000 0x0 0x400>;

interrupts = <0x1>;

clocks = <0x8>;

pinctrl-names = "default", "sleep";

pinctrl-1 = <0xa>;

uart0_port = <0x0>;

uart0_type = <0x2>;

status = "disabled";

pinctrl-0 = <0x50>;

};

uart@01c25400 {

compatible = "allwinner,suniv-uart";

device_type = "uart1";

reg = <0x0 0x1c25400 0x0 0x400>;

interrupts = <0x2>;

clocks = <0xb>;

pinctrl-names = "default", "sleep";

pinctrl-1 = <0xd>;

uart1_port = <0x1>;

uart1_type = <0x2>;

status = "disabled";

pinctrl-0 = <0x51>;

};

uart@01c25800 {

compatible = "allwinner,suniv-uart";

device_type = "uart2";

reg = <0x0 0x1c25800 0x0 0x400>;

interrupts = <0x3>;

clocks = <0xe>;

pinctrl-names = "default", "sleep";

pinctrl-1 = <0x10>;

uart2_port = <0x2>;

uart2_type = <0x4>;

status = "disabled";

uart1_used = <0x1>;

uart1_port = <0x2>;

uart1_type = <0x2>;

pinctrl-0 = <0x52>;

};

cir {

compatible = "allwinner,s_cir";

reg = <0x0 0x1c22c00 0x0 0x400>;

interrupts = <0x6>;

clocks = <0x11 0x12>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x13>;

pinctrl-1 = <0x14>;

supply = "vcc-pl";

ir_power_key_code = <0x0>;

ir_addr_code = <0x0>;

status = "okay";

};

twi@0x01c27000 {

#address-cells = <0x1>;

#size-cells = <0x0>;

compatible = "allwinner,suniv-twi";

device_type = "twi0";

reg = <0x0 0x1c27000 0x0 0x400>;

interrupts = <0x7>;

clocks = <0x15>;

clock-frequency = <0x186a0>;

pinctrl-names = "default", "sleep";

pinctrl-1 = <0x17>;

status = "disabled";

pinctrl-0 = <0x4d>;

rtc@0x51 {

compatible = "nxp,pcf8563";

i2c-max-frequency = <0x186a0>;

reg = <0x51>;

};

io_expand@0x20 {

compatible = "ti,pcf8574a";

i2c-max-frequency = <0x186a0>;

reg = <0x20>;

};

sensor_ov5640@0x78 {

compatible = "allwinner,sensor_ov5640";

i2c-max-frequency = <0x186a0>;

reg = <0x78>;

status = "okay";

};

};

twi@0x01c27400 {

#address-cells = <0x1>;

#size-cells = <0x0>;

compatible = "allwinner,suniv-twi";

device_type = "twi1";

reg = <0x0 0x1c27400 0x0 0x400>;

interrupts = <0x8>;

clocks = <0x18>;

clock-frequency = <0x30d40>;

pinctrl-names = "default", "sleep";

pinctrl-1 = <0x1a>;

status = "disabled";

pinctrl-0 = <0x4e>;

};

twi@0x01c27800 {

#address-cells = <0x1>;

#size-cells = <0x0>;

compatible = "allwinner,suniv-twi";

device_type = "twi2";

reg = <0x0 0x1c27800 0x0 0x400>;

interrupts = <0x9>;

clocks = <0x1b>;

clock-frequency = <0x30d40>;

pinctrl-names = "default", "sleep";

pinctrl-1 = <0x1d>;

status = "okay";

pinctrl-0 = <0x4f>;

};

spi@01c05000 {

#address-cells = <0x1>;

#size-cells = <0x0>;

compatible = "allwinner,sun8i-spi";

device_type = "spi0";

reg = <0x0 0x1c05000 0x0 0x1000>;

interrupts = <0xa>;

clocks = <0x4 0x1e>;

clock-frequency = <0x5f5e100>;

pinctrl-names = "default", "sleep";

pinctrl-1 = <0x21>;

spi0_cs_number = <0x1>;

spi0_cs_bitmap = <0x1>;

dmas = <0x22 0x0 0x4 0x22 0x0 0x4>;

dma-names = "rx", "tx";

status = "okay";

pinctrl-0 = <0x53 0x54>;

nor_flash@0 {

#address-cells = <0x1>;

#size-cells = <0x1>;

compatible = "st,m25p64";

spi-max-frequency = <0x989680>;

reg = <0x0>;

};

};

spi@01c06000 {

#address-cells = <0x1>;

#size-cells = <0x0>;

compatible = "allwinner,sun8i-spi";

device_type = "spi1";

reg = <0x0 0x1c06000 0x0 0x1000>;

interrupts = <0xb>;

clocks = <0x4 0x23>;

clock-frequency = <0x5f5e100>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x24 0x25>;

pinctrl-1 = <0x26>;

spi1_cs_number = <0x1>;

spi1_cs_bitmap = <0x1>;

status = "disabled";

};

sdmmc@01c0f000 {

compatible = "allwinner,sunivw1p1-sdmmc0";

device_type = "sdc0";

reg = <0x0 0x1c0f000 0x0 0x1000>;

interrupts = <0x17>;

clocks = <0x11 0x4 0x27 0x28 0x29>;

clock-names = "osc24m", "pll_periph", "mmc", "ahb", "rst";

pinctrl-names = "default", "sleep";

pinctrl-1 = <0x2b>;

max-frequency = <0x2faf080>;

bus-width = <0x4>;

cap-sdio-irq;

keep-power-in-suspend;

ignore-pm-notify;

status = "okay";

sdc0_detmode = <0x4>;

sdc0_buswidth = <0x4>;

pinctrl-0 = <0x5c>;

sdc0_det = <0x38 0x0 0x1 0x0 0x1 0x2 0xffffffff>;

sdc0_use_wp = <0x0>;

sdc0_wp;

sdc0_isio = <0x0>;

sdc0_regulator = "none";

};

sdmmc@01c10000 {

compatible = "allwinner,sunivw1p1-sdmmc1";

device_type = "sdc1";

reg = <0x0 0x1c10000 0x0 0x1000>;

interrupts = <0x18>;

clocks = <0x11 0x4 0x2c 0x2d 0x2e>;

clock-names = "osc24m", "pll_periph", "mmc", "ahb", "rst";

pinctrl-names = "default", "sleep";

pinctrl-1 = <0x30>;

max-frequency = <0x2faf080>;

bus-width = <0x1>;

cap-sdio-irq;

keep-power-in-suspend;

ignore-pm-notify;

sunxi-dly-52M-ddr4 = <0x1 0x0 0x0 0x0 0x2>;

sunxi-dly-104M = <0x1 0x0 0x0 0x0 0x1>;

sunxi-dly-208M = <0x1 0x0 0x0 0x0 0x1>;

status = "disabled";

sdc1_detmode = <0x4>;

sdc1_buswidth = <0x1>;

pinctrl-0 = <0x5d>;

sdc1_det;

sdc1_use_wp = <0x0>;

sdc1_wp;

sdc1_isio = <0x1>;

sdc1_regulator = "none";

};

disp@0x01e00000 {

compatible = "allwinner,suniv-disp";

reg = <0x0 0x1e00000 0x0 0x20000 0x0 0x1e60000 0x0 0x10000 0x0 0x1e70000 0x0 0x10000 0x0 0x1c0c000 0x0 0x1000>;

interrupts = <0x1e 0x1f 0x21 0x1d>;

clocks = <0x31 0x32 0x33 0x34>;

status = "okay";

};

lcd0@01c0c000 {

compatible = "allwinner,sunxi-lcd0";

pinctrl-names = "active", "sleep";

status = "okay";

device_type = "lcd0";

lcd_used = <0x0>;

lcd_driver_name = "default_lcd";

lcd_if = <0x0>;

lcd_x = <0x320>;

lcd_y = <0x1e0>;

lcd_width = <0x96>;

lcd_height = <0x5e>;

lcd_dclk_freq = <0x21>;

lcd_pwm_used = <0x0>;

lcd_pwm_ch = <0x0>;

lcd_pwm_freq = <0x2710>;

lcd_pwm_pol = <0x0>;

lcd_hbp = <0x2e>;

lcd_ht = <0x41f>;

lcd_hspw = <0x0>;

lcd_vbp = <0x17>;

lcd_vt = <0x20d>;

lcd_vspw = <0x0>;

lcd_hv_if = <0x0>;

lcd_hv_smode = <0x0>;

lcd_hv_s888_if = <0x0>;

lcd_hv_syuv_if = <0x0>;

lcd_hv_vspw = <0x0>;

lcd_hv_hspw = <0x0>;

lcd_lvds_if = <0x0>;

lcd_lvds_colordepth = <0x1>;

lcd_lvds_mode = <0x0>;

lcd_lvds_ch = <0x0>;

lcd_lvds_bitwidth = <0x0>;

lcd_lvds_io_cross = <0x0>;

lcd_cpu_if = <0x0>;

lcd_frm = <0x0>;

lcd_io_phase = <0x0>;

lcd_gamma_en = <0x0>;

lcd_bright_curve_en = <0x0>;

lcd_cmap_en = <0x0>;

deu_mode = <0x0>;

lcdgamma4iep = <0x16>;

lcd_io_cfg0 = <0x4000000>;

smart_color = <0x5a>;

lcd_bl_en_used = <0x1>;

lcd_bl_en = <0x38 0x4 0xc 0x1 0x0 0xffffffff 0x1>;

lcd_power = <0x38 0x0 0x0 0x1 0x0 0xffffffff 0x1>;

pinctrl-0 = <0x57>;

};

csi_res@0x01cb0000 {

compatible = "allwinner,sunxi-csi";

reg = <0x0 0x1cb0000 0x0 0x1000>;

clocks = <0x35 0x3 0x11>;

clocks-index = <0x0 0x1 0x2>;

status = "okay";

};

vfe@0 {

device_type = "csi0";

compatible = "allwinner,sunxi-vfe";

interrupts = <0x20>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x36>;

pinctrl-1 = <0x37>;

csi_sel = <0x0>;

csi0_sensor_list = <0x0>;

csi0_mck = <0x38 0x4 0xb 0x2 0x0 0x1 0x0>;

status = "disable";

dev@1 {

compatible = "allwinner,sensor_ov5640";

csi0_dev0_mname = "ov5640";

csi0_dev0_twi_addr = <0x78>;

csi0_dev0_pos = "rear";

csi0_dev0_isp_used = <0x0>;

csi0_dev0_fmt = <0x0>;

csi0_dev0_stby_mode = <0x0>;

csi0_dev0_vflip = <0x0>;

csi0_dev0_hflip = <0x0>;

csi0_dev0_iovdd = <0x0>;

csi0_dev0_iovdd_vol = <0x0>;

csi0_dev0_avdd = <0x0>;

csi0_dev0_avdd_vol = <0x0>;

csi0_dev0_dvdd = <0x0>;

csi0_dev0_dvdd_vol = <0x0>;

csi0_dev0_afvdd = <0x0>;

csi0_dev0_afvdd_vol = <0x0>;

csi0_dev0_power_en;

csi0_dev0_flash_en;

csi0_dev0_flash_mode;

csi0_dev0_af_pwdn;

csi0_dev0_act_used = <0x0>;

csi0_dev0_act_name = <0x0>;

csi0_dev0_act_slave = <0x0>;

status = "disable";

};

};

usbc0@0 {

device_type = "usbc0";

compatible = "allwinner,sun50i-otg-manager";

usb_port_type = <0x1>;

usb_detect_type = <0x1>;

usb_det_vbus_gpio = <0x38 0x0 0x2 0x0 0x1 0x1 0x1>;

usb_host_init_state = <0x0>;

usb_regulator_io = "nocare";

usb_wakeup_suspend = <0x0>;

usb_luns = <0x3>;

usb_serial_unique = <0x0>;

usb_serial_number = "20080411";

rndis_wceis = <0x1>;

status = "okay";

};

udc-controller@0x01c13000 {

compatible = "allwinner,sun50i-udc";

reg = <0x0 0x1c13000 0x0 0x1000 0x0 0x1c00000 0x0 0x100>;

interrupts = <0x1a>;

clocks = <0x39 0x3a>;

status = "okay";

};

otghci0-controller@0x01c13000 {

compatible = "allwinner,sunxi-otghci";

reg = <0x0 0x1c13000 0x0 0x1000 0x0 0x1c00000 0x0 0x100>;

interrupts = <0x1a>;

clocks = <0x39 0x3a>;

hci_ctrl_no = <0x0>;

status = "okay";

};

daudio@0x01c22000 {

compatible = "allwinner,sunxi-daudio";

reg = <0x0 0x1c22000 0x0 0x3c>;

clocks = <0x2 0x3b>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x3c 0x3d>;

pinctrl-1 = <0x3e>;

word_select_size = <0x20>;

pcm_sync_period = <0x10>;

pcm_lsb_first = <0x0>;

slot_width_select = <0x8>;

pcm_sync_type = <0x0>;

pcm_start_slot = <0x4>;

tx_data_mode = <0x0>;

rx_data_mode = <0x0>;

tdm_config = <0x1>;

tdm_num = <0x0>;

dmas = <0x22 0x0 0xe 0x22 0x0 0xe>;

dma-names = "rx-tx", "rx-tx";

status = "okay";

linux,phandle = <0x46>;

phandle = <0x46>;

};

spdif-controller@0x01c21400 {

compatible = "allwinner,sunxi-spdif";

reg = <0x0 0x1c21400 0x0 0x38>;

clocks = <0x2 0x3f>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x40>;

pinctrl-1 = <0x41>;

dmas = <0x22 0x0 0x1 0x22 0x0 0x1>;

status = "disabled";

linux,phandle = <0x45>;

phandle = <0x45>;

};

codec@0x01c23c00 {

compatible = "allwinner,sunxi-internal-codec";

reg = <0x0 0x1c23c00 0x0 0x9c>;

clocks = <0x2 0x42>;

headphonevol = <0x3b>;

spkervol = <0x1b>;

maingain = <0x4>;

hp_dirused = <0x0>;

pa_sleep_time = <0x15e>;

status = "okay";

linux,phandle = <0x44>;

phandle = <0x44>;

};

cpudai0-controller@0x01c23c00 {

compatible = "allwinner,sunxi-internal-cpudai";

reg = <0x0 0x1c23c00 0x0 0x9c>;

clocks = <0x42>;

dmas = <0x22 0x0 0xc 0x22 0x0 0xc>;

dma-names = "rx-tx", "rx-tx";

status = "okay";

linux,phandle = <0x43>;

phandle = <0x43>;

};

sound@0 {

compatible = "allwinner,sunxi-codec-machine";

sunxi,cpudai-controller = <0x43>;

sunxi,audio-codec = <0x44>;

hp_detect_case = <0x0>;

status = "okay";

};

sound@1 {

compatible = "allwinner,sunxi-spdif-machine";

sunxi,spdif-controller = <0x45>;

status = "okay";

};

sound@2 {

device_type = "sndi2scodec_conf";

compatible = "allwinner,sunxi-codec-machine-i2s";

sunxi,cpudai-controller-i2s = <0x46>;

sta33x_pwrdn_gpio = <0x38 0x4 0x7 0x0 0x1 0x1 0x1>;

sta33x_reset_gpio = <0x38 0x4 0x8 0x0 0x1 0x1 0x1>;

status = "okay";

};

wifi {

device_type = "wifi_conf";

interrupts = <0x26>;

power_en;

reset_pin = <0x38 0x3 0x10 0x0 0x1 0x1 0x1>;

irq_pin = <0x38 0x3 0xd 0x0 0x6 0x1 0x1>;

status = "okay";

};

power {

device_type = "power_ctrl";

usb_drvbus_down = <0x38 0x3 0xb 0x0 0x1 0x1 0x1>;

power_on = <0x38 0x3 0xf 0x0 0x1 0x1 0x1>;

status = "okay";

};

gpio_keys {

compatible = "gpio-keys";

#address-cells = <0x1>;

#size-cells = <0x0>;

autorepeat;

button@21 {

label = "GPIO Key Power";

linux,code = <0x6c>;

gpios = <0x38 0x3 0xe 0x0 0x6 0x1 0x1>;

status = "okay";

};

};

keyboard {

compatible = "allwinner,keyboard_2000mv";

reg = <0x0 0x1c23400 0x0 0x400>;

interrupts = <0x16>;

status = "okay";

key_cnt = <0x6>;

key1 = <0xf8 0x73>;

key2 = <0x193 0x72>;

key3 = <0x24d 0x8b>;

key4 = <0x307 0x1c>;

key5 = <0x3c1 0x66>;

key6 = <0x4b9 0x67>;

};

wirelesskey@0 {

compatible = "allwinner,wireless-key";

gpio-key = <0x38 0x4 0x3 0x0 0x6 0x1 0x1>;

debounce = <0x0>;

status = "disabled";

};

product {

device_type = "product";

version = "100";

machine = "evb";

};

platform {

device_type = "platform";

eraseflag = <0x0>;

};

target {

device_type = "target";

boot_clock = <0x198>;

storage_type = <0x3>;

burn_key = <0x1>;

};

power_sply {

device_type = "power_sply";

dcdc1_vol = <0xbb8>;

dcdc2_vol = <0x4b0>;

dcdc3_vol = <0x4b0>;

dcdc4_vol = <0x4b0>;

dcdc5_vol = <0x5dc>;

aldo2_vol = <0x708>;

aldo3_vol = <0xbb8>;

};

card_boot {

device_type = "card_boot";

logical_start = <0xa000>;

sprite_gpio0;

};

pm_para {

device_type = "pm_para";

standby_mode = <0x1>;

};

card0_boot_para {

device_type = "card0_boot_para";

card_ctrl = <0x0>;

card_high_speed = <0x1>;

card_line = <0x4>;

pinctrl-0 = <0x47>;

};

card2_boot_para {

device_type = "card2_boot_para";

card_ctrl = <0x2>;

card_high_speed = <0x1>;

card_line = <0x8>;

pinctrl-0 = <0x48>;

};

twi_para {

device_type = "twi_para";

twi_port = <0x0>;

pinctrl-0 = <0x49>;

};

uart_para {

device_type = "uart_para";

uart_debug_port = <0x2>;

pinctrl-0 = <0x4a>;

};

force_uart_para {

device_type = "force_uart_para";

force_uart__port = <0x2>;

pinctrl-0 = <0x4b>;

};

jtag_para {

device_type = "jtag_para";

jtag_enable = <0x0>;

pinctrl-0 = <0x4c>;

};

dram {

device_type = "dram";

dram_clk = <0x1e0>;

dram_type = <0x3>;

dram_zq = <0x77bb>;

dram_odt_en = <0x1>;

dram_para1 = <0x4319f4>;

dram_para2 = <0x5>;

dram_mr0 = <0x620>;

dram_mr1 = <0x0>;

dram_mr2 = <0x8>;

dram_mr3 = <0x0>;

dram_tpr0 = <0x6141b10>;

dram_tpr1 = <0x40416>;

dram_tpr2 = <0x3030306>;

dram_tpr3 = <0x2006>;

dram_tpr4 = <0x5040405>;

dram_tpr5 = <0x5050302>;

dram_tpr6 = <0x90006644>;

dram_tpr7 = <0x42c21590>;

dram_tpr8 = <0xd05612c0>;

dram_tpr9 = <0x83def>;

dram_tpr10 = <0x18082356>;

dram_tpr11 = <0x32034156>;

dram_tpr12 = <0x0>;

dram_tpr13 = <0x0>;

};

rtp_para {

device_type = "rtp_para";

rtp_used = <0x0>;

rtp_screen_size = <0x5>;

rtp_regidity_level = <0x5>;

rtp_press_threshold_enable = <0x0>;

rtp_press_threshold = <0x1f40>;

rtp_sensitive_level = <0xf>;

rtp_exchange_x_y_flag = <0x0>;

};

ctp_para {

device_type = "ctp_para";

ctp_used = <0x0>;

ctp_twi_id = <0x1>;

ctp_twi_addr = <0x5d>;

ctp_screen_max_x = <0x500>;

ctp_screen_max_y = <0x320>;

ctp_revert_x_flag = <0x1>;

ctp_revert_y_flag = <0x1>;

ctp_exchange_x_y_flag = <0x1>;

ctp_int_port = <0x38 0x0 0x3 0x6 0xffffffff 0xffffffff 0xffffffff>;

ctp_wakeup = <0x38 0x0 0x2 0x1 0xffffffff 0xffffffff 0x1>;

};

tkey_para {

device_type = "tkey_para";

tkey_used = <0x0>;

tkey_twi_id;

tkey_twi_addr;

tkey_int;

};

motor_para {

device_type = "motor_para";

motor_used = <0x0>;

};

nand0 {

device_type = "nand0";

nand0_support_2ch = <0x0>;

status = "disabled";

pinctrl-0 = <0x55 0x56>;

nand0_regulator1 = "vcc-nand";

nand0_regulator2 = "none";

nand0_cache_level = <0x55aaaa55>;

nand0_flush_cache_num = <0x55aaaa55>;

nand0_capacity_level = <0x55aaaa55>;

nand0_id_number_ctl = <0x55aaaa55>;

nand0_print_level = <0x55aaaa55>;

nand0_p0 = <0x55aaaa55>;

nand0_p1 = <0x55aaaa55>;

nand0_p2 = <0x55aaaa55>;

nand0_p3 = <0x55aaaa55>;

};

disp_init {

device_type = "disp_init";

disp_init_enable = <0x0>;

disp_mode = <0x0>;

screen0_output_type = <0x1>;

screen0_output_mode = <0x4>;

screen1_output_type = <0x1>;

screen1_output_mode = <0x4>;

fb0_framebuffer_num = <0x2>;

fb0_pixel_sequence = <0x0>;

fb0_scaler_mode_enable = <0x0>;

fb0_format = <0x5>;

fb0_width = <0x320>;

fb0_height = <0x1e0>;

fb1_framebuffer_num = <0x0>;

fb1_pixel_sequence = <0x0>;

fb1_scaler_mode_enable = <0x0>;

fb1_format = <0x0>;

fb1_width = <0x0>;

fb1_height = <0x0>;

lcd0_backlight = <0x32>;

lcd1_backlight = <0x32>;

lcd0_bright = <0x32>;

lcd0_contrast = <0x32>;

lcd0_saturation = <0x39>;

lcd0_hue = <0x32>;

lcd1_bright = <0x32>;

lcd1_contrast = <0x32>;

lcd1_saturation = <0x39>;

lcd1_hue = <0x32>;

};

pwm0_para {

device_type = "pwm0_para";

pwm_used = <0x0>;

pinctrl-0 = <0x58>;

};

pwm1_para {

device_type = "pwm1_para";

pwm_used = <0x0>;

pinctrl-0 = <0x59>;

};

vip0 {

device_type = "vip0";

status = "disabled";

pinctrl-0 = <0x5a 0x5b>;

vip0_mname = "ov5640";

vip0_twi_addr = <0x78>;

vip0_isp_used = <0x1>;

vip0_fmt = <0x0>;

vip0_stby_mode = <0x0>;

vip0_vflip = <0x0>;

vip0_hflip = <0x0>;

vip0_iovdd = "axp22_eldo3";

vip0_iovdd_vol = <0x2ab980>;

vip0_avdd = "axp22_dldo4";

vip0_avdd_vol = <0x2ab980>;

vip0_dvdd = "axp22_eldo2";

vip0_dvdd_vol = <0x16e360>;

vip0_afvdd;

vip0_afvdd_vol = <0x2ab980>;

vip0_power_en;

vip0_reset = <0x38 0x4 0x10 0x1 0x0 0x1 0x0>;

vip0_pwdn = <0x38 0x4 0x11 0x1 0x0 0x1 0x0>;

vip0_flash_en;

vip0_flash_mode;

vip0_af_pwdn;

};

tvout_para {

device_type = "tvout_para";

tvout_used;

tvout_channel_num;

tv_en;

};

tvin_para {

device_type = "tvin_para";

tvin_used;

tvin_channel_num;

};

di {

device_type = "di";

status = "disabled";

};

smc {

device_type = "smc";

smc_used;

smc_rst;

smc_vppen;

smc_vppp;

smc_det;

smc_vccen;

smc_sck;

smc_sda;

};

gsensor_para {

device_type = "gsensor_para";

gsensor_used = <0x0>;

gsensor_twi_id = <0x2>;

gsensor_twi_addr = <0x18>;

gsensor_int1 = <0x38 0x0 0x9 0x6 0x1 0xffffffff 0xffffffff>;

gsensor_int2;

};

gps_para {

device_type = "gps_para";

};

wifi_para {

device_type = "wifi_para";

wifi_used = <0x0>;

wifi_sdc_id = <0x1>;

wifi_usbc_id = <0x1>;

wifi_usbc_type = <0x1>;

wifi_mod_sel = <0x3>;

wifi_power = "axp22_aldo1";

};

gy_para {

device_type = "gy_para";

gy_used = <0x0>;

gy_twi_id = <0x2>;

gy_twi_addr = <0x6a>;

gy_int1 = <0x38 0x0 0xa 0x6 0x1 0xffffffff 0xffffffff>;

gy_int2;

};

ls_para {

device_type = "ls_para";

ls_used = <0x0>;

ls_twi_id = <0x2>;

ls_twi_addr = <0x23>;

ls_int = <0x38 0x0 0xc 0x6 0x1 0xffffffff 0xffffffff>;

};

compass_para {

device_type = "compass_para";

compass_used = <0x0>;

compass_twi_id = <0x2>;

compass_twi_addr = <0xd>;

compass_int = <0x38 0x0 0xb 0x6 0x1 0xffffffff 0xffffffff>;

};

bt_para {

device_type = "bt_para";

bt_used;

bt_uart_id;

bt_wakeup;

bt_gpio;

bt_rst;

};

audiospdif {

device_type = "audiospdif";

status = "disabled";

};

spdif_machine {

device_type = "spdif_machine";

status = "disabled";

};

audiohdmi {

device_type = "audiohdmi";

status = "disabled";

};

hdmi_machine {

device_type = "hdmi_machine";

status = "disabled";

};

pmu0 {

device_type = "pmu0";

status = "disabled";

pmu_id = <0x6>;

pmu_twi_addr = <0x34>;

pmu_twi_id = <0x1>;

pmu_irq_id = <0x0>;

pmu_chg_ic_temp = <0x0>;

pmu_battery_rdc = <0x64>;

pmu_battery_cap = <0x0>;

pmu_runtime_chgcur = <0x1c2>;

pmu_suspend_chgcur = <0x5dc>;

pmu_shutdown_chgcur = <0x5dc>;

pmu_init_chgvol = <0x1068>;

pmu_ac_vol = <0xfa0>;

pmu_ac_cur = <0x0>;

pmu_usbpc_vol = <0x1130>;

pmu_usbpc_cur = <0x1f4>;

pmu_battery_warning_level1 = <0xf>;

pmu_battery_warning_level2 = <0x0>;

pmu_chgled_func = <0x0>;

pmu_chgled_type = <0x0>;

pmu_bat_para1 = <0x0>;

pmu_bat_para2 = <0x0>;

pmu_bat_para3 = <0x0>;

pmu_bat_para4 = <0x0>;

pmu_bat_para5 = <0x0>;

pmu_bat_para6 = <0x0>;

pmu_bat_para7 = <0x0>;

pmu_bat_para8 = <0x0>;

pmu_bat_para9 = <0x5>;

pmu_bat_para10 = <0x8>;

pmu_bat_para11 = <0x9>;

pmu_bat_para12 = <0xa>;

pmu_bat_para13 = <0xd>;

pmu_bat_para14 = <0x10>;

pmu_bat_para15 = <0x14>;

pmu_bat_para16 = <0x21>;

pmu_bat_para17 = <0x29>;

pmu_bat_para18 = <0x2e>;

pmu_bat_para19 = <0x32>;

pmu_bat_para20 = <0x35>;

pmu_bat_para21 = <0x39>;

pmu_bat_para22 = <0x3d>;

pmu_bat_para23 = <0x43>;

pmu_bat_para24 = <0x49>;

pmu_bat_para25 = <0x4e>;

pmu_bat_para26 = <0x54>;

pmu_bat_para27 = <0x58>;

pmu_bat_para28 = <0x5c>;

pmu_bat_para29 = <0x5d>;

pmu_bat_para30 = <0x5e>;

pmu_bat_para31 = <0x5f>;

pmu_bat_para32 = <0x64>;

pmu_bat_temp_enable = <0x0>;

pmu_bat_charge_ltf = <0x8d5>;

pmu_bat_charge_htf = <0x184>;

pmu_bat_shutdown_ltf = <0xc80>;

pmu_bat_shutdown_htf = <0xed>;

pmu_bat_temp_para1 = <0x1d2a>;

pmu_bat_temp_para2 = <0x1180>;

pmu_bat_temp_para3 = <0xdbe>;

pmu_bat_temp_para4 = <0xae2>;

pmu_bat_temp_para5 = <0x8af>;

pmu_bat_temp_para6 = <0x6fc>;

pmu_bat_temp_para7 = <0x5a8>;

pmu_bat_temp_para8 = <0x3c9>;

pmu_bat_temp_para9 = <0x298>;

pmu_bat_temp_para10 = <0x1d2>;

pmu_bat_temp_para11 = <0x189>;

pmu_bat_temp_para12 = <0x14d>;

pmu_bat_temp_para13 = <0x11b>;

pmu_bat_temp_para14 = <0xf2>;

pmu_bat_temp_para15 = <0xb3>;

pmu_bat_temp_para16 = <0x86>;

pmu_powkey_off_time = <0x1770>;

pmu_powkey_off_func = <0x0>;

pmu_powkey_off_en = <0x1>;

pmu_powkey_long_time = <0x5dc>;

pmu_powkey_on_time = <0x3e8>;

};

pmu0_regu {

device_type = "pmu0_regu";

regulator_count = <0x17>;

regulator1 = "axp28_rtc";

regulator2 = "axp28_aldo1";

regulator3 = "axp28_aldo2";

regulator4 = "axp28_aldo3";

regulator5 = "axp28_dldo1";

regulator6 = "axp28_dldo2";

regulator7 = "axp28_dldo3";

regulator8 = "axp28_dldo4";

regulator9 = "axp28_eldo1";

regulator0 = "axp28_eldo2";

regulator11 = "axp28_eldo3";

regulator12 = "axp28_fldo1";

regulator13 = "axp28_fldo2";

regulator14 = "axp28_dcdc1";

regulator15 = "axp28_dcdc2";

regulator16 = "axp28_dcdc3";

regulator17 = "axp28_dcdc4";

regulator18 = "axp28_dcdc5";

regulator19 = "axp28_dcdc6";

regulator20 = "axp28_dcdc7";

regulator21 = "axp28_gpio0ldo";

regulator22 = "axp28_gpio1ldo";

};

dvfs_table {

device_type = "dvfs_table";

max_freq = <0x47868c00>;

min_freq = <0x1c9c3800>;

LV_count = <0x8>;

LV1_freq = <0x5b8d8000>;

LV1_volt = <0x5dc>;

LV2_freq = <0x501bd000>;

LV2_volt = <0x5b4>;

LV3_freq = <0x47868c00>;

LV3_volt = <0x528>;

LV4_freq = <0x3c14dc00>;

LV4_volt = <0x4b0>;

LV5_freq = <0x30a32c00>;

LV5_volt = <0x44c>;

LV6_freq = <0x269fb200>;

LV6_volt = <0x410>;

LV7_freq = <0x0>;

LV7_volt = <0x410>;

LV8_freq = <0x0>;

LV8_volt = <0x410>;

};

Vdevice {

device_type = "Vdevice";

status = "disabled";

pinctrl-0 = <0x5e>;

};

};

aliases {

serial0 = "/soc/uart@01c25000";

serial1 = "/soc/uart@01c25400";

serial2 = "/soc/uart@01c25800";

twi0 = "/soc/twi@0x01c27000";

twi1 = "/soc/twi@0x01c27400";

twi2 = "/soc/twi@0x01c27800";

spi0 = "/soc/spi@01c05000";

spi1 = "/soc/spi@01c06000";

mmc0 = "/soc/sdmmc@01c0f000";

mmc1 = "/soc/sdmmc@01c10000";

global_timer0 = "/soc/timer@1c20c00";

csi_res0 = "/soc/csi_res@0x01cb0000";

vfe0 = "/soc/vfe@0";

disp = "/soc/disp@0x01e00000";

lcd0 = "/soc/lcd0@01c0c000";

};

chosen {

bootargs = "earlyprintk=sunxi-uart,0x01c25000 loglevel=8 initcall_debug=1 console=ttyS0 init=/init";

linux,initrd-start = <0x0 0x0>;

linux,initrd-end = <0x0 0x0>;

};

cpus {

#address-cells = <0x1>;

#size-cells = <0x0>;

cpu@0 {

device_type = "cpu";

compatible = "arm,arm926ejs";

reg = <0x0>;

};

};

sram_ctrl {

device_type = "sram_ctrl";

compatible = "allwinner,sram_ctrl";

reg = <0x0 0x1c00000 0x0 0x100>;

};

ion {

compatible = "allwinner,sunxi-ion";

system {

type = <0x0>;

};

system_contig {

type = <0x1>;

};

carveout {

type = <0x2>;

base = <0x81c00000>;

size = <0x400000>;

};

cma {

type = <0x4>;

};

};

memory@80000000 {

device_type = "memory";

reg = <0x0 0x80000000 0x0 0x2000000>;

};

interrupt-controller@01c20400 {

compatible = "allwinner,suniv-intc";

#interrupt-cells = <0x1>;

#address-cells = <0x0>;

device_type = "intc";

interrupt-controller;

reg = <0x0 0x1c20400 0x0 0x400>;

linux,phandle = <0x1>;

phandle = <0x1>;

};

watchdog@01c20ca0 {

compatible = "allwinner,sun8i-wdt";

reg = <0x0 0x1c20ca0 0x0 0x18>;

};

};最近编辑记录 Sam (2022-03-17 17:28:55)

离线

#8 2022-03-17 19:18:37 分享评论

- Sam

- 会员

- 注册时间: 2019-12-06

- 已发帖子: 55

- 积分: 50

Re: F1C100S/F1C200S主线uboot更改默认终端串口为uart1

修改了BSP linux-3.10/arch/arm/include/debug/sunxi.S 33行

#elif defined(CONFIG_DEBUG_SUNXI_UART2)

#ifdef CONFIG_ARCH_SUNIVW1

#define SUNXI_UART_DEBUG_PHYS_BASE 0x01c25800

#define SUNXI_UART_DEBUG_VIRT_BASE 0xf1c25800

#else

#define SUNXI_UART_DEBUG_PHYS_BASE 0x01c28800

#define SUNXI_UART_DEBUG_VIRT_BASE 0xf1c28800

#endif直接修改 .config文件

# CONFIG_DEBUG_SUNXI_UART0 is not set

# CONFIG_DEBUG_SUNXI_UART1 is not set

CONFIG_DEBUG_SUNXI_UART2=ybsp 根目录下 编译

./build.sh

编译后.config 自动重新回到以前的状态

CONFIG_DEBUG_SUNXI_UART0=y

# CONFIG_DEBUG_SUNXI_UART1 is not set求解???

离线

#9 2022-03-18 13:35:28 分享评论

- Sam

- 会员

- 注册时间: 2019-12-06

- 已发帖子: 55

- 积分: 50

Re: F1C100S/F1C200S主线uboot更改默认终端串口为uart1

@Sam UBOOT 下的dts 文件

// SPDX-License-Identifier: (GPL-2.0+ OR X11)

/*

* Copyright 2018 Icenowy Zheng <icenowy@aosc.io>

*/

/dts-v1/;

#include "suniv-f1c100s.dtsi"

#include <dt-bindings/gpio/gpio.h>

/ {

model = "Lichee Pi Nano";

compatible = "licheepi,licheepi-nano", "allwinner,suniv-f1c100s",

"allwinner,suniv";

aliases {

serial2 = &uart2;

spi0 = &spi0;

};

chosen {

stdout-path = "serial2:115200n8";

};

};

&otg_sram {

status = "okay";

};

&spi0 {

pinctrl-names = "default";

pinctrl-0 = <&spi0_pins_a>;

status = "okay";

flash@0 {

#address-cells = <1>;

#size-cells = <1>;

compatible = "winbond,w25q128", "jedec,spi-nor";

reg = <0>;

spi-max-frequency = <40000000>;

};

};

&uart2 {

pinctrl-names = "default";

pinctrl-0 = <&uart2_pins_e>;

status = "okay";

};

&usb_otg {

dr_mode = "otg";

status = "okay";

};

&usbphy {

usb0_id_det-gpio = <&pio 4 2 GPIO_ACTIVE_HIGH>; /* PE2 */

status = "okay";

};// SPDX-License-Identifier: (GPL-2.0+ OR X11)

/*

* Copyright 2018 Icenowy Zheng <icenowy@aosc.io>

*/

#include <dt-bindings/clock/suniv-ccu.h>

#include <dt-bindings/reset/suniv-ccu.h>

/ {

#address-cells = <1>;

#size-cells = <1>;

interrupt-parent = <&intc>;

clocks {

#address-cells = <1>;

#size-cells = <1>;

ranges;

osc24M: clk-24M {

#clock-cells = <0>;

compatible = "fixed-clock";

clock-frequency = <24000000>;

clock-output-names = "osc24M";

};

osc32k: clk-32k {

#clock-cells = <0>;

compatible = "fixed-clock";

clock-frequency = <32768>;

clock-output-names = "osc32k";

};

fake100M: clk-100M {

#clock-cells = <0>;

compatible = "fixed-clock";

clock-frequency = <100000000>;

clock-output-names = "fake-100M";

};

};

cpus {

#address-cells = <0>;

#size-cells = <0>;

cpu {

compatible = "arm,arm926ej-s";

device_type = "cpu";

};

};

soc {

compatible = "simple-bus";

#address-cells = <1>;

#size-cells = <1>;

ranges;

sram-controller@1c00000 {

compatible = "allwinner,sun4i-a10-sram-controller";

reg = <0x01c00000 0x30>;

#address-cells = <1>;

#size-cells = <1>;

ranges;

sram_d: sram@10000 {

compatible = "mmio-sram";

reg = <0x00010000 0x1000>;

#address-cells = <1>;

#size-cells = <1>;

ranges = <0 0x00010000 0x1000>;

otg_sram: sram-section@0 {

compatible = "allwinner,sun4i-a10-sram-d";

reg = <0x0000 0x1000>;

status = "disabled";

};

};

};

spi0: spi@1c05000 {

compatible = "allwinner,suniv-spi",

"allwinner,sun8i-h3-spi";

reg = <0x01c05000 0x1000>;

interrupts = <10>;

clocks = <&ccu CLK_BUS_SPI0>, <&ccu CLK_BUS_SPI0>;

clock-names = "ahb", "mod";

resets = <&ccu RST_BUS_SPI0>;

status = "disabled";

#address-cells = <1>;

#size-cells = <0>;

};

ccu: clock@1c20000 {

compatible = "allwinner,suniv-ccu";

reg = <0x01c20000 0x400>;

clocks = <&osc24M>, <&osc32k>;

clock-names = "hosc", "losc";

#clock-cells = <1>;

#reset-cells = <1>;

};

intc: interrupt-controller@1c20400 {

compatible = "allwinner,suniv-ic";

reg = <0x01c20400 0x400>;

interrupt-controller;

#interrupt-cells = <1>;

};

pio: pinctrl@1c20800 {

compatible = "allwinner,suniv-pinctrl";

reg = <0x01c20800 0x400>;

interrupts = <38>, <39>, <40>;

clocks = <&ccu CLK_BUS_PIO>, <&osc24M>, <&osc32k>;

clock-names = "apb", "hosc", "losc";

gpio-controller;

interrupt-controller;

#interrupt-cells = <3>;

#gpio-cells = <3>;

spi0_pins_a: spi0-pins-pc {

pins = "PC0", "PC1", "PC2", "PC3";

function = "spi0";

};

uart2_pins_e: uart-pins-pe {

pins = "PE7", "PE8";

function = "uart2";

};

};

timer@1c20c00 {

compatible = "allwinner,sun4i-a10-timer";

reg = <0x01c20c00 0x90>;

interrupts = <13>;

clocks = <&osc24M>;

};

wdt: watchdog@1c20ca0 {

compatible = "allwinner,sun6i-a31-wdt";

reg = <0x01c20ca0 0x20>;

};

uart0: serial@1c25000 {

compatible = "snps,dw-apb-uart";

reg = <0x01c25000 0x400>;

interrupts = <1>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_BUS_UART0>;

resets = <&ccu RST_BUS_UART0>;

status = "disabled";

};

uart1: serial@1c25400 {

compatible = "snps,dw-apb-uart";

reg = <0x01c25400 0x400>;

interrupts = <2>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_BUS_UART1>;

resets = <&ccu RST_BUS_UART1>;

status = "disabled";

};

uart2: serial@1c25800 {

compatible = "snps,dw-apb-uart";

reg = <0x01c25800 0x400>;

interrupts = <3>;

reg-shift = <2>;

reg-io-width = <4>;

clocks = <&ccu CLK_BUS_UART2>;

resets = <&ccu RST_BUS_UART2>;

status = "disabled";

};

usb_otg: usb@1c13000 {

compatible = "allwinner,suniv-musb";

reg = <0x01c13000 0x0400>;

clocks = <&ccu CLK_BUS_OTG>;

resets = <&ccu RST_BUS_OTG>;

interrupts = <26>;

interrupt-names = "mc";

phys = <&usbphy 0>;

phy-names = "usb";

extcon = <&usbphy 0>;

allwinner,sram = <&otg_sram 1>;

status = "disabled";

};

usbphy: phy@1c13400 {

compatible = "allwinner,suniv-usb-phy";

reg = <0x01c13400 0x10>;

reg-names = "phy_ctrl";

clocks = <&ccu CLK_USB_PHY0>;

clock-names = "usb0_phy";

resets = <&ccu RST_USB_PHY0>;

reset-names = "usb0_reset";

#phy-cells = <1>;

status = "disabled";

};

};

};.config 文件

#

# Automatically generated file; DO NOT EDIT.

# U-Boot 2018.01 Configuration

#

CONFIG_CREATE_ARCH_SYMLINK=y

# CONFIG_ARC is not set

CONFIG_ARM=y

# CONFIG_M68K is not set

# CONFIG_MICROBLAZE is not set

# CONFIG_MIPS is not set

# CONFIG_NDS32 is not set

# CONFIG_NIOS2 is not set

# CONFIG_PPC is not set

# CONFIG_SANDBOX is not set

# CONFIG_SH is not set

# CONFIG_X86 is not set

# CONFIG_XTENSA is not set

CONFIG_SYS_ARCH="arm"

CONFIG_SYS_CPU="arm926ejs"

CONFIG_SYS_SOC="sunxi"

CONFIG_SYS_BOARD="sunxi"

CONFIG_SYS_CONFIG_NAME="suniv"

#

# ARM architecture

#

CONFIG_ARM_ASM_UNIFIED=y

CONFIG_CPU_ARM926EJS=y

CONFIG_SYS_ARM_ARCH=5

CONFIG_SYS_CACHE_SHIFT_5=y

CONFIG_SYS_CACHELINE_SIZE=32

# CONFIG_SEMIHOSTING is not set

CONFIG_SYS_THUMB_BUILD=y

CONFIG_SPL_SYS_THUMB_BUILD=y

# CONFIG_SYS_L2CACHE_OFF is not set

# CONFIG_ENABLE_ARM_SOC_BOOT0_HOOK is not set

# CONFIG_ARM_CORTEX_CPU_IS_UP is not set

CONFIG_USE_ARCH_MEMCPY=y

CONFIG_SPL_USE_ARCH_MEMCPY=y

CONFIG_USE_ARCH_MEMSET=y

CONFIG_SPL_USE_ARCH_MEMSET=y

# CONFIG_ARM64_SUPPORT_AARCH32 is not set

# CONFIG_ARCH_AT91 is not set

# CONFIG_TARGET_EDB93XX is not set

# CONFIG_TARGET_ASPENITE is not set

# CONFIG_TARGET_GPLUGD is not set

# CONFIG_ARCH_DAVINCI is not set

# CONFIG_KIRKWOOD is not set

# CONFIG_ARCH_MVEBU is not set

# CONFIG_TARGET_DEVKIT3250 is not set

# CONFIG_TARGET_WORK_92105 is not set

# CONFIG_TARGET_APF27 is not set

# CONFIG_TARGET_APX4DEVKIT is not set

# CONFIG_TARGET_XFI3 is not set

# CONFIG_TARGET_M28EVK is not set

# CONFIG_TARGET_MX23EVK is not set

# CONFIG_TARGET_MX28EVK is not set

# CONFIG_TARGET_MX23_OLINUXINO is not set

# CONFIG_TARGET_BG0900 is not set

# CONFIG_TARGET_SANSA_FUZE_PLUS is not set

# CONFIG_TARGET_SC_SPS_1 is not set

# CONFIG_ORION5X is not set

# CONFIG_TARGET_SPEAR300 is not set

# CONFIG_TARGET_SPEAR310 is not set

# CONFIG_TARGET_SPEAR320 is not set

# CONFIG_TARGET_SPEAR600 is not set

# CONFIG_TARGET_STV0991 is not set

# CONFIG_TARGET_X600 is not set

# CONFIG_TARGET_IMX31_PHYCORE is not set

# CONFIG_TARGET_IMX31_PHYCORE_EET is not set

# CONFIG_TARGET_MX31ADS is not set

# CONFIG_TARGET_MX31PDK is not set

# CONFIG_TARGET_WOODBURN is not set

# CONFIG_TARGET_WOODBURN_SD is not set

# CONFIG_TARGET_FLEA3 is not set

# CONFIG_TARGET_MX35PDK is not set

# CONFIG_ARCH_BCM283X is not set

# CONFIG_TARGET_VEXPRESS_CA15_TC2 is not set

# CONFIG_TARGET_VEXPRESS_CA5X2 is not set

# CONFIG_TARGET_VEXPRESS_CA9X4 is not set

# CONFIG_TARGET_BCM23550_W1D is not set

# CONFIG_TARGET_BCM28155_AP is not set

# CONFIG_TARGET_BCMCYGNUS is not set

# CONFIG_TARGET_BCMNSP is not set

# CONFIG_TARGET_BCMNS2 is not set

# CONFIG_ARCH_EXYNOS is not set

# CONFIG_ARCH_S5PC1XX is not set

# CONFIG_ARCH_HIGHBANK is not set

# CONFIG_ARCH_INTEGRATOR is not set

# CONFIG_ARCH_KEYSTONE is not set

# CONFIG_ARCH_OMAP2PLUS is not set

# CONFIG_ARCH_MESON is not set

# CONFIG_ARCH_MX25 is not set

# CONFIG_ARCH_MX7ULP is not set

# CONFIG_ARCH_MX7 is not set

# CONFIG_ARCH_MX6 is not set

CONFIG_SPL_LDSCRIPT="arch/arm/cpu/arm926ejs/sunxi/u-boot-spl.lds"

# CONFIG_ARCH_MX5 is not set

# CONFIG_ARCH_QEMU is not set

# CONFIG_ARCH_RMOBILE is not set

# CONFIG_TARGET_S32V234EVB is not set

# CONFIG_ARCH_SNAPDRAGON is not set

# CONFIG_ARCH_SOCFPGA is not set

CONFIG_ARCH_SUNXI=y

# CONFIG_TARGET_TS4600 is not set

# CONFIG_ARCH_VF610 is not set

# CONFIG_ARCH_ZYNQ is not set

# CONFIG_ARCH_ZYNQMP is not set

# CONFIG_TEGRA is not set

# CONFIG_TARGET_VEXPRESS64_AEMV8A is not set

# CONFIG_TARGET_VEXPRESS64_BASE_FVP is not set

# CONFIG_TARGET_VEXPRESS64_BASE_FVP_DRAM is not set

# CONFIG_TARGET_VEXPRESS64_JUNO is not set

# CONFIG_TARGET_LS2080A_EMU is not set

# CONFIG_TARGET_LS2080A_SIMU is not set

# CONFIG_TARGET_LS1088AQDS is not set

# CONFIG_TARGET_LS2080AQDS is not set

# CONFIG_TARGET_LS2080ARDB is not set

# CONFIG_TARGET_LS2081ARDB is not set

# CONFIG_TARGET_HIKEY is not set

# CONFIG_TARGET_POPLAR is not set

# CONFIG_TARGET_LS1012AQDS is not set

# CONFIG_TARGET_LS1012ARDB is not set

# CONFIG_TARGET_LS1012AFRDM is not set

# CONFIG_TARGET_LS1088ARDB is not set

# CONFIG_TARGET_LS1021AQDS is not set

# CONFIG_TARGET_LS1021ATWR is not set

# CONFIG_TARGET_LS1021AIOT is not set

# CONFIG_TARGET_LS1043AQDS is not set

# CONFIG_TARGET_LS1043ARDB is not set

# CONFIG_TARGET_LS1046AQDS is not set

# CONFIG_TARGET_LS1046ARDB is not set

# CONFIG_TARGET_H2200 is not set

# CONFIG_TARGET_ZIPITZ2 is not set

# CONFIG_TARGET_COLIBRI_PXA270 is not set

# CONFIG_ARCH_UNIPHIER is not set

# CONFIG_STM32 is not set

# CONFIG_ARCH_STI is not set

# CONFIG_ARCH_ROCKCHIP is not set

# CONFIG_TARGET_THUNDERX_88XX is not set

# CONFIG_ARCH_ASPEED is not set

CONFIG_SPL_GPIO_SUPPORT=y

CONFIG_SPL_LIBCOMMON_SUPPORT=y

CONFIG_SPL_LIBGENERIC_SUPPORT=y

CONFIG_SYS_MALLOC_F_LEN=0x400

CONFIG_CONS_INDEX=2

CONFIG_SPL_MMC_SUPPORT=y

CONFIG_SPL_SERIAL_SUPPORT=y

# CONFIG_SPL_DRIVERS_MISC_SUPPORT is not set

CONFIG_ENV_SIZE=0x8000

CONFIG_ENV_OFFSET=0xf8000

CONFIG_SPL_LIBDISK_SUPPORT=y

# CONFIG_SPL_NAND_SUPPORT is not set

# CONFIG_SPL_SPI_FLASH_SUPPORT is not set

# CONFIG_SPL_SPI_SUPPORT is not set

# CONFIG_SPL_WATCHDOG_SUPPORT is not set

CONFIG_IDENT_STRING=" Allwinner Technology"

# CONFIG_SUNXI_HIGH_SRAM is not set

CONFIG_SUNXI_GEN_SUN6I=y

CONFIG_MACH_SUNIV=y

# CONFIG_MACH_SUN4I is not set

# CONFIG_MACH_SUN5I is not set

# CONFIG_MACH_SUN6I is not set

# CONFIG_MACH_SUN7I is not set

# CONFIG_MACH_SUN8I_A23 is not set

# CONFIG_MACH_SUN8I_A33 is not set

# CONFIG_MACH_SUN8I_A83T is not set

# CONFIG_MACH_SUN8I_H3 is not set

# CONFIG_MACH_SUN8I_R40 is not set

# CONFIG_MACH_SUN8I_V3S is not set

# CONFIG_MACH_SUN9I is not set

# CONFIG_MACH_SUN50I is not set

# CONFIG_MACH_SUN50I_H5 is not set

# CONFIG_RESERVE_ALLWINNER_BOOT0_HEADER is not set

CONFIG_DRAM_CLK=156

CONFIG_DRAM_ZQ=0

# CONFIG_DRAM_ODT_EN is not set

CONFIG_SYS_CLK_FREQ=408000000

# CONFIG_UART0_PORT_F is not set

# CONFIG_OLD_SUNXI_KERNEL_COMPAT is not set

CONFIG_MACPWR=""

CONFIG_MMC0_CD_PIN=""

CONFIG_MMC1_CD_PIN=""

CONFIG_MMC2_CD_PIN=""

CONFIG_MMC3_CD_PIN=""

CONFIG_MMC1_PINS=""

CONFIG_MMC2_PINS=""

CONFIG_MMC3_PINS=""

CONFIG_MMC_SUNXI_SLOT_EXTRA=-1

CONFIG_INITIAL_USB_SCAN_DELAY=0

CONFIG_USB0_VBUS_PIN=""

CONFIG_USB0_VBUS_DET=""

CONFIG_USB0_ID_DET=""

CONFIG_USB1_VBUS_PIN=""

CONFIG_USB2_VBUS_PIN=""

CONFIG_USB3_VBUS_PIN=""

# CONFIG_I2C0_ENABLE is not set

# CONFIG_I2C1_ENABLE is not set

# CONFIG_I2C2_ENABLE is not set

# CONFIG_R_I2C_ENABLE is not set

# CONFIG_AXP_GPIO is not set

# CONFIG_VIDEO_SUNXI is not set

# CONFIG_SUNXI_DE2 is not set

CONFIG_SATAPWR=""

CONFIG_GMAC_TX_DELAY=0

CONFIG_SPL_STACK_R_ADDR=0x81e00000

# CONFIG_SPL_FAT_SUPPORT is not set

# CONFIG_CMD_DEKBLOB is not set

# CONFIG_CMD_HDMIDETECT is not set

#

# ARM debug

#

# CONFIG_DEBUG_LL is not set

CONFIG_DEFAULT_DEVICE_TREE="suniv-f1c100s-licheepi-nano"

CONFIG_SMBIOS_PRODUCT_NAME="sunxi"

# CONFIG_DEBUG_UART is not set

# CONFIG_AHCI is not set

#

# General setup

#

CONFIG_LOCALVERSION=""

CONFIG_LOCALVERSION_AUTO=y

CONFIG_CC_OPTIMIZE_FOR_SIZE=y

CONFIG_DISTRO_DEFAULTS=y

CONFIG_SYS_MALLOC_F=y

CONFIG_SPL_SYS_MALLOC_F_LEN=0x400

CONFIG_TPL_SYS_MALLOC_F_LEN=0x400

CONFIG_EXPERT=y

CONFIG_SYS_MALLOC_CLEAR_ON_INIT=y

# CONFIG_TOOLS_DEBUG is not set

# CONFIG_PHYS_64BIT is not set

#

# Boot images

#

# CONFIG_ANDROID_BOOT_IMAGE is not set

# CONFIG_FIT is not set

CONFIG_OF_BOARD_SETUP=y

# CONFIG_OF_SYSTEM_SETUP is not set

# CONFIG_OF_STDOUT_VIA_ALIAS is not set

CONFIG_SYS_EXTRA_OPTIONS=""

CONFIG_ARCH_FIXUP_FDT_MEMORY=y

#

# API

#

# CONFIG_API is not set

#

# Boot timing

#

# CONFIG_BOOTSTAGE is not set

CONFIG_BOOTSTAGE_RECORD_COUNT=30

CONFIG_SPL_BOOTSTAGE_RECORD_COUNT=5

CONFIG_BOOTSTAGE_STASH_ADDR=0

CONFIG_BOOTSTAGE_STASH_SIZE=0x1000

#

# Boot media

#

# CONFIG_NAND_BOOT is not set

# CONFIG_ONENAND_BOOT is not set

# CONFIG_QSPI_BOOT is not set

# CONFIG_SATA_BOOT is not set

# CONFIG_SD_BOOT is not set

# CONFIG_SPI_BOOT is not set

CONFIG_BOOTDELAY=2

CONFIG_USE_BOOTARGS=y

CONFIG_BOOTARGS="console=ttyS2,115200 panic=5 rootwait root=/dev/mtdblock3 rw rootfstype=jffs2"

CONFIG_USE_BOOTCOMMAND=y

CONFIG_BOOTCOMMAND="sf probe 0 50000000; sf read 0x80C00000 0x100000 0x4000; sf read 0x80008000 0x110000 0x400000; bootz 0x80008000 - 0x80C00000"

#

# Console

#

CONFIG_MENU=y

# CONFIG_CONSOLE_RECORD is not set

CONFIG_LOGLEVEL=4

CONFIG_SPL_LOGLEVEL=4

# CONFIG_SILENT_CONSOLE is not set

CONFIG_PRE_CONSOLE_BUFFER=y

CONFIG_PRE_CON_BUF_SZ=4096

CONFIG_PRE_CON_BUF_ADDR=0x4f000000

# CONFIG_CONSOLE_MUX is not set

# CONFIG_SYS_CONSOLE_IS_IN_ENV is not set

# CONFIG_SYS_CONSOLE_OVERWRITE_ROUTINE is not set

# CONFIG_SYS_CONSOLE_ENV_OVERWRITE is not set

# CONFIG_SYS_CONSOLE_INFO_QUIET is not set

CONFIG_SYS_STDIO_DEREGISTER=y

#

# Logging

#

CONFIG_LOG=y

# CONFIG_SPL_LOG is not set

CONFIG_LOG_MAX_LEVEL=5

CONFIG_LOG_CONSOLE=y

# CONFIG_LOG_TEST is not set

CONFIG_DEFAULT_FDT_FILE=""

# CONFIG_VERSION_VARIABLE is not set

CONFIG_DISPLAY_CPUINFO=y

CONFIG_DISPLAY_BOARDINFO=y

#

# Start-up hooks

#

# CONFIG_ARCH_EARLY_INIT_R is not set

# CONFIG_ARCH_MISC_INIT is not set

# CONFIG_BOARD_EARLY_INIT_F is not set

#

# Security support

#

#

# SPL / TPL

#

CONFIG_SUPPORT_SPL=y

CONFIG_SPL=y

# CONFIG_SPL_BOARD_INIT is not set

# CONFIG_SPL_BOOTROM_SUPPORT is not set

CONFIG_SPL_RAW_IMAGE_SUPPORT=y

CONFIG_SPL_LEGACY_IMAGE_SUPPORT=y

CONFIG_SPL_SYS_MALLOC_SIMPLE=y

# CONFIG_TPL_SYS_MALLOC_SIMPLE is not set

CONFIG_SPL_STACK_R=y

CONFIG_SPL_STACK_R_MALLOC_SIMPLE_LEN=0x100000

# CONFIG_SPL_SEPARATE_BSS is not set

# CONFIG_SPL_DISPLAY_PRINT is not set

CONFIG_SYS_MMCSD_RAW_MODE_U_BOOT_USE_SECTOR=y

CONFIG_SYS_MMCSD_RAW_MODE_U_BOOT_SECTOR=0x50

# CONFIG_SYS_MMCSD_RAW_MODE_U_BOOT_USE_PARTITION is not set

# CONFIG_SPL_CPU_SUPPORT is not set

# CONFIG_SPL_CRYPTO_SUPPORT is not set

# CONFIG_SPL_HASH_SUPPORT is not set

# CONFIG_SPL_DMA_SUPPORT is not set

# CONFIG_SPL_ENV_SUPPORT is not set

# CONFIG_SPL_EXT_SUPPORT is not set

# CONFIG_SPL_FPGA_SUPPORT is not set

# CONFIG_SPL_I2C_SUPPORT is not set

# CONFIG_SPL_MPC8XXX_INIT_DDR_SUPPORT is not set

# CONFIG_SPL_MTD_SUPPORT is not set

# CONFIG_SPL_MUSB_NEW_SUPPORT is not set

# CONFIG_SPL_NET_SUPPORT is not set

# CONFIG_SPL_NO_CPU_SUPPORT is not set

# CONFIG_SPL_NOR_SUPPORT is not set

# CONFIG_SPL_XIP_SUPPORT is not set

# CONFIG_SPL_ONENAND_SUPPORT is not set

# CONFIG_SPL_OS_BOOT is not set

# CONFIG_SPL_PCI_SUPPORT is not set

# CONFIG_SPL_PCH_SUPPORT is not set

# CONFIG_SPL_POST_MEM_SUPPORT is not set

CONFIG_SPL_POWER_SUPPORT=y