楼主 # 2025-10-27 11:48:10 分享评论

- hzqlz

- 会员

- 注册时间: 2018-03-23

- 已发帖子: 173

- 积分: 151

关于串口复用的硬件电路问题请教

首先描述一下应用场景:

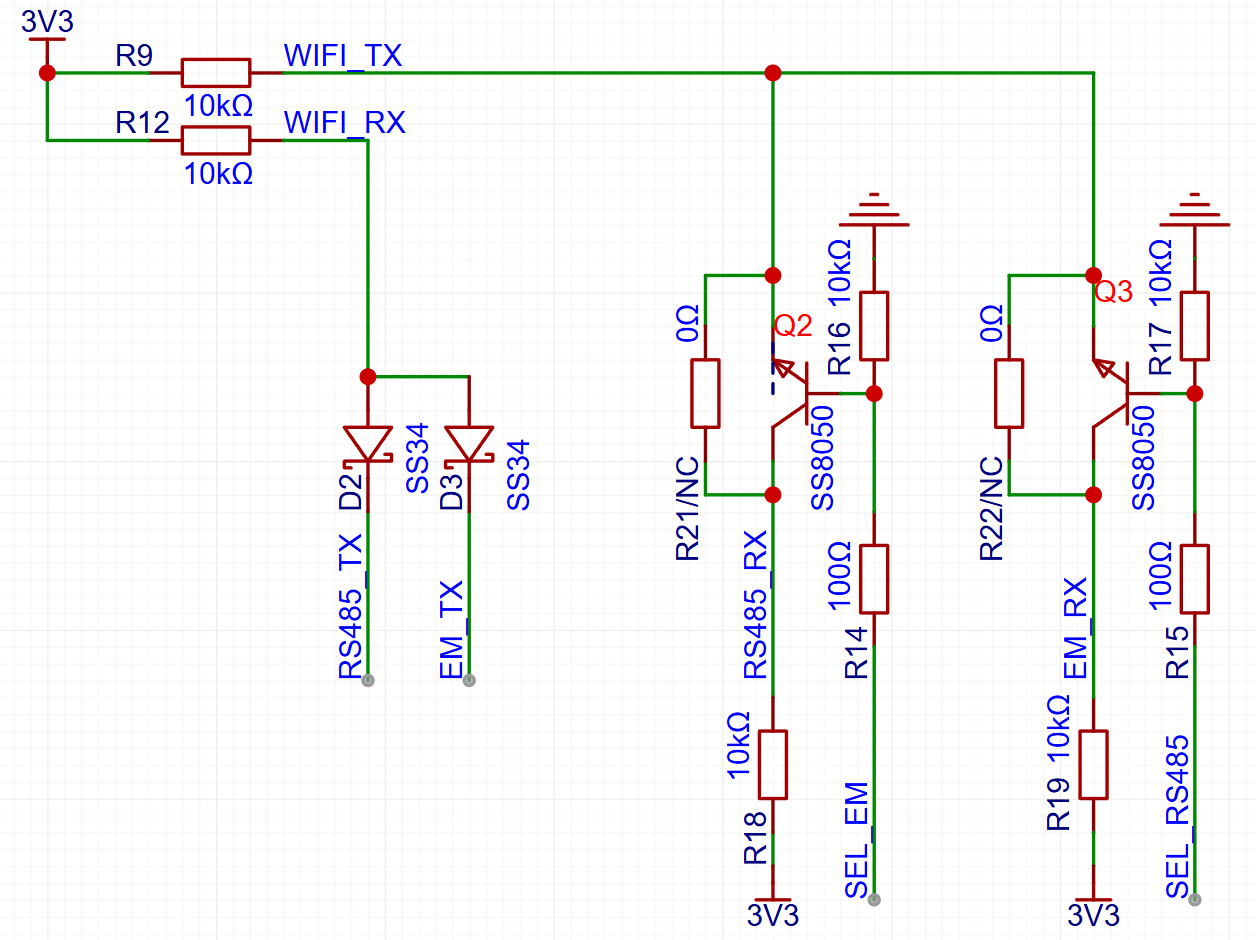

板子上的WIFI模块仅有1个串口,但是需要接2个串口设备,为了避免通讯干扰,我用MOS管(Q2和Q3,实际贴的是AO3400,NMOS)设计了一个电路,SEL_XXX引脚设置为高电平时选通对应的串口,低电平时断开对应的串口,请教各位大佬,如下图所示的设计有什么原理上的问题吗?

实际测试的时候发现,把两个SEL_XXX引脚都拉高,通讯数据才能正常发出来,只关闭其中一路,数据是异常的。

离线

#1 2025-11-02 08:52:05 分享评论

- philoman

- 会员

- 注册时间: 2025-11-02

- 已发帖子: 6

- 积分: 6

Re: 关于串口复用的硬件电路问题请教

数字信号的选通,用现成的芯片会不会更简单些,比如SN74LVC2G157

离线

感谢为中文互联网持续输出优质内容的各位老铁们。

QQ: 516333132, 微信(wechat): whycan_cn (哇酷网/挖坑网/填坑网) service@whycan.cn