楼主 # 2024-10-30 17:50:53 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

T113-I ddr初始化失败[悬赏200块]

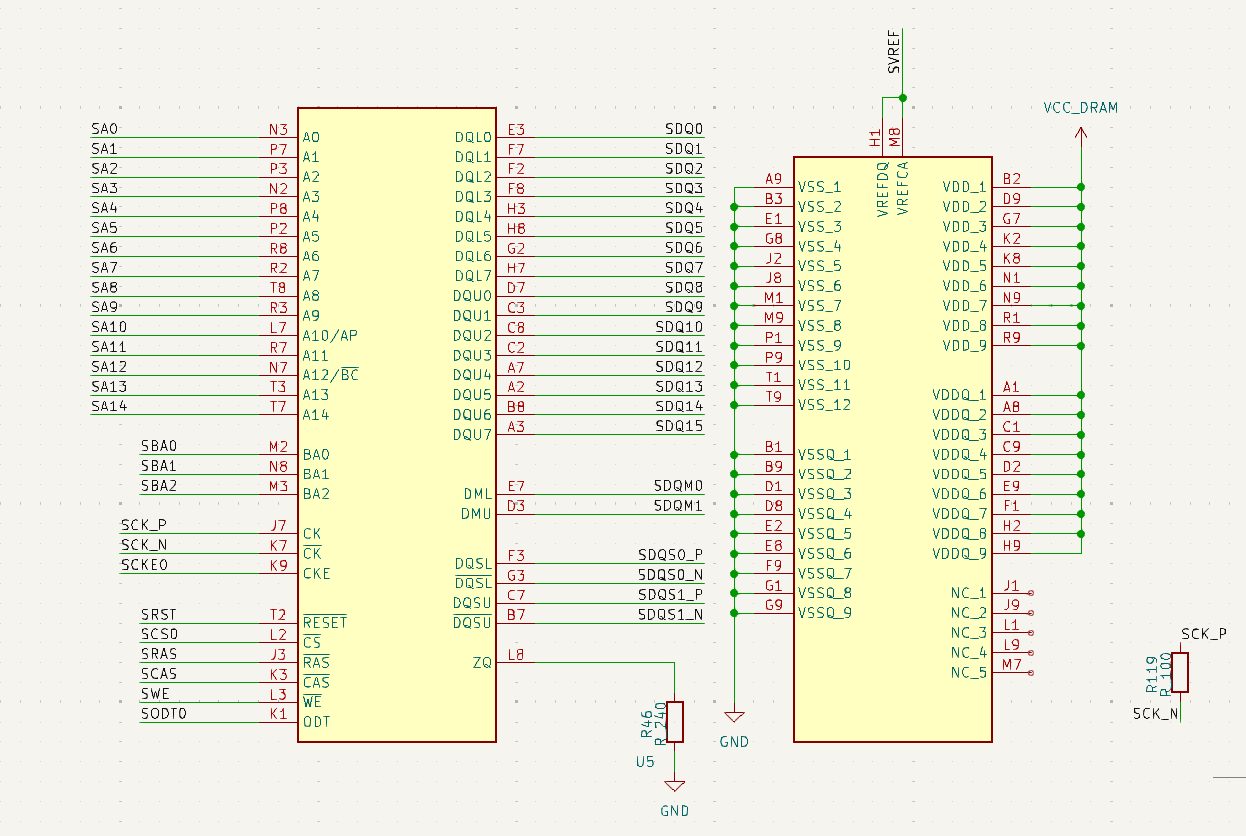

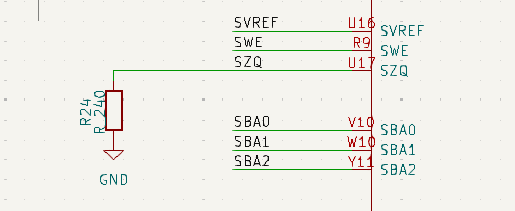

自己做了个板子测试T113-I, ddr3用了NT5CC256M16ER和F60C1A0004都试过了,spl启动的时候识别不到dram,试过降低频率,降低到120M也不行。焊接是过得回流焊,几块都是一样反应。VDRAM=1.33V, vref=0.66v, 电压看起来都正常,封装检查过很多次了,应该没有问题。有没有大哥帮忙分析下什么问题,悬赏200块解决问题。

[96]HELLO! BOOT0 is starting!

[99]BOOT0 commit : 09b36272

[102]set pll start

[108]periph0 has been enabled

[111]set pll end

[112][pmu]: bus read error

[115]board init ok

[117]enable_jtag

[118]DRAM only have internal ZQ!!

[122]get_pmu_exist() = -1

[124]ddr_efuse_type: 0x0

[127]mark_id: 0x34

[129]trefi:7.8ms

[131]DX0 state:1

[133]DX1 state:1

[134][ERROR DEBUG] auto scan dram rank&width fail !

[139]init dram fail

最近编辑记录 aeo1234 (2024-10-30 19:55:35)

离线

楼主 #3 2024-10-31 16:20:45 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

dram的配置参数不对,先用DragonHD调试

Round : 1

Running : DDR3-uart_init

uart init finish!

Running : DDR3-dram_init

DragonHD V3.0,dram init fail! channel0----(byte0 erro:1,byte1 erro:1,byte2 erro:0,byte3 erro:0)

parameter Fail:[DDR3-dram_init] .看起来两个byte都不通,是硬件问题可能较大吗。不过焊了几块都这样,难绷啊:(

离线

楼主 #6 2024-11-09 14:46:29 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

DDR3 供电不是1.5么

焊的是ddr3l,电压是1.35

离线

楼主 #7 2024-11-09 14:46:53 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

@aeo1234

选看看参数是否不对?位宽等等,具体你可以在DragonHD的dram_init右击修改。

目前看起来是原理图不对,完全不能识别

离线

楼主 #15 2024-11-18 15:24:54 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

哈哈,200要归我了。

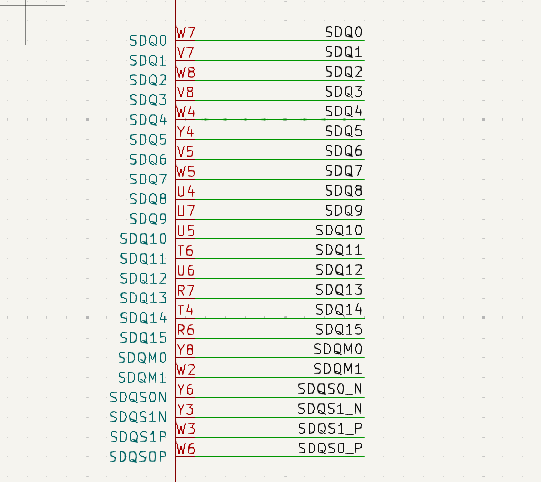

找到全志的参考原理图调整数据线的线序,你这个线序不对。

确实很诡异,我淘宝买了一个哪吒开发板的资料包。30块,正在打样中,还不知道行不行

离线

楼主 #16 2024-11-18 15:25:26 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

suibian 说:哈哈,200要归我了。

找到全志的参考原理图调整数据线的线序,你这个线序不对。@aeo1234 请问楼主你的问题解决了吗?

已给楼主发 email

还没有,还在改版打样中

离线

楼主 #17 2024-11-18 15:30:30 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

@Gentlepig

这是淘宝30块钱买的哪吒开发板的原理图,我看和楼上发的官方资料差不多,那个线序是乱的,有没有大佬知道是为什么,是原理图封装故意标错了吗

D1-H_SCHEMATIC_NEZA_V1_2.pdf

D1-H_package.zip

离线

楼主 #18 2024-11-18 15:38:32 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

哈哈,200要归我了。

找到全志的参考原理图调整数据线的线序,你这个线序不对。

不要说我是标题党。只是你回答太晚了。这期间我买了一堆开发板和资料研究,不缺这点钱哈,这些开发板全新我都没退货,有需要二手的可以找我,5折。

至于那个线序到底行不行,才改完,还在嘉立创打样,有待验证,要是成功了在v你200

最近编辑记录 aeo1234 (2024-11-18 15:40:04)

离线

楼主 #19 2024-11-18 15:45:32 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

@Gentlepig

一比一对着接线已知不行,之前这个就是完全对着接的。焊接肯定没问题

离线

楼主 #25 2024-12-09 20:12:41 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

@suibian

验证完。最近我同时打了三块板验证,一块是直接用买的哪个开发板原理一gerber打样,一个是在之前的pcb改了按照evb改了线序,还有个是在evb的基础再次组内交换字节顺序的数据线,交换了少量地址线(没有交换控制线)。经过验证全部可以启动,线序交换是符合理论预期的。在对比最早的一版,对着接线不行是因为引脚是错的。不过楼下说的内存类型不对是否正确有待考证

离线

楼主 #26 2024-12-09 20:14:38 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

@vectorspace

我验证了确实封装引脚是错的, 但是是否内存类型错误有待考证,没有在任何资料看到过。不过我感觉可能性较大,认可此答案1/2。 发支付码,打钱1/2.

离线

楼主 #27 2024-12-09 20:17:42 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

@suibian

和走线这些其实关系不大,经过我三板验证,以及研究了买的图纸,芯片做了内部等长,组内只需要简易等长岂可,注意时钟线差分,4层都能随便走,目前频率打满非常正常。 不过嘉立创6层甚至比4层还便宜。 上面发的原理图有效, 认可此答案1/2。 发支付码,打钱1/2。

离线

楼主 #30 2024-12-20 22:17:05 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

论坛打给谁,二维码,打钱

离线

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发