楼主 #1 2018-09-16 17:03:49 分享评论

楼主 #2 2018-09-16 17:09:54 分享评论

楼主 #3 2018-09-16 17:10:49 分享评论

#4 2018-09-18 09:58:52 分享评论

- Jin劲

- 会员

- 注册时间: 2018-04-06

- 已发帖子: 217

- 积分: 217

Re: 最权威的 RISC-V 汇编程序员手册

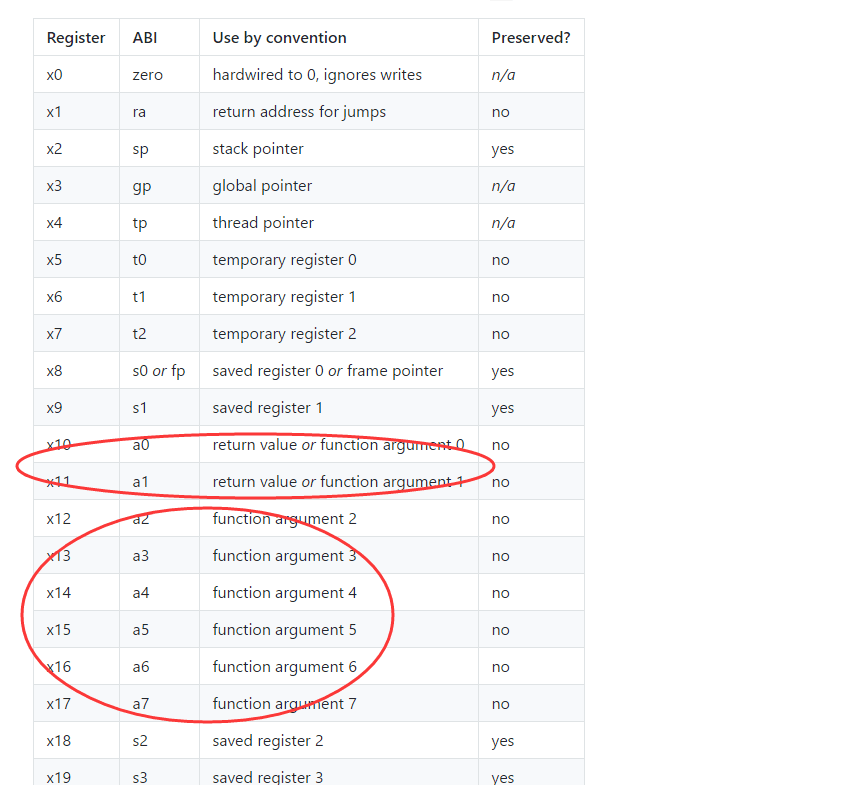

多达 32 个寄存器(x0 .. x31)也是一大特色了,

一般的函数调用都用不上堆栈了,

直接寄存器传参了。这也算一个后发优势吧, 没有历史包袱,架构和指令集可以吸取众家之长。

我偏偏要搞一个33个参数的函数[骄傲脸]

最近编辑记录 Jin劲 (2018-09-18 09:59:07)

离线

楼主 #5 2018-09-18 10:03:05 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,442

- 积分: 9202

离线

#6 2018-09-18 13:54:32 分享评论

- Jin劲

- 会员

- 注册时间: 2018-04-06

- 已发帖子: 217

- 积分: 217

Re: 最权威的 RISC-V 汇编程序员手册

Jin劲 说:晕哥 说:多达 32 个寄存器(x0 .. x31)也是一大特色了,

一般的函数调用都用不上堆栈了,

直接寄存器传参了。这也算一个后发优势吧, 没有历史包袱,架构和指令集可以吸取众家之长。

我偏偏要搞一个33个参数的函数[骄傲脸]

x10 - x17 八个参数的函数就爆了, 超过八个就要用栈传递参数了。

不好意思 今天没吃药[捂脸]

离线

楼主 #7 2018-09-18 14:03:56 分享评论

#8 2018-09-18 14:09:16 分享评论

- 路人甲

- 会员

- 注册时间: 2017-09-07

- 已发帖子: 202

- 积分: 199.5

Re: 最权威的 RISC-V 汇编程序员手册

还好我只会C,汇编看不懂,管他什么架构,拿起键盘就开干。

离线

#9 2018-09-18 14:12:08 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,140

- 积分: 1092.5

Re: 最权威的 RISC-V 汇编程序员手册

8个参数之内不需要栈协助参数传递, 坑定可以大大提高函数调用的效率.

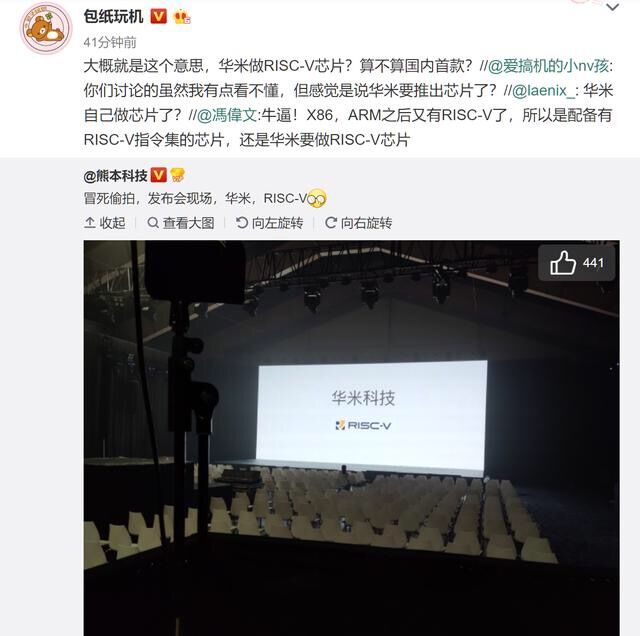

感觉不久的将来 RISC-V 与 X86, ARM要三分天下了。

我们的近邻印度把 RISC-V 作为国家指令集.

期待类似v3s这样的芯片,8块钱一个哈哈?

离线

楼主 #10 2018-09-18 14:15:47 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,442

- 积分: 9202

离线

楼主 #11 2018-09-18 14:17:28 分享评论

#12 2018-09-18 18:44:50 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,140

- 积分: 1092.5

Re: 最权威的 RISC-V 汇编程序员手册

离线

楼主 #13 2018-09-18 19:20:27 分享评论

#14 2022-11-24 13:18:46 分享评论

- 吴助建

- 会员

- 注册时间: 2021-12-08

- 已发帖子: 116

- 积分: 19

Re: 最权威的 RISC-V 汇编程序员手册

寄存器多,对于单个程序来说,是好事。

但如果有中断,甚至有OS,那就是灾难!灾难!灾难!

32个寄存器,保存它,至少32个周期;恢复它,同样至少32个周期;

如果中断一多,CPU大部分的时间都花在:保存寄存器/恢复寄存器。

也不知道有没有人想过这个问题?

离线

#15 2022-11-24 17:25:23 分享评论

- STM32F030

- 会员

- 注册时间: 2020-03-24

- 已发帖子: 16

- 积分: 40

Re: 最权威的 RISC-V 汇编程序员手册

@吴助建

看了下WCH家的手册,针对中断现场保存,设计了硬件压栈。支持硬件单周期将相关寄存器保存至内部堆栈区,硬件压栈支持3级嵌套深度。超过3级好像就会一个寄存器一个寄存器的往用户堆栈区保存现场。

离线

#16 2022-11-24 18:28:40 分享评论

- 吴助建

- 会员

- 注册时间: 2021-12-08

- 已发帖子: 116

- 积分: 19

Re: 最权威的 RISC-V 汇编程序员手册

@吴助建

看了下WCH家的手册,针对中断现场保存,设计了硬件压栈。支持硬件单周期将相关寄存器保存至内部堆栈区,硬件压栈支持3级嵌套深度。超过3级好像就会一个寄存器一个寄存器的往用户堆栈区保存现场。

有硬件压栈,解决不了RTOS,因为硬件压栈的数据是不可访问的。

硬件压栈,不用RTOS的时候,有用。

离线

#17 2022-11-24 19:16:09 分享评论

- XIVN1987

- 会员

- 注册时间: 2019-08-30

- 已发帖子: 271

- 积分: 332.5

Re: 最权威的 RISC-V 汇编程序员手册

RISC-V 有 RV32E 版本,,16个寄存器。。

离线

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发