楼主 #1 2021-04-28 16:15:12 分享评论

楼主 #2 2021-04-28 16:15:36 分享评论

Re: 淘宝V3s摄像头(防瞌睡? 检测司机打电话?)卡在gc0403驱动,有能力继续研究的朋友送两台拆解,跟帖或者联系微信 whycan_cn

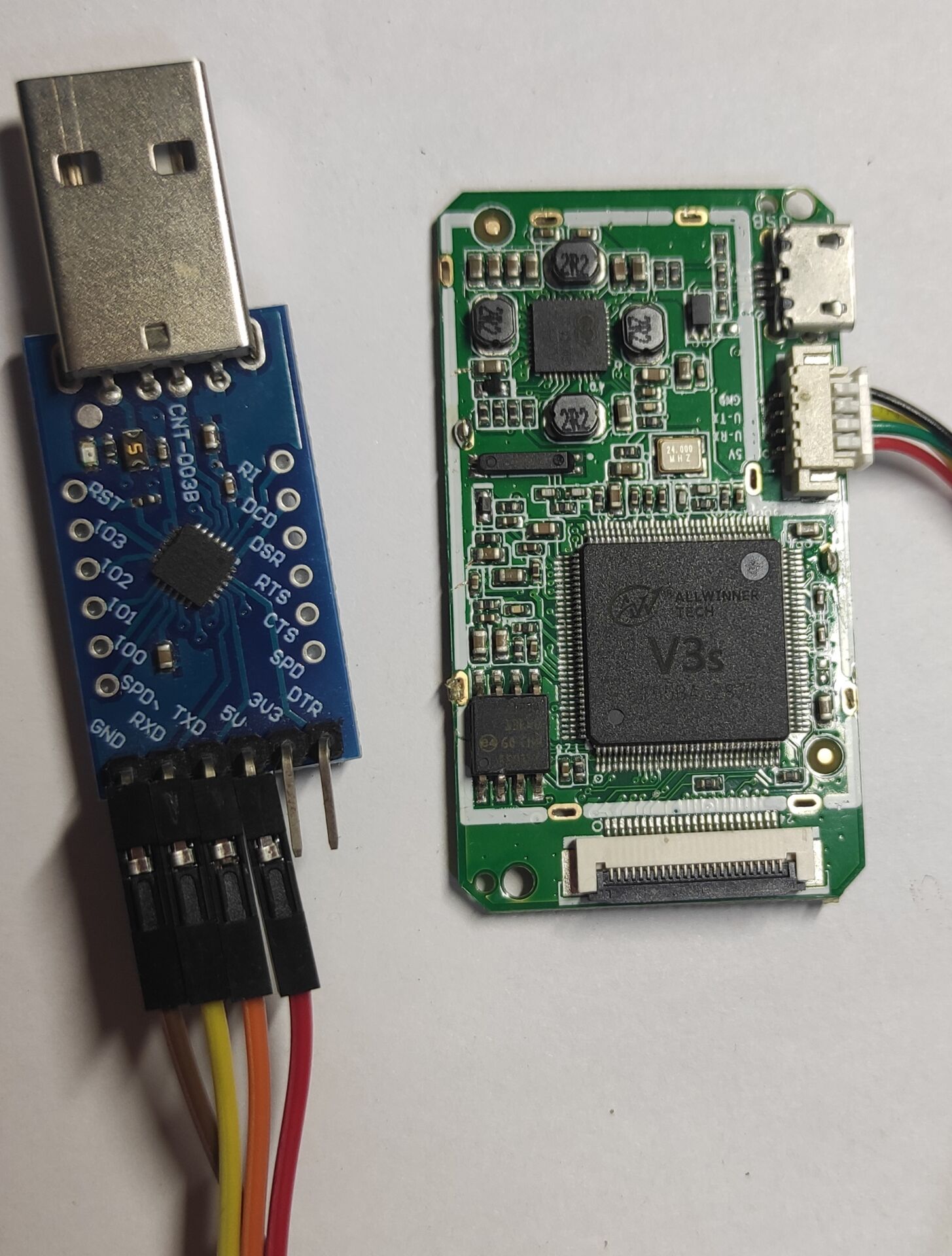

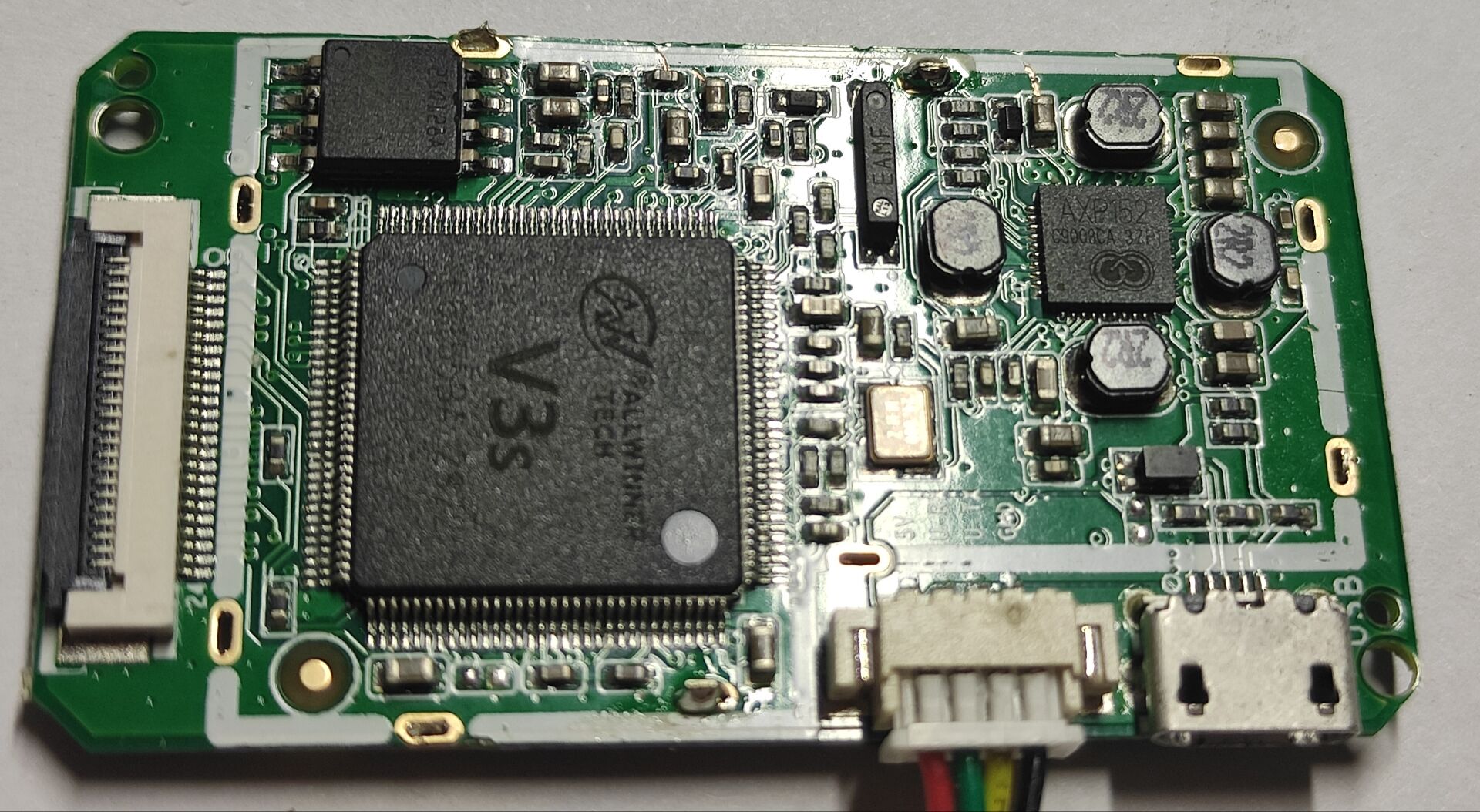

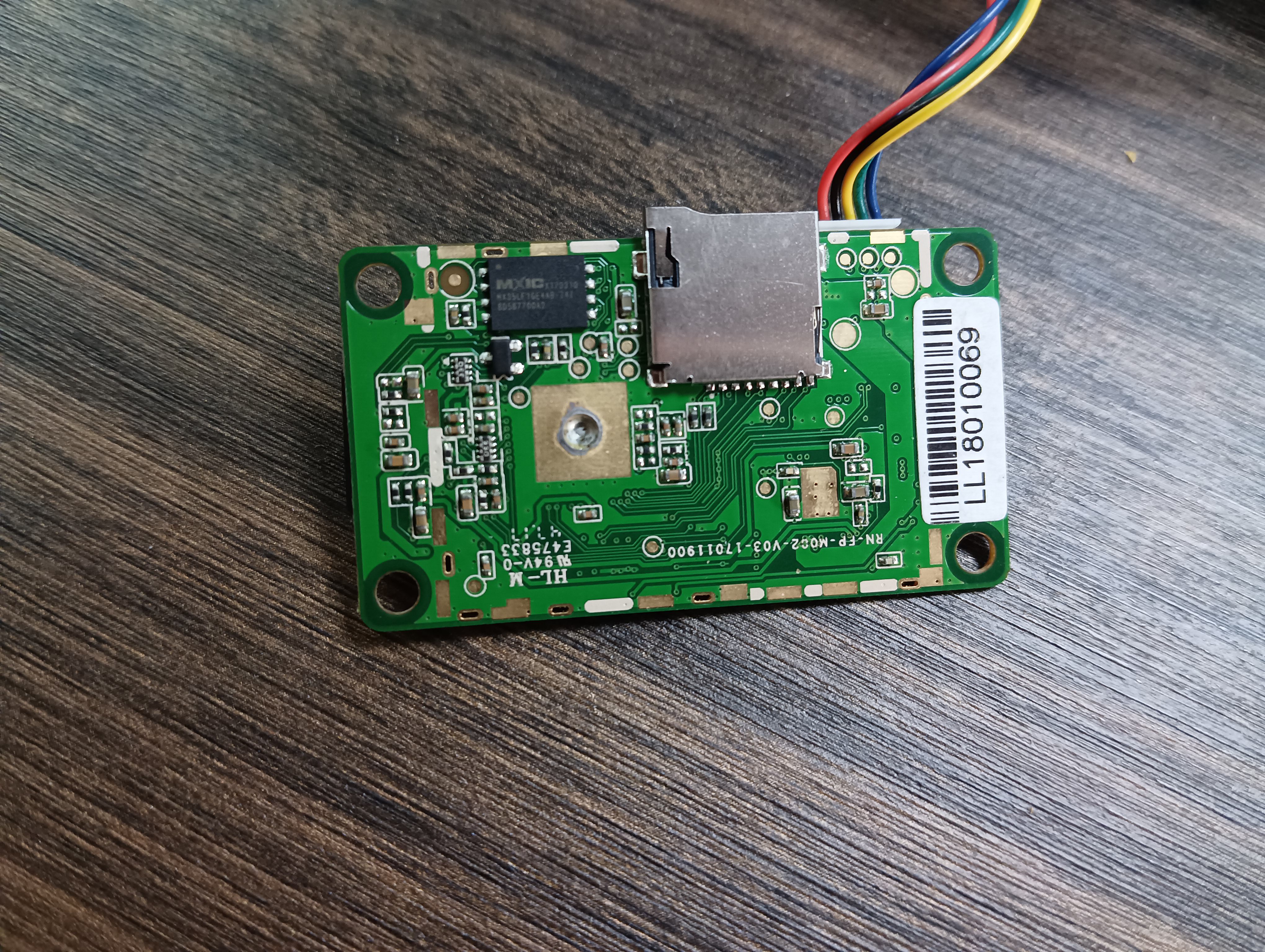

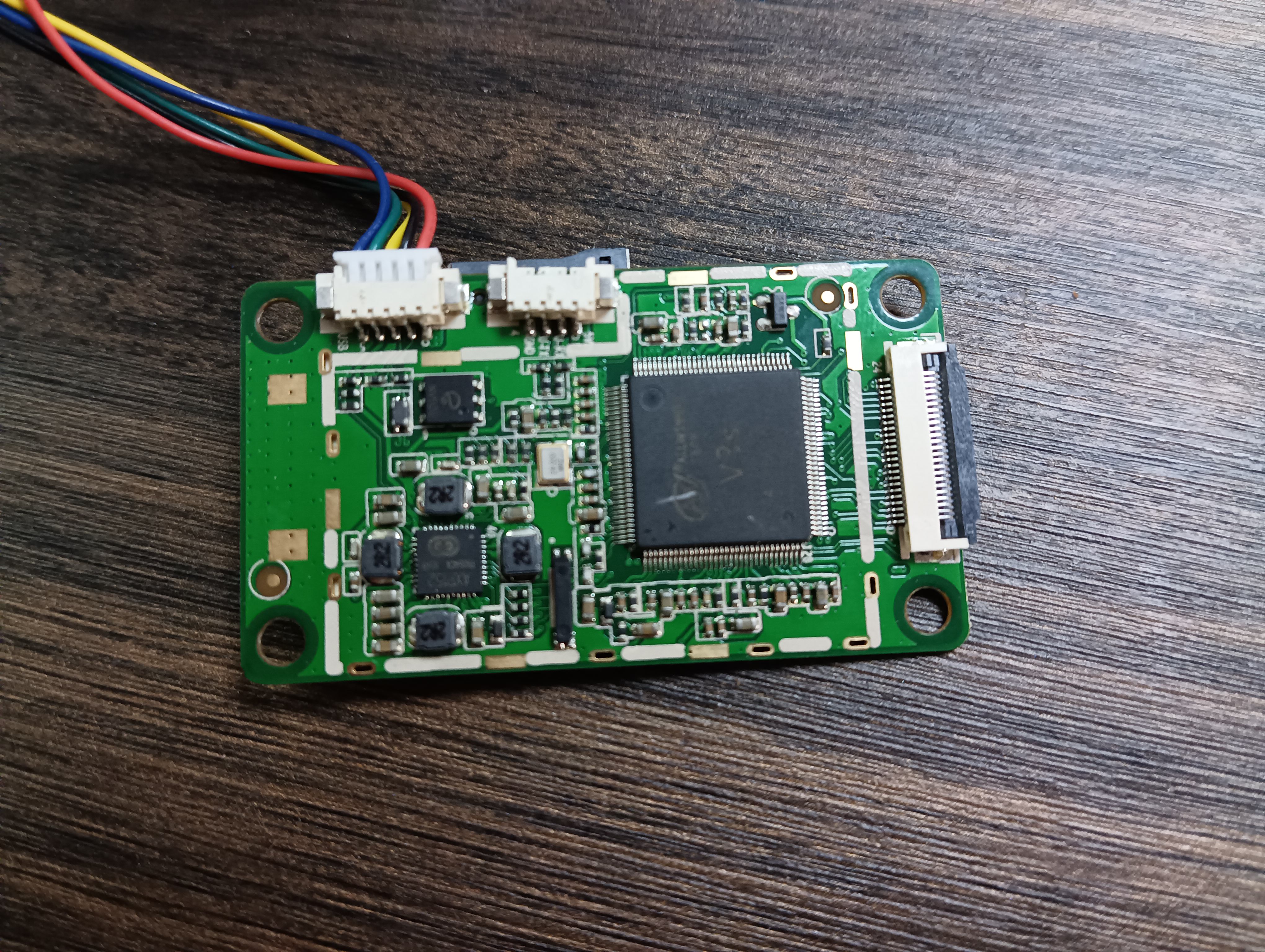

板子很紧凑, 不是使用V3s公版推荐的AXP223, 而是使用四路DC-DC的AXP152

板载摄像头, 目前不知道型号,

有USB口, 和串口

对外只有串口和电源, 根据多年忽悠经验, 估计是一个车载检测司机有无瞌睡, 检测有无打手机的设备.

串口不定时发送数据.

购买链接: https://item.taobao.com/item.htm?id=602763666443

讨论QQ群: 516836432

离线

楼主 #3 2021-04-28 16:15:38 分享评论

Re: 淘宝V3s摄像头(防瞌睡? 检测司机打电话?)卡在gc0403驱动,有能力继续研究的朋友送两台拆解,跟帖或者联系微信 whycan_cn

(编辑中 ...)

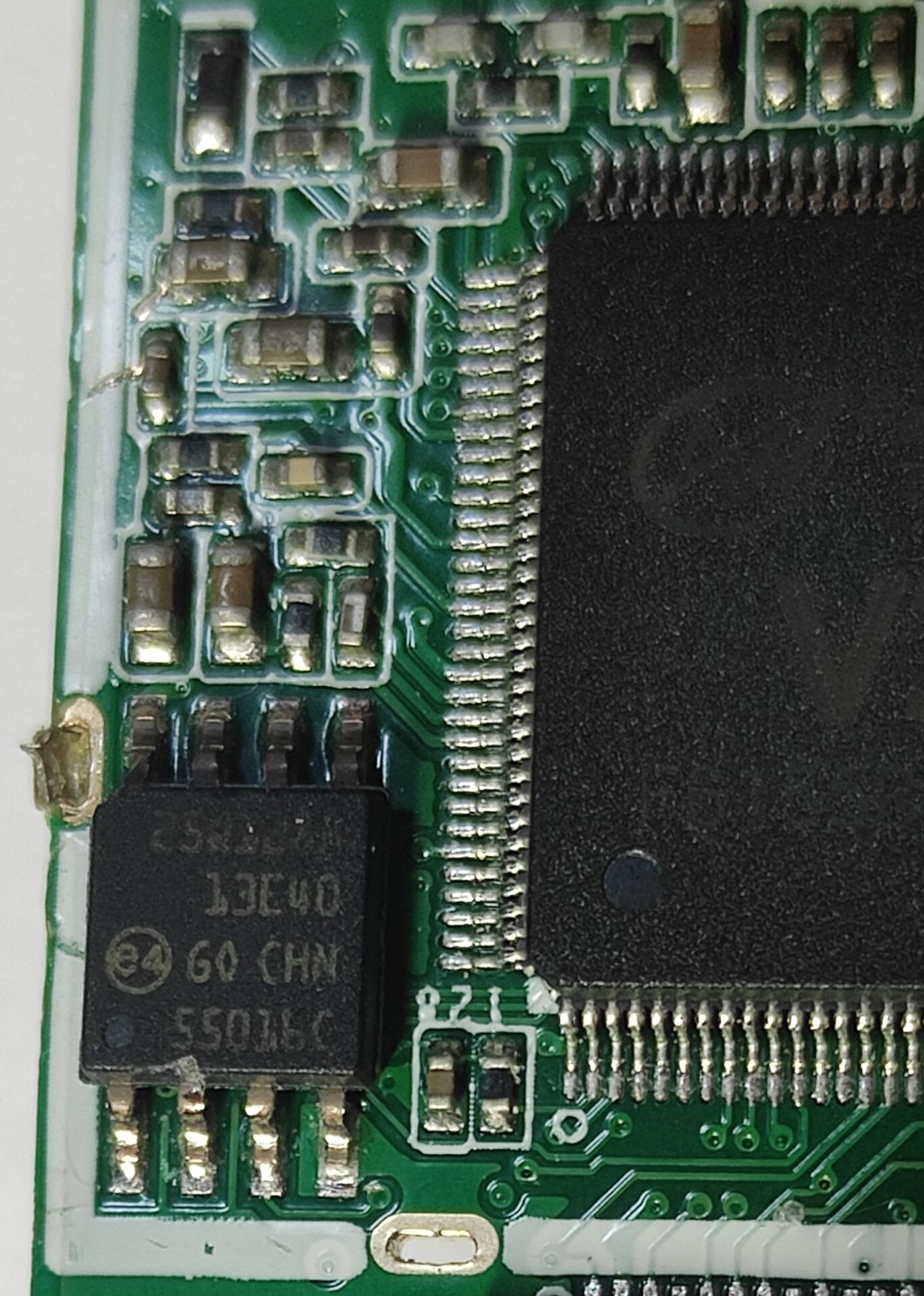

CPU: V3s

V3s手册V1.0: Allwinner_V3s_Datasheet_V1.0.pdf

本站下载: n25q_128mb_3v_65nm.pdf

电源芯片AXP152: AXP152_Datasheet_v1.0_cn.pdf

GC0403摄像头手册: GC0403_DataSheet_V1.0_for_Released_20141222.pdf

其他摄像头手册:

GC0310_DataSheet_Released_V1_0_20140219.pdf

GC0310_Design_V1_0_20140214.pdf

GC0312_DataSheet_Released_V1_0_20140314.pdf

GC0312_Design_V1_0_20140314.pdf

固件下载: flash_16m_n25q128.7z

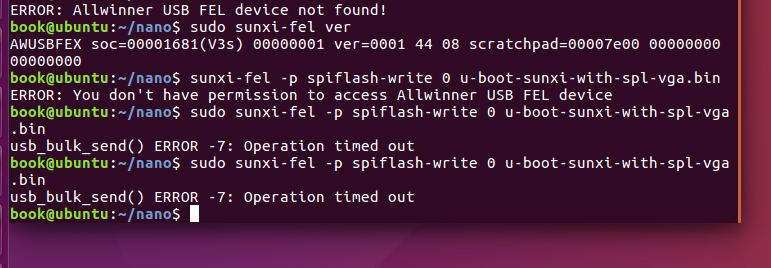

固件提取, 短路flash 3/4脚, 插入usb线:

Administrator@PC-20170510YOBI MINGW64 /f/fff/l

$ "D:\Downloads\sunxi-tools-win32support_f1c100s_v3s_201812219\V3s\sunxi-fel.exe " -p spiflash-info

ERROR: Allwinner USB FEL device not found!

Administrator@PC-20170510YOBI MINGW64 /f/fff/l

$ "D:\Downloads\sunxi-tools-win32support_f1c100s_v3s_201812219\V3s\sunxi-fel.exe " -p spiflash-info

Manufacturer: Unknown (20h), model: BAh, size: 16777216 bytes.

Administrator@PC-20170510YOBI MINGW64 /f/fff/l

$ "D:\Downloads\sunxi-tools-win32support_f1c100s_v3s_201812219\V3s\sunxi-fel.exe" -p spiflash-read 0 16777216 read1.bin

100% [================================================] 16777 kB, 95.6 kB/s

Administrator@PC-20170510YOBI MINGW64 /f/fff/l

$ "D:\Downloads\sunxi-tools-win32support_f1c100s_v3s_201812219\V3s\sunxi-fel.exe" -p spiflash-read 0 16777216 read2.bin

100% [================================================] 16777 kB, 89.7 kB/s读两次, 比较是否一致。

串口: UART0 PF2 / PF4

// SPDX-License-Identifier: GPL-2.0

/*

* gc0403 driver

*

* Copyright (C) 2019 Fuzhou Rockchip Electronics Co.,Ltd.

* V0.0X01.0X02 add enum_frame_interval function.

*/

#include <linux/clk.h>

#include <linux/device.h>

#include <linux/delay.h>

#include <linux/gpio/consumer.h>

#include <linux/i2c.h>

#include <linux/module.h>

#include <linux/pm_runtime.h>

#include <linux/regulator/consumer.h>

#include <linux/sysfs.h>

#include <media/media-entity.h>

#include <media/v4l2-async.h>

#include <media/v4l2-ctrls.h>

#include <media/v4l2-subdev.h>

#include <linux/rk-camera-module.h>

/*

* GC0403 register definitions

*/

#define GC0403_REG_EXP_H 0x03

#define GC0403_REG_EXP_L 0x04

#define GC0403_REG_VBLK_H 0x07

#define GC0403_REG_VBLK_L 0x08

#define GC0403_REG_MIPI_EN 0x10

#define GC0403_REG_DGAIN_H 0xb1

#define GC0403_REG_DGAIN_L 0xb2

#define GC0403_REG_AGAIN 0xb6

#define GC0403_REG_CHIP_ID_H 0xf0

#define GC0403_REG_CHIP_ID_L 0xf1

#define PAGE_SELECT_REG 0xfe

#define REG_NULL 0xff

#define GC0403_CHIP_ID 0x0403

#define SENSOR_ID(_msb, _lsb) ((_msb) << 8 | (_lsb))

#define GC0403_ANALOG_GAIN_MIN 0

#define GC0403_ANALOG_GAIN_MAX 0x0a

#define GC0403_ANALOG_GAIN_STP 1

#define GC0403_ANALOG_GAIN_DFT 1

/* gain[4:0] [0x00,0x0a]*/

#define GC0403_FETCH_ANALOG_GAIN(VAL) ((VAL) & 0x0F)

#ifndef V4L2_CID_DIGITAL_GAIN

#define V4L2_CID_DIGITAL_GAIN V4L2_CID_GAIN

#endif

#define GC0403_DIGI_GAIN_MIN 0x40

#define GC0403_DIGI_GAIN_MAX 0x3ff

#define GC0403_DIGI_GAIN_STP 1

#define GC0403_DIGI_GAIN_DFT 0x40

/* gain[9:6] */

#define GC0403_FETCH_DIGITAL_GAIN_HIGH(VAL) (((VAL) >> 6) & 0x0F)

/* gain[5:0] */

#define GC0403_FETCH_DIGITAL_GAIN_LOW(VAL) (((VAL) << 2) & 0xFC)

#define GC0403_TOTAL_GAIN_MIN 100

#define GC0403_TOTAL_GAIN_MAX 3200

#define GC0403_TOTAL_GAIN_STEP 1

#define GC0403_EXPOSURE_MAX 8191

#define GC0403_EXPOSURE_MIN 1

#define GC0403_NAME "gc0403"

#define DRIVER_VERSION KERNEL_VERSION(0, 0x01, 0x02)

#define GC0403_XVCLK_FREQ 24000000

#define GC0403_LINK_FREQ 96000000

#define GC0403_PIXEL_RATE (GC0403_LINK_FREQ * 2 * 1 / 10)

static const s64 link_freq_menu_items[] = {

GC0403_LINK_FREQ

};

static const char * const gc0403_supply_names[] = {

"dovdd", /* Digital I/O power */

"avdd", /* Analog power */

};

#define GC0403_NUM_SUPPLIES ARRAY_SIZE(gc0403_supply_names)

struct regval {

u8 addr;

u8 val;

};

struct gc0403_mode {

u32 width;

u32 height;

struct v4l2_fract max_fps;

u32 hts_def;

u32 vts_def;

u32 exp_def;

const struct regval *reg_list;

};

struct gc0403 {

struct i2c_client *client;

struct clk *xvclk;

struct gpio_desc *pwdn_gpio;

struct regulator_bulk_data supplies[GC0403_NUM_SUPPLIES];

struct v4l2_subdev subdev;

struct media_pad pad;

struct v4l2_ctrl_handler ctrl_handler;

struct v4l2_ctrl *exposure;

struct v4l2_ctrl *anal_gain;

struct v4l2_ctrl *digi_gain;

struct v4l2_ctrl *hblank;

struct v4l2_ctrl *vblank;

/* mutex lock, protect current operation */

struct mutex mutex;

bool streaming;

const struct gc0403_mode *cur_mode;

u32 module_index;

const char *module_facing;

const char *module_name;

const char *len_name;

};

#define to_gc0403(sd) container_of(sd, struct gc0403, subdev)

/*

* MCLK=24Mhz

* MIPI_CLOCK=192Mbps

* Actual_window_size=640*480

* HD=1362

* VD=586

* row_time=56.75us,FPS = 30fps;

*/

static const struct regval gc0403_vga_regs[] = {

/****SYS****/

{0xfe, 0x80},

{0xfe, 0x80},

{0xfe, 0x80},

{0xf2, 0x00}, /* sync_pad_io_ebi */

{0xf6, 0x00}, /*up down */

{0xfc, 0xc6},

{0xf7, 0x19}, /* pll enable */

{0xf8, 0x01}, /* Pll mode 2 */

{0xf9, 0x3e}, /* [0] pll enable solve IOVDD large current problem */

{0xfe, 0x03},

{0x06, 0x80},

{0x06, 0x00},

{0xfe, 0x00},

{0xf9, 0x2e},

{0xfe, 0x00},

{0xfa, 0x00}, /* div */

{0xfe, 0x00},

/**ANALOG&CISCTL**/

{0x03, 0x02},

{0x04, 0x55},

{0x05, 0x01}, /* H blank */

{0x06, 0x49}, /* H blank=bb=187 */

{0x07, 0x00}, /* VB */

{0x08, 0x5a}, /* VB=E8=232 */

{0x09, 0x00},

{0x0a, 0x2c},

{0x0b, 0x00},

{0x0c, 0x3c},

{0x0d, 0x01}, /* win_height */

{0x0e, 0xf0}, /* 496 */

{0x0f, 0x02}, /* win_width */

{0x10, 0x90}, /* 656 */

{0x11, 0x23}, /* 44FPN abnormal column */

{0x12, 0x10},

{0x13, 0x11},

{0x14, 0x01},

{0x15, 0x00},

{0x16, 0xc0},

{0x17, 0x14},

{0x18, 0x02},

{0x19, 0x38},

{0x1a, 0x11},

{0x1b, 0x06},

{0x1c, 0x04},

{0x1d, 0x00},

{0x1e, 0xfc},

{0x1f, 0x09},

{0x20, 0xb5},

{0x21, 0x3f},

{0x22, 0xe6},

{0x23, 0x32},

{0x24, 0x2f},

{0x27, 0x00},

{0x28, 0x00},

{0x2a, 0x00},

{0x2b, 0x00},

{0x2c, 0x00},

{0x2d, 0x01},

{0x2e, 0xf0},

{0x2f, 0x01},

{0x25, 0xc0},

{0x3d, 0xe0},

{0x3e, 0x45},

{0x3f, 0x1f},

{0xc2, 0x17},

{0x30, 0x22},

{0x31, 0x23},

{0x32, 0x02},

{0x33, 0x03},

{0x34, 0x04},

{0x35, 0x05},

{0x36, 0x06},

{0x37, 0x07},

{0x38, 0x0f},

{0x39, 0x17},

{0x3a, 0x1f},

/****ISP****/

{0xfe, 0x00},

{0x8a, 0x00},

{0x8c, 0x07},

{0x8e, 0x02}, /* luma value not normal */

{0x90, 0x01},

{0x94, 0x02},

{0x95, 0x01},

{0x96, 0xe0}, /* 480 */

{0x97, 0x02},

{0x98, 0x80}, /* 640 */

/****BLK****/

{0xfe, 0x00},

{0x18, 0x02},

{0x40, 0x22},

{0x41, 0x01},

{0x5e, 0x00},

{0x66, 0x20},

/****MIPI****/

{0xfe, 0x03},

{0x01, 0x83},

{0x02, 0x11},

{0x03, 0x96},

{0x04, 0x01},

{0x05, 0x00},

{0x06, 0xa4},

{0x10, 0x90},

{0x11, 0x2b},

{0x12, 0x20},

{0x13, 0x03},

{0x15, 0x00},

{0x21, 0x10},

{0x22, 0x03},

{0x23, 0x20},

{0x24, 0x02},

{0x25, 0x10},

{0x26, 0x05},

{0x21, 0x10},

{0x29, 0x03},

{0x2a, 0x0a},

{0x2b, 0x04},

{0xfe, 0x00},

{0xb0, 0x50},

{0xb6, 0x09},

{REG_NULL, 0x00},

};

/*

* MCLK=24Mhz

* MIPI_CLOCK=192Mbps

* Actual_window_size=768*576

* HD=1206

* VD=663

* row_time=50.25us,FPS = 30fps;

*/

static const struct regval gc0403_768x576_regs[] = {

/****SYS****/

{0xfe, 0x80},

{0xfe, 0x80},

{0xfe, 0x80},

{0xf2, 0x00}, /* sync_pad_io_ebi */

{0xf6, 0x00}, /* up down */

{0xfc, 0xc6},

{0xf7, 0x19}, /* pll enable */

{0xf8, 0x01}, /* Pll mode 2 */

{0xf9, 0x3e}, /* [0] pll enable solve IOVDD large current problem */

{0xfe, 0x03},

{0x06, 0x80},

{0x06, 0x00},

{0xfe, 0x00},

{0xf9, 0x2e},

{0xfe, 0x00},

{0xfa, 0x00}, /* div */

{0xfe, 0x00},

/**ANALOG&CISCTL**/

{0x03, 0x02},

{0x04, 0x55},

{0x05, 0x00}, /* H blank */

{0x06, 0xbb}, /* H blank=bb=187 */

{0x07, 0x00}, /* VB */

{0x08, 0x46}, /* VB=E8=232 */

{0x0c, 0x04},

{0x0d, 0x02}, /* win_height */

{0x0e, 0x48}, /* 584 */

{0x0f, 0x03}, /* win_width */

{0x10, 0x08}, /* 776 */

{0x11, 0x23}, /* 44FPN abnormal column */

{0x12, 0x10},

{0x13, 0x11},

{0x14, 0x01},

{0x15, 0x00},

{0x16, 0xc0},

{0x17, 0x14},

{0x18, 0x02},

{0x19, 0x38},

{0x1a, 0x11},

{0x1b, 0x06},

{0x1c, 0x04},

{0x1d, 0x00},

{0x1e, 0xfc},

{0x1f, 0x09},

{0x20, 0xb5},

{0x21, 0x3f},

{0x22, 0xe6},

{0x23, 0x32},

{0x24, 0x2f},

{0x27, 0x00},

{0x28, 0x00},

{0x2a, 0x00},

{0x2b, 0x00},

{0x2c, 0x00},

{0x2d, 0x01},

{0x2e, 0xf0},

{0x2f, 0x01},

{0x25, 0xc0},

{0x3d, 0xe0},

{0x3e, 0x45},

{0x3f, 0x1f},

{0xc2, 0x17},

{0x30, 0x22},

{0x31, 0x23},

{0x32, 0x02},

{0x33, 0x03},

{0x34, 0x04},

{0x35, 0x05},

{0x36, 0x06},

{0x37, 0x07},

{0x38, 0x0f},

{0x39, 0x17},

{0x3a, 0x1f},

/****ISP****/

{0xfe, 0x00},

{0x8a, 0x00},

{0x8c, 0x07},

{0x8e, 0x02}, /* luma value not normal */

{0x90, 0x01},

{0x94, 0x02},

{0x95, 0x02},

{0x96, 0x40}, /* 576 */

{0x97, 0x03},

{0x98, 0x00}, /* 768 */

/****BLK****/

{0xfe, 0x00},

{0x18, 0x02},

{0x40, 0x22},

{0x41, 0x01},

{0x5e, 0x00},

{0x66, 0x20},

/****MIPI****/

{0xfe, 0x03},

{0x01, 0x83},

{0x02, 0x11},

{0x03, 0x96},

{0x04, 0x01},

{0x05, 0x00},

{0x06, 0xa4},

{0x10, 0x80},

{0x11, 0x2b},

{0x12, 0xc0},

{0x13, 0x03},

{0x15, 0x00},

{0x21, 0x10},

{0x22, 0x03},

{0x23, 0x20},

{0x24, 0x02},

{0x25, 0x10},

{0x26, 0x05},

{0x21, 0x10},

{0x29, 0x01},

{0x2a, 0x0a},

{0x2b, 0x04},

{0xfe, 0x00},

{0xb0, 0x50},

{0xb6, 0x01},

{REG_NULL, 0x00},

};

static const struct gc0403_mode supported_modes[] = {

{

.width = 640,

.height = 480,

.max_fps = {

.numerator = 10000,

.denominator = 300000,

},

.exp_def = 500,

.hts_def = 1362,

.vts_def = 586,

.reg_list = gc0403_vga_regs,

},

{

.width = 768,

.height = 576,

.max_fps = {

.numerator = 10000,

.denominator = 300000,

},

.exp_def = 500,

.hts_def = 1206,

.vts_def = 663,

.reg_list = gc0403_768x576_regs,

}

};

/* sensor register write */

static int gc0403_write_reg(struct i2c_client *client, u8 reg, u8 val)

{

struct i2c_msg msg;

u8 buf[2];

int ret;

buf[0] = reg & 0xFF;

buf[1] = val;

msg.addr = client->addr;

msg.flags = client->flags;

msg.buf = buf;

msg.len = sizeof(buf);

ret = i2c_transfer(client->adapter, &msg, 1);

if (ret >= 0)

return 0;

dev_err(&client->dev,

"gc0403 write reg(0x%x val:0x%x) failed !\n", reg, val);

return ret;

}

static int gc0403_write_array(struct i2c_client *client,

const struct regval *regs)

{

int i, ret = 0;

i = 0;

while (regs[i].addr != REG_NULL) {

ret = gc0403_write_reg(client, regs[i].addr, regs[i].val);

if (ret) {

dev_err(&client->dev, "%s failed !\n", __func__);

break;

}

i++;

}

return ret;

}

/* sensor register read */

static int gc0403_read_reg(struct i2c_client *client, u8 reg, u8 *val)

{

struct i2c_msg msg[2];

u8 buf[1];

int ret;

buf[0] = reg & 0xFF;

msg[0].addr = client->addr;

msg[0].flags = client->flags;

msg[0].buf = buf;

msg[0].len = sizeof(buf);

msg[1].addr = client->addr;

msg[1].flags = client->flags | I2C_M_RD;

msg[1].buf = buf;

msg[1].len = 1;

ret = i2c_transfer(client->adapter, msg, 2);

if (ret >= 0) {

*val = buf[0];

return 0;

}

dev_err(&client->dev,

"gc0403 read reg(0x%x val:0x%x) failed !\n", reg, *val);

return ret;

}

static int gc0403_get_reso_dist(const struct gc0403_mode *mode,

struct v4l2_mbus_framefmt *framefmt)

{

return abs(mode->width - framefmt->width) +

abs(mode->height - framefmt->height);

}

static const struct gc0403_mode *

gc0403_find_best_fit(struct v4l2_subdev_format *fmt)

{

struct v4l2_mbus_framefmt *framefmt = &fmt->format;

int dist;

int cur_best_fit = 0;

int cur_best_fit_dist = -1;

unsigned int i;

for (i = 0; i < ARRAY_SIZE(supported_modes); i++) {

dist = gc0403_get_reso_dist(&supported_modes[i], framefmt);

if (cur_best_fit_dist == -1 || dist < cur_best_fit_dist) {

cur_best_fit_dist = dist;

cur_best_fit = i;

}

}

return &supported_modes[cur_best_fit];

}

static int gc0403_set_fmt(struct v4l2_subdev *sd,

struct v4l2_subdev_pad_config *cfg,

struct v4l2_subdev_format *fmt)

{

struct gc0403 *gc0403 = to_gc0403(sd);

const struct gc0403_mode *mode;

mutex_lock(&gc0403->mutex);

mode = gc0403_find_best_fit(fmt);

fmt->format.code = MEDIA_BUS_FMT_SRGGB10_1X10;

fmt->format.width = mode->width;

fmt->format.height = mode->height;

fmt->format.field = V4L2_FIELD_NONE;

if (fmt->which == V4L2_SUBDEV_FORMAT_TRY) {

#ifdef CONFIG_VIDEO_V4L2_SUBDEV_API

*v4l2_subdev_get_try_format(sd, cfg, fmt->pad) = fmt->format;

#else

mutex_unlock(&gc0403->mutex);

return -ENOTTY;

#endif

} else {

gc0403->cur_mode = mode;

}

mutex_unlock(&gc0403->mutex);

return 0;

}

static int gc0403_get_fmt(struct v4l2_subdev *sd,

struct v4l2_subdev_pad_config *cfg,

struct v4l2_subdev_format *fmt)

{

struct gc0403 *gc0403 = to_gc0403(sd);

const struct gc0403_mode *mode = gc0403->cur_mode;

mutex_lock(&gc0403->mutex);

if (fmt->which == V4L2_SUBDEV_FORMAT_TRY) {

#ifdef CONFIG_VIDEO_V4L2_SUBDEV_API

fmt->format = *v4l2_subdev_get_try_format(sd, cfg, fmt->pad);

#else

mutex_unlock(&gc0403->mutex);

return -ENOTTY;

#endif

} else {

fmt->format.width = mode->width;

fmt->format.height = mode->height;

fmt->format.code = MEDIA_BUS_FMT_SRGGB10_1X10;

fmt->format.field = V4L2_FIELD_NONE;

}

mutex_unlock(&gc0403->mutex);

return 0;

}

static int gc0403_enum_mbus_code(struct v4l2_subdev *sd,

struct v4l2_subdev_pad_config *cfg,

struct v4l2_subdev_mbus_code_enum *code)

{

if (code->index != 0)

return -EINVAL;

code->code = MEDIA_BUS_FMT_SRGGB10_1X10;

return 0;

}

static int gc0403_enum_frame_sizes(struct v4l2_subdev *sd,

struct v4l2_subdev_pad_config *cfg,

struct v4l2_subdev_frame_size_enum *fse)

{

if (fse->index >= ARRAY_SIZE(supported_modes))

return -EINVAL;

if (fse->code != MEDIA_BUS_FMT_SRGGB10_1X10)

return -EINVAL;

fse->min_width = supported_modes[fse->index].width;

fse->max_width = supported_modes[fse->index].width;

fse->max_height = supported_modes[fse->index].height;

fse->min_height = supported_modes[fse->index].height;

return 0;

}

static int gc0403_g_frame_interval(struct v4l2_subdev *sd,

struct v4l2_subdev_frame_interval *fi)

{

struct gc0403 *gc0403 = to_gc0403(sd);

const struct gc0403_mode *mode = gc0403->cur_mode;

mutex_lock(&gc0403->mutex);

fi->interval = mode->max_fps;

mutex_unlock(&gc0403->mutex);

return 0;

}

static void gc0403_get_module_inf(struct gc0403 *gc0403,

struct rkmodule_inf *inf)

{

memset(inf, 0, sizeof(*inf));

strlcpy(inf->base.sensor, GC0403_NAME, sizeof(inf->base.sensor));

strlcpy(inf->base.module, gc0403->module_name,

sizeof(inf->base.module));

strlcpy(inf->base.lens, gc0403->len_name, sizeof(inf->base.lens));

}

static long gc0403_ioctl(struct v4l2_subdev *sd, unsigned int cmd, void *arg)

{

struct gc0403 *gc0403 = to_gc0403(sd);

long ret = 0;

switch (cmd) {

case RKMODULE_GET_MODULE_INFO:

gc0403_get_module_inf(gc0403, (struct rkmodule_inf *)arg);

break;

default:

ret = -ENOIOCTLCMD;

break;

}

return ret;

}

#ifdef CONFIG_COMPAT

static long gc0403_compat_ioctl32(struct v4l2_subdev *sd,

unsigned int cmd, unsigned long arg)

{

void __user *up = compat_ptr(arg);

struct rkmodule_inf *inf;

struct rkmodule_awb_cfg *cfg;

long ret;

switch (cmd) {

case RKMODULE_GET_MODULE_INFO:

inf = kzalloc(sizeof(*inf), GFP_KERNEL);

if (!inf) {

ret = -ENOMEM;

return ret;

}

ret = gc0403_ioctl(sd, cmd, inf);

if (!ret) {

ret = copy_to_user(up, inf, sizeof(*inf));

if (ret) {

ret = -EFAULT;

return ret;

}

}

kfree(inf);

break;

case RKMODULE_AWB_CFG:

cfg = kzalloc(sizeof(*cfg), GFP_KERNEL);

if (!cfg) {

ret = -ENOMEM;

return ret;

}

ret = copy_from_user(cfg, up, sizeof(*cfg));

if (!ret)

ret = gc0403_ioctl(sd, cmd, cfg);

else

ret = -EFAULT;

kfree(cfg);

break;

default:

ret = -ENOIOCTLCMD;

break;

}

return ret;

}

#endif

static int __gc0403_start_stream(struct gc0403 *gc0403)

{

int ret = 0;

/* In case these controls are set before streaming */

mutex_unlock(&gc0403->mutex);

ret = v4l2_ctrl_handler_setup(&gc0403->ctrl_handler);

mutex_lock(&gc0403->mutex);

if (ret)

return ret;

ret = gc0403_write_reg(gc0403->client, PAGE_SELECT_REG, 0x03);

ret |= gc0403_write_reg(gc0403->client, GC0403_REG_MIPI_EN, 0x90);

ret |= gc0403_write_reg(gc0403->client, PAGE_SELECT_REG, 0x00);

return ret;

}

static int __gc0403_stop_stream(struct gc0403 *gc0403)

{

int ret = 0;

ret = gc0403_write_reg(gc0403->client, PAGE_SELECT_REG, 0x03);

ret |= gc0403_write_reg(gc0403->client, GC0403_REG_MIPI_EN, 0x80);

ret |= gc0403_write_reg(gc0403->client, PAGE_SELECT_REG, 0x00);

return ret;

}

static int __gc0403_power_on(struct gc0403 *gc0403);

static void __gc0403_power_off(struct gc0403 *gc0403);

static int gc0403_s_power(struct v4l2_subdev *sd, int on)

{

struct gc0403 *gc0403 = to_gc0403(sd);

int ret = 0;

mutex_lock(&gc0403->mutex);

on = !!on;

if (on)

ret = pm_runtime_get_sync(&gc0403->client->dev);

else

ret = pm_runtime_put(&gc0403->client->dev);

mutex_unlock(&gc0403->mutex);

return ret;

}

static int gc0403_s_stream(struct v4l2_subdev *sd, int on)

{

struct gc0403 *gc0403 = to_gc0403(sd);

int ret = 0;

mutex_lock(&gc0403->mutex);

on = !!on;

if (on == gc0403->streaming)

goto unlock_and_return;

if (on) {

ret = __gc0403_start_stream(gc0403);

if (ret) {

v4l2_err(sd, "start stream failed while write regs\n");

goto unlock_and_return;

}

} else {

__gc0403_stop_stream(gc0403);

usleep_range(33 * 1000, 35 * 1000);

}

gc0403->streaming = on;

unlock_and_return:

mutex_unlock(&gc0403->mutex);

return ret;

}

/* Calculate the delay in us by clock rate and clock cycles */

static int __gc0403_power_on(struct gc0403 *gc0403)

{

int ret;

struct device *dev = &gc0403->client->dev;

ret = clk_set_rate(gc0403->xvclk, GC0403_XVCLK_FREQ);

if (ret < 0) {

dev_err(dev, "Failed to set xvclk rate (24MHz)\n");

return ret;

}

if (clk_get_rate(gc0403->xvclk) != GC0403_XVCLK_FREQ)

dev_warn(dev, "xvclk mismatched,modes are based on 24MHz\n");

ret = clk_prepare_enable(gc0403->xvclk);

if (ret < 0) {

dev_err(dev, "Failed to enable xvclk\n");

return ret;

}

ret = regulator_bulk_enable(GC0403_NUM_SUPPLIES, gc0403->supplies);

if (ret < 0) {

dev_err(dev, "Failed to enable regulators\n");

goto disable_clk;

}

if (!IS_ERR(gc0403->pwdn_gpio))

gpiod_set_value_cansleep(gc0403->pwdn_gpio, 0);

/* here usleep at least 10~15ms,will better */

usleep_range(10 * 1000, 15 * 1000);

ret = gc0403_write_array(gc0403->client, gc0403->cur_mode->reg_list);

if (ret)

return ret;

usleep_range(10 * 1000, 20 * 1000);

return 0;

disable_clk:

clk_disable_unprepare(gc0403->xvclk);

return ret;

}

static void __gc0403_power_off(struct gc0403 *gc0403)

{

if (!IS_ERR(gc0403->pwdn_gpio))

gpiod_set_value_cansleep(gc0403->pwdn_gpio, 1);

clk_disable_unprepare(gc0403->xvclk);

regulator_bulk_disable(GC0403_NUM_SUPPLIES, gc0403->supplies);

}

static int gc0403_runtime_resume(struct device *dev)

{

struct i2c_client *client = to_i2c_client(dev);

struct v4l2_subdev *sd = i2c_get_clientdata(client);

struct gc0403 *gc0403 = to_gc0403(sd);

int ret;

ret = __gc0403_power_on(gc0403);

if (ret)

return ret;

if (gc0403->streaming) {

ret = gc0403_s_stream(sd, 1);

if (ret)

__gc0403_power_off(gc0403);

}

return ret;

}

static int gc0403_runtime_suspend(struct device *dev)

{

struct i2c_client *client = to_i2c_client(dev);

struct v4l2_subdev *sd = i2c_get_clientdata(client);

struct gc0403 *gc0403 = to_gc0403(sd);

__gc0403_power_off(gc0403);

return 0;

}

#ifdef CONFIG_VIDEO_V4L2_SUBDEV_API

static int gc0403_open(struct v4l2_subdev *sd, struct v4l2_subdev_fh *fh)

{

struct gc0403 *gc0403 = to_gc0403(sd);

struct v4l2_mbus_framefmt *try_fmt =

v4l2_subdev_get_try_format(sd, fh->pad, 0);

const struct gc0403_mode *def_mode = &supported_modes[1];

mutex_lock(&gc0403->mutex);

/* Initialize try_fmt */

try_fmt->width = def_mode->width;

try_fmt->height = def_mode->height;

try_fmt->code = MEDIA_BUS_FMT_SRGGB10_1X10;

try_fmt->field = V4L2_FIELD_NONE;

mutex_unlock(&gc0403->mutex);

/* No crop or compose */

return 0;

}

#endif

static int gc0403_enum_frame_interval(struct v4l2_subdev *sd,

struct v4l2_subdev_pad_config *cfg,

struct v4l2_subdev_frame_interval_enum *fie)

{

if (fie->index >= ARRAY_SIZE(supported_modes))

return -EINVAL;

if (fie->code != MEDIA_BUS_FMT_SRGGB10_1X10)

return -EINVAL;

fie->width = supported_modes[fie->index].width;

fie->height = supported_modes[fie->index].height;

fie->interval = supported_modes[fie->index].max_fps;

return 0;

}

static const struct dev_pm_ops gc0403_pm_ops = {

SET_RUNTIME_PM_OPS(gc0403_runtime_suspend,

gc0403_runtime_resume, NULL)

};

#ifdef CONFIG_VIDEO_V4L2_SUBDEV_API

static const struct v4l2_subdev_internal_ops gc0403_internal_ops = {

.open = gc0403_open,

};

#endif

static struct v4l2_subdev_core_ops gc0403_core_ops = {

.s_power = gc0403_s_power,

.ioctl = gc0403_ioctl,

#ifdef CONFIG_COMPAT

.compat_ioctl32 = gc0403_compat_ioctl32,

#endif

};

static const struct v4l2_subdev_video_ops gc0403_video_ops = {

.s_stream = gc0403_s_stream,

.g_frame_interval = gc0403_g_frame_interval,

};

static const struct v4l2_subdev_pad_ops gc0403_pad_ops = {

.enum_mbus_code = gc0403_enum_mbus_code,

.enum_frame_size = gc0403_enum_frame_sizes,

.enum_frame_interval = gc0403_enum_frame_interval,

.get_fmt = gc0403_get_fmt,

.set_fmt = gc0403_set_fmt,

};

static const struct v4l2_subdev_ops gc0403_subdev_ops = {

.core = &gc0403_core_ops,

.video = &gc0403_video_ops,

.pad = &gc0403_pad_ops,

};

static int gc0403_set_ctrl(struct v4l2_ctrl *ctrl)

{

struct gc0403 *gc0403 = container_of(ctrl->handler,

struct gc0403, ctrl_handler);

struct i2c_client *client = gc0403->client;

int ret = 0;

int analog_gain_table[] = {100, 142, 250, 354, 490, 691, 970,

1363, 1945, 2704, 3889};

int table_cnt = 11;

int analog_gain_reg_value = 0x00;

int digital_gain_reg_value = 0x00;

int total_gain = 0;

int analog_gain = 0;

int i = 0;

if (pm_runtime_get(&client->dev) <= 0)

return 0;

switch (ctrl->id) {

case V4L2_CID_EXPOSURE:

dev_dbg(&client->dev,

"gc0403: V4L2_CID_EXPOSURE exp val = 0x%x\n",

ctrl->val);

/* 4 least significant bits of expsoure are fractional part */

ret = gc0403_write_reg(gc0403->client, GC0403_REG_EXP_H,

(ctrl->val >> 8) & 0x1f);

ret |= gc0403_write_reg(gc0403->client, GC0403_REG_EXP_L,

ctrl->val & 0xff);

break;

case V4L2_CID_ANALOGUE_GAIN:

case V4L2_CID_DIGITAL_GAIN:

total_gain = ctrl->val;

for (i = 0; i < table_cnt; i++) {

if (total_gain < analog_gain_table[i])

break;

}

i = i - 1;

if (i < 0)

i = 0;

analog_gain = analog_gain_table[i];

analog_gain_reg_value = i;

digital_gain_reg_value = total_gain * 64 / analog_gain;

if (analog_gain_reg_value < GC0403_ANALOG_GAIN_MIN)

analog_gain_reg_value = GC0403_ANALOG_GAIN_MIN;

if (analog_gain_reg_value > GC0403_ANALOG_GAIN_MAX)

analog_gain_reg_value = GC0403_ANALOG_GAIN_MAX;

if (digital_gain_reg_value < GC0403_DIGI_GAIN_MIN)

digital_gain_reg_value = GC0403_DIGI_GAIN_MIN;

if (digital_gain_reg_value > GC0403_DIGI_GAIN_MAX)

digital_gain_reg_value = GC0403_DIGI_GAIN_MAX;

ret = gc0403_write_reg(gc0403->client,

GC0403_REG_AGAIN,

GC0403_FETCH_ANALOG_GAIN

(analog_gain_reg_value));

ret |= gc0403_write_reg(gc0403->client,

GC0403_REG_DGAIN_H,

GC0403_FETCH_DIGITAL_GAIN_HIGH

(digital_gain_reg_value));

ret |= gc0403_write_reg(gc0403->client,

GC0403_REG_DGAIN_L,

GC0403_FETCH_DIGITAL_GAIN_LOW

(digital_gain_reg_value));

dev_dbg(&client->dev, "gc0403: gain: %d,a: %d,d: %d\n",

total_gain, analog_gain_reg_value,

digital_gain_reg_value);

break;

case V4L2_CID_VBLANK:

ret = gc0403_write_reg(gc0403->client, GC0403_REG_VBLK_H,

(ctrl->val) >> 8);

ret |= gc0403_write_reg(gc0403->client, GC0403_REG_VBLK_L,

(ctrl->val) & 0xff);

break;

default:

dev_warn(&client->dev, "%s Unhandled id:0x%x, val:0x%x\n",

__func__, ctrl->id, ctrl->val);

break;

}

pm_runtime_put(&client->dev);

return ret;

}

static const struct v4l2_ctrl_ops gc0403_ctrl_ops = {

.s_ctrl = gc0403_set_ctrl,

};

static int gc0403_initialize_controls(struct gc0403 *gc0403)

{

const struct gc0403_mode *mode;

struct v4l2_ctrl_handler *handler;

struct v4l2_ctrl *ctrl;

s64 vblank_def;

u32 h_blank;

int ret;

handler = &gc0403->ctrl_handler;

mode = gc0403->cur_mode;

ret = v4l2_ctrl_handler_init(handler, 5);

if (ret)

return ret;

handler->lock = &gc0403->mutex;

ctrl = v4l2_ctrl_new_int_menu(handler, NULL, V4L2_CID_LINK_FREQ,

0, 0, link_freq_menu_items);

if (ctrl)

ctrl->flags |= V4L2_CTRL_FLAG_READ_ONLY;

v4l2_ctrl_new_std(handler, NULL, V4L2_CID_PIXEL_RATE,

0, GC0403_PIXEL_RATE, 1, GC0403_PIXEL_RATE);

h_blank = mode->hts_def - mode->width;

gc0403->hblank = v4l2_ctrl_new_std(handler, NULL, V4L2_CID_HBLANK,

h_blank, h_blank, 1, h_blank);

if (gc0403->hblank)

gc0403->hblank->flags |= V4L2_CTRL_FLAG_READ_ONLY;

vblank_def = mode->vts_def - mode->height;

gc0403->vblank = v4l2_ctrl_new_std(handler, &gc0403_ctrl_ops,

V4L2_CID_VBLANK, vblank_def, vblank_def,

1, vblank_def);

gc0403->exposure = v4l2_ctrl_new_std(handler, &gc0403_ctrl_ops,

V4L2_CID_EXPOSURE,

GC0403_EXPOSURE_MIN, GC0403_EXPOSURE_MAX,

1, mode->exp_def);

/* Anolog gain */

gc0403->anal_gain = v4l2_ctrl_new_std(handler, &gc0403_ctrl_ops,

V4L2_CID_ANALOGUE_GAIN, GC0403_TOTAL_GAIN_MIN,

GC0403_TOTAL_GAIN_MAX, GC0403_TOTAL_GAIN_STEP,

GC0403_TOTAL_GAIN_MIN);

/* Digital gain */

gc0403->digi_gain = v4l2_ctrl_new_std(handler, &gc0403_ctrl_ops,

V4L2_CID_DIGITAL_GAIN, GC0403_TOTAL_GAIN_MIN,

GC0403_TOTAL_GAIN_MAX, GC0403_TOTAL_GAIN_STEP,

GC0403_TOTAL_GAIN_MIN);

if (handler->error) {

ret = handler->error;

dev_err(&gc0403->client->dev,

"Failed to init controls(%d)\n", ret);

goto err_free_handler;

}

gc0403->subdev.ctrl_handler = handler;

return 0;

err_free_handler:

v4l2_ctrl_handler_free(handler);

return ret;

}

static int gc0403_check_sensor_id(struct gc0403 *gc0403,

struct i2c_client *client)

{

struct device *dev = &gc0403->client->dev;

u8 pid = 0, ver = 0;

u16 id = 0;

int ret = 0;

/* Check sensor revision */

ret = gc0403_read_reg(client, GC0403_REG_CHIP_ID_H, &pid);

ret |= gc0403_read_reg(client, GC0403_REG_CHIP_ID_L, &ver);

if (ret) {

dev_err(&client->dev, "gc0403_read_reg failed (%d)\n", ret);

return ret;

}

id = SENSOR_ID(pid, ver);

if (id != GC0403_CHIP_ID) {

dev_err(&client->dev,

"Sensor detection failed (%04X,%d)\n",

id, ret);

return -ENODEV;

}

dev_info(dev, "Detected GC%04x sensor\n", id);

return 0;

}

static int gc0403_configure_regulators(struct gc0403 *gc0403)

{

unsigned int i;

for (i = 0; i < GC0403_NUM_SUPPLIES; i++)

gc0403->supplies[i].supply = gc0403_supply_names[i];

return devm_regulator_bulk_get(&gc0403->client->dev,

GC0403_NUM_SUPPLIES,

gc0403->supplies);

}

static int gc0403_probe(struct i2c_client *client,

const struct i2c_device_id *id)

{

struct device *dev = &client->dev;

/* add a dev_node */

struct device_node *node = dev->of_node;

struct gc0403 *gc0403;

struct v4l2_subdev *sd;

char facing[2];

int ret;

/* add info */

dev_info(dev, "driver version: %02x.%02x.%02x",

DRIVER_VERSION >> 16,

(DRIVER_VERSION & 0xff00) >> 8,

DRIVER_VERSION & 0x00ff);

gc0403 = devm_kzalloc(dev, sizeof(*gc0403), GFP_KERNEL);

if (!gc0403)

return -ENOMEM;

ret = of_property_read_u32(node, RKMODULE_CAMERA_MODULE_INDEX,

&gc0403->module_index);

ret |= of_property_read_string(node, RKMODULE_CAMERA_MODULE_FACING,

&gc0403->module_facing);

ret |= of_property_read_string(node, RKMODULE_CAMERA_MODULE_NAME,

&gc0403->module_name);

ret |= of_property_read_string(node, RKMODULE_CAMERA_LENS_NAME,

&gc0403->len_name);

if (ret) {

dev_err(dev, "could not get module information!\n");

return -EINVAL;

}

gc0403->client = client;

gc0403->cur_mode = &supported_modes[1];

gc0403->xvclk = devm_clk_get(dev, "xvclk");

if (IS_ERR(gc0403->xvclk)) {

dev_err(dev, "Failed to get xvclk\n");

return -EINVAL;

}

gc0403->pwdn_gpio = devm_gpiod_get(dev, "pwdn", GPIOD_OUT_LOW);

if (IS_ERR(gc0403->pwdn_gpio))

dev_warn(dev, "Failed to get pwdn-gpios\n");

ret = gc0403_configure_regulators(gc0403);

if (ret) {

dev_err(dev, "Failed to get power regulators\n");

return ret;

}

mutex_init(&gc0403->mutex);

sd = &gc0403->subdev;

v4l2_i2c_subdev_init(sd, client, &gc0403_subdev_ops);

ret = gc0403_initialize_controls(gc0403);

if (ret)

goto err_destroy_mutex;

ret = __gc0403_power_on(gc0403);

if (ret)

goto err_free_handler;

ret = gc0403_check_sensor_id(gc0403, client);

if (ret)

goto err_power_off;

#ifdef CONFIG_VIDEO_V4L2_SUBDEV_API

sd->internal_ops = &gc0403_internal_ops;

sd->flags |= V4L2_SUBDEV_FL_HAS_DEVNODE;

#endif

#if defined(CONFIG_MEDIA_CONTROLLER)

gc0403->pad.flags = MEDIA_PAD_FL_SOURCE;

sd->entity.type = MEDIA_ENT_T_V4L2_SUBDEV_SENSOR;

ret = media_entity_init(&sd->entity, 1, &gc0403->pad, 0);

if (ret < 0)

goto err_power_off;

#endif

memset(facing, 0, sizeof(facing));

if (strcmp(gc0403->module_facing, "back") == 0)

facing[0] = 'b';

else

facing[0] = 'f';

snprintf(sd->name, sizeof(sd->name), "m%02d_%s_%s %s",

gc0403->module_index, facing,

GC0403_NAME, dev_name(sd->dev));

ret = v4l2_async_register_subdev(sd);

if (ret) {

dev_err(dev, "v4l2 async register subdev failed\n");

goto err_clean_entity;

}

pm_runtime_set_active(dev);

pm_runtime_enable(dev);

pm_runtime_idle(dev);

return 0;

err_clean_entity:

#if defined(CONFIG_MEDIA_CONTROLLER)

media_entity_cleanup(&sd->entity);

#endif

err_power_off:

__gc0403_power_off(gc0403);

err_free_handler:

v4l2_ctrl_handler_free(&gc0403->ctrl_handler);

err_destroy_mutex:

mutex_destroy(&gc0403->mutex);

return ret;

}

static int gc0403_remove(struct i2c_client *client)

{

struct v4l2_subdev *sd = i2c_get_clientdata(client);

struct gc0403 *gc0403 = to_gc0403(sd);

v4l2_async_unregister_subdev(sd);

#if defined(CONFIG_MEDIA_CONTROLLER)

media_entity_cleanup(&sd->entity);

#endif

v4l2_ctrl_handler_free(&gc0403->ctrl_handler);

mutex_destroy(&gc0403->mutex);

pm_runtime_disable(&client->dev);

if (!pm_runtime_status_suspended(&client->dev))

__gc0403_power_off(gc0403);

pm_runtime_set_suspended(&client->dev);

return 0;

}

#if IS_ENABLED(CONFIG_OF)

static const struct of_device_id gc0403_of_match[] = {

{ .compatible = "galaxycore,gc0403" },

{},

};

MODULE_DEVICE_TABLE(of, gc0403_of_match);

#endif

static const struct i2c_device_id gc0403_match_id[] = {

{ "gc0403", 0 },

{ },

};

static struct i2c_driver gc0403_i2c_driver = {

.driver = {

.name = "gc0403",

.pm = &gc0403_pm_ops,

.of_match_table = of_match_ptr(gc0403_of_match),

},

.probe = &gc0403_probe,

.remove = &gc0403_remove,

.id_table = gc0403_match_id,

};

static int __init sensor_mod_init(void)

{

return i2c_add_driver(&gc0403_i2c_driver);

}

static void __exit sensor_mod_exit(void)

{

i2c_del_driver(&gc0403_i2c_driver);

}

device_initcall_sync(sensor_mod_init);

module_exit(sensor_mod_exit);

MODULE_DESCRIPTION("Galaxycore gc0403 sensor driver");

MODULE_LICENSE("GPL v2");离线

楼主 #4 2021-04-28 16:15:41 分享评论

Re: 淘宝V3s摄像头(防瞌睡? 检测司机打电话?)卡在gc0403驱动,有能力继续研究的朋友送两台拆解,跟帖或者联系微信 whycan_cn

开始hack, 首先从bin文件获取 sys_config.bin文件:

dd if=flash_16m_n25q128.bin of=sys_config.bin bs=1 skip=$((0x32000)) count=$((0x3b000-0x32000))

36864+0 records in

36864+0 records out

36864 bytes (37 kB, 36 KiB) copied, 0.701018 s, 52.6 kB/s然后用 bin2fex 工具把 sys_config.bin 转成 sys_config.fex

/sunxi-tools$ ./bin2fex -vq /mnt/hgfs/F/sys_config.bin /mnt/hgfs/F/sys_config.fex

fexc-bin: /mnt/hgfs/F/sys_config.bin: version: 1.2

fexc-bin: /mnt/hgfs/F/sys_config.bin: size: 36864 (65 sections), header value: 33368

fexc-bin: Warning: Malformed entry key "vdd-cpua"

fexc-bin: Warning: Malformed entry key "vdd-sys"

fexc-bin: Warning: Malformed entry key ": If set gamc_phy to use"sys_config.fex 内容:

[product]

version = "100"

machine = "tiger-rw1002"

[platform]

eraseflag = 0

[target]

boot_clock = 1008

storage_type = -1

[boot_spi_board0]

boot_spi_speed_hz = 60000000

speed_mod = 1

[power_sply]

dcdc2_vol = 1100

dcdc3_vol = 1800

aldo2_vol = 2500

aldo3_vol = 3000

ldo1_vol = 3300

ldo2_vol = 3000

ldo3_vol = 3000

[axp15_para]

dcdc1_vol = 3300

dcdc2_vol = 1100

dcdc3_vol = 1800

dcdc4_vol = 1800

aldo1_vol = 3000

aldo2_vol = 3000

dldo1_vol = 3000

[card_boot]

logical_start = 40960

sprite_gpio0 =

[card0_boot_para]

card_ctrl = 0

card_high_speed = 1

card_line = 4

sdc_d1 = port:PF00<2><1><default><default>

sdc_d0 = port:PF01<2><1><default><default>

sdc_clk = port:PF02<2><1><default><default>

sdc_cmd = port:PF03<2><1><default><default>

sdc_d3 = port:PF04<2><1><default><default>

sdc_d2 = port:PF05<2><1><default><default>

[twi_para]

twi_port = 0

twi_scl = port:PB06<2><default><default><default>

twi_sda = port:PB07<2><default><default><default>

[uart_para]

uart_debug_port = 2

uart_debug_tx = port:PB00<2><1><default><default>

uart_debug_rx = port:PB01<2><1><default><default>

[jtag_para]

jtag_enable = 0

jtag_ms = port:PF00<3><default><default><default>

jtag_ck = port:PF05<3><default><default><default>

jtag_do = port:PF03<3><default><default><default>

jtag_di = port:PF01<3><default><default><default>

[clock]

pll3 = 297

pll4 = 300

pll6 = 600

pll8 = 360

pll9 = 480

pll10 = 297

[pm_para]

standby_mode = 1

[sys_pwr_dm_para]

vdd-cpua = 1

vdd-sys = 1

[dynamic_standby_para]

enable = 0

dram_selfresh_flag = 1

vdd_cpua_vol = 1200

vdd_sys_vol = 1200

[dram_para]

dram_clk = 408

dram_type = 2

dram_zq = 0x39bb

dram_odt_en = 0

dram_para1 = 283246592

dram_para2 = 0

dram_mr0 = 6208

dram_mr1 = 4

dram_mr2 = 24

dram_mr3 = 4

dram_tpr0 = 0x832087

dram_tpr1 = 0x1c24085

dram_tpr2 = 0x2a01d

dram_tpr3 = 0x0

dram_tpr4 = 0x0

dram_tpr5 = 0x0

dram_tpr6 = 0x0

dram_tpr7 = 0x0

dram_tpr8 = 0x0

dram_tpr9 = 0x0

dram_tpr10 = 0x0

dram_tpr11 = 0x220000

dram_tpr12 = 0x78

dram_tpr13 = 0xd000000

[pm_para]

standby_mode = 0

[wakeup_src_para]

cpu_en = 0

cpu_freq = 48

pll_ratio = 273

dram_selfresh_en = 1

dram_freq = 36

wakeup_src_wl = port:PL07<4><default><default><0>

wakeup_src_bt = port:PL09<4><default><default><0>

bb_wake_ap = port:PL02<4><default><default><0>

[twi0]

twi_used = 1

twi_scl = port:PB06<2><default><default><default>

twi_sda = port:PB07<2><default><default><default>

[twi1]

twi_used = 0

twi_scl = port:PB08<2><default><default><default>

twi_sda = port:PB09<2><default><default><default>

[uart0]

uart_used = 1

uart_type = 2

uart_tx = port:PF02<3><1><1><default>

uart_rx = port:PF04<3><1><1><default>

[uart1]

uart_used = 0

uart_type = 2

uart_tx = port:PE21<4><1><default><default>

uart_rx = port:PE22<4><1><default><default>

[uart2]

uart_used = 1

uart_type = 2

uart_tx = port:PB00<2><1><default><default>

uart_rx = port:PB01<2><1><default><default>

[spi0]

spi_used = 1

spi_cs_bitmap = 1

spi_mosi = port:PC03<3><default><default><default>

spi_miso = port:PC00<3><default><default><default>

spi_sclk = port:PC01<3><default><default><default>

spi_cs0 = port:PC02<3><1><default><default>

[spi_devices]

spi_dev_num = 1

[spi_board0]

modalias = "gd25q128"

max_speed_hz = 50000000

bus_num = 0

chip_select = 0

mode = 0

sflash_size = 16

[ctp_para]

ctp_used = 0

ctp_name = "gt911_m785q6"

ctp_twi_id = 1

ctp_twi_addr = 0x5d

ctp_screen_max_x = 800

ctp_screen_max_y = 480

ctp_revert_x_flag = 0

ctp_revert_y_flag = 0

ctp_exchange_x_y_flag = 1

ctp_int_port = port:PG04<6><default><default><default>

ctp_wakeup = port:PG03<1><default><default><1>

[ctp_list_para]

ctp_det_used = 0

gt911_ts = 1

ft5x_ts = 1

gt82x = 1

gslX680 = 1

gt9xx_ts = 1

gt811 = 1

zet622x = 1

aw5306_ts = 1

[tkey_para]

tkey_used = 0

tkey_twi_id =

tkey_twi_addr =

tkey_int =

[motor_para]

motor_used = 0

motor_shake = port:power3<1><default><default><1>

[cooler_table]

cooler_count = 4

cooler0 = "1340000 4 4294967295 0"

cooler1 = "1200000 4 4294967295 0"

cooler2 = "1008000 4 4294967295 0"

cooler3 = "648000 4 4294967295 0"

[disp_init]

disp_init_enable = 0

disp_mode = 0

screen0_output_type = 1

screen0_output_mode = 4

screen1_output_type = 1

screen1_output_mode = 4

fb0_format = 0

fb0_pixel_sequence = 0

fb0_scaler_mode_enable = 0

fb0_width = 0

fb0_height = 0

fb1_format = 0

fb1_pixel_sequence = 0

fb1_scaler_mode_enable = 0

fb1_width = 0

fb1_height = 0

lcd0_backlight = 200

lcd1_backlight = 50

lcd0_bright = 50

lcd0_contrast = 50

lcd0_saturation = 57

lcd0_hue = 50

lcd1_bright = 50

lcd1_contrast = 50

lcd1_saturation = 57

lcd1_hue = 50

[lcd0_para]

lcd_used = 0

lcd_driver_name = "t27p06"

lcd_if = 0

lcd_x = 320

lcd_y = 480

lcd_width = 108

lcd_height = 64

lcd_dclk_freq = 48

lcd_pwm_used = 1

lcd_pwm_ch = 0

lcd_pwm_freq = 50000

lcd_pwm_pol = 1

lcd_pwm_max_limit = 255

lcd_hbp = 40

lcd_ht = 1440

lcd_hspw = 1

lcd_vbp = 42

lcd_vt = 525

lcd_vspw = 1

lcd_frm = 0

lcd_hv_clk_phase = 0

lcd_hv_sync_polarity = 0

lcd_gamma_en = 0

lcd_bright_curve_en = 1

lcd_cmap_en = 0

lcd_hv_if = 11

lcd_hv_srgb_seq = 0

lcd_rb_swap = 0

lcdgamma4iep = 22

lcd_bl_en = port:PE13<1><0><default><1>

lcd_power = ""

lcd_gpio_3 = port:PE14<1><0><default><1>

lcd_gpio_0 = port:PE15<1><0><default><1>

lcd_gpio_2 = port:PE16<1><0><default><1>

lcdd3 = port:PE05<3><0><default><default>

lcdd4 = port:PE06<3><0><default><default>

lcdd5 = port:PE07<3><0><default><default>

lcdd6 = port:PE08<3><0><default><default>

lcdd7 = port:PE09<3><0><default><default>

lcdd10 = port:PE10<3><0><default><default>

lcdd11 = port:PE11<3><0><default><default>

lcdd12 = port:PE12<3><0><default><default>

lcdclk = port:PE00<3><0><3><default>

lcdhsync = port:PE02<3><0><3><default>

lcdvsync = port:PE03<3><0><3><default>

[pwm0_para]

pwm_used = 0

pwm_positive = port:PB04<2><0><default><default>

[pwm1_para]

pwm_used = 0

pwm_positive = port:PH01<2><0><default><default>

: If set gamc_phy to use = 0

[gmac0]

gmac_used = 0

gmac_power1 =

[csi0]

vip_used = 0

vip_mode = 0

vip_dev_qty = 1

vip_define_sensor_list = 0

vip_csi_pck = port:PE00<2><default><default><default>

vip_csi_mck = port:PE20<3><default><default><default>

vip_csi_sck = port:PE21<2><default><default><default>

vip_csi_sda = port:PE22<2><default><default><default>

vip_csi_hsync = port:PE02<2><default><default><default>

vip_csi_vsync = port:PE03<2><default><default><default>

vip_csi_d0 = port:PE08<2><default><default><default>

vip_csi_d1 = port:PE09<2><default><default><default>

vip_csi_d2 = port:PE10<2><default><default><default>

vip_csi_d3 = port:PE11<2><default><default><default>

vip_csi_d4 = port:PE12<2><default><default><default>

vip_csi_d5 = port:PE13<2><default><default><default>

vip_csi_d6 = port:PE14<2><default><default><default>

vip_csi_d7 = port:PE15<2><default><default><default>

vip_dev0_mname = "nt99141"

vip_dev0_pos = "rear"

vip_dev0_lane = 1

vip_dev0_twi_id = 0

vip_dev0_twi_addr = 84

vip_dev0_isp_used = 0

vip_dev0_fmt = 0

vip_dev0_stby_mode = 0

vip_dev0_vflip = 1

vip_dev0_hflip = 1

vip_dev0_iovdd = ""

vip_dev0_iovdd_vol = 3000000

vip_dev0_avdd = "axp15_aldo2"

vip_dev0_avdd_vol = 3000000

vip_dev0_dvdd = "axp15_dcdc4"

vip_dev0_dvdd_vol = 1500000

vip_dev0_afvdd = ""

vip_dev0_afvdd_vol = 2800000

vip_dev0_power_en =

vip_dev0_reset = port:PE16<1><default><default><default>

vip_dev0_pwdn = port:PE17<1><default><default><default>

vip_dev0_flash_en =

vip_dev0_flash_mode =

vip_dev0_af_pwdn =

vip_dev0_act_used = 0

vip_dev0_act_name = ""

vip_dev0_act_slave = 0

vip_dev1_mname = ""

vip_dev1_pos = "front"

vip_dev1_lane = 1

vip_dev1_twi_id = 0

vip_dev1_twi_addr =

vip_dev1_isp_used = 0

vip_dev1_fmt = 1

vip_dev1_stby_mode = 0

vip_dev1_vflip = 0

vip_dev1_hflip = 0

vip_dev1_iovdd = ""

vip_dev1_iovdd_vol = 2800000

vip_dev1_avdd = ""

vip_dev1_avdd_vol = 2800000

vip_dev1_dvdd = ""

vip_dev1_dvdd_vol = 1500000

vip_dev1_afvdd = ""

vip_dev1_afvdd_vol = 2800000

vip_dev1_power_en =

vip_dev1_reset =

vip_dev1_pwdn =

vip_dev1_flash_en =

vip_dev1_flash_mode =

vip_dev1_af_pwdn =

[csi1]

vip_used = 1

vip_mode = 0

vip_dev_qty = 1

vip_define_sensor_list = 1

vip_csi_pck = port:PE00<2><default><default><default>

vip_csi_mck = port:PE20<3><default><default><default>

vip_csi_sck = port:PE21<2><default><default><default>

vip_csi_sda = port:PE22<2><default><default><default>

vip_csi_hsync = port:PE02<2><default><default><default>

vip_csi_vsync = port:PE03<2><default><default><default>

vip_csi_d0 = port:PE08<2><default><default><default>

vip_csi_d1 = port:PE09<2><default><default><default>

vip_csi_d2 = port:PE10<2><default><default><default>

vip_csi_d3 = port:PE11<2><default><default><default>

vip_csi_d4 = port:PE12<2><default><default><default>

vip_csi_d5 = port:PE13<2><default><default><default>

vip_csi_d6 = port:PE14<2><default><default><default>

vip_csi_d7 = port:PE15<2><default><default><default>

vip_dev0_mname = "gc0403"

vip_dev0_pos = "rear"

vip_dev0_twi_id = 0

vip_dev0_twi_addr = 120

vip_dev0_isp_used = 1

vip_dev0_fmt = 1

vip_dev0_stby_mode = 0

vip_dev0_vflip = 1

vip_dev0_hflip = 1

vip_dev0_iovdd = ""

vip_dev0_iovdd_vol = 3000000

vip_dev0_avdd = "axp15_aldo2"

vip_dev0_avdd_vol = 3000000

vip_dev0_dvdd = "axp15_dcdc4"

vip_dev0_dvdd_vol = 1800000

vip_dev0_afvdd = ""

vip_dev0_afvdd_vol = 2800000

vip_dev0_power_en =

vip_dev0_reset = port:PE16<1><default><default><default>

vip_dev0_pwdn = port:PE17<1><default><default><default>

vip_dev0_flash_en =

vip_dev0_flash_mode =

vip_dev0_af_pwdn =

vip_dev0_act_used = 0

vip_dev0_act_name = ""

vip_dev0_act_slave = 0

vip_dev1_mname = "gc2035"

vip_dev1_pos = "front"

vip_dev1_lane = 1

vip_dev1_twi_id = 4

vip_dev1_twi_addr = 120

vip_dev1_isp_used = 0

vip_dev1_fmt = 1

vip_dev1_stby_mode = 0

vip_dev1_vflip = 0

vip_dev1_hflip = 0

vip_dev1_iovdd = ""

vip_dev1_iovdd_vol = 2800000

vip_dev1_avdd = ""

vip_dev1_avdd_vol = 2800000

vip_dev1_dvdd = ""

vip_dev1_dvdd_vol = 1500000

vip_dev1_afvdd = ""

vip_dev1_afvdd_vol = 2800000

vip_dev1_power_en =

vip_dev1_reset =

vip_dev1_pwdn =

vip_dev1_flash_en =

vip_dev1_flash_mode =

vip_dev1_af_pwdn =

[mmc0_para]

sdc_used = 0

sdc_detmode = 1

sdc_buswidth = 4

sdc_d1 = port:PF00<2><1><2><default>

sdc_d0 = port:PF01<2><1><2><default>

sdc_clk = port:PF02<2><1><2><default>

sdc_cmd = port:PF03<2><1><2><default>

sdc_d3 = port:PF04<2><1><2><default>

sdc_d2 = port:PF05<2><1><2><default>

sdc_det = port:PF06<0><1><default><default>

sdc_use_wp = 0

sdc_wp =

sdc_isio = 0

sdc_regulator = "none"

[mmc1_para]

sdc_used = 0

sdc_detmode = 4

sdc_buswidth = 4

sdc_clk = port:PG00<2><1><2><default>

sdc_cmd = port:PG01<2><1><2><default>

sdc_d0 = port:PG02<2><1><2><default>

sdc_d1 = port:PG03<2><1><2><default>

sdc_d2 = port:PG04<2><1><2><default>

sdc_d3 = port:PG05<2><1><2><default>

sdc_det =

sdc_use_wp = 0

sdc_wp =

sdc_isio = 1

sdc_regulator = "none"

[mmc2_para]

sdc_used = 0

sdc_detmode = 3

sdc_buswidth = 8

sdc_clk = port:PC00<2><1><2><default>

sdc_cmd = port:PC01<2><1><2><default>

sdc_d0 = port:PC03<2><1><2><default>

sdc_d1 = port:PC04<2><1><2><default>

sdc_d2 = port:PC05<2><1><2><default>

sdc_d3 = port:PC06<2><1><2><default>

sdc_d4 = port:PC07<2><1><2><default>

sdc_d5 = port:PC08<2><1><2><default>

sdc_d6 = port:PC09<2><1><2><default>

sdc_d7 = port:PC10<2><1><2><default>

emmc_rst = port:PC02<2><1><2><default>

sdc_det =

sdc_use_wp = 0

sdc_wp =

sdc_isio = 0

sdc_regulator = "none"

[usbc0]

usb_used = 1

usb_port_type = 0

usb_detect_type = 0

usb_id_gpio =

usb_det_vbus_gpio =

usb_drv_vbus_gpio =

usb_restrict_gpio =

usb_host_init_state = 0

usb_restric_flag = 0

usb_restric_voltage = 3550000

usb_restric_capacity = 5

usb_regulator_io = "nocare"

usb_regulator_vol = 0

usb_not_suspend = 0

[usb_feature]

vendor_id = 6353

mass_storage_id = 1

adb_id = 2

manufacturer_name = "USB Developer"

product_name = "Android"

serial_number = "20080411"

[msc_feature]

vendor_name = "USB 2.0"

product_name = "USB Flash Driver"

release = 100

luns = 1

[serial_feature]

serial_unique = 0

[gsensor_para]

gsensor_used = 0

gsensor_twi_id = 1

gsensor_twi_addr = 0x27

gsensor_int1 =

gsensor_int2 =

[gsensor_list_para]

gsensor_det_used = 0

bma250 = 1

da380 = 1

mma8452 = 1

mma7660 = 1

mma865x = 1

afa750 = 1

lis3de_acc = 1

lis3dh_acc = 1

kxtik = 1

dmard10 = 0

dmard06 = 1

mxc622x = 1

fxos8700 = 1

lsm303d = 1

[gps_para]

[module_para]

module_num = 1

module_power0 =

module_power0_vol =

module_power1 =

module_power1_vol =

module_power2 =

module_power2_vol =

module_power3 =

module_power3_vol =

chip_en =

[wifi_para]

wifi_used = 0

wifi_sdc_id = 1

wifi_usbc_id = 0

wifi_usbc_type = 1

wifi_mod_sel = 1

wl_reg_on = port:PE17<1><default><default><0>

wl_host_wake_invert = 0

[ls_para]

ls_used = 0

ls_twi_id = 1

ls_twi_addr = 35

ls_int = port:PB07<4><1><default><default>

[ls_list_para]

ls_det_used = 0

ltr_501als = 1

jsa1212 = 1

[compass_para]

compass_used = 0

compass_twi_id = 1

compass_twi_addr = 13

compass_int =

[tdm0]

daudio_used = 0

daudio_master = 4

daudio_select = 1

audio_format = 1

signal_inversion = 1

mclk_fs = 512

sample_resolution = 16

slot_width_select = 16

pcm_lrck_period = 32

pcm_lrckr_period = 1

msb_lsb_first = 0

sign_extend = 0

slot_index = 0

slot_width = 16

frame_width = 1

tx_data_mode = 0

rx_data_mode = 0

i2s_bclk = port:PG11<2><1><default><default>

i2s_lrclk = port:PG10<2><1><default><default>

i2s_dout0 = port:PG12<2><1><default><default>

i2s_dout1 =

i2s_dout2 =

i2s_dout3 =

i2s_din = port:PG13<2><1><default><default>

[audio0]

audio_used = 1

headphone_vol = 59

cap_vol = 5

Differential_output = 1

pa_single_vol = 63

pa_double_used = 0

pa_double_vol = 31

headphone_direct_used = 0

phone_mic_vol = 6

version_v3_used = 0

headphone_mute_used = 0

audio_hp_ldo = "none"

audio_pa_ctrl = port:PE18<1><default><default><0>

adcagc_used = 0

adcdrc_used = 0

dacdrc_used = 0

adchpf_used = 0

dachpf_used = 0

[s_ir0]

ir_used = 0

ir_rx = port:PL04<2><1><default><default>

[pmu1_para]

pmu_used = 1

pmu_id = 1

pmu_twi_addr = 48

pmu_twi_id = 0

pmu_irq_id = 64

pmu_irq_gpio = port:PG02<6><default><default><default>

pmu_battery_rdc = 249

pmu_battery_cap = 183

pmu_batdeten = 1

pmu_runtime_chgcur = 300

pmu_earlysuspend_chgcur = 300

pmu_suspend_chgcur = 300

pmu_shutdown_chgcur = 300

pmu_init_chgvol = 4200

pmu_init_chgend_rate = 15

pmu_init_chg_enabled = 1

pmu_init_adc_freq = 100

pmu_init_chg_pretime = 50

pmu_init_chg_csttime = 720

pmu_bat_para1 = 0

pmu_bat_para2 = 0

pmu_bat_para3 = 0

pmu_bat_para4 = 0

pmu_bat_para5 = 8

pmu_bat_para6 = 16

pmu_bat_para7 = 25

pmu_bat_para8 = 37

pmu_bat_para9 = 47

pmu_bat_para10 = 55

pmu_bat_para11 = 61

pmu_bat_para12 = 68

pmu_bat_para13 = 79

pmu_bat_para14 = 87

pmu_bat_para15 = 94

pmu_bat_para16 = 100

pmu_usbvol_limit = 1

pmu_usbcur_limit = 0

pmu_usbvol = 4000

pmu_usbcur = 0

pmu_usbvol_pc = 4000

pmu_usbcur_pc = 0

pmu_pwroff_vol = 3300

pmu_pwron_vol = 2900

pmu_pekoff_time = 6000

pmu_pekoff_en = 1

pmu_peklong_time = 1500

pmu_pekon_time = 1000

pmu_pwrok_time = 64

pmu_pwrnoe_time = 2000

pmu_hot_shutdown = 1

pmu_suspendpwroff_vol = 3500

power_start = 3

[pmu1_regu]

regulator_count = 7

regulator1 = "axp20_dcdc2 none vdd-sys vdd-cpu vdd-ephy"

regulator2 = "axp20_dcdc3 none vcc-io hpvcc vcc-pd vcc-usb vcc-ephy vcc-mcsi vcc-lcd vcc-wifi vcc-device vcc-csi vcc-ctp"

regulator3 = "axp20_ldo1 none vcc-rtc"

regulator4 = "axp20_ldo2 none vcc-avcc vcc-pll"

regulator5 = "axp20_ldo3 none vcc-pe csi-avdd"

regulator6 = "axp20_ldo4 none csi-dvdd"

regulator7 = "axp20_ldoio0 none"

[dvfs_table]

extremity_freq = 1008000000

max_freq = 1008000000

min_freq = 60000000

LV_count = 8

LV1_freq = 1008000000

LV1_volt = 1200

LV2_freq = 1008000000

LV2_volt = 1200

LV3_freq = 940000000

LV3_volt = 1200

LV4_freq = 940000000

LV4_volt = 1200

LV5_freq = 816000000

LV5_volt = 1100

LV6_freq = 648000000

LV6_volt = 1040

LV7_freq = 0

LV7_volt = 1040

LV8_freq = 0

LV8_volt = 1040

[Vdevice]

Vdevice_used = 1

Vdevice_0 = port:PA01<5><1><2><default>

Vdevice_1 = port:PA02<5><1><2><default>

[dram_dvfs_table]

LV_count = 3

LV1_freq = 552000000

LV1_volt = 1100

LV2_freq = 360000000

LV2_volt = 1000

LV3_freq = 0

LV3_volt = 1000

[fel_key]

fel_key_used = 1

fel_key_min = 0

fel_key_max = 60

[leds_para]

leds_used = 0

led_0 = port:PB08<1><default><default><0>

led_0_active_low = 0

led_1 = port:PB09<1><default><default><0>

led_1_active_low = 0

[nv906_para]

nv906_used = 1

nv906_gpio = port:PB09<1><1><default><1>

[irled_para]

irled_used = 1

irled_enable = port:PG03<1><default><default><1>sys_config.bin & sys_config.fex 下载: sys_config_bin_fex.7z

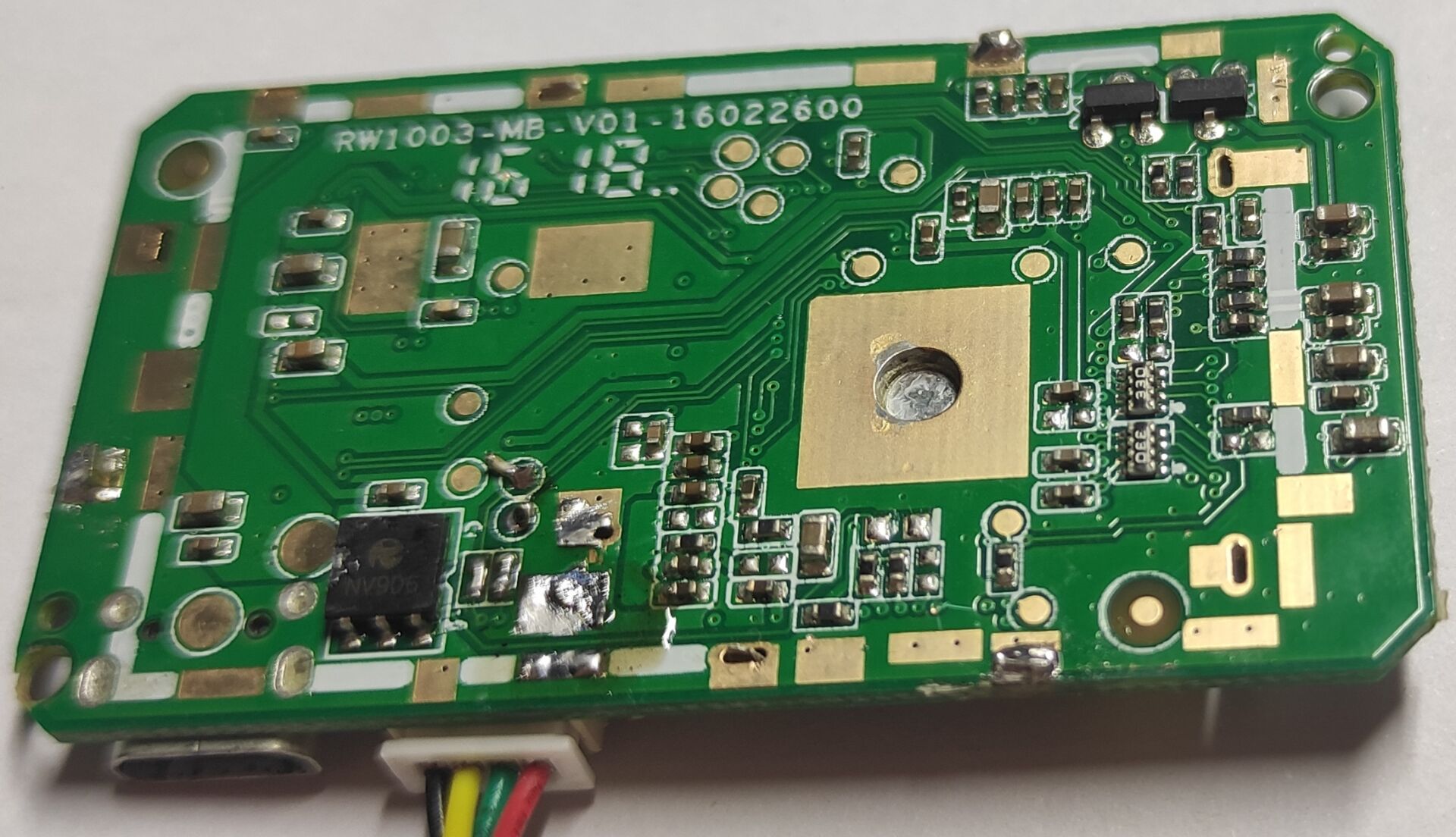

由 sys_confex.fex 可以看出,

调试串口使用 uart2 (PB0/PB1), 应该在板子背面的pad上,

应用串口在 uart0(PF2/PF4), 1.25mm排针引出,

I2C0被启动, 使用 PB6/PB7, 连接AXP152

I2C1被启动, 使用 PE21/PE22, 连接GC0403摄像头

摄像头复位脚 PE16, 使能脚PE17

DVP摄像头型号 gc0403, 开启了ISP

USB被开启,无切换id引脚,

PMU芯片接V3s PG02作为中断脚

NV906应该是单线加密芯片, 引脚是PB9

红外灯控制IO是PG03

uboot里面给PG3 高/低电平, LED都不亮, 看来没有他喜欢的电平?

=> gpio set pg3 0

gpio: pin pg3 (gpio 195) value is 1

=> gpio clear pg3

gpio: pin pg3 (gpio 195) value is 0或者说灯坏了,所以进了淘宝?

更新 ->

-----------------------------

失误失误,并没有坏,肉眼几乎看不见,要手机摄像头才能看到红外光

离线

楼主 #5 2021-04-28 17:10:32 分享评论

Re: 淘宝V3s摄像头(防瞌睡? 检测司机打电话?)卡在gc0403驱动,有能力继续研究的朋友送两台拆解,跟帖或者联系微信 whycan_cn

编译主线 u-boot

克隆 v2020.04

git clone https://github.com/u-boot/u-boot.git

cd u-boot

git reset --hard v2020.04配置文件.config

#

# Automatically generated file; DO NOT EDIT.

# U-Boot 2020.04 Configuration

#

CONFIG_CREATE_ARCH_SYMLINK=y

# CONFIG_ARC is not set

CONFIG_ARM=y

# CONFIG_M68K is not set

# CONFIG_MICROBLAZE is not set

# CONFIG_MIPS is not set

# CONFIG_NDS32 is not set

# CONFIG_NIOS2 is not set

# CONFIG_PPC is not set

# CONFIG_RISCV is not set

# CONFIG_SANDBOX is not set

# CONFIG_SH is not set

# CONFIG_X86 is not set

# CONFIG_XTENSA is not set

CONFIG_SYS_ARCH="arm"

CONFIG_SYS_CPU="armv7"

CONFIG_SYS_SOC="sunxi"

CONFIG_SYS_BOARD="sunxi"

CONFIG_SYS_CONFIG_NAME="sun8i"

# CONFIG_SYS_ICACHE_OFF is not set

# CONFIG_SPL_SYS_ICACHE_OFF is not set

# CONFIG_SYS_DCACHE_OFF is not set

# CONFIG_SPL_SYS_DCACHE_OFF is not set

#

# ARM architecture

#

# CONFIG_GIC_V3_ITS is not set

CONFIG_HAS_VBAR=y

CONFIG_HAS_THUMB2=y

CONFIG_ARM_ASM_UNIFIED=y

CONFIG_SYS_ARM_CACHE_CP15=y

CONFIG_SYS_ARM_MMU=y

# CONFIG_SYS_ARM_MPU is not set

CONFIG_CPU_V7A=y

CONFIG_SYS_ARM_ARCH=7

CONFIG_SYS_CACHE_SHIFT_6=y

CONFIG_SYS_CACHELINE_SIZE=64

# CONFIG_ARCH_CPU_INIT is not set

# CONFIG_SYS_ARCH_TIMER is not set

# CONFIG_ARM_SMCCC is not set

# CONFIG_SEMIHOSTING is not set

CONFIG_SYS_THUMB_BUILD=y

CONFIG_SPL_SYS_THUMB_BUILD=y

# CONFIG_SYS_L2CACHE_OFF is not set

# CONFIG_ENABLE_ARM_SOC_BOOT0_HOOK is not set

CONFIG_USE_ARCH_MEMCPY=y

CONFIG_SPL_USE_ARCH_MEMCPY=y

CONFIG_USE_ARCH_MEMSET=y

CONFIG_SPL_USE_ARCH_MEMSET=y

# CONFIG_SET_STACK_SIZE is not set

# CONFIG_ARCH_AT91 is not set

# CONFIG_TARGET_EDB93XX is not set

# CONFIG_TARGET_ASPENITE is not set

# CONFIG_TARGET_GPLUGD is not set

# CONFIG_ARCH_DAVINCI is not set

# CONFIG_KIRKWOOD is not set

# CONFIG_ARCH_MVEBU is not set

# CONFIG_TARGET_APF27 is not set

# CONFIG_ORION5X is not set

# CONFIG_TARGET_SPEAR300 is not set

# CONFIG_TARGET_SPEAR310 is not set

# CONFIG_TARGET_SPEAR320 is not set

# CONFIG_TARGET_SPEAR600 is not set

# CONFIG_TARGET_STV0991 is not set

# CONFIG_TARGET_X600 is not set

# CONFIG_TARGET_FLEA3 is not set

# CONFIG_TARGET_MX35PDK is not set

# CONFIG_ARCH_BCM283X is not set

# CONFIG_ARCH_BCM63158 is not set

# CONFIG_ARCH_BCM68360 is not set

# CONFIG_ARCH_BCM6858 is not set

# CONFIG_TARGET_VEXPRESS_CA15_TC2 is not set

# CONFIG_ARCH_BCMSTB is not set

# CONFIG_TARGET_VEXPRESS_CA5X2 is not set

# CONFIG_TARGET_VEXPRESS_CA9X4 is not set

# CONFIG_TARGET_BCM23550_W1D is not set

# CONFIG_TARGET_BCM28155_AP is not set

# CONFIG_TARGET_BCMCYGNUS is not set

# CONFIG_TARGET_BCMNSP is not set

# CONFIG_TARGET_BCMNS2 is not set

# CONFIG_ARCH_EXYNOS is not set

# CONFIG_ARCH_S5PC1XX is not set

# CONFIG_ARCH_HIGHBANK is not set

# CONFIG_ARCH_INTEGRATOR is not set

# CONFIG_ARCH_KEYSTONE is not set

# CONFIG_ARCH_K3 is not set

# CONFIG_ARCH_OMAP2PLUS is not set

# CONFIG_ARCH_MESON is not set

# CONFIG_ARCH_MEDIATEK is not set

# CONFIG_ARCH_LPC32XX is not set

# CONFIG_ARCH_IMX8 is not set

# CONFIG_ARCH_IMX8M is not set

# CONFIG_ARCH_IMXRT is not set

# CONFIG_ARCH_MX23 is not set

# CONFIG_ARCH_MX25 is not set

# CONFIG_ARCH_MX28 is not set

# CONFIG_ARCH_MX31 is not set

# CONFIG_ARCH_MX7ULP is not set

# CONFIG_ARCH_MX7 is not set

# CONFIG_ARCH_MX6 is not set

CONFIG_SPL_LDSCRIPT="arch/arm/cpu/armv7/sunxi/u-boot-spl.lds"

# CONFIG_ARCH_MX5 is not set

# CONFIG_ARCH_OWL is not set

# CONFIG_ARCH_QEMU is not set

# CONFIG_ARCH_RMOBILE is not set

# CONFIG_TARGET_S32V234EVB is not set

# CONFIG_ARCH_SNAPDRAGON is not set

# CONFIG_ARCH_SOCFPGA is not set

CONFIG_ARCH_SUNXI=y

# CONFIG_ARCH_U8500 is not set

# CONFIG_ARCH_VERSAL is not set

# CONFIG_ARCH_VF610 is not set

# CONFIG_ARCH_ZYNQ is not set

# CONFIG_ARCH_ZYNQMP_R5 is not set

# CONFIG_ARCH_ZYNQMP is not set

# CONFIG_TEGRA is not set

# CONFIG_TARGET_VEXPRESS64_AEMV8A is not set

# CONFIG_TARGET_VEXPRESS64_BASE_FVP is not set

# CONFIG_TARGET_VEXPRESS64_JUNO is not set

# CONFIG_TARGET_LS2080A_EMU is not set

# CONFIG_TARGET_LS2080A_SIMU is not set

# CONFIG_TARGET_LS1088AQDS is not set

# CONFIG_TARGET_LS2080AQDS is not set

# CONFIG_TARGET_LS2080ARDB is not set

# CONFIG_TARGET_LS2081ARDB is not set

# CONFIG_TARGET_LX2160ARDB is not set

# CONFIG_TARGET_LX2160AQDS is not set

# CONFIG_TARGET_HIKEY is not set

# CONFIG_TARGET_HIKEY960 is not set

# CONFIG_TARGET_POPLAR is not set

# CONFIG_TARGET_LS1012AQDS is not set

# CONFIG_TARGET_LS1012ARDB is not set

# CONFIG_TARGET_LS1012A2G5RDB is not set

# CONFIG_TARGET_LS1012AFRWY is not set

# CONFIG_TARGET_LS1012AFRDM is not set

# CONFIG_TARGET_LS1028AQDS is not set

# CONFIG_TARGET_LS1028ARDB is not set

# CONFIG_TARGET_LS1088ARDB is not set

# CONFIG_TARGET_LS1021AQDS is not set

# CONFIG_TARGET_LS1021ATWR is not set

# CONFIG_TARGET_LS1021ATSN is not set

# CONFIG_TARGET_LS1021AIOT is not set

# CONFIG_TARGET_LS1043AQDS is not set

# CONFIG_TARGET_LS1043ARDB is not set

# CONFIG_TARGET_LS1046AQDS is not set

# CONFIG_TARGET_LS1046ARDB is not set

# CONFIG_TARGET_LS1046AFRWY is not set

# CONFIG_TARGET_COLIBRI_PXA270 is not set

# CONFIG_ARCH_UNIPHIER is not set

# CONFIG_STM32 is not set

# CONFIG_ARCH_STI is not set

# CONFIG_ARCH_STM32MP is not set

# CONFIG_ARCH_ROCKCHIP is not set

# CONFIG_TARGET_THUNDERX_88XX is not set

# CONFIG_ARCH_ASPEED is not set

# CONFIG_TARGET_DURIAN is not set

# CONFIG_TARGET_PRESIDIO_ASIC is not set

CONFIG_SYS_TEXT_BASE=0x42e00000

CONFIG_SPL_GPIO_SUPPORT=y

CONFIG_SPL_LIBCOMMON_SUPPORT=y

CONFIG_SPL_LIBGENERIC_SUPPORT=y

CONFIG_SYS_MALLOC_F_LEN=0x400

CONFIG_ENV_SIZE=0x20000

CONFIG_DM_GPIO=y

CONFIG_SPL_SERIAL_SUPPORT=y

# CONFIG_SPL_DRIVERS_MISC_SUPPORT is not set

CONFIG_SPL_STACK_R_ADDR=0x4fe00000

CONFIG_SPL_SYS_MALLOC_F_LEN=0x400

CONFIG_ERR_PTR_OFFSET=0x0

CONFIG_NR_DRAM_BANKS=1

CONFIG_SPL_SIZE_LIMIT=0

CONFIG_SPL=y

CONFIG_PRE_CON_BUF_ADDR=0x4f000000

CONFIG_PRE_CON_BUF_SZ=4096

CONFIG_BOOTSTAGE_STASH_ADDR=0

CONFIG_IDENT_STRING=" Allwinner Technology"

# CONFIG_SUN6I_P2WI is not set

CONFIG_SUN6I_PRCM=y

# CONFIG_AXP_PMIC_BUS is not set

CONFIG_SUN8I_RSB=y

CONFIG_SUNXI_SRAM_ADDRESS=0x0

CONFIG_SUNXI_GEN_SUN6I=y

CONFIG_SUNXI_DRAM_DW=y

CONFIG_SUNXI_DRAM_DW_16BIT=y

CONFIG_SUNXI_DRAM_MAX_SIZE=0x80000000

# CONFIG_MACH_SUN4I is not set

# CONFIG_MACH_SUN5I is not set

# CONFIG_MACH_SUN6I is not set

# CONFIG_MACH_SUN7I is not set

# CONFIG_MACH_SUN8I_A23 is not set

# CONFIG_MACH_SUN8I_A33 is not set

# CONFIG_MACH_SUN8I_A83T is not set

# CONFIG_MACH_SUN8I_H3 is not set

# CONFIG_MACH_SUN8I_R40 is not set

CONFIG_MACH_SUN8I_V3S=y

# CONFIG_MACH_SUN9I is not set

# CONFIG_MACH_SUN50I is not set

# CONFIG_MACH_SUN50I_H5 is not set

# CONFIG_MACH_SUN50I_H6 is not set

CONFIG_MACH_SUN8I=y

# CONFIG_RESERVE_ALLWINNER_BOOT0_HEADER is not set

CONFIG_SUNXI_DRAM_DDR2=y

# CONFIG_SUNXI_DRAM_LPDDR3_STOCK is not set

CONFIG_SUNXI_DRAM_DDR2_V3S=y

CONFIG_DRAM_CLK=360

CONFIG_DRAM_ZQ=14779

# CONFIG_DRAM_ODT_EN is not set

CONFIG_SYS_CLK_FREQ=1008000000

CONFIG_UART0_PORT_F=y

# CONFIG_OLD_SUNXI_KERNEL_COMPAT is not set

CONFIG_MACPWR=""

CONFIG_MMC0_CD_PIN=""

CONFIG_MMC1_CD_PIN=""

CONFIG_MMC2_CD_PIN=""

CONFIG_MMC3_CD_PIN=""

CONFIG_MMC1_PINS=""

CONFIG_MMC2_PINS=""

CONFIG_MMC3_PINS=""

CONFIG_MMC_SUNXI_SLOT_EXTRA=-1

CONFIG_INITIAL_USB_SCAN_DELAY=0

CONFIG_USB0_VBUS_PIN=""

CONFIG_USB0_VBUS_DET=""

CONFIG_USB0_ID_DET=""

CONFIG_USB1_VBUS_PIN=""

CONFIG_USB2_VBUS_PIN=""

CONFIG_USB3_VBUS_PIN=""

# CONFIG_I2C0_ENABLE is not set

# CONFIG_I2C1_ENABLE is not set

# CONFIG_I2C2_ENABLE is not set

# CONFIG_R_I2C_ENABLE is not set

# CONFIG_AXP_GPIO is not set

CONFIG_SATAPWR=""

CONFIG_GMAC_TX_DELAY=0

CONFIG_SPL_SPI_SUNXI=y

# CONFIG_SPL_FS_FAT is not set

# CONFIG_SPL_LIBDISK_SUPPORT is not set

# CONFIG_SPL_SPI_SUPPORT is not set

CONFIG_CPU_V7_HAS_NONSEC=y

CONFIG_CPU_V7_HAS_VIRT=y

CONFIG_ARCH_SUPPORT_PSCI=y

CONFIG_ARMV7_NONSEC=y

# CONFIG_ARMV7_BOOT_SEC_DEFAULT is not set

CONFIG_ARMV7_VIRT=y

CONFIG_ARMV7_PSCI=y

CONFIG_ARMV7_PSCI_NR_CPUS=4

CONFIG_ARMV7_LPAE=y

CONFIG_CSF_SIZE=0x2060

# CONFIG_CMD_DEKBLOB is not set

# CONFIG_CMD_HDMIDETECT is not set

CONFIG_IMX_DCD_ADDR=0x00910000

#

# ARM debug

#

# CONFIG_DEBUG_LL is not set

CONFIG_SMBIOS_PRODUCT_NAME="sunxi"

# CONFIG_DEBUG_UART is not set

# CONFIG_AHCI is not set

CONFIG_SPL_TEXT_BASE=0x00060

#

# General setup

#

CONFIG_LOCALVERSION=""

CONFIG_LOCALVERSION_AUTO=y

CONFIG_CC_OPTIMIZE_FOR_SIZE=y

CONFIG_DISTRO_DEFAULTS=y

CONFIG_ENV_VARS_UBOOT_CONFIG=y

# CONFIG_SYS_BOOT_GET_CMDLINE is not set

# CONFIG_SYS_BOOT_GET_KBD is not set

CONFIG_SYS_MALLOC_F=y

CONFIG_EXPERT=y

# CONFIG_SYS_MALLOC_CLEAR_ON_INIT is not set

# CONFIG_TOOLS_DEBUG is not set

# CONFIG_PHYS_64BIT is not set

CONFIG_SPL_IMAGE="spl/u-boot-spl.bin"

CONFIG_BUILD_TARGET=""

# CONFIG_SYS_CUSTOM_LDSCRIPT is not set

CONFIG_PLATFORM_ELFENTRY="_start"

#

# Boot images

#

# CONFIG_ANDROID_BOOT_IMAGE is not set

CONFIG_FIT=y

CONFIG_FIT_EXTERNAL_OFFSET=0x0

CONFIG_FIT_ENABLE_SHA256_SUPPORT=y

# CONFIG_FIT_SIGNATURE is not set

# CONFIG_FIT_CIPHER is not set

# CONFIG_FIT_VERBOSE is not set

# CONFIG_FIT_BEST_MATCH is not set

# CONFIG_SPL_FIT is not set

# CONFIG_SPL_LOAD_FIT is not set

# CONFIG_SPL_LOAD_FIT_FULL is not set

CONFIG_LEGACY_IMAGE_FORMAT=y

CONFIG_OF_BOARD_SETUP=y

# CONFIG_OF_SYSTEM_SETUP is not set

# CONFIG_OF_STDOUT_VIA_ALIAS is not set

CONFIG_SYS_EXTRA_OPTIONS=""

CONFIG_HAVE_SYS_TEXT_BASE=y

CONFIG_ARCH_FIXUP_FDT_MEMORY=y

#

# API

#

# CONFIG_API is not set

#

# Boot timing

#

# CONFIG_BOOTSTAGE is not set

CONFIG_BOOTSTAGE_RECORD_COUNT=30

CONFIG_SPL_BOOTSTAGE_RECORD_COUNT=5

CONFIG_TPL_BOOTSTAGE_RECORD_COUNT=5

CONFIG_BOOTSTAGE_STASH_SIZE=0x1000

# CONFIG_SHOW_BOOT_PROGRESS is not set

#

# Boot media

#

# CONFIG_NAND_BOOT is not set

# CONFIG_ONENAND_BOOT is not set

# CONFIG_QSPI_BOOT is not set

# CONFIG_SATA_BOOT is not set

# CONFIG_SD_BOOT is not set

# CONFIG_SPI_BOOT is not set

CONFIG_BOOTDELAY=2

# CONFIG_USE_BOOTARGS is not set

CONFIG_USE_BOOTCOMMAND=y

CONFIG_BOOTCOMMAND="run distro_bootcmd"

CONFIG_USE_PREBOOT=y

CONFIG_PREBOOT=""

#

# Console

#

CONFIG_MENU=y

# CONFIG_CONSOLE_RECORD is not set

# CONFIG_DISABLE_CONSOLE is not set

CONFIG_LOGLEVEL=4

CONFIG_SPL_LOGLEVEL=4

CONFIG_TPL_LOGLEVEL=4

# CONFIG_SILENT_CONSOLE is not set

CONFIG_PRE_CONSOLE_BUFFER=y

# CONFIG_CONSOLE_MUX is not set

# CONFIG_SYS_CONSOLE_IS_IN_ENV is not set

# CONFIG_SYS_CONSOLE_OVERWRITE_ROUTINE is not set

# CONFIG_SYS_CONSOLE_ENV_OVERWRITE is not set

# CONFIG_SYS_CONSOLE_INFO_QUIET is not set

CONFIG_SYS_STDIO_DEREGISTER=y

#

# Logging

#

# CONFIG_LOG is not set

CONFIG_LOG_DEFAULT_LEVEL=6

CONFIG_SUPPORT_RAW_INITRD=y

CONFIG_DEFAULT_FDT_FILE=""

CONFIG_MISC_INIT_R=y

# CONFIG_VERSION_VARIABLE is not set

# CONFIG_BOARD_LATE_INIT is not set

CONFIG_DISPLAY_CPUINFO=y

CONFIG_DISPLAY_BOARDINFO=y

# CONFIG_DISPLAY_BOARDINFO_LATE is not set

# CONFIG_BOUNCE_BUFFER is not set

# CONFIG_BOARD_TYPES is not set

#

# Start-up hooks

#

# CONFIG_ARCH_EARLY_INIT_R is not set

# CONFIG_ARCH_MISC_INIT is not set

# CONFIG_BOARD_EARLY_INIT_F is not set

# CONFIG_BOARD_EARLY_INIT_R is not set

# CONFIG_LAST_STAGE_INIT is not set

#

# Security support

#

CONFIG_HASH=y

#

# Update support

#

# CONFIG_UPDATE_TFTP is not set

# CONFIG_ANDROID_AB is not set

#

# Blob list

#

# CONFIG_BLOBLIST is not set

#

# SPL / TPL

#

CONFIG_SUPPORT_SPL=y

CONFIG_SPL_FRAMEWORK=y

# CONFIG_SPL_FRAMEWORK_BOARD_INIT_F is not set

CONFIG_SPL_SYS_STACK_F_CHECK_BYTE=0xaa

# CONFIG_SPL_SYS_REPORT_STACK_F_USAGE is not set

#

# PowerPC and LayerScape SPL Boot options

#

# CONFIG_SPL_BOARD_INIT is not set

# CONFIG_SPL_BOOTROM_SUPPORT is not set

CONFIG_SPL_RAW_IMAGE_SUPPORT=y

CONFIG_SPL_LEGACY_IMAGE_SUPPORT=y

# CONFIG_SPL_LEGACY_IMAGE_CRC_CHECK is not set

CONFIG_SPL_SYS_MALLOC_SIMPLE=y

CONFIG_SPL_STACK_R=y

CONFIG_SPL_STACK_R_MALLOC_SIMPLE_LEN=0x100000

# CONFIG_SPL_SEPARATE_BSS is not set

CONFIG_SPL_BANNER_PRINT=y

# CONFIG_SPL_EARLY_BSS is not set

# CONFIG_SPL_DISPLAY_PRINT is not set

CONFIG_SYS_MMCSD_RAW_MODE_U_BOOT_USE_SECTOR=y

CONFIG_SYS_MMCSD_RAW_MODE_U_BOOT_SECTOR=0x50

CONFIG_SYS_MMCSD_RAW_MODE_U_BOOT_DATA_PART_OFFSET=0x0

# CONFIG_SYS_MMCSD_RAW_MODE_U_BOOT_USE_PARTITION is not set

CONFIG_SPL_CRC32_SUPPORT=y

# CONFIG_SPL_CACHE_SUPPORT is not set

# CONFIG_SPL_CPU_SUPPORT is not set

# CONFIG_SPL_CRYPTO_SUPPORT is not set

# CONFIG_SPL_HASH_SUPPORT is not set

# CONFIG_SPL_DMA is not set

# CONFIG_SPL_DM_GPIO is not set

# CONFIG_SPL_ENV_SUPPORT is not set

# CONFIG_SPL_FS_EXT4 is not set

# CONFIG_SPL_FAT_WRITE is not set

# CONFIG_SPL_FPGA_SUPPORT is not set

# CONFIG_SPL_I2C_SUPPORT is not set

# CONFIG_SPL_DM_MAILBOX is not set

# CONFIG_SPL_MPC8XXX_INIT_DDR_SUPPORT is not set

# CONFIG_SPL_MTD_SUPPORT is not set

# CONFIG_SPL_MUSB_NEW_SUPPORT is not set

# CONFIG_SPL_NAND_SUPPORT is not set

# CONFIG_SPL_UBI is not set

# CONFIG_SPL_NET_SUPPORT is not set

# CONFIG_SPL_NO_CPU_SUPPORT is not set

# CONFIG_SPL_NOR_SUPPORT is not set

# CONFIG_SPL_XIP_SUPPORT is not set

# CONFIG_SPL_ONENAND_SUPPORT is not set

# CONFIG_SPL_OS_BOOT is not set

CONFIG_SPL_PAYLOAD="u-boot.bin"

# CONFIG_SPL_PCI is not set

# CONFIG_SPL_PCH_SUPPORT is not set

# CONFIG_SPL_POST_MEM_SUPPORT is not set

# CONFIG_SPL_DM_RESET is not set

CONFIG_SPL_POWER_SUPPORT=y

# CONFIG_SPL_POWER_DOMAIN is not set

# CONFIG_SPL_RAM_SUPPORT is not set

# CONFIG_SPL_REMOTEPROC is not set

# CONFIG_SPL_RTC_SUPPORT is not set

# CONFIG_SPL_SATA_SUPPORT is not set

CONFIG_SYS_SPI_U_BOOT_OFFS=0x8000

# CONFIG_SPL_THERMAL is not set

# CONFIG_SPL_USB_HOST_SUPPORT is not set

# CONFIG_SPL_USB_GADGET is not set

# CONFIG_SPL_WATCHDOG_SUPPORT is not set

# CONFIG_SPL_YMODEM_SUPPORT is not set

# CONFIG_SPL_AM33XX_ENABLE_RTC32K_OSC is not set

# CONFIG_SPL_OPTEE is not set

#

# Command line interface

#

CONFIG_CMDLINE=y

CONFIG_HUSH_PARSER=y

CONFIG_CMDLINE_EDITING=y

CONFIG_AUTO_COMPLETE=y

CONFIG_SYS_LONGHELP=y

CONFIG_SYS_PROMPT="=> "

CONFIG_SYS_XTRACE="y"

#

# Autoboot options

#

CONFIG_AUTOBOOT=y

# CONFIG_AUTOBOOT_KEYED is not set

# CONFIG_AUTOBOOT_USE_MENUKEY is not set

#

# Commands

#

#

# Info commands

#

CONFIG_CMD_BDI=y

# CONFIG_CMD_CONFIG is not set

CONFIG_CMD_CONSOLE=y

# CONFIG_CMD_CPU is not set

# CONFIG_CMD_LICENSE is not set

# CONFIG_CMD_PMC is not set

#

# Boot commands

#

CONFIG_CMD_BOOTD=y

CONFIG_CMD_BOOTM=y

CONFIG_BOOTM_EFI=y

CONFIG_CMD_BOOTZ=y

CONFIG_BOOTM_LINUX=y

CONFIG_BOOTM_NETBSD=y

# CONFIG_BOOTM_OPENRTOS is not set

# CONFIG_BOOTM_OSE is not set

CONFIG_BOOTM_PLAN9=y

CONFIG_BOOTM_RTEMS=y

CONFIG_BOOTM_VXWORKS=y

CONFIG_CMD_BOOTEFI=y

CONFIG_CMD_BOOTEFI_HELLO_COMPILE=y

# CONFIG_CMD_BOOTEFI_HELLO is not set

# CONFIG_CMD_BOOTEFI_SELFTEST is not set

# CONFIG_CMD_BOOTMENU is not set

# CONFIG_CMD_ADTIMG is not set

CONFIG_CMD_ELF=y

CONFIG_CMD_FDT=y

CONFIG_CMD_GO=y

CONFIG_CMD_RUN=y

CONFIG_CMD_IMI=y

# CONFIG_CMD_IMLS is not set

CONFIG_CMD_XIMG=y

# CONFIG_CMD_SPL is not set

# CONFIG_CMD_FITUPD is not set

# CONFIG_CMD_THOR_DOWNLOAD is not set

# CONFIG_CMD_ZBOOT is not set

#

# Environment commands

#

# CONFIG_CMD_ASKENV is not set

CONFIG_CMD_EXPORTENV=y

CONFIG_CMD_IMPORTENV=y

CONFIG_CMD_EDITENV=y

# CONFIG_CMD_GREPENV is not set

CONFIG_CMD_SAVEENV=y

# CONFIG_CMD_ERASEENV is not set

CONFIG_CMD_ENV_EXISTS=y

# CONFIG_CMD_ENV_CALLBACK is not set

# CONFIG_CMD_ENV_FLAGS is not set

# CONFIG_CMD_NVEDIT_EFI is not set

# CONFIG_CMD_NVEDIT_INFO is not set

#

# Memory commands

#

# CONFIG_CMD_BINOP is not set

CONFIG_CMD_CRC32=y

# CONFIG_CRC32_VERIFY is not set

# CONFIG_CMD_EEPROM is not set

# CONFIG_LOOPW is not set

# CONFIG_CMD_MD5SUM is not set

# CONFIG_CMD_MEMINFO is not set

CONFIG_CMD_MEMORY=y

# CONFIG_CMD_MX_CYCLIC is not set

CONFIG_CMD_RANDOM=y

# CONFIG_CMD_MEMTEST is not set

# CONFIG_CMD_SHA1SUM is not set

# CONFIG_CMD_STRINGS is not set

#

# Compression commands

#

# CONFIG_CMD_LZMADEC is not set

# CONFIG_CMD_UNZIP is not set

# CONFIG_CMD_ZIP is not set

#

# Device access commands

#

# CONFIG_CMD_ARMFLASH is not set

# CONFIG_CMD_ADC is not set

# CONFIG_CMD_BIND is not set

# CONFIG_CMD_CLK is not set

# CONFIG_CMD_DEMO is not set

# CONFIG_CMD_DFU is not set

CONFIG_CMD_DM=y

# CONFIG_CMD_FPGAD is not set

# CONFIG_CMD_FUSE is not set

CONFIG_CMD_GPIO=y

CONFIG_CMD_GPT=y

CONFIG_RANDOM_UUID=y

# CONFIG_CMD_GPT_RENAME is not set

# CONFIG_CMD_IDE is not set

# CONFIG_CMD_IO is not set

# CONFIG_CMD_IOTRACE is not set

# CONFIG_CMD_I2C is not set

CONFIG_CMD_LOADB=y

CONFIG_CMD_LOADS=y

# CONFIG_CMD_MMC is not set

# CONFIG_CMD_OSD is not set

CONFIG_CMD_PART=y

# CONFIG_CMD_PCI is not set

# CONFIG_CMD_PINMUX is not set