楼主 # 2023-02-28 01:24:50 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

怒开新坑,自制低成本高速USB分析仪(随缘更新)

最近参加了沁恒举办的RISC-V MCU创新应用大赛),虽然很可惜没能在限定的时间内完成所有工作,不过毕竟也做了一些有意义的事情。在deadline来临之际,这里我把之前整理的一些资料和已经完成的部分分享给大家,后续有时间会尽力完成这个设计,争取把BOM成本降低到可以自制的水平,做一个有实用价值的东西出来。

考虑到参加比赛的情况,这里暂时不会把参赛用的代码直接发出来,但后续会提供一个开源版本,希望能够和大家一起讨论相关技术,一起改进现有的设计。

由于楼主工作繁忙,更新进度比较随缘,还请大家见谅。

离线

楼主 #1 2023-02-28 01:51:18 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

既然要做一个USB分析仪,那自然要对它的原理有一个初步的了解,只知其然不知其所以然总归是不好的嘛。

在大多数应用中,USB分析仪也就是一个特殊的逻辑分析仪,通过抓取逻辑信号的方式来获取USB传输的物理层信号,之后通过层层翻译最终得到USB协议包、USB类乃至应用层的信息。当然,相对于一般意义上的逻辑分析仪,USB分析仪有以下几点不同:

USB的传输速率和当前的USB模式有关,如果是全速(12Mbps)或者低速(1.5Mbps)的话,普通的逻辑分析仪就可以实现(事实上sigrok等逻辑分析仪上位机已经支持USB全速和低速分析了);但是,高速(480Mbps)还是比较有难度的,这个速率超过了大部分逻辑分析仪可以达到的速度。

从物理层来看,高速USB其实是个比较蛋疼的存在:一方面为了兼容性需要使用3.3V CMOS电平进行握手和一些特定状态的处理,一方面为了传输效率使用了17.78mA的差分电流源,而这两种电平需要两路驱动和接收器在不同状态下进行切换。因此,如果要抓取高速USB信号,也必须要有相应的设计才行。

相对于通用的逻辑分析仪,USB传递的数据基本上是遵循一些上层协议的(如USB类),所以分析得到的数据时最好也要整理为相应形式以呈现给开发者,否则由于USB数据量大于大部分常见协议,可能会造成分析上的困难。

除了抓取物理层信号分析的方式,其实我们还有其它方式可以分析USB,比如在计算机上使用软件(例如Bus Hound等)进行抓包。实际上,软件抓包在大多数场合都要比USB分析仪好用,毕竟在计算机上更容易实现数据过滤和分析,但是,在有些场合,USB分析仪还是无法替代的:

最典型的情况是在嵌入式开发USB主机相关应用。在嵌入式中,通常难以使用软件抓包的方式来分析,即使能够通过输出log等方式获取一些简略的信息,但终究无法反映所有的信息。

对于USB无法正常使用的场合,USB分析仪能够抓取错误的波形和数据,而软件抓包只能在驱动层进行操作,对于USB控制器自动过滤或者忽略的情况则毫无办法。一个典型的例子是,Windows在获取描述符失败后无法识别设备,因此在驱动层面无法给出具体的错误信息。

USB分析仪可以抓取更精确的信息,例如时间戳等。由于驱动层给出的信息可能不准确(比如说驱动层反馈信息的时间有延迟),这个时候就需要USB分析仪补充相关信息了。

USB分析仪可以在一些特殊情况下使用,例如系统启动时、休眠时等。

考虑到USB分析仪的使用场景,我们通常可以假定其不需要分析物理层的内容,可以从协议层开始看起。那么,一个完整的USB分析仪系统,就可以分为以下这三个部分:

USB信号采集,也就是把抓取到的物理层信号翻译为USB协议包,并且附加一些信息(如时间戳等)。

USB数据转发,一般是把采集到的USB协议包传输到上位机,当然也可以保存下来之类的。

上位机分析,也就是把USB协议包翻译成方便人类阅读的方式,从而高效的定位和分析问题。

不考虑USB物理层的原因不外乎以下几点:

这部分内容以分析信号传输质量为主,通常由专业仪器测定,一般只有IC和PCB设计时会考虑,程序猿不用头疼这个事情。

高速USB的鲁棒性其实挺强的,你想想一般情况下接个几米的线都没问题,如果不是板子画得太离谱,一般不需要往这个方面去考虑问题。

退一步说,就算高速USB出问题,一般情况下都会回退到全速,这个就真的是“拉通了就能用”的程度,以USB堪比Windows的兼容性来看,只要全速USB能工作,剩下的问题应该就容易定位了。

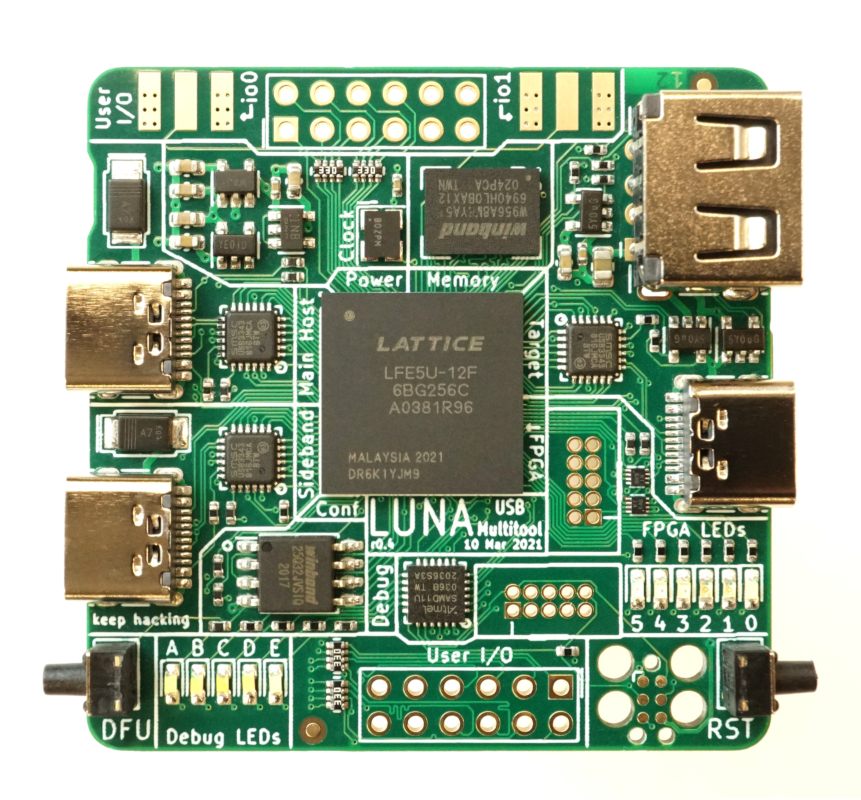

LUNA(现在硬件部分改名为Cynthion)就是一个完整的USB分析仪实现,也是本文的主要技术参考和灵感来源。可以从官方网站Cynthion - Great Scott Gadgets获取更多信息。

USB分析仪有一点和逻辑分析仪很像:作为调试程序时使用的工具,USB分析仪的上位机是非常重要的,一个成熟可靠的上位机才是吸引大家使用的关键。对于个人来说,开发USB分析仪上位机是一件比较庞杂的工作,好在我们可以搭上开源的快车,像Great Scott Gadgets开源的ViewSB(不得不说这个名字在汉语语境中十分微妙)和Packetry都是可以参考的对象。

综上所述,如果要自制USB分析仪,我们至少需要完成以下工作:

设计一套能够抓取USB信号,并将信号传输到上位机的硬件

为这套硬件编写必要的代码,使之可以和上位机通信

在上位机中适配新的USB分析仪

接下来的帖子也将围绕这些工作展开。

离线

#3 2023-02-28 08:59:38 分享评论

- lanlanzhilian

- 会员

- 注册时间: 2021-12-21

- 已发帖子: 167

- 积分: 62

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

期待楼主更新

离线

#4 2023-02-28 09:22:28 分享评论

- zjsx133

- 会员

- 注册时间: 2018-07-23

- 已发帖子: 101

- 积分: 36

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

支持楼主,这个开源吗

离线

#5 2023-02-28 09:27:23 分享评论

- david

- 会员

- 注册时间: 2018-03-05

- 已发帖子: 397

- 积分: 328.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

usb抓包都不算问题 协议分析软件比较繁琐 没有好的分析软件 抓到数据也是一头雾水

离线

#7 2023-02-28 09:58:56 分享评论

- llinjupt

- 会员

- 注册时间: 2020-12-21

- 已发帖子: 93

- 积分: 163

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

前排围观,期待尽量使用已经开源软件,这样参与度比较高,后期功能也容易扩展

离线

#8 2023-02-28 11:24:49 分享评论

- wxws

- 会员

- 注册时间: 2019-11-29

- 已发帖子: 33

- 积分: 31.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

这款不错,

比http://openvizsla.org/ 好

离线

#9 2023-02-28 12:37:21 分享评论

- wonderfullook

- 会员

- 注册时间: 2021-04-09

- 已发帖子: 5

- 积分: 4.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

前排围观,坐等更新

离线

#10 2023-02-28 13:25:25 分享评论

- libc0607

- 会员

- 注册时间: 2018-12-13

- 已发帖子: 25

- 积分: 48.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

期待

离线

#11 2023-02-28 19:44:54 分享评论

- echo

- 会员

- 注册时间: 2020-04-16

- 已发帖子: 364

- 积分: 370.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

高速USB分析仪用得还是少一些,大部分时候直接在PC端通过驱动抓包就行了。我也看过openvizsla,用得还是少。

全速USB直接用逻辑分析仪即可,稍微好点的逻辑分析仪就带USB协议解析,很多隐藏的比较深的bug,只能通过逻辑分析仪来debug。

离线

#14 2023-03-03 12:32:26 分享评论

- Blueskull

- 会员

- 注册时间: 2020-02-20

- 已发帖子: 458

- 积分: 444.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

讲道理,楼主的比力科沁恒和Vizsla都好。楼主这个是俩PHY,一个上行一个下行,中间插一个FPGA,这个方案可以截获、注入信号,而且可以延长线缆,改善信号完整性问题。上面那几个都是上下行直连,和PHY并联,相当于三通,PHY只能被动收包,还影响信号完整性。

最近编辑记录 Blueskull (2023-03-03 12:32:41)

离线

#15 2023-03-05 19:02:54 分享评论

- histimes

- 会员

- 注册时间: 2022-05-31

- 已发帖子: 31

- 积分: 31

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

这淘宝上已经在卖了

离线

楼主 #16 2023-03-07 00:15:21 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@Blueskull

LUNA确实底子挺不错的,这也是主要参考它的原因(这个项目没有参与过哈哈,顶多就是产品的使用者而已)。可惜HDL部分更新缓慢,现在HyperRAM都还没用上,等到USB分析以外的功能都做好估计得等到众筹发货了(是的,前年的众筹发货时间已经推迟到今年年中了),不过倒是已经有不少人已经有板子了(毕竟硬件都全开源了)。

我也有一块LUNA的板子,价格不贵(接近200),作为FPGA感觉性价比尚可。不过如果只是想做个USB分析仪的话,感觉还是有些浪费,所以在考虑做一个低成本方案,只做一件事情的话应该可以把FPGA砍成低容量的型号。

离线

楼主 #17 2023-03-07 00:17:48 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@echo

是的,我这边目前调试USB也是以全速设备为主,逻辑分析仪其实就够用了。之前也用逻辑分析仪找出了不少USB相关的问题。

不过我也在考虑一个问题,如果USB分析仪可以做更高级的事情(比如做USB Class层面的分析),那样的话还是有意义的——因为总有一些情况是没法把USB设备直接接电脑调试的,而一个靠谱的USB分析仪能够以更小的代价解决问题。

离线

#18 2023-03-07 08:16:47 分享评论

- echo

- 会员

- 注册时间: 2020-04-16

- 已发帖子: 364

- 积分: 370.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@metro

FPGA可以考虑AGM的AG10KL144H,价格便宜,焊接容易。还有内置64Mbits SDRAM的版本AG10KSDE176。

离线

#19 2023-03-07 09:40:59 分享评论

- johnnyzhong

- 会员

- 注册时间: 2023-03-06

- 已发帖子: 7

- 积分: 2

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

给楼主点赞,板凳准备好了

离线

楼主 #20 2023-03-07 12:53:40 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

echo wrote:

@metro

FPGA可以考虑AGM的AG10KL144H,价格便宜,焊接容易。还有内置64Mbits SDRAM的版本AG10KSDE176。

这个挺适合做高配版本的,加上CH569可以实现功能完整的USB分析仪了,BOM成本可以做到80-100。

不过呢,这次我打算从低配版本做起,先验证下功能再确定高配版本的设计。

这一版计划使用更低端的MCU和FPGA,成本减半应该没啥问题,主要看功能是否满足需要。估计月底可以画好板子,之后看软硬件要调试到什么时候了。

离线

#21 2023-03-07 19:52:33 分享评论

- echo

- 会员

- 注册时间: 2020-04-16

- 已发帖子: 364

- 积分: 370.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@metro

关键看需要多少LE资源了,AG10KL144H价格大约三四十,10k LE资源,要便宜只有1k资源AG1280不到10块钱,AGM还有2k,3k资源的,不过用得比较少,也没有P2P兼容的Altera型号。openvizsla用的是xc6slx9,这东西前一阵和cyclone4一样涨成天价了,不知道现在回来没。AGM价格倒是一直很稳定。

离线

楼主 #22 2023-03-07 23:39:41 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@echo

嗯,所以接下来需要确认下需要使用多少资源,如果AG1280够用的话那当然是最好的(虽然估计只能实现部分功能,buffer长度也比较堪忧),不够用就上更大资源的FPGA呗。

如果没记错的话,LUNA的USB分析仪使用了4K左右的LUT(包括了一个完整的USB控制器,用于连接PC)。不过LUNA实现的功能太少,连基础的USB速度自动识别和时间戳功能都不支持,HyperRAM目前也是闲置的状态。

离线

#23 2023-03-08 08:08:35 分享评论

- astankvai

- 会员

- 注册时间: 2021-02-23

- 已发帖子: 75

- 积分: 75

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

楼主的这个是USB 2.0 HS 还是想USB 3.0? 手上有一个WCH 的 2.0 HS, 2000不到, 性价比还可以。 支持楼主!

离线

#24 2023-03-08 13:25:44 分享评论

- bigniudiy

- 会员

- 注册时间: 2022-04-18

- 已发帖子: 40

- 积分: 80

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

我是来劝退的,楼主我按照官方的文档自己做了一个,有些物料不好买,我还自己找了替代料(价格也贵)

接下来说说坑:

1,官方的LUNA固件,要自己编译,中间会遇到各种库不对的问题,不过按照官方文档的步骤来基本上都没问题

2, 固件烧录进去了,测试脚本运行也OK,但不代表这个板子就好了。请看第3

3,最重要的是上位机,目前官方的上位机,我还未成功运行出来,找到了viewsb的代码,也编译安装OK,但是按照文档运行,一直出错。

我也是卡在第3点,板子已经吃灰好几个月了。中间也了解到,LUNA 连接到WINDOWS 也是要安装驱动的

当初买物料打板花了2000+ ,楼主考虑一下

离线

#25 2023-03-08 14:23:45 分享评论

- Blueskull

- 会员

- 注册时间: 2020-02-20

- 已发帖子: 458

- 积分: 444.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@bigniudiy

楼主是手撸USB协议栈的大神,这些问题不大

离线

楼主 #26 2023-03-08 14:53:26 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@bigniudiy

我手头也有LUNA,是之前淘宝那个众筹的版本,从FPGA到上位机都跑过了,ViewSB可以正常抓包,Windows和Linux都能用。这方面有问题可以交流下。

另外,LUNA那个协议栈我也尝试过移植到其它FPGA板子,Sipeed Tang Primer 20K的USB demo就是俺搞的🤣不过导出Verilog这事儿做起来太麻烦,最好还是能用Lattice这样有全套EDA工具的FPGA来玩。

离线

楼主 #27 2023-03-08 14:55:00 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

astankvai wrote:

楼主的这个是USB 2.0 HS 还是想USB 3.0? 手上有一个WCH 的 2.0 HS, 2000不到, 性价比还可以。 支持楼主!

目前是抓2.0的信号,有考虑用3.0的USB和上位机连接。

想抓3.0信号的话需要FPGA支持5G的serdes,这个成本就上去了,先不着急吧(反正3.0的spec还没看过(逃

最近编辑记录 metro (2023-03-08 15:18:43)

离线

#28 2023-03-09 07:58:50 分享评论

- echo

- 会员

- 注册时间: 2020-04-16

- 已发帖子: 364

- 积分: 370.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@metro

那1k的AG1280不用想了,起码准备10k LE,这东西体积和成本都不太可能很低。当然最重要的还是上位机软件。

比如Saleae Logic这个逻辑分析仪,做得最好的其实是上位机软件。

最近编辑记录 echo (2023-03-09 08:09:41)

离线

#29 2023-03-09 10:05:16 分享评论

- bigniudiy

- 会员

- 注册时间: 2022-04-18

- 已发帖子: 40

- 积分: 80

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@metro

看来是我板子的问题,回头有时间了拿出来再看看

离线

#30 2023-03-09 11:10:55 分享评论

- zzm24

- 会员

- 注册时间: 2018-05-07

- 已发帖子: 127

- 积分: 89

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

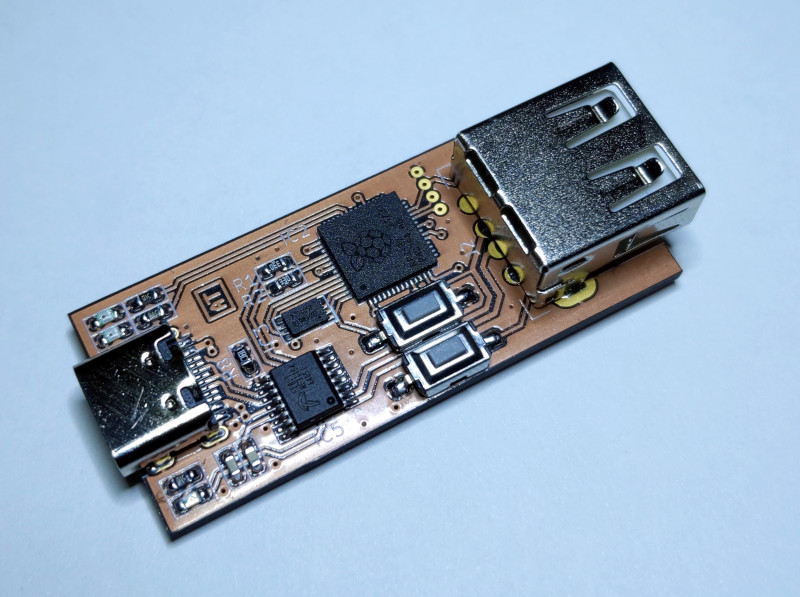

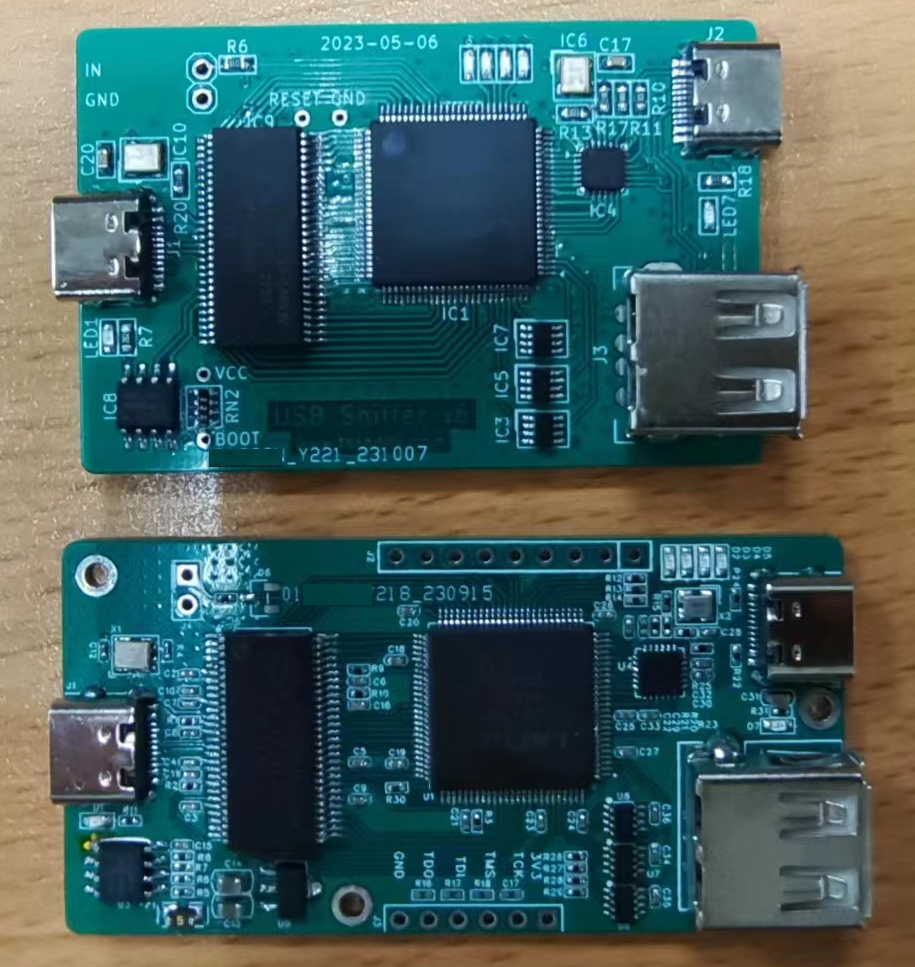

咸鱼500收了一个2.0 HS的,顺手拆给大家看看

离线

#31 2023-03-09 13:18:35 分享评论

- Winston

- 会员

- 注册时间: 2023-03-09

- 已发帖子: 15

- 积分: 45

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

收藏了,如果有需要的话可以拉个qq群,对usb系列协议还是挺感兴趣的,当时调STM32USB的时候就碰到很多问题,Win端也确实缺少很多好用的抓包设备,包是抓到了,但是分析包很头疼。期待楼主的更多工作

离线

#32 2023-03-09 13:19:53 分享评论

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

120通道逻辑分析仪

https://github.com/gusmanb/logicanalyzer

树莓派单片机24通道100Msps逻辑分析仪提升至支持120通道。

支持了菊花链方式级联五个设备,从而允许捕获120个通道。包括渲染引擎的性能改进和可见性改进、屏幕中的更多样本、自动选择捕获模式、编辑功能等。

摘自:硬汉嵌入式 https://www.bilibili.com/read/cv22245829?spm_id_from=333.999.0.0 出处:bilibili

离线

#33 2023-03-09 16:34:07 分享评论

- david

- 会员

- 注册时间: 2018-03-05

- 已发帖子: 397

- 积分: 328.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

设计不错 就是内存小 要是能跟sigrok连上 功能会更好些

离线

#34 2023-03-09 16:40:58 分享评论

- david

- 会员

- 注册时间: 2018-03-05

- 已发帖子: 397

- 积分: 328.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

这个实用还是要靠软件 最好有个结构可以第三方协议解析 这样开源出来大家好一起加东西

离线

#35 2023-03-09 16:44:00 分享评论

- david

- 会员

- 注册时间: 2018-03-05

- 已发帖子: 397

- 积分: 328.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

初步想的是 框架软件做基本的usb数据包标识 然后由协议分析插件对数据做进一步的解析和标注 最后交给框架软件做ui

离线

楼主 #36 2023-03-09 23:39:50 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

david wrote:

设计不错 就是内存小 要是能跟sigrok连上 功能会更好些

其实sigrok可能未必是最好的,原因上面有总结过,主要是USB分析仪需要能分层次呈现相关信息。至于其它方案,我想到的比较好的有两种:

使用已有的开源USB分析上位机,比如上面提到的ViewSB(不过这玩意实在是太半成品了一些),或者是同一个作者正在优化的Packetry。这个比较适合实时捕获,不过功能上还比较简陋,需要优化。

将数据保存为其它工具可以打开的形式,之后可以进行离线分析。这个我能想到最好的软件是Wireshark,配合相应插件可以实现USB Class级的分析,并且有强大的功能支持(例如正则表达式筛选)。按理来说这个工作量不会很大,不过似乎没有看到过成品。

离线

#38 2023-03-10 11:15:55 分享评论

- Blueskull

- 会员

- 注册时间: 2020-02-20

- 已发帖子: 458

- 积分: 444.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

话说有个简单粗暴的方案 -- 用PHY收发2.0信号,然后通过3.0接口发出去。这样就可以假设大水管包的下小水管,也就是说所有处理可以都丢到上位机。

CH569+小FPGA+UTMI PHY似乎可行。有些厂商甚至提供了软PHY,可以IP核直接调用(高云),没错,是480M的,这个很逆天。

可以用FPGA收USB包,做个简单的识别解析,压到SRAM里面,然后乒乓模式把SRAM里的东西吐到CH569里面,之后就全是上位机的了。

现代多核x86处理器实时分析USB2.0应该是轻松的,虽然风扇可能会狂转,但是连续抓包连续分析还是香啊。

离线

楼主 #39 2023-03-11 00:42:20 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@Blueskull

其实LUNA也是类似这样的方案,如果去看LUNA的代码(从抓USB信号到转发全都是nMigen写的,哦不这玩意现在应该叫做Amaranth了),就会发现逻辑其实很清晰:抓ULPI信号,加上包长度,一个FIFO给USB控制器,直接往一个端点发数据就完事了。

至于高云的那个SoftPHY 2.0,俺也玩过,确实能跑,但是成本其实不算低(记得单一个PHY至少需要2k的LUT,加上控制器大概4k),也就是说最少需要GW1N-LV4级别的才够用,成本其实比MCU要高一些(CH32V307也就十块出头)。

离线

#40 2023-03-11 01:34:56 分享评论

- 曾半仙

- 会员

- 注册时间: 2020-01-08

- 已发帖子: 5

- 积分: 15

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

考虑下商业软件的上位机 比如totalphase的data center, ellisys的visualusb

离线

楼主 #41 2023-03-13 18:03:26 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

曾半仙 wrote:

考虑下商业软件的上位机 比如totalphase的data center, ellisys的visualusb

目前没有适配商业软件的计划,不过到时候应该会开源全部代码,可以自行适配。

离线

楼主 #42 2023-03-16 00:02:43 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

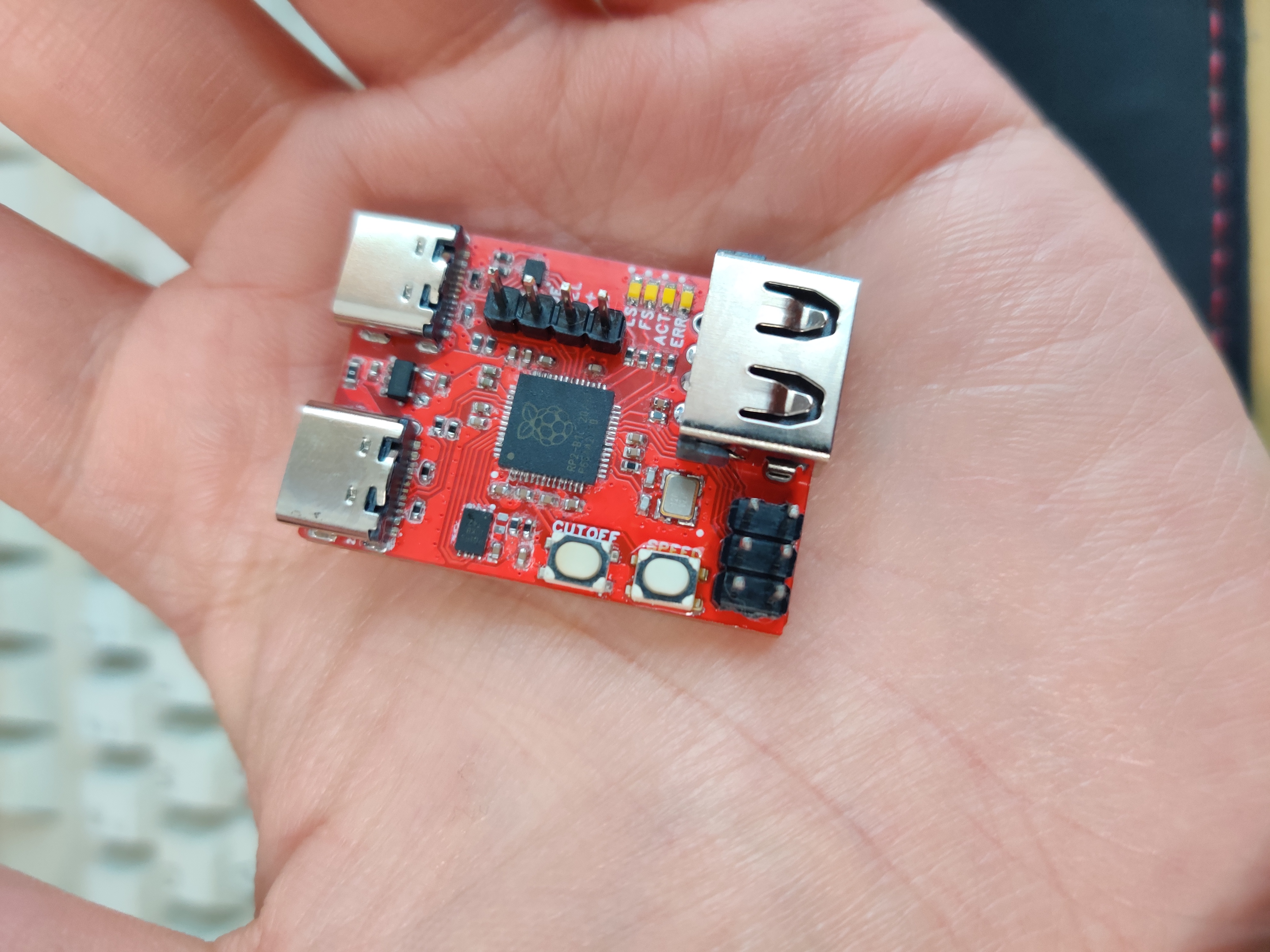

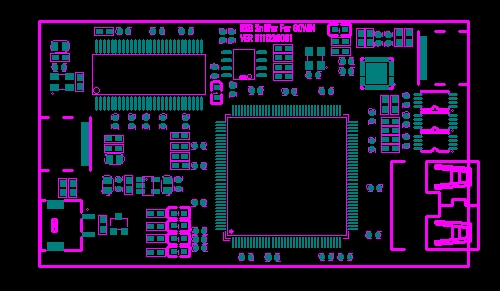

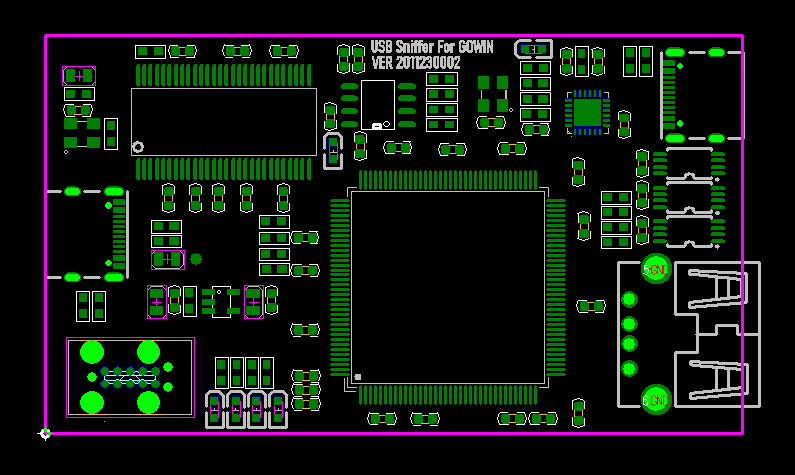

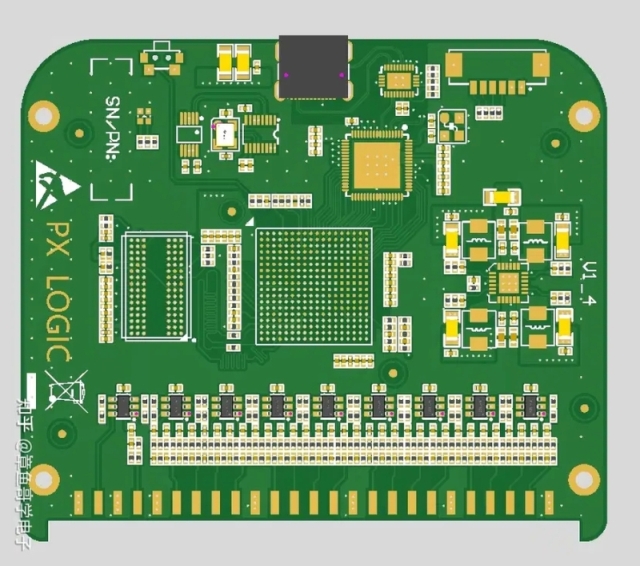

趁下班时间画了一版,大家猜猜这是什么方案😏

离线

#43 2023-03-16 08:57:16 分享评论

- Blueskull

- 会员

- 注册时间: 2020-02-20

- 已发帖子: 458

- 积分: 444.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

metro wrote:

趁下班时间画了一版,大家猜猜这是什么方案😏

/files/members/1510/AQUA-Lite.png

这是要用PIO做USB PHY?也就是只能测FS/LS咯?

离线

#45 2023-03-16 10:56:12 分享评论

- wls

- 会员

- 注册时间: 2022-09-23

- 已发帖子: 1

- 积分: 1

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

metro wrote:

趁下班时间画了一版,大家猜猜这是什么方案😏

/files/members/1510/AQUA-Lite.png

RP2040的逻辑分析仪🤭

离线

楼主 #46 2023-03-16 11:19:25 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

Blueskull wrote:

metro wrote:

趁下班时间画了一版,大家猜猜这是什么方案😏

/files/members/1510/AQUA-Lite.png这是要用PIO做USB PHY?也就是只能测FS/LS咯?

是的,先从简单的做起,熟悉下上位机。

不过这个会按照自己的想法做一些功能,具体的话可以期待一下🤭

离线

#47 2023-03-19 11:58:18 分享评论

- 1847123212

- 会员

- 注册时间: 2019-11-21

- 已发帖子: 70

- 积分: 46

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@metro

寂寞哥不考虑用agrv2k做一个吗,2k逻辑可能勉强够用

离线

#48 2023-03-19 16:51:28 分享评论

- MosesChan

- 会员

- 注册时间: 2023-03-19

- 已发帖子: 4

- 积分: 4

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

大佬问一下他们的板子上用的带通孔的SWD接口是什么? 淘宝上有卖的吗?

离线

楼主 #49 2023-03-20 14:21:25 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

1847123212 wrote:

@metro

寂寞哥不考虑用agrv2k做一个吗,2k逻辑可能勉强够用

AGRV2K挺可惜的,带了DWC2但接了个只支持到全速的PHY,如果能够把ULPI拉出来就很合适,可以用2K逻辑做很多想做的事情了。

离线

楼主 #50 2023-03-22 12:03:38 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

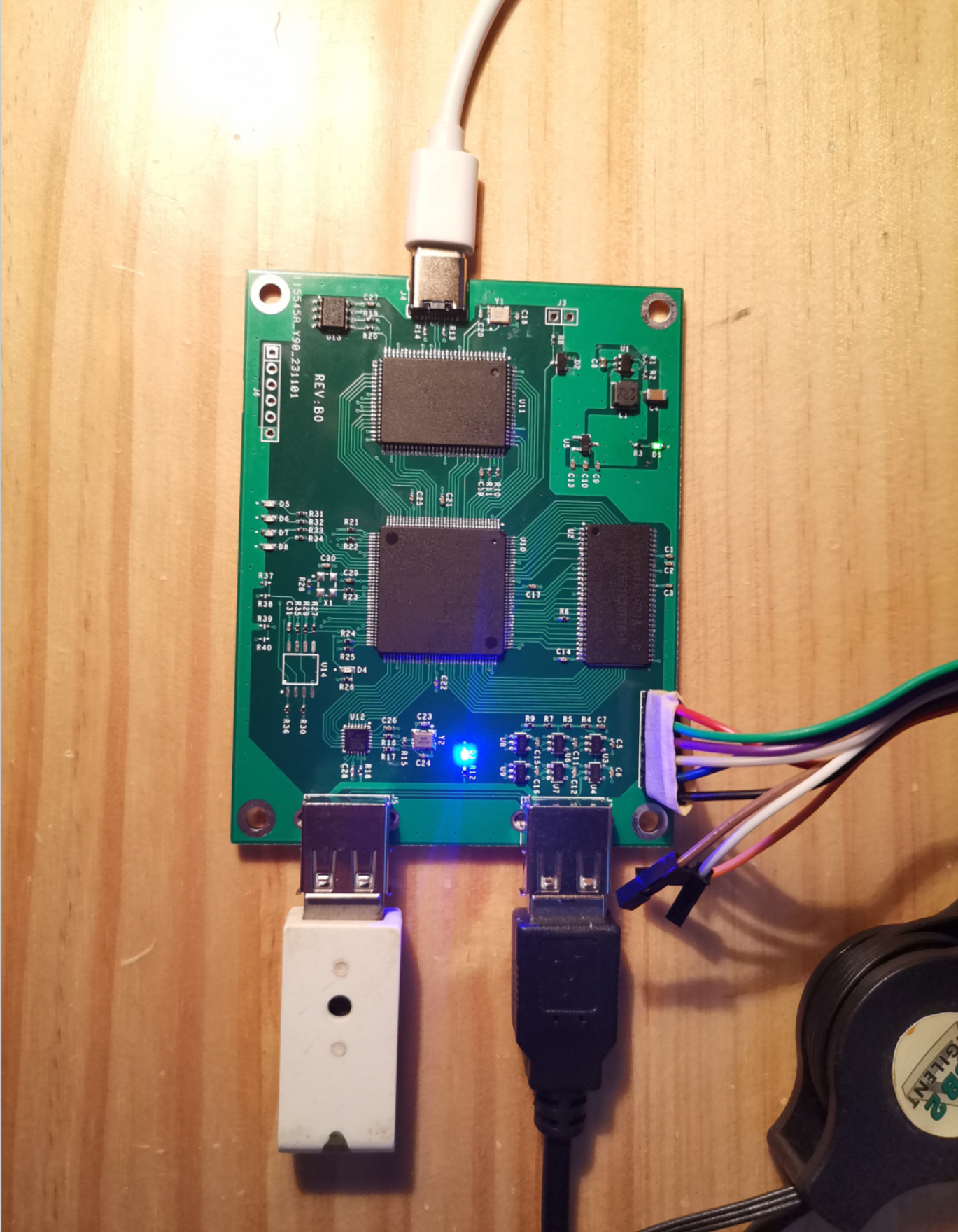

来个图,有空就开始写代码

离线

#51 2023-03-22 12:11:13 分享评论

- echo

- 会员

- 注册时间: 2020-04-16

- 已发帖子: 364

- 积分: 370.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

metro wrote:

趁下班时间画了一版,大家猜猜这是什么方案😏

/files/members/1510/AQUA-Lite.png

为啥你们都喜欢用TypeC,USB2.0 HS也只需要D+D-两个信号,MicroUSB足够了,TypeC多出来一堆无用管脚,焊接麻烦,体积还大。

离线

楼主 #53 2023-03-22 13:14:27 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@echo

主要原因是我手上的AtoC线比其它线都多,插座也是😂当然USB-C也有优势,比如说电源触点多能过大电流(USB-C插座基本上都能过3A),对只有USB-C的笔记本更友好(CtoMicro的线基本上只能另外买),线材质量相对更好(毕竟成本本来就更高)等,正反插毕竟也还是更方便的。

最近编辑记录 metro (2023-03-22 13:16:35)

离线

#54 2023-03-22 19:26:35 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

很高兴能找到组织,支持LZ保持热情,把这项工作持续下去。

我不是硬件/固件开发者,但因为研究U盘USB启动需要,掉入USB协议分析仪大坑。

现在手头上已经有了支持HS抓包的USB packet viewer,ellisys USB explorer 200(二手乞丐版)两套分析仪。

我赞同楼上很多同学反复强调的观点:抓包不算问题,关键在上位机软件,协议解析。我也是花了大价钱才直观认识到这一点。

由于USB packet viewer的协议解析软件,不支持USB启动用到的几个UFI/SCSI命令解析,所以,我才不得不购买二手

ellisys USB explorer 200,他家的Mass storage解析很漂亮。

但我没想到从一个坑掉入更大的坑,ellisys USB explorer 200的协议解析,Pro版才有,basic版没有。basic版只有帧解析

(类似沁恒的USB2分析仪那样,对这样的没诚意解析,兴趣顿时大减)。升级需要单独付费,且协议解析软件费用 >> 分析仪硬件本身,

这就很坑了。

=========================================================================

看了一下ViewSB,decode部分似乎完成度也不高,这将是严重障碍,需要特别注意避坑。想要用起来,几个急需的

基础协议解析要完成,例如Mass storage/SCSI命令的解析。

离线

#56 2023-03-24 10:19:40 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

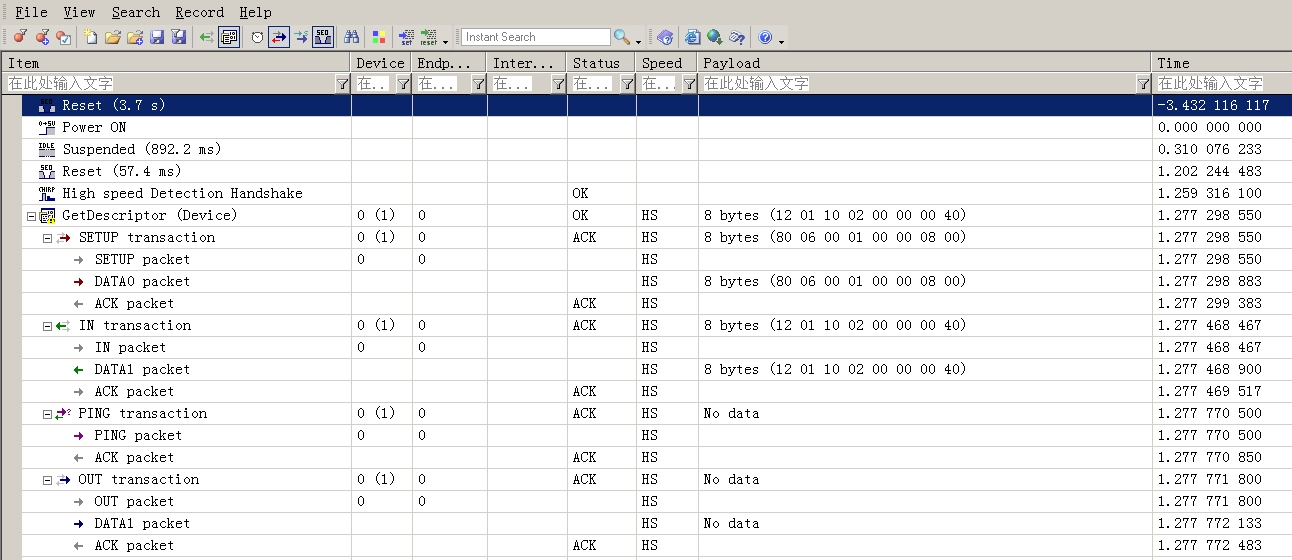

最关心上位机解析软件。我是门外汉发言,仅供参考,说错了请多包涵。

一、USB packet viewer的上位机软件是实时捕获解析。其解析器开源,LUA script,

不知有没有参考价值。

二、数据保存、离线分析可行。能不能考虑Save as输出多种格式,便于交换。

wireshark用得不多,似乎是pcapng格式?前面有同学说ellisys的visualusb,

我们倒不一定适配它这个闭源软件。但其数据保存格式策略,是不是可以借鉴

一下?

举例来说,其export格式有pkg、txt、xml等常见几种。pkt 实质就是自定义的TXT

文件,也是visualusb可以直接import的格式,而txt、xml不能import(蛋疼)。

这样一个枚举:

pkt内容是这个样子:

Reset duration<3.742 192 317> time<-3.432 116 117>

PowerChange state<ON> time<0.000 000 000>

Suspended duration<0.892 170 267> time<0.310 076 233>

Reset duration<0.057 357 367> time<1.202 244 483>

HighSpeedHandshake status<Success> time<1.259 316 100>

RawPacket data<2D 00 10> speed<HS> time<1.277 298 550>

RawPacket data<C3 80 06 00 01 00 00 08 00 EB 94> speed<HS> time<1.277 298 883>

RawPacket data<D2> speed<HS> time<1.277 299 383>

RawPacket data<69 00 10> speed<HS> time<1.277 468 467>

RawPacket data<4B 12 01 10 02 00 00 00 40 55 41> speed<HS> time<1.277 468 900>

RawPacket data<D2> speed<HS> time<1.277 469 517>

xml内容是这样:

<Reset duration="3.7 seconds" time="-3.432 116 117"></Reset>

<Power state="OFF" time="0.000 000 000"></Power>

<Suspended duration="892.2 milliseconds" time="0.310 076 233"></Suspended>

<Reset duration="57.4 milliseconds" time="1.202 244 483"></Reset>

<HighSpeedHandshake status="Success" time="1.259 316 100"></HighSpeedHandshake>

...

txt内容是这样:

______________________________________________________________________________

Reset duration<3.7 seconds> time<-3.432 116 117>

______________________________________________________________________________

Power state<OFF> time<0.000 000 000>

______________________________________________________________________________

Suspended duration<892.2 milliseconds> time<0.310 076 233>

______________________________________________________________________________

Reset duration<57.4 milliseconds> time<1.202 244 483>

______________________________________________________________________________

HighSpeedHandshake status<Success> time<1.259 316 100>

______________________________________________________________________________

Container title<GetDescriptor (Device)> device<0 (1)> endpoint<0> status<OK>

speed<HS> time<1.277 298 550>

Transaction type<SETUP> device<0 (1)> endpoint<0> status<ACK> speed<HS>

time<1.277 298 550>

Packet id<SETUP> devAddr<0> epNum<0> crc5<0x02> speed<HS>

time<1.277 298 550>

Packet id<DATA0> length<8> data<80 06 00 01 00 00 08 00> crc16<0x94EB>

speed<HS> time<1.277 298 883>

Packet id<ACK> speed<HS> time<1.277 299 383>

Transaction type<IN> device<0 (1)> endpoint<0> status<ACK> speed<HS>

time<1.277 468 467>

Packet id<IN> devAddr<0> epNum<0> crc5<0x02> speed<HS> time<1.277

468 467>

Packet id<DATA1> length<8> data<12 01 10 02 00 00 00 40> crc16<0x4155>

speed<HS> time<1.277 468 900>

Packet id<ACK> speed<HS> time<1.277 469 517>

Transaction type<PING> device<0 (1)> endpoint<0> status<ACK> speed<HS>

time<1.277 770 500>

Packet id<PING> devAddr<0> epNum<0> crc5<0x02> speed<HS>

time<1.277 770 500>

Packet id<ACK> speed<HS> time<1.277 770 850>

Transaction type<OUT> device<0 (1)> endpoint<0> status<ACK> speed<HS>

time<1.277 771 800>

Packet id<OUT> devAddr<0> epNum<0> crc5<0x02> speed<HS> time<1.277

771 800>

Packet id<DATA1> length<0> crc16<0x0000> speed<HS> time<1.277 772 133>

Packet id<ACK> speed<HS> time<1.277 772 483>

离线

#57 2023-04-25 11:50:18 分享评论

- iamseer

- 会员

- 注册时间: 2020-06-06

- 已发帖子: 75

- 积分: 52.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

metro wrote:

来个图,有空就开始写代码

这硬件看起来不错。我今天又被迫掏出了砖块大的“沁恒USB1.1总线分析仪”来调试代码。可能由于产品过于古老,上位机虽然能用但是也不是很好用。希望楼主能开发出小巧的替代品。

离线

#58 2023-06-02 11:52:44 分享评论

- xzy2003

- 会员

- 注册时间: 2022-02-14

- 已发帖子: 1

- 积分: 1

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@bigniudiy

请问一下,刚刚接触这个,现在环境基本配好了,不知道如何使用apollo烧录二进制文件,也不知道该烧的文件在哪,如果有空的话还望不吝赐教,万分感谢。

离线

#59 2023-06-06 16:18:25 分享评论

- bigniudiy

- 会员

- 注册时间: 2022-04-18

- 已发帖子: 40

- 积分: 80

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

xzy2003 wrote:

@bigniudiy

请问一下,刚刚接触这个,现在环境基本配好了,不知道如何使用apollo烧录二进制文件,也不知道该烧的文件在哪,如果有空的话还望不吝赐教,万分感谢。

首先你需要把boot loader烧录进MCU,这个需要JLINK或者其他烧录器。后面就简单了

至于boot loader哪里来,你在官方文档上应该能找到。当初我就是按照官方文档一步一步来的,出错都是一些软件版本问题

离线

#61 2023-06-09 11:48:52 分享评论

- dukefly

- 会员

- 注册时间: 2019-03-26

- 已发帖子: 7

- 积分: 1

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

metro wrote:

来个图,有空就开始写代码

/files/members/1510/IMG_20230321_142531.jpg

搞的怎样了?

离线

#63 2023-06-10 15:11:44 分享评论

- Xure

- 会员

- 注册时间: 2020-02-09

- 已发帖子: 16

- 积分: 16

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@metro, 看不出来,用的什么芯片,/files/members/1510/IMG_20230321_142531.jpg

离线

#64 2023-06-10 17:10:45 分享评论

- xlbook

- 会员

- 注册时间: 2023-02-21

- 已发帖子: 16

- 积分: 21

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@Xure rp2040呗,树莓派小芯片只有这个。

最近编辑记录 xlbook (2023-06-10 17:11:38)

离线

#65 2023-06-13 15:31:49 分享评论

- Xure

- 会员

- 注册时间: 2020-02-09

- 已发帖子: 16

- 积分: 16

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

有点疑问,用rp2040这个芯片能做USB分析仪?原理上行不通吧?搞不懂,麻烦能给解释一下不?(先不管HS/FS)

离线

#66 2023-06-13 18:19:16 分享评论

- marcus

- 会员

- 注册时间: 2021-03-19

- 已发帖子: 72

- 积分: 22

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

Xure wrote:

有点疑问,用rp2040这个芯片能做USB分析仪?原理上行不通吧?搞不懂,麻烦能给解释一下不?(先不管HS/FS)

PIO+DMA,采样频率能提高不少的。

离线

#67 2023-06-14 17:03:31 分享评论

- Xure

- 会员

- 注册时间: 2020-02-09

- 已发帖子: 16

- 积分: 16

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

疑问的不是速率高低,而是觉得这样连物理上都跑不通;不知是怎么做分析仪的,哪位能说明一下

离线

#68 2023-07-23 12:12:08 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

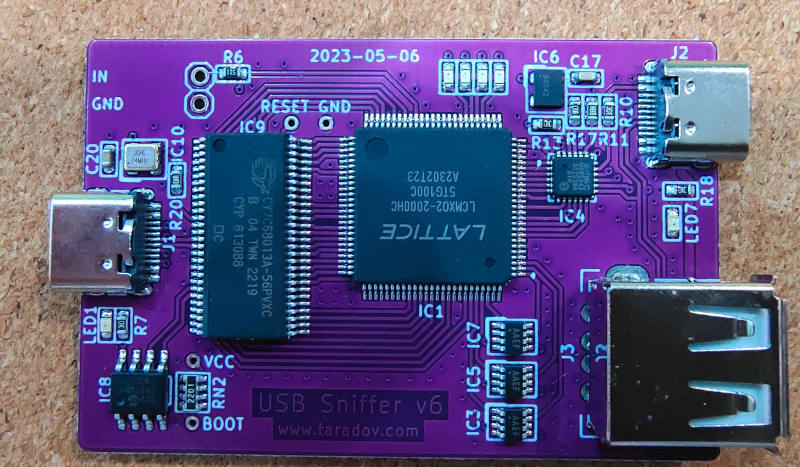

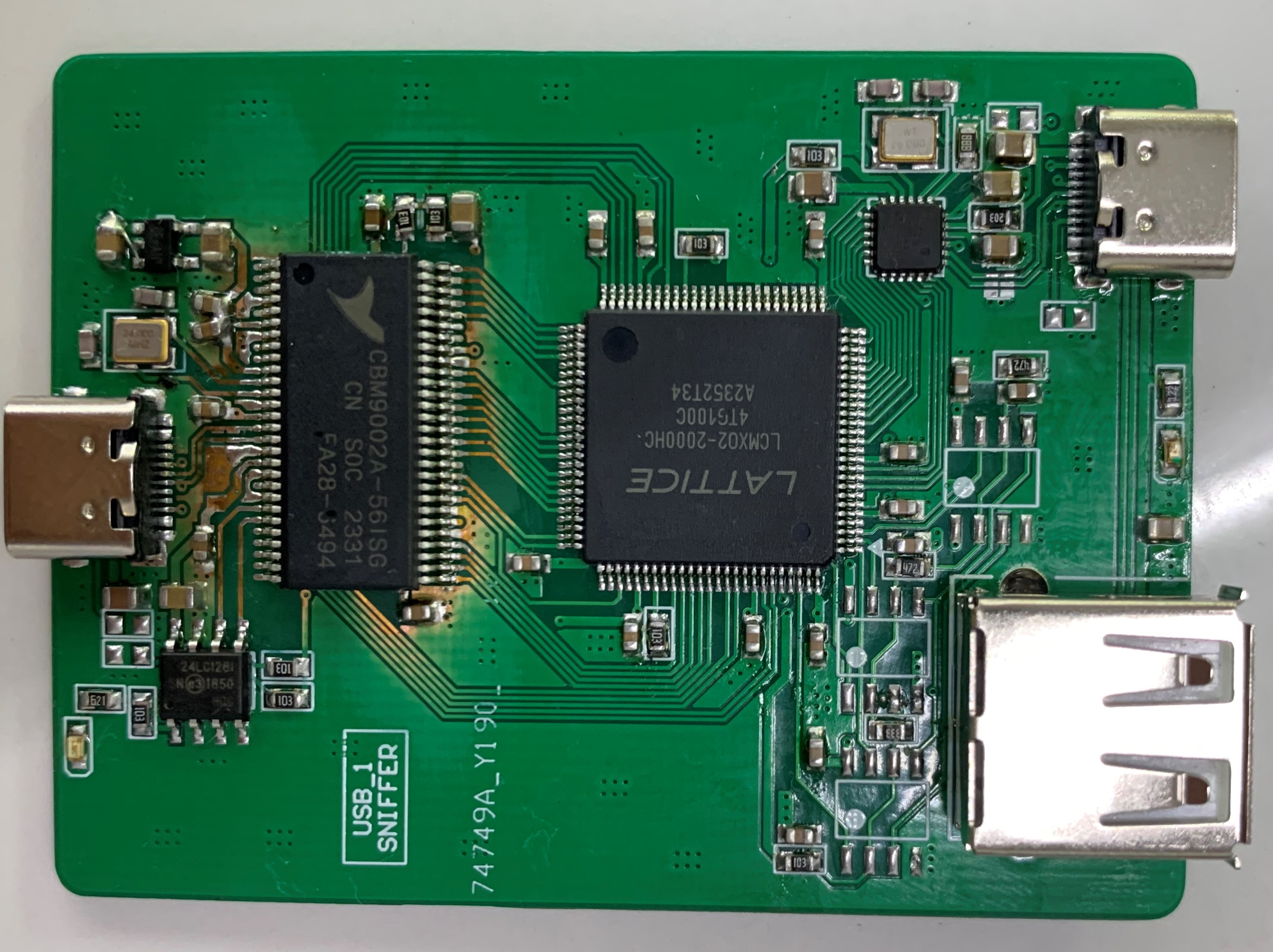

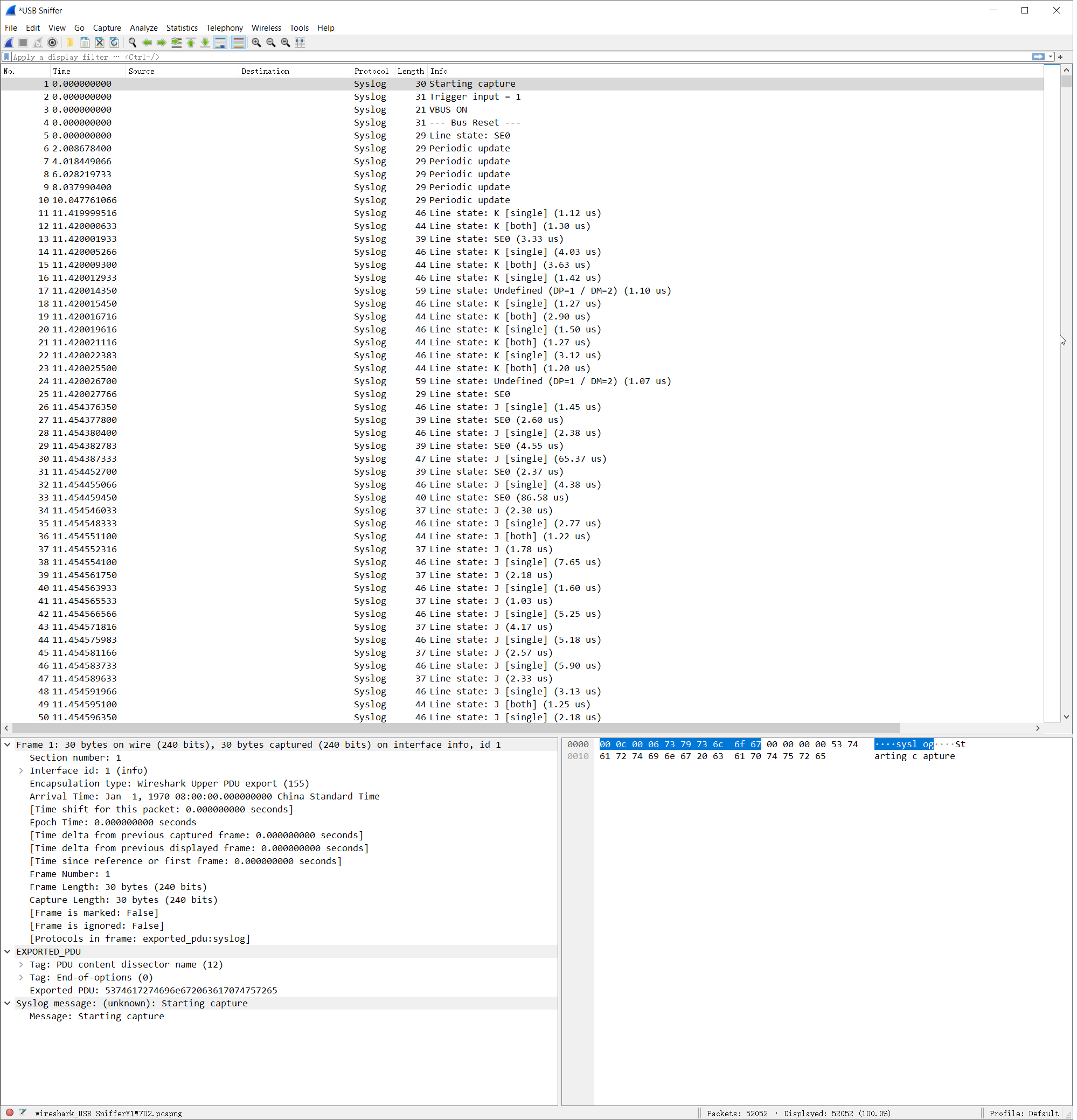

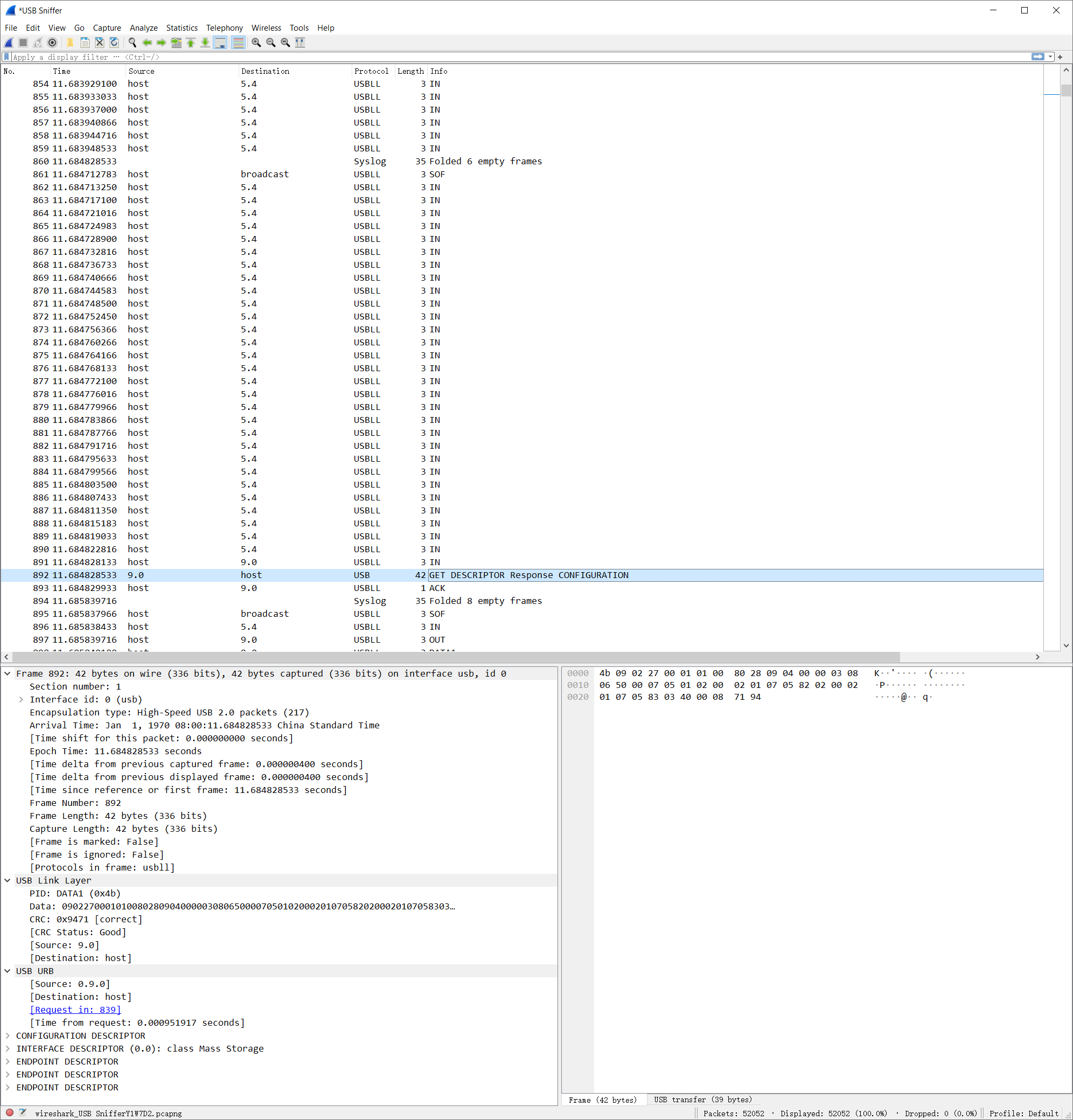

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

最近无意中翻到一个开源USB2协议分析仪

https://github.com/ataradov/usb-sniffer

硬件配置:

CY7C68013A MCU + Lattice LCMXO2 FPGA + Microchip USB3343 PHY

===========================================

我对硬件不熟,但这个开源分析仪我最欣赏的地方就是:

上位机软件直接使用Wireshark,这简直太好了。

分析仪硬件再牛,上位机软件协议解析(尤其是Mass storage解析)

不行,最终使用效果=0。而这个开源分析仪既没花大力气,还解决

了关键问题!设计思路很好。

最近编辑记录 usbbios (2023-07-23 12:16:41)

离线

#71 2023-09-08 11:28:02 分享评论

- zjsx133

- 会员

- 注册时间: 2018-07-23

- 已发帖子: 101

- 积分: 36

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@usbbios

usb分析的软件很少啊

离线

#72 2023-09-18 21:44:53 分享评论

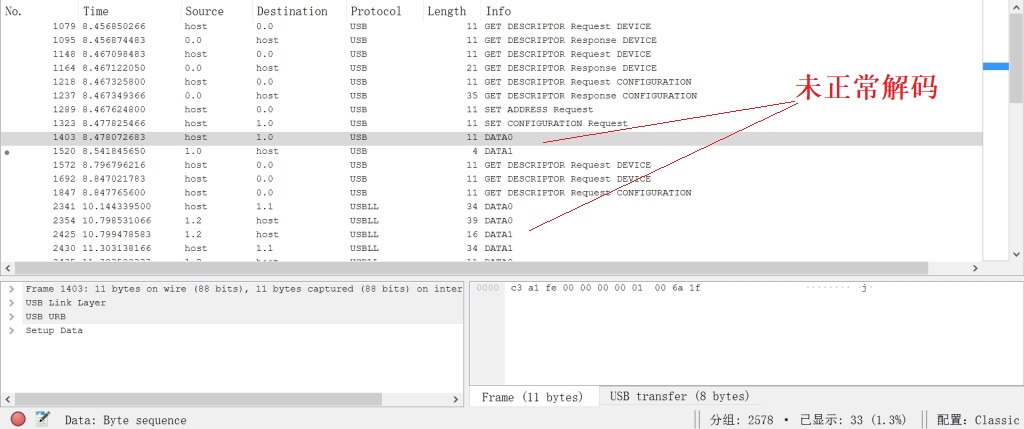

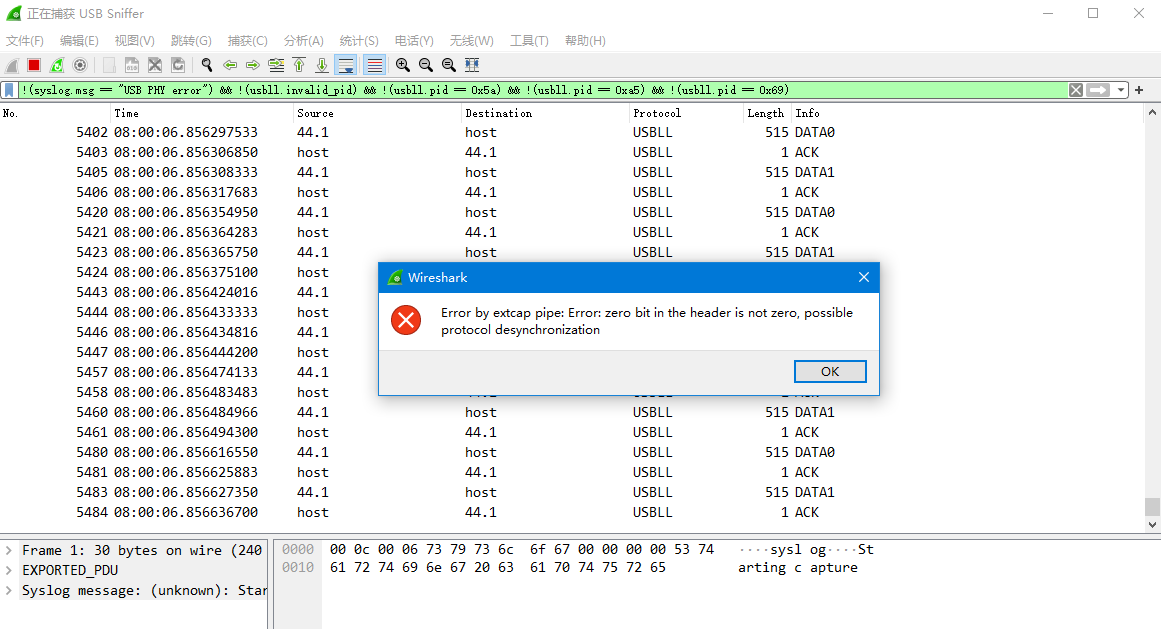

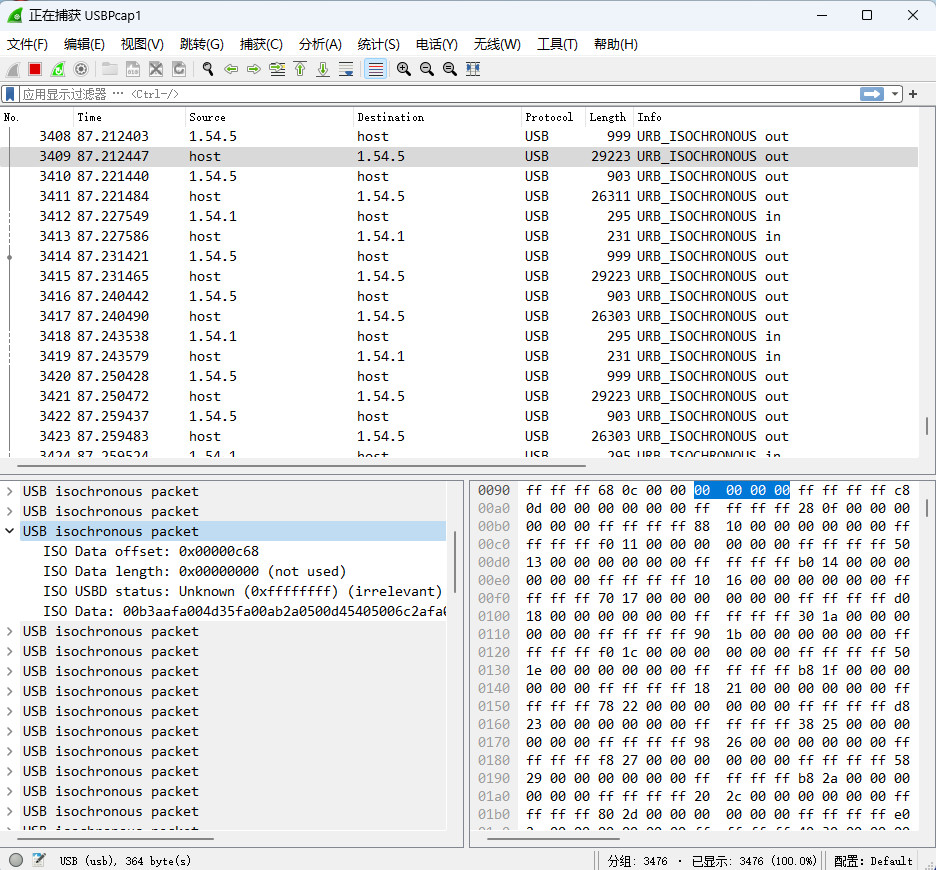

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

aozima wrote:

@usbbios 这个硬件有人发车吗? 想搭个车。

或新开1趟车?

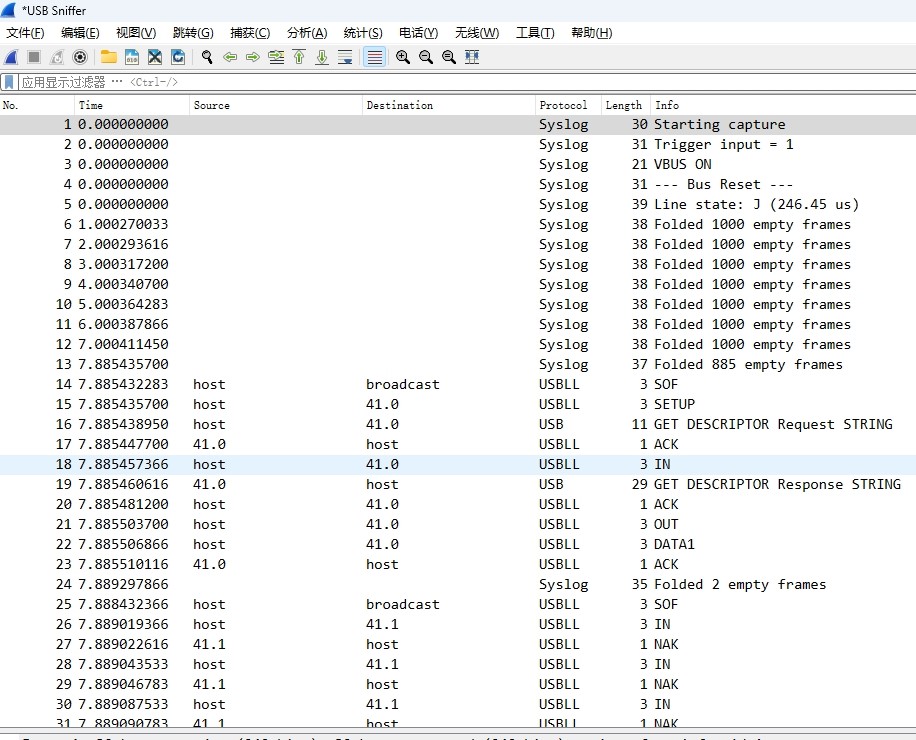

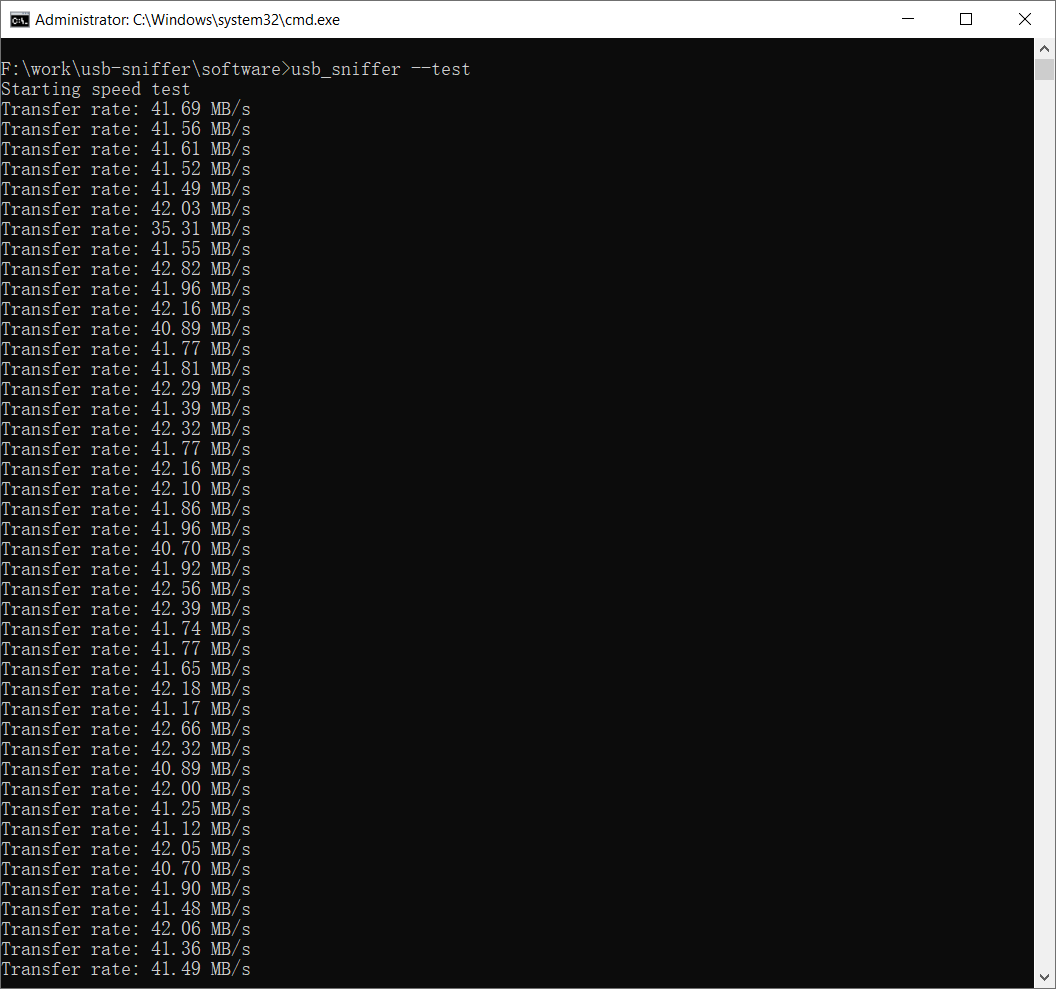

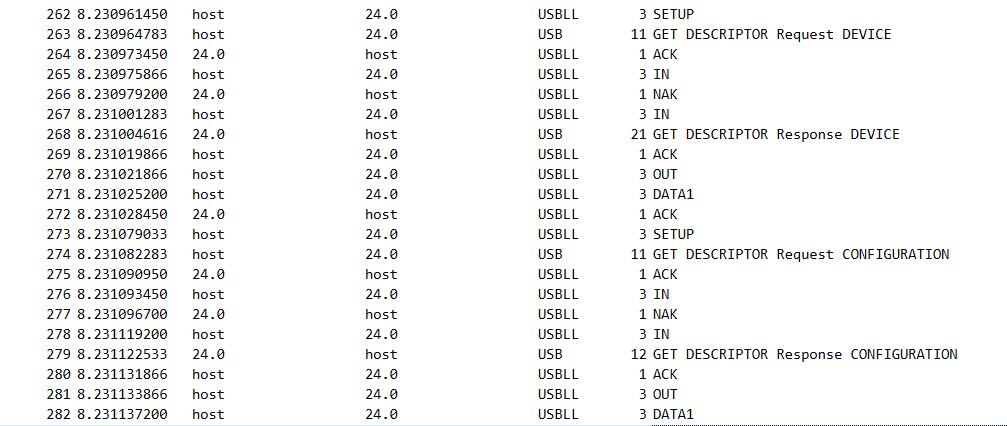

做回来了,体验挺好的,软件直接把68013的烧录和fpga的烧录全做了,不用额外安装软件和下载器。

同样还是这个软件,直接扔Wireshark里面就能抓包。

显示的内容也比较全,好在可以使用Wireshark的过滤器过滤掉不需要显示的内容。

!(usbll.pid == 0x69) IN

!(usbll.pid == 0x5a) NAK

!(usbll.pid == 0xa5) SOF

!(syslog.msg == "USB PHY error") && !(usbll.invalid_pid) && !(usbll.pid == 0x5a) && !(usbll.pid == 0xa5) && !(usbll.pid == 0x69)

离线

#75 2023-09-19 09:43:22 分享评论

- jordonwu

- 会员

- 注册时间: 2021-07-05

- 已发帖子: 66

- 积分: 37

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@aozima

想玩,有多余的板子不?能转一块吗

离线

#76 2023-09-20 07:59:33 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

我被上位机软件解码器折磨消耗了太多时间、精力、金钱,

看到这个能用wireshark的,且老兄成功了,简直太高兴了。

我不是搞硬件&固件开发的,动手能力不强,先前也是苦于

没购买门路。老兄吃了螃蟹,看结果这个项目完成度较高,

实用性好很多,新开1趟车还是可行的。

aozima wrote:

@usbbios 这个硬件有人发车吗? 想搭个车。

或新开1趟车?aozima wrote:

没翻!

Wireshark 的接口配置里面忘记改高速了。

离线

#77 2023-09-20 08:04:00 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

知道途径了,编辑掉原回帖,需要打板时的PCB文件。

最近编辑记录 usbbios (2023-09-20 20:03:52)

离线

#78 2023-09-20 08:20:13 分享评论

- seamas

- 会员

- 注册时间: 2019-12-01

- 已发帖子: 6

- 积分: 31

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

Wireshark不太熟悉,怎么设置解码usb协议?在哪里改成高速?

离线

#79 2023-09-20 14:11:14 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

我也打样了一个,不过板子重新画,希望不翻车。

@aozima

离线

#81 2023-09-20 23:38:28 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@aozima

你好!因我不是专业搞这个的,许多术语也不懂。

我自己搞不定PCB相关文件,老兄方便的话,能不能转一块给我?300元的价格我能接受。

或者,不方便转让成品的话,嘉立创SMT下单要求上传BOM、坐标文件,这2个文件能发

一下吗?我让嘉立创再多贴几片成品。谢谢了!

最近编辑记录 usbbios (2023-09-21 08:05:12)

离线

#84 2023-09-21 11:30:53 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@aozima

OK,发顺丰。

请您私信告知我一下:联系方式、含邮费总价款、付款方式,我会尽快按要求支付。

我邮箱地址usbbios@163.com。

最近编辑记录 usbbios (2023-09-21 11:38:53)

离线

#85 2023-09-21 12:48:14 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@aozima

我已拍下,您再检查一下,看有无需要说明修改的地方。

如没有,我将执行下一步付款操作。

离线

#86 2023-09-24 20:03:36 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

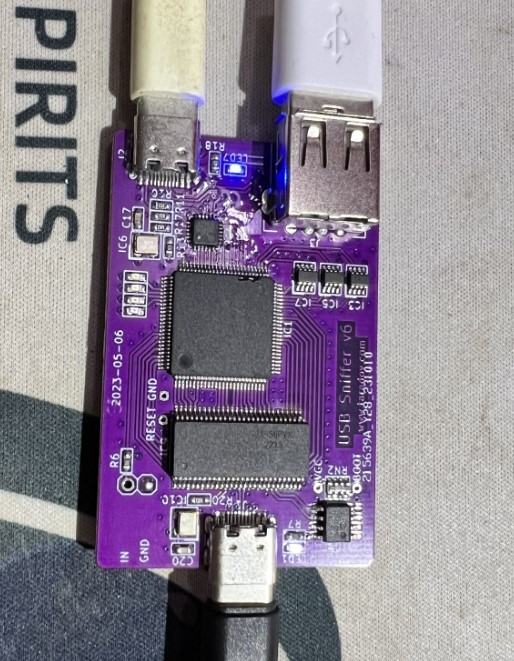

感谢楼上aozima,转让的usb-sniffer成品已收到。经试用,体验还是不错的。

这个开源项目完成度非常高,已经达到可用程度了。谈下粗浅感受:

我只试了win上位机环境,Linux没试。对Win的要求:只支持64位。因为:

1.原配usb-sniffer-win.exe是64位;

2.要求wireshark V4.X以上,而wireshark 4.X是针对X64的,所以win

必须用X64版。但我试了win7 X64环境执行不正常,win10 x64环境可以。

用同一U盘,测试了几台机器USB启动,抓UEFI/BIOS包,wireshark

均正常解码。但其中有1台神舟优雅A350-T45 D2老笔记本,AMI BIOS,

可能是SET ADDRESS顺序有误,导致包是抓到了,但wireshark未能把

U盘作为USB Mass Storage设备正常解码(而wireshark中似乎也没有

补救措施,菜单Decode as...没有USBms选项?)

离线

#87 2023-09-26 09:05:03 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

Xure wrote:

疑问的不是速率高低,而是觉得这样连物理上都跑不通;不知是怎么做分析仪的,哪位能说明一下

可以做。

我不知道具体原理,usb-sniffer的作者还有个LS/FS作品:usb-sniffer-lite,就是用RP2040做的

Usb Sniffer Lite for RP2040

This is a simple USB sniffer based on a Raspberry Pi RP2040. It supports Low Speed and Full Speed modes.

https://github.com/ataradov/usb-sniffer-lite

离线

#88 2023-09-26 09:09:10 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

lcfmax wrote:

我也打样了一个,不过板子重新画,希望不翻车。

@aozima

老哥重新画板测试成功了吗?能不能说说哪些地方做了改进?

离线

#89 2023-09-27 18:59:29 分享评论

- seamas

- 会员

- 注册时间: 2019-12-01

- 已发帖子: 6

- 积分: 31

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

这块板子用了3颗max9032aka+t,不太常用,有没有替代型号推荐?

离线

#90 2023-09-30 10:26:31 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

usb-sniffer板子的实际性能、结果已经明了了,可用度非常高。楼上专业搞电子的同学去搞没难度,

一定会成的。对比LZ基础方案的固件、上位机解码完成度,usb-sniffer进度优势太明显了。

至于我这个门外汉,gerber、BOM、坐标文件都捣鼓得差不多了,但到了JLC SMT这一步又卡壳了。

一个是预览图元件位置要旋转对齐(我搞不清第1脚位置不会弄);二是有的原件JLC库内没有,得加钱。

3颗max9032还好,JLC库内有;就是LCMXO2-2000HC-5XXX这个FPGA、还有其他零碎不一定有,

从扩展库选一个就得+20块钱(坑~)。然后,我看到有人说用-4xxx的FPGA替换也能成功(当然原作者

ataradov说极不推荐4,速度太慢)

离线

#92 2023-09-30 14:25:32 分享评论

- zzm24

- 会员

- 注册时间: 2018-05-07

- 已发帖子: 127

- 积分: 89

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

特地装了Diamond 3.12编译FPGA看看能不能采用便宜的LCMXO2-1200HC-5TG100,综合时不过,资源不够,这个LCMXO2-2000HC-5TG100太贵了

离线

#93 2023-09-30 20:56:23 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

啊? 这...... 层主再完整统计一下,看最后成本是?

==============================================

下午捣鼓了半天,JLC下单助手试算出了明细,有点奇怪。费用构成跟同学们不太

一样。

1、JLC库内有这个: LCMXO2-2000HC-5TG100I ,100块左右,用这个替换后,

贴2个的元件费在225块/个。

2、可加工费就比较高了,怎么看,都要大于100块/个的样子。

==============================================

aozima wrote:

坑了,果然翻车了。

我统计价格时,没算LCMXO2-2000HC-5TG100,

因为LCMXO2-2000HC-5TG100是在 mouser.cn 上面额外买的。。。。。。aozima wrote:

主要是LCMXO2-2000HC-5TG100C比较贵,再加上其它的物料。

光物料成本就200多了,算上加工费等接近300左右。

离线

#94 2023-09-30 20:58:12 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

JLC库内有LCMXO2-2000HC-5TG100I ,100块左右。

zzm24 wrote:

特地装了Diamond 3.12编译FPGA看看能不能采用便宜的LCMXO2-1200HC-5TG100,综合时不过,

资源不够,这个LCMXO2-2000HC-5TG100太贵了

离线

#95 2023-09-30 22:38:02 分享评论

- srovio

- 会员

- 注册时间: 2019-10-16

- 已发帖子: 17

- 积分: 11.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

usbbios wrote:

JLC库内有LCMXO2-2000HC-5TG100I ,100块左右。

zzm24 wrote:

特地装了Diamond 3.12编译FPGA看看能不能采用便宜的LCMXO2-1200HC-5TG100,综合时不过,

资源不够,这个LCMXO2-2000HC-5TG100太贵了

有价无货啊,那价格是以前的价格,等新货到了他才会去更新价格

离线

#96 2023-10-01 08:47:28 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@srovio

啊,这个我没实际打过板,还有这一招?不太清楚。看了一下其他网站情况,

按aozima同学说的Mouser 或 taobao,均有货,120多块。JLC的现报价

100+20选料费,基本也差不多这个价了。

srovio wrote:

有价无货啊,那价格是以前的价格,等新货到了他才会去更新价格

离线

#97 2023-10-02 11:46:19 分享评论

- seamas

- 会员

- 注册时间: 2019-12-01

- 已发帖子: 6

- 积分: 31

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

LCMXO2-1200HC的EBR只有7个,正好缺了一个。其实LCMXO2-2000HC-4的timing也不是差太多,按理说也能凑合。

zzm24 wrote:

特地装了Diamond 3.12编译FPGA看看能不能采用便宜的LCMXO2-1200HC-5TG100,综合时不过,资源不够,这个LCMXO2-2000HC-5TG100太贵了

离线

#98 2023-10-02 14:15:39 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

B站那个阿伟用-4的测试了,好像没问题,也可以。

seamas wrote:

LCMXO2-1200HC的EBR只有7个,正好缺了一个。其实LCMXO2-2000HC-4的timing也不是差太多,按理说也能凑合。

离线

#99 2023-10-02 21:34:41 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

usbbios wrote:

lcfmax wrote:

我也打样了一个,不过板子重新画,希望不翻车。

@aozima老哥重新画板测试成功了吗?能不能说说哪些地方做了改进?

板子已经回来,缺少max9032,刚下单。PCB主要是改成单面贴片,元件基本是0402,用JLC软件画的。

手头也只有 LCMXO2-2000HC-4,打算用这个是测试

最近编辑记录 lcfmax (2023-10-02 21:46:45)

离线

#100 2023-10-02 22:32:01 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@lcfmax

单面贴片? 改动比较大。看介绍,那3个max9032是原作者设计有特色的地方,且JLC库存有此元件。

期待层主新板能够测试成功,为降低成本趟出新路。

离线

#101 2023-10-06 10:43:35 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

aozima wrote:

aozima wrote:

好像翻车了,全速正常,高速时依然识别为全速,都是 Detected speed: Full-Speed。

可能得改下代码,让强制为高速看看行不行。没翻!

Wireshark 的接口配置里面忘记改高速了。

请问这里怎么改高速?,我测试板子,全速设备能解码数据正常,但是高速USB就获取不到正确的数据,也没提示进入高速模式,谢谢了。

最近编辑记录 lcfmax (2023-10-06 11:02:02)

离线

#102 2023-10-06 10:57:56 分享评论

#103 2023-10-06 11:13:32 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

aozima wrote:

请问这里怎么改高速?

点那个齿轮图标,我开始也没留意到。。。

我用的-4的FPGA,还担心速度是不是跟不上,这个错误有遇到么?

测试下来,在高速USB下,少数据量采集是正常,但是一旦大批量数据传输,例如U盘拷贝或者读取大文件,就会出现上面的报错,初步怀疑是FPGA -4的原因,大家还是一步到位,至少采用-5级别的保险点。

最近编辑记录 lcfmax (2023-10-06 14:48:29)

离线

#104 2023-10-06 15:27:27 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@lcfmax

USB2 HS高速测试通过了吗?

离线

#105 2023-10-06 16:14:37 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

usbbios wrote:

@lcfmax

USB2 HS高速测试通过了吗?

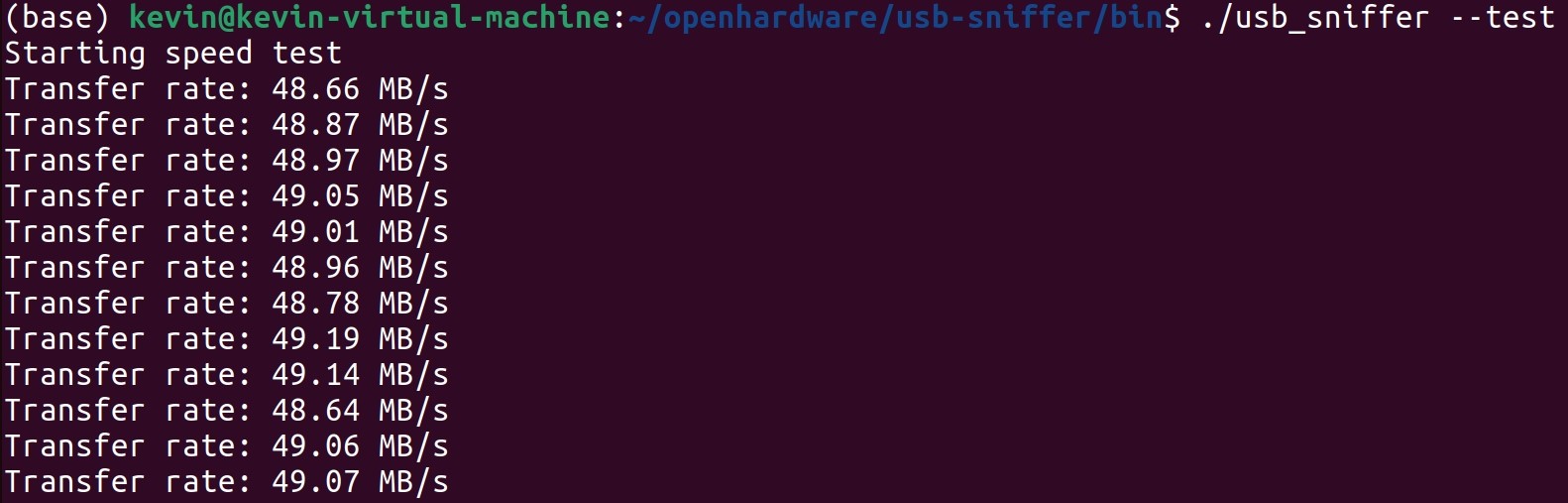

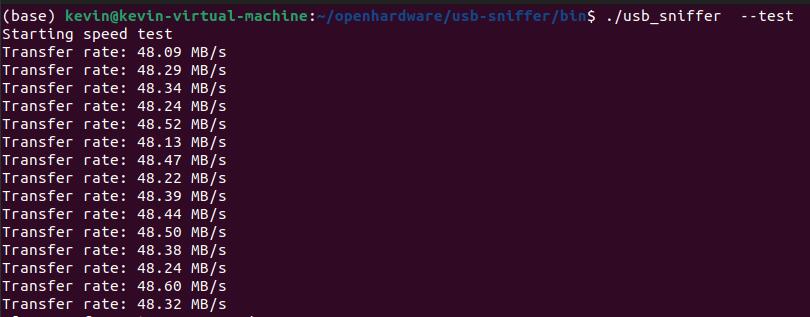

高速测试是通过的,有40MB以上的,但是这个测速应该不涉及USB3343。我怀疑瓶颈在USB3343的并行接口时序上。

离线

#106 2023-10-06 22:14:41 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@lcfmax

-4配置有报错的话,HS测试不完全成功。aozima同学复刻的-5配置抓包器没有类似报错。

同时,由于板子有改动,不太好排查引发出错因素是-4,还是板子改动。

测试下来,在高速USB下,少数据量采集是正常,但是一旦大批量数据传输,例如U盘拷贝或者读取大文件,就会出现上面的报错,初步怀疑是FPGA -4的原因,大家还是一步到位,至少采用-5级别的保险点。

高速测试是通过的,有40MB以上的,但是这个测速应该不涉及USB3343。我怀疑瓶颈在USB3343的并行接口时序上。

最近编辑记录 usbbios (2023-10-06 22:25:36)

离线

#107 2023-10-07 08:50:03 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@usbbios

所以我正考虑用回作者的gerber文件,打样一块板子,还是用-4去验证一下。我板子电路跟原来是一样的,只是部分元件封装和布局改变,而且还是4层板,一般不会出问题。

离线

#108 2023-10-07 09:30:45 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@lcfmax

高速测试是通过的,有40MB以上的,但是这个测速应该不涉及USB3343。我怀疑瓶颈在USB3343的并行接口时序上。

我看readme中说:“MCU和FPGA连接的功能和性能可以使用usb_sniffer命令进行测试,应该得到40-50MB/s结果”

这样看来,USB3343确实没涉及到。

所以我正考虑用回作者的gerber文件,打样一块板子,还是用-4去验证一下。我板子电路跟原来是一样的,只是部分元件封装

和布局改变,而且还是4层板,一般不会出问题。

是的,理论上是这样。如果成功,很有意义:JLC单面焊接加工费要比双面焊接低不少(一半?),我也很期待单面焊接板子能成功。

另外,我看其他网站介绍,max9032是有特色的设计,检测USB上升沿、下降沿。单面焊接板不用这个max9032,不知有没有

大的影响。

最近编辑记录 usbbios (2023-10-07 10:22:49)

离线

#109 2023-10-07 15:20:38 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

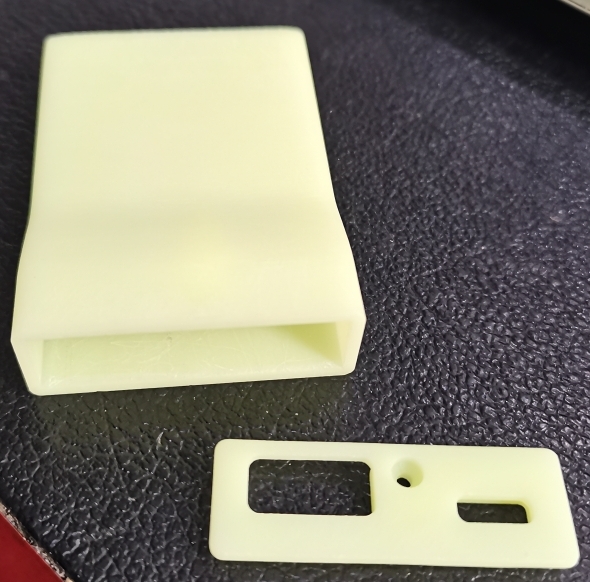

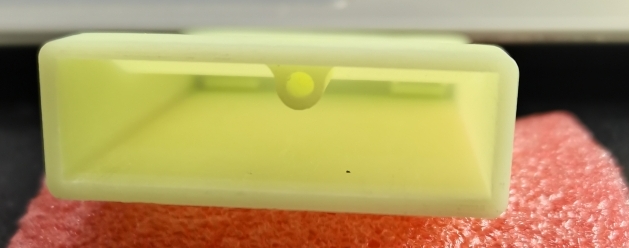

usb-sniffer的作者比较细心,设计、提供了外壳CAD/STL文件,找一家3D打印店就能做出外壳。

我选用的是树脂材料,今天打印好的外壳快递到了,效果还不错。需要注意的是:

1)图纸中长、宽、高尺寸比较精密,面板、壳子有卡槽。先前aozima同学转给我的板子用料扎实,

底面USB-A头焊锡多,需要挫平,否则板子高度与卡槽有1mm左右差异,不能严丝合缝,面板装

不上。2)预留了螺丝位圆孔,图纸中是没有螺纹的。

离线

#111 2023-10-07 21:26:06 分享评论

- jude9d

- 会员

- 注册时间: 2023-10-07

- 已发帖子: 10

- 积分: 5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

lcfmax wrote:

usbbios wrote:

@lcfmax

USB2 HS高速测试通过了吗?

高速测试是通过的,有40MB以上的,但是这个测速应该不涉及USB3343。我怀疑瓶颈在USB3343的并行接口时序上。

瓶颈怎么可能在并行接口时序上? 只要USB3343的ULPI接口是符合ULPI协议的, 就满足60M X 8bit =480Mbit, HS 40M 以上应该差不多了,还有协议开销,sof 开销。

离线

#112 2023-10-08 08:38:07 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@jude9d

如果瓶颈不在FPGA,那我现在剩下怀疑的就是26M晶振问题,我用了一个普通的20PPM的有源晶振,但是作者用的晶振是25PPM,晶振精度比作者还高点,应该不会出问题啊。

@aozima

请问你用的什么型号的26Mhz晶振?

最近编辑记录 lcfmax (2023-10-08 08:42:44)

离线

#113 2023-10-08 11:19:56 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

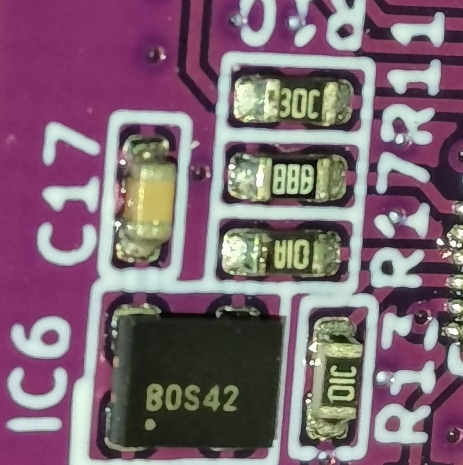

我那块aozima板没装外壳前,对照过IC6,上面文字比较小,肉眼看不太清。

如果是JLC打板,匹配的是下面这个样子:

离线

#114 2023-10-10 10:18:27 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@lcfmax

我把aozima板的外壳拆掉看了,IC6标记如下,没有其他信息了:

@aozima

请问你用的什么型号的26Mhz晶振?

最近编辑记录 usbbios (2023-10-10 10:36:48)

离线

#115 2023-10-10 11:36:54 分享评论

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

晶振就频率,电压,封装引脚, 这3条对得上就行。

ppm看不同应用,但有源晶振基本没太差的。

我同事贴的应该是这个 https://item.szlcsc.com/30858.html

离线

#116 2023-10-10 15:52:58 分享评论

- bigniudiy

- 会员

- 注册时间: 2022-04-18

- 已发帖子: 40

- 积分: 80

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

我也准备自制一个,目前已经发嘉立创PCB打样了,后面有时间再慢慢贴

离线

#117 2023-10-10 17:10:39 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

aozima wrote:

晶振就频率,电压,封装引脚, 这3条对得上就行。

ppm看不同应用,但有源晶振基本没太差的。我同事贴的应该是这个 https://item.szlcsc.com/30858.html

好的,谢谢,我觉得晶振不是主要问题,

@usbbios 原作者的板子已经打样回来了,这几天在用-4的FPGA试试,实在不行,就另外买-5的再试。

不过原作者在几个月前说-4没测试或许可以,后面更新,直接否定了,说-4的时序不符合。估计要看-4的个别体质好的或许可以,一般估计不行。

离线

#119 2023-10-11 08:23:30 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

对于2000HC-5xx FPGA,近日看网上资料,高云有低成本对应兼容替代型号

(未实际验证过,供有兴趣的同学参考)

LCMXO2-2000HC-5TG100 对应高云 GW1N-UV2LQ100X

LCMXO2-2000HC-5TG144 对应高云 GW1N-UV2LQ144X

LCMXO2-2000HC-5BG256 对应高云 GW2AN-UV9XUG256

LCMXO2-2000HC-5FTG256 对应高云 GW2AN-UV9XPG256

离线

#120 2023-10-12 10:04:53 分享评论

- 1847123212

- 会员

- 注册时间: 2019-11-21

- 已发帖子: 70

- 积分: 46

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@lcfmax

不是说-4速度不够吗?

我看了下,应该可以用国产的复制一个,应该也不复杂

离线

#121 2023-10-23 16:48:49 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@lcfmax

原作者板 + 2000HC-4xx FPGA

新单面板 + 2000HC-5xx FPGA

不知测试结果如何? 排查到出错原因了吗?

最近编辑记录 usbbios (2023-10-23 18:02:28)

离线

#122 2023-10-23 18:35:07 分享评论

- 小老弟

- 会员

- 注册时间: 2023-10-23

- 已发帖子: 2

- 积分: 2

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

LCMXO2-2000HC-5TG100 你们在哪买的,淘宝上都是-4,立创上也没货了

离线

#123 2023-10-24 08:28:45 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

小老弟 wrote:

LCMXO2-2000HC-5TG100 你们在哪买的,淘宝上都是-4,立创上也没货了

@小老弟 先不急买-5,

@usbbios 我这里有进展的,等两天,我对比好实验,让大家心里有数。

最近编辑记录 lcfmax (2023-10-24 09:18:22)

离线

#124 2023-10-24 08:42:28 分享评论

- 1847123212

- 会员

- 注册时间: 2019-11-21

- 已发帖子: 70

- 积分: 46

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

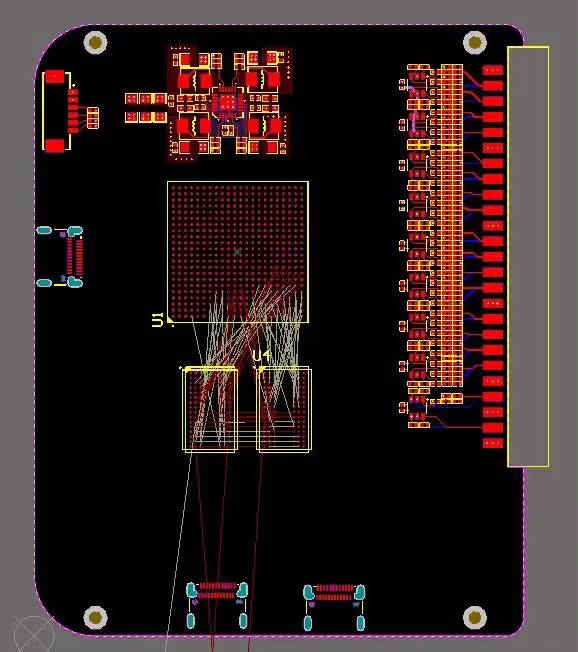

换了个fpga画了一版,还缺点器件,回头补上了就可以测试了。

离线

#125 2023-10-24 09:14:59 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

小老弟 wrote:

LCMXO2-2000HC-5TG100 你们在哪买的,淘宝上都是-4,立创上也没货了

Mouser有。

离线

#126 2023-10-24 10:35:48 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

请问,这个板子是用高云FPGA (GW1N-UV2LQ100X or GW1N-UV2LQ144X) 替换设计么?

它可以像原始设计那样,直接使用usb-sniffer-win.exe把68013、fpga的固件烧录全做了,

不用额外安装软件和下载器吗?

1847123212 wrote:

换了个fpga画了一版,还缺点器件,回头补上了就可以测试了。

/files/members/2468/微信图片_20231024084049.jpg

离线

#127 2023-10-26 09:28:05 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

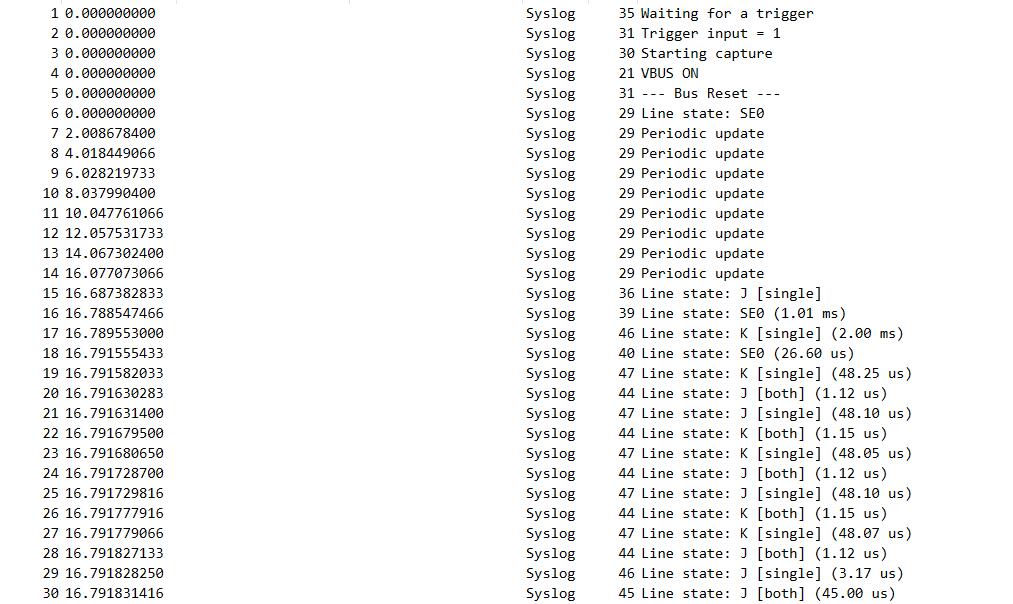

原作者板子+FPGA -5, 自己重新画的4层板+FPGA-4,这两种板子都可以正常工作了。原来自己板子的USB芯片没焊好,导致另外买了-5来验证才发现是焊接问题,浪费了不少时间做了好几套去验证,晕死。

话说这个分析仪很好,把USB信号的所有细节都记录下来了,连从全速识别高速这个过程细节都记录下来了,想分析了解USB协议,这个工具完全能满足。如果wireshark后续版本再加上一些图形化的分析辅助,就完美了。

最近编辑记录 lcfmax (2023-10-26 09:31:04)

离线

#128 2023-10-26 10:59:45 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@lcfmax

十分感谢您的测试和反馈!

不知您新画的的单面版gerber、BOM、坐标文件是否可以共享?

如果不方便共享,您做好的单面版本抓包器,是否有多余可以转让1块给我?

========================================

wireshark新版本,我是迫切希望能增加/增强“Decode as MSC”

解码选项。这样,当遇到类似103#那样的Mass storage包识别

不正确时,可以强制按MSC解码,修正错误。

离线

#129 2023-10-26 13:33:28 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@usbbios

板子有空余的,给你发邮件了,麻烦收一下哈

最近编辑记录 lcfmax (2023-10-26 13:34:11)

离线

#130 2023-10-26 14:26:05 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

lcfmax wrote:

@usbbios

板子有空余的,给你发邮件了,麻烦收一下哈

你好!邮件已收到,已发微信。

离线

#131 2023-10-26 14:46:27 分享评论

- zzm24

- 会员

- 注册时间: 2018-05-07

- 已发帖子: 127

- 积分: 89

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

大家都跟风我也做了一个精简cost down版,晶振换无源,改单面板,比较器换SOP8封装,连68013都换为9002,FPGA-5换-4速度,以为会翻车,哪知道就成功了,正在找替换9032的器件,发现把3个9032拆了也正常使用,有没有大佬分析下fpga代码看看9032有什么用?拆了9032,大数据ISO端点也正常,有图有真相:

离线

#132 2023-10-26 14:48:15 分享评论

- bigniudiy

- 会员

- 注册时间: 2022-04-18

- 已发帖子: 40

- 积分: 80

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

FPGA-4 完全可用的话,完全不需要找国产替代了,价格差不多

离线

#133 2023-10-26 16:41:29 分享评论

- jordonwu

- 会员

- 注册时间: 2021-07-05

- 已发帖子: 66

- 积分: 37

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@lcfmax, 还有多余板子吗? jordon.wu@qq.com 我邮箱,谢谢

离线

#134 2023-10-26 18:10:48 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@zzm24

很高兴看到您的成功。这是第2种单面焊改版成功了。

我不是大佬,也不懂软硬件设计。 我在B站看到有人做过分析,这里人云亦云一下:

max9032是usb-sniffer有特色的设计,作用是检测USB上升沿、下降沿。

离线

#135 2023-10-26 18:21:47 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

我联系了原作者,把这里的情况反馈给他了。 关于-4、-5,他大致说了两个方面:

一、正品-4、-5 FPGA在US的差价仅2$,(在mouser换算成RMB也类似),所以...

二、关于-4成功,他说:

I would expect speed grade 4 to work at least for most of the devices at room temperature.

The synthesis fails dues to timing violations, so there may be issues on some devices, but

it does not fail by a lot, so it would probably work in most cases.

@bigniudiy

bigniudiy wrote:

FPGA-4 完全可用的话,完全不需要找国产替代了,价格差不多

@zzm24

zzm24 wrote:

FPGA-5换-4速度,以为会翻车,哪知道就成功了

离线

#136 2023-10-26 21:30:11 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

jordonwu wrote:

@lcfmax, 还有多余板子吗? jordon.wu@qq.com 我邮箱,谢谢

已经给你发邮件了。

离线

#137 2023-10-26 21:33:49 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@zzm24

使用9032,是用来检测D+,D-的电平,用来识别有没有设备插入,插入的是全速设备,还是高速设备。

刚插入USB设备,提示的SE0,J, K状态应该就是靠比较器来检测的。全速设备的D+ D-电平接近3.3V,高速设备的D+D-是400mV,看看比较器的分压电阻就知道,主要是区分这些电平的。

最近编辑记录 lcfmax (2023-10-26 21:41:30)

离线

#138 2023-10-27 09:25:11 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

我个人想法,精简cost down是好事,同时需考虑保留“必要的”功能。

能把大头的IC费用降下来就已经很好了,其他可能会对性能造成影响、现在还看不出来的小件精简,

暂不考虑了。(精简估计也减不了多少费用,有点得不偿失的味道),晶振还是保留有源的。

另外,这个板子好像看不到BOOT、VCC短接触点,它们是刷MCU固件失败时恢复用的,需要保留。

@zzm24

zzm24 wrote:

精简cost down版,晶振换无源

离线

#139 2023-10-27 11:20:48 分享评论

- zzm24

- 会员

- 注册时间: 2018-05-07

- 已发帖子: 127

- 积分: 89

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

又折腾了一会,现在清楚一些了

首先usb_sniffer_win.exe要复制到C:\Program Files\Wireshark\extcap\usb_sniffer_win.exe,不然Wireshark不识别

MAX9032完全可以替换为国产的高速比较器,甚至不用,不用的话就是抓不到开始的J K SE0状态(感谢lcfmax讲解),用上了就真可以媲美很多商用分析仪了,按照我上面的改法加换国产比较器,PCBA成本可以控制在70元,看来很多人可以干活了

离线

#140 2023-10-28 22:17:05 分享评论

- bigniudiy

- 会员

- 注册时间: 2022-04-18

- 已发帖子: 40

- 积分: 80

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

过程有点曲折,但是结果是好的,我也成功复刻了一个

68013A和FPGA,都是翻新货。成本比用全新的少一点。

在这里我不是推荐用翻新货,是不建议后来者使用翻新货。中间折腾了许久,过程不是很顺利。一度以为翻车了

离线

#141 2023-10-29 11:07:51 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@bigniudiy

考虑到大家很可能使用二手货器件,以降低成本花费,

正好可以说说您的曲折踩坑经历,不顺利的经验也是

很宝贵的。

bigniudiy wrote:

过程有点曲折…中间折腾了许久,过程不是很顺利

离线

#142 2023-10-29 12:07:55 分享评论

- bigniudiy

- 会员

- 注册时间: 2022-04-18

- 已发帖子: 40

- 积分: 80

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

usbbios wrote:

@bigniudiy

考虑到大家很可能使用二手货器件,以降低成本花费,

正好可以说说您的曲折踩坑经历,不顺利的经验也是

很宝贵的。bigniudiy wrote:

过程有点曲折…中间折腾了许久,过程不是很顺利

经验没有可借鉴性,买翻新本身就充满了不确定性,比如买到别的型号打磨的,坏的,都有可能。

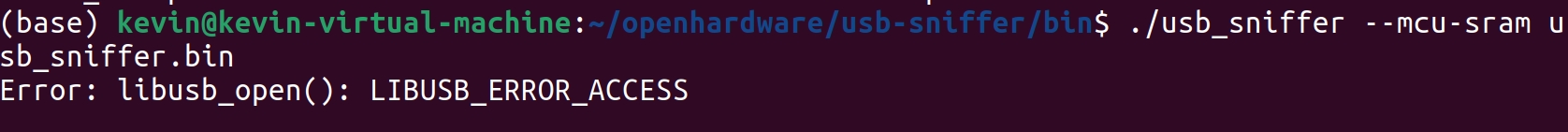

我遇到的问题中,我感觉最大的一个就是:无法烧录固件

本来是想在windows下烧录的,结果提示libusb不支持,中间各种折腾,也是一样,后来想试下Linux,于是装了一个虚拟机然后来烧录,结果还是上面那种报错

到这时已经感觉翻车了,认为芯片有问题 。

不过我仔细考虑了一下,Linux下USB驱动信息已经识别到68013,那么芯片应该没有问题,烧录不进去是不是内部本身有程序?

于是我把芯片在上电的情况下,进行了复位。在复位后快速烧录,结果还真成功了。

离线

#143 2023-10-29 13:46:56 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@bigniudiy

我觉得这个经验很好啊。二手货硬件没问题,但ROM中残留有其他旧固件,没清空直接刷入

usb-sniffer(的新固件)出错。这也给大家提个醒,要先做清空操作...

bigniudiy wrote:

是不是内部本身有程序?于是我把芯片在上电的情况下,进行了复位

最近编辑记录 usbbios (2023-10-29 13:48:24)

离线

#144 2023-10-29 22:31:57 分享评论

- seamas

- 会员

- 注册时间: 2019-12-01

- 已发帖子: 6

- 积分: 31

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

68013内部是SRAM,程序是存储在EEPROM上。板上预留的BOOT和VCC测试点应该是在插入USB时可以用镊子短接一下,让68013无法从EEPROM启动,改用默认的VID/PID枚举,这时烧写程序能正常识别到USB设备,就可以正常擦写EEPROM了。

离线

#145 2023-10-30 11:47:34 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

谢谢您的解释,澄清了模糊认识和错误描述,

这是很好的事。把这个方案琢磨得越透彻,

对将来实际操作和改进帮助越大。

seamas wrote:

68013内部是SRAM,程序是存储在EEPROM上。板上预留的BOOT和VCC测试点应该是在插入USB时可以用镊子短接一下,让68013无法从EEPROM启动,改用默认的VID/PID枚举,这时烧写程序能正常识别到USB设备,就可以正常擦写EEPROM了。

离线

#146 2023-10-30 19:02:36 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@zzm24

希望能看到您的 “有源晶振+国产替代9032+9002+FPGA” 作品问世,想收一个。

zzm24 wrote:

上面的改法加换国产比较器,PCBA成本可以控制

离线

#147 2023-10-31 09:31:48 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

大家有没有开源的比较好的USB示波器项目推荐,想做一个玩玩。

离线

#148 2023-11-01 09:45:55 分享评论

- bigniudiy

- 会员

- 注册时间: 2022-04-18

- 已发帖子: 40

- 积分: 80

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

usbbios wrote:

@zzm24

希望能看到您的 “有源晶振+国产替代9032+9002+FPGA” 作品问世,想收一个。

zzm24 wrote:

上面的改法加换国产比较器,PCBA成本可以控制

个人认为下一步改成,替代比较器+国产FPGA比较给力点

离线

#149 2023-11-01 10:30:55 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@bigniudiy

理论上改国产FPGA是给力。

只是我粗略浏览software下的C源码后,立刻头大,与很多lattice内部的东西耦合。

我拿不准改国产FPGA会给楼上电子专业的同学,额外增加多少工作量?我想,

至少C代码需要重新修改编译?

bigniudiy wrote:

个人认为下一步改成,替代比较器+国产FPGA比较给力点

离线

#150 2023-11-01 11:13:56 分享评论

- bigniudiy

- 会员

- 注册时间: 2022-04-18

- 已发帖子: 40

- 积分: 80

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@usbbios

我来当这个小白鼠,前段时间就有想法了,不过由于没做过,希望不大

这个板子,除了68013没换,其他的都换了

今天发出去打板

离线

#151 2023-11-01 12:10:58 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

FPGA换国产,拿原来代码编译一下,重新配置一下管脚,功能应该问题不大。主要是烧录改动,68013 端的JTAG烧录协议需要相应修改,要不就要用外挂烧录器去烧录FGPA,但这样失去原作者的不用额外编程器的初衷。

离线

#152 2023-11-01 12:20:44 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@bigniudiy

强烈期待您的成功。

如果FPGA厂家资料齐全,命令和接口都说的详细,那会大大帮助修改C代码。

还是建议选择-5、-6级别的FPGA。-4的我用了,虽没打断抓包分析,但有

Hardware buffer overflow出错提示,有点影响心情。

1847同学在124#提了一嘴,已经做出了换FPGA的板子,但不知他换的是啥

国产FPGA,也不知现在进度、遇到的困难。

bigniudiy wrote:

我来当这个小白鼠,前段时间就有想法了,不过由于没做过,希望不大

/files/members/9092/微信截图_20231101111200.jpg

这个板子,除了68013没换,其他的都换了。今天发出去打板

离线

#153 2023-11-01 13:34:46 分享评论

- bigniudiy

- 会员

- 注册时间: 2022-04-18

- 已发帖子: 40

- 积分: 80

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

lcfmax wrote:

FPGA换国产,拿原来代码编译一下,重新配置一下管脚,功能应该问题不大。主要是烧录改动,68013 端的JTAG烧录协议需要相应修改,要不就要用外挂烧录器去烧录FGPA,但这样失去原作者的不用额外编程器的初衷。

是的,FPGA的编译我已经完成了,就等着板子回来,调试68013了

离线

#154 2023-11-01 14:35:20 分享评论

- pldjn_V3S

- 会员

- 注册时间: 2021-04-09

- 已发帖子: 110

- 积分: 118

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

离线

#155 2023-11-01 15:54:56 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

楼上zzm24没换FPGA,倒是把MCU换成了9002,看样子MCU刷固件走得顺。

bigniudiy wrote:

FPGA的编译我已经完成了,就等着板子回来,调试68013了

离线

#156 2023-11-01 18:42:28 分享评论

- smartH666

- 会员

- 注册时间: 2022-08-01

- 已发帖子: 1

- 积分: 1

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@bigniudiy

建议68013换芯佰微CBM9002试试,全国产FPGA+MCU更有香

离线

#157 2023-11-05 12:13:44 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

情况通报:

usb-sniffer抓USB启动期间、UEFI/BIOS发的USB包。当被测U盘是USB3盘、被测机器是

USB3口机器时(由于连接的抓包器是USB2口,被测USB3优盘、被测机器USB3口将降速至

high speed工作)。

但是,抓包器wireshark将有很大几率只显示Detected full speed信息,没有Detected high

speed信息。(被测U盘、PC实际已工作在high speed状态,只是抓包器wireshark未显示

Detected high speed信息)

经与原作者交流,这不是BUG。是因为被测机器SE0持续时间过短(一般在30uS以下),不符合

USB规范造成。作者是按默认SE0持续时间在1mS左右来的,SE0持续时间过短将被忽略,不会

进入Detected high speed流程。

如果您想看到Detected high speed信息,请自行修改源代码调试。

离线

#158 2023-11-06 10:38:18 分享评论

- 1847123212

- 会员

- 注册时间: 2019-11-21

- 已发帖子: 70

- 积分: 46

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

smartH666 wrote:

@bigniudiy

建议68013换芯佰微CBM9002试试,全国产FPGA+MCU更有香

这个没必要 68013也不贵,CBM9002说不定反而量少还贵些

离线

#159 2023-11-06 16:44:44 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@1847123212

不知您在124#设计的 换国产FPGA新板子 测试运行情况如何? 推测应该是高性价比的优秀成品?

1847123212 wrote:

换了个fpga画了一版...可以测试了。

1847123212 wrote:

这个没必要 68013也不贵,CBM9002说不定反而量少还贵些

离线

#160 2023-11-06 19:07:02 分享评论

- yywyai

- 会员

- 注册时间: 2019-01-17

- 已发帖子: 64

- 积分: 89

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

68013+XC6SLX9 测试OK

离线

#161 2023-11-06 21:02:21 分享评论

#162 2023-11-07 06:44:28 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@yywyai

首先祝贺您的改版测试成功!

其次,因图片光线强,看不清芯片丝印,问一下这个板子的细节:

1、是XC6SLX9的哪个子型号,2TQG144? 它大致对应Lattice FPGA的-4、-5、-6哪个级别?

2、看图片用了外置JTAG烧录器?不用额外编程器,像原版那样直接用USB可以刷固件么?

3、有类似VCC-BOOT那样的短接触点么?

4、相对于原版,新板子成本?

yywyai wrote:

68013+XC6SLX9 测试OK

离线

#164 2023-11-07 09:44:48 分享评论

- yywyai

- 会员

- 注册时间: 2019-01-17

- 已发帖子: 64

- 积分: 89

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

1、XC6SLX9 -2,基本上大部分FPGA速度等级都能满足USB Sniffer,毕竟最高时钟才60M,温度的话自己玩的 -C -I都是无所谓的。

2、基本上FPGA都可以通过MCU配置,只是需要修改代码。

3、触电滴没有,镊子短接EEPROM地址引脚

4、我用的都是已有的元件,只买了比较器,所以并不是从成本出发。

结论就是国产FPGA应该没有问题的。另外我的线缆用的也是中国制造的

离线

#165 2023-11-07 11:20:27 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@yywyai

十分感谢您的认真解答!

问成本的原因是,原作者也(有点带吐槽口吻)说,大洋那边现在IC原器件供应不够稳定、持续,

(不像中国这样方便)。我已经收了原版复刻,现在有几种国产器件改版测试成功,我想等大家

稳定下来后,价格合适再收1个。

yywyai wrote:

1、XC6SLX9 -2,基本上大部分FPGA速度...

离线

#166 2023-11-20 15:52:17 分享评论

- bigniudiy

- 会员

- 注册时间: 2022-04-18

- 已发帖子: 40

- 积分: 80

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

进度预告,这是第二版PCB。

第一版可以验证国产高云FPGA也可以用,由于我把USB3343也换了,FPGA没有抓到数据,第二版要改回USB3343 :)希望我推断是正确的。

关于不用外置JTAG烧录器,目前还没有调通,打算先把功能都实现了,再来慢慢修改代码。

离线

#167 2023-11-20 23:37:20 分享评论

- HunanJLR

- 会员

- 注册时间: 2023-11-19

- 已发帖子: 5

- 积分: 0

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

普通的用BusHound软件抓取数据,HID通信够用了

离线

#168 2023-11-24 20:15:22 分享评论

- pldjn_V3S

- 会员

- 注册时间: 2021-04-09

- 已发帖子: 110

- 积分: 118

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

HunanJLR wrote:

普通的用BusHound软件抓取数据,HID通信够用了

BusHound的问题是软件驱动要读走数据才能看到,其他的都挺好。

离线

#169 2023-11-28 23:13:20 分享评论

- bigniudiy

- 会员

- 注册时间: 2022-04-18

- 已发帖子: 40

- 积分: 80

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

交卷来了

高云的JTAG_EN脚逻辑和LATTICE是反的,要正常使用需要重新编译USB_sniffer,目前是直接断开了JTAG_EN脚的连线,使用没问题

离线

#170 2023-11-29 08:31:39 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@bigniudiy

用的比较器的型号是啥?

离线

#171 2023-11-29 08:40:51 分享评论

- jordonwu

- 会员

- 注册时间: 2021-07-05

- 已发帖子: 66

- 积分: 37

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@bigniudiy

是要重新编译那个wireshark plugin吗?

离线

#172 2023-11-29 10:52:35 分享评论

- bigniudiy

- 会员

- 注册时间: 2022-04-18

- 已发帖子: 40

- 积分: 80

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

lcfmax wrote:

@bigniudiy

用的比较器的型号是啥?

在JLC上随便找的便宜货

LM2903YPT

离线

#173 2023-11-29 10:54:35 分享评论

- bigniudiy

- 会员

- 注册时间: 2022-04-18

- 已发帖子: 40

- 积分: 80

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

jordonwu wrote:

@bigniudiy

是要重新编译那个wireshark plugin吗?

是的,不重新修改,烧录68013的固件也有问题,会出错,原版的程序会在烧录前验证FPGA ID对不对,不对就退出烧录

离线

#174 2023-11-29 14:46:38 分享评论

- 小老弟

- 会员

- 注册时间: 2023-10-23

- 已发帖子: 2

- 积分: 2

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@bigniudiy

高云fpga的固件可以直接用lattice,需要移植吗

离线

#175 2023-11-29 17:39:38 分享评论

- bigniudiy

- 会员

- 注册时间: 2022-04-18

- 已发帖子: 40

- 积分: 80

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

小老弟 wrote:

@bigniudiy

高云fpga的固件可以直接用lattice,需要移植吗

要移植的,需要重新编译

离线

#176 2023-11-29 18:41:24 分享评论

- EricWang56888

- 会员

- 注册时间: 2023-11-29

- 已发帖子: 1

- 积分: 1

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@metro

请问,现在这个项目做得怎么样了,我这边也打了一个板来测试LUNA ,但是遇到些问题,是否方便加个V : 15899795033

离线

#177 2023-11-29 18:41:52 分享评论

- EricWang56888

- 会员

- 注册时间: 2023-11-29

- 已发帖子: 1

- 积分: 1

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@bigniudiy

我这边也打了一个板来测试LUNA ,但是遇到些问题

离线

#178 2023-11-29 18:49:35 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

bigniudiy wrote:

lcfmax wrote:

@bigniudiy

用的比较器的型号是啥?

在JLC上随便找的便宜货

LM2903YPT

LM2903YPT 应该是开漏的,FPGA那边的输入IO需要设置上拉功能才行,要不就外面加上拉电阻。

离线

#179 2023-11-29 21:50:21 分享评论

- bigniudiy

- 会员

- 注册时间: 2022-04-18

- 已发帖子: 40

- 积分: 80

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

lcfmax wrote:

bigniudiy wrote:

lcfmax wrote:

@bigniudiy

用的比较器的型号是啥?

在JLC上随便找的便宜货

LM2903YPTLM2903YPT 应该是开漏的,FPGA那边的输入IO需要设置上拉功能才行,要不就外面加上拉电阻。

确实没注意到,不过我试了一下,HS模式也能正常识别

最近编辑记录 bigniudiy (2023-11-29 21:58:00)

离线

#180 2023-11-30 11:02:52 分享评论

#182 2023-12-04 15:25:37 分享评论

#183 2023-12-17 17:04:31 分享评论

- liuse2ee

- 会员

- 注册时间: 2018-07-08

- 已发帖子: 7

- 积分: 2

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

不考虑物理层,只做抓包分析协议的话还是好做的。

离线

#184 2024-01-12 08:50:00 分享评论

- taozhiwei22

- 会员

- 注册时间: 2024-01-12

- 已发帖子: 1

- 积分: 1

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

mysteryli wrote:

我这里有个硬件的加密狗要破解,预算1w以内,有没有感兴趣的老板来接单

q

19995451

离线

#185 2024-01-23 16:34:02 分享评论

- wl989898

- 会员

- 注册时间: 2024-01-15

- 已发帖子: 42

- 积分: 5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

动手能力太强了!

离线

#186 2024-06-14 12:48:52 分享评论

- Haven

- 会员

- 注册时间: 2024-06-14

- 已发帖子: 1

- 积分: 1

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

metro wrote:

趁下班时间画了一版,大家猜猜这是什么方案😏

/files/members/1510/AQUA-Lite.png

这个需要怎么使用呢?用什么上位机?usb-sniffer-lite也没写怎么使用

离线

#187 2024-09-10 09:53:33 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

去年底因为个人原因,没能再继续关注,现在有空回来看看。

短短半年多时间,开源USB2.0协议分析仪ataradov/usb-sniffer在中国就百花齐放商品化,淘宝、闲鱼换个名大量在售,看销量,

用的人似乎还挺多。我作为本帖首个推荐介绍者,也很有成就感,哈~

在售产品看配置,应该是-4级的居多,我不知道有多少是本帖层主们在搞。我觉得,可优化的地方有2条:

一、硬件上。使用国产FPGA、其他配件,降低成本。可以的话,同时提高配置至-5、-6级...加量不加价也是挺好的。

二、软件上。优化Wireshark 解码,这是影响用户体验的关键。比如常用的USB存储设备类(Mass Storage),增加右键菜单选项,

强制Decode as Mass storage。这是为了防止Wireshark默认没能正常解码时,自己进行强制解码。

=============================================================

当然,野心再大一点,未来的目标是USB3协议分析仪。 解码器软件不好做,能否先探讨DIY硬件抓包器可行性? 抓USB3包,

我不知道得要多大的资源,PCB DIY预估成本得是多少,这就有赖诸位懂行的大佬匡算了。

最近编辑记录 usbbios (2024-09-10 09:54:46)

离线

#188 2024-10-05 17:26:48 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

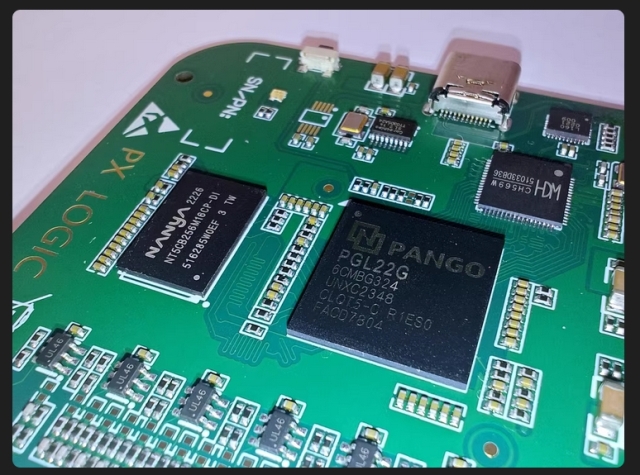

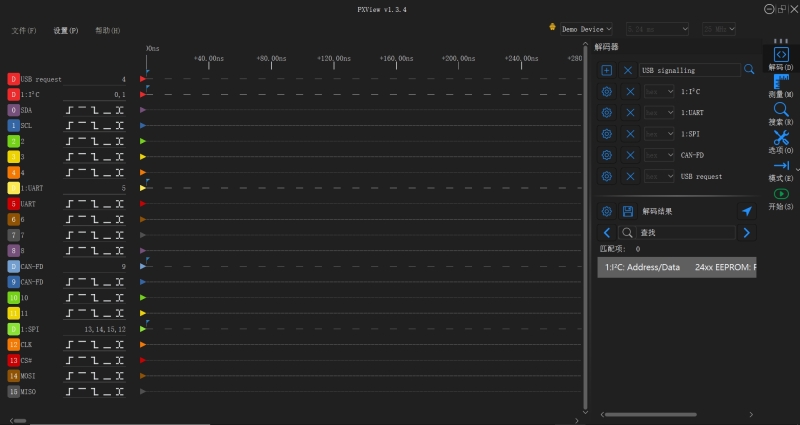

USB3.0协议分析仪的抓包器硬件,总算有点影子毛了。

章鱼哥搞出了PX Logic usb3.0超高速逻辑分析仪,淘宝已开卖。介绍帖子在这https://zhuanlan.zhihu.com/p/601285602。

硬件基于国产USB3.0芯片沁恒ch569w与国产紫光FPGA PGL22G ;软件是开源PXview项目。

然后,UPV的作者说,要和章鱼哥计划USB 3.0分析仪,这是一个binggo我心事的想法。

我一直想要个价格能接受的USB3.0协议分析仪(流行的商用USB3分析仪,动辄几万的价格,实在玩不起),现在难题回到上位机软件。

请路过的佬们扫一眼,章鱼的这个硬件配置是不是可以做USB3.0协议分析仪的基础平台;解码软件设计,能不能复制usb sniffer的

成功思路,用wireshark做上位机软件,降低解码开发难度。

最近编辑记录 usbbios (2024-10-05 17:31:14)

离线

#189 2024-11-15 16:59:05 分享评论

- david

- 会员

- 注册时间: 2018-03-05

- 已发帖子: 397

- 积分: 328.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

这个不错 能否把wireshark相关功能集成在sigrok里

最近编辑记录 david (2024-11-15 17:03:00)

离线

#190 2025-02-10 15:00:16 分享评论

- zjsx133

- 会员

- 注册时间: 2018-07-23

- 已发帖子: 101

- 积分: 36

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@bigniudiy

请问下载fpga的文件是要高云的烧录器吗?还是可以用68013来下载?

离线

#191 2025-10-18 13:53:23 分享评论

- chujunzbdx

- 会员

- 注册时间: 2025-03-28

- 已发帖子: 2

- 积分: 2

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@lcfmax

我想问下官方原版本,是否存在被监测口不能识别的情况

离线

#192 2025-10-18 13:56:04 分享评论

- chujunzbdx

- 会员

- 注册时间: 2025-03-28

- 已发帖子: 2

- 积分: 2

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@bigniudiy

我想咨询下,官方的原始版本,被监测USB口是否存在无法识别的情况

离线

#196 2025-11-26 11:32:27 分享评论

- usbbios

- 会员

- 注册时间: 2023-03-22

- 已发帖子: 46

- 积分: 131

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

传说中USB3协议分析仪有确切的影子了。章鱼哥开发中的USB3协议分析仪硬件碟照如下,

上位机软件计划外包给UPV的作者xtoolbox,预计售价5K。这个USB分析仪是附带的,

按章鱼的设计,是集成了USB3分析、mipi2.5分析,再送个32通道的逻分。路过大佬可参考一下。

离线

#197 2025-11-27 08:38:18 分享评论

- le062

- 会员

- 注册时间: 2019-02-07

- 已发帖子: 75

- 积分: 65.5

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

chujunzbdx wrote:

@lcfmax

我想问下官方原版本,是否存在被监测口不能识别的情况

首先,监测线不能太长,尽量总长不要超过两米。其次,USB高速尽量用带屏蔽的USB数据线。

离线

#198 2025-11-27 09:10:41 分享评论

- astankvai

- 会员

- 注册时间: 2021-02-23

- 已发帖子: 75

- 积分: 75

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

@usbbios

MIPI 可以分析HS吗? 如果可以HS, 那就NB了。

离线

#199 2026-02-07 01:18:45 分享评论

- xiaoerge

- 会员

- 注册时间: 2020-07-16

- 已发帖子: 9

- 积分: 9

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

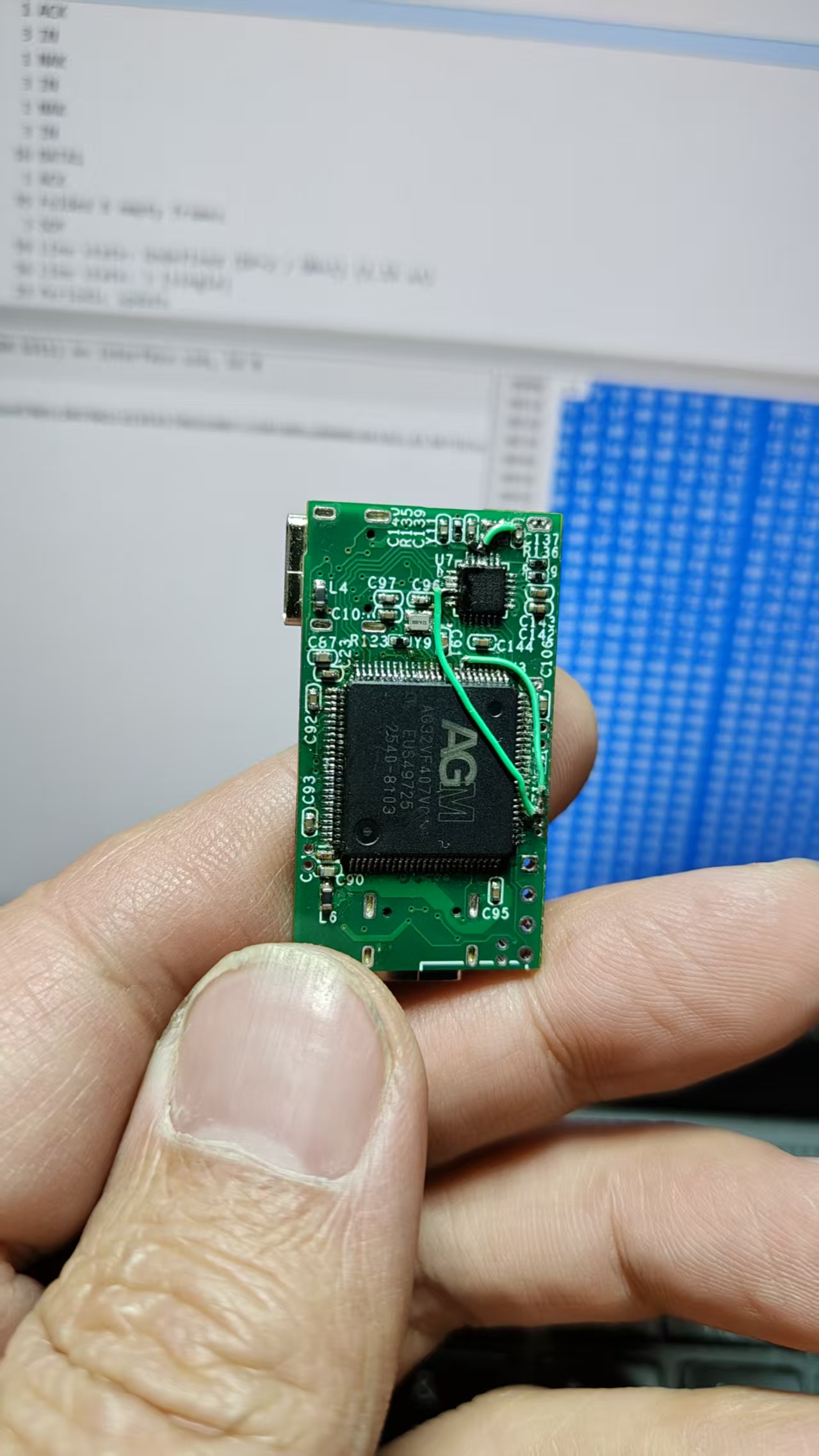

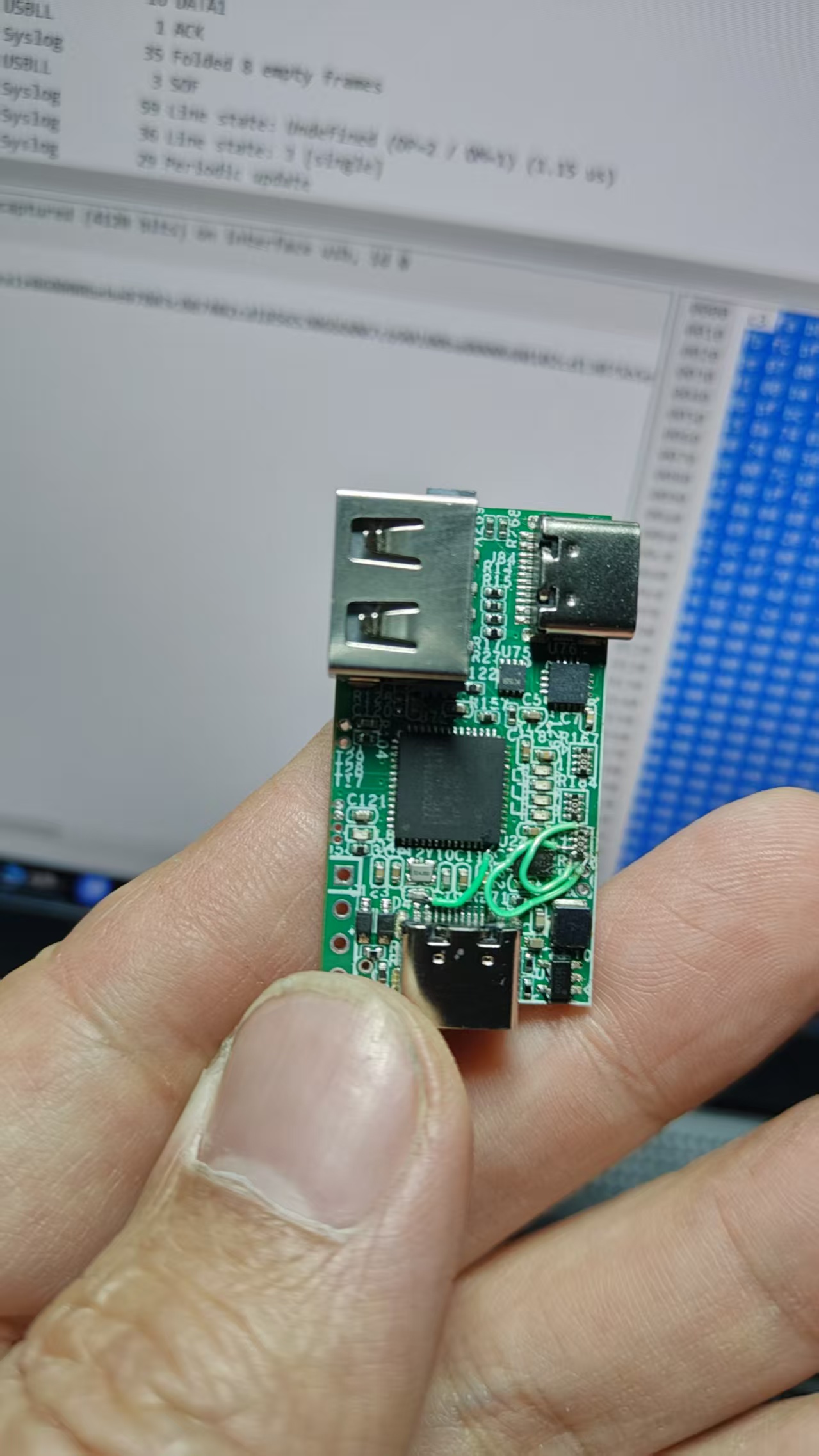

USB SNIFFER我也做一板,双面器件,尺寸约2*3.8cm,FPGA用的AG32VF407VGT6,比较器搞的LM393和LM339,终于基本调通,PCB搞出几个低级错误,搞得调试郁闷之极

下一步打算FPGA 100脚换成64脚搞一个

离线

#200 2026-02-07 01:23:39 分享评论

- xiaoerge

- 会员

- 注册时间: 2020-07-16

- 已发帖子: 9

- 积分: 9

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

AG32VF407的块RAM容量只有原版的一半,将代码定义改小了,不知道会不会有问题

离线

#201 2026-02-13 17:11:37 分享评论

- Gaudi

- 会员

- 注册时间: 2023-02-04

- 已发帖子: 4

- 积分: 4

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

xiaoerge wrote:

AG32VF407的块RAM容量只有原版的一半,将代码定义改小了,不知道会不会有问题

68013 能换掉吗?

离线

#202 2026-02-25 01:05:32 分享评论

- xiaoerge

- 会员

- 注册时间: 2020-07-16

- 已发帖子: 9

- 积分: 9

Re: 怒开新坑,自制低成本高速USB分析仪(随缘更新)

Gaudi wrote:

xiaoerge wrote:

AG32VF407的块RAM容量只有原版的一半,将代码定义改小了,不知道会不会有问题

68013 能换掉吗?

有源码,想换都可以,68013的代码不复杂,USB部分一方面是处理上位机的命令,通过两根线发送命令给FPGA,另一方面将FPGA捕获的数据发送到上位机,这部分数据68013是直通的,FPGA组织两种数据包,一种是状态包,数据头4个字节,一种是数据包,数据头7个字节,我看数据头的开销也不小,每个NAK都添加了数据头,连续大量数据有可能会溢出

楼上有用国产型号直接替代的

离线

东莞哇酷科技有限公司开发