- 首页

- » 搜索

- » kemp 发表的帖子

页次: 1

#2 全志 SOC » T113S3点亮ST7701S MIPI屏幕显示正常但出现抖动问题 » 2024-10-26 17:20:18

- kemp

- 回复: 4

这几天在测试一款新屏幕,ST7701S MIPI接口 480*480,显示颜色和位置正常,但是屏幕会一直抖动,视频如下

测试MIPI CLK时钟时,发现频率有点奇怪,只有4MHz来着,按配置的参数,应该要去到100MHz吧

dsi clk = Bitclk / 2 = H-total x V-total x fps x 位深 / lane number / 2 = 528*501*60*24/2/2 = 95,230,080

有进行过几个排查方法:

root@TinaLinux:/# cat /sys/class/disp/disp/attr/sys

screen 0:

de_rate 300000000 hz, ref_fps:60

mgr0: 480x480 fmt[rgb] cs[0x204] range[full] eotf[0x4] bits[8bits] err[0] force_sync[0] unblank direct_show[false] iommu[1]

dmabuf: cache[0] cache max[0] umap skip[0] umap skip max[66]

lcd output backlight( 50) fps:61.3 480x 480

err:0 skip:116 irq:7828 vsync:0 vsync_skip:0

BUF enable ch[1] lyr[0] z[16] prem[N] a[pixel 255] fmt[ 0] fb[ 480, 480; 480, 480; 480, 480] crop[ 0, 0, 480, 480] frame[ 0, 0, 480, 480] addr[ 0, 0, 0] flags[0x 0] trd[0,0]硬件部分,因为有点亮过其它分辨率的屏幕,所以可以排除硬件原因。

各位大佬,能否给点建议呢?

DTS配置如下:

&lcd0 {

lcd_used = <1>; //# 启用lcd

lcd_driver_name = "st7701s"; //# 使用 default_lcd 驱动

lcd_backlight = <50>;

lcd_if = <4>; //# 0:rgb 4:dsi

lcd_dsi_if = <0>;

lcd_dsi_lane = <2>;

pinctrl-0 = <&dsi2lane_pins_a>;

pinctrl-1 = <&dsi2lane_pins_b>;

lcd_x = <480>; //# 宽度

lcd_y = <480>; //# 高度

lcd_width = <72>; //# 屏幕物理宽度,单位 mm

lcd_height = <72>; //# 屏幕物理高度,单位 mm

lcd_dclk_freq = <16>; //屏幕时钟 MHz

lcd_hbp = <28>; //hbp+hspw

lcd_ht = <528>; //lcd_x+hs+hbp+hspw

lcd_hspw = <8>; //hspw

lcd_vbp = <16>; //vbp+vspw

lcd_vt = <501>; //lcd_y+vs+vbp+vspw

lcd_vspw = <3>; //vspw

lcd_pwm_used = <1>; //# 启用背光 PWM

lcd_pwm_ch = <7>; //# 使用 PWM 通道 9

lcd_pwm_freq = <10000>; //# PWM 频率,单位 Hz

lcd_pwm_pol = <0>; //# 背光 PWM 的极性

lcd_pwm_max_limit = <255>;

lcd_dsi_format = <0>;

lcd_dsi_te = <0>;

lcd_frm = <0>;

lcd_gamma_en = <0>;

lcd_cmap_en = <0>;

lcd_gpio_0 = <&pio PD 20 GPIO_ACTIVE_HIGH>;

};屏参如下

static struct LCM_setting_table lcm_initialization_setting[] = {

{0x11, 1, {0x00} },

{REGFLAG_DELAY, 120, {} },

{0xff, 5, {0x77,0x01,0x00,0x00,0x10} },

{0xc0, 2, {0x3B,0x00} }, //NL = (0x3B+1 )* 8 = 480

{0xc1, 2, {0x0D,0x02} }, //VBP=13 vfp=2

{0xc2, 2, {0x31,0x08} },

//Inversion Selection 2 Dot 30-1dot 31-2dot 37-column

//PCLK=512+(RTNI[4:0]x16) = 512+8*16 = 640

{0xb0, 16, {0x00,0x11,0x18,0x0E,0x11,0x06,0x07,0x08,0x07,0x22,0x04,0x12,0x0F,0xAA,0x31,0x18} },

{0xb1, 16, {0x00,0x11,0x19,0x0E,0x12,0x07,0x08,0x08,0x08,0x22,0x04,0x11,0x11,0xA9,0x32,0x18} },

{0xff, 5, {0x77, 0x01, 0x00, 0x00, 0x11} },

{0xb0, 1, {0x60} },

{0xb1, 1, {0x30} },

{0xb2, 1, {0x87} },

{0xb3, 1, {0x80} },

{0xb5, 1, {0x49} },

{0xb7, 1, {0x85} },

{0xb8, 1, {0x21} },

{0xc1, 1, {0x78} },

{0xc2, 1, {0x78} },

{REGFLAG_DELAY, 20, {} },

{0xe0, 3, {0x00, 0x1b, 0x02} },

{0xe1, 11,{0x08,0xA0,0x00,0x00,0x07,0xA0,0x00,0x00,0x00,0x44,0x44} },

{0xe2, 12,{0x11,0x11,0x44,0x44,0xED,0xA0,0x00,0x00,0xEC,0xA0,0x00,0x00} },

{0xe3, 4, {0x00, 0x00, 0x11, 0x11} },

{0xe4, 2, {0x44, 0x44} },

{0xe5, 16,{0x0A,0xE9,0xD8,0xA0,0x0C,0xEB,0xD8,0xA0,0x0E,0xED,0xD8,0xA0,0x10,0xEF,0xD8,0xA0} },

{0xe6, 4, {0x00, 0x00, 0x11, 0x11} },

{0xe7, 2, {0x44, 0x44} },

{0xe8, 16,{0x09,0xE8,0xD8,0xA0,0x0B,0xEA,0xD8,0xA0,0x0D,0xEC,0xD8,0xA0,0x0F,0xEE,0xD8,0xA0} },

{0xeb, 7, {0x02,0x00,0xE4,0xE4,0x88,0x00,0x40} },

{0xec, 2, {0x3c, 0x00} },

{0xed, 16, {0xAB,0x89,0x76,0x54,0x02,0xFF,0xFF,0xFF,0xFF,0xFF,0xFF,0x20,0x45,0x67,0x98,0xBA} },

{0xef, 6, {0x10,0x0D,0x04,0x08,0x3F,0x1F} },

{0xff, 5, {0x77,0x01,0x00,0x00,0x00} },

{0xff, 5, {0x77,0x01,0x00,0x00,0x13} },

{0xe8, 2, {0x00,0x0E} },

{0xff, 5, {0x77,0x01,0x00,0x00,0x00} },

{0x11, 1, {0x00} },

{REGFLAG_DELAY, 120, {} },

{0xff, 5, {0x77,0x01,0x00,0x00,0x13} },

{0xe8, 2, {0x00,0x0C} },

{REGFLAG_DELAY, 10, {} },

{0xe8, 2, {0x00,0x00} },

{0xff, 5, {0x77,0x01,0x00,0x00,0x00} },

{0x3A, 1, {0x66} },

{0x2A, 1, {0x00} },

{0x11, 1, {0x00} },

{REGFLAG_DELAY, 120, {} },

{0x29, 1, {0x00} },

{REGFLAG_DELAY, 20, {} },

{REGFLAG_END_OF_TABLE, 0x00, {} }

};#3 全志 SOC » T113屏参和屏驱动在kernel可以正常点亮工作,同样的代码放到uboot,打开uboot显示后,出现一侧花屏问题 » 2024-10-12 10:50:16

- kemp

- 回复: 0

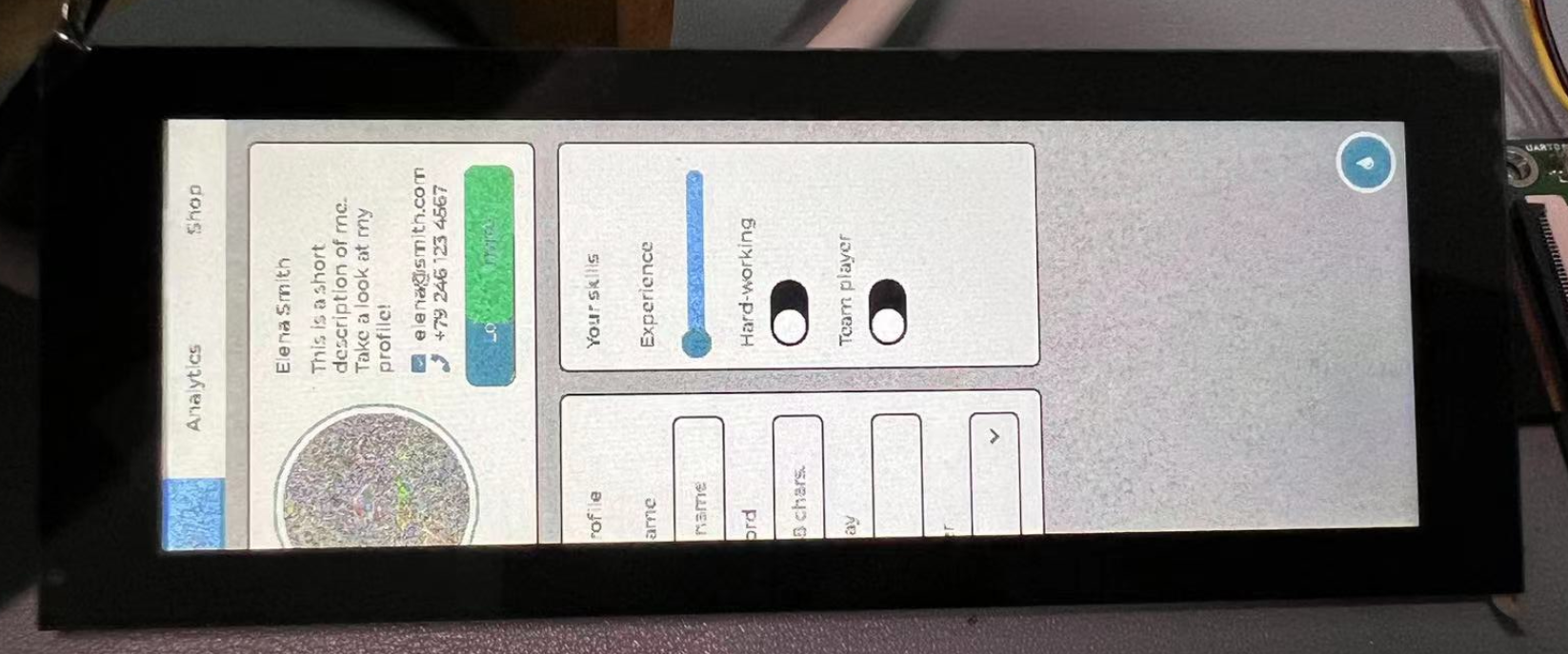

这两天在调ST7701S的一款480*480 RGB方屏,uboot启动屏幕右侧1/4是花屏的,其它区域正常

然后关闭uboot显示驱动,把驱动代码放到kernel中打开屏驱,发现显示却是正常的。

已尝试方法:

1、uboot的驱动中添加日志,运行是已打印添加日志,意味着驱动文件是我更改的

2、uboot驱动文件中,也尝试过加大过延时,本来是20,50,100的,现在改为200,200,100也无效

LCD_OPEN_FUNC(sel, LCD_power_on, 200);

LCD_OPEN_FUNC(sel, LCD_panel_init, 200);

LCD_OPEN_FUNC(sel, sunxi_lcd_tcon_enable, 100);

3、修改加大过dts的hvp和ht,显示还是右侧花屏

4、屏参部分,设置的是DE模式,所以HS信号线应该不影响?

我的疑问是,一份屏参在kernel下运行正常,放到uboot中异常,还有其它的原因不?各位大佬给点思路呗。

已解决,dts配置错误

#4 Re: 全志 SOC » F133驱动MIPI JD9365的条屏 » 2024-09-14 11:04:31

我也遇到这个问题了,求指引

#7 Re: 全志 SOC » 使用T113S3 tina linux驱动ST7701S RGB长条屏幕,显示lvgl demo分两半问题 » 2024-08-30 11:34:01

@晕哥

实际面板参数如下

LCM outline size 40.37 (H) x 117.90 (V) mm

Active area 36.77 (H) x 110.30 (V) mm

Number of pixels 320(H)X960(V)

Pixel arrangement RGB stripe - Pixel Pitch 114.9x114.9 um

Controller / Driver ST7701S

Data interface SPI3W+RGB18bit

我使用400x960是因为厂家给的参数是这样的:

HS:10 HBP:30 HFP: 50

VS:2 VBP:15 VFP:17

400*960

我这边拿到的ST7701S手册看,只能看到这样的分辨率,难道是旧版本?

Display Resolution

- 480*RGB (H) *864(V) (WVGA)

- 480*RGB (H) *854(V)

- 480*RGB (H) *800(V)

- 480*RGB (H) *720(V)

- 480*RGB (H) *640(V) (VGA)

- 480*RGB (H) *360(V)

#8 Re: 全志 SOC » 使用T113S3 tina linux驱动ST7701S RGB长条屏幕,显示lvgl demo分两半问题 » 2024-08-30 09:57:28

我对比了下ST7701S手册中,描述到支持最高分辨率480RGBX864 in resolution

但是LCD_panel_init初始的C0H部分,Display Line Setting的是960,不知道是否会有影响呢?

LNESET (C0h/C000h): Display Line Setting

LDE_EN=”0”,no add delta line , NL= (Line[6:0]+1)*8

LCD_WRITE_COMMAND (0xC0);

LCD_WRITE_DATA (0x77);

LCD_WRITE_DATA (0x00);

(0x77+1)*8 = 960

#10 Re: 全志 SOC » 使用T113S3 tina linux驱动ST7701S RGB长条屏幕,显示lvgl demo分两半问题 » 2024-08-29 22:54:45

LCD_panel_init()

这个里面是初始化成 400*960 吗?

感谢晕哥指点,是的,这个LCD_panel_init函数中的参数是根据厂家提供的启动参数配置。

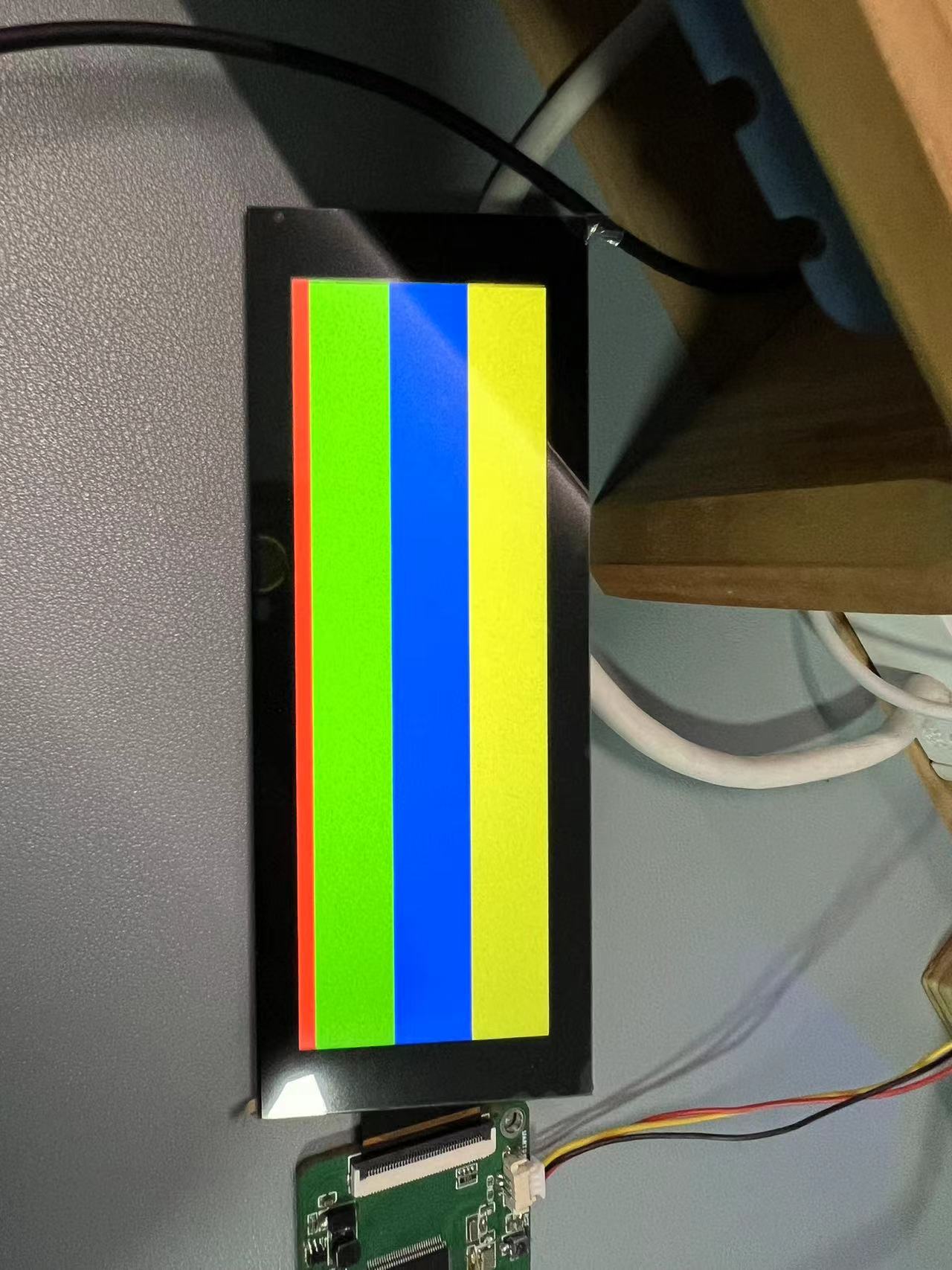

今天我改了下lcd_dclk_freq,从29改到20,现在显示是这样的,会不会是PCB设计的原因呢?

root@TinaLinux:/# cat /sys/class/disp/disp/attr/sys

screen 0:

de_rate 300000000 hz, ref_fps:47

mgr0: 400x960 fmt[rgb] cs[0x204] range[full] eotf[0x4] bits[8bits] err[0] force_sync[0] unblank direct_show[false] iommu[1]

dmabuf: cache[0] cache max[0] umap skip[0] umap skip max[12]

lcd output backlight( 50) fps:49.7 400x 960

err:0 skip:42 irq:1399 vsync:0 vsync_skip:0

BUF enable ch[1] lyr[0] z[16] prem[N] a[pixel 255] fmt[ 0] fb[ 400, 960; 400, 960; 400, 960] crop[ 0, 0, 400, 960] frame[ 0, 0, 400, 960] addr[ 0, 0, 0] flags[0x 0] trd[0,0]另外,界面抖动得比较厉害,左侧有明显颗粒

#11 Re: 全志 SOC » 使用T113S3 tina linux驱动ST7701S RGB长条屏幕,显示lvgl demo分两半问题 » 2024-08-28 22:08:41

补充下运行时的屏参

root@TinaLinux:/data# cat /sys/class/disp/disp/attr/sys

screen 0:

de_rate 300000000 hz, ref_fps:60

mgr0: 400x960 fmt[rgb] cs[0x204] range[full] eotf[0x4] bits[8bits] err[0] force_sync[0] unblank direct_show[false] iommu[1]

dmabuf: cache[0] cache max[0] umap skip[0] umap skip max[4]

lcd output backlight( 50) fps:77.5 400x 960

err:0 skip:19 irq:1880 vsync:0 vsync_skip:0

BUF enable ch[1] lyr[0] z[16] prem[N] a[pixel 255] fmt[ 0] fb[ 400, 960; 400, 960; 400, 960] crop[ 0, 0, 400, 960] frame[ 0, 0, 400, 960] addr[ 0, 0, 0] flags[0x 0] trd[0,0]

depth[ 0] #12 全志 SOC » 使用T113S3 tina linux驱动ST7701S RGB长条屏幕,显示lvgl demo分两半问题 » 2024-08-28 22:06:36

- kemp

- 回复: 11

问题卡了两周,各位路过的大佬帮忙看看呗!感激不尽

使用T113S3 tina linux驱动ST7701S RGB屏幕,打开lvgl demo,显示分了两半的问题:

通过指令保存的图片是正常的:

echo 0 > /sys/class/disp/disp/attr/disp

echo /data/1.bmp > /sys/class/disp/disp/attr/capture_dump

厂家给的参数:

HS:10 HBP:30 HFP: 50

VS:2 VBP:15 VFP:17

400*960

DTS部分配置如下:

&disp {

disp_init_enable = <1>;

disp_mode = <0>;

screen0_output_type = <1>;

screen0_output_mode = <4>;

screen1_output_type = <3>;

screen1_output_mode = <4>;

screen1_output_format = <0>;

screen1_output_bits = <0>;

screen1_output_eotf = <4>;

screen1_output_cs = <257>;

screen1_output_range = <2>;

screen1_output_scan = <0>;

screen1_output_aspect_ratio = <8>;

dev0_output_type = <1>;

dev0_output_mode = <4>;

dev0_screen_id = <0>;

dev0_do_hpd = <0>;

dev1_output_type = <4>;

dev1_output_mode = <10>;

dev1_screen_id = <1>;

dev1_do_hpd = <1>;

def_output_dev = <0>;

disp_rotation_used = <1>;

degree0 = <0>;

fb0_format = <0>;

fb0_buffer_num = <1>;

fb0_width = <400>;

fb0_height = <960>; /*read from lcd*/

fb1_format = <0>;

fb1_width = <0>;

fb1_height = <0>;

chn_cfg_mode = <1>;

disp_para_zone = <1>;

};&lcd0 {

lcd_used = <1>;

lcd_driver_name = "st7701s_rgb";

lcd_if = <0>; //0:rgb 1:CPU/I80 2:保留 3:lvds 4:dsi

lcd_hv_if = <0>; //0:并行rgb

lcd_width = <46>; //物理宽度 mm

lcd_height = <110>; //物理高度 mm

lcd_x = <400>; //宽度

lcd_y = <960>; //高度

lcd_dclk_freq = <29>; //屏幕时钟 MHz

lcd_hbp = <40>; //hbp+hspw,从时序图可以看到hspw包含在hbp中,所以只需要填写hbp的值

lcd_ht = <490>; //lcd_x+hs+hbp+hspw

lcd_hspw = <10>; //hspw

lcd_vbp = <17>; //vbp+vspw

lcd_vt = <994>; //lcd_y+vs+vbp+vspw

lcd_vspw = <2>; //vspw

lcd_backlight = <50>; //背光默认亮度

lcd_pwm_used = <1>; //使用背光

lcd_pwm_ch = <7>; //使用pwm通道7

lcd_pwm_freq = <10000>; //PWM 频率,单位 Hz

lcd_pwm_pol = <0>; //背光 PWM 的极性

lcd_pwm_max_limit = <255>;

lcd_bright_curve_en = <0>;

lcd_dsi_if = <0>;

lcd_dsi_lane = <4>;

lcd_lvds_if = <0>;

lcd_lvds_colordepth = <0>;

lcd_lvds_mode = <0>;

lcd_frm = <1>;

lcd_hv_clk_phase = <0>;

lcd_hv_sync_polarity= <0>;

lcd_io_phase = <0x0000>;

lcd_gamma_en = <0>;

lcd_bright_curve_en = <0>;

lcd_cmap_en = <0>;

lcd_fsync_en = <0>;

lcd_fsync_act_time = <1000>;

lcd_fsync_dis_time = <1000>;

lcd_fsync_pol = <0>;

deu_mode = <0>;

lcdgamma4iep = <22>;

smart_color = <90>;

pinctrl-0 = <&rgb18_pins_a>;

pinctrl-1 = <&rgb18_pins_b>;

lcd_gpio_0 = <&pio PE 9 GPIO_ACTIVE_HIGH>; //RST

lcd_gpio_1 = <&pio PE 8 GPIO_ACTIVE_HIGH>; //CS

lcd_gpio_2 = <&pio PE 7 GPIO_ACTIVE_HIGH>; //SDA

lcd_gpio_3 = <&pio PE 6 GPIO_ACTIVE_HIGH>; //SCK

};驱动源码如下:

#include "st7701s_rgb.h"

#include "default_panel.h"

//s32 sunxi_lcd_gpio_set_value(u32 screen_id, u32 io_index, u32 value)

#define st7701s_spi_scl_1 sunxi_lcd_gpio_set_value(0, 3, 1)

#define st7701s_spi_scl_0 sunxi_lcd_gpio_set_value(0, 3, 0)

#define st7701s_spi_sdi_1 sunxi_lcd_gpio_set_value(0, 2, 1)

#define st7701s_spi_sdi_0 sunxi_lcd_gpio_set_value(0, 2, 0)

#define st7701s_spi_cs_1 sunxi_lcd_gpio_set_value(0, 1, 1)

#define st7701s_spi_cs_0 sunxi_lcd_gpio_set_value(0, 1, 0)

#define st7701s_spi_reset_1 sunxi_lcd_gpio_set_value(0, 0, 1)

#define st7701s_spi_reset_0 sunxi_lcd_gpio_set_value(0, 0, 0)

static void LCD_power_on(u32 sel);

static void LCD_power_off(u32 sel);

static void LCD_bl_open(u32 sel);

static void LCD_bl_close(u32 sel);

static void LCD_panel_init(u32 sel);

static void LCD_panel_exit(u32 sel);

static void LCD_cfg_panel_info(panel_extend_para *info)

{

u32 i = 0, j = 0;

u32 items;

u8 lcd_gamma_tbl[][2] = {

/* {input value, corrected value} */

{0, 0},

{15, 15},

{30, 30},

{45, 45},

{60, 60},

{75, 75},

{90, 90},

{105, 105},

{120, 120},

{135, 135},

{150, 150},

{165, 165},

{180, 180},

{195, 195},

{210, 210},

{225, 225},

{240, 240},

{255, 255},

};

u32 lcd_cmap_tbl[2][3][4] = {

{

{LCD_CMAP_G0, LCD_CMAP_B1, LCD_CMAP_G2, LCD_CMAP_B3},

{LCD_CMAP_B0, LCD_CMAP_R1, LCD_CMAP_B2, LCD_CMAP_R3},

{LCD_CMAP_R0, LCD_CMAP_G1, LCD_CMAP_R2, LCD_CMAP_G3},

},

{

{LCD_CMAP_B3, LCD_CMAP_G2, LCD_CMAP_B1, LCD_CMAP_G0},

{LCD_CMAP_R3, LCD_CMAP_B2, LCD_CMAP_R1, LCD_CMAP_B0},

{LCD_CMAP_G3, LCD_CMAP_R2, LCD_CMAP_G1, LCD_CMAP_R0},

},

};

items = sizeof(lcd_gamma_tbl) / 2;

for (i = 0; i < items - 1; i++) {

u32 num = lcd_gamma_tbl[i + 1][0] - lcd_gamma_tbl[i][0];

for (j = 0; j < num; j++) {

u32 value = 0;

value =

lcd_gamma_tbl[i][1] +

((lcd_gamma_tbl[i + 1][1] -

lcd_gamma_tbl[i][1]) * j) / num;

info->lcd_gamma_tbl[lcd_gamma_tbl[i][0] + j] =

(value << 16) + (value << 8) + value;

}

}

info->lcd_gamma_tbl[255] =

(lcd_gamma_tbl[items - 1][1] << 16) +

(lcd_gamma_tbl[items - 1][1] << 8) + lcd_gamma_tbl[items - 1][1];

memcpy(info->lcd_cmap_tbl, lcd_cmap_tbl, sizeof(lcd_cmap_tbl));

}

static s32 LCD_open_flow(u32 sel)

{

printk("=====================LCD_open_flow\n");

/* open lcd power, and delay 50ms */

LCD_OPEN_FUNC(sel, LCD_power_on, 20);

/* open lcd power, than delay 200ms */

LCD_OPEN_FUNC(sel, LCD_panel_init, 20);

/* open lcd controller, and delay 100ms */

LCD_OPEN_FUNC(sel, sunxi_lcd_tcon_enable, 100);

/* open lcd backlight, and delay 0ms */

LCD_OPEN_FUNC(sel, LCD_bl_open, 0);

return 0;

}

static s32 LCD_close_flow(u32 sel)

{

/* close lcd backlight, and delay 0ms */

LCD_CLOSE_FUNC(sel, LCD_bl_close, 0);

/* close lcd controller, and delay 0ms */

LCD_CLOSE_FUNC(sel, sunxi_lcd_tcon_disable, 0);

/* open lcd power, than delay 200ms */

LCD_CLOSE_FUNC(sel, LCD_panel_exit, 200);

/* close lcd power, and delay 500ms */

LCD_CLOSE_FUNC(sel, LCD_power_off, 500);

return 0;

}

static void LCD_power_on(u32 sel)

{

printk("=====================LCD_power_on\n");

/* config lcd_power pin to open lcd power0 */

sunxi_lcd_power_enable(sel, 0);

sunxi_lcd_pin_cfg(sel, 1);

}

static void LCD_power_off(u32 sel)

{

sunxi_lcd_pin_cfg(sel, 0);

/* config lcd_power pin to close lcd power0 */

sunxi_lcd_power_disable(sel, 0);

}

static void LCD_bl_open(u32 sel)

{

printk("=====================LCD_bl_open\n");

sunxi_lcd_pwm_enable(sel);

sunxi_lcd_backlight_enable(sel);

}

static void LCD_bl_close(u32 sel)

{

/* config lcd_bl_en pin to close lcd backlight */

sunxi_lcd_backlight_disable(sel);

sunxi_lcd_pwm_disable(sel);

}

//three line 9bit mode

static void LCD_WRITE_DATA(u32 value)

{

u32 i;

st7701s_spi_cs_0;

st7701s_spi_sdi_1;

st7701s_spi_scl_0;

sunxi_lcd_delay_us(10);

st7701s_spi_scl_1;

for (i = 0; i < 8; i++) {

sunxi_lcd_delay_us(10);

if (value & 0x80)

st7701s_spi_sdi_1;

else

st7701s_spi_sdi_0;

value <<= 1;

sunxi_lcd_delay_us(10);

st7701s_spi_scl_0;

st7701s_spi_scl_1;

}

sunxi_lcd_delay_us(10);

st7701s_spi_cs_1;

}

static void LCD_WRITE_COMMAND(u32 value)

{

u32 i;

st7701s_spi_cs_0;

st7701s_spi_sdi_0;

st7701s_spi_scl_0;

sunxi_lcd_delay_us(10);

st7701s_spi_scl_1;

for (i = 0; i < 8; i++) {

sunxi_lcd_delay_us(10);

if (value & 0x80)

st7701s_spi_sdi_1;

else

st7701s_spi_sdi_0;

st7701s_spi_scl_0;

sunxi_lcd_delay_us(10);

st7701s_spi_scl_1;

value <<= 1;

}

sunxi_lcd_delay_us(10);

st7701s_spi_cs_1;

}

static void LCD_panel_init(u32 sel)

{

printk("=====================LCD_panel_init\n");

//ST7701S+AUO4.58

LCD_WRITE_COMMAND (0xFF);

LCD_WRITE_DATA (0x77);

LCD_WRITE_DATA (0x01);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x13);

LCD_WRITE_COMMAND (0xEF);

LCD_WRITE_DATA (0x08);

LCD_WRITE_COMMAND (0xFF);

LCD_WRITE_DATA (0x77);

LCD_WRITE_DATA (0x01);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x10);

LCD_WRITE_COMMAND (0xC0);

LCD_WRITE_DATA (0x77);

LCD_WRITE_DATA (0x00);

LCD_WRITE_COMMAND (0xC1);

LCD_WRITE_DATA (0x09);

LCD_WRITE_DATA (0x08);

LCD_WRITE_COMMAND (0xC2);//inv

LCD_WRITE_DATA (0x01);

LCD_WRITE_DATA (0x02);

LCD_WRITE_COMMAND (0xC3); //????

LCD_WRITE_DATA (0x02); //82 HVmode 02 DEmode

LCD_WRITE_COMMAND (0xCC);

LCD_WRITE_DATA (0x10);

LCD_WRITE_COMMAND (0xB0);

LCD_WRITE_DATA (0x40);

LCD_WRITE_DATA (0x14);

LCD_WRITE_DATA (0x59);

LCD_WRITE_DATA (0x10);

LCD_WRITE_DATA (0x12);

LCD_WRITE_DATA (0x08);

LCD_WRITE_DATA (0x03);

LCD_WRITE_DATA (0x09);

LCD_WRITE_DATA (0x05);

LCD_WRITE_DATA (0x1E);

LCD_WRITE_DATA (0x05);

LCD_WRITE_DATA (0x14);

LCD_WRITE_DATA (0x10);

LCD_WRITE_DATA (0x68);

LCD_WRITE_DATA (0x33);

LCD_WRITE_DATA (0x15);

LCD_WRITE_COMMAND (0xB1);

LCD_WRITE_DATA (0x40);

LCD_WRITE_DATA (0x08);

LCD_WRITE_DATA (0x53);

LCD_WRITE_DATA (0x09);

LCD_WRITE_DATA (0x11);

LCD_WRITE_DATA (0x09);

LCD_WRITE_DATA (0x02);

LCD_WRITE_DATA (0x07);

LCD_WRITE_DATA (0x09);

LCD_WRITE_DATA (0x1A);

LCD_WRITE_DATA (0x04);

LCD_WRITE_DATA (0x12);

LCD_WRITE_DATA (0x12);

LCD_WRITE_DATA (0x64);

LCD_WRITE_DATA (0x29);

LCD_WRITE_DATA (0x29);

LCD_WRITE_COMMAND (0xFF);

LCD_WRITE_DATA (0x77);

LCD_WRITE_DATA (0x01);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x11);

LCD_WRITE_COMMAND (0xB0);

LCD_WRITE_DATA (0x6D); //6D

LCD_WRITE_COMMAND (0xB1); //vcom

LCD_WRITE_DATA (0x1D);

LCD_WRITE_COMMAND (0xB2);

LCD_WRITE_DATA (0x87);

LCD_WRITE_COMMAND (0xB3);

LCD_WRITE_DATA (0x80);

LCD_WRITE_COMMAND (0xB5);

LCD_WRITE_DATA (0x49);

LCD_WRITE_COMMAND (0xB7);

LCD_WRITE_DATA (0x85);

LCD_WRITE_COMMAND (0xB8);

LCD_WRITE_DATA (0x20);

LCD_WRITE_COMMAND (0xC1);

LCD_WRITE_DATA (0x78);

LCD_WRITE_COMMAND (0xC2);

LCD_WRITE_DATA (0x78);

LCD_WRITE_COMMAND (0xD0);

LCD_WRITE_DATA (0x88);

LCD_WRITE_COMMAND (0xE0);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x02);

LCD_WRITE_COMMAND (0xE1);

LCD_WRITE_DATA (0x02);

LCD_WRITE_DATA (0x8C);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x03);

LCD_WRITE_DATA (0x8C);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x33);

LCD_WRITE_DATA (0x33);

LCD_WRITE_COMMAND (0xE2);

LCD_WRITE_DATA (0x33);

LCD_WRITE_DATA (0x33);

LCD_WRITE_DATA (0x33);

LCD_WRITE_DATA (0x33);

LCD_WRITE_DATA (0xC9);

LCD_WRITE_DATA (0x3C);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0xCA);

LCD_WRITE_DATA (0x3C);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x00);

LCD_WRITE_COMMAND (0xE3);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x33);

LCD_WRITE_DATA (0x33);

LCD_WRITE_COMMAND (0xE4);

LCD_WRITE_DATA (0x44);

LCD_WRITE_DATA (0x44);

LCD_WRITE_COMMAND (0xE5);

LCD_WRITE_DATA (0x05);

LCD_WRITE_DATA (0xCD);

LCD_WRITE_DATA (0x82);

LCD_WRITE_DATA (0x82);

LCD_WRITE_DATA (0x01);

LCD_WRITE_DATA (0xC9);

LCD_WRITE_DATA (0x82);

LCD_WRITE_DATA (0x82);

LCD_WRITE_DATA (0x07);

LCD_WRITE_DATA (0xCF);

LCD_WRITE_DATA (0x82);

LCD_WRITE_DATA (0x82);

LCD_WRITE_DATA (0x03);

LCD_WRITE_DATA (0xCB);

LCD_WRITE_DATA (0x82);

LCD_WRITE_DATA (0x82);

LCD_WRITE_COMMAND (0xE6);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x33);

LCD_WRITE_DATA (0x33);

LCD_WRITE_COMMAND (0xE7);

LCD_WRITE_DATA (0x44);

LCD_WRITE_DATA (0x44);

LCD_WRITE_COMMAND (0xE8);

LCD_WRITE_DATA (0x06);

LCD_WRITE_DATA (0xCE);

LCD_WRITE_DATA (0x82);

LCD_WRITE_DATA (0x82);

LCD_WRITE_DATA (0x02);

LCD_WRITE_DATA (0xCA);

LCD_WRITE_DATA (0x82);

LCD_WRITE_DATA (0x82);

LCD_WRITE_DATA (0x08);

LCD_WRITE_DATA (0xD0);

LCD_WRITE_DATA (0x82);

LCD_WRITE_DATA (0x82);

LCD_WRITE_DATA (0x04);

LCD_WRITE_DATA (0xCC);

LCD_WRITE_DATA (0x82);

LCD_WRITE_DATA (0x82);

LCD_WRITE_COMMAND (0xEB);

LCD_WRITE_DATA (0x08);

LCD_WRITE_DATA (0x01);

LCD_WRITE_DATA (0xE4);

LCD_WRITE_DATA (0xE4);

LCD_WRITE_DATA (0x88);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x40);

LCD_WRITE_COMMAND (0xEC);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x00);

LCD_WRITE_COMMAND (0xED);

LCD_WRITE_DATA (0xFF);

LCD_WRITE_DATA (0xF0);

LCD_WRITE_DATA (0x07);

LCD_WRITE_DATA (0x65);

LCD_WRITE_DATA (0x4F);

LCD_WRITE_DATA (0xFC);

LCD_WRITE_DATA (0xC2);

LCD_WRITE_DATA (0x2F);

LCD_WRITE_DATA (0xF2);

LCD_WRITE_DATA (0x2C);

LCD_WRITE_DATA (0xCF);

LCD_WRITE_DATA (0xF4);

LCD_WRITE_DATA (0x56);

LCD_WRITE_DATA (0x70);

LCD_WRITE_DATA (0x0F);

LCD_WRITE_DATA (0xFF);

LCD_WRITE_COMMAND (0xEF);

LCD_WRITE_DATA (0x10);

LCD_WRITE_DATA (0x0D);

LCD_WRITE_DATA (0x04);

LCD_WRITE_DATA (0x08);

LCD_WRITE_DATA (0x3F);

LCD_WRITE_DATA (0x1F);

LCD_WRITE_COMMAND (0xFF);

LCD_WRITE_DATA (0x77);

LCD_WRITE_DATA (0x01);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x00);

LCD_WRITE_DATA (0x00);

LCD_WRITE_COMMAND (0x11);

sunxi_lcd_delay_ms(120);

LCD_WRITE_COMMAND (0x35);

LCD_WRITE_DATA (0x00);

LCD_WRITE_COMMAND (0x3A);

LCD_WRITE_DATA (0x66);

//LCD_WRITE_COMMAND (0x11);

//sunxi_lcd_delay_ms(120);

LCD_WRITE_COMMAND (0x29);

return;

}

static void LCD_panel_exit(u32 sel)

{

return;

}

/* sel: 0:lcd0; 1:lcd1 */

static s32 LCD_user_defined_func(u32 sel, u32 para1, u32 para2, u32 para3)

{

return 0;

}

__lcd_panel_t st7701s_rgb_panel = {

/* panel driver name, must mach the lcd_drv_name in sys_config.fex */

.name = "st7701s_rgb",

.func = {

.cfg_panel_info = LCD_cfg_panel_info,

.cfg_open_flow = LCD_open_flow,

.cfg_close_flow = LCD_close_flow,

.lcd_user_defined_func = LCD_user_defined_func,

}

,

};#13 Re: 全志 SOC » T113S3使用spinand启动进不了kernel问题 » 2024-08-21 11:30:57

对比下能够正常启动的固件,和不能正常启动的日志,差异如下,目前还没找到问题的解决办法来着。

正常

[17:24:57.908] [01.880]Loading Environment from SUNXI_FLASH... OK

异常

[11:12:03.078] [01.569]Loading Environment from SUNXI_FLASH... Can't find env-redund partition

[11:12:03.158] *** Warning - no device, using default environment

正常

[17:24:57.698] partno erro : can't find partition bootloader

异常

[11:12:03.178] partno erro : can't find partition bootloader

[11:12:03.199] partno erro : can't find partition boot-resource

[11:12:03.219] [01.662]Get bootloader and boot-resource partition number fail!

正常

[17:24:59.469] List file under ULI/factory

[17:24:59.469] ** Unrecognized filesystem type **

异常

[11:12:03.838] cann't get the boot_base from the env#14 Re: 全志 SOC » T113S3使用spinand启动进不了kernel问题 » 2024-08-20 17:36:47

看日志说的是找不发到env-redund分区

Loading Environment from SUNXI_FLASH... Can't find env-redund partition

[17:26:53.990] *** Warning - no device, using default environment

但是我的sys_partition.fex已经了加了这个分区来着

;---------------------------------------------------------------------------------------------------

; 说明: 脚本中的字符串区分大小写,用户可以修改"="后面的数值,但是不要修改前面的字符串

;---------------------------------------------------------------------------------------------------

;---------------------------------------------------------------------------------------------------

; 固件下载参数配置

;---------------------------------------------------------------------------------------------------

;***************************************************************************************************

; mbr的大小, 以Kbyte为单位

;***************************************************************************************************

[mbr]

size = 252

;***************************************************************************************************

; 分区配置

;

;

; partition 定义范例:

; [partition] ; //表示是一个分区

; name = USERFS2 ; //分区名称

; size = 16384 ; //分区大小 单位: 扇区.分区表示个数最多2^31 * 512 = 2T

; downloadfile = "123.fex" ; //下载文件的路径和名称,可以使用相对路径,相对是指相对于image.cfg文件所在分区。也可以使用绝对路径

; keydata = 1 ; //私有数据分区,重新量产数据将不丢失

; encrypt = 1 ; //采用加密方式烧录,将提供数据加密,但损失烧录速度

; user_type = ? ; //私有用法

; verify = 1 ; //要求量产完成后校验是否正确

;

; 注:1、name唯一, 不允许同名

; 2、name最大12个字符

; 3、size = 0, 将创建一个无大小的空分区

; 4、align to logical block size(504 sectors), leb size = 2*(1 nand phy block size - 1 phy page size)

;***************************************************************************************************

[partition_start]

[partition]

name = boot-resource

size = 504

downloadfile = "boot-resource.fex"

user_type = 0x8000

[partition]

name = env

size = 504

downloadfile = "env.fex"

user_type = 0x8000

[partition]

name = env-redund

size = 504

downloadfile = "env.fex"

user_type = 0x8000

[partition]

name = boot

size = 20160

downloadfile = "boot.fex"

user_type = 0x8000

[partition]

name = rootfs

size = 61440

downloadfile = "rootfs.fex"

user_type = 0x8000

[partition]

name = private

size = 10080

user_type = 0x8000

[partition]

name = recovery

size = 23184

;downloadfile = "recovery.fex"

user_type = 0x8000#15 全志 SOC » T113S3使用spinand启动进不了kernel问题 » 2024-08-20 10:06:59

- kemp

- 回复: 2

使用evb1板卡的配置,跟随下方链接配置为spi nand启动后,发现进不了kernel

https://bbs.aw-ol.com/topic/1701/tina-linux-%E5%AD%98%E5%82%A8%E4%BB%8B%E8%B4%A8%E5%88%87%E6%8D%A2-emmc-spi-nand-spi-nor-sd-card-sd-nand?_=1699127558925

使用的flash是1Gbit的XT26G04CWSIGA,看到id.c中有这个芯片的支持。

完整日志如下:

HELLO! BOOT0 is starting!

[09:59:25.488] [140]BOOT0 commit : 1417090655

[09:59:25.498] [143]set pll start

[09:59:25.498] [149]periph0 has been enabled

[09:59:25.498] [152]set pll end

[09:59:25.508] [154][pmu]: bus read error

[09:59:25.508] [157]board init ok

[09:59:25.508] [159]enable_jtag

[09:59:25.508] [160]ZQ value = 0x30

[09:59:25.519] [162]get_pmu_exist() = -1

[09:59:25.519] [165]DRAM BOOT DRIVE INFO: V0.33

[09:59:25.519] [168]DRAM CLK = 792 MHz

[09:59:25.519] [170]DRAM Type = 3 (2:DDR2,3:DDR3)

[09:59:25.529] [174]DRAMC read ODT off.

[09:59:25.529] [176]DRAM ODT value: 0x42.

[09:59:25.529] [179]ddr_efuse_type: 0xa

[09:59:25.529] [182]DRAM SIZE =128 M

[09:59:25.539] [184]dram_tpr4:0x0

[09:59:25.539] [186]PLL_DDR_CTRL_REG:0xf8004100

[09:59:25.539] [189]DRAM_CLK_REG:0xc0000000

[09:59:25.539] [192][TIMING DEBUG] MR2= 0x18

[09:59:25.549] [200]DRAM simple test OK.

[09:59:25.549] [202]rtc standby flag is 0x0, super standby flag is 0x0

[09:59:25.559] [208]dram size =128

[09:59:25.559] [211]spinand UBOOT_START_BLK_NUM 8 UBOOT_LAST_BLK_NUM 32

[09:59:25.569] [216]block from 8 to 32

[09:59:25.569] [300]Check is correct.

[09:59:25.648] [302]dma 0x2ac4c int is not used yet

[09:59:25.658] [305]dma 0x2ac4c int is free, you do not need to free it again

[09:59:25.658] [311]Entry_name = u-boot

[09:59:25.668] [318]Entry_name = optee

[09:59:25.668] [322]Entry_name = dtb

[09:59:25.678] [325]Jump to second Boot.

[09:59:25.678] M/TC: OP-TEE version: 8b49ce62-dirty (gcc version 5.3.1 20160412 (Linaro GCC 5.3-2016.05)) #1 Fri Aug 12 08:24:15 UTC 2022 arm

[09:59:25.718]

[09:59:25.718]

[09:59:25.718] U-Boot 2018.07-gd9e6718-dirty (Aug 20 2024 - 01:08:36 +0000) Allwinner Technology

[09:59:25.728]

[09:59:25.728] [00.377]CPU: Allwinner Family

[09:59:25.728] [00.380]Model: sun8iw20

[09:59:25.738] [00.382]DRAM: 128 MiB

[09:59:25.738] [00.386]Relocation Offset is: 04ec4000

[09:59:25.738] [00.413]secure enable bit: 0

[09:59:25.768] E/TC:0 fdt_getprop_u32:343 prop trace_level not found

[09:59:25.778] [00.426]CPU=1008 MHz,PLL6=600 Mhz,AHB=200 Mhz, APB1=100Mhz MBus=300Mhz

[09:59:25.788] [00.432]gic: sec monitor mode

[09:59:25.788] sunxi flash map init

[09:59:25.788] SPI ALL: ready

[09:59:25.788] [00.439]flash init start

[09:59:25.798] [00.442]workmode = 0,storage type = 0

[09:59:25.798] [00.448]sunxi-spinand-phy: spinand sample_mode:2 sample_delay:8

[09:59:25.808]

[09:59:25.808] device nand0 <nand>, # parts = 4

[09:59:25.818] #: name size offset mask_flags

[09:59:25.818] 0: boot0 0x00200000 0x00000000 1

[09:59:25.818] 1: uboot 0x00600000 0x00200000 1

[09:59:25.818] 2: secure_storage 0x00200000 0x00800000 1

[09:59:25.828] 3: sys 0x1f600000 0x00a00000 0

[09:59:25.828]

[09:59:25.828] active partition: nand0,0 - (boot0) 0x00200000 @ 0x00000000

[09:59:25.838]

[09:59:25.838] defaults:

[09:59:25.838] mtdids : nand0=nand

[09:59:25.838] mtdparts: mtdparts=nand:2048k@0(boot0)ro,6144k@2097152(uboot)ro,2048k@8388608(secure_storage)ro,-(sys)

[09:59:25.848] [00.894]ubi0: attaching mtd4

[09:59:26.249] [01.443]ubi0: scanning is finished

[09:59:26.798] [01.450]ubi0: attached mtd4 (name "sys", size 502 MiB)

[09:59:26.809] [01.455]ubi0: PEB size: 524288 bytes (512 KiB), LEB size: 516096 bytes

[09:59:26.819] [01.461]ubi0: min./max. I/O unit sizes: 8192/8192, sub-page size 4096

[09:59:26.819] [01.467]ubi0: VID header offset: 4096 (aligned 4096), data offset: 8192

[09:59:26.829] [01.474]ubi0: good PEBs: 999, bad PEBs: 5, corrupted PEBs: 0

[09:59:26.829] [01.479]ubi0: user volume: 3, internal volumes: 1, max. volumes count: 128

[09:59:26.839] [01.486]ubi0: max/mean erase counter: 2/1, WL threshold: 4096, image sequence number: 0

[09:59:26.849] [01.493]ubi0: available PEBs: 0, total reserved PEBs: 999, PEBs reserved for bad PEB handling: 35

[09:59:26.849] [01.502]sunxi flash init ok

[09:59:26.859] [01.505]line:703 init_clocks

[09:59:26.859] [01.508]drv_disp_init

[09:59:26.859] [01.512]handle_num : 6

[09:59:26.869] request pwm success, pwm7:pwm7:0x2000c00.

[09:59:26.879] [01.523]drv_disp_init finish

[09:59:26.879] [01.568]Loading Environment from SUNXI_FLASH... Can't find env-redund partition

[09:59:26.949] *** Warning - no device, using default environment

[09:59:26.949]

[09:59:26.949] Failed (-19)

[09:59:26.959] [01.603]boot_gui_init:start

[09:59:26.959] [01.606]set disp.dev2_output_type fail. using defval=0

[09:59:26.959] [01.612]set disp.fb0_rot_used fail. using defval=0

[09:59:26.969] [01.617]set disp.fb0_rot_degree fail. using defval=0

[09:59:26.969] [01.622]boot_gui_init:finish

[09:59:26.979] partno erro : can't find partition bootloader

[09:59:26.989] partno erro : can't find partition boot-resource

[09:59:27.009] [01.660]Get bootloader and boot-resource partition number fail!

[09:59:27.018] [01.668]Item0 (Map) magic is bad

[09:59:27.028] [01.671]usb burn from boot

[09:59:27.028] delay time 0

[09:59:27.028] weak:otg_phy_config

[09:59:27.028] [01.682]usb prepare ok

[09:59:27.038] [01.793]LCD open finish

[09:59:27.148] [01.869]usb sof ok

[09:59:27.218] [01.871]usb probe ok

[09:59:27.228] [01.873]usb setup ok

[09:59:27.228] set address 0x3e

[09:59:27.258] set address 0x3e ok

[09:59:27.258] set address 0x3f

[09:59:27.449] set address 0x3f ok

[09:59:27.449] try to update

[09:59:27.488] [02.278]do_burn_from_boot usb : have no handshake

[09:59:27.639] cann't get the boot_base from the env

[09:59:27.639] [02.300]update bootcmd

[09:59:27.649] [02.334]change working_fdt 0x45e83e70 to 0x45e63e70

[09:59:27.689] [02.353]update dts

[09:59:27.709] Hit any key to stop autoboot: 2

1 0

[09:59:29.718] ## Error: "distro_bootcmd" not definedenv.cfg如下

#kernel command arguments

earlyprintk=sunxi-uart,0x02500000

initcall_debug=0

console=ttyS0,115200

nand_root=/dev/ubiblock0_5

mmc_root=/dev/mmcblk0p5

mtd_name=sys

rootfstype=squashfs

root_partition=rootfs

boot_partition=boot

init=/init

loglevel=8

cma=4M

mac=

wifi_mac=

bt_mac=

specialstr=

#keybox_list=widevine,ec_key,ec_cert1,ec_cert2,ec_cert3,rsa_key,rsa_cert1,rsa_cert2,rsa_cert3

dsp0_partition=dsp0

#set kernel cmdline if boot.img or recovery.img has no cmdline we will use this

setargs_nand=setenv bootargs ubi.mtd=${mtd_name} ubi.block=0,${root_partition} earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${nand_root} rootfstype=${rootfstype} init=${init} partitions=${partitions} cma=${cma} snum=${snum} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} specialstr=${specialstr} gpt=1

setargs_nand_ubi=setenv bootargs ubi.mtd=${mtd_name} ubi.block=0,${root_partition} earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${nand_root} rootfstype=${rootfstype} init=${init} partitions=${partitions} cma=${cma} snum=${snum} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} specialstr=${specialstr} gpt=1

setargs_mmc=setenv bootargs earlyprintk=${earlyprintk} clk_ignore_unused initcall_debug=${initcall_debug} console=${console} loglevel=${loglevel} root=${mmc_root} init=${init} partitions=${partitions} cma=${cma} snum=${snum} mac_addr=${mac} wifi_mac=${wifi_mac} bt_mac=${bt_mac} specialstr=${specialstr} gpt=1

#nand command syntax: sunxi_flash read address partition_name read_bytes

#0x4007f800 = 0x40080000(kernel entry) - 0x800(boot.img header 2k)

#boot_dsp0=sunxi_flash read 43000000 ${dsp0_partition};bootr 43000000 0 0

#boot_normal=sunxi_flash read 43000000 ${boot_partition};bootm 43000000

boot_dsp0=sunxi_flash read 43000000 ${dsp0_partition};bootr 43000000 0 0

boot_normal=sunxi_flash read 43000000 ${boot_partition};bootm 43000000

boot_recovery=sunxi_flash read 43000000 recovery;bootm 43000000

boot_fastboot=fastboot

#uboot system env config

bootdelay=2

#default bootcmd, will change at runtime according to key press

#default nand boot

#bootcmd=run setargs_nand boot_dsp0 boot_normal

bootcmd=run setargs_nand boot_normalsys_config.fex中storage_type = 5

看日志似乎和分区表sys_partition.fex有点关系?

麻烦各位大佬帮忙看看,提供点思路。

#17 Re: 全志 SOC » V3S RTL8723DS WiFi初始化无错误但找不到wlan0问题-验证中 » 2023-10-19 22:06:38

@kemp

/sys/bus/[mmc|sdio]/devices/X:XXXX/

下的manfid与oemid如果确定找不到RTL8723D的驱动想用RTL8723B源码尝试,

就在sdio_intf.c里强行加入上面ID

感谢大佬,果然是驱动的问题。

我下载了这个驱动加到内核中可以了,驱动源码如下:

https://github.com/lwfinger/rtl8723ds/tree/master

但是多了一个问题,一下子出来两个网卡

# ifconfig -a

wlan0 Link encap:Ethernet HWaddr 34:75:63:28:56:4F

BROADCAST MULTICAST MTU:1500 Metric:1

RX packets:0 errors:0 dropped:0 overruns:0 frame:0

TX packets:0 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1000

RX bytes:0 (0.0 B) TX bytes:0 (0.0 B)

wlan1 Link encap:Ethernet HWaddr 36:75:63:28:56:4F

BROADCAST MULTICAST MTU:1500 Metric:1

RX packets:0 errors:0 dropped:0 overruns:0 frame:0

TX packets:0 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1000

RX bytes:0 (0.0 B) TX bytes:0 (0.0 B)

当然了,我单独启动wlan0是可以的,但是这个wlan1是哪里来的呢,奇怪了

# ping www.baidu.com

PING www.baidu.com (120.232.145.185): 56 data bytes

64 bytes from 120.232.145.185: seq=0 ttl=51 time=58.909 ms

64 bytes from 120.232.145.185: seq=1 ttl=51 time=35.932 ms

#18 Re: 全志 SOC » V3S RTL8723DS WiFi初始化无错误但找不到wlan0问题-验证中 » 2023-10-19 10:28:58

@kemp https://whycan.com/viewtopic.php?id=10207

螃蟹家不同尾缀字母就是不同芯片,驱动不兼容编辑驱动的Makefile,不是linux的

CONFIG_RTL8723D = y指的类似USB一样VIDPID来让驱动识别的,sdio卡也有,/sys下的哪个文件我忘记了

好的,感谢。

我对比了下RTL8723BS和RTL8723DS,发现两个版本只是支持蓝牙的协议栈不一样,其它兼容,我再找找DS的固件和驱动看看,另外,我也买了几块BS的模组,等到了同步验证下。

同时,我计划把bus-width改为单线模式看看,不知道layout上面会不会影响到。

指令应该是这两条

~# ls /sys/bus/sdio/devices/

~# cat /sys/bus/sdio/devices/mmcxxx

#19 Re: 全志 SOC » V3S RTL8723DS WiFi初始化无错误但找不到wlan0问题-验证中 » 2023-10-19 08:54:55

驱动不对吧,

[ 1.418684] mmc1: new high speed SDIO card at address 0001

看着是认卡了,看一下卡的ID是什么rtl8723b的ID是024c:B723,

rtl8723d的ID是024c:D723/D724

编译时打开支持了吗?

MMC1读到的地址是0001,可以通过sudo blkid查看挂载的sd设备是吗?一般通过哪个指令查询呢,这块不太熟悉,感谢大佬支持

这里说的编译支持指的是dts和内核的mmc1和下面这些吗?

我dts打开了mmc1,然后占用PG口的leds已经disable

CONFIG_WLAN=y

CONFIG_MMC=y

CONFIG_CFG80211=y

CONFIG_RTL8723BS=y

还是有其他需要打开的?

#23 Re: 全志 SOC » V3S RTL8723DS WiFi初始化无错误但找不到wlan0问题-验证中 » 2023-10-18 14:18:05

同时贴上dtb转换回的dts,目前还没啥头绪

/dts-v1/;

/ {

#address-cells = <0x1>;

#size-cells = <0x1>;

interrupt-parent = <0x1>;

model = "Lichee Pi Zero with Dock";

compatible = "licheepi,licheepi-zero-dock", "licheepi,licheepi-zero", "allwinner,sun8i-v3s";

chosen {

#address-cells = <0x1>;

#size-cells = <0x1>;

ranges;

stdout-path = "serial0:115200n8";

framebuffer@0 {

compatible = "allwinner,simple-framebuffer", "simple-framebuffer";

allwinner,pipeline = "de0-lcd0";

clocks = <0x2 0x21 0x3 0x0 0x3 0x6 0x2 0x40>;

status = "disabled";

};

};

cpus {

#address-cells = <0x1>;

#size-cells = <0x0>;

cpu@0 {

compatible = "arm,cortex-a7";

device_type = "cpu";

reg = <0x0>;

clocks = <0x2 0xe>;

};

};

display-engine {

compatible = "allwinner,sun8i-v3s-display-engine";

allwinner,pipelines = <0x4>;

status = "disabled";

};

timer {

compatible = "arm,armv7-timer";

interrupts = <0x1 0xd 0xf08 0x1 0xe 0xf08 0x1 0xb 0xf08 0x1 0xa 0xf08>;

};

clocks {

#address-cells = <0x1>;

#size-cells = <0x1>;

ranges;

osc24M_clk {

#clock-cells = <0x0>;

compatible = "fixed-clock";

clock-frequency = <0x16e3600>;

clock-output-names = "osc24M";

linux,phandle = <0xc>;

phandle = <0xc>;

};

osc32k_clk {

#clock-cells = <0x0>;

compatible = "fixed-clock";

clock-frequency = <0x8000>;

clock-output-names = "osc32k";

linux,phandle = <0xd>;

phandle = <0xd>;

};

};

soc {

compatible = "simple-bus";

#address-cells = <0x1>;

#size-cells = <0x1>;

ranges;

clock@1000000 {

compatible = "allwinner,sun8i-v3s-de2-clk";

reg = <0x1000000 0x100000>;

clocks = <0x2 0x3f 0x2 0x23>;

clock-names = "mod", "bus";

resets = <0x2 0x22>;

#clock-cells = <0x1>;

#reset-cells = <0x1>;

linux,phandle = <0x3>;

phandle = <0x3>;

};

mixer@1100000 {

compatible = "allwinner,sun8i-v3s-de2-mixer";

reg = <0x1100000 0x100000>;

clocks = <0x3 0x0 0x3 0x6>;

clock-names = "bus", "mod";

resets = <0x3 0x0>;

assigned-clocks = <0x3 0x6>;

assigned-clock-rates = <0x8f0d180>;

linux,phandle = <0x4>;

phandle = <0x4>;

ports {

#address-cells = <0x1>;

#size-cells = <0x0>;

port@1 {

#address-cells = <0x1>;

#size-cells = <0x0>;

reg = <0x1>;

endpoint@0 {

reg = <0x0>;

remote-endpoint = <0x5>;

linux,phandle = <0x6>;

phandle = <0x6>;

};

};

};

};

syscon@1c00000 {

compatible = "allwinner,sun8i-v3s-system-controller", "syscon";

reg = <0x1c00000 0x1000>;

linux,phandle = <0x14>;

phandle = <0x14>;

};

lcd-controller@1c0c000 {

compatible = "allwinner,sun8i-v3s-tcon";

reg = <0x1c0c000 0x1000>;

interrupts = <0x0 0x56 0x4>;

clocks = <0x2 0x21 0x2 0x40>;

clock-names = "ahb", "tcon-ch0";

clock-output-names = "tcon-pixel-clock";

resets = <0x2 0x1b>;

reset-names = "lcd";

status = "disabled";

ports {

#address-cells = <0x1>;

#size-cells = <0x0>;

port@0 {

#address-cells = <0x1>;

#size-cells = <0x0>;

reg = <0x0>;

endpoint@0 {

reg = <0x0>;

remote-endpoint = <0x6>;

linux,phandle = <0x5>;

phandle = <0x5>;

};

};

port@1 {

#address-cells = <0x1>;

#size-cells = <0x0>;

reg = <0x1>;

};

};

};

dma-controller@01c02000 {

compatible = "allwinner,sun8i-v3s-dma";

reg = <0x1c02000 0x1000>;

interrupts = <0x0 0x32 0x4>;

clocks = <0x2 0x15>;

resets = <0x2 0x6>;

#dma-cells = <0x1>;

linux,phandle = <0xf>;

phandle = <0xf>;

};

mmc@01c0f000 {

compatible = "allwinner,sun7i-a20-mmc";

reg = <0x1c0f000 0x1000>;

clocks = <0x2 0x16 0x2 0x2d 0x2 0x2f 0x2 0x2e>;

clock-names = "ahb", "mmc", "output", "sample";

resets = <0x2 0x7>;

reset-names = "ahb";

interrupts = <0x0 0x3c 0x4>;

status = "okay";

#address-cells = <0x1>;

#size-cells = <0x0>;

pinctrl-0 = <0x7>;

pinctrl-names = "default";

broken-cd;

bus-width = <0x4>;

vmmc-supply = <0x8>;

};

mmc@01c10000 {

compatible = "allwinner,sun7i-a20-mmc";

reg = <0x1c10000 0x1000>;

clocks = <0x2 0x17 0x2 0x30 0x2 0x32 0x2 0x31>;

clock-names = "ahb", "mmc", "output", "sample";

resets = <0x2 0x8>;

reset-names = "ahb";

interrupts = <0x0 0x3d 0x4>;

pinctrl-names = "default";

pinctrl-0 = <0x9>;

status = "okay";

#address-cells = <0x1>;

#size-cells = <0x0>;

broken-cd;

bus-width = <0x4>;

vmmc-supply = <0x8>;

};

mmc@01c11000 {

compatible = "allwinner,sun7i-a20-mmc";

reg = <0x1c11000 0x1000>;

clocks = <0x2 0x18 0x2 0x33 0x2 0x35 0x2 0x34>;

clock-names = "ahb", "mmc", "output", "sample";

resets = <0x2 0x9>;

reset-names = "ahb";

interrupts = <0x0 0x3e 0x4>;

status = "disabled";

#address-cells = <0x1>;

#size-cells = <0x0>;

};

usb@01c19000 {

compatible = "allwinner,sun8i-h3-musb";

reg = <0x1c19000 0x400>;

clocks = <0x2 0x1d>;

resets = <0x2 0x11>;

interrupts = <0x0 0x47 0x4>;

interrupt-names = "mc";

phys = <0xa 0x0>;

phy-names = "usb";

extcon = <0xa 0x0>;

status = "okay";

dr_mode = "otg";

};

phy@01c19400 {

compatible = "allwinner,sun8i-v3s-usb-phy";

reg = <0x1c19400 0x2c 0x1c1a800 0x4>;

reg-names = "phy_ctrl", "pmu0";

clocks = <0x2 0x38>;

clock-names = "usb0_phy";

resets = <0x2 0x0>;

reset-names = "usb0_reset";

status = "okay";

#phy-cells = <0x1>;

usb0_id_det-gpio = <0xb 0x5 0x6 0x0>;

linux,phandle = <0xa>;

phandle = <0xa>;

};

usb@01c1a000 {

compatible = "allwinner,sun8i-v3s-ehci", "generic-ehci";

reg = <0x1c1a000 0x100>;

interrupts = <0x0 0x48 0x4>;

clocks = <0x2 0x1e 0x2 0x1f>;

resets = <0x2 0x12 0x2 0x16>;

status = "okay";

};

usb@01c1a400 {

compatible = "allwinner,sun8i-v3s-ohci", "generic-ohci";

reg = <0x1c1a400 0x100>;

interrupts = <0x0 0x49 0x4>;

clocks = <0x2 0x1e 0x2 0x1f 0x2 0x39>;

resets = <0x2 0x12 0x2 0x16>;

status = "okay";

};

clock@01c20000 {

compatible = "allwinner,sun8i-v3s-ccu";

reg = <0x1c20000 0x400>;

clocks = <0xc 0xd>;

clock-names = "hosc", "losc";

#clock-cells = <0x1>;

#reset-cells = <0x1>;

linux,phandle = <0x2>;

phandle = <0x2>;

};

rtc@01c20400 {

compatible = "allwinner,sun6i-a31-rtc";

reg = <0x1c20400 0x54>;

interrupts = <0x0 0x28 0x4 0x0 0x29 0x4>;

};

pinctrl@01c20800 {

compatible = "allwinner,sun8i-v3s-pinctrl";

reg = <0x1c20800 0x400>;

interrupts = <0x0 0xf 0x4 0x0 0x11 0x4>;

clocks = <0x2 0x25 0xc 0xd>;

clock-names = "apb", "hosc", "losc";

gpio-controller;

#gpio-cells = <0x3>;

interrupt-controller;

#interrupt-cells = <0x3>;

linux,phandle = <0xb>;

phandle = <0xb>;

i2c0 {

pins = "PB6", "PB7";

function = "i2c0";

linux,phandle = <0x13>;

phandle = <0x13>;

};

uart0@0 {

pins = "PB8", "PB9";

function = "uart0";

linux,phandle = <0x11>;

phandle = <0x11>;

};

uart1@0 {

pins = "PE21", "PE22";

function = "uart1";

bias-pull-up;

};

uart2@0 {

pins = "PB0", "PB1";

function = "uart2";

bias-pull-up;

linux,phandle = <0x12>;

phandle = <0x12>;

};

mmc0@0 {

pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5";

function = "mmc0";

drive-strength = <0x1e>;

bias-pull-up;

linux,phandle = <0x7>;

phandle = <0x7>;

};

mmc1 {

pins = "PG0", "PG1", "PG2", "PG3", "PG4", "PG5";

function = "mmc1";

drive-strength = <0x1e>;

bias-pull-up;

linux,phandle = <0x9>;

phandle = <0x9>;

};

spi0 {

pins = "PC0", "PC1", "PC2", "PC3";

function = "spi0";

linux,phandle = <0x16>;

phandle = <0x16>;

};

};

timer@01c20c00 {

compatible = "allwinner,sun4i-a10-timer";

reg = <0x1c20c00 0xa0>;

interrupts = <0x0 0x12 0x4 0x0 0x13 0x4>;

clocks = <0xc>;

};

watchdog@01c20ca0 {

compatible = "allwinner,sun6i-a31-wdt";

reg = <0x1c20ca0 0x20>;

interrupts = <0x0 0x19 0x4>;

};

lradc@1c22800 {

compatible = "allwinner,sun4i-a10-lradc-keys";

reg = <0x1c22800 0x400>;

interrupts = <0x0 0x1e 0x4>;

status = "okay";

vref-supply = <0xe>;

button@200 {

label = "Volume Up";

linux,code = <0x73>;

channel = <0x0>;

voltage = <0x30d40>;

};

button@400 {

label = "Volume Down";

linux,code = <0x72>;

channel = <0x0>;

voltage = <0x61a80>;

};

button@600 {

label = "Select";

linux,code = <0x161>;

channel = <0x0>;

voltage = <0x927c0>;

};

button@800 {

label = "Start";

linux,code = <0x160>;

channel = <0x0>;

voltage = <0xc3500>;

};

};

codec@01c22c00 {

#sound-dai-cells = <0x0>;

compatible = "allwinner,sun8i-v3s-codec";

reg = <0x1c22c00 0x400>;

interrupts = <0x0 0x1d 0x4>;

clocks = <0x2 0x24 0x2 0x46>;

clock-names = "apb", "codec";

resets = <0x2 0x28>;

dmas = <0xf 0xf 0xf 0xf>;

dma-names = "rx", "tx";

allwinner,codec-analog-controls = <0x10>;

status = "okay";

allwinner,audio-routing = "Headphone", "HP", "Headphone", "HPCOM", "MIC1", "Mic", "Mic", "HBIAS";

};

codec-analog@01c23000 {

compatible = "allwinner,sun8i-v3s-codec-analog";

reg = <0x1c23000 0x4>;

linux,phandle = <0x10>;

phandle = <0x10>;

};

serial@01c28000 {

compatible = "snps,dw-apb-uart";

reg = <0x1c28000 0x400>;

interrupts = <0x0 0x0 0x4>;

reg-shift = <0x2>;

reg-io-width = <0x4>;

clocks = <0x2 0x28>;

resets = <0x2 0x31>;

status = "okay";

pinctrl-0 = <0x11>;

pinctrl-names = "default";

};

serial@01c28400 {

compatible = "snps,dw-apb-uart";

reg = <0x1c28400 0x400>;

interrupts = <0x0 0x1 0x4>;

reg-shift = <0x2>;

reg-io-width = <0x4>;

clocks = <0x2 0x29>;

resets = <0x2 0x32>;

status = "disabled";

};

serial@01c28800 {

compatible = "snps,dw-apb-uart";

reg = <0x1c28800 0x400>;

interrupts = <0x0 0x2 0x4>;

reg-shift = <0x2>;

reg-io-width = <0x4>;

clocks = <0x2 0x2a>;

resets = <0x2 0x33>;

status = "okay";

pinctrl-0 = <0x12>;

pinctrl-names = "default";

};

i2c@01c2ac00 {

compatible = "allwinner,sun6i-a31-i2c";

reg = <0x1c2ac00 0x400>;

interrupts = <0x0 0x6 0x4>;

clocks = <0x2 0x26>;

resets = <0x2 0x2e>;

pinctrl-names = "default";

pinctrl-0 = <0x13>;

status = "okay";

#address-cells = <0x1>;

#size-cells = <0x0>;

ns2009@48 {

compatible = "nsiway,ns2009";

reg = <0x48>;

};

};

i2c@01c2b000 {

compatible = "allwinner,sun6i-a31-i2c";

reg = <0x1c2b000 0x400>;

interrupts = <0x0 0x7 0x4>;

clocks = <0x2 0x27>;

resets = <0x2 0x2f>;

status = "disabled";

#address-cells = <0x1>;

#size-cells = <0x0>;

};

ethernet@1c30000 {

compatible = "allwinner,sun8i-v3s-emac";

syscon = <0x14>;

reg = <0x1c30000 0x10000>;

interrupts = <0x0 0x52 0x4>;

interrupt-names = "macirq";

resets = <0x2 0xc>;

reset-names = "stmmaceth";

clocks = <0x2 0x1a>;

clock-names = "stmmaceth";

phy-handle = <0x15>;

phy-mode = "mii";

#address-cells = <0x1>;

#size-cells = <0x0>;

status = "okay";

mdio {

#address-cells = <0x1>;

#size-cells = <0x0>;

ethernet-phy@1 {

compatible = "ethernet-phy-ieee802.3-c22";

reg = <0x1>;

clocks = <0x2 0x2b>;

resets = <0x2 0x27>;

phy-is-integrated;

linux,phandle = <0x15>;

phandle = <0x15>;

};

};

};

spi@1c68000 {

compatible = "allwinner,sun8i-h3-spi";

reg = <0x1c68000 0x1000>;

interrupts = <0x0 0x41 0x4>;

clocks = <0x2 0x1c 0x2 0x37>;

clock-names = "ahb", "mod";

pinctrl-names = "default";

pinctrl-0 = <0x16>;

resets = <0x2 0xf>;

status = "disabled";

#address-cells = <0x1>;

#size-cells = <0x0>;

};

interrupt-controller@01c81000 {

compatible = "arm,cortex-a7-gic", "arm,cortex-a15-gic";

reg = <0x1c81000 0x1000 0x1c82000 0x1000 0x1c84000 0x2000 0x1c86000 0x2000>;

interrupt-controller;

#interrupt-cells = <0x3>;

interrupts = <0x1 0x9 0xf04>;

linux,phandle = <0x1>;

phandle = <0x1>;

};

};

ahci-5v {

compatible = "regulator-fixed";

regulator-name = "ahci-5v";

regulator-min-microvolt = <0x4c4b40>;

regulator-max-microvolt = <0x4c4b40>;

regulator-boot-on;

enable-active-high;

gpio = <0xb 0x1 0x8 0x0>;

status = "disabled";

};

usb0-vbus {

compatible = "regulator-fixed";

regulator-name = "usb0-vbus";

regulator-min-microvolt = <0x4c4b40>;

regulator-max-microvolt = <0x4c4b40>;

enable-active-high;

gpio = <0xb 0x1 0x9 0x0>;

status = "disabled";

};

usb1-vbus {

compatible = "regulator-fixed";

regulator-name = "usb1-vbus";

regulator-min-microvolt = <0x4c4b40>;

regulator-max-microvolt = <0x4c4b40>;

regulator-boot-on;

enable-active-high;

gpio = <0xb 0x7 0x6 0x0>;

status = "disabled";

};

usb2-vbus {

compatible = "regulator-fixed";

regulator-name = "usb2-vbus";

regulator-min-microvolt = <0x4c4b40>;

regulator-max-microvolt = <0x4c4b40>;

regulator-boot-on;

enable-active-high;

gpio = <0xb 0x7 0x3 0x0>;

status = "disabled";

};

vcc3v0 {

compatible = "regulator-fixed";

regulator-name = "vcc3v0";

regulator-min-microvolt = <0x2dc6c0>;

regulator-max-microvolt = <0x2dc6c0>;

linux,phandle = <0xe>;

phandle = <0xe>;

};

vcc3v3 {

compatible = "regulator-fixed";

regulator-name = "vcc3v3";

regulator-min-microvolt = <0x325aa0>;

regulator-max-microvolt = <0x325aa0>;

linux,phandle = <0x8>;

phandle = <0x8>;

};

vcc5v0 {

compatible = "regulator-fixed";

regulator-name = "vcc5v0";

regulator-min-microvolt = <0x4c4b40>;

regulator-max-microvolt = <0x4c4b40>;

};

aliases {

serial0 = "/soc/serial@01c28000";

ethernet0 = "/soc/ethernet@1c30000";

};

leds {

compatible = "gpio-leds";

status = "disbaled";

blue_led {

label = "licheepi:blue:usr";

gpios = <0xb 0x6 0x1 0x1>;

};

green_led {

label = "licheepi:green:usr";

gpios = <0xb 0x6 0x0 0x1>;

default-state = "on";

};

red_led {

label = "licheepi:red:usr";

gpios = <0xb 0x6 0x2 0x1>;

};

};

};#24 Re: 全志 SOC » V3S RTL8723DS WiFi初始化无错误但找不到wlan0问题-验证中 » 2023-10-18 09:01:11

附上完整的开机日志:

U-Boot SPL 2017.01-rc2-00073-gdd6e874-dirty (Oct 14 2023 - 16:57:06)

DRAM: 64 MiB

Trying to boot from MMC1

U-Boot 2017.01-rc2-00073-gdd6e874-dirty (Oct 14 2023 - 16:57:06 +0000) Allwinner Technology

CPU: Allwinner V3s (SUN8I 1681)

Model: Lichee Pi Zero

DRAM: 64 MiB

MMC: SUNXI SD/MMC: 0

SF: unrecognized JEDEC id bytes: 00, 00, 00

*** Warning - spi_flash_probe() failed, using default environment

Setting up a 800x480 lcd console (overscan 0x0)

dotclock: 33000kHz = 33000kHz: (1 * 3MHz * 66) / 6

In: serial@01c28000

Out: serial@01c28000

Err: serial@01c28000

U-Boot 2017.01-rc2-00073-gdd6e874-dirty (Oct 14 2023 - 16:57:06 +0000) Allwinner Technology

CPU: Allwinner V3s (SUN8I 1681)

Model: Lichee Pi Zero

DRAM: 64 MiB

MMC: SUNXI SD/MMC: 0

SF: unrecognized JEDEC id bytes: 00, 00, 00

*** Warning - spi_flash_probe() failed, using default environment

Setting up a 800x480 lcd console (overscan 0x0)

dotclock: 33000kHz = 33000kHz: (1 * 3MHz * 66) / 6

In: serial@01c28000

Out: serial@01c28000

Err: serial@01c28000

Net: No ethernet found.

starting USB...

No controllers found

Hit any key to stop autoboot: 2

1

0

reading zImage

4105144 bytes read in 211 ms (18.6 MiB/s)

reading sun8i-v3s-licheepi-zero-dock.dtb

11741 bytes read in 26 ms (440.4 KiB/s)

## Flattened Device Tree blob at 41800000

Booting using the fdt blob at 0x41800000

Loading Device Tree to 42dfa000, end 42dffddc ... OK

Starting kernel ...

[ 0.000000] Booting Linux on physical CPU 0x0

[ 0.000000] Linux version 4.13.0-licheepi-zero+ (root@5b077f6e0bc8) (gcc version 6.3.1 20170404 (Linaro GCC 6.3-2017.05)) #3 SMP Tue Oct 17 13:52:01 UTC 2023

[ 0.000000] CPU: ARMv7 Processor [410fc075] revision 5 (ARMv7), cr=10c5387d

[ 0.000000] CPU: div instructions available: patching division code

[ 0.000000] CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache

[ 0.000000] OF: fdt: Machine model: Lichee Pi Zero with Dock

[ 0.000000] Memory policy: Data cache writealloc

[ 0.000000] percpu: Embedded 16 pages/cpu @c3de6000 s33868 r8192 d23476 u65536

[ 0.000000] Built 1 zonelists in Zone order, mobility grouping on. Total pages: 15883

[ 0.000000] Kernel command line: console=ttyS0,115200 panic=5 rootwait mtdparts=spi32766.0:1M(uboot)ro,64k(dtb)ro,6M(kernel)ro,-(rootfs) root=/dev/mmcblk0p2 earlyprintk rw

[ 0.000000] PID hash table entries: 256 (order: -2, 1024 bytes)

[ 0.000000] Dentry cache hash table entries: 8192 (order: 3, 32768 bytes)

[ 0.000000] Inode-cache hash table entries: 4096 (order: 2, 16384 bytes)

[ 0.000000] Memory: 53580K/64036K available (6144K kernel code, 219K rwdata, 1468K rodata, 1024K init, 262K bss, 10456K reserved, 0K cma-reserved, 0K highmem)

[ 0.000000] Virtual kernel memory layout:

[ 0.000000] vector : 0xffff0000 - 0xffff1000 ( 4 kB)

[ 0.000000] fixmap : 0xffc00000 - 0xfff00000 (3072 kB)

[ 0.000000] vmalloc : 0xc4000000 - 0xff800000 ( 952 MB)

[ 0.000000] lowmem : 0xc0000000 - 0xc3e89000 ( 62 MB)

[ 0.000000] pkmap : 0xbfe00000 - 0xc0000000 ( 2 MB)

[ 0.000000] modules : 0xbf000000 - 0xbfe00000 ( 14 MB)

[ 0.000000] .text : 0xc0008000 - 0xc0700000 (7136 kB)

[ 0.000000] .init : 0xc0900000 - 0xc0a00000 (1024 kB)

[ 0.000000] .data : 0xc0a00000 - 0xc0a36dc0 ( 220 kB)

[ 0.000000] .bss : 0xc0a3d8b0 - 0xc0a7f194 ( 263 kB)

[ 0.000000] SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=1, Nodes=1

[ 0.000000] Hierarchical RCU implementation.

[ 0.000000] RCU event tracing is enabled.

[ 0.000000] RCU restricting CPUs from NR_CPUS=8 to nr_cpu_ids=1.

[ 0.000000] RCU: Adjusting geometry for rcu_fanout_leaf=16, nr_cpu_ids=1

[ 0.000000] NR_IRQS: 16, nr_irqs: 16, preallocated irqs: 16

[ 0.000000] arch_timer: cp15 timer(s) running at 24.00MHz (virt).

[ 0.000000] clocksource: arch_sys_counter: mask: 0xffffffffffffff max_cycles: 0x588fe9dc0, max_idle_ns: 440795202592 ns

[ 0.000009] sched_clock: 56 bits at 24MHz, resolution 41ns, wraps every 4398046511097ns

[ 0.000021] Switching to timer-based delay loop, resolution 41ns

[ 0.000191] clocksource: timer: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 79635851949 ns

[ 0.000419] Console: colour dummy device 80x30

[ 0.000456] Calibrating delay loop (skipped), value calculated using timer frequency.. 48.00 BogoMIPS (lpj=240000)

[ 0.000471] pid_max: default: 32768 minimum: 301

[ 0.000602] Mount-cache hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.000615] Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.001214] CPU: Testing write buffer coherency: ok

[ 0.001595] /cpus/cpu@0 missing clock-frequency property

[ 0.001620] CPU0: thread -1, cpu 0, socket 0, mpidr 80000000

[ 0.002059] Setting up static identity map for 0x40100000 - 0x40100060

[ 0.002240] Hierarchical SRCU implementation.

[ 0.002747] smp: Bringing up secondary CPUs ...

[ 0.002761] smp: Brought up 1 node, 1 CPU

[ 0.002772] SMP: Total of 1 processors activated (48.00 BogoMIPS).

[ 0.002779] CPU: All CPU(s) started in SVC mode.

[ 0.003545] devtmpfs: initialized

[ 0.006666] VFP support v0.3: implementor 41 architecture 2 part 30 variant 7 rev 5

[ 0.006958] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604462750000 ns

[ 0.006986] futex hash table entries: 256 (order: 2, 16384 bytes)

[ 0.007148] pinctrl core: initialized pinctrl subsystem

[ 0.008044] random: get_random_u32 called from bucket_table_alloc+0xf4/0x244 with crng_init=0

[ 0.008181] NET: Registered protocol family 16

[ 0.008655] DMA: preallocated 256 KiB pool for atomic coherent allocations

[ 0.009766] hw-breakpoint: found 5 (+1 reserved) breakpoint and 4 watchpoint registers.

[ 0.009783] hw-breakpoint: maximum watchpoint size is 8 bytes.

[ 0.023267] SCSI subsystem initialized

[ 0.023548] usbcore: registered new interface driver usbfs

[ 0.023634] usbcore: registered new interface driver hub

[ 0.023724] usbcore: registered new device driver usb

[ 0.023974] pps_core: LinuxPPS API ver. 1 registered

[ 0.023983] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it>

[ 0.024005] PTP clock support registered

[ 0.024216] Advanced Linux Sound Architecture Driver Initialized.

[ 0.024892] Bluetooth: Core ver 2.22

[ 0.024966] NET: Registered protocol family 31

[ 0.024974] Bluetooth: HCI device and connection manager initialized

[ 0.024991] Bluetooth: HCI socket layer initialized

[ 0.025002] Bluetooth: L2CAP socket layer initialized

[ 0.025037] Bluetooth: SCO socket layer initialized

[ 0.026245] clocksource: Switched to clocksource arch_sys_counter

[ 0.037480] NET: Registered protocol family 2

[ 0.038091] TCP established hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.038126] TCP bind hash table entries: 1024 (order: 1, 8192 bytes)

[ 0.038150] TCP: Hash tables configured (established 1024 bind 1024)

[ 0.038280] UDP hash table entries: 256 (order: 1, 8192 bytes)

[ 0.038328] UDP-Lite hash table entries: 256 (order: 1, 8192 bytes)

[ 0.038548] NET: Registered protocol family 1

[ 0.039137] RPC: Registered named UNIX socket transport module.

[ 0.039154] RPC: Registered udp transport module.

[ 0.039160] RPC: Registered tcp transport module.

[ 0.039166] RPC: Registered tcp NFSv4.1 backchannel transport module.

[ 0.041264] workingset: timestamp_bits=30 max_order=14 bucket_order=0

[ 0.050323] NFS: Registering the id_resolver key type

[ 0.050373] Key type id_resolver registered

[ 0.050381] Key type id_legacy registered

[ 0.051353] random: fast init done

[ 0.054361] Block layer SCSI generic (bsg) driver version 0.4 loaded (major 249)

[ 0.054385] io scheduler noop registered

[ 0.054393] io scheduler deadline registered

[ 0.054634] io scheduler cfq registered (default)

[ 0.054646] io scheduler mq-deadline registered

[ 0.054654] io scheduler kyber registered

[ 0.059129] sun8i-v3s-pinctrl 1c20800.pinctrl: initialized sunXi PIO driver

[ 0.131137] Serial: 8250/16550 driver, 8 ports, IRQ sharing disabled

[ 0.134513] console [ttyS0] disabled

[ 0.154788] 1c28000.serial: ttyS0 at MMIO 0x1c28000 (irq = 36, base_baud = 1500000) is a U6_16550A

[ 0.766530] console [ttyS0] enabled

[ 0.791543] 1c28800.serial: ttyS1 at MMIO 0x1c28800 (irq = 37, base_baud = 1500000) is a U6_16550A

[ 0.804068] libphy: Fixed MDIO Bus: probed

[ 0.808686] ehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver

[ 0.815212] ehci-platform: EHCI generic platform driver

[ 0.820765] ehci-platform 1c1a000.usb: EHCI Host Controller

[ 0.826439] ehci-platform 1c1a000.usb: new USB bus registered, assigned bus number 1

[ 0.834361] ehci-platform 1c1a000.usb: irq 26, io mem 0x01c1a000

[ 0.866256] ehci-platform 1c1a000.usb: USB 2.0 started, EHCI 1.00

[ 0.873476] hub 1-0:1.0: USB hub found

[ 0.877402] hub 1-0:1.0: 1 port detected

[ 0.881883] ohci_hcd: USB 1.1 'Open' Host Controller (OHCI) Driver

[ 0.888183] ohci-platform: OHCI generic platform driver

[ 0.893728] ohci-platform 1c1a400.usb: Generic Platform OHCI controller

[ 0.900459] ohci-platform 1c1a400.usb: new USB bus registered, assigned bus number 2

[ 0.908388] ohci-platform 1c1a400.usb: irq 27, io mem 0x01c1a400

[ 0.981330] hub 2-0:1.0: USB hub found

[ 0.985148] hub 2-0:1.0: 1 port detected

[ 0.992764] udc-core: couldn't find an available UDC - added [g_cdc] to list of pending drivers

[ 1.002379] input: 1c22800.lradc as /devices/platform/soc/1c22800.lradc/input/input0

[ 1.011336] sun6i-rtc 1c20400.rtc: rtc core: registered rtc-sun6i as rtc0

[ 1.018245] sun6i-rtc 1c20400.rtc: RTC enabled

[ 1.022787] i2c /dev entries driver

[ 1.027823] input: ns2009_ts as /devices/platform/soc/1c2ac00.i2c/i2c-0/0-0048/input/input1

[ 1.037372] sunxi-wdt 1c20ca0.watchdog: Watchdog enabled (timeout=16 sec, nowayout=0)

[ 1.045297] Bluetooth: HCI UART driver ver 2.3

[ 1.049848] Bluetooth: HCI UART protocol Three-wire (H5) registered

[ 1.116296] sunxi-mmc 1c0f000.mmc: base:0xc406d000 irq:23

[ 1.164273] mmc0: host does not support reading read-only switch, assuming write-enable

[ 1.175447] mmc0: new high speed SDHC card at address aaaa

[ 1.181516] sunxi-mmc 1c10000.mmc: base:0xc4071000 irq:24

[ 1.188067] usbcore: registered new interface driver usbhid

[ 1.193642] usbhid: USB HID core driver

[ 1.198264] mmcblk0: mmc0:aaaa SH32G 29.7 GiB

[ 1.205945] sun4i-codec 1c22c00.codec: ASoC: /soc/codec-analog@01c23000 not registered

[ 1.214005] sun4i-codec 1c22c00.codec: Failed to register our card

[ 1.222557] mmcblk0: p1 p2

[ 1.226601] sunxi-mmc 1c10000.mmc: card claims to support voltages below defined range

[ 1.235543] NET: Registered protocol family 17

[ 1.240229] Key type dns_resolver registered

[ 1.244640] Registering SWP/SWPB emulation handler

[ 1.254159] simple-framebuffer 43e89000.framebuffer: framebuffer at 0x43e89000, 0x177000 bytes, mapped to 0xc4380000

[ 1.264828] simple-framebuffer 43e89000.framebuffer: format=x8r8g8b8, mode=800x480x32, linelength=3200

[ 1.281149] Console: switching to colour frame buffer device 100x30

[ 1.293580] simple-framebuffer 43e89000.framebuffer: fb0: simplefb registered!

[ 1.302143] usb_phy_generic usb_phy_generic.0.auto: usb_phy_generic.0.auto supply vcc not found, using dummy regulator

[ 1.313539] musb-hdrc musb-hdrc.1.auto: MUSB HDRC host driver

[ 1.319382] musb-hdrc musb-hdrc.1.auto: new USB bus registered, assigned bus number 3

[ 1.328534] hub 3-0:1.0: USB hub found

[ 1.332400] hub 3-0:1.0: 1 port detected

[ 1.337713] using random self ethernet address

[ 1.342168] using random host ethernet address

[ 1.347755] usb0: HOST MAC 6a:16:d4:89:b8:6e

[ 1.352079] usb0: MAC 9e:83:ef:6f:8f:87

[ 1.355958] g_cdc gadget: CDC Composite Gadget, version: King Kamehameha Day 2008

[ 1.363545] g_cdc gadget: g_cdc ready

[ 1.369894] sun4i-codec 1c22c00.codec: Codec <-> 1c22c00.codec mapping ok

[ 1.378718] sun6i-rtc 1c20400.rtc: setting system clock to 1970-01-01 00:12:11 UTC (731)

[ 1.387148] vcc5v0: disabling

[ 1.390127] ALSA device list:

[ 1.393090] #0: V3s Audio Codec

[ 1.398477] EXT4-fs (mmcblk0p2): couldn't mount as ext3 due to feature incompatibilities

[ 1.407745] EXT4-fs (mmcblk0p2): couldn't mount as ext2 due to feature incompatibilities

[ 1.418684] mmc1: new high speed SDIO card at address 0001

[ 1.449345] EXT4-fs (mmcblk0p2): recovery complete

[ 1.456001] EXT4-fs (mmcblk0p2): mounted filesystem with ordered data mode. Opts: (null)

[ 1.464233] VFS: Mounted root (ext4 filesystem) on device 179:2.

[ 1.471107] devtmpfs: mounted

[ 1.475385] Freeing unused kernel memory: 1024K

[ 1.519728] musb-hdrc musb-hdrc.1.auto: VBUS_ERROR in b_idle (80, <SessEnd), retry #0, port1 00000100

[ 1.590177] EXT4-fs (mmcblk0p2): re-mounted. Opts: data=ordered

Starting logging: OK

Initializing random number generator... done.

Starting system message bus:

done

Starting network:

OK

Welcome to LicheePi

licheepi login: #25 全志 SOC » V3S RTL8723DS WiFi初始化无错误但找不到wlan0问题-验证中 » 2023-10-18 08:58:49

- kemp

- 回复: 16

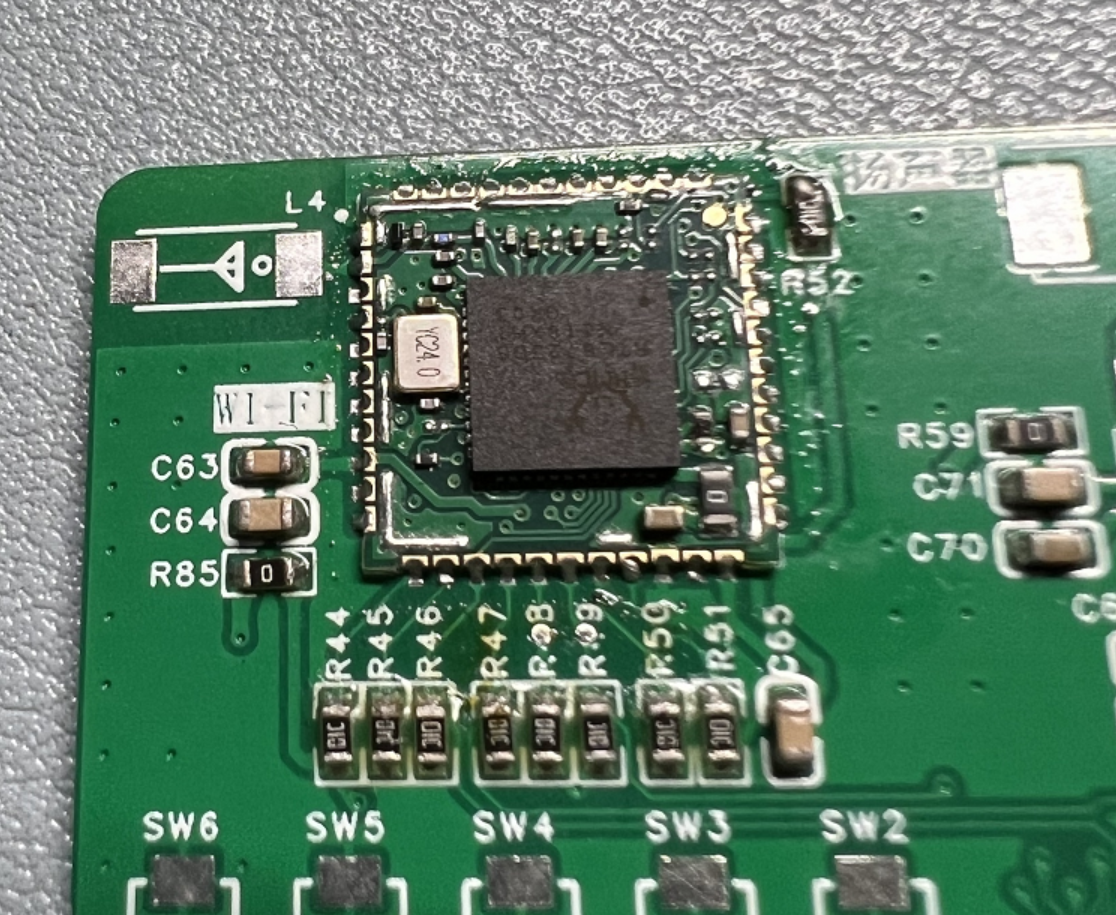

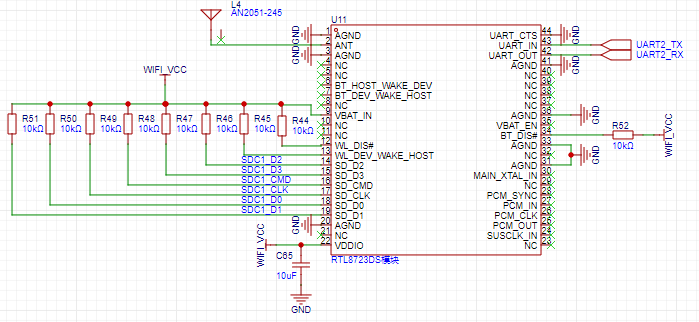

自己绘制的V3S板卡,RTL8723DS接到MMC1中 ,使用licheepi的dts文件,uboot、主线kernel4.1.3、buildroot均已正常跑起,已经关闭占用IO的leds,并且打开mmc1。

&mmc1 {

broken-cd;

bus-width = <4>;

vmmc-supply = <®_vcc3v3>;

status = "okay";

};

kernel中编译rtl8723bs的驱动(不知道bs和ds有没有差异,我查资料说ds只是多了bt功能),生成r8723bs.ko

同时拷贝wifi固件rtl8723bs_nic.bin 到根文件系统的 /lib/firmware/rtlwifi/ 目录下

insmod r8723bs.ko时,日志如下

# insmod r8723bs.ko

[ 486.608732] r8723bs: module is from the staging directory, the quality is unknown, you have been warned.

[ 486.625290] RTL8723BS: module init start

[ 486.629363] RTL8723BS: rtl8723bs v4.3.5.5_12290.20140916_BTCOEX20140507-4E40

[ 486.636428] RTL8723BS: rtl8723bs BT-Coex version = BTCOEX20140507-4E40

[ 486.643041] RTL8723BS: module init ret =0

#

# ifconfig -a

lo Link encap:Local Loopback

inet addr:127.0.0.1 Mask:255.0.0.0

UP LOOPBACK RUNNING MTU:65536 Metric:1

RX packets:0 errors:0 dropped:0 overruns:0 frame:0

TX packets:0 errors:0 dropped:0 overruns:0 carrier:0

collisions:0 txqueuelen:1000

RX bytes:0 (0.0 B) TX bytes:0 (0.0 B)从上面看加载驱动时并没有报相关的错误,但也没看到下载固件的日志,最终还是找不到wlan0

硬件信号测试:

模组VCC供电3.3V、电压纹波正常,天线未焊接

CLK线上有时钟信号产生,但是时钟下边沿不是0V,不知道有没有影响。

wifi模块原理图如下:

各位大佬能不能给个排查思路,感谢!

页次: 1

- 首页

- » 搜索

- » kemp 发表的帖子

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发