- 首页

- » 搜索

- » wuyu 发表的帖子

页次: 1

#1 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2026-04-08 11:52:31

#2 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2026-04-08 09:21:10

硬件资料和BSP还在整理中。主要是主线linux内核不好选择,需要支持g2d驱动才行。

另外先把Windows副屏驱动的源代码放上来。Windows副屏驱动

#3 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2026-03-31 09:24:46

#4 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2025-12-24 11:56:08

我是做软件开发的,硬件在哪里可以买到,我想买台自己玩,群主怎么联系?要不建个群大家一起玩

欢迎加入进来,这个项目就是缺做软件的。这个是驱动板的链接https://item.taobao.com/item.htm?id=997003052181

目前在建立一个wiki,打算先把硬件资料,BSP的编译加载的资料放上去。

#5 Re: 全志 SOC » 送T113-S3工程样板 » 2025-12-24 11:50:26

#6 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2025-12-07 11:42:28

#7 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2025-12-04 10:33:59

#8 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2025-11-22 11:24:54

#9 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2025-10-18 16:26:25

#10 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2025-10-17 14:59:24

wuyu 说:666

这个用哪个通讯协议呢? Ubuntu Linux下应该免驱吧?

https://github.com/JT365/beada

是一个DRM驱动,通迅协议是公开的Panel-Link.

#11 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2025-10-17 12:13:44

#12 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2025-10-16 11:05:39

#13 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2025-10-16 11:00:10

#14 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2025-10-15 17:30:20

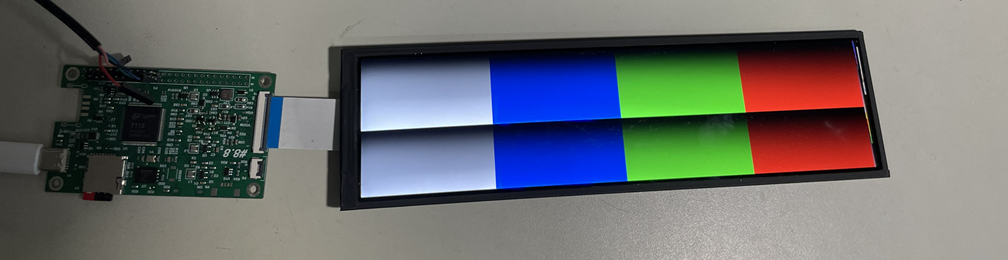

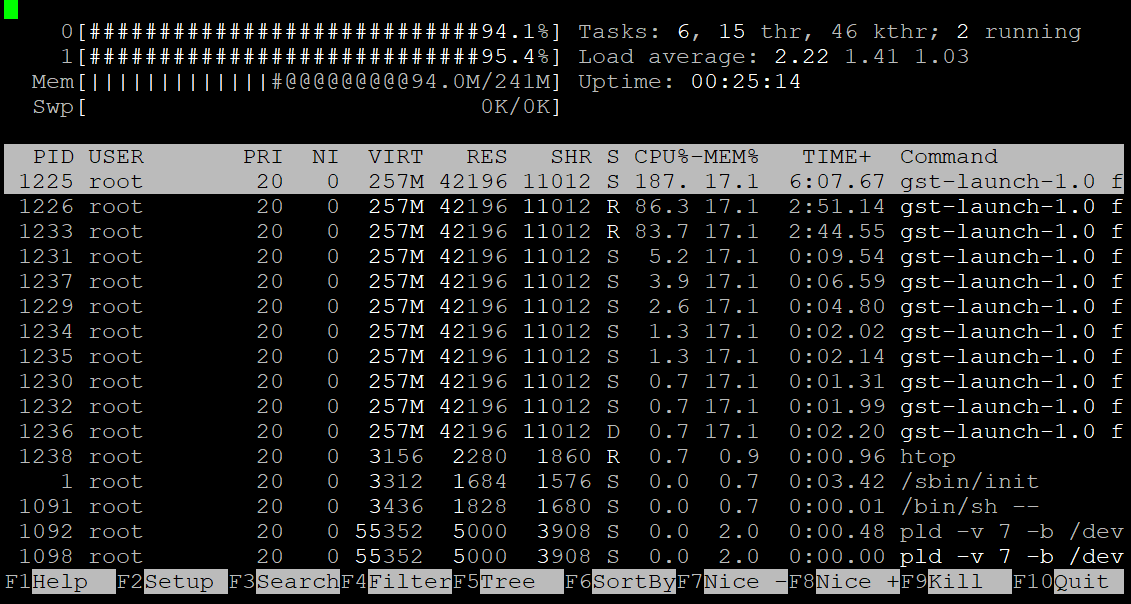

Mipi屏也调通了。也没怎么调,采用的whycan的驱动程序,一字没改就是通的。

/ # cat /sys/class/disp/disp/attr/sys

screen 0:

de_rate 300000000 hz, ref_fps:60

mgr0: 480x1920 fmt[rgb] cs[0x204] range[full] eotf[0x4] bits[8bits] err[0] force_sync[0] unblank direct_show[false] iommu[1]

dmabuf: cache[0] cache max[0] umap skip[0] umap skip max[90]

lcd output backlight(255) fps:60.6 480x1920

err:1 skip:156 irq:7663 vsync:0 vsync_skip:0

BUF enable ch[1] lyr[0] z[16] prem[N] a[pixel 255] fmt[ 0] fb[ 480,1920; 480,1920; 480,1920] crop[ 0, 0, 480,1920] frame[ 0, 0, 480,1920] addr[ 800000, 0, 0] flags[0x 0] trd[0,0]

depth[ 0] / #

#15 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2025-10-14 09:50:33

#16 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2025-10-14 09:34:52

不错,蹲个后续,到时加一个usb的副屏功能~

是有打算实现Windows副屏功能。

IddCx是微软和英国的DisplayLink联合开发的Windows虚拟显卡模型。它于2018年正式发布,支持的操作系统有Windows 10和Windows 11。它的基本原理是利用电脑现有的真实显卡资源,虚拟出一个或者多个Windows显卡以及对应的显示器。利用这项技术,可以很方便的开发出类似网络显示器,usb显示器或者无线显示器等应用。由于这项技术是DisplayLink主导开发的,所以微软的MSDN上对它的介绍也是语焉不详,一笔带过。开发者仅凭MSDN的资料很难开发出实用的虚拟显示器应用。

值得庆幸的是github上已经有了开源的IddCx驱动代码,而且还是一个中国人做的。我打算参考他的代码实现,然后设法把代码推送到他的git库中去。

https://github.com/chuanjinpang/win10_idd_xfz1986_usb_graphic_driver_display

据我所知,这个代码是全球范围内IddCx模型USB副屏驱动开源第一人。向作者致敬!他在本站也有账号:

https://whycan.com/t_9873.html

#17 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2025-10-10 22:07:53

#18 Re: 全志 SOC » 送T113-S3工程样板 » 2025-10-10 07:58:44

#19 Re: 全志 SOC » 送T113-S3工程样板 » 2025-10-09 10:21:58

#20 Re: 全志 SOC » 送T113-S3工程样板 » 2025-10-09 09:37:51

#21 Re: 全志 SOC » 送T113-S3工程样板 » 2025-10-09 09:30:16

#22 Re: 全志 SOC » 送T113-S3工程样板 » 2025-10-08 18:59:00

#23 全志 SOC » 送T113-S3工程样板 » 2025-10-08 12:58:04

- wuyu

- 回复: 19

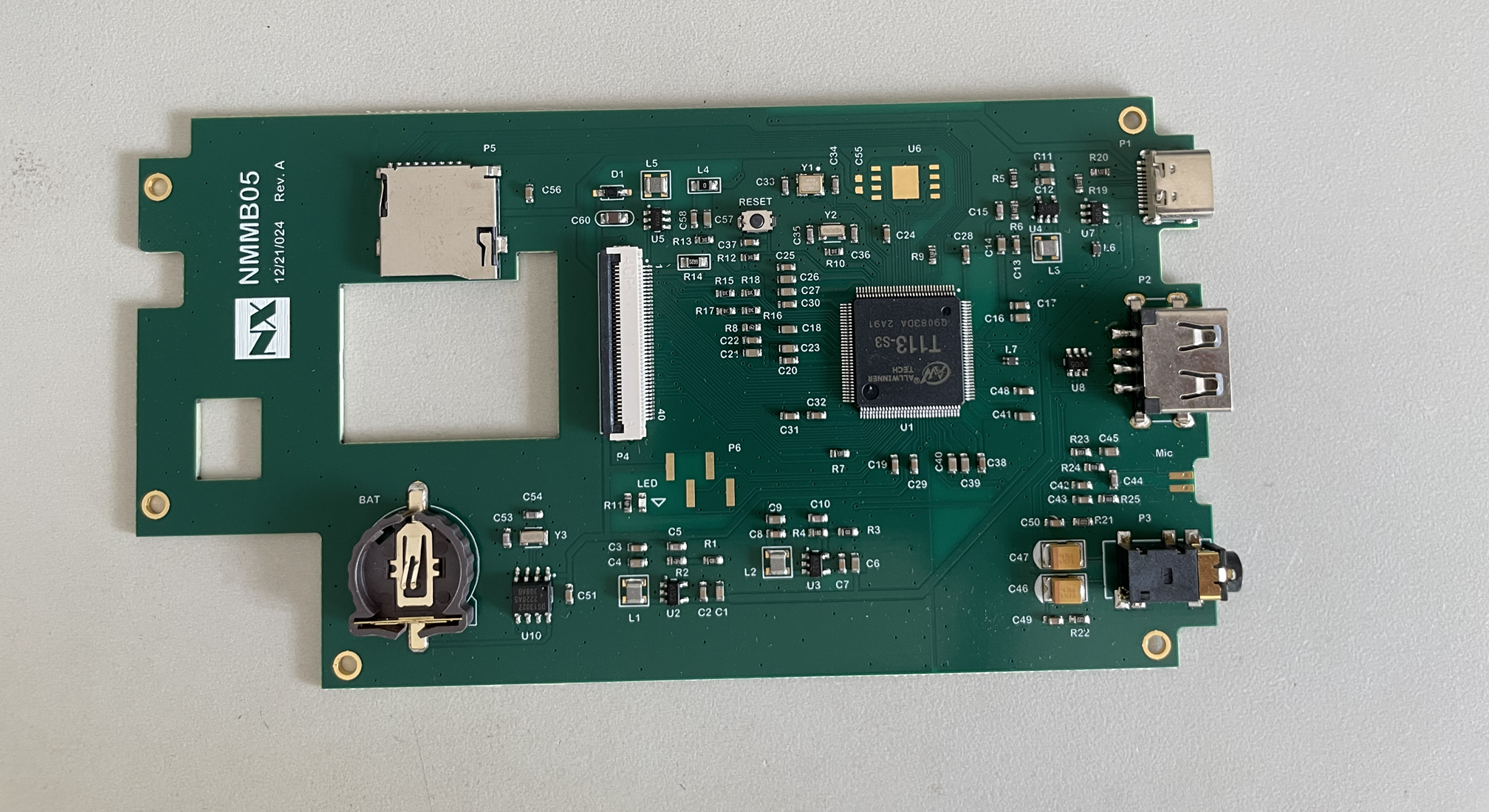

样板功能正常,因为产品外型改变成为了呆料。

基本规格:

1、T113-S3 SOC

2、USB Type A接口(未焊接)

3、USB Type C接口

4、Audio输出

5、板内Mic(未焊接)

6、调试串口(未焊接)

7、spi Flash(未焊接)

8、通用40Pin LCD接口(可接常见的5寸800x480屏)

9、板上RTC电路(不带电池)

一共20块,送有缘人(每人只得一块,送完即止),提供原理图,不提供技术支持。

-------------------------------------------------------------

2025-10-09 更新:

#8

这是原理图:maple.pdf

#9

考虑了一下,不再免费送了,象征性收10元。每人限购一个。淘宝链接

#24 Re: 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2025-10-07 12:58:39

#25 全志 SOC » 用T113-S4搭建一个8.8寸长条屏HMI开发平台 » 2025-10-07 07:13:03

- wuyu

- 回复: 35

愿景就是用最流行的硬件元素搭建一个通用的HMI开发平台,方便广大工程师朋友和电子发烧友验证和拓展自己的想法。

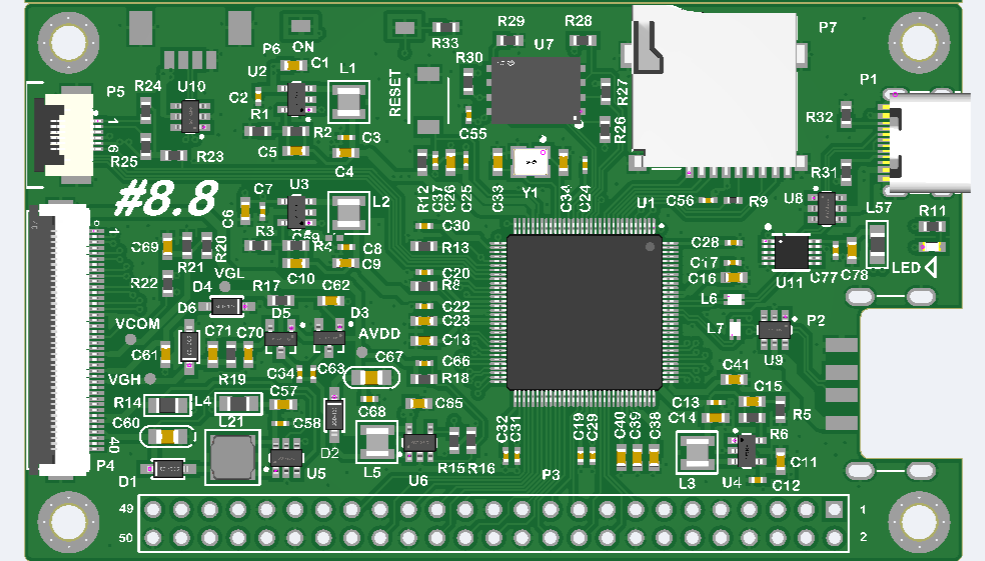

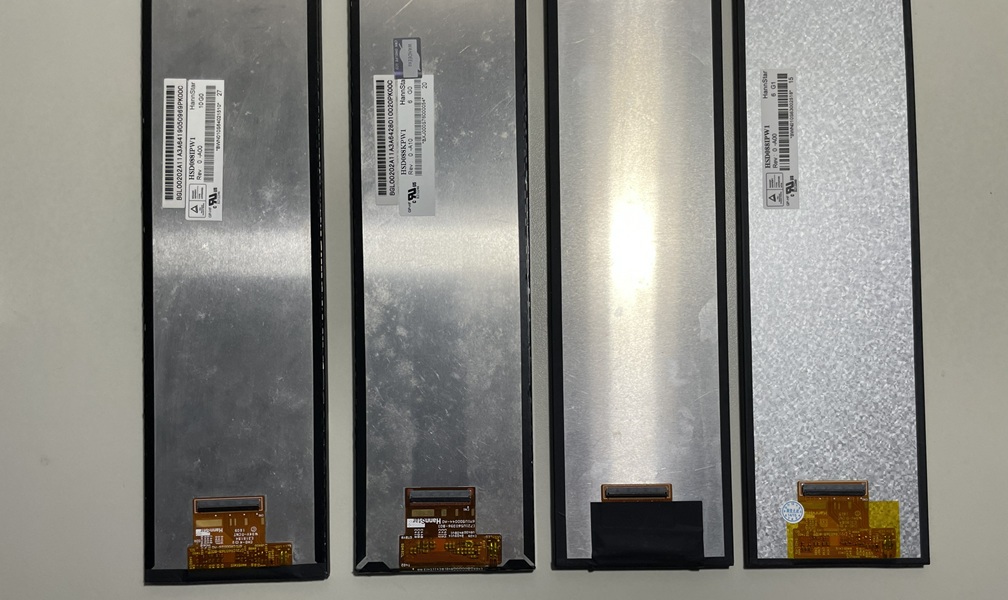

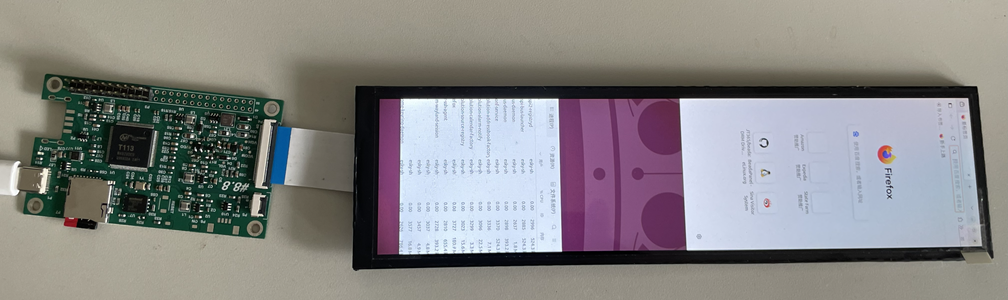

SOC选用T113-S4,是当红的全志SOC平台,双A7自带256MB内存,足够支撑Qt之类的图形应用开发;屏幕选用8.8寸MIPI长条屏,国内众多厂家都有出品,淘宝上早卖成了白菜价。最后希望这个平台能够做到5年之内不过时,不停产。

板子已经画好了。带一个USB Type A和一个Type C接口,液晶屏和触摸屏接口在左侧。SOC多余的引脚通过下方的双排针引出。板子比较紧凑84mmx50mm。

欢迎大家留言讨论。板子打样回来以后,我会更新后续的调试进展。

#27 Re: 全志 SOC » 整理一些 D1 / D1s 的 DisplayEngine / LCD / HDMI 常用骚操作 » 2025-01-14 13:44:15

LCD0重新初始化:

mount -t debugfs none /sys/kernel/debug; cd /sys/kernel/debug/dispdbg; echo suspend > command; echo disp0 > name; echo 1 > start echo resume > command; echo disp0 > name; echo 1 > start find / -name pinmux-pins |xargs cat

楼主,这个重新初始化,disp0的配置是从哪里读取的?比如lcd时钟设置等等。我能不能修改配置,比如lcd的旋转角度,然后再重新初始化disp0?

#29 Re: 全志 SOC » 哪吒D1使用gstreamer硬解码 » 2024-11-04 13:41:18

这是第二次不出图像的时候的log:

root@(none):/# GST_DEBUG=3 gst-launch-1.0 filesrc location=/mnt/vfat/album/video

/2020BLACKPINK1280x480.mp4 ! decodebin3 ! sunxifbsink

-->sunxifbsink init.

Setting pipeline to PAUSED ...

dd: error writing '/dev/fb0': No space left on device

[ 317.151764] VE: enable hw clock

6406+0 records in

6405+0 records out

[ 317.159162] enable_cedar_hw_clk,552

Succesfully opened fbdev framebuffer device /dev/fb0, mapped sized 12.00 MB of which 10.95 MB (7 buffers) usable for page flipping.

fbdev phy=0x00000000,len=0x320a00,vir=0xb5aac000,size=0xc00000.

-->/dev/transform does not exist, hardware rotation is not supported.

-->reserver layer called (screen = 480 x 854).

-->Hardware overlay available.

Succesfully opened screen of pixel depth 32, dimensions 480 x 854, format BGRx, 12.00 MB video memory available, max 7 pannable screen buffers, vsync enabled.

0:00:00.138380542 392 0xba3360 WARN basesrc gstbasesrc.c:3600:gst_base_src_start_complete:<filesrc0> pad not activated yet

Pipeline is PREROLLING ...

0:00:00.171607375 392 0xafdd68 WARN qtdemux qtdemux.c:3308:qtdemux_parse_trex:<qtdemux0> failed to find fragment defa[ 317.252563] VE: VE real_freq=576000000

[ 317.252563]

ults for stream 1

0:00:00.181692875 392 0xafdd68 FIXME decodebin3 gstdecodebin3.c:1098:update_requested_selection:<decodebin3-0> Implement EXPOSE_ALL_MODE

0:00:00.185581500 392 0xafdd68 FIXME decodebin3 gstdecodebin3-parse.c:420:parsebin_buffer_probe:<decodebin3-0> Re-use existing input streams if/when possible

0:00:00.187064167 392 0xb511fb50 FIXME decodebin3 gstdecodebin3.c:1528:get_output_for_slot:<decodebin3-0> emit autoplug-continue

0:00:00.187181708 392 0xb511fb50 FIXME decodebin3 gstdecodebin3.c:1531:get_output_for_slot:<decodebin3-0> Handle EXPOSE_ALL_MODE

0:00:00.196250875 392 0xb511fb50 ERROR omx gstomx.c:4036:plugin_init: Invalid type name 'GstOMXVP8Dec' for element 'omxvp8videodec'

0:00:00.196417417 392 0xb511fb50 ERROR omx gstomx.c:4036:plugin_init: Invalid type name 'GstOMXH265Dec' for element 'omxhevcvideodec'

INFO : cedarc <VeInitialize:1476>: *** ic_version = 0x1301000010210,

INFO : cedarc <VeRelease:1667>: not malloc locks

INFO : cedarc <VeInitialize:1476>: *** ic_version = 0x1301000010210,

WARNING: omx_vdec <__AwOmxVdecSetParameter:1593>: Set Parameter called in valid state

ERROR : omx_vdec <AwOmxVdecPortGetFormat:364>: erro: pParamData->nIndex > m_sPortFormatType.nIndex

0:00:00.222868083 392 0xb511fb50 ERROR omxvideodec gstomxvideodec.c:2083:gst_omx_video_dec_negotiate:<omxh264dec-omxh264dec0> Empty caps

WARNING: cedarc <AddVDPlugin:1614>: 1117 get local path: /usr/lib/

WARNING: omx_vdec <__AwOmxVdecGetConfig:1667>: +++++ get display crop: top[0],left[0],width[1280],height[480]

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_aacdec.so

---->sunxifb pre overlay(SCWxSCN=1280 x 480,out_rec=[0 187,480,480]).

Using one framebuffer plus 8 overlays in video memory (format YV12).

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_alacdec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_amrdec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_apedec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_atrcdec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_dsddec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_flacdec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_g729dec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_mp3dec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_oggdec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_opusdec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_radec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_siprdec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_wavdec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, [ 317.642333] VE: VE real_freq=576000000

[ 317.642333]

CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libawh264.so

INFO : cedarc <CedarPluginVDInit:80>: register h264 decoder success!

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libawh265.so

INFO : cedarc <CedarPluginVDInit:85>: register h265 decoder success!

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libawmjpeg.so

INFO : cedarc <CedarPluginVDInit:84>: register mjpeg decoder success!

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libawmpeg2.so

INFO : cedarc <CedarPluginVDInit:86>: register mpeg2 decoder success!

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libawmpeg4base.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libawmpeg4dx.so

INFO : cedarc <CedarPluginVDInit:98>: register mpeg4dx decoder success!

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libawmpeg4h263.so

INFO : cedarc <CedarPluginVDInit:79>: register mpeg4H263 decoder success!

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libawmpeg4normal.so

INFO : cedarc <CedarPluginVDInit:90>: register mpeg4Normal decoder success!

INFO : cedarc <log_set_level:71>: Set log level to 5 from /vendor/etc/cedarc.conf

ERROR : cedarc <DebugCheckConfig:360>: now cedarc log level:5

WARNING: cedarc <InitializeVideoDecoder:668>: warning: the nDeInterlaceHoldingFrameBufferNum is 0

WARNING: cedarc <InitializeVideoDecoder:677>: warning: the nDisplayHoldingFrameBufferNum is 0

WARNING: omx_vdec <__AwOmxVdecGetConfig:1667>: +++++ get display crop: top[0],left[0],width[1280],height[480]

0:00:00.654857292 392 0xbce6f8 ERROR omx gstomx.c:2621:gst_omx_port_allocate_buffers_unlocked:<omxh264dec-omxh264dec0> Allocated buffers for avc port 1: Not implemented (0x80001006)

-->show_layer id (0).

Pipeline is PREROLLED ...

Setting pipeline to PLAYING ...

New clock: GstSystemClock

0:00:19.489524926 392 0xafdd68 WARN decodebin3 gstdecodebin3.c:756:parsebin_drained_cb:<decodebin3-0> input 0xbb2288 drained

0:00:19.489690009 392 0xafdd68 WARN decodebin3 gstdecodebin3.c:767:parsebin_drained_cb:<decodebin3-0> All inputs drained. Posting about-to-finish

0:00:19.494544176 392 0xafdd68 FIXME decodebin3 gstdecodebin3-parse.c:137:check_all_streams_for_eos:<parsebin0:src_0> Remove input stream

0:00:19.780261634 392 0xb511fb50 FIXME decodebin3 gstdecodebin3.c:1837:multiqueue_src_probe:<multiqueue0:src_0> EOS on multiqueue source pad. input:0xb3c1a480

0:00:19.780558718 392 0xb511fb50 FIXME decodebin3 gstdecodebin3.c:1837:multiqueue_src_probe:<multiqueue0:src_0> EOS on multiqueue source pad. input:0xb3c1a480

Got EOS from element "pipeline0".

Execution ended after 0:00:20.060703051

Setting pipeline to NULL ...

482 frames rendered, 482 from system memory, 0 from video memory.[ 337.951828] VE: disable hw clock

-->sunxifbsink close.

-->sunxifbsink_hide_layer.

-->sunxifbsink_release_layer.

[ 337.960526] disable_cedar_hw_clk,592

Freeing pipeline ...

#30 Re: 全志 SOC » 哪吒D1使用gstreamer硬解码 » 2024-11-04 13:37:57

楼主你好,

你在D1h上有没有遇到sunxifbsink组件只能运行一次的情况?我这边在T113平台上,第一次播放成功了,但是第二次运行的时候就不出图像了。我用fbdevsink也做过对比测试,fbdevsink就可以反复播放。

这是第一次播放时候的log:

root@(none):/# gst-launch-1.0 filesrc location=/mnt/vfat/album/video/2020BLACKPI

NK1280x480.mp4 ! decodebin3 ! sunxifbsink rotate-angle=3

-->sunxifbsink init.

Setting pipeline to PAUSED ...

dd: error writing '/dev/fb0': No space left on device

6406+0 records in

6405+0 records out

[ 105.577056] VE: enable hw clock

[ 105.582910] enable_cedar_hw_clk,552

Succesfully opened fbdev framebuffer device /dev/fb0, mapped sized 12.00 MB of which 10.95 MB (7 buffers) usable for page flipping.

fbdev phy=0x00000000,len=0x320a00,vir=0xb5a79000,size=0xc00000.

-->/dev/transform does not exist, hardware rotation is not supported.

-->reserver layer called (screen = 480 x 854).

-->Hardware overlay available.

Succesfully opened screen of pixel depth 32, dimensions 480 x 854, format BGRx, 12.00 MB video memory available, max 7 pannable screen buffers, vsync enabled.

Pipeline is PREROLLING ...

INFO : cedarc <VeInitialize:1476>: *** ic_version = 0x1301000010210,

[ 105.811615] VE: VE real_freq=576000000

[ 105.811615]

INFO : cedarc <VeRelease:1667>: not malloc locks

INFO : cedarc <VeInitialize:1476>: *** ic_version = 0x1301000010210,

WARNING: omx_vdec <__AwOmxVdecSetParameter:1593>: Set Parameter called in valid state

ERROR : omx_vdec <AwOmxVdecPortGetFormat:364>: erro: pParamData->nIndex > m_sPortFormatType.nIndex

WARNING: omx_vdec <__AwOmxVdecGetConfig:1667>: +++++ get display crop: top[0],left[0],width[1280],height[480]

WARNING: cedarc <AddVDPlugin:1614>: 1117 get local path: /usr/lib/

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_aacdec.so

---->sunxifb pre overlay(SCWxSCN=1280 x 480,out_rec=[0 187,480,480]).

Using one framebuffer plus 8 overlays in video memory (format YV12).

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_alacdec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_amrdec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_apedec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_atrcdec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_dsddec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_flacdec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624[ 105.971969] VE: VE real_freq=576000000

[ 105.971969]

>: 1117 load so: /usr/lib/libaw_g729dec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_mp3dec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_oggdec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_opusdec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_radec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_siprdec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libaw_wavdec.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libawh264.so

INFO : cedarc <CedarPluginVDInit:80>: register h264 decoder success!

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libawh265.so

INFO : cedarc <CedarPluginVDInit:85>: register h265 decoder success!

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libawmjpeg.so

INFO : cedarc <CedarPluginVDInit:84>: register mjpeg decoder success!

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libawmpeg2.so

INFO : cedarc <CedarPluginVDInit:86>: register mpeg2 decoder success!

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libawmpeg4base.so

WARNING: cedarc <AddVDPluginSingle:1464>: Invalid plugin, CedarPluginVDInit not found.

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libawmpeg4dx.so

INFO : cedarc <CedarPluginVDInit:98>: register mpeg4dx decoder success!

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libawmpeg4h263.so

INFO : cedarc <CedarPluginVDInit:79>: register mpeg4H263 decoder success!

WARNING: cedarc <AddVDPlugin:1624>: 1117 load so: /usr/lib/libawmpeg4normal.so

INFO : cedarc <CedarPluginVDInit:90>: register mpeg4Normal decoder success!

INFO : cedarc <log_set_level:71>: Set log level to 5 from /vendor/etc/cedarc.conf

ERROR : cedarc <DebugCheckConfig:360>: now cedarc log level:5

WARNING: cedarc <InitializeVideoDecoder:668>: warning: the nDeInterlaceHoldingFrameBufferNum is 0

WARNING: cedarc <InitializeVideoDecoder:677>: warning: the nDisplayHoldingFrameBufferNum is 0

WARNING: omx_vdec <__AwOmxVdecGetConfig:1667>: +++++ get display crop: top[0],left[0],width[1280],height[480]

-->show_layer id (0).

Pipeline is PREROLLED ...

Setting pipeline to PLAYING ...

New clock: GstSystemClock

Got EOS from element "pipeline0".

Execution ended after 0:00:20.060249177

Setting pipeline to NULL ...

482 frames rendered, 482 from system memory, 0 from video memory.

[ 126.293057] L2 PageTable Invalid

[ 126.302169] 0x23ae000 is not mapped!

[ 126.306173] DE invalid address: 0x23ae000, data:0x0, id:0x4

-->sunxifbsink close.

-->sunxifbsink_hide_layer.

-->sunxifbsink_release_layer.

[ 126.312479] L2 PageTable Invalid

[ 126.323177] 0x2300000 is not mapped!

[ 126.327179] DE invalid address: 0x2300000, data:0x0, id:0x4

[ 126.333438] L2 PageTable Invalid

[ 126.337049] 0x2300000 is not mapped!

[ 126.341051] DE invalid address: 0x2300000, data:0x0, id:0x4

[ 126.348407] VE: disable hw clock

[ 126.352057] disable_cedar_hw_clk,592

Freeing pipeline ...

#33 Re: 全志 SOC » T113-S3 测试gstreamer sunxifbsink组件出现异常 » 2024-10-27 15:34:10

同样的环境,用fbdevsink组件测试是成功的。

root@(none):/# GST_DEBUG=3 gst-launch-1.0 videotestsrc ! fbdevsink

divx class init!

0:00:00.783731584 1403 0x1802460 ERROR omx gstomx.c:4036:plugin_init: Invalid type name 'GstOMXVP8Dec' for element 'omxvp8videodec'

0:00:00.784432667 1403 0x1802460 ERROR omx gstomx.c:4036:plugin_init: Invalid type name 'GstOMXH265Dec' for element 'omxhevcvideodec'

mjpeg class init!

0:00:01.166389251 1403 0x1802460 WARN GST_PLUGIN_LOADING gstplugin.c:793:_priv_gst_plugin_load_file_for_registry: module_open failed: /usr/lib/gstreamer-1.0/libgstvideo4linux2.so: undefined symbol: gst_v4l2_buffer_pool_resurect_buffer

(gst-plugin-scanner:1403): GStreamer-WARNING **: 15:17:25.634: Failed to load plugin '/usr/lib/gstreamer-1.0/libgstvideo4linux2.so': /usr/lib/gstreamer-1.0/libgstvideo4linux2.so: undefined symbol: gst_v4l2_buffer_pool_resurect_buffer

Setting pipeline to PAUSED ...

Pipeline is PREROLLING ...

0:00:01.552186584 1402 0x1cb2880 FIXME default gstutils.c:3981:gst_pad_create_stream_id_internal:<videotestsrc0:src> Creating random stream-id, consider implementing a deterministic way of creating a stream-id

Pipeline is PREROLLED ...

Setting pipeline to PLAYING ...

New clock: GstSystemClock

#34 Re: 全志 SOC » T113-S3 测试gstreamer sunxifbsink组件出现异常 » 2024-10-25 15:47:55

由错误日志

L2 PageTable Invalid

[ 19.590243] 0x321000 is not mapped!

[ 19.594130] DE invalid address: 0x321000, data:0x0, id:0x4

跟踪到了sunxi-iommu.c文件当中的

static irqreturn_t sunxi_iommu_irq(int irq, void *dev_id)

{

u32 inter_status_reg = 0;

u32 addr_reg = 0;

u32 int_masterid_bitmap = 0;

u32 data_reg = 0;

u32 l1_pgint_reg = 0;

u32 l2_pgint_reg = 0;

u32 master_id = 0;

unsigned long mflag;

struct sunxi_iommu_dev *iommu = dev_id;

spin_lock_irqsave(&iommu->iommu_lock, mflag);

inter_status_reg = sunxi_iommu_read(iommu, IOMMU_INT_STA_REG) & 0x3ffff;

l1_pgint_reg = sunxi_iommu_read(iommu, IOMMU_L1PG_INT_REG);

l2_pgint_reg = sunxi_iommu_read(iommu, IOMMU_L2PG_INT_REG);

int_masterid_bitmap = inter_status_reg | l1_pgint_reg | l2_pgint_reg;

if (inter_status_reg & MICRO_TLB0_INVALID_INTER_MASK) {

pr_err("%s Invalid Authority\n", master[0]);

addr_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_ADDR_REG0);

data_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_DATA_REG0);

} else if (inter_status_reg & MICRO_TLB1_INVALID_INTER_MASK) {

pr_err("%s Invalid Authority\n", master[1]);

addr_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_ADDR_REG1);

data_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_DATA_REG1);

} else if (inter_status_reg & MICRO_TLB2_INVALID_INTER_MASK) {

pr_err("%s Invalid Authority\n", master[2]);

addr_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_ADDR_REG2);

data_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_DATA_REG2);

} else if (inter_status_reg & MICRO_TLB3_INVALID_INTER_MASK) {

pr_err("%s Invalid Authority\n", master[3]);

addr_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_ADDR_REG3);

data_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_DATA_REG3);

} else if (inter_status_reg & MICRO_TLB4_INVALID_INTER_MASK) {

pr_err("%s Invalid Authority\n", master[4]);

addr_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_ADDR_REG4);

data_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_DATA_REG4);

} else if (inter_status_reg & MICRO_TLB5_INVALID_INTER_MASK) {

pr_err("%s Invalid Authority\n", master[5]);

addr_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_ADDR_REG5);

data_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_DATA_REG5);

}

#if IS_ENABLED(CONFIG_ARCH_SUN8IW15) || IS_ENABLED(CONFIG_ARCH_SUN50IW9) \

|| IS_ENABLED(CONFIG_ARCH_SUN8IW19) || IS_ENABLED(CONFIG_ARCH_SUN50IW10) \

|| IS_ENABLED(CONFIG_ARCH_SUN8IW20) || IS_ENABLED(CONFIG_ARCH_SUN50IW12) \

|| IS_ENABLED(CONFIG_ARCH_SUN20IW1) || IS_ENABLED(CONFIG_ARCH_SUN55IW3)

else if (inter_status_reg & MICRO_TLB6_INVALID_INTER_MASK) {

pr_err("%s Invalid Authority\n", master[6]);

addr_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_ADDR_REG6);

data_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_DATA_REG6);

} else if (inter_status_reg & L1_PAGETABLE_INVALID_INTER_MASK) {

/*It's OK to prefetch an invalid pagetable,no need to print msg for debug.*/

if (!(int_masterid_bitmap & (1U << 31)))

pr_err("L1 PageTable Invalid\n");

addr_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_ADDR_REG7);

data_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_DATA_REG7);

} else if (inter_status_reg & L2_PAGETABLE_INVALID_INTER_MASK) {

if (!(int_masterid_bitmap & (1U << 31)))

pr_err("L2 PageTable Invalid\n");

addr_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_ADDR_REG8);

data_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_DATA_REG8);

}

#else

else if (inter_status_reg & L1_PAGETABLE_INVALID_INTER_MASK) {

pr_err("L1 PageTable Invalid\n");

addr_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_ADDR_REG6);

data_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_DATA_REG6);

} else if (inter_status_reg & L2_PAGETABLE_INVALID_INTER_MASK) {

pr_err("L2 PageTable Invalid\n");

addr_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_ADDR_REG7);

data_reg = sunxi_iommu_read(iommu, IOMMU_INT_ERR_DATA_REG7);

}

#endif

else

pr_err("sunxi iommu int error!!!\n");

if (!(int_masterid_bitmap & (1U << 31))) {

if (sunxi_iova_invalid_helper(addr_reg)) {

int_masterid_bitmap &= 0xffff;

master_id = __ffs(int_masterid_bitmap);

}

pr_err("%s invalid address: 0x%x, data:0x%x, id:0x%x\n",

master[master_id], addr_reg, data_reg,

int_masterid_bitmap);

}

#if IS_ENABLED(CONFIG_ARCH_SUN8IW19) || IS_ENABLED(CONFIG_ARCH_SUN50IW9) \

|| IS_ENABLED(CONFIG_ARCH_SUN50IW10)

sunxi_iommu_write(iommu, IOMMU_TLB_IVLD_START_ADDR_REG, addr_reg);

sunxi_iommu_write(iommu, IOMMU_TLB_IVLD_END_ADDR_REG, addr_reg + 4 * SPAGE_SIZE);

sunxi_iommu_write(iommu, IOMMU_TLB_IVLD_ENABLE_REG, 0x1);

while (sunxi_iommu_read(iommu, IOMMU_TLB_IVLD_ENABLE_REG) & 0x1)

;

sunxi_iommu_write(iommu, IOMMU_PC_IVLD_ADDR_REG, addr_reg);

sunxi_iommu_write(iommu, IOMMU_PC_IVLD_ENABLE_REG, 0x1);

while (sunxi_iommu_read(iommu, IOMMU_PC_IVLD_ENABLE_REG) & 0x1)

;

sunxi_iommu_write(iommu, IOMMU_PC_IVLD_ADDR_REG,

addr_reg + 0x200000);

sunxi_iommu_write(iommu, IOMMU_PC_IVLD_ENABLE_REG, 0x1);

while (sunxi_iommu_read(iommu, IOMMU_PC_IVLD_ENABLE_REG) & 0x1)

;

#elif IS_ENABLED(CONFIG_ARCH_SUN8IW20) || IS_ENABLED(CONFIG_ARCH_SUN50IW12) \

|| IS_ENABLED(CONFIG_ARCH_SUN20IW1) || IS_ENABLED(CONFIG_ARCH_SUN55IW3)

sunxi_iommu_write(iommu, IOMMU_TLB_IVLD_START_ADDR_REG, addr_reg);

sunxi_iommu_write(iommu, IOMMU_TLB_IVLD_END_ADDR_REG, addr_reg + 4 * SPAGE_SIZE);

sunxi_iommu_write(iommu, IOMMU_TLB_IVLD_ENABLE_REG, 0x1);

while (sunxi_iommu_read(iommu, IOMMU_TLB_IVLD_ENABLE_REG) & 0x1)

;

sunxi_iommu_write(iommu, IOMMU_PC_IVLD_START_ADDR_REG, addr_reg);

sunxi_iommu_write(iommu, IOMMU_PC_IVLD_END_ADDR_REG, addr_reg + 2 * SPD_SIZE);

sunxi_iommu_write(iommu, IOMMU_PC_IVLD_ENABLE_REG, 0x1);

while (sunxi_iommu_read(iommu, IOMMU_PC_IVLD_ENABLE_REG) & 0x1)

;

#else

sunxi_iommu_write(iommu, IOMMU_TLB_IVLD_ADDR_REG, addr_reg);

sunxi_iommu_write(iommu, IOMMU_TLB_IVLD_ADDR_MASK_REG,

(u32)IOMMU_PT_MASK);

sunxi_iommu_write(iommu, IOMMU_TLB_IVLD_ENABLE_REG, 0x1);

while (sunxi_iommu_read(iommu, IOMMU_TLB_IVLD_ENABLE_REG) & 0x1)

;

sunxi_iommu_write(iommu, IOMMU_TLB_IVLD_ADDR_REG,

addr_reg + 0x2000);

sunxi_iommu_write(iommu, IOMMU_TLB_IVLD_ADDR_MASK_REG,

(u32)IOMMU_PT_MASK);

sunxi_iommu_write(iommu, IOMMU_TLB_IVLD_ENABLE_REG, 0x1);

while (sunxi_iommu_read(iommu, IOMMU_TLB_IVLD_ENABLE_REG) & 0x1)

;

sunxi_iommu_write(iommu, IOMMU_PC_IVLD_ADDR_REG, addr_reg);

sunxi_iommu_write(iommu, IOMMU_PC_IVLD_ENABLE_REG, 0x1);

while (sunxi_iommu_read(iommu, IOMMU_PC_IVLD_ENABLE_REG) & 0x1)

;

sunxi_iommu_write(iommu, IOMMU_PC_IVLD_ADDR_REG,

addr_reg + 0x200000);

sunxi_iommu_write(iommu, IOMMU_PC_IVLD_ENABLE_REG, 0x1);

while (sunxi_iommu_read(iommu, IOMMU_PC_IVLD_ENABLE_REG) & 0x1)

;

#endif

sunxi_iommu_write(iommu, IOMMU_INT_CLR_REG, inter_status_reg);

inter_status_reg |= (l1_pgint_reg | l2_pgint_reg);

inter_status_reg &= 0xffff;

sunxi_iommu_write(iommu, IOMMU_RESET_REG, ~inter_status_reg);

sunxi_iommu_write(iommu, IOMMU_RESET_REG, 0xffffffff);

spin_unlock_irqrestore(&iommu->iommu_lock, mflag);

return IRQ_HANDLED;

}

感觉内存还没有映射好。也就是初始化的问题。

#35 Re: 全志 SOC » T113-S3 测试gstreamer sunxifbsink组件出现异常 » 2024-10-25 15:45:58

今天测试了一下,fbdev2sink组件也有问题。

root@TinaLinux:/# GST_DEBUG=3 gst-launch-1.0 videotestsrc ! fbdev2sink

divx class init!

0:00:00.781325584 2157 0x20f45a0 ERROR omx gstomx.c:4036:plugin_init: Invalid type name 'GstOMXVP8Dec' for element 'omxvp8videodec'

0:00:00.781992209 2157 0x20f45a0 ERROR omx gstomx.c:4036:plugin_init: Invalid type name 'GstOMXH265Dec' for element 'omxhevcvideodec'

mjpeg class init!

0:00:01.428525959 2156 0x1a959c0 WARN GST_REGISTRY gstregistry.c:1841:gst_update_registry: registry update failed: Error writing registry cache to /root/.cache/gstreamer-1.0/registry.arm.bin: No such file or d[ 19.492522] VE: enable hw clock

irectory

Setting pipeline to PAUSED ...

[ 19.499475] enable_cedar_hw_clk,563

Succesfully opened fbdev framebuffer device /dev/fb0, mapped sized 12.00 MB of which 10.95 MB (7 buffers) usable for page flipping.

fbdev phy=0x00000000,len=0x320a00,vir=0xb5c35000,size=0xc00000.

Succesfully opened screen of pixel depth 32, dimensions 480 x 854, format BGRx, 12.00 MB video memory available, max 7 pannable screen buffers, vsync enabled.

Pipeline is PREROLLING ...

0:00:01.476811043 2156 0x19e28b8 FIXME default gstutils.c:3981:gst_pad_create_stream_id_internal:<videotestsrc0:src> Creating random stream-id, consider implementing a deterministic way of creating a stream-id

Using 3 framebuffers for page flipping.

Allocating 3 screen buffers.

Pipeline is PREROLLED ...

Setting pipeline to[ 19.581106] L2 PageTable Invalid

[ 19.590243] 0x321000 is not mapped!

[ 19.594130] DE invalid address: 0x321000, data:0x0, id:0x4

PLAYING ...

New clock: GstSystemClock

[ 19.601317] L2 PageTable Invalid

[ 19.607440] 0x321000 is not mapped!

[ 19.611348] DE invalid address: 0x321000, data:0x0, id:0x4

[ 19.682155] L2 PageTable Invalid

[ 19.685766] 0x321000 is not mapped!

[ 19.689654] DE invalid address: 0x321000, data:0x0, id:0x4

[ 19.702361] L2 PageTable Invalid

[ 19.705970] 0x321000 is not mapped!

[ 19.709878] DE invalid address: 0x321000, data:0x0, id:0x4

^Chandling interrupt.

Interrupt: Stopping pipeline ...

Execution ended after 0:00:31.326661723

Setting pipeline to NULL ...

942 frames rendered, 942 from system memory, 0 from video memory.[ 50.886824] VE: disable hw clock

[ 50.895704] disable_cedar_hw_clk,603

Freeing pipeline ...

#36 全志 SOC » T113-S3 测试gstreamer sunxifbsink组件出现异常 » 2024-10-23 11:31:21

- wuyu

- 回复: 7

用的100ask tina5.0开发环境。按照这个帖子配置的G2D。

https://bbs.aw-ol.com/topic/4086/t113-s3-%E9%A9%B1%E5%8A%A8%E5%B1%8F%E5%B9%95%E6%98%BE%E7%A4%BA%E9%97%AE%E9%A2%98

openwrt环境,测试gstreamer sunxifbsink组件出现异常。大虾们能帮我看看,问题可能在哪?测试命令和异常日志如下:

root@TinaLinux:/# gst-launch-1.0 videotestsrc ! sunxifbsink

divx class init!

mjpeg class init!

-->sunxifbsink init.

Setting pipeline to PAUSED ...

dd: error writing '/dev/fb0': No space left on device

[ 132.495401] VE: enable hw clock

6406+0 records in

6405+0 records out

[ 132.502556] enable_cedar_hw_clk,563

Succesfully opened fbdev framebuffer device /dev/fb0, mapped sized 12.00 MB of which 10.95 MB (7 buffers) usable for page flippi[ 132.524014] 8<--- cut here ---

ng.

fbdev phy=0x00000000,len=0x320a00,vir=0xb5c89000,size=0xc00000.

-->/dev/transform does not exist, hardware rotation [ 132.528973] Unable to handle kernel paging request at virtual address ebebebc0

is not supported.

-->reserver layer called (screen = 480 x 854).

-->Hardware overlay available.

Succesfully opened screen[ 132.548127] pgd = 5db4edc1

of pixel depth 32, dimensions 480 x 854, format BGRx, 12.00 MB video memory available, max 7 pannable screen buffers, vsync ena[ 132.562229] [ebebebc0] *pgd=00000000

bled.

Pipeline is PREROLLING ...

---->sunxifb pre overlay(SCWxSCN=320 x 240,out_rec=[80 307,320,240]).

Using one framebuffer [ 132.577311] Internal error: Oops: 2805 [#1] PREEMPT SMP ARM

plus 8 overlays in video memory (format YV12).

[ 132.594611] Modules linked in:

[ 132.602178] CPU: 1 PID: 2195 Comm: videotestsrc0:s Not tainted 5.4.61 #1

[ 132.609643] Hardware name: Generic DT based system

[ 132.614991] PC is at b15_dma_flush_range+0x1c/0x34

[ 132.620335] LR is at compat_cedardev_ioctl+0xc28/0xdb4

[ 132.626058] pc : [<c0114d00>] lr : [<c0593b78>] psr: 60030013

[ 132.633041] sp : c59f3ed0 ip : 00000010 fp : 0018dcd0

[ 132.638861] r10: 00000036 r9 : c59f2000 r8 : c59f2000

[ 132.644682] r7 : c5964700 r6 : 00000506 r5 : c59f2000 r4 : b5c87568

[ 132.651956] r3 : 0000003f r2 : 00000040 r1 : ebedadeb r0 : ebebebc0

[ 132.659230] Flags: nZCv IRQs on FIQs on Mode SVC_32 ISA ARM Segment none

[ 132.667181] Control: 10c5387d Table: 459ac06a DAC: 00000051

[ 132.673583] Process videotestsrc0:s (pid: 2195, stack limit = 0xd0e007f5)

[ 132.681148] Stack: (0xc59f3ed0 to 0xc59f4000)

[ 132.686002] 3ec0: ebebebeb 00000000 ebedadeb 00000000

[ 132.695121] 3ee0: b5e35000 5150fb9a c59aed78 b5c87568 c5a0c038 c5964700 00000506 c59f2000

[ 132.704237] 3f00: c59f2000 c01ed19c b5c87568 c01edf50 00000000 00000000 00000000 00000000

[ 132.713356] 3f20: b5345000 5150fb9a 00200070 c59f3fb0 00000055 b5e35000 c5a99e40 c014fe14

[ 132.722474] 3f40: c59f3fb0 00000055 b5e35000 c010f320 c5964700 00000001 00004000 c6b46100

[ 132.731591] 3f60: 00000006 5150fb9a 00000036 00000006 c5964701 c5964700 00000506 b5c87568

[ 132.740707] 3f80: c59f2000 00000036 0018dcd0 c01ee02c b689cf10 ebebebeb ebebebeb 00000036

[ 132.749824] 3fa0: c0101228 c0101000 b689cf10 ebebebeb 00000006 00000506 b5c87568 000cb910

[ 132.758943] 3fc0: b689cf10 ebebebeb ebebebeb 00000036 000cff78 0018dcd0 b68edf34 0018dcd0

[ 132.768061] 3fe0: b689cf3c b5c87564 b688aa20 b6b2a92c 20030010 00000006 00000000 00000000

[ 132.777187] [<c0114d00>] (b15_dma_flush_range) from [<c0593b78>] (compat_cedardev_ioctl+0xc28/0xdb4)

[ 132.787376] [<c0593b78>] (compat_cedardev_ioctl) from [<c01ed19c>] (vfs_ioctl+0x18/0x3c)

[ 132.796400] [<c01ed19c>] (vfs_ioctl) from [<c01edf50>] (do_vfs_ioctl+0x620/0x6c8)

[ 132.804746] [<c01edf50>] (do_vfs_ioctl) from [<c01ee02c>] (ksys_ioctl+0x34/0x5c)

[ 132.812994] [<c01ee02c>] (ksys_ioctl) from [<c0101000>] (ret_fast_syscall+0x0/0x54)

[ 132.821527] Exception stack(0xc59f3fa8 to 0xc59f3ff0)

[ 132.827157] 3fa0: b689cf10 ebebebeb 00000006 00000506 b5c87568 000cb910

[ 132.836273] 3fc0: b689cf10 ebebebeb ebebebeb 00000036 000cff78 0018dcd0 b68edf34 0018dcd0

[ 132.845388] 3fe0: b689cf3c b5c87564 b688aa20 b6b2a92c

[ 132.851019] Code: e3a02004 e1a02312 e2423001 e1c00003 (ee070f3e)

[ 132.857811] ---[ end trace 56fe497e048d5b88 ]---

内核配置文件内容(为节约空间,删除了usb部分的设置):

# CONFIG_LOCALVERSION_AUTO is not set

CONFIG_SYSVIPC=y

CONFIG_NO_HZ=y

CONFIG_HIGH_RES_TIMERS=y

CONFIG_PREEMPT=y

CONFIG_BSD_PROCESS_ACCT=y

CONFIG_BSD_PROCESS_ACCT_V3=y

CONFIG_IKCONFIG=y

CONFIG_IKCONFIG_PROC=y

CONFIG_LOG_BUF_SHIFT=16

CONFIG_CC_OPTIMIZE_FOR_SIZE=y

# CONFIG_SYSFS_SYSCALL is not set

CONFIG_KALLSYMS_ALL=y

CONFIG_EMBEDDED=y

# CONFIG_PERF_EVENTS is not set

# CONFIG_COMPAT_BRK is not set

CONFIG_PROFILING=y

CONFIG_ARCH_SUNXI=y

# CONFIG_MACH_SUN4I is not set

# CONFIG_MACH_SUN5I is not set

# CONFIG_MACH_SUN6I is not set

# CONFIG_MACH_SUN7I is not set

# CONFIG_MACH_SUN8I is not set

# CONFIG_MACH_SUN9I is not set

CONFIG_ARCH_SUN8IW20=y

CONFIG_EVB_PLATFORM=y

CONFIG_SUNXI_SOC_NAME="sun8iw20"

# CONFIG_VDSO is not set

CONFIG_SMP=y

CONFIG_SCHED_MC=y

CONFIG_NR_CPUS=2

CONFIG_ARM_PSCI=y

CONFIG_OABI_COMPAT=y

CONFIG_HIGHMEM=y

# CONFIG_ARM_MODULE_PLTS is not set

# CONFIG_ATAGS is not set

CONFIG_CMDLINE="loglevel=8 initcall_debug=1 console=ttyS0 init=/init"

CONFIG_CPU_FREQ=y

CONFIG_CPU_FREQ_STAT=y

CONFIG_CPU_FREQ_TIMES=y

CONFIG_CPU_FREQ_GOV_POWERSAVE=y

CONFIG_CPU_FREQ_GOV_USERSPACE=y

CONFIG_CPU_FREQ_GOV_ONDEMAND=y

CONFIG_CPU_FREQ_GOV_CONSERVATIVE=y

CONFIG_CPU_FREQ_GOV_SCHEDUTIL=y

CONFIG_CPUFREQ_DT=y

CONFIG_ARM_ALLWINNER_SUN50I_CPUFREQ_NVMEM=y

CONFIG_VFP=y

CONFIG_NEON=y

CONFIG_PM_WAKELOCKS=y

CONFIG_PM_DEBUG=y

CONFIG_PM_ADVANCED_DEBUG=y

CONFIG_JUMP_LABEL=y

CONFIG_MODULES=y

CONFIG_MODULE_UNLOAD=y

# CONFIG_CORE_DUMP_DEFAULT_ELF_HEADERS is not set

# CONFIG_COMPACTION is not set

CONFIG_CMA=y

CONFIG_NET=y

CONFIG_PACKET=y

CONFIG_UNIX=y

CONFIG_UNIX_DIAG=y

CONFIG_NET_KEY=y

CONFIG_INET=y

CONFIG_IP_MULTICAST=y

CONFIG_IP_ADVANCED_ROUTER=y

CONFIG_IP_FIB_TRIE_STATS=y

CONFIG_IP_MULTIPLE_TABLES=y

CONFIG_INET_IPCOMP=y

CONFIG_INET_UDP_DIAG=y

CONFIG_IPV6_TUNNEL=y

CONFIG_NETLINK_DIAG=y

CONFIG_CAN=y

CONFIG_BT=y

CONFIG_BT_RFCOMM=y

CONFIG_BT_RFCOMM_TTY=y

CONFIG_BT_HCIUART=y

CONFIG_BT_HCIUART_H4=y

CONFIG_XR_BT_LPM=y

CONFIG_CFG80211=y

CONFIG_RFKILL=y

CONFIG_RFKILL_GPIO=y

CONFIG_UEVENT_HELPER=y

CONFIG_UEVENT_HELPER_PATH="/sbin/hotplug"

CONFIG_DEVTMPFS=y

CONFIG_DEVTMPFS_MOUNT=y

CONFIG_SUNXI_MBUS=y

CONFIG_MTD=y

CONFIG_MTD_SUNXI_PARTS=y

CONFIG_MTD_CHAR=y

CONFIG_MTD_BLOCK=y

CONFIG_MTD_SPI_NAND=y

CONFIG_AW_MTD_SPINAND=y

CONFIG_MTD_SPI_NOR=y

CONFIG_MTD_UBI_BLOCK=y

CONFIG_SUNXI_RFKILL=y

CONFIG_SUNXI_ADDR_MGT=y

CONFIG_SUNXI_BOOTEVENT=y

CONFIG_SCSI=y

CONFIG_BLK_DEV_SD=y

CONFIG_NETDEVICES=y

CONFIG_SUNXI_GMAC=y

CONFIG_USB_USBNET=y

CONFIG_XR829_WLAN=m

CONFIG_INPUT_EVDEV=y

CONFIG_INPUT_SENSORINIT=y

CONFIG_KEYBOARD_SUNXI=y

# CONFIG_INPUT_MOUSE is not set

CONFIG_INPUT_TOUCHSCREEN=y

CONFIG_TOUCHSCREEN_SUNXI=y

# CONFIG_TOUCHSCREEN_GSLX680NEW is not set

CONFIG_TOUCHSCREEN_GT9XXNEW_TS=m

CONFIG_INPUT_SENSOR=y

# CONFIG_LEGACY_PTYS is not set

CONFIG_DEVKMEM=y

# CONFIG_HW_RANDOM is not set

CONFIG_SUNXI_G2D=y

CONFIG_SUNXI_G2D_MIXER=y

CONFIG_SUNXI_G2D_ROTATE=y

CONFIG_SUNXI_DI=y

CONFIG_SUNXI_DI_V1XX=y

CONFIG_SUNXI_SYS_INFO=y

CONFIG_SUNXI_SMC=y

CONFIG_I2C=y

CONFIG_I2C_CHARDEV=y

CONFIG_I2C_SUNXI=y

CONFIG_SPI=y

CONFIG_SPI_SUNXI=y

CONFIG_SPI_SPIDEV=y

CONFIG_PINCTRL_SUNXI_DEBUGFS=y

CONFIG_DEBUG_GPIO=y

CONFIG_GPIO_SYSFS=y

CONFIG_GPIO_SUNXI=y

CONFIG_POWER_SUPPLY=y

CONFIG_THERMAL=y

CONFIG_THERMAL_DEFAULT_GOV_POWER_ALLOCATOR=y

CONFIG_THERMAL_GOV_STEP_WISE=y

CONFIG_THERMAL_GOV_USER_SPACE=y

CONFIG_THERMAL_GOV_POWER_ALLOCATOR=y

CONFIG_CPU_THERMAL=y

CONFIG_THERMAL_EMULATION=y

CONFIG_SUNXI_THERMAL=y

CONFIG_WATCHDOG=y

CONFIG_SUNXI_WATCHDOG=y

CONFIG_MFD_SUN6I_PRCM=y

CONFIG_REGULATOR=y

CONFIG_REGULATOR_FIXED_VOLTAGE=y

CONFIG_SUNXI_REGULATOR_PWM=y

CONFIG_RC_CORE=y

CONFIG_RC_DECODERS=y

CONFIG_IR_NEC_DECODER=y

CONFIG_IR_RC5_DECODER=y

CONFIG_RC_DEVICES=y

CONFIG_IR_RX_SUNXI=y

CONFIG_MEDIA_SUPPORT=y

CONFIG_MEDIA_CAMERA_SUPPORT=y

CONFIG_MEDIA_CONTROLLER=y

CONFIG_VIDEO_V4L2_SUBDEV_API=y

CONFIG_MEDIA_USB_SUPPORT=y

CONFIG_USB_VIDEO_CLASS=y

CONFIG_USB_GSPCA=y

CONFIG_V4L_PLATFORM_DRIVERS=y

CONFIG_VIDEO_SUNXI_TVD=y

CONFIG_SUNXI_PLATFORM_DRIVERS=y

CONFIG_VIDEO_SUNXI_VIN=y

CONFIG_CSI_VIN=y

# CONFIG_CSI_CCI is not set

CONFIG_SENSOR_N5_DVP=y

CONFIG_FB=y

CONFIG_DISP2_SUNXI=y

CONFIG_SUNXI_DISP2_FB_HW_ROTATION_SUPPORT=y

CONFIG_DISP2_SUNXI_DEBUG=y

# CONFIG_DISP2_SUNXI_DEVICE_OFF_ON_RELEASE is not set

CONFIG_SOUND=y

CONFIG_SND=y

CONFIG_SND_SOC=y

CONFIG_SND_SUNXI_SOC_SUN8IW20_CODEC=y

CONFIG_SND_SUNXI_SOC_SIMPLE_CARD=y

CONFIG_SND_SUNXI_SOC_DAUDIO=y

CONFIG_MMC=y

CONFIG_MMC_SUNXI=y

CONFIG_NEW_LEDS=y

CONFIG_LEDS_CLASS=y

CONFIG_LEDS_GPIO=y

CONFIG_LEDS_TRIGGERS=y

CONFIG_LEDS_TRIGGER_TIMER=y

CONFIG_LEDS_TRIGGER_ONESHOT=y

CONFIG_LEDS_TRIGGER_MTD=y

CONFIG_LEDS_TRIGGER_HEARTBEAT=y

CONFIG_LEDS_TRIGGER_BACKLIGHT=y

CONFIG_LEDS_TRIGGER_CPU=y

CONFIG_LEDS_TRIGGER_ACTIVITY=y

CONFIG_LEDS_TRIGGER_GPIO=y

CONFIG_LEDS_TRIGGER_DEFAULT_ON=y

CONFIG_RTC_CLASS=y

CONFIG_RTC_DRV_DS1302=y

CONFIG_DMADEVICES=y

CONFIG_DMA_SUN6I=y

CONFIG_STAGING=y

CONFIG_ION=y

CONFIG_ION_SYSTEM_HEAP=y

CONFIG_ION_CMA_HEAP=y

CONFIG_EXFAT_FS=y

CONFIG_EXFAT_DELAYED_SYNC=y

CONFIG_EXFAT_KERNEL_DEBUG=y

CONFIG_EXFAT_DEBUG_MSG=y

# CONFIG_COMMON_CLK_DEBUG is not set

# CONFIG_CLK_SUNXI_CLOCKS is not set

# CONFIG_CLK_SUNXI_DDR is not set

# CONFIG_CLK_SUNXI_PRCM_SUN6I is not set

# CONFIG_CLK_SUNXI_PRCM_SUN8I is not set

# CONFIG_CLK_SUNXI_PRCM_SUN9I is not set

# CONFIG_ARM_ARCH_TIMER_EVTSTREAM is not set

CONFIG_SUNXI_MAILBOX=y

CONFIG_SUNXI_IOMMU=y

CONFIG_SUNXI_IOMMU_DEBUG=y

CONFIG_SUNXI_IOMMU_TESTS=y

CONFIG_REMOTEPROC=y

CONFIG_SUNXI_REMOTEPROC=y

CONFIG_SUNXI_REMOTEPROC_HIFI4_BOOT=y

CONFIG_SUNXI_REMOTEPROC_C906_BOOT=y

CONFIG_RPMSG_VIRTIO=y

CONFIG_RPMSG_CTRL=y

CONFIG_RPBUF_SERVICE_RPMSG=y

CONFIG_RPBUF_CONTROLLER_SUNXI=y

# CONFIG_SUNXI_SRAM is not set

CONFIG_SUNXI_PM_DOMAINS=y

CONFIG_SUNXI_SID=y

CONFIG_PWM=y

CONFIG_PWM_SUNXI_GROUP=y

CONFIG_ANDROID=y

CONFIG_NVMEM_SUNXI_SID=y

CONFIG_EXT4_FS=y

CONFIG_EXT4_FS_POSIX_ACL=y

CONFIG_EXT4_FS_SECURITY=y

CONFIG_EXT4_DEBUG=y

# CONFIG_DNOTIFY is not set

CONFIG_FUSE_FS=y

CONFIG_CUSE=y

CONFIG_VIRTIO_FS=y

CONFIG_OVERLAY_FS=y

CONFIG_MSDOS_FS=y

CONFIG_VFAT_FS=y

CONFIG_FAT_DEFAULT_UTF8=y

CONFIG_NTFS_FS=y

CONFIG_NTFS_RW=y

CONFIG_TMPFS=y

CONFIG_TMPFS_POSIX_ACL=y

CONFIG_UBIFS_FS=y

CONFIG_UBIFS_FS_ADVANCED_COMPR=y

# CONFIG_UBIFS_FS_ZLIB is not set

# CONFIG_UBIFS_FS_ZSTD is not set

CONFIG_SQUASHFS=y

CONFIG_SQUASHFS_XZ=y

CONFIG_NLS_CODEPAGE_437=y

CONFIG_NLS_ISO8859_1=y

CONFIG_CRYPTO_ARC4=y

CONFIG_CRYPTO_DES=y

CONFIG_CRYPTO_ZSTD=y

CONFIG_CRYPTO_USER_API_HASH=y

CONFIG_CRYPTO_USER_API_SKCIPHER=y

CONFIG_CRYPTO_USER_API_RNG=y

CONFIG_CRYPTO_USER_API_AEAD=y

CONFIG_CRYPTO_DEV_SUNXI=m

CONFIG_DMA_CMA=y

CONFIG_PRINTK_TIME=y

CONFIG_DEBUG_INFO=y

CONFIG_FRAME_WARN=2048

CONFIG_DEBUG_FS=y

CONFIG_MAGIC_SYSRQ=y

CONFIG_DEBUG_VM=y

# CONFIG_SCHED_DEBUG is not set

CONFIG_DEBUG_MUTEXES=y

CONFIG_STACKTRACE=y

# CONFIG_FTRACE is not set

CONFIG_ATOMIC64_SELFTEST=y

CONFIG_DEBUG_LL=y

CONFIG_DEBUG_UART_PHYS=0x02500c00

CONFIG_DEBUG_UART_VIRT=0xf2500c00

CONFIG_EARLY_PRINTK=y

#37 Re: 全志 SOC » 深入研究T113 EFUSE,现已扩展XFEL工具,并支持烧写T113熔丝位 » 2023-12-18 14:57:10

@xboot

楼主精通底层技术,赞一个。

上面的验签过程,有两种应用场景,需求不同,思路也会不同。

第一种,自己的产品防盗版,没有升级需求,或者loader没有升级需求,也就是某部分固件,完全不变化,且需防盗版抄袭。

这种需求,你需要将CPU ID + 固件或者loader,两者所有信息进行sha256摘要运算,并用ECDSA256对SHA256的摘要进行签名,存储在EFUSE里。当别人复制产品时,复制了SPI NOR FLASH,复制了EFUSE 签名,因CPU ID不同,也无法正常验签。第二种,自己是方案商仅出主控芯片,客户自行烧录生产,有固件及各种烧写工具。这种情况要求客户必须从你这里走芯片,而不能从市面上随便购买。

对于这种需求,仅需要对CPU ID 进行SHA256摘要运算,并用ECDSA256对SHA256的摘要进行签名,存储在EFUSE里,烧录好,出给客户就可以了。客户可以随便刷机,升级,但不能随便购买芯片。当然,固件完整性,固件防逆向,这些需求,可结合坑网之前的讨论的帖子,来实现。

最后一句话,攻防手段千千万,但几千年来,唯一不变的,还是人心,人性。

请问应用程序验签的时候使用什么库?openssl吗?还是用SOC内嵌的安全算法?

#38 Re: 全志 SOC » 发生一件很奇怪的事情,不知道问题出在哪里,大家帮忙看一下? » 2023-12-01 11:09:06

#41 Re: 好钜润半导体(TIKY) » 好钜润3.5寸屏RGB888模式,无法点亮 » 2022-11-26 11:36:42

#42 Re: 司徒开源 » 研究FC3000掌機的開源可行性 » 2022-11-26 11:05:55

#44 Re: 全志 SOC » 有偿求助F1C100S 硬件defe转yuv » 2022-11-23 14:01:16

自己整了个小项目,用软件yuv转rgb太慢了。有没有大神帮助提供下调用de-fe硬件转yuv的代码。

用的是f1c100s,主线linux 5.2

500元红包答谢:)

联系:1171262261@qq.com

楼主的硬件转RGB搞定了吗?我现在用widora tiny200 R3,采用了aodzip大佬的 buildroot一键生成生成的image可以用modetest做四层叠加,但是只能支持RGB格式的图像,如果是yuv格式的图像,则会显示成全绿色。有没有什么线索在主线drm中使用这个硬件转码功能? @晕哥 有线索吗?

#45 Re: 全志 SOC » buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *,支持SPI NAND » 2022-11-22 14:25:06

@aodzip 感谢楼主的贡献,让我们能够站在前人的肩膀上工作而不要重新造轮子。

从楼主的git库,取最新的版本,build了一个sysimage-sdcard.img,烧到sd卡,在tiny200 R3上电启动,加载rootfs时出错。

[

[ 1.776903] Kernel panic - not syncing: VFS: Unable to mount root fs on unkno wn-block(31,2)

[ 1.785238] CPU: 0 PID: 1 Comm: swapper Not tainted 5.4.99 #1

[ 1.790965] Hardware name: Allwinner suniv Family

[ 1.795734] [<c010e1c8>] (unwind_backtrace) from [<c010b964>] (show_stack+0x1 0/0x14)

[ 1.803513] [<c010b964>] (show_stack) from [<c06eea9c>] (panic+0xe8/0x2e4)

[ 1.810403] [<c06eea9c>] (panic) from [<c090135c>] (mount_block_root+0x2bc/0x 31c)

[ 1.817882] [<c090135c>] (mount_block_root) from [<c0901568>] (prepare_namesp ace+0x128/0x188)

[ 1.826412] [<c0901568>] (prepare_namespace) from [<c06f68d4>] (kernel_init+0 x8/0x108)

[ 1.834326] [<c06f68d4>] (kernel_init) from [<c01010e0>] (ret_from_fork+0x14/ 0x34)

[ 1.841873] Exception stack(0xc2839fb0 to 0xc2839ff8)

]似乎kernel使用的bootargs参数错了,这个bootargs是从spi flash上加载rootfs,而我们是从tf卡启动的,rootfs也在tf卡上。

[

Starting kernel ...

[ 0.000000] Booting Linux on physical CPU 0x0

[ 0.000000] Linux version 5.4.99 (yocto@85-159-213-31) (gcc version 8.4.0 (Buildroot -g21de572)) #1 Sun Nov 20 09:53:48 UTC 2022

[ 0.000000] CPU: ARM926EJ-S [41069265] revision 5 (ARMv5TEJ), cr=0005317f

[ 0.000000] CPU: VIVT data cache, VIVT instruction cache

[ 0.000000] OF: fdt: Machine model: Widora MangoPi R3

[ 0.000000] Memory policy: Data cache writeback

[ 0.000000] cma: Reserved 16 MiB at 0x82c00000

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 15883

[ 0.000000] Kernel command line: console=ttyS0,115200 rootwait init=/preinit root=/dev/mtdblock2 rootfstype=squashfs overlayfsdev=/dev/mtdblock3 net.ifnames=0 vt.global_cursor_default=0

[ 0.000000] Dentry cache hash table entries: 8192 (order: 3, 32768 bytes, lin ear)

[ 0.000000] Inode-cache hash table entries: 4096 (order: 2, 16384 bytes, line ar)

]我进去uboot的命令行,bootcmd变量打印出来看了,似乎uboot没有设置bootargs环境变量?那么kernel启动的bootargs从哪里来的?是kernel编译时候的缺省参数?

[

boot_device=mmc0

boot_slot_0=empty

boot_slot_1=empty

boot_targets=fel dfu mmc0 mmc1 spi loopdfu

bootcmd=setenv lcd_bl_pin 134; run distro_bootcmd;

bootcmd_dfu=if test "${boot_device}" != "mmc0" || test "${boot_slot_1}" = "empty"; then run dfu_boot; fi;

bootcmd_fel=if test "${boot_device}" = "fel"; then run fel_boot; fi;

bootcmd_loopdfu=setenv dfu_wait_timeout; run bootcmd_dfu;

bootcmd_mmc0=if test "${boot_device}" = "mmc0"; then devnum=0; run mmc_boot; fi;

bootcmd_mmc1=if test "${boot_device}" = "mmc1"; then devnum=1; run mmc_boot; fi;

bootcmd_spi=if test "${boot_device}" = "spi"; then run nor_nand_boot; fi;

bootm_size=0x1800000

dfu_boot=if test "${boot_slot_1}" = "spi-nand"; then echo "DFU waiting on SPI-NAND..."; run dfu_nand; fi; if test "${boot_slot_1}" = "spi-nor"; then echo "DFU waiting on SPI-NOR..."; run dfu_nor; fi; if test "${boot_slot_1}" = "mmc1"; then echo "DFU waiting on MMC1..."; setenv dfu_mmc_dev 1; run dfu_mmc; fi; if test "${boot_slot_1}" = "empty" && test "${boot_slot_0}" = "mmc0"; then echo "DFU waiting on MMC0..."; setenv dfu_mmc_dev 0; run dfu_mmc; fi;

dfu_mmc=mmc dev ${dfu_mmc_dev}; run mmc_dfu_info; dfu 0 mmc ${dfu_mmc_dev} ${dfu_wait_timeout};

dfu_nand=run nand_dfu_info; dfu 0 mtd spi-nand0 ${dfu_wait_timeout};

dfu_nor=run nor_dfu_info; dfu 0 sf 0:0 ${dfu_wait_timeout};

dfu_wait_timeout=3

distro_bootcmd=run scan_boot_slot; run show_splash; for target in ${boot_targets}; do run bootcmd_${target}; done

fdtcontroladdr=82e5f9b0

fel_boot=echo "Booting from FEL..."; bootm ${kernel_addr_r};

kernel_addr_r=0x81000000

mmc_boot=mmc dev ${devnum}; echo "Booting from MMC${devnum}..."; load mmc ${devnum}:${mmc_bootpart} $kernel_addr_r ${mmc_kernel}; bootm ${kernel_addr_r};

mmc_bootdev=0

mmc_bootpart=2

mmc_dfu_info=setenv dfu_alt_info "all raw 0x0 0x37000;u-boot raw 0x10 0x7f0;boot part ${dfu_mmc_dev} ${mmc_bootpart};rom part ${dfu_mmc_dev} ${mmc_rootpart};kernel fat ${dfu_mmc_dev} ${mmc_bootpart}"

mmc_kernel=kernel.itb

mmc_rootpart=3

mmc_splash=splash.bmp

mmc_ubootpart=1

nand_boot=echo "Booting from SPI-NAND..."; mtd read spi-nand0 ${kernel_addr_r} ${nand_kernel_offset} ${nand_kernel_length}; bootm ${kernel_addr_r};

nand_dfu_info=setenv dfu_alt_info "all raw 0x0 ${nand_size};u-boot raw 0x0 0x80000;kernel raw ${nand_kernel_offset} ${nand_kernel_length};rom raw 0x600000 0x2a00000;vendor raw 0x3000000 0x1000000"

nand_kernel_length=0x500000

nand_kernel_offset=0x100000

nand_size=0x8000000

nand_splash_offset=0x80000

nor_boot=echo "Booting from SPI-NOR..."; sf probe; sf read ${kernel_addr_r} ${sf_kernel_offset} ${sf_kernel_length}; bootm ${kernel_addr_r};

nor_dfu_info=setenv dfu_alt_info "all raw 0x0 ${sf_size};u-boot raw 0x0 0x80000;kernel raw ${sf_kernel_offset} ${sf_kernel_length};rom raw 0x600000 0x700000"

nor_nand_boot=if test "${boot_slot_1}" = "spi-nor"; then run nor_boot; fi; if test "${boot_slot_1}" = "spi-nand"; then run nand_boot; fi;

scan_boot_slot=run scan_boot_slot_0; run scan_boot_slot_1; echo "========================="; echo "Boot Device: ${boot_device}"; echo "Boot Slot 0: ${boot_slot_0}"; echo "Boot Slot 1: ${boot_slot_1}"; echo "=========================";

scan_boot_slot_0=if mmc dev 0; then setenv boot_slot_0 mmc0; fi;

scan_boot_slot_1=if mmc dev 1; then setenv boot_slot_1 mmc1; else if sf probe; then setenv boot_slot_1 spi-nor; else if mtd list; then setenv boot_slot_1 spi-nand; fi; fi; fi;

sf_kernel_length=0x500000

sf_kernel_offset=0x100000

sf_size=0x1000000

sf_splash_offset=0x80000

show_splash=run splash_${boot_device}; bmp display ${splash_addr}; gpio set ${lcd_bl_pin};

splash_addr=0x80000000

splash_length=0x80000

splash_mmc=load mmc ${devnum}:${mmc_bootpart} ${splash_addr} ${mmc_splash};

splash_nand=mtd read spi-nand0 ${splash_addr} ${nand_splash_offset} ${splash_length};

splash_nor=sf probe; sf read ${splash_addr} ${sf_splash_offset} ${splash_length};

splash_spi=if test "${boot_slot_1}" = "spi-nor"; then run splash_nor; fi; if test "${boot_slot_1}" = "spi-nand"; then run splash_nand; fi;

stderr=serial

stdin=serial

stdout=serial

]最后手动加了一个bootargs环境变量

[console=ttyS0,115200 rootwait init=/preinit root=/dev/mmcblk0p3 rw net.ifnames=0 vt.global_cursor_default=0]这次成功启动了

[[ 1.735975] Waiting for root device /dev/mmcblk0p3...

[ 1.764950] mmc0: host does not support reading read-only switch, assuming write-enable

[ 1.775198] mmc0: new high speed SDHC card at address 1234

[ 1.782943] mmcblk0: mmc0:1234 SA32G 29.1 GiB

[ 1.793292] mmcblk0: p1 p2 p3

[ 1.966257] EXT4-fs (mmcblk0p3): mounted filesystem with ordered data mode. Opts: (null)

[ 1.974644] VFS: Mounted root (ext4 filesystem) on device 179:3.

[ 1.982569] devtmpfs: mounted

[ 1.991513] Freeing unused kernel memory: 1024K

[ 1.996158] Run /preinit as init process

[ 2.495549] EXT4-fs (mmcblk0p3): re-mounted. Opts: (null)

Starting syslogd: OK

Starting klogd: OK

Running sysctl: OK

Populating /dev using udev: [ 3.168942] udevd[88]: starting version 3.2.9

[ 3.314178] udevd[89]: starting eudev-3.2.9

[ 5.142050] Goodix-TS 0-005d: 0-005d supply AVDD28 not found, using dummy regulator

[ 5.150141] Goodix-TS 0-005d: 0-005d supply VDDIO not found, using dummy regulator

[ 5.178156] ov2640 0-0030: Product ID error fa:fa

[ 5.363941] Goodix-TS 0-005d: i2c test failed attempt 1: -6

[ 5.408790] Goodix-TS 0-005d: i2c test failed attempt 2: -6

[ 5.448939] Goodix-TS 0-005d: I2C communication failure: -6

done

Saving random seed: OK

Starting haveged: haveged: listening socket at 3

OK

Starting system message bus: done

Starting network: OK

Starting ofono ... done.

Starting uMTPrd: [ 8.085344] file system registered

[ 8.424268] read descriptors

[ 8.427221] read strings

OK

Welcome to Widora MangoPi R3

]结论:

楼主的u-boot里面bootargs环境变量没有设置,kernel启动缺省从spi flash里面加载rootfs,如果是从tf卡启动的用户,需要增加这个环境变量,否则加载rootfs失败。

另外由于u-boot映像中没有包含saveenv命令,所以添加的bootargs变量无法保存,下次启动就又丢失了。要想解决问题,必须重新编译u-boot。

后记:

无意中发现,kernel 采用的bootargs来自dtb文件

[ chosen {

#address-cells = <1>;

#size-cells = <1>;

ranges;

bootargs = "console=ttyS0,115200 rootwait init=/preinit root=/dev/mtdblock2 rootfstype=squashfs overlayfsdev=/dev/mtdblock3";

simplefb_lcd: framebuffer-lcd0 {

compatible = "allwinner,simple-framebuffer",

"simple-framebuffer";

allwinner,pipeline = "de_be0-lcd0";

clocks = <&ccu CLK_BUS_DE_BE>, <&ccu CLK_DE_BE>,

<&ccu CLK_DRAM_DE_BE>, <&ccu CLK_BUS_LCD>,

<&ccu CLK_TCON>;

status = "disabled";

};

};]感觉有点乱。。。所以,不想修改u-boot源代码,那就修改dts文件吧。

#46 Re: 全志 SOC » 解决f1c100s 主线Linux 升级到 4.19 之后的版本没有 framebuffer(fb0)设备问题(转转转)(Linux5.2) » 2022-11-17 16:50:04

@晕哥

楼主,我用licheepi zero(V3S)。在主线5.19.3的内核中尝试初始化LCD的时候,也遇到了fb0设备不出现的问题。

按照你的方法打印了drm的初始化log

[ 0.056344] [drm:0xc070eda1] Initialized

[ 0.056506] [drm:0xc02a4577] Adding component /soc/mixer@1100000

[ 0.056609] [drm:0xc02a4577] Adding component /soc/lcd-controller@1c0c000

[ 0.056676] [drm:0xc02a43ff] Endpoint is our panel... skipping

[ 0.060684] panel-simple panel: supply power not found, using dummy regulator

[ 0.060947] panel-simple panel: Specify missing connector_type能帮着分析一下是什么原因导致的吗?还是说V3S DE设备的初始化只能在v5.2内核版本下工作?

吊诡的是,panel设备不出现,对应的backlight设备也没有出现在设备树当中。

我用的dts文件是参照licheepi zero官方的修改而来,官方的内核版本是v5.2

[ backlight: backlight {

compatible = "pwm-backlight";

pwms = <&pwm 0 1000000 0>;

brightness-levels = <0 30 40 50 60 70 100>;

default-brightness-level = <6>;

};

panel: panel {

compatible = "urt,umsh-8596md-t", "simple-panel";

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

backlight = <&backlight>;

#address-cells = <1>;

#size-cells = <0>;

panel_input: endpoint@0 {

reg = <0>;

remote-endpoint = <&tcon0_out_lcd>;

};

};

};

&de {

status = "okay";

};

&pwm {

pinctrl-names = "default";

pinctrl-0 = <&pwm0_pins>;

status = "okay";

};

&tcon0 {

pinctrl-names = "default";

pinctrl-0 = <&lcd_rgb666_pins_a>;

status = "okay";

};

&tcon0_out {

tcon0_out_lcd: endpoint@0 {

reg = <0>;

remote-endpoint = <&panel_input>;

};

};

]官方的v5.2版本,fb设备初始化成功的时候,还有下面的打印信息,我这边就没有

[

[ 1.259771] sun8i-v3s-pinctrl 1c20800.pinctrl: 1c20800.pinctrl supply vcc-pe not found, using dummy regulator

[ 1.272296] sun4i-drm display-engine: bound 1100000.mixer (ops 0xc0773d40)

[ 1.279881] sun4i-drm display-engine: bound 1c0c000.lcd-controller (ops 0xc07 7103c)

[ 1.287569] [drm] Supports vblank timestamp caching Rev 2 (21.10.2013).

[ 1.294258] [drm] No driver support for vblank timestamp query.

[ 1.301264] [drm] Initialized sun4i-drm 1.0.0 20150629 for display-engine on

]#47 Re: 好钜润半导体(TIKY) » 好钜润3.5寸屏RGB888模式,无法点亮 » 2021-10-26 10:04:24

TKM32F499GT8评估板资料集

https://whycan.com/t_5861.html18、TK499_LCD_TK035F5589_TK80_DMA例程.rar

楼主你用的是这个Demo吗? 是基于这个Demo 修改吗?

你发的这个例程是并口的,我用的是spi串口初始化的。我看了一下寄存器设置也不太一样。

#48 Re: 好钜润半导体(TIKY) » 好钜润3.5寸屏RGB888模式,无法点亮 » 2021-10-24 16:56:18

#49 Re: 好钜润半导体(TIKY) » 好钜润3.5寸屏RGB888模式,无法点亮 » 2021-10-15 19:10:54

#50 Re: 好钜润半导体(TIKY) » 好钜润3.5寸屏RGB888模式,无法点亮 » 2021-10-15 12:56:50

#51 Re: 好钜润半导体(TIKY) » 好钜润3.5寸屏RGB888模式,无法点亮 » 2021-10-14 18:04:36

#52 Re: 好钜润半导体(TIKY) » 好钜润3.5寸屏RGB888模式,无法点亮 » 2021-10-12 09:34:16

#53 Re: 好钜润半导体(TIKY) » 好钜润3.5寸屏RGB888模式,无法点亮 » 2021-10-11 16:53:25

#54 Re: 好钜润半导体(TIKY) » 好钜润3.5寸屏RGB888模式,无法点亮 » 2021-10-11 13:30:58

@memory

这是我们的初始化代码,可以看到读device id都是成功的,就是代码中的byte1和byte2。感觉spi口时序已经对了。

{

unsigned char byte1,byte2;

/* Initialize the pins */

if (r61408_enable_gpio(cfg) != 0)

return ;

gpio_set_value(cfg->csx_pin, 1);

mdelay(20);

gpio_set_value(cfg->csx_pin, 0);

gpio_set_value(cfg->reset_pin, 0);

mdelay(200);

gpio_set_value(cfg->reset_pin, 1);

mdelay(200);

#if 1

// Enter read mode

SPI_WriteComm(0xB0);

SPI_WriteData(0x04);

SPI_WriteComm(0xBF);

SPI_ReadData();

printf("DDB0=%x, DDB1=%x\n", SPI_ReadData(), SPI_ReadData());

byte1 = SPI_ReadData();

byte2 = SPI_ReadData();

// Enter read mode

SPI_WriteComm(0xB0);

SPI_WriteData(0x04);

if (byte1==0x15 && byte2==0x29) {

printf("R61259 found!\n");

r61529_Reg_Fill();

}

gpio_set_value(cfg->csx_pin, 1);

#else

#endif

}static void r61529_Reg_Fill(void)

{

SPI_WriteComm(0xB4);

SPI_WriteData(0x00);

SPI_WriteComm(0xB0);

SPI_WriteData(0x04);

SPI_WriteComm(0x20);

SPI_WriteComm(0x36); //Set_address_mode

SPI_WriteData(0x6A); //

SPI_WriteComm(0x3A);

SPI_WriteData(0x77);

SPI_WriteComm(0xB3);

SPI_WriteData(0x02);

SPI_WriteData(0x00);

SPI_WriteData(0x00);

SPI_WriteData(0x20);

SPI_WriteComm(0xc0);

SPI_WriteData(0x03);

SPI_WriteData(0xdf);

SPI_WriteData(0x40);

SPI_WriteData(0x12);

SPI_WriteData(0x00);

SPI_WriteData(0x01);

SPI_WriteData(0x00);

SPI_WriteData(0x55);//

SPI_WriteComm(0xc1);

SPI_WriteData(0x07);

SPI_WriteData(0x28);

SPI_WriteData(0x08);//

SPI_WriteData(0x08);//

SPI_WriteData(0x00);//

SPI_WriteComm(0xc4);

SPI_WriteData(0x70);//

SPI_WriteData(0x00);

SPI_WriteData(0x03);

SPI_WriteData(0x01);

SPI_WriteComm(0xc6);

SPI_WriteData(0x1d);//1d

SPI_WriteComm(0xc8);

SPI_WriteData(0x06);

SPI_WriteData(0x0c);

SPI_WriteData(0x16);

SPI_WriteData(0x24);

SPI_WriteData(0x30);

SPI_WriteData(0x48);

SPI_WriteData(0x3d);

SPI_WriteData(0x28);

SPI_WriteData(0x20);

SPI_WriteData(0x14);

SPI_WriteData(0x0c);

SPI_WriteData(0x04);

SPI_WriteData(0x06);

SPI_WriteData(0x0C);

SPI_WriteData(0x16);

SPI_WriteData(0x24);

SPI_WriteData(0x30);

SPI_WriteData(0x48);

SPI_WriteData(0x3D);

SPI_WriteData(0x28);

SPI_WriteData(0x20);

SPI_WriteData(0x14);

SPI_WriteData(0x0C);

SPI_WriteData(0x04);

SPI_WriteComm(0xC9);

SPI_WriteData(0x06);

SPI_WriteData(0x0C);

SPI_WriteData(0x16);

SPI_WriteData(0x24);

SPI_WriteData(0x30);

SPI_WriteData(0x48);

SPI_WriteData(0x3D);

SPI_WriteData(0x28);

SPI_WriteData(0x20);

SPI_WriteData(0x14);

SPI_WriteData(0x0C);

SPI_WriteData(0x04);

SPI_WriteData(0x06);

SPI_WriteData(0x0C);

SPI_WriteData(0x16);

SPI_WriteData(0x24);

SPI_WriteData(0x30);

SPI_WriteData(0x48);

SPI_WriteData(0x3D);

SPI_WriteData(0x28);

SPI_WriteData(0x20);

SPI_WriteData(0x14);

SPI_WriteData(0x0C);

SPI_WriteData(0x04);

SPI_WriteComm(0xCA);

SPI_WriteData(0x06);

SPI_WriteData(0x0C);

SPI_WriteData(0x16);

SPI_WriteData(0x24);

SPI_WriteData(0x30);

SPI_WriteData(0x48);

SPI_WriteData(0x3D);

SPI_WriteData(0x28);

SPI_WriteData(0x20);

SPI_WriteData(0x14);

SPI_WriteData(0x0C);

SPI_WriteData(0x04);

SPI_WriteData(0x06);

SPI_WriteData(0x0C);

SPI_WriteData(0x16);

SPI_WriteData(0x24);

SPI_WriteData(0x30);

SPI_WriteData(0x48);

SPI_WriteData(0x3D);

SPI_WriteData(0x28);

SPI_WriteData(0x20);

SPI_WriteData(0x14);

SPI_WriteData(0x0C);

SPI_WriteData(0x04);

SPI_WriteComm(0xD0);

SPI_WriteData(0x95);

SPI_WriteData(0x0A);

SPI_WriteData(0x08);

SPI_WriteData(0x10);

SPI_WriteData(0x39);

SPI_WriteComm(0xD1);

SPI_WriteData(0x02);

SPI_WriteData(0x2c);//

SPI_WriteData(0x2c);//

SPI_WriteData(0x44);//

SPI_WriteData(0x00);//0x08

SPI_WriteComm(0x11);

mdelay(100);

SPI_WriteComm(0x29);

mdelay(100);

SPI_WriteComm(0x2C);

SPI_WriteComm(0x36);

#if LCD_RGB_ORIENTATION //

SPI_WriteData(0x09);

#else

SPI_WriteData(0x08);

#endif

}#55 Re: 好钜润半导体(TIKY) » 好钜润3.5寸屏RGB888模式,无法点亮 » 2021-10-11 13:23:08

@memory

我们的初始化代码,RGB时序都是根据卖家提供的一大堆资料连蒙带猜出来的。上逻辑分析仪当然可以,但是最好卖家能确认一下我们当前的设置是不是对的。

感觉卖家的态度就是,一切都由买家自己决定。。。

下面是卖家提供的初始化代码。比如第一条指令0xB4和第二条指令0xB0,按照瑞萨R61529的手册,必须先执行0xB0指令打开寄存器保护,否则任何寄存器访问都是无效的。也就是说第一条指令0xB4是一个无效访问。

void Lcd_Initialize(void) //LCD初始化函数

{

LCD_SPI_CS(1);

LCD_delay(20);

LCD_SPI_CS(0);

LCD_Reset();

SPI_WriteComm(0xB4);

SPI_WriteData(0x00);

SPI_WriteComm(0xB0);

SPI_WriteData(0x04);

SPI_WriteComm(0x20);

SPI_WriteComm(0x36); //Set_address_mode

SPI_WriteData(0x6A); //横屏

SPI_WriteComm(0x3A);

SPI_WriteData(0x77);

SPI_WriteComm(0xB3);

SPI_WriteData(0x02);

SPI_WriteData(0x00);

SPI_WriteData(0x00);

SPI_WriteData(0x20);

SPI_WriteComm(0xc0);

SPI_WriteData(0x03);

SPI_WriteData(0xdf);

SPI_WriteData(0x40);

SPI_WriteData(0x12);

SPI_WriteData(0x00);

SPI_WriteData(0x01);

SPI_WriteData(0x00);

SPI_WriteData(0x55);//

SPI_WriteComm(0xc1);

SPI_WriteData(0x07);

SPI_WriteData(0x28);

SPI_WriteData(0x08);//

SPI_WriteData(0x08);//

SPI_WriteData(0x00);//

SPI_WriteComm(0xc4);

SPI_WriteData(0x70);//

SPI_WriteData(0x00);

SPI_WriteData(0x03);

SPI_WriteData(0x01);

SPI_WriteComm(0xc6);

SPI_WriteData(0x1d);//1d

SPI_WriteComm(0xc8);

SPI_WriteData(0x06);

SPI_WriteData(0x0c);

SPI_WriteData(0x16);

SPI_WriteData(0x24);

SPI_WriteData(0x30);

SPI_WriteData(0x48);

SPI_WriteData(0x3d);

SPI_WriteData(0x28);

SPI_WriteData(0x20);

SPI_WriteData(0x14);

SPI_WriteData(0x0c);

SPI_WriteData(0x04);

SPI_WriteData(0x06);

SPI_WriteData(0x0C);

SPI_WriteData(0x16);

SPI_WriteData(0x24);

SPI_WriteData(0x30);

SPI_WriteData(0x48);

SPI_WriteData(0x3D);

SPI_WriteData(0x28);

SPI_WriteData(0x20);

SPI_WriteData(0x14);

SPI_WriteData(0x0C);

SPI_WriteData(0x04);

SPI_WriteComm(0xC9);

SPI_WriteData(0x06);

SPI_WriteData(0x0C);

SPI_WriteData(0x16);

SPI_WriteData(0x24);

SPI_WriteData(0x30);

SPI_WriteData(0x48);

SPI_WriteData(0x3D);

SPI_WriteData(0x28);

SPI_WriteData(0x20);

SPI_WriteData(0x14);

SPI_WriteData(0x0C);

SPI_WriteData(0x04);

SPI_WriteData(0x06);

SPI_WriteData(0x0C);

SPI_WriteData(0x16);

SPI_WriteData(0x24);

SPI_WriteData(0x30);

SPI_WriteData(0x48);

SPI_WriteData(0x3D);

SPI_WriteData(0x28);

SPI_WriteData(0x20);

SPI_WriteData(0x14);

SPI_WriteData(0x0C);

SPI_WriteData(0x04);

SPI_WriteComm(0xCA);

SPI_WriteData(0x06);

SPI_WriteData(0x0C);

SPI_WriteData(0x16);

SPI_WriteData(0x24);

SPI_WriteData(0x30);

SPI_WriteData(0x48);

SPI_WriteData(0x3D);

SPI_WriteData(0x28);

SPI_WriteData(0x20);

SPI_WriteData(0x14);

SPI_WriteData(0x0C);

SPI_WriteData(0x04);

SPI_WriteData(0x06);

SPI_WriteData(0x0C);

SPI_WriteData(0x16);

SPI_WriteData(0x24);

SPI_WriteData(0x30);

SPI_WriteData(0x48);

SPI_WriteData(0x3D);

SPI_WriteData(0x28);

SPI_WriteData(0x20);

SPI_WriteData(0x14);

SPI_WriteData(0x0C);

SPI_WriteData(0x04);

SPI_WriteComm(0xD0);

SPI_WriteData(0x95);

SPI_WriteData(0x0A);

SPI_WriteData(0x08);

SPI_WriteData(0x10);

SPI_WriteData(0x39);

SPI_WriteComm(0xD1);

SPI_WriteData(0x02);

SPI_WriteData(0x2c);//

SPI_WriteData(0x2c);//

SPI_WriteData(0x44);//

SPI_WriteData(0x00);//0x08

SPI_WriteComm(0x11);

LCD_delay(100);

SPI_WriteComm(0x29);

LCD_delay(100);

SPI_WriteComm(0x2C);

SPI_WriteComm(0x36);

#if LCD_RGB_ORIENTATION //是否旋转90度

SPI_WriteData(0x09);

#else

SPI_WriteData(0x08);

#endif

}#56 Re: 好钜润半导体(TIKY) » 好钜润3.5寸屏RGB888模式,无法点亮 » 2021-10-11 13:00:30

#57 Re: 好钜润半导体(TIKY) » 好钜润3.5寸屏RGB888模式,无法点亮 » 2021-10-11 12:54:10

#58 Re: 好钜润半导体(TIKY) » 好钜润3.5寸屏RGB888模式,无法点亮 » 2021-10-10 10:35:43

页次: 1

- 首页

- » 搜索

- » wuyu 发表的帖子

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发

![IMG_20211014_162231[1].jpg](https://whycan.com/files/members/7454/IMG_20211014_162231[1].jpg)