楼主 #1 2018-09-03 10:46:29 分享评论

楼主 #2 2018-09-03 10:47:23 分享评论

楼主 #3 2018-09-03 10:48:43 分享评论

#4 2018-09-03 11:09:10 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,140

- 积分: 1092.5

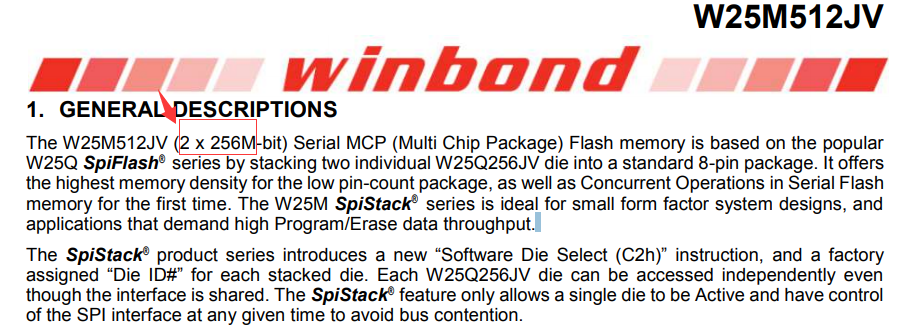

Re: 买两片 W25M512JVFIQ 测试一下

多少钱?

离线

楼主 #5 2018-09-03 11:16:50 分享评论

楼主 #6 2018-09-03 11:17:23 分享评论

楼主 #7 2018-09-03 11:18:33 分享评论

楼主 #8 2018-09-03 11:19:27 分享评论

楼主 #9 2018-09-03 11:21:16 分享评论

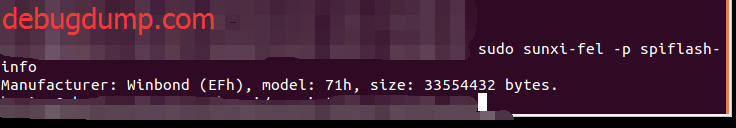

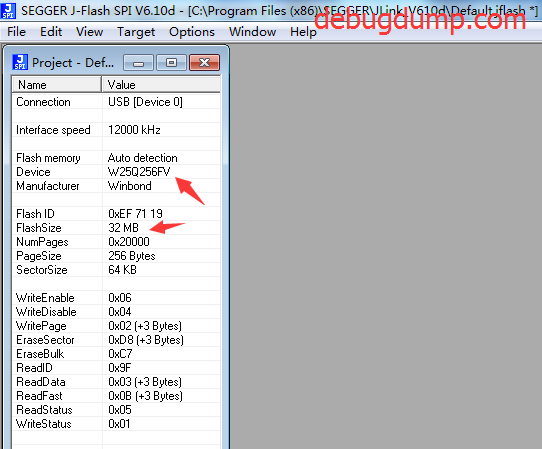

楼主 #10 2018-09-03 16:37:00 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,445

- 积分: 9202

Re: 买两片 W25M512JVFIQ 测试一下

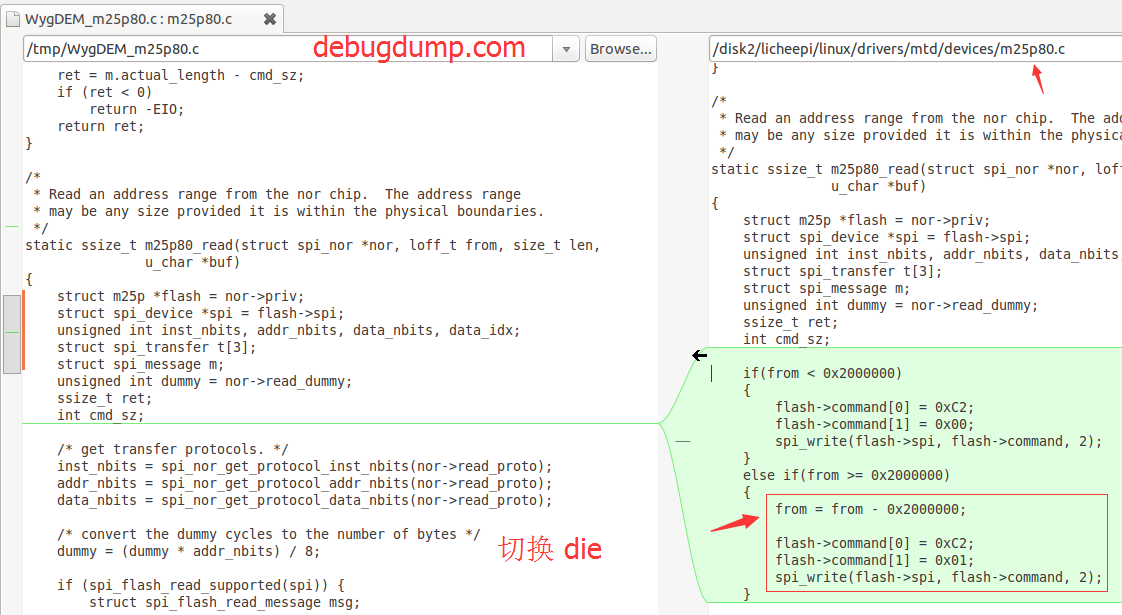

V3s u-boot 修改

licheepi/u-boot/drivers/mtd/spi/spi_flash_ids.c

添加一行:

{"w25m512jv", INFO(0xef7119, 0x0, 64 * 1024, 1024, RD_FULL | WR_QPP | SECT_4K) },

linux

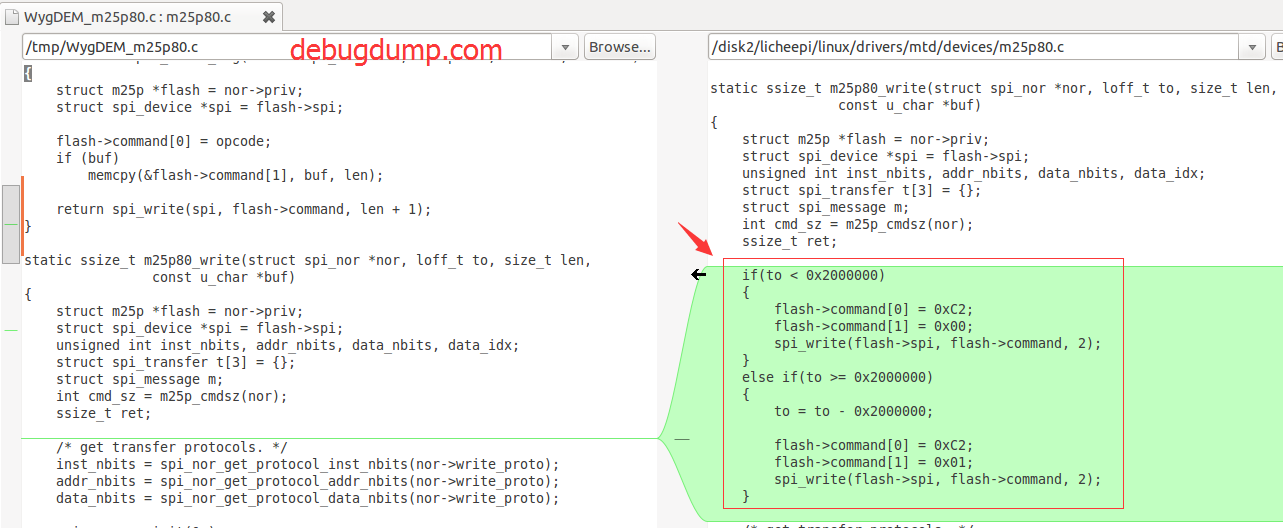

licheepi/linux/drivers/mtd/devices/m25p80.c

添加

{"w25q80bl"}, {"w25q128"}, {"w25q256"}, {"w25m512jv"},

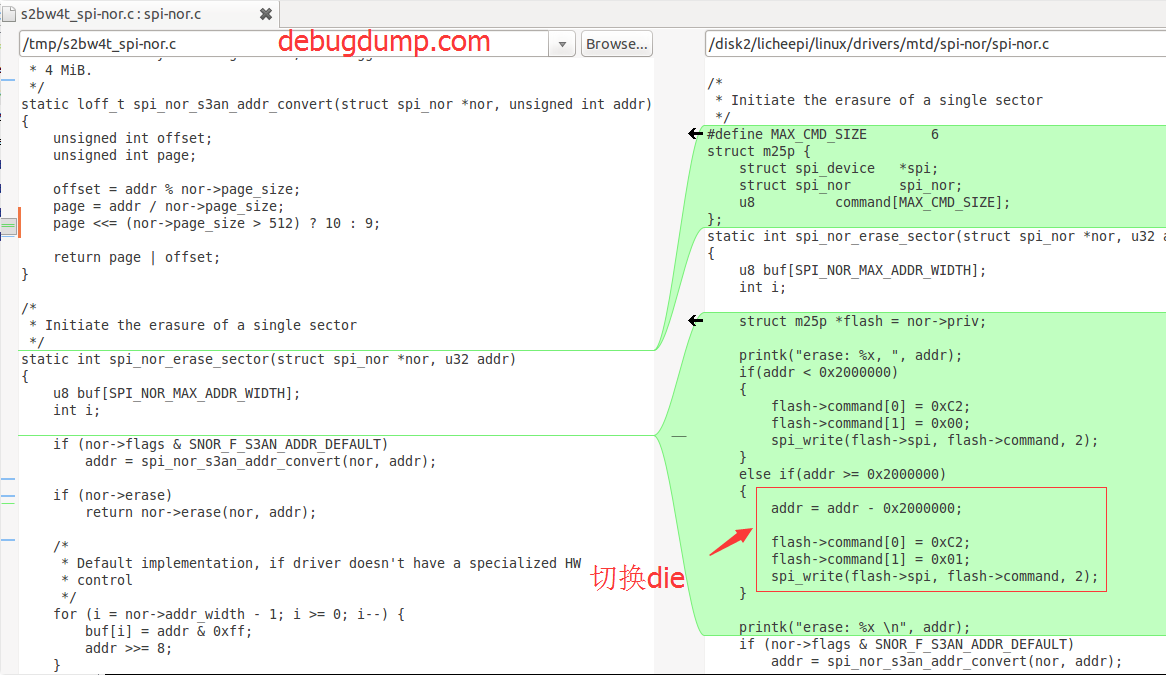

licheepi/linux/drivers/mtd/spi-nor/spi-nor.c

{ "w25m512jv", INFO(0xef7119, 0, 64 * 1024, 1024, SPI_NOR_QUAD_READ | SPI_NOR_DUAL_READ) },

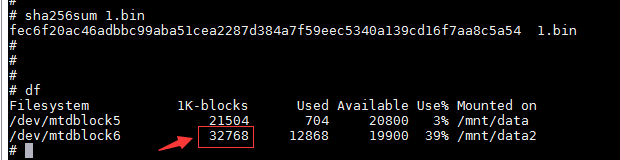

改完之后重新编译烧录, 发现u-boot, Linux都可以启动,w25q256驱动不正常了:

[ 0.624277] m25p80 spi32766.0: unrecognized JEDEC id bytes: 00, 00, 00

[ 0.624352] m25p80: probe of spi32766.0 failed with error -2

离线

楼主 #11 2018-09-03 16:38:42 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,445

- 积分: 9202

Re: 买两片 W25M512JVFIQ 测试一下

经过 @assert 大神指点, 把 spi 时钟频率从 50Mhz 调整到 16Mhz,

识别flash正常了.

licheepi/linux/arch/arm/boot/dts/sun8i-v3s-sya.dts

&spi0 {

status ="okay";mx25l25635e:mx25l25635e@0 {

compatible = "jedec,spi-nor";

reg = <0x0>;

spi-max-frequency = <16000000>;

#address-cells = <1>;

#size-cells = <1>;

};};

离线

楼主 #12 2018-09-03 18:36:36 分享评论

楼主 #13 2018-09-03 18:39:00 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,445

- 积分: 9202

Re: 买两片 W25M512JVFIQ 测试一下

找到一个 linux 下的 W25M512 的补丁

From c7025568f83800de384c457557169e44740dc8f7 Mon Sep 17 00:00:00 2001

From: "Anton D. Kachalov" <mouse@yandex-team.ru>

Date: Tue, 24 May 2016 19:36:35 +0300

Subject: [PATCH 06/14] Add various MTD SPI chips

Signed-off-by: Anton D. Kachalov <mouse@yandex-team.ru>

---

drivers/mtd/spichips/Kconfig | 94 ++++

drivers/mtd/spichips/Makefile | 18 +

drivers/mtd/spichips/astspi.c | 367 +++++++++++++

drivers/mtd/spichips/atmel.c | 133 +++++

drivers/mtd/spichips/default.c | 106 ++++

drivers/mtd/spichips/generic.c | 1052 ++++++++++++++++++++++++++++++++++++++

drivers/mtd/spichips/intels33.c | 96 ++++

drivers/mtd/spichips/m25pxx.c | 121 +++++

drivers/mtd/spichips/macronix.c | 208 ++++++++

drivers/mtd/spichips/micron.c | 104 ++++

drivers/mtd/spichips/spansion.c | 103 ++++

drivers/mtd/spichips/spiaccess.c | 433 ++++++++++++++++

drivers/mtd/spichips/spiflash.h | 178 +++++++

drivers/mtd/spichips/spimtd.c | 241 +++++++++

drivers/mtd/spichips/spireg.c | 180 +++++++

drivers/mtd/spichips/winbond.c | 98 ++++

16 files changed, 3532 insertions(+)

create mode 100644 drivers/mtd/spichips/Kconfig

create mode 100644 drivers/mtd/spichips/Makefile

create mode 100644 drivers/mtd/spichips/astspi.c

create mode 100644 drivers/mtd/spichips/atmel.c

create mode 100644 drivers/mtd/spichips/default.c

create mode 100644 drivers/mtd/spichips/generic.c

create mode 100644 drivers/mtd/spichips/intels33.c

create mode 100644 drivers/mtd/spichips/m25pxx.c

create mode 100644 drivers/mtd/spichips/macronix.c

create mode 100644 drivers/mtd/spichips/micron.c

create mode 100644 drivers/mtd/spichips/spansion.c

create mode 100644 drivers/mtd/spichips/spiaccess.c

create mode 100644 drivers/mtd/spichips/spiflash.h

create mode 100644 drivers/mtd/spichips/spimtd.c

create mode 100644 drivers/mtd/spichips/spireg.c

create mode 100644 drivers/mtd/spichips/winbond.c

diff --git a/drivers/mtd/spichips/Kconfig b/drivers/mtd/spichips/Kconfig

new file mode 100644

index 0000000..c5e5a4c

--- /dev/null

+++ b/drivers/mtd/spichips/Kconfig

@@ -0,0 +1,94 @@

+# drivers/mtd/chips/Kconfig

+# $Id: Kconfig,v 1.18 2005/11/07 11:14:22 gleixner Exp $

+

+menu "SPI Flash chip drivers"

+ depends on MTD!=n

+

+config MTD_SPI

+ bool "Enable MTD support on SPI devices"

+ depends on MTD

+ help

+ Select this if you want to access SPI flash devices via MTD

+

+config MTD_SPI_SPANSION

+ bool "Spansion SPI devices Support"

+ depends on MTD_SPI

+ help

+ Select this if you want to use Spansion SPI devices

+

+config MTD_SPI_MACRONIX

+ bool "Macronix SPI devices Support"

+ depends on MTD_SPI

+ help

+ Select this if you want to use Macronix SPI devices

+

+config MTD_SPI_INTEL_S33

+ bool "Intel S33 SPI devices Support"

+ depends on MTD_SPI

+ help

+ Select this if you want to use Intel S33 SPI devices

+

+config MTD_SPI_WINBOND

+ bool "Winbond SPI devices Support"

+ depends on MTD_SPI

+ help

+ Select this if you want to use Winbond SPI devices

+

+config MTD_SPI_AT

+ bool "Atmel SPI devices Support"

+ depends on MTD_SPI

+ help

+ Select this if you want to use Atmel SPI devices

+

+config MTD_SPI_ST

+ bool "ST Micro SPI devices Support"

+ depends on MTD_SPI

+ help

+ Select this if you want to use ST Microelectronics SPI devices

+

+config MTD_SPI_NUMONYX

+ bool "Numonyx SPI devices Support"

+ depends on MTD_SPI

+ help

+ Select this if you want to use Numonyx SPI devices

+

+config MTD_SPI_MICRON

+ bool "Numonyx SPI devices Support"

+ depends on MTD_SPI

+ help

+ Select this if you want to use Micron SPI devices

+

+config MTD_SPI_DEFAULT

+ bool "Support for SPI Devices not supporting ReadID"

+ depends on MTD_SPI

+ help

+ Select this if the SPI device on your board does not SPI ReadID Command

+

+config DEFAULT_SPI_NAME

+ string "Default SPI Name"

+ depends on MTD_SPI && MTD_SPI_DEFAULT

+ default "default"

+ help

+ Name of the SPI Device that does not support ReadID

+

+config DEFAULT_SPI_SIZE

+ int "Default SPI Size in Bytes"

+ depends on MTD_SPI && MTD_SPI_DEFAULT

+ default "65536"

+ help

+ Chip Size of the SPI Device that does not support ReadID

+

+config DEFAULT_SPI_ERASE_SIZE

+ int "Default SPI Erase Block Size in Bytes"

+ depends on MTD_SPI && MTD_SPI_DEFAULT

+ default "65536"

+ help

+ Erase Block Size of the SPI Device that does not support ReadID

+

+config MTD_AST_SPI

+ bool "AST SOC SPI Flash Controller"

+ depends on MTD_SPI

+ help

+ If you are using SPI device on AST SOC, select Y

+

+endmenu

diff --git a/drivers/mtd/spichips/Makefile b/drivers/mtd/spichips/Makefile

new file mode 100644

index 0000000..b30a452

--- /dev/null

+++ b/drivers/mtd/spichips/Makefile

@@ -0,0 +1,18 @@

+#

+# linux/drivers/spichips/Makefile

+#

+obj-$(CONFIG_MTD_SPI) += spimtd.o spiaccess.o spireg.o generic.o

+

+obj-$(CONFIG_MTD_SPI_ST) += m25pxx.o

+obj-$(CONFIG_MTD_SPI_SPANSION) += spansion.o

+obj-$(CONFIG_MTD_SPI_MACRONIX) += macronix.o

+obj-$(CONFIG_MTD_SPI_AT) += atmel.o

+obj-$(CONFIG_MTD_SPI_INTEL_S33) += intels33.o

+obj-$(CONFIG_MTD_SPI_WINBOND) += winbond.o

+obj-$(CONFIG_MTD_SPI_MICRON) += micron.o

+obj-$(CONFIG_MTD_SPI_NUMONYX) += micron.o

+

+# The default driver should be the last in the list of suppported devices

+obj-$(CONFIG_MTD_SPI_DEFAULT) += default.o

+

+obj-$(CONFIG_MTD_AST_SPI) += astspi.o

diff --git a/drivers/mtd/spichips/astspi.c b/drivers/mtd/spichips/astspi.c

new file mode 100644

index 0000000..a0dc9d4

--- /dev/null

+++ b/drivers/mtd/spichips/astspi.c

@@ -0,0 +1,367 @@

+/*

+ * (C) Copyright 2009

+ * American Megatrends Inc.

+ *

+ * SPI flash controller driver for the AST SoC

+ *

+ * See file CREDITS for list of people who contributed to this

+ * project.

+ *

+ * This program is free software; you can redistribute it and/or

+ * modify it under the terms of the GNU General Public License as

+ * published by the Free Software Foundation; either version 2 of

+ * the License, or (at your option) any later version.

+ *

+ * This program is distributed in the hope that it will be useful,

+ * but WITHOUT ANY WARRANTY; without even the implied warranty of

+ * MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

+ * GNU General Public License for more details.

+ *

+ * You should have received a copy of the GNU General Public License

+ * along with this program; if not, write to the Free Software

+ * Foundation, Inc., 59 Temple Place, Suite 330, Boston,

+ * MA 02111-1307 USA

+ */

+

+#include "spiflash.h"

+

+#define AST_FMC_REG_BASE AST_FMC_VA_BASE /* 0x1E620000 */

+#define AST_FMC_FLASH_CTRL_REG 0x00

+

+#define AST_FMC_CE0_CTRL_REG 0x10

+#define AST_FMC_CTRL_REG_SIZE 0x04

+

+#define AST_SPI_CMD_MASK 0x00FF0000 /* bit[23:16] */

+#define AST_SPI_CMD_SHIFT 16

+

+#define AST_SPI_CLOCK_MASK 0x00000F00 /* bit[11:8] */

+#define AST_SPI_CLOCK_SHIFT 8

+

+#define AST_SPI_DUMMY_MASK 0x000000C0 /* bit[7:6] */

+#define AST_SPI_DUMMY_0 0x00000000

+#define AST_SPI_DUMMY_1 0x00000040

+#define AST_SPI_DUMMY_2 0x00000080

+#define AST_SPI_DUMMY_3 0x000000C0

+

+#define AST_SPI_DATA_SINGLE 0x00000000

+#define AST_SPI_DATA_DUAL 0x00000008

+#define AST_SPI_DUAL_IO 0x00000002

+#define AST_SPI_FULL_DUAL_IO 0x00000003

+#define AST_SPI_DATA_MASK 7

+#define AST_SPI_DUAL_IO_SHIFT 28

+

+#define AST_SPI_CE_LOW 0x00000000

+#define AST_SPI_CE_HI 0x00000004

+

+#define AST_SPI_CMD_MODE_MASK 0x00000007 /* bit[2:0] */

+#define AST_SPI_CMD_MODE_NORMAL 0x00000000

+#define AST_SPI_CMD_MODE_FAST 0x00000001

+#define AST_SPI_CMD_MODE_WRITE 0x00000002

+#define AST_SPI_CMD_MODE_USER 0x00000003

+

+#define SPI_FAST_READ_CMD 0x0B

+#define SPI_DREAD_CMD 0x3B

+#define SPI_2READ_CMD 0xBB

+

+extern unsigned long ractrends_spiflash_flash_size[MAX_SPI_BANKS];

+static int *g_fast_read = 0;

+

+static void reset_flash(int bank)

+{

+ uint32_t reg;

+ uint32_t ctrl_reg;

+

+ // bank = 0,CE0 (0x10) ; bank = 1,CE1 (0x14) ; bank = 2,CE2 (0x18)

+ ctrl_reg = AST_FMC_CE0_CTRL_REG + (bank * AST_FMC_CTRL_REG_SIZE);

+

+ reg = ioread32((void __iomem *)AST_FMC_REG_BASE + ctrl_reg);

+ if (*g_fast_read == 3)//2xI/O Read

+ {

+ reg &= ~(AST_SPI_CMD_MASK | AST_SPI_DUMMY_MASK | AST_SPI_CMD_MODE_MASK);

+ reg |= (SPI_2READ_CMD << AST_SPI_CMD_SHIFT) | AST_SPI_DUMMY_1 | AST_SPI_CE_LOW | AST_SPI_CMD_MODE_FAST | (AST_SPI_FULL_DUAL_IO << AST_SPI_DUAL_IO_SHIFT);

+ }

+ else if (*g_fast_read == 2)//Dual Read

+ {

+ reg &= ~(AST_SPI_CMD_MASK | AST_SPI_DUMMY_MASK | AST_SPI_CMD_MODE_MASK);

+ reg |= (SPI_DREAD_CMD << AST_SPI_CMD_SHIFT) | AST_SPI_DUMMY_1 | AST_SPI_CE_LOW | AST_SPI_CMD_MODE_FAST | (AST_SPI_DUAL_IO << AST_SPI_DUAL_IO_SHIFT);

+ }

+ else if (*g_fast_read == 1)//Fast Read

+ {

+ reg &= ~(AST_SPI_CMD_MASK | AST_SPI_DUMMY_MASK | AST_SPI_CMD_MODE_MASK);

+ reg |= (SPI_FAST_READ_CMD << AST_SPI_CMD_SHIFT) | AST_SPI_DUMMY_1 | AST_SPI_CE_LOW | AST_SPI_CMD_MODE_FAST;

+ }

+ else

+ {

+ reg &= (~AST_SPI_CMD_MODE_MASK);

+ reg |= (AST_SPI_CE_LOW | AST_SPI_CMD_MODE_NORMAL);

+ }

+ iowrite32(reg, (void __iomem *)AST_FMC_REG_BASE + ctrl_reg);

+

+}

+

+static void reset_iomode (int bank)

+{

+ uint32_t reg;

+ uint32_t ctrl_reg;

+

+ // bank = 0,CE0 (0x10) ; bank = 1,CE1 (0x14) ; bank = 2,CE2 (0x18)

+ ctrl_reg = AST_FMC_CE0_CTRL_REG + (bank * AST_FMC_CTRL_REG_SIZE);

+

+ reg = ioread32((void __iomem *)AST_FMC_REG_BASE + ctrl_reg);

+ reg &= ~(AST_SPI_CMD_MASK | AST_SPI_DUMMY_MASK | (AST_SPI_DATA_MASK << AST_SPI_DUAL_IO_SHIFT));

+

+ if (*g_fast_read == 2)//Dual Read

+ reg |= (AST_SPI_DUAL_IO << AST_SPI_DUAL_IO_SHIFT);

+ else if (*g_fast_read == 3)//2xI/O Read

+ reg |= (AST_SPI_FULL_DUAL_IO << AST_SPI_DUAL_IO_SHIFT);

+

+ iowrite32(reg, (void __iomem *)AST_FMC_REG_BASE + ctrl_reg);

+

+ return;

+}

+

+static void chip_select_active(int bank)

+{

+ uint32_t reg;

+ uint32_t ctrl_reg;

+

+ // bank = 0,CE0 (0x10) ; bank = 1,CE1 (0x14) ; bank = 2,CE2 (0x18)

+ ctrl_reg = AST_FMC_CE0_CTRL_REG + (bank * AST_FMC_CTRL_REG_SIZE);

+

+ reg = ioread32((void __iomem *)AST_FMC_REG_BASE + ctrl_reg);

+ reg &= (~(AST_SPI_CMD_MODE_MASK | (AST_SPI_DATA_MASK << AST_SPI_DUAL_IO_SHIFT)) );

+ reg |= (AST_SPI_CE_LOW | AST_SPI_CMD_MODE_USER);

+ iowrite32(reg, (void __iomem *)AST_FMC_REG_BASE + ctrl_reg);

+}

+

+static void chip_select_deactive(int bank)

+{

+ uint32_t reg;

+ uint32_t ctrl_reg;

+

+ // bank = 0,CE0 (0x10) ; bank = 1,CE1 (0x14) ; bank = 2,CE2 (0x18)

+ ctrl_reg = AST_FMC_CE0_CTRL_REG + (bank * AST_FMC_CTRL_REG_SIZE);

+

+ reg = ioread32((void __iomem *)AST_FMC_REG_BASE + ctrl_reg);

+ reg &= (~(AST_SPI_CMD_MODE_MASK | (AST_SPI_DATA_MASK << AST_SPI_DUAL_IO_SHIFT)) );

+ reg |= (AST_SPI_CE_HI | AST_SPI_CMD_MODE_USER);

+ iowrite32(reg, (void __iomem *)AST_FMC_REG_BASE + ctrl_reg);

+}

+

+static int astspiflash_transfer(int bank, unsigned char *cmd, int cmdlen, SPI_DIR dir, unsigned char *data, unsigned long datalen)

+{

+ ulong base;

+ int i;

+ ulong offset = 0;

+

+ for(i = 0; i < bank; i++)

+ {

+ offset += ractrends_spiflash_flash_size[i];

+ }

+

+ base = AST_SPI_FLASH_VA_BASE + offset;

+

+ chip_select_active(bank);

+

+ if (cmd[0] == 0xBB)

+ {

+ *((volatile unsigned char *) base) = cmd[0];

+ reset_iomode(bank);

+ for (i = 1; i < cmdlen; i ++)

+ *((volatile unsigned char *) base) = cmd[i];

+ }

+ else if (cmd[0] == 0x3B)

+ {

+ for (i = 0; i < cmdlen; i ++)

+ *((volatile unsigned char *) base) = cmd[i];

+ reset_iomode(bank);

+ }

+ else

+ {

+ /* issue command */

+ for (i = 0; i < cmdlen; i ++)

+ *((volatile unsigned char *) base) = cmd[i];

+ }

+

+ if (dir == SPI_WRITE) {

+ /* write data to flash */

+ for (i = 0; i < datalen; i ++) {

+ *((volatile unsigned char *) base) = data[i];

+ }

+ } else if (dir == SPI_READ) {

+ /* read data from flash */

+ for (i = 0; i < datalen; i ++) {

+ data[i] = ((volatile unsigned char *) base)[i];

+ }

+ }

+

+ chip_select_deactive(bank);

+

+

+ reset_flash(bank);

+ return 0;

+}

+

+static const unsigned char clock_selection_table[] = {

+ 0x0F, /* 1 */

+ 0x07, /* 2 */

+ 0x0E, /* 3 */

+ 0x06, /* 4 */

+ 0x0D, /* 5 */

+ 0x05, /* 6 */

+ 0x0C, /* 7 */

+ 0x04, /* 8 */

+ 0x0B, /* 9 */

+ 0x03, /* 10 */

+ 0x0A, /* 11 */

+ 0x02, /* 12 */

+ 0x09, /* 13 */

+ 0x01, /* 14 */

+ 0x08, /* 15 */

+ 0x00, /* 16 */

+};

+

+static int astspiflash_configure_clock(int bank, unsigned int clock)

+{

+ uint32_t reg;

+ uint32_t cpu_clock;

+ uint32_t clock_divisor;

+ uint32_t ctrl_reg;

+#if defined(CONFIG_SOC_AST2500) || defined(CONFIG_SOC_AST2530)

+ uint32_t cpu_ratio;

+ uint32_t axi_ratio;

+#endif

+ // bank = 0,CE0 (0x10) ; bank = 1,CE1 (0x14) ; bank = 2,CE2 (0x18)

+ ctrl_reg = AST_FMC_CE0_CTRL_REG + (bank * AST_FMC_CTRL_REG_SIZE);

+

+ /* according to AST spec, clock of SPI controller can not exceed 50M Hz */

+ if (clock > (50 * 1000000))

+ clock = 50 * 1000000;

+

+ /* read CPU clock rate and CPU/AHB ratio from SCU */

+ reg = ioread32((void __iomem *)SCU_HW_STRAPPING_REG);

+

+ #if defined(CONFIG_SOC_AST2500) || defined(CONFIG_SOC_AST2530)

+ cpu_ratio = 2;

+

+ switch ((reg & 0x00000E00) >> 9) {

+ case 0x01:

+ axi_ratio = 2;

+ break;

+ case 0x02:

+ axi_ratio = 3;

+ break;

+ case 0x03:

+ axi_ratio = 4;

+ break;

+ case 0x04:

+ axi_ratio = 5;

+ break;

+ case 0x05:

+ axi_ratio = 6;

+ break;

+ case 0x06:

+ axi_ratio = 7;

+ break;

+ case 0x07:

+ axi_ratio = 8;

+ break;

+ default:

+ axi_ratio = 2;

+ break;

+ }

+

+ cpu_clock = 792 * 1000000;//Default H-PLL value

+ cpu_clock = cpu_clock / cpu_ratio / axi_ratio;

+ #else

+ switch ((reg & 0x00000300) >> 8) {

+ case 0x00:

+ cpu_clock = 384 * 1000000;

+ break;

+ case 0x01:

+ cpu_clock = 360 * 1000000;

+ break;

+ case 0x02:

+ cpu_clock = 336 * 1000000;

+ break;

+ case 0x03:

+ cpu_clock = 408 * 1000000;

+ break;

+ default:

+ cpu_clock = 408 * 1000000;

+ }

+

+ switch ((reg & 0x00000C00) >> 10) {

+ case 0x01:

+ cpu_clock /= 2;

+ break;

+ case 0x02:

+ cpu_clock /= 4;

+ break;

+ case 0x03:

+ cpu_clock /= 3;

+ break;

+ }

+ #endif

+

+ clock_divisor = 1;

+ while ((cpu_clock / clock_divisor) > clock) {

+ clock_divisor ++;

+ if (clock_divisor == 16)

+ break;

+ }

+

+ reg = ioread32((void __iomem *)AST_FMC_REG_BASE + ctrl_reg);

+ reg &= ~AST_SPI_CLOCK_MASK;

+ reg |= (clock_selection_table[clock_divisor - 1] << AST_SPI_CLOCK_SHIFT);

+ iowrite32(reg, (void __iomem *)AST_FMC_REG_BASE + ctrl_reg);

+

+ return 0;

+}

+

+struct spi_ctrl_driver astspi_driver = {

+ .name = "astspiflash",

+ .module = THIS_MODULE,

+ .max_read = (64 * 1024 * 1024), /* 32 MB */

+ #ifdef CONFIG_FLASH_OPERATION_MODE_MASK

+ .operation_mode_mask = CONFIG_FLASH_OPERATION_MODE_MASK,

+ #else

+ .operation_mode_mask = 0x00010003, //Default

+ #endif

+ .fast_read = 1,

+ .fast_write = 0,

+ .spi_transfer = astspiflash_transfer,

+ .spi_burst_read = astspiflash_transfer,

+ .spi_configure_clock = astspiflash_configure_clock,

+};

+

+static int astspi_init(void)

+{

+ sema_init(&astspi_driver.lock, 1);

+ register_spi_ctrl_driver(&astspi_driver);

+

+ g_fast_read = &astspi_driver.fast_read;

+

+ reset_flash(0); // CE0

+

+ reset_flash(1); // CE1

+

+ reset_flash(2); // CE2

+ #if !defined(CONFIG_SOC_AST2500) && !defined(CONFIG_SOC_AST2530)

+ reset_flash(3); // CE3

+ #endif

+

+ return 0;

+}

+

+static void astspi_exit(void)

+{

+ unregister_spi_ctrl_driver(&astspi_driver);

+}

+

+module_init(astspi_init);

+module_exit(astspi_exit);

+

+MODULE_LICENSE("GPL");

+MODULE_AUTHOR("American Megatrends Inc");

+MODULE_DESCRIPTION("AST SOC SPI flash controller driver");

diff --git a/drivers/mtd/spichips/atmel.c b/drivers/mtd/spichips/atmel.c

new file mode 100644

index 0000000..a7cfddb

--- /dev/null

+++ b/drivers/mtd/spichips/atmel.c

@@ -0,0 +1,133 @@

+/*

+ * Copyright (C) 2007 American Megatrends Inc

+ *

+ * This program is free software; you can redistribute it and/or modify

+ * it under the terms of the GNU General Public License as published by

+ * the Free Software Foundation; either version 2 of the License, or

+ * (at your option) any later version.

+ *

+ * This program is distributed in the hope that it will be useful,

+ * but WITHOUT ANY WARRANTY; without even the implied warranty of

+ * MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

+ * GNU General Public License for more details.

+ *

+ * You should have received a copy of the GNU General Public License

+ * along with this program; if not, write to the Free Software

+ * Foundation, Inc., 675 Mass Ave, Cambridge, MA 02139, USA.

+ */

+

+#ifdef __UBOOT__

+#include <common.h>

+#endif

+#include "spiflash.h"

+#ifdef CFG_FLASH_SPI_DRIVER

+

+/* Name, ID1, ID2 , Size, Clock, Erase regions, address mode,{ Offset, Erase Size, Erase Block Count } */

+/* address mode: 0x00 -3 byte address

+ 0x01 - 4 byte address

+ 0x02 - Low byte: 3 byte address, High byte: 4 byte address*/

+static struct spi_flash_info atmel_data [] =

+{

+ /* Atmel 26F 64K Sectors */

+ { "Atmel at26f004" , 0x1F, 0x0004, 0x00010001, 0x100000 , 25 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 8 },} },

+

+ /* Atmel 25DF 64K Sectors */

+ { "Atmel at25df041a" , 0x1F, 0x0144, 0x00010001, 0x100000 , 70 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 8 },} },

+

+ /* Atmel 26DF 64K Sectors */

+ { "Atmel at26df081a" , 0x1F, 0x0145, 0x00010001, 0x100000 , 70 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 16 },} },

+ { "Atmel at26df161a" , 0x1F, 0x0146, 0x00010001, 0x200000 , 25 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 32 },} },

+ { "Atmel at26df161" , 0x1F, 0x0046, 0x00010001, 0x200000 , 25 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 32 },} },

+ { "Atmel at26df321" , 0x1F, 0x0047, 0x00010001, 0x400000 , 25 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 64 },} },

+ { "Atmel at25df321" , 0x1F, 0x0147, 0x00010001, 0x400000 , 85 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 64 },} },

+};

+

+

+static

+int

+atmel_probe(int bank,struct spi_ctrl_driver *ctrl_drv, struct spi_flash_info *chip_info)

+{

+ int retval;

+ unsigned char status;

+

+ retval = spi_generic_probe(bank, ctrl_drv,chip_info,"atmel",atmel_data,ARRAY_SIZE(atmel_data));

+ if (retval == -1)

+ return retval;

+

+ if (spi_generic_read_status(bank,ctrl_drv,&status) < 0)

+ {

+ printk("atmel: Read SR Failed.Cannot Unprotect all sectors\n");

+ return retval;

+ }

+

+ /* If SRPL = 1 (Bit 7)and WP/ = 0 (Bit 4), then it is hardware locked */

+ if ((status & 0x80) && (!(status & 0x10)))

+ {

+ printk("atmel: Hardware Locked\n");

+ return retval;

+ }

+

+ /* Check if already unprotected */

+ if ((status & 0xC) == 0)

+ return retval;

+

+ /* if SRPL is set, we have to disable SRPL before unprotect */

+ if (status & 0x80)

+ {

+ if (spi_generic_write_status(bank,ctrl_drv,status& 0x7F) < 0)

+ {

+ printk("atmel: Clearing SRPL failed .Cannot Unprotect all sectors\n");

+ return retval;

+ }

+ }

+

+ /* Unprotect all sectors */

+ if (spi_generic_write_status(bank,ctrl_drv,0x0) < 0)

+ printk("atmel: Unable to Unprotect all sectors\n");

+

+

+ return retval;

+}

+

+struct spi_chip_driver atmel_driver =

+{

+ .name = "atmel",

+ .module = THIS_MODULE,

+ .probe = atmel_probe,

+ .erase_sector = spi_generic_erase,

+ .read_bytes = spi_generic_read,

+ .write_bytes = spi_generic_write,

+ /* Atmel supports individual protect and unprotect of sectors */

+ /* if needed implement the functions and add here */

+};

+

+int

+atmel_init(void)

+{

+ sema_init(&atmel_driver.lock, 1);

+#ifdef __UBOOT__ /* MIPS */

+ atmel_driver.probe = atmel_probe;

+ atmel_driver.erase_sector = spi_generic_erase;

+ atmel_driver.read_bytes = spi_generic_read;

+ atmel_driver.write_bytes = spi_generic_write;

+#endif

+ register_spi_chip_driver(&atmel_driver);

+ return 0;

+}

+

+void

+atmel_exit(void)

+{

+ sema_init(&atmel_driver.lock, 1);

+ unregister_spi_chip_driver(&atmel_driver);

+ return;

+}

+

+module_init(atmel_init);

+module_exit(atmel_exit);

+

+MODULE_LICENSE("GPL");

+MODULE_AUTHOR("American Megatrends Inc");

+MODULE_DESCRIPTION("MTD SPI driver for Atmel flash chips");

+

+#endif

diff --git a/drivers/mtd/spichips/default.c b/drivers/mtd/spichips/default.c

new file mode 100644

index 0000000..93f31d7

--- /dev/null

+++ b/drivers/mtd/spichips/default.c

@@ -0,0 +1,106 @@

+/*

+ * Copyright (C) 2007 American Megatrends Inc

+ *

+ * This program is free software; you can redistribute it and/or modify

+ * it under the terms of the GNU General Public License as published by

+ * the Free Software Foundation; either version 2 of the License, or

+ * (at your option) any later version.

+ *

+ * This program is distributed in the hope that it will be useful,

+ * but WITHOUT ANY WARRANTY; without even the implied warranty of

+ * MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

+ * GNU General Public License for more details.

+ *

+ * You should have received a copy of the GNU General Public License

+ * along with this program; if not, write to the Free Software

+ * Foundation, Inc., 675 Mass Ave, Cambridge, MA 02139, USA.

+ */

+

+

+#ifdef __UBOOT__

+#include <common.h>

+#endif

+#include "spiflash.h"

+#ifdef CFG_FLASH_SPI_DRIVER

+

+#ifndef CONFIG_DEFAULT_SPI_NAME

+#define CONFIG_DEFAULT_SPI_NAME "Unknown SPI Device"

+#endif

+

+#ifndef CONFIG_DEFAULT_SPI_SIZE

+#define CONFIG_DEFAULT_SPI_SIZE 0

+#endif

+

+#ifndef CONFIG_DEFAULT_SPI_CLOCK

+#define CONFIG_DEFAULT_SPI_CLOCK (25 * 1000000)

+#endif

+

+#ifndef CONFIG_DEFAULT_SPI_ERASE_SIZE

+#define CONFIG_DEFAULT_SPI_ERASE_SIZE (64 *1024)

+#endif

+

+

+/* This driver is called at end when all probe failed. Some chips don't support read id

+ commands and user can provide the information here */

+

+/* Name, ID1, ID2 , Size, Clock, Erase regions, address mode,{ Offset, Erase Size, Erase Block Count } */

+/* address mode: 0x00 -3 byte address

+ 0x01 - 4 byte address

+ 0x02 - Low byte: 3 byte address, High byte: 4 byte address*/

+static struct spi_flash_info default_data [] =

+{

+ { CONFIG_DEFAULT_SPI_NAME , 0xFF, 0x0FFFF, 0x00010001, CONFIG_DEFAULT_SPI_SIZE , CONFIG_DEFAULT_SPI_CLOCK, 1, 0x00,

+ {{ 0, CONFIG_DEFAULT_SPI_ERASE_SIZE, CONFIG_DEFAULT_SPI_SIZE/CONFIG_DEFAULT_SPI_ERASE_SIZE },} },

+};

+

+static

+int

+default_probe(int bank,struct spi_ctrl_driver *ctrl_drv, struct spi_flash_info *chip_info)

+{

+ memcpy(chip_info,&default_data[0],sizeof(struct spi_flash_info));

+

+ if (spi_generic_write_status(bank,ctrl_drv,0x0) < 0)

+ printk("%s: Unable to Unprotect all sectors\n",CONFIG_DEFAULT_SPI_NAME);

+ return 0;

+}

+

+struct spi_chip_driver default_driver =

+{

+ .name = "default",

+ .module = THIS_MODULE,

+ .probe = default_probe,

+ .erase_sector = spi_generic_erase,

+ .read_bytes = spi_generic_read,

+ .write_bytes = spi_generic_write,

+};

+

+int

+default_init(void)

+{

+ sema_init(&default_driver.lock, 1);

+#ifdef __UBOOT__ /* MIPS */

+ default_driver.probe = default_probe;

+ default_driver.erase_sector = spi_generic_erase;

+ default_driver.read_bytes = spi_generic_read;

+ default_driver.write_bytes = spi_generic_write;

+#endif

+ register_spi_chip_driver(&default_driver);

+ return 0;

+}

+

+void

+default_exit(void)

+{

+ sema_init(&default_driver.lock, 1);

+ unregister_spi_chip_driver(&default_driver);

+ return;

+}

+

+module_init(default_init);

+module_exit(default_exit);

+

+MODULE_LICENSE("GPL");

+MODULE_AUTHOR("American Megatrends Inc");

+MODULE_DESCRIPTION("MTD SPI driver for Default flash chips");

+

+#endif

diff --git a/drivers/mtd/spichips/generic.c b/drivers/mtd/spichips/generic.c

new file mode 100644

index 0000000..50a70f6

--- /dev/null

+++ b/drivers/mtd/spichips/generic.c

@@ -0,0 +1,1052 @@

+/*

+ * Copyright (C) 2007-2013 American Megatrends Inc

+ *

+ * This program is free software; you can redistribute it and/or modify

+ * it under the terms of the GNU General Public License as published by

+ * the Free Software Foundation; either version 2 of the License, or

+ * (at your option) any later version.

+ *

+ * This program is distributed in the hope that it will be useful,

+ * but WITHOUT ANY WARRANTY; without even the implied warranty of

+ * MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

+ * GNU General Public License for more details.

+ *

+ * You should have received a copy of the GNU General Public License

+ * along with this program; if not, write to the Free Software

+ * Foundation, Inc., 675 Mass Ave, Cambridge, MA 02139, USA.

+ */

+

+

+#ifdef __UBOOT__

+#include <common.h>

+#endif

+#include "spiflash.h"

+#ifdef CFG_FLASH_SPI_DRIVER

+

+/* Flash opcodes. */

+#define OPCODE_WREN 0x06 /* Write enable */

+#define OPCODE_WRDI 0x04 /* Write disable*/

+#define OPCODE_RDID 0x9F /* Read JEDEC ID */

+#define OPCODE_RDSR 0x05 /* Read status register */

+#define OPCODE_WRSR 0x01 /* Write status register */

+#define OPCODE_READ 0x03 /* Read data bytes */

+#define OPCODE_FAST_READ 0x0B /* Read Fast read */

+#define OPCODE_DREAD 0x3B /* Dual Read Mode */

+#define OPCODE_2READ 0xBB /* 2 x I/O Read Mode */

+#define OPCODE_PP 0x02 /* Page program */

+#define OPCODE_SE 0xD8 /* Sector erase */

+#define OPCODE_DP 0xB9 /* Deep Power Down */

+#define OPCODE_RES 0xAB /* Read Electronic Signature */

+

+/* Status Register bits. */

+#define SR_WIP 0x01 /* Write in progress */

+#define SR_WEL 0x02 /* Write enable latch */

+#define SR_BP0 0x04 /* Block protect 0 */

+#define SR_BP1 0x08 /* Block protect 1 */

+#define SR_BP2 0x10 /* Block protect 2 */

+#define SR_SRWD 0x80 /* SR write protect */

+

+#define PROGRAM_PAGE_SIZE 256 /* Max Program Size */

+

+#define ADDR_16MB 0x1000000

+#define CMD_MX25XX_EN4B 0xb7 /* Enter 4-byte address mode */

+#define CMD_MX25XX_EX4B 0xe9 /* Exit 4-byte address mode */

+

+

+#define ADDRESS_3BYTE 0x00

+#define ADDRESS_4BYTE 0x01

+#define ADDRESS_LO3_HI4_BYTE 0x02

+

+#define ADDRESS_DIE_LO3_HI4_BYTE 0x06

+#define ADDR_32MB 0x2000000

+#define CMD_WX25XX_CS 0xc2 /* Die select */

+

+extern unsigned long ractrends_spiflash_flash_id[MAX_SPI_BANKS];

+

+static int wait_till_ready(int bank,struct spi_ctrl_driver *ctrl_drv);

+

+static

+int inline

+spi_error(int retval)

+{

+ printk("SPI Chip %s (%d) : Error (%d)\n",__FILE__,__LINE__,retval);

+ return retval;

+}

+

+static int

+spi_generic_read_flag_status(int bank, struct spi_ctrl_driver *ctrl_drv,unsigned char *status)

+{

+ int retval;

+ u8 code = 0x70;

+

+ /* Issue Controller Transfer Routine */

+ retval = ctrl_drv->spi_transfer(bank,&code, 1,SPI_READ,status, 1);

+

+ if (retval < 0)

+ return spi_error(retval);

+

+ return 0;

+}

+

+

+

+int

+spi_generic_read_status(int bank, struct spi_ctrl_driver *ctrl_drv,unsigned char *status)

+{

+ int retval;

+ u8 code = OPCODE_RDSR;

+

+ /* Issue Controller Transfer Routine */

+ retval = ctrl_drv->spi_transfer(bank,&code, 1,SPI_READ,status, 1);

+

+ if (retval < 0)

+ return spi_error(retval);

+

+ return 0;

+}

+

+int

+spi_generic_write_status(int bank,struct spi_ctrl_driver *ctrl_drv, unsigned char status)

+{

+ int retval;

+ u8 code = OPCODE_WRSR;

+

+ /* Send write enable */

+ spi_generic_write_enable(bank,ctrl_drv);

+

+ /* Issue Controller Transfer Routine */

+ retval = ctrl_drv->spi_transfer(bank,&code, 1,SPI_WRITE,&status, 1);

+ if (retval < 0)

+ return spi_error(retval);

+

+ return 0;

+}

+

+

+int

+spi_generic_write_enable(int bank,struct spi_ctrl_driver *ctrl_drv)

+{

+ u8 code = OPCODE_WREN;

+ int retval;

+

+ /* Issue Controller Transfer Routine */

+ retval = ctrl_drv->spi_transfer(bank,&code, 1,SPI_NONE, NULL, 0);

+ if (retval < 0)

+ return spi_error(retval);

+ return 0;

+}

+

+int

+spi_generic_write_disable(int bank, struct spi_ctrl_driver *ctrl_drv)

+{

+ u8 code = OPCODE_WRDI;

+ int retval;

+

+ /* Issue Controller Transfer Routine */

+ retval = ctrl_drv->spi_transfer(bank,&code, 1,SPI_NONE, NULL, 0);

+ if (retval < 0)

+ return spi_error(retval);

+ return 0;

+}

+

+int spi_generic_select_die(int bank, u8 die_num, struct spi_ctrl_driver *ctrl_drv)

+{

+ int retval;

+ u8 command[2];

+

+ command[0] = CMD_WX25XX_CS;

+ command[1] = die_num;

+

+ /* Wait until finished previous command. */

+ if (wait_till_ready(bank,ctrl_drv))

+ {

+ return -1;

+ }

+

+ retval = ctrl_drv->spi_transfer(bank, command, 2, SPI_NONE, NULL, 0);

+

+ if (retval < 0)

+ {

+ printk ("Could not select die.\n");

+ return spi_error(retval);

+ }

+ return 0;

+}

+

+int enter_4byte_addr_mode(int bank, struct spi_ctrl_driver *ctrl_drv)

+{

+ //enable 32 MB Address mode

+ u8 code = CMD_MX25XX_EN4B;

+ int retval;

+

+ //printf("<ENTER> 4 BYTE\n");

+ /* Wait until finished previous command. */

+ if (wait_till_ready(bank,ctrl_drv))

+ {

+ return -1;

+ }

+

+

+ /* Issue Controller Transfer Routine */

+ if ((ractrends_spiflash_flash_id[bank] == 0x002019BA) || (ractrends_spiflash_flash_id[bank] == 0x002020BA) || (ractrends_spiflash_flash_id[bank] == 0x002021BA))

+ spi_generic_write_enable(bank,ctrl_drv);

+ retval = ctrl_drv->spi_transfer(bank, &code, 1, SPI_NONE, NULL, 0);

+ if ((ractrends_spiflash_flash_id[bank] == 0x002019BA) || (ractrends_spiflash_flash_id[bank] == 0x002021BA))

+ spi_generic_write_disable(bank,ctrl_drv);

+ if (retval < 0)

+ {

+ printk ("Could not Enter into 4-byte address mode\n");

+ return spi_error(retval);

+ }

+ return 0;

+}

+

+int exit_4byte_addr_mode(int bank, struct spi_ctrl_driver *ctrl_drv)

+{

+ //Disable 32 MB Address mode

+ u8 code = CMD_MX25XX_EX4B;

+ int retval;

+

+ //printf("<EXIT> 4 BYTE\n");

+ /* Wait until finished previous command. */

+ if (wait_till_ready(bank,ctrl_drv))

+ {

+ return -1;

+ }

+

+

+ /* Issue Controller Transfer Routine */

+ if ((ractrends_spiflash_flash_id[bank] == 0x002019BA) || (ractrends_spiflash_flash_id[bank] == 0x002020BA) || (ractrends_spiflash_flash_id[bank] == 0x002021BA))

+ spi_generic_write_enable(bank,ctrl_drv);

+ retval = ctrl_drv->spi_transfer(bank, &code, 1, SPI_NONE, NULL, 0);

+ if ((ractrends_spiflash_flash_id[bank] == 0x002019BA) || (ractrends_spiflash_flash_id[bank] == 0x002020BA) || (ractrends_spiflash_flash_id[bank] == 0x002021BA))

+ spi_generic_write_disable(bank,ctrl_drv);

+ if (retval < 0)

+ {

+ printk ("Could not Exit from 4-byte address mode\n");

+ return spi_error(retval);

+ }

+ return 0;

+}

+

+int spi_generic_extended_address(int bank, SPI_DIR dir, u8 addr, struct spi_ctrl_driver *ctrl_drv)

+{

+ int retval;

+

+ if (dir == SPI_READ)

+ {

+ u8 code = 0xC8;

+ u8 reg_data;

+

+ ctrl_drv->spi_transfer(bank, &code, 1, SPI_READ, ®_data, 1);

+ retval = (int) reg_data;

+ }

+ else if (dir == SPI_WRITE)

+ {

+ u8 command[2];

+

+ command[0] = 0xC5;

+ command[1] = addr;

+ spi_generic_write_enable(bank, ctrl_drv);

+ ctrl_drv->spi_transfer(bank, command, 2, SPI_NONE, NULL, 0);

+ spi_generic_write_disable(bank, ctrl_drv);

+ retval = command[1];

+ }

+ else // SPI_NONE

+ {

+ retval = 0;

+ }

+

+ return retval;

+}

+

+// the function just for WINBOND W25Q256 only, always revise the extended address to the defalut

+int w25q256_force_extended_address(int bank, struct spi_ctrl_driver *ctrl_drv)

+{

+ int retval;

+ u8 code;

+ u8 reg_data;

+ u8 command[5];

+

+ code = 0xC8; // "Read Extended Address Register"

+ retval = ctrl_drv->spi_transfer(bank, &code, 1, SPI_READ, ®_data, 1);

+ if (reg_data == 0x01)

+ {

+ spi_generic_write_enable(bank,ctrl_drv);

+ command[0] = 0xC5; // "Write Extended Address Register" with the force address 0x00

+ command[1] = command[2] = command[3] = command[4] = 0x00;

+ retval = ctrl_drv->spi_transfer(bank, command, 5, SPI_NONE, NULL, 0);

+ spi_generic_write_disable(bank,ctrl_drv);

+ }

+ return 0;

+}

+

+/* Define max times to check status register before we give up. */

+#define MAX_READY_WAIT_COUNT 4000000

+

+static int

+wait_till_ready(int bank,struct spi_ctrl_driver *ctrl_drv)

+{

+ unsigned long count;

+ unsigned char sr;

+

+ for (count = 0; count < MAX_READY_WAIT_COUNT; count++)

+ {

+ if (spi_generic_read_status(bank,ctrl_drv,&sr) < 0)

+ {

+ printk("Error reading SPI Status Register\n");

+ break;

+ }

+ else

+ {

+ if (!(sr & SR_WIP))

+ return 0;

+ }

+ }

+

+ printk("spi_generic: Waiting for Ready Failed\n");

+ return 1;

+}

+

+static int

+require_read_flag_status(int bank,struct spi_ctrl_driver *ctrl_drv)

+{

+ unsigned long count;

+ unsigned char sr;

+

+ for (count = 0; count < MAX_READY_WAIT_COUNT; count++)

+ {

+ if (spi_generic_read_flag_status(bank,ctrl_drv,&sr) < 0)

+ {

+ printk("Error reading SPI Status Register\n");

+ break;

+ }

+ else

+ {

+ if (sr & SR_SRWD)

+ return 0;

+ }

+ }

+

+ printk("spi_generic %s() : Waiting for Ready Failed\n", __func__);

+ return 1;

+}

+

+

+

+int

+spi_generic_erase(struct map_info *map, unsigned long sect_addr)

+{

+ struct spi_flash_private *priv=map->fldrv_priv;

+ int bank = map->map_priv_1;

+ struct spi_ctrl_driver *ctrl_drv = priv->ctrl_drv;

+ int retval;

+ unsigned char command[5];

+ int cmd_size;

+ u8 address32 = priv->address32;

+ //unsigned long flash_size = priv->size;

+ u8 had_switch_die = 0;

+ u8 pwr_up_mode = 0;

+

+ down(&priv->chip_drv->lock);

+

+

+ /* Wait until finished previous command. */

+ if (wait_till_ready(bank,ctrl_drv))

+ {

+ up(&priv->chip_drv->lock);

+ return -1;

+ }

+

+ if (address32 == ADDRESS_DIE_LO3_HI4_BYTE) {

+ if(sect_addr>=ADDR_32MB){

+ spi_generic_select_die( bank, 1,ctrl_drv);

+ had_switch_die = 1;

+ sect_addr-=ADDR_32MB;

+ }

+ }

+

+ if (ractrends_spiflash_flash_id[bank] == 0x00EF1940)

+ {

+ u8 reg_data;

+

+ command[0] = 0x15; /* Read Status Register S23 ~ S16 */

+ cmd_size = 1;

+ retval = ctrl_drv->spi_transfer(bank,command, cmd_size ,SPI_READ, ®_data, 1);

+ pwr_up_mode = (reg_data & 0x2)>>1; /* S17(ADP) field */

+ }

+

+ /* Logic for 4 byte address mode Enter */

+ if ( ((sect_addr >= ADDR_16MB) && ((address32 == ADDRESS_LO3_HI4_BYTE )||(address32 == ADDRESS_DIE_LO3_HI4_BYTE))) || pwr_up_mode)

+ {

+ retval = enter_4byte_addr_mode(bank, ctrl_drv);

+ if (retval < 0)

+ {

+ printk ("Unable to enter 4 byte address mode\n");

+ if(had_switch_die == 1)

+ {

+ spi_generic_select_die( bank, 0,ctrl_drv);

+ }

+ up(&priv->chip_drv->lock);

+ return spi_error(retval);

+ }

+ }

+

+ if (ractrends_spiflash_flash_id[bank] == 0x00EF1940) w25q256_force_extended_address(bank, ctrl_drv);

+ if ((ractrends_spiflash_flash_id[bank] == 0x002020BA) || (ractrends_spiflash_flash_id[bank] == 0x002021BA) || (ractrends_spiflash_flash_id[bank] == 0x00C21A20))

+ spi_generic_extended_address(bank, SPI_WRITE, (sect_addr & 0xFF000000) >> 24, ctrl_drv);

+

+ if ( (((sect_addr >= ADDR_16MB) && ((address32 == ADDRESS_LO3_HI4_BYTE)||(address32 == ADDRESS_DIE_LO3_HI4_BYTE))) || (address32 == ADDRESS_4BYTE)) || pwr_up_mode)

+ {

+ /* Set up command buffer. */

+ command[0] = OPCODE_SE;

+ if (ractrends_spiflash_flash_id[bank] == 0x00011902) command[0] = 0xDC; // ERASE command in 4byte mode [spansion only]

+ if (address32 == ADDRESS_DIE_LO3_HI4_BYTE) command[0] = 0xDC; // ERASE command in 4byte mode

+ command[1] = sect_addr >> 24;

+ command[2] = sect_addr >> 16;

+ command[3] = sect_addr >> 8;

+ command[4] = sect_addr;

+

+ cmd_size = 5;

+ }

+ else {

+ /* Set up command buffer. */

+ command[0] = OPCODE_SE;

+ command[1] = sect_addr >> 16;

+ command[2] = sect_addr >> 8;

+ command[3] = sect_addr;

+

+ cmd_size = 4;

+ }

+

+ /* Issue Controller Transfer Routine */

+ spi_generic_write_enable(bank,ctrl_drv); /* Send write enable */

+ retval = ctrl_drv->spi_transfer(bank,command, cmd_size ,SPI_NONE, NULL, 0);

+ spi_generic_write_disable(bank,ctrl_drv); /* Send write disable */

+

+ if (ractrends_spiflash_flash_id[bank] == 0x002020BA || ractrends_spiflash_flash_id[bank] == 0x002021BA)

+ {

+ /* requires the read flag status with at latest one byte. */

+ if (require_read_flag_status(bank,ctrl_drv))

+ {

+ up(&priv->chip_drv->lock);

+ return -1;

+ }

+ }

+

+ if (retval < 0)

+ {

+ //if 4 byte mode exit

+ if ( ((sect_addr >= ADDR_16MB) && ((address32 == ADDRESS_LO3_HI4_BYTE)||(address32 == ADDRESS_DIE_LO3_HI4_BYTE))) || pwr_up_mode)

+ {

+ retval = exit_4byte_addr_mode(bank, ctrl_drv);

+ if (retval < 0)

+ {

+ printk ("Unable to exit 4 byte address mode\n");

+ }

+ }

+

+ if (ractrends_spiflash_flash_id[bank] == 0x00EF1940) w25q256_force_extended_address(bank, ctrl_drv);

+ if ((ractrends_spiflash_flash_id[bank] == 0x002020BA) || (ractrends_spiflash_flash_id[bank] == 0x002021BA) || (ractrends_spiflash_flash_id[bank] == 0x00C21A20))

+ spi_generic_extended_address(bank, SPI_WRITE, 0x00, ctrl_drv);

+

+ if(had_switch_die == 1)

+ {

+ spi_generic_select_die( bank, 0,ctrl_drv);

+ }

+ up(&priv->chip_drv->lock);

+ return spi_error(retval);

+ }

+

+ if ( ((sect_addr >= ADDR_16MB) && ((address32 == ADDRESS_LO3_HI4_BYTE)||(address32 == ADDRESS_DIE_LO3_HI4_BYTE))) || pwr_up_mode)

+ {

+ retval = exit_4byte_addr_mode(bank, ctrl_drv);

+ if (retval < 0)

+ {

+ printk ("Unable to exit 4 byte address mode\n");

+ }

+ }

+

+ if (ractrends_spiflash_flash_id[bank] == 0x00EF1940) w25q256_force_extended_address(bank, ctrl_drv);

+ if ((ractrends_spiflash_flash_id[bank] == 0x002020BA) || (ractrends_spiflash_flash_id[bank] == 0x002021BA) || (ractrends_spiflash_flash_id[bank] == 0x00C21A20))

+ spi_generic_extended_address(bank, SPI_WRITE, 0x00, ctrl_drv);

+

+ if(had_switch_die == 1)

+ {

+ spi_generic_select_die( bank, 0,ctrl_drv);

+ }

+ up(&priv->chip_drv->lock);

+ return retval;

+}

+

+

+int

+spi_generic_read(struct map_info *map, loff_t addr, size_t bytes, unsigned char *buff)

+{

+ struct spi_flash_private *priv=map->fldrv_priv;

+ int bank = map->map_priv_1;

+ struct spi_ctrl_driver *ctrl_drv = priv->ctrl_drv;

+ int retval = 0;

+ size_t transfer;

+ unsigned char command[6];

+ int cmd_size;

+ int (*readfn)(int bank,unsigned char *,int , SPI_DIR, unsigned char *, unsigned long); //unsigned long);

+ int end_addr = (addr+bytes-1);

+ u8 address32 = priv->address32;

+ //unsigned long flash_size = priv->size;

+ u8 had_switch_die = 0;

+ u8 pwr_up_mode = 0;

+

+ /* Some time zero bytes length are sent */

+ if (bytes==0)

+ return 0;

+

+ if (ractrends_spiflash_flash_id[bank] == 0x00EF1940)

+ {

+ u8 reg_data;

+

+ command[0] = 0x15; /* Read Status Register S23 ~ S16 */

+ cmd_size = 1;

+ retval = ctrl_drv->spi_transfer(bank,command, cmd_size ,SPI_READ, ®_data, 1);

+ pwr_up_mode = (reg_data & 0x2)>>1; /* S17(ADP) field */

+ }

+

+ if (address32 == ADDRESS_DIE_LO3_HI4_BYTE)

+ {

+ if (addr < ADDR_32MB && end_addr >= ADDR_32MB)

+ {

+ int ErrorCode;

+ transfer = (ADDR_32MB - addr);

+ ErrorCode = spi_generic_read(map, addr, transfer, buff);

+ if (ErrorCode != 0) return ErrorCode;

+

+ //fix address

+ bytes-=transfer;

+ addr+=transfer;

+ buff+=transfer;

+

+ end_addr = (addr+bytes-1);

+ if (bytes==0) return 0;

+ }

+ }

+ down(&priv->chip_drv->lock);

+

+

+

+ /* Wait until finished previous command. */

+ if (wait_till_ready(bank,ctrl_drv))

+ {

+ up(&priv->chip_drv->lock);

+ return -1;

+ }

+

+ if (address32 == ADDRESS_DIE_LO3_HI4_BYTE){

+ if(addr >= ADDR_32MB){

+ spi_generic_select_die( bank, 1,ctrl_drv);

+ had_switch_die = 1;

+ addr-=ADDR_32MB;

+ end_addr = (addr+bytes-1);

+ }

+ }

+

+ if (ctrl_drv->spi_burst_read)

+ readfn = ctrl_drv->spi_burst_read;

+ else

+ readfn = ctrl_drv->spi_transfer;

+

+ transfer=bytes;

+

+

+ /* Logic for 4 byte address mode Enter */

+ if ( (( end_addr >= ADDR_16MB) && ((address32 == ADDRESS_LO3_HI4_BYTE )||(address32 == ADDRESS_DIE_LO3_HI4_BYTE))) || pwr_up_mode)

+ {

+ //printk ("Trying to enter 4 byte mode\n");

+ retval = enter_4byte_addr_mode(bank, ctrl_drv);

+ if (retval < 0)

+ {

+ printk ("Unable to enter 4 byte address mode\n");

+ if(had_switch_die == 1)

+ {

+ spi_generic_select_die( bank, 0,ctrl_drv);

+ }

+ up(&priv->chip_drv->lock);

+ return spi_error(retval);

+ }

+ }

+

+ if (ractrends_spiflash_flash_id[bank] == 0x00EF1940) w25q256_force_extended_address(bank, ctrl_drv);

+ if ((ractrends_spiflash_flash_id[bank] == 0x002020BA) || (ractrends_spiflash_flash_id[bank] == 0x002021BA) || (ractrends_spiflash_flash_id[bank] == 0x00C21A20))

+ spi_generic_extended_address(bank, SPI_WRITE, (addr & 0xFF000000) >> 24, ctrl_drv);

+

+ while (bytes)

+ {

+ if (ctrl_drv->spi_burst_read)

+ transfer=bytes;

+ else

+ {

+ transfer=ctrl_drv->max_read;

+ if (transfer > bytes)

+ transfer = bytes;

+ }

+

+ if (!ctrl_drv->fast_read)

+ {

+ if ( ((( end_addr >= ADDR_16MB) && ((address32 == ADDRESS_LO3_HI4_BYTE)||(address32 == ADDRESS_DIE_LO3_HI4_BYTE))) || (address32 == ADDRESS_4BYTE)) || pwr_up_mode )

+ {

+ /* Set up command buffer. */ /* Normal Read */

+ command[0] = OPCODE_READ;

+ if (ractrends_spiflash_flash_id[bank] == 0x00011902) command[0] = 0x13; // READ command in 4byte mode [spansion only]

+ if (address32 == ADDRESS_DIE_LO3_HI4_BYTE) command[0] = 0x13; // READ command in 4byte mode

+ command[1] = addr >> 24;

+ command[2] = addr >> 16;

+ command[3] = addr >> 8;

+ command[4] = addr;

+

+ cmd_size = 5;

+ }

+ else {

+

+ /* Set up command buffer. */ /* Normal Read */

+ command[0] = OPCODE_READ;

+ command[1] = addr >> 16;

+ command[2] = addr >> 8;

+ command[3] = addr;

+

+ cmd_size = 4;

+ }

+ /* Issue Controller Transfer Routine */

+ retval = (*readfn)(bank,command, cmd_size ,SPI_READ, buff, (unsigned long)transfer);

+ }

+ else if (ctrl_drv->fast_read == 1) // Need to check Fast Read in 4 byte address mode

+ {

+ if ( ((( end_addr >= ADDR_16MB) && ((address32 == ADDRESS_LO3_HI4_BYTE)||(address32 == ADDRESS_DIE_LO3_HI4_BYTE))) || (address32 == ADDRESS_4BYTE)) || pwr_up_mode )

+ {

+ /* Set up command buffer. */ /* Fast Read */

+ command[0] = OPCODE_FAST_READ;

+ if (ractrends_spiflash_flash_id[bank] == 0x00011902) command[0] = 0x0C; // FAST_READ command in 4byte mode [spansion only]

+ if (address32 == ADDRESS_DIE_LO3_HI4_BYTE) command[0] = 0x0C; // FAST_READ command in 4byte mode

+ command[1] = addr >> 24;

+ command[2] = addr >> 16;

+ command[3] = addr >> 8;

+ command[4] = addr;

+ command[5] = 0; /* dummy data */

+

+ cmd_size = 6;

+ }

+ else

+ {

+ /* Set up command buffer. */ /* Fast Read */

+ command[0] = OPCODE_FAST_READ;

+ command[1] = addr >> 16;

+ command[2] = addr >> 8;

+ command[3] = addr;

+ command[4] = 0; /* dummy data */

+

+ cmd_size = 5;

+ }

+ /* Issue Controller Transfer Routine */

+ retval = (*readfn)(bank,command, cmd_size ,SPI_READ, buff, (unsigned long)transfer);

+ }

+ else if (ctrl_drv->fast_read == 2) // Need to check Dual Read in 4 byte address mode

+ {

+ if ( ((( end_addr >= ADDR_16MB) && ((address32 == ADDRESS_LO3_HI4_BYTE)||(address32 == ADDRESS_DIE_LO3_HI4_BYTE))) || (address32 == ADDRESS_4BYTE)) || pwr_up_mode )

+ {

+ /* Set up command buffer. */ /* Dual Read */

+ command[0] = OPCODE_DREAD;

+ command[1] = addr >> 24;

+ command[2] = addr >> 16;

+ command[3] = addr >> 8;

+ command[4] = addr;

+ command[5] = 0; /* dummy data */

+

+ cmd_size = 6;

+ }

+ else

+ {

+ /* Set up command buffer. */ /* Dual Read */

+ command[0] = OPCODE_DREAD;

+ command[1] = addr >> 16;

+ command[2] = addr >> 8;

+ command[3] = addr;

+ command[4] = 0; /* dummy data */

+

+ cmd_size = 5;

+ }

+ /* Issue Controller Transfer Routine */

+ retval = (*readfn)(bank,command, cmd_size ,SPI_READ, buff, (unsigned long)transfer);

+ }

+ else if (ctrl_drv->fast_read == 3) // Need to check 2xI/O Read in 4 byte address mode

+ {

+ if ( ((( end_addr >= ADDR_16MB) && ((address32 == ADDRESS_LO3_HI4_BYTE)||(address32 == ADDRESS_DIE_LO3_HI4_BYTE))) || (address32 == ADDRESS_4BYTE)) || pwr_up_mode )

+ {

+ /* Set up command buffer. */ /* 2xI/O Read */

+ command[0] = OPCODE_2READ;

+ command[1] = addr >> 24;

+ command[2] = addr >> 16;

+ command[3] = addr >> 8;

+ command[4] = addr;

+ command[5] = 0; /* dummy data */

+

+ cmd_size = 6;

+ }

+ else

+ {

+ /* Set up command buffer. */ /* 2xI/O Read */

+ command[0] = OPCODE_2READ;

+ command[1] = addr >> 16;

+ command[2] = addr >> 8;

+ command[3] = addr;

+ command[4] = 0; /* dummy data */

+

+ cmd_size = 5;

+ }

+ /* Issue Controller Transfer Routine */

+ retval = (*readfn)(bank,command, cmd_size ,SPI_READ, buff, (unsigned long)transfer);

+ }

+

+ if (retval < 0)

+ {

+ //if 4 byte mode, exit

+ if ( (( end_addr >= ADDR_16MB) && ((address32 == ADDRESS_LO3_HI4_BYTE)||(address32 == ADDRESS_DIE_LO3_HI4_BYTE))) || pwr_up_mode)

+ {

+ retval = exit_4byte_addr_mode(bank, ctrl_drv);

+ if (retval < 0)

+ {

+ printk ("Unable to exit 4 byte address mode\n");

+ }

+ }

+

+ if (ractrends_spiflash_flash_id[bank] == 0x00EF1940) w25q256_force_extended_address(bank, ctrl_drv);

+ if ((ractrends_spiflash_flash_id[bank] == 0x002020BA) || (ractrends_spiflash_flash_id[bank] == 0x002021BA) || (ractrends_spiflash_flash_id[bank] == 0x00C21A20))

+ spi_generic_extended_address(bank, SPI_WRITE, 0x00, ctrl_drv);

+

+ if(had_switch_die == 1)

+ {

+ spi_generic_select_die( bank, 0,ctrl_drv);

+ }

+ up(&priv->chip_drv->lock);

+ return spi_error(retval);

+ }

+

+ bytes-=transfer;

+ addr+=transfer;

+ buff+=transfer;

+ }

+

+ //if 4 byte mode exit

+ if ( (( end_addr >= ADDR_16MB) && ((address32 == ADDRESS_LO3_HI4_BYTE)||(address32 == ADDRESS_DIE_LO3_HI4_BYTE))) || pwr_up_mode)

+ {

+ //printk ("Trying to exit 4 byte mode\n");

+ retval = exit_4byte_addr_mode(bank, ctrl_drv);

+ if (retval < 0)

+ {

+ printk ("Unable to exit 4 byte address mode\n");

+ }

+ }

+

+ if (ractrends_spiflash_flash_id[bank] == 0x00EF1940) w25q256_force_extended_address(bank, ctrl_drv);

+ if ((ractrends_spiflash_flash_id[bank] == 0x002020BA) || (ractrends_spiflash_flash_id[bank] == 0x002021BA) || (ractrends_spiflash_flash_id[bank] == 0x00C21A20))

+ spi_generic_extended_address(bank, SPI_WRITE, 0x00, ctrl_drv);

+

+ if(had_switch_die == 1)

+ {

+ spi_generic_select_die( bank, 0,ctrl_drv);

+ }

+ up(&priv->chip_drv->lock);

+ return 0;

+}

+

+

+int

+spi_generic_write(struct map_info *map, loff_t addr, size_t bytes, const unsigned char *buff)

+{

+ struct spi_flash_private *priv=map->fldrv_priv;

+ int bank = map->map_priv_1;

+ struct spi_ctrl_driver *ctrl_drv = priv->ctrl_drv;

+

+ int retval;

+ unsigned char command[5];

+ size_t transfer;

+ int cmd_size = 0;

+ int end_addr = (addr+bytes-1);

+ u8 address32 = priv->address32;

+ //unsigned long flash_size = priv->size;

+ u8 had_switch_die = 0;

+ u8 pwr_up_mode = 0;

+

+ /* Some time zero bytes length are sent */

+ if (bytes==0)

+ return 0;

+

+ if (ractrends_spiflash_flash_id[bank] == 0x00EF1940)

+ {

+ u8 reg_data;

+

+ command[0] = 0x15; /* Read Status Register S23 ~ S16 */

+ cmd_size = 1;

+ retval = ctrl_drv->spi_transfer(bank,command, cmd_size ,SPI_READ, ®_data, 1);

+ pwr_up_mode = (reg_data & 0x2)>>1; /* S17(ADP) field */

+ }

+

+ if (address32 == ADDRESS_DIE_LO3_HI4_BYTE)

+ {

+ if (addr < ADDR_32MB && end_addr >= ADDR_32MB)

+ {

+ int ErrorCode;

+ transfer = (ADDR_32MB - addr);

+ ErrorCode = spi_generic_write(map, addr, transfer, buff);

+ if (ErrorCode != 0) return ErrorCode;

+

+ //fix address

+ bytes-=transfer;

+ addr+=transfer;

+ buff+=transfer;

+

+ end_addr = (addr+bytes-1);

+ if (bytes==0) return 0;

+ }

+ }

+

+ down(&priv->chip_drv->lock);

+

+ if (address32 == ADDRESS_DIE_LO3_HI4_BYTE){

+ if(addr >= ADDR_32MB){

+ spi_generic_select_die( bank, 1,ctrl_drv);

+ had_switch_die = 1;

+ addr-=ADDR_32MB;

+ end_addr = (addr+bytes-1);

+ }

+ }

+

+ /* Logic for 4 byte address mode Enter */

+ if ( (( end_addr >= ADDR_16MB) && ((address32 == ADDRESS_LO3_HI4_BYTE)||(address32 == ADDRESS_DIE_LO3_HI4_BYTE))) || pwr_up_mode)

+ {

+ retval = enter_4byte_addr_mode(bank, ctrl_drv);

+ if (retval < 0)

+ {

+ printk ("Unable to enter 4 byte address mode\n");

+ if(had_switch_die == 1)

+ {

+ spi_generic_select_die( bank, 0,ctrl_drv);

+ }

+ up(&priv->chip_drv->lock);

+ return spi_error(retval);

+ }

+ }

+

+ if (ractrends_spiflash_flash_id[bank] == 0x00EF1940) w25q256_force_extended_address(bank, ctrl_drv);

+ if ((ractrends_spiflash_flash_id[bank] == 0x002020BA) || (ractrends_spiflash_flash_id[bank] == 0x002021BA) || (ractrends_spiflash_flash_id[bank] == 0x00C21A20))

+ spi_generic_extended_address(bank, SPI_WRITE, (addr & 0xFF000000) >> 24, ctrl_drv);

+

+ while (bytes)

+ {

+ /* Wait until finished previous command. */

+ if (wait_till_ready(bank,ctrl_drv))

+ {

+ if(had_switch_die == 1)

+ {

+ spi_generic_select_die( bank, 0,ctrl_drv);

+ }

+ up(&priv->chip_drv->lock);

+ return -1;

+ }

+

+ transfer = PROGRAM_PAGE_SIZE;

+ if (bytes < transfer)

+ transfer = bytes;

+

+ if (!ctrl_drv->fast_write)

+ {

+ if ( (((end_addr >= ADDR_16MB) && (address32 == ADDRESS_LO3_HI4_BYTE)) || (address32 == ADDRESS_4BYTE)) || pwr_up_mode)

+ {

+ /* Set up command buffer. */

+ command[0] = OPCODE_PP;

+ if (ractrends_spiflash_flash_id[bank] == 0x00011902) command[0] = 0x12; // PROGRAM command in 4byte mode [spansion only]

+ if (address32 == ADDRESS_DIE_LO3_HI4_BYTE) command[0] = 0x12; // PROGRAM command in 4byte mode

+ command[1] = addr >> 24;

+ command[2] = addr >> 16;

+ command[3] = addr >> 8;

+ command[4] = addr;

+ cmd_size = 5;

+ }

+ else {

+ /* Set up command buffer. */

+ command[0] = OPCODE_PP;

+ command[1] = addr >> 16;

+ command[2] = addr >> 8;

+ command[3] = addr;

+ cmd_size = 4;

+ }

+ }

+

+ /* Issue Controller Transfer Routine */

+ spi_generic_write_enable(bank,ctrl_drv); /* Send write enable */

+ retval = ctrl_drv->spi_transfer(bank,command,cmd_size ,SPI_WRITE,

+ (unsigned char *)buff, transfer);

+ spi_generic_write_disable(bank,ctrl_drv); /* Send write disable */

+

+ if (ractrends_spiflash_flash_id[bank] == 0x002020BA || ractrends_spiflash_flash_id[bank] == 0x002021BA)

+ {

+ /* requires the read flag status with at latest one byte. */

+ if (require_read_flag_status(bank,ctrl_drv))

+ {

+ up(&priv->chip_drv->lock);

+ return -1;

+ }

+ }

+

+ if (retval < 0)

+ {

+ //if 4 byte mode exit

+ if ( (( end_addr >= ADDR_16MB) && ((address32 == ADDRESS_LO3_HI4_BYTE)||(address32 == ADDRESS_DIE_LO3_HI4_BYTE))) || pwr_up_mode)

+ {

+ retval = exit_4byte_addr_mode(bank, ctrl_drv);

+ if (retval < 0)

+ {

+ printk ("Unable to exit 4 byte address mode\n");

+ }

+ }

+

+ if (ractrends_spiflash_flash_id[bank] == 0x00EF1940) w25q256_force_extended_address(bank, ctrl_drv);

+ if ((ractrends_spiflash_flash_id[bank] == 0x002020BA) || (ractrends_spiflash_flash_id[bank] == 0x002021BA) || (ractrends_spiflash_flash_id[bank] == 0x00C21A20))

+ spi_generic_extended_address(bank, SPI_WRITE, 0x00, ctrl_drv);

+

+ if(had_switch_die == 1)

+ {

+ spi_generic_select_die( bank, 0,ctrl_drv);

+ }

+ up(&priv->chip_drv->lock);

+ return spi_error(retval);

+ }

+ addr+=(transfer-retval);

+ buff+=(transfer-retval);

+ bytes-=(transfer-retval);

+ }

+

+ //if 4 byte mode exit

+ if ( (( end_addr >= ADDR_16MB) && ((address32 == ADDRESS_LO3_HI4_BYTE)||(address32 == ADDRESS_DIE_LO3_HI4_BYTE))) || pwr_up_mode)

+ {

+ retval = exit_4byte_addr_mode(bank, ctrl_drv);

+ if (retval < 0)

+ {

+ printk ("Unable to exit 4 byte address mode\n");

+ }

+ }

+

+ if (ractrends_spiflash_flash_id[bank] == 0x00EF1940) w25q256_force_extended_address(bank, ctrl_drv);

+ if ((ractrends_spiflash_flash_id[bank] == 0x002020BA) || (ractrends_spiflash_flash_id[bank] == 0x002021BA) || (ractrends_spiflash_flash_id[bank] == 0x00C21A20))

+ spi_generic_extended_address(bank, SPI_WRITE, 0x00, ctrl_drv);

+

+ if(had_switch_die == 1)

+ {

+ spi_generic_select_die( bank, 0,ctrl_drv);

+ }

+ up(&priv->chip_drv->lock);

+ return 0;

+}

+

+/***********************************************************************************/

+extern int spi_verbose;

+int

+spi_generic_probe(int bank,struct spi_ctrl_driver *ctrl_drv, struct spi_flash_info *chip_info,

+ char *spi_name,struct spi_flash_info *spi_list, int spi_list_len)

+{

+ int retval;

+ u32 val;

+ int i;

+ u16 opread;

+ u16 opwrite;

+ u8 code = OPCODE_RDID;

+ //int address_mode = 0;

+

+ if (spi_verbose == 2)

+ printk("SPI: probing for %s devices ...\n",spi_name);

+

+ /* Send write enable */

+ retval =spi_generic_write_enable(bank,ctrl_drv);

+ if (retval < 0)

+ return -1;

+

+ /* Issue Controller Transfer Routine */

+ val = 0;

+ retval = ctrl_drv->spi_transfer(bank,&code, 1,SPI_READ,(unsigned char *)&val, 3);

+ val &= 0x00FFFFFF;

+

+ if (retval < 0)

+ {

+ spi_error(retval);

+ return -1;

+ }

+

+ /* Send write disable */

+ retval = spi_generic_write_disable(bank,ctrl_drv);

+ if (retval < 0)

+ return -1;

+

+ /* Match the ID against the table entries */

+ for (i = 0; i < spi_list_len; i++)

+ {

+ if ((spi_list[i].mfr_id == ((val)& 0xFF)) && (spi_list[i].dev_id == ((val >> 8)& 0xFFFF)))

+ {

+ /* Check Operation Mode */

+ //for Read Operation

+ opread = (spi_list[i].operationmode & 0xFFFF);

+ opread &= ctrl_drv->operation_mode_mask;

+ if (opread > 0x7)

+ {

+ ctrl_drv->fast_read = 3;

+ }

+ else if ((0x3 < opread) && (opread <= 0x7))

+ {

+ ctrl_drv->fast_read = 2;

+ }

+ else if ((0x1 < opread) && (opread <= 0x3))

+ {

+ ctrl_drv->fast_read = 1;

+ }

+ else if (opread <= 0x1)

+ {

+ ctrl_drv->fast_read = 0;

+ }

+

+ //for Write Operation

+ opwrite = (spi_list[i].operationmode >> 16);

+ opwrite &= (ctrl_drv->operation_mode_mask >> 16);

+ if (opwrite <= 0x1)

+ {

+ ctrl_drv->fast_write = 0;

+ }

+

+ break;

+ }

+ }

+

+ if (i == spi_list_len)

+ {

+// if (spi_verbose == 2)

+// printk("%s : Unrecognized ID (0x%x) got \n",spi_name,val);

+ return -1;

+ }

+ memcpy(chip_info,&spi_list[i],sizeof(struct spi_flash_info));

+

+ if (spi_verbose > 0)

+ printk(KERN_INFO"Found SPI Chip %s \n",spi_list[i].name);

+

+ return 0;

+

+}

+

+EXPORT_SYMBOL(spi_generic_probe);

+EXPORT_SYMBOL(spi_generic_erase);

+EXPORT_SYMBOL(spi_generic_read);

+EXPORT_SYMBOL(spi_generic_write);

+EXPORT_SYMBOL(spi_generic_write_disable);

+EXPORT_SYMBOL(spi_generic_write_enable);

+EXPORT_SYMBOL(spi_generic_read_status);

+EXPORT_SYMBOL(spi_generic_write_status);

+

+MODULE_LICENSE("GPL");

+MODULE_AUTHOR("American Megatrends Inc");

+MODULE_DESCRIPTION("MTD SPI driver for Generic SPI flash chips");

+

+#endif

diff --git a/drivers/mtd/spichips/intels33.c b/drivers/mtd/spichips/intels33.c

new file mode 100644

index 0000000..6900319

--- /dev/null

+++ b/drivers/mtd/spichips/intels33.c

@@ -0,0 +1,96 @@

+/*

+ * Copyright (C) 2007 American Megatrends Inc

+ *

+ * This program is free software; you can redistribute it and/or modify

+ * it under the terms of the GNU General Public License as published by

+ * the Free Software Foundation; either version 2 of the License, or

+ * (at your option) any later version.

+ *

+ * This program is distributed in the hope that it will be useful,

+ * but WITHOUT ANY WARRANTY; without even the implied warranty of

+ * MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

+ * GNU General Public License for more details.

+ *

+ * You should have received a copy of the GNU General Public License

+ * along with this program; if not, write to the Free Software

+ * Foundation, Inc., 675 Mass Ave, Cambridge, MA 02139, USA.

+ */

+

+

+#ifdef __UBOOT__

+#include <common.h>

+#endif

+#include "spiflash.h"

+#ifdef CFG_FLASH_SPI_DRIVER

+

+/* Name, ID1, ID2 , Size, Clock, Erase regions, address mode,{ Offset, Erase Size, Erase Block Count } */

+/* address mode: 0x00 -3 byte address

+ 0x01 - 4 byte address

+ 0x02 - Low byte: 3 byte address, High byte: 4 byte address*/

+static struct spi_flash_info s33_data [] =

+{

+ /* Intel S33 64 K Sectors */

+ { "Intel S33 16Mb" , 0x89, 0x1189, 0x00010001, 0x200000 , 68 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 32 },} },

+ { "Intel S33 32Mb" , 0x89, 0x1289, 0x00010001, 0x400000 , 68 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 64 },} },

+ { "Intel S33 64Mb" , 0x89, 0x1389, 0x00010001, 0x800000 , 68 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 128 },} },

+};

+

+

+static

+int

+s33_probe(int bank,struct spi_ctrl_driver *ctrl_drv, struct spi_flash_info *chip_info)

+{

+ int retval;

+ retval = spi_generic_probe(bank,ctrl_drv,chip_info,"intel s33",

+ s33_data,ARRAY_SIZE(s33_data));

+

+ if (retval == -1)

+ return retval;

+

+ /* UnProctect all sectors */

+ /* SRWD=0 (Bit 7) BP0,BP1,BP2 = 0 (Bit 2,3,4) */

+ if (spi_generic_write_status(bank,ctrl_drv,0x0) < 0)

+ printk("intel s33: Unable to Unprotect all sectors\n");

+ return retval;

+}

+

+struct spi_chip_driver s33_driver =

+{

+ .name = "intel s33",

+ .module = THIS_MODULE,

+ .probe = s33_probe,

+ .erase_sector = spi_generic_erase,

+ .read_bytes = spi_generic_read,

+ .write_bytes = spi_generic_write,

+};

+

+int

+s33_init(void)

+{

+ sema_init(&s33_driver.lock, 1);

+#ifdef __UBOOT__ /* MIPS */

+ s33_driver.probe = s33_probe;

+ s33_driver.erase_sector = spi_generic_erase;

+ s33_driver.read_bytes = spi_generic_read;

+ s33_driver.write_bytes = spi_generic_write;

+#endif

+ register_spi_chip_driver(&s33_driver);

+ return 0;

+}

+

+void

+s33_exit(void)

+{

+ sema_init(&s33_driver.lock, 1);

+ unregister_spi_chip_driver(&s33_driver);

+ return;

+}

+

+module_init(s33_init);

+module_exit(s33_exit);

+

+MODULE_LICENSE("GPL");

+MODULE_AUTHOR("American Megatrends Inc");

+MODULE_DESCRIPTION("MTD SPI driver for Intel S33 flash chips");

+

+#endif

diff --git a/drivers/mtd/spichips/m25pxx.c b/drivers/mtd/spichips/m25pxx.c

new file mode 100644

index 0000000..448fe06

--- /dev/null

+++ b/drivers/mtd/spichips/m25pxx.c

@@ -0,0 +1,121 @@

+/*

+ * Copyright (C) 2007 American Megatrends Inc

+ *

+ * This program is free software; you can redistribute it and/or modify

+ * it under the terms of the GNU General Public License as published by

+ * the Free Software Foundation; either version 2 of the License, or

+ * (at your option) any later version.

+ *

+ * This program is distributed in the hope that it will be useful,

+ * but WITHOUT ANY WARRANTY; without even the implied warranty of

+ * MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

+ * GNU General Public License for more details.

+ *

+ * You should have received a copy of the GNU General Public License

+ * along with this program; if not, write to the Free Software

+ * Foundation, Inc., 675 Mass Ave, Cambridge, MA 02139, USA.

+ */

+

+

+#ifdef __UBOOT__

+#include <common.h>

+#endif

+#include "spiflash.h"

+#ifdef CFG_FLASH_SPI_DRIVER

+

+/* Name, ID1, ID2 , Size, Clock, Erase regions, address mode,{ Offset, Erase Size, Erase Block Count } */

+/* address mode: 0x00 -3 byte address

+ 0x01 - 4 byte address

+ 0x02 - Low byte: 3 byte address, High byte: 4 byte address*/

+static struct spi_flash_info m25pxx_data [] =

+{

+ /* ST Micro 32K Sectors */

+ { "ST Micro m25p05A" , 0x20, 0x1020, 0x00010001, 0x010000 , 50 * 1000000, 1, 0x00, {{ 0, 32 * 1024, 2 },} },

+ { "ST Micro m25p10A" , 0x20, 0x1120, 0x00010001, 0x020000 , 50 * 1000000, 1, 0x00, {{ 0, 32 * 1024, 4 },} },

+

+ /* ST Micro 64 K Sectors */

+ { "ST Micro m25p20" , 0x20, 0x1220, 0x00010001, 0x040000 , 75 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 4 },} },

+ { "ST Micro m25p40" , 0x20, 0x1320, 0x00010001, 0x080000 , 75 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 8 },} },

+ { "ST Micro m25p80" , 0x20, 0x1420, 0x00010001, 0x100000 , 75 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 16 },} },

+ { "ST Micro m25p16" , 0x20, 0x1520, 0x00010001, 0x200000 , 75 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 32 },} },

+ { "ST Micro m25p32" , 0x20, 0x1620, 0x00010001, 0x400000 , 75 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 64 },} },

+ { "ST Micro m25p64" , 0x20, 0x1720, 0x00010001, 0x800000 , 75 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 128 },} },

+ { "ST Micro m25px64" , 0x20, 0x1771, 0x00010001, 0x800000 , 75 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 128 },} },

+

+ /* ST Micro 256K Sectors */

+ { "ST Micro m25p128" , 0x20, 0x1820, 0x00010001, 0x1000000, 50 * 1000000, 1, 0x00, {{ 0, 256 * 1024, 64 },} },

+

+ /* ST Micro 64 K Sectors, 25MHz speed */

+ { "ST Micro m45p20" , 0x20, 0x1240, 0x00010001, 0x040000 , 25 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 4 },} },

+ { "ST Micro m45p40" , 0x20, 0x1340, 0x00010001, 0x080000 , 25 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 8 },} },

+ { "ST Micro m45p80" , 0x20, 0x1440, 0x00010001, 0x100000 , 25 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 16 },} },

+ { "ST Micro m45p16" , 0x20, 0x1540, 0x00010001, 0x200000 , 25 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 32 },} },

+ { "ST Micro m45p32" , 0x20, 0x1640, 0x00010001, 0x400000 , 25 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 64 },} },

+ { "ST Micro m45p64" , 0x20, 0x1740, 0x00010001, 0x800000 , 25 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 128 },} },

+

+};

+

+

+static

+int

+m25pxx_probe(int bank,struct spi_ctrl_driver *ctrl_drv, struct spi_flash_info *chip_info)

+{

+ int retval;

+ retval = spi_generic_probe(bank,ctrl_drv,chip_info,"m25pxx",

+ m25pxx_data,ARRAY_SIZE(m25pxx_data));

+

+ if (retval == -1)

+ return retval;

+

+ /* UnProctect all sectors */

+ /* SRWD=0 (Bit 7) BP0,BP1,BP2 = 0 (Bit 2,3,4) */

+ if (spi_generic_write_status(bank,ctrl_drv,0x0) < 0)

+ printk("m25pxx: Unable to Unprotect all sectors\n");

+

+ return retval;

+}

+

+struct spi_chip_driver m25pxx_driver =

+{

+ .name = "m25pxx",

+ .module = THIS_MODULE,

+ .probe = m25pxx_probe,

+ .erase_sector = spi_generic_erase,

+ .read_bytes = spi_generic_read,

+ .write_bytes = spi_generic_write,

+};

+

+

+

+int

+m25pxx_init(void)

+{

+ sema_init(&m25pxx_driver.lock, 1);

+#ifdef __UBOOT__ /* MIPS */

+ m25pxx_driver.probe = m25pxx_probe;

+ m25pxx_driver.erase_sector = spi_generic_erase;

+ m25pxx_driver.read_bytes = spi_generic_read;

+ m25pxx_driver.write_bytes = spi_generic_write;

+#endif

+ register_spi_chip_driver(&m25pxx_driver);

+ return 0;

+}

+

+

+void

+m25pxx_exit(void)

+{

+ sema_init(&m25pxx_driver.lock, 1);

+ unregister_spi_chip_driver(&m25pxx_driver);

+ return;

+}

+

+

+module_init(m25pxx_init);

+module_exit(m25pxx_exit);

+

+MODULE_LICENSE("GPL");

+MODULE_AUTHOR("American Megatrends Inc");

+MODULE_DESCRIPTION("MTD SPI driver for ST M25Pxx flash chips");

+

+#endif

diff --git a/drivers/mtd/spichips/macronix.c b/drivers/mtd/spichips/macronix.c

new file mode 100644

index 0000000..176d101

--- /dev/null

+++ b/drivers/mtd/spichips/macronix.c

@@ -0,0 +1,208 @@

+/*

+ * Copyright (C) 2007 American Megatrends Inc

+ *

+ * This program is free software; you can redistribute it and/or modify

+ * it under the terms of the GNU General Public License as published by

+ * the Free Software Foundation; either version 2 of the License, or

+ * (at your option) any later version.

+ *

+ * This program is distributed in the hope that it will be useful,

+ * but WITHOUT ANY WARRANTY; without even the implied warranty of

+ * MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

+ * GNU General Public License for more details.

+ *

+ * You should have received a copy of the GNU General Public License

+ * along with this program; if not, write to the Free Software

+ * Foundation, Inc., 675 Mass Ave, Cambridge, MA 02139, USA.

+ */

+

+

+#ifdef __UBOOT__

+#include <common.h>

+#endif

+#include "spiflash.h"

+#ifdef CFG_FLASH_SPI_DRIVER

+

+#define CMD_MX25XX_RDSCUR 0x2B /* Read security register */

+#define CMD_MX25XX_RDCR 0x15 /* Read configuration register */

+

+/* Security register */

+#define SCUR_BIT2 0x04

+

+/* Configuration register */

+#define CR_BIT5 0x20

+

+#define ADDRESS_3BYTE 0x00

+#define ADDRESS_4BYTE 0x01

+#define ADDRESS_LO3_HI4_BYTE 0x02

+#define MX25L25x35E_MFR_ID 0xC2

+#define MX25L25x35E_DEV_ID 0x1920

+

+

+/* Name, ID1, ID2 , Size, Clock, Erase regions, address mode,{ Offset, Erase Size, Erase Block Count } */

+/* address mode: 0x00 -3 byte address

+ 0x01 - 4 byte address

+ 0x02 - Low byte: 3 byte address, High byte: 4 byte address*/

+static struct spi_flash_info macronix_data [] =

+{

+ /* Macronix 64 K Sectors */

+ { "Macronix MX25L1605D" , 0xC2, 0x1520, 0x0001000B, 0x200000 , 66 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 32 },} },

+ { "Macronix MX25L3205D" , 0xC2, 0x1620, 0x0001000B, 0x400000 , 66 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 64 },} },

+ { "Macronix MX25L6405D" , 0xC2, 0x1720, 0x0001000B, 0x800000 , 66 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 128 },} },

+ { "Macronix MX25L12805D", 0xC2, 0x1820, 0x00010001, 0x1000000, 50 * 1000000, 1, 0x00, {{ 0, 64 * 1024, 256 },} },

+ { "Macronix MX25L25635E", 0xC2, 0x1920, 0x0001000F, 0x2000000, 50 * 1000000, 1, 0x02, {{ 0, 64 * 1024, 512 },} },

+ { "Macronix MX25L25735E", 0xC2, 0x1920, 0x0001000F, 0x2000000, 50 * 1000000, 1, 0x01, {{ 0, 64 * 1024, 512 },} },

+ { "Macronix MX66L51235F", 0xC2, 0x1A20, 0x0001000F, 0x4000000, 50 * 1000000, 1, 0x02, {{ 0, 64 * 1024, 1024 },} },

+ { "EON EN25QH256", 0x1C, 0x1970, 0x0001000F, 0x2000000, 50 * 1000000, 1, 0x02, {{ 0, 64 * 1024, 512 },} },

+

+};

+

+/* to dinstinguish between MX25L25635/MX25L25735 E and F type */

+static int read_security_register(int bank, struct spi_ctrl_driver *ctrl_drv)

+{

+ u8 code = CMD_MX25XX_RDSCUR;

+ int retval;

+ unsigned char scur_reg;

+

+ /* Issue Controller Transfer Routine*/

+ retval = ctrl_drv->spi_transfer(bank,&code, 1,SPI_READ,&scur_reg, 1);

+ if (retval < 0)

+ {

+ printk ("Could not read security register\n");

+ return -1;

+

+ }

+

+ /* 0x00 - 3 byte mode

+ 0x04 - 4 byte mode */

+ scur_reg &= SCUR_BIT2;

+

+ if(scur_reg == 0x04)

+ return ADDRESS_4BYTE; // MX25L25735E

+ else

+ return ADDRESS_LO3_HI4_BYTE; // MX25L25635E, MX25L25635F, MX25L25735F

+

+ return 0;

+}

+

+/* to dinstinguish MX25L25635/MX25L25735 F type */

+static int read_configuration_register(int bank, struct spi_ctrl_driver *ctrl_drv)