楼主 # 2022-07-29 17:10:58 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

RV1103/RV1106 裸奔日记

RV1103 / RV1106开始裸奔了,要搞定裸奔必须研究透RK的引导机制,经过一整天的深入研究,在没有任何TRM手册的情况下,搞定了RV1106的SPI NAND FLASH引导启动。

下面是启动日记

DDR Version V1.07 20220523

f947

F

DDRConf2

DDR3, BW=16 Col=10 Bk=8 CS0 Row=13 CS=1 Die BW=16 Size=128MB

924MHz

DDR bin out

█████████████████████████

██ ▄▄▄▄▄ ██▄▀▀▀█ ▄▄▄▄▄ ██

██ █ █ █ ▀▄█ █ █ █ ██

██ █▄▄▄█ ██▄ ██ █▄▄▄█ ██

██▄▄▄▄▄▄▄█▄█ █ █▄▄▄▄▄▄▄██

████▀▄ ▀▄▄█ ▀█▄▀█▀▀ █▀██

███▀▄▀ ▀▄ ▄█▀▀▄▀█ ▀█ ▄███

███▄█▄█▄▄▄▀▀ ▄ ▀ ▄▄ ▀ ██

██ ▄▄▄▄▄ █▄ ▄█▄▀▄████▄▄██

██ █ █ █ ▀█▄█▄▄█ ▄▀█▄██

██ █▄▄▄█ ██▀ █ ▄▄▄▄█▄ ██

██▄▄▄▄▄▄▄███▄██▄▄▄▄▄▄▄███

█████████████████████████

_ _

_ _ | |___ _____ _____ _| |_

\ \/ /| _ | _ | _ |_ _| (C) 2007-2022

) ( | |_| | |_| | |_| | | |____JIANJUN.JIANG__

/_/\_\|_____|_____|_____| |_____________________|

V3.0.0 (Jul 29 2022 - 16:59:22) - [x1106][X1106 Based On RV1106 SOC]

[ 0.000020]Probe device 'blk-romdisk.0' with blk-romdisk

[ 0.000800]Probe device 'usbphy480m' with clk-fixed

[ 0.000810]Probe device 'xin24m' with clk-fixed

[ 0.000820]Probe device 'xin32k' with clk-fixed

[ 0.000830]Probe device 'link-uart0' with clk-link

[ 0.000840]Probe device 'link-uart1' with clk-link

[ 0.000850]Probe device 'link-uart2' with clk-link

[ 0.000860]Probe device 'link-uart3' with clk-link

[ 0.000870]Probe device 'link-uart4' with clk-link

[ 0.000880]Probe device 'link-uart5' with clk-link

[ 0.000890]Probe device 'uart-8250.0' with uar & S&LWobe device 'uart-8250.2' with uart-8250

[ 0.000920]Probe device 'uart-8250.3' with uart-8250

[ 0.000930]Probe device 'uart-8250.4' with uart-8250

[ 0.000940]Probe device 'uart-8250.5' with uart-8250

[ 0.000950]Probe device 'console-uart.0' with console-uart

[ 0.001060]mount /private with 'ram' filesystem

xboot: /#

xboot: /# 离线

楼主 #1 2022-07-29 17:13:52 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

为了烧写裸奔镜像,这里对xrock工具进行了扩展,支持了RV1103/RV1106芯片

https://github.com/xboot/xrock

烧写指令:

sudo xrock maskrom rv1106_ddr_924MHz_v1.07.bin rv1106_usbplug_v1.03.bin --rc4-off;

sleep 3;

sudo xrock flash write 512 xbootpak.bin;

sudo xrock reset;离线

#2 2022-07-29 17:49:32 分享评论

- dykxjh

- 会员

- 注册时间: 2020-03-25

- 已发帖子: 190

- 积分: 150

Re: RV1103/RV1106 裸奔日记

xboot出品,必属精品!

离线

#3 2022-07-29 19:13:35 分享评论

- unturned3

- 会员

- 注册时间: 2020-07-01

- 已发帖子: 272

- 积分: 301

Re: RV1103/RV1106 裸奔日记

没TRM都能搞出来,太厉害了 orz

最近编辑记录 unturned3 (2022-07-29 19:13:46)

离线

#5 2022-07-29 20:04:38 分享评论

- jasonhu

- 会员

- 注册时间: 2020-12-22

- 已发帖子: 21

- 积分: 55

Re: RV1103/RV1106 裸奔日记

搞个二维码是什么意思?哈哈哈

离线

#6 2022-07-29 20:38:06 分享评论

- 九重天

- 会员

- 注册时间: 2020-10-06

- 已发帖子: 27

- 积分: 19.5

Re: RV1103/RV1106 裸奔日记

二维码居然给我扫出来了.

离线

#7 2022-07-30 08:28:21 分享评论

- Gentlepig

- 会员

- 注册时间: 2018-10-24

- 已发帖子: 1,409

- 积分: 1368.5

Re: RV1103/RV1106 裸奔日记

用QQ扫了下,该二维码暂不支持识别。

离线

#9 2022-07-31 20:45:14 分享评论

- Timaker

- 会员

- 注册时间: 2020-05-18

- 已发帖子: 65

- 积分: 43.5

Re: RV1103/RV1106 裸奔日记

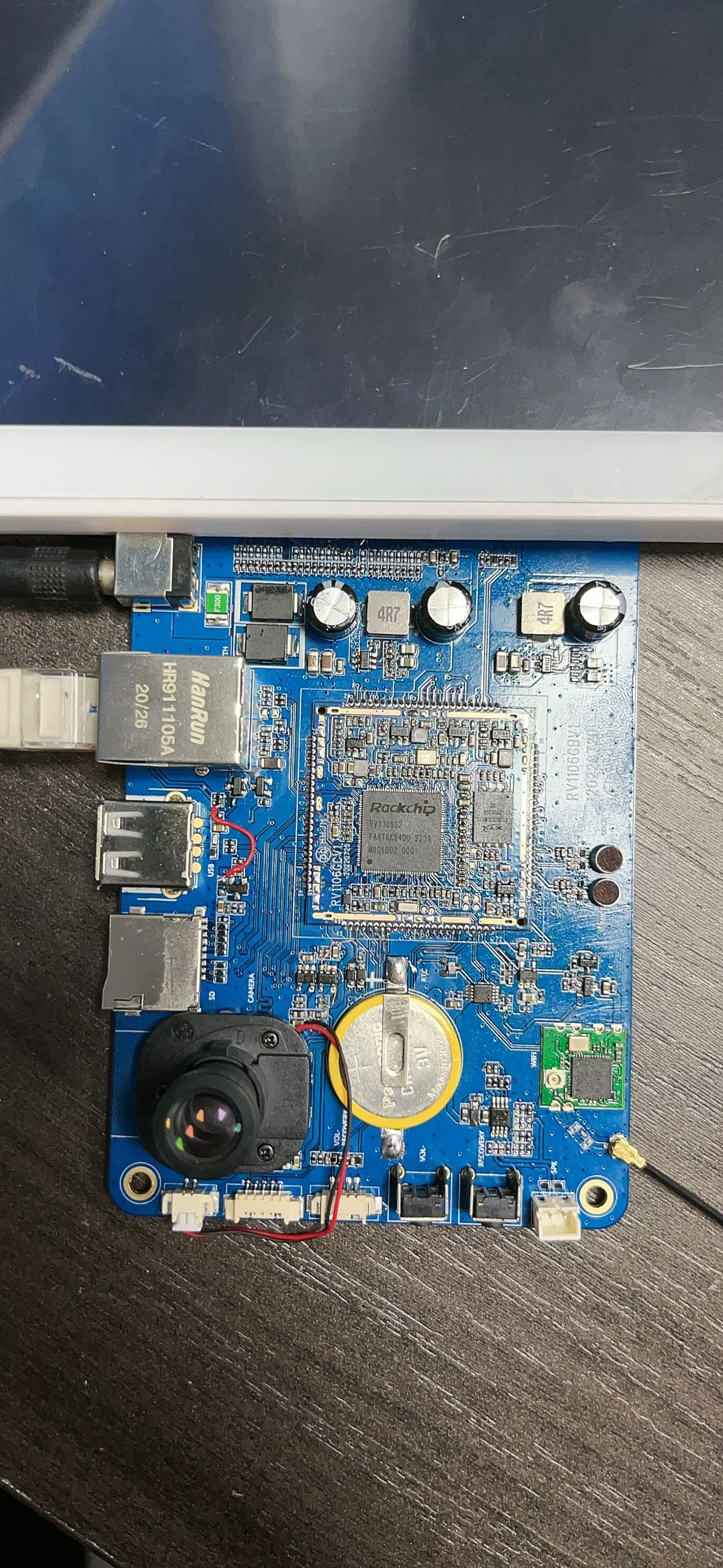

板子拿到了,哪一家的?

离线

楼主 #10 2022-08-01 15:11:42 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

自己造的一个板子,没有寄存器手册,只能用各种资料来推测具体芯片内部细节了,搞定常规外设,基本没太大问题,先用官方的sdk来跑通所有功能先。

离线

#11 2022-08-01 16:22:58 分享评论

- david

- 会员

- 注册时间: 2018-03-05

- 已发帖子: 397

- 积分: 328.5

Re: RV1103/RV1106 裸奔日记

1106这芯片贵么 某宝没见到有

离线

#12 2022-08-01 21:01:25 分享评论

- Timaker

- 会员

- 注册时间: 2020-05-18

- 已发帖子: 65

- 积分: 43.5

Re: RV1103/RV1106 裸奔日记

大佬,出板子吗,我也想玩

离线

楼主 #13 2022-08-02 09:53:58 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

这个芯片比F133/D1S/T113便宜,有价格优势

离线

#14 2022-08-02 12:25:15 分享评论

- tango_zhu

- 会员

- 注册时间: 2018-04-12

- 已发帖子: 132

- 积分: 4

Re: RV1103/RV1106 裸奔日记

xboot wrote:

这个芯片比F133/D1S/T113便宜,有价格优势

啥时候出开发板

离线

#15 2022-08-02 15:24:05 分享评论

- Timaker

- 会员

- 注册时间: 2020-05-18

- 已发帖子: 65

- 积分: 43.5

Re: RV1103/RV1106 裸奔日记

xboot wrote:

这个芯片比F133/D1S/T113便宜,有价格优势

好像含税25左右,等大佬出板子

离线

楼主 #16 2022-08-09 17:28:00 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

先DUMP整个时种树,以便裸奔时参考。

# cat clk_summary

enable prepare protect duty

clock count count count rate accuracy phase cycle

---------------------------------------------------------------------------------------------

xin24m 18 18 0 24000000 0 0 50000

pclk_vi_rtc_root 2 2 0 24000000 0 0 50000

pclk_vi_rtc_phy 1 1 0 24000000 0 0 50000

pclk_vi_rtc_test 1 1 0 24000000 0 0 50000

clk_tsadc_tsen 1 1 0 12000000 0 0 50000

clk_tsadc 1 1 0 1000000 0 0 50000

clk_user_otpc_s 0 0 0 12000000 0 0 50000

clk_sbpi_otpc_s 0 0 0 24000000 0 0 50000

clk_pmc_otp 0 0 0 24000000 0 0 50000

clk_user_otpc_ns 0 0 0 12000000 0 0 50000

clk_sbpi_otpc_ns 0 0 0 24000000 0 0 50000

clk_otpc_arb 0 0 0 24000000 0 0 50000

clk_macphy 1 1 0 24000000 0 0 50000

dbclk_gpio2 0 0 0 24000000 0 0 50000

clk_sdmmc_detn_flt 0 0 0 24000000 0 0 50000

cclk_src_sdmmc 1 1 0 800000 0 0 50000

sdmmc_sample 0 0 0 400000 0 0 50000

sdmmc_drv 0 0 0 400000 0 90 50000

dbclk_gpio3 0 0 0 24000000 0 0 50000

dbclk_gpio1 0 0 0 24000000 0 0 50000

clk_uart_detn_flt 0 0 0 24000000 0 0 50000

tclk_pmu_wdt 0 0 0 24000000 0 0 50000

clk_refout 0 0 0 24000000 0 0 50000

clk_pvtm_pmu 0 0 0 24000000 0 0 50000

clk_pmu_mcu_rtc 0 0 0 24000000 0 0 50000

dbclk_pmu_gpio0 0 0 0 24000000 0 0 50000

clk_pmu 1 1 0 24000000 0 0 50000

clk_ddr_fail_safe 0 0 0 24000000 0 0 50000

clk_rtc32k_frac 0 0 0 32768 0 0 50000

clk_rtc_32k 0 0 0 32768 0 0 50000

tclk_wdt_s 0 0 0 24000000 0 0 50000

tclk_wdt_ns 0 0 0 24000000 0 0 50000

clk_ref_usbphy 2 2 0 24000000 0 0 50000

clk_usbphy_480m 1 1 0 480000000 0 0 50000

clk_ref_usbotg 1 1 0 24000000 0 0 50000

clk_saradc 1 1 0 3000000 0 0 50000

clk_capture_pwm2_peri 0 0 0 24000000 0 0 50000

clk_capture_pwm1_peri 0 0 0 24000000 0 0 50000

clk_timer_root 2 2 0 24000000 0 0 50000

clk_timer5 1 1 0 24000000 0 0 50000

clk_timer4 0 0 0 24000000 0 0 50000

clk_timer3 0 0 0 24000000 0 0 50000

clk_timer2 0 0 0 24000000 0 0 50000

clk_timer1 0 0 0 24000000 0 0 50000

clk_timer0 0 0 0 24000000 0 0 50000

clk_stimer1 0 0 0 24000000 0 0 50000

clk_stimer0 0 0 0 24000000 0 0 50000

clk_capture_pwm0_peri 0 0 0 24000000 0 0 50000

dbclk_gpio4 0 0 0 24000000 0 0 50000

cclk_src_emmc 0 0 0 400000 0 0 50000

emmc_sample 0 0 0 200000 0 0 50000

emmc_drv 0 0 0 200000 0 180 50000

clk_timer_ddrmon 0 0 0 24000000 0 0 50000

clk_vicap_m1 1 1 0 24000000 0 0 50000

sclk_vicap_m1 1 1 0 24000000 0 0 50000

clk_vicap_m0 1 1 0 24000000 0 0 50000

sclk_vicap_m0 1 1 0 24000000 0 0 50000

clk_uart5 0 0 0 24000000 0 0 50000

sclk_uart5 0 0 0 24000000 0 0 50000

clk_uart4 0 0 0 24000000 0 0 50000

sclk_uart4 0 0 0 24000000 0 0 50000

clk_uart3 0 0 0 24000000 0 0 50000

sclk_uart3 0 0 0 24000000 0 0 50000

clk_uart2 1 1 0 24000000 0 0 50000

sclk_uart2 1 1 0 24000000 0 0 50000

clk_uart1 0 0 0 24000000 0 0 50000

sclk_uart1 0 0 0 24000000 0 0 50000

clk_uart0 0 0 0 24000000 0 0 50000

sclk_uart0 0 0 0 24000000 0 0 50000

clk_ref_mipi1 0 0 0 24000000 0 0 50000

mclk_ref_mipi1 0 0 0 24000000 0 0 50000

clk_core_mcu_rtc 1 1 0 24000000 0 0 50000

clk_pvtm_core 0 0 0 24000000 0 0 50000

xin_osc0_half 0 0 0 12000000 0 0 50000

i2s0_8ch_mclkout 0 0 0 12000000 0 0 50000

pll_gpll 1 1 0 1188000000 0 0 50000

gpll 12 12 0 1188000000 0 0 50000

clk_vicap_m1_src 0 0 0 594000000 0 0 50000

clk_vicap_m1_frac 0 0 0 12000000 0 0 50000

clk_vicap_m0_src 0 0 0 594000000 0 0 50000

clk_vicap_m0_frac 0 0 0 12000000 0 0 50000

clk_uart5_src 0 0 0 594000000 0 0 50000

clk_uart5_frac 0 0 0 12000000 0 0 50000

clk_uart4_src 0 0 0 594000000 0 0 50000

clk_uart4_frac 0 0 0 12000000 0 0 50000

clk_uart3_src 0 0 0 594000000 0 0 50000

clk_uart3_frac 0 0 0 12000000 0 0 50000

clk_uart2_src 0 0 0 594000000 0 0 50000

clk_uart2_frac 0 0 0 12000000 0 0 50000

clk_uart1_src 0 0 0 594000000 0 0 50000

clk_uart1_frac 0 0 0 12000000 0 0 50000

clk_uart0_src 0 0 0 594000000 0 0 50000

clk_uart0_frac 0 0 0 12000000 0 0 50000

clk_ref_mipi1_src 0 0 0 594000000 0 0 50000

clk_ref_mipi1_frac 0 0 0 12000000 0 0 50000

clk_ref_mipi0_src 1 1 0 594000000 0 0 50000

clk_ref_mipi0_frac 1 1 0 27000000 0 0 50000

clk_ref_mipi0 1 1 0 27000000 0 0 50000

mclk_ref_mipi0 1 1 0 27000000 0 0 50000

clk_i2s0_8ch_rx_src 1 1 0 594000000 0 0 50000

clk_i2s0_8ch_rx_frac 1 1 0 2048000 0 0 50000

clk_i2s0_8ch_rx 1 1 0 2048000 0 0 50000

mclk_i2s0_8ch_rx 1 1 0 2048000 0 0 50000

clk_i2s0_8ch_tx_src 1 1 0 594000000 0 0 50000

clk_i2s0_8ch_tx_frac 1 1 0 2048000 0 0 50000

clk_i2s0_8ch_tx 1 1 0 2048000 0 0 50000

mclk_i2s0_8ch_tx 2 2 0 2048000 0 0 50000

mclk_sai 0 0 0 2048000 0 0 50000

mclk_dsm 0 0 0 2048000 0 0 50000

mclk_acodec_tx 1 1 0 2048000 0 0 50000

clk_450m_src 1 1 0 475200000 0 0 50000

clk_400m_src 4 4 0 396000000 0 0 50000

cclk_src_sdio 0 0 0 396000000 0 0 50000

sdio_sample 0 0 0 198000000 0 0 50000

sdio_drv 0 0 0 198000000 0 180 50000

clk_core_rga2e 0 0 0 396000000 0 0 50000

aclk_vo_root 1 1 0 396000000 0 0 50000

aclk_rga2e 0 0 0 396000000 0 0 50000

aclk_vepu_com_root 1 1 0 396000000 0 0 50000

dclk_decom 0 0 0 396000000 0 0 50000

aclk_peri_root 1 1 0 396000000 0 0 50000

aclk_ive 0 0 0 396000000 0 0 50000

aclk_decom 0 0 0 396000000 0 0 50000

clk_339m_src 4 4 0 339428572 0 0 50000

clk_core_isp3p2 1 1 0 339428572 0 0 50000

dclk_vicap 1 1 0 339428572 0 0 50000

aclk_vi_root 3 3 0 339428572 0 0 50000

aclk_vicap 1 1 0 339428572 0 0 50000

aclk_isp3p2 1 1 0 339428572 0 0 50000

clk_300m_src 5 5 0 297000000 0 0 50000

sclk_sfc 0 0 0 74250000 0 0 50000

aclk_vop_root 1 1 0 297000000 0 0 50000

aclk_vop 1 1 0 297000000 0 0 50000

aclk_mac_root 1 1 0 297000000 0 0 50000

aclk_mac 1 1 0 297000000 0 0 50000

aclk_vepu_root 2 2 0 297000000 0 0 50000

aclk_vepu_pp 0 0 0 297000000 0 0 50000

aclk_vepu 1 1 0 297000000 0 0 50000

clk_pka_crypto 0 0 0 297000000 0 0 50000

clk_core_crypto 0 0 0 297000000 0 0 50000

aclk_bus_root 3 3 0 297000000 0 0 50000

aclk_usbotg 1 1 0 297000000 0 0 50000

aclk_dmac 1 1 0 297000000 0 0 50000

aclk_crypto 0 0 0 297000000 0 0 50000

clk_200m_src 6 8 0 198000000 0 0 50000

hclk_vo_root 2 2 0 198000000 0 0 50000

hclk_vop 1 1 0 198000000 0 0 50000

hclk_sdio 0 0 0 198000000 0 0 50000

hclk_rga2e 0 0 0 198000000 0 0 50000

clk_core_vepu_dvbm 0 0 0 198000000 0 0 50000

clk_spi0 0 0 0 198000000 0 0 50000

hclk_vepu_root 2 2 0 198000000 0 0 50000

hclk_vepu_pp 0 0 0 198000000 0 0 50000

hclk_vepu 1 1 0 198000000 0 0 50000

clk_i2c1 0 1 0 198000000 0 0 50000

hclk_pmu_root 1 1 0 198000000 0 0 50000

hclk_pmu_sram 0 0 0 198000000 0 0 50000

clk_pmu_mcu 0 0 0 198000000 0 0 50000

clk_100m_pmu 1 1 0 99000000 0 0 50000

pclk_pmu_root 3 4 0 99000000 0 0 50000

pclk_pmu_wdt 0 0 0 99000000 0 0 50000

pclk_pvtm_pmu 0 0 0 99000000 0 0 50000

pclk_pmu_mailbox 0 0 0 99000000 0 0 50000

pclk_i2c1 0 1 0 99000000 0 0 50000

pclk_pmu_gpio0 1 1 0 99000000 0 0 50000

pclk_pmu 1 1 0 99000000 0 0 50000

clk_i2c4 0 1 0 198000000 0 0 50000

clk_i2c3 0 0 0 198000000 0 0 50000

clk_i2c2 0 0 0 198000000 0 0 50000

clk_i2c0 0 0 0 198000000 0 0 50000

hclk_peri_root 2 2 0 198000000 0 0 50000

hclk_trng_s 0 0 0 198000000 0 0 50000

hclk_trng_ns 0 0 0 198000000 0 0 50000

hclk_sai 0 0 0 198000000 0 0 50000

hclk_bootrom 0 0 0 198000000 0 0 50000

hclk_sfc 0 0 0 198000000 0 0 50000

hclk_ive 0 0 0 198000000 0 0 50000

hclk_i2s0 1 1 0 198000000 0 0 50000

hclk_emmc 0 0 0 198000000 0 0 50000

hclk_crypto 0 0 0 198000000 0 0 50000

clk_150m_src 5 5 0 148500000 0 0 50000

pclk_vo_root 4 4 0 148500000 0 0 50000

pclk_tsadc 1 1 0 148500000 0 0 50000

pclk_otp_mask 0 0 0 148500000 0 0 50000

pclk_otpc_s 0 0 0 148500000 0 0 50000

pclk_otpc_ns 0 0 0 148500000 0 0 50000

pclk_mac 2 2 0 148500000 0 0 50000

pclk_gpio2 1 1 0 148500000 0 0 50000

pclk_vi_root 4 4 0 148500000 0 0 50000

pclk_mipicsiphy 1 1 0 148500000 0 0 50000

pclk_gpio3 1 1 0 148500000 0 0 50000

pclk_csihost1 0 0 0 148500000 0 0 50000

pclk_csihost0 1 1 0 148500000 0 0 50000

hclk_vi_root 4 4 0 148500000 0 0 50000

hclk_vicap 1 1 0 148500000 0 0 50000

hclk_sdmmc 1 1 0 148500000 0 0 50000

hclk_isp3p2 1 1 0 148500000 0 0 50000

hclk_npu_root 2 2 0 148500000 0 0 50000

hclk_rknn 1 1 0 148500000 0 0 50000

clk_core_mcu 1 1 0 297000000 0 0 50000

hclk_cpu 1 1 0 198000000 0 0 50000

pll_cpll 1 1 0 1000000000 0 0 50000

cpll 5 5 0 1000000000 0 0 50000

dclk_vop_src 1 1 0 50000000 0 0 50000

dclk_vop 1 1 0 50000000 0 0 50000

clk_500m_src 2 2 0 500000000 0 0 50000

aclk_ddr_root 2 2 0 500000000 0 0 50000

aclk_sys_shrm 1 1 0 500000000 0 0 50000

clk_250m_src 1 1 0 250000000 0 0 50000

clk_100m_src 7 7 0 100000000 0 0 50000

pclk_vepu_root 2 2 0 100000000 0 0 50000

pclk_gpio1 1 1 0 100000000 0 0 50000

pclk_spi0 0 0 0 100000000 0 0 50000

clk_pwm2_peri 0 0 0 100000000 0 0 50000

clk_pwm1_peri 0 0 0 100000000 0 0 50000

clk_pwm0_peri 2 2 0 100000000 0 0 50000

pclk_peri_root 7 9 0 100000000 0 0 50000

pclk_wdt_s 0 0 0 100000000 0 0 50000

pclk_wdt_ns 0 0 0 100000000 0 0 50000

pclk_usbphy 1 1 0 100000000 0 0 50000

pclk_uart5 0 0 0 100000000 0 0 50000

pclk_uart4 0 0 0 100000000 0 0 50000

pclk_uart3 0 0 0 100000000 0 0 50000

pclk_uart2 1 1 0 100000000 0 0 50000

pclk_timer 1 1 0 100000000 0 0 50000

pclk_stimer 0 0 0 100000000 0 0 50000

pclk_spi1 0 0 0 100000000 0 0 50000

pclk_saradc 1 1 0 100000000 0 0 50000

pclk_pwm2_peri 0 0 0 100000000 0 0 50000

pclk_pwm1_peri 0 0 0 100000000 0 0 50000

pclk_uart1 0 0 0 100000000 0 0 50000

pclk_uart0 0 0 0 100000000 0 0 50000

pclk_pwm0_peri 0 2 0 100000000 0 0 50000

pclk_dft2apb 0 0 0 100000000 0 0 50000

pclk_i2c4 0 1 0 100000000 0 0 50000

pclk_i2c3 0 0 0 100000000 0 0 50000

pclk_i2c2 0 0 0 100000000 0 0 50000

pclk_i2c0 0 0 0 100000000 0 0 50000

pclk_gpio4 1 1 0 100000000 0 0 50000

pclk_dsm 0 0 0 100000000 0 0 50000

pclk_decom 0 0 0 100000000 0 0 50000

pclk_acodec 1 1 0 100000000 0 0 50000

pclk_npu_root 1 1 0 100000000 0 0 50000

pclk_ddr_root 2 2 0 100000000 0 0 50000

pclk_dfictrl 1 1 0 100000000 0 0 50000

pclk_ddrc 0 0 0 100000000 0 0 50000

pclk_ddrmon 0 0 0 100000000 0 0 50000

pclk_ddr_hwlp 0 0 0 100000000 0 0 50000

pclk_ddrphy 0 0 0 100000000 0 0 50000

pclk_top_root 1 1 0 100000000 0 0 50000

clk_50m_src 2 2 0 50000000 0 0 50000

clk_gmac0_50m_o 2 2 0 50000000 0 0 50000

clk_gmac0_tx_50m_o 1 1 0 50000000 0 0 50000

clk_gmac0_ref_50m 1 1 0 50000000 0 0 50000

clk_spi1 0 0 0 50000000 0 0 50000

pll_dpll 1 1 0 924000000 0 0 50000

dpll 1 1 0 924000000 0 0 50000

clk_core_ddrc_src 2 2 0 462000000 0 0 50000

clk_core_ddrc 1 1 0 462000000 0 0 50000

aclk_ddrc 1 1 0 462000000 0 0 50000

clk_ddr_phy 0 0 0 462000000 0 0 50000

clk_ddrmon 0 0 0 462000000 0 0 50000

clk_dfictrl 0 0 0 462000000 0 0 50000

pll_apll 1 1 0 1608000000 0 0 50000

apll 1 1 0 1608000000 0 0 50000

armclk 1 1 0 1608000000 0 0 50000

pclk_dbg 2 2 0 201000000 0 0 50000

pclk_cpu_root 2 2 0 201000000 0 0 50000

pclk_mailbox 1 1 0 201000000 0 0 50000

clk_pvtpll_1 1 1 0 420000000 0 0 50000

aclk_npu_root 2 2 0 420000000 0 0 50000

aclk_rknn 1 1 0 420000000 0 0 50000

clk_pvtpll_0 1 1 0 410000000 0 0 50000

clk_core_vepu 1 1 0 410000000 0 0 50000

clk_utmi_usbotg 1 1 0 0 0 0 50000

sclk_in_spi0 0 0 0 0 0 0 50000

pclk_vicap_vepu 1 1 0 0 0 0 50000

clk_rxbyteclkhs_1 0 0 0 0 0 0 50000

clk_rxbyteclkhs_0 1 1 0 0 0 0 50000

pclk_vicap 1 1 0 0 0 0 50000

i1clk_vicap 1 1 0 0 0 0 50000

i0clk_vicap 1 1 0 0 0 0 50000

isp0clk_vicap 2 2 0 0 0 0 50000

rx1pclk_vicap 1 1 0 0 0 0 50000

rx0pclk_vicap 1 1 0 0 0 0 50000离线

楼主 #17 2022-08-09 20:01:28 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

搞定linux系统所有功能,跑个lvgl8先。

离线

楼主 #18 2022-08-10 15:56:21 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

上传个LVGL触摸的操作视频,1024X600的分辨率

离线

#19 2022-08-10 21:21:51 分享评论

- Timaker

- 会员

- 注册时间: 2020-05-18

- 已发帖子: 65

- 积分: 43.5

Re: RV1103/RV1106 裸奔日记

大佬tql

离线

楼主 #20 2022-08-11 18:10:12 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

RV1103 / RV1106 裸奔已支持SPI NOR FLASH以及SPI NAND FLASH引导

SPI NOR FLASH烧录指令 (offset = 0x00020000, sector = 256)

sudo xrock maskrom rv1106_ddr_924MHz_v1.09.bin rv1106_usbplug_v1.03.bin --rc4-off;

sleep 3;

sudo xrock flash write 256 xbootpak.bin;

sudo xrock reset;SPI NAND FLASH烧录指令 (offset = 0x00040000, sector = 512)

sudo xrock maskrom rv1106_ddr_924MHz_v1.09.bin rv1106_usbplug_v1.03.bin --rc4-off;

sleep 3;

sudo xrock flash write 512 xbootpak.bin;

sudo xrock reset;离线

楼主 #21 2022-08-11 18:18:58 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

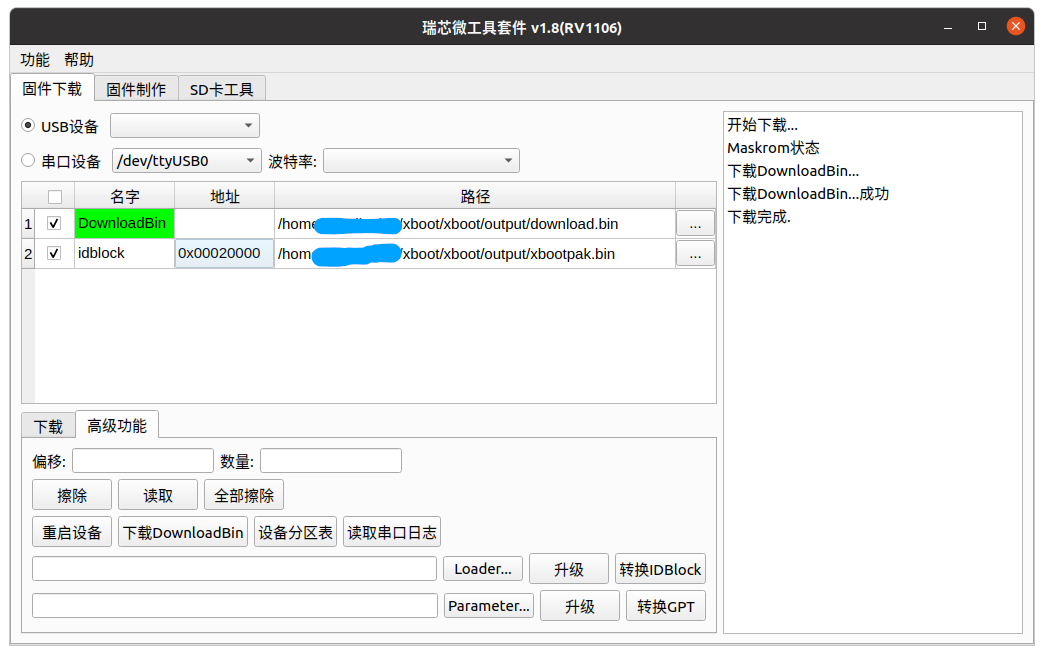

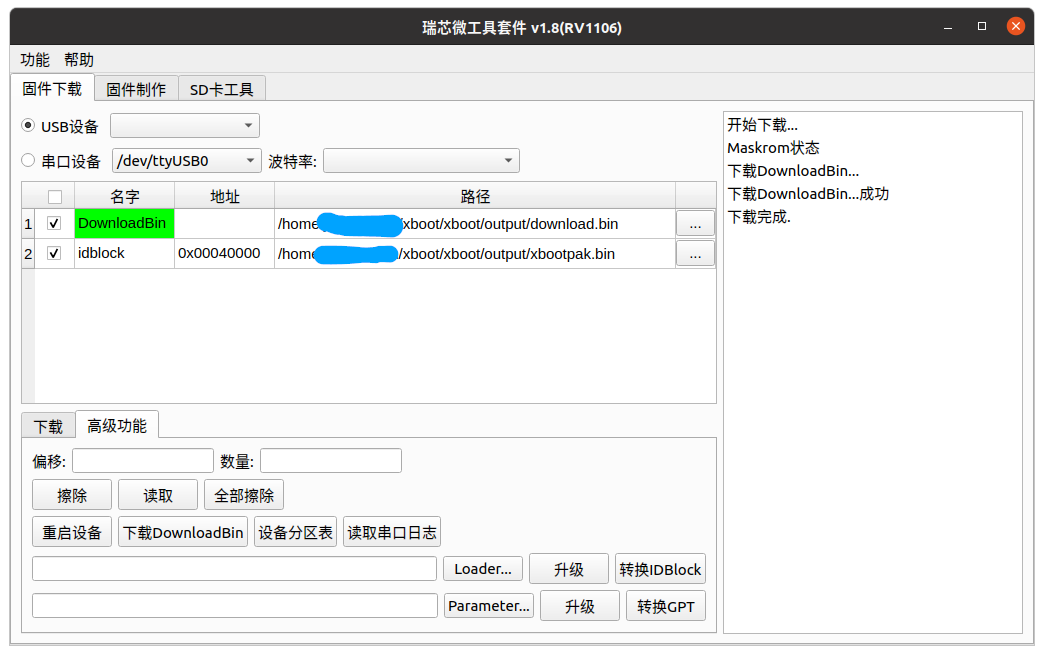

当然,除了使用XROCK工具进行烧写之外,还可以利用《瑞芯微工具套件 1.8》进行烧写裸机程序。

两种烧写方法原理是一样的,如果是windows平台,注意下,两者的驱动是不一样的。

spi nor flash 烧写

spi nand flash 烧写

离线

楼主 #22 2022-08-11 18:33:24 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

虽然,未进行EMMC引导测试,但根据分析,如果需要用EMMC介质进行裸奔,烧写指令会是如下方式:

EMMC烧录指令 (offset = 0x00080000, sector = 1024)

sudo xrock maskrom rv1106_ddr_924MHz_v1.09.bin rv1106_usbplug_v1.03.bin --rc4-off;

sleep 3;

sudo xrock flash write 1024 xbootpak.bin;

sudo xrock reset;离线

楼主 #23 2022-08-11 18:42:07 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

EMMC引导肯定是可以支持的,只不过现在因为硬件限制,无法进行测试,那么疑问来了。

RV1103/RV1106是否能支持SD NAND引导呢,至少这种玩意有一定的性价比,特别是容量有要求时,优势会比较明显。

SPI NAND 最大容量是4Gbit

SD NAND 最大容量是8Gbit

EMMC这玩意最小得4GB

离线

楼主 #24 2022-08-12 16:37:33 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

对于RV1106支持SD NAND有个比较棘手的问题,RK默认EMMC启动使用200MHZ的时钟,而SD NAND基本不够格,从这一点来说RV1106是无法使用SD NAND做引导介质的

但是否可以修改EMMC时钟频率,这个就不敢肯定了

烧录不行,引导启动肯定也是不行的

离线

楼主 #25 2022-08-18 09:14:48 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

继续RV1106的裸奔,在编写看门狗驱动,发现时间到了后,并不能复位芯片,有一个机关,必须在启动时执行如下代码

/*

* Release the watchdog

*/

write32(0xff000000 + 0x0004, 0x2000200);

write32(0xff3b0000 + 0x0c10, 0x400040);现在没TRM手册,也搞不清是啥意思,先能用就行,顺便来个sys_cpu_init函数吧,start.S里调用下,免得后面还有一堆未知的依赖。

void sys_cpu_init(void)

{

/*

* Set all devices to Non-secure

*/

write32(0xff070000 + 0x0020, 0xffff0000);

write32(0xff070000 + 0x0024, 0xffff0000);

write32(0xff070000 + 0x0028, 0xffff0000);

write32(0xff070000 + 0x002c, 0xffff0000);

write32(0xff070000 + 0x0030, 0xffff0000);

write32(0xff070000 + 0x00bc, 0x000f0000);

write32(0xff076000 + 0x0020, 0xffff0000);

write32(0xff076000 + 0x0024, 0xffff0000);

write32(0xff076000 + 0x0028, 0xffff0000);

write32(0xff076000 + 0x002c, 0xffff0000);

write32(0xff076000 + 0x0030, 0xffff0000);

write32(0xff076000 + 0x0040, 0x00030002);

write32(0xff080000, 0x20000000);

/*

* Set the emmc and fspi to access secure area

*/

write32(0xff900000 + 0x4c, 0x00000000);

write32(0xff910000 + 0x44, 0xff00ffff);

/*

* Set fspi clk 6mA

*/

write32(0xff568000 + 0x0030, 0x0f000700);

/*

* Set the USB2 PHY in suspend mode and turn off the

* USB2 PHY FS/LS differential receiver to save power

*/

write32(0xff000000 + 0x0050, 0x01ff01d1);

write32(0xff3e0000 + 0x0100, 0x00000000);

/*

* Release the watchdog

*/

write32(0xff000000 + 0x0004, 0x2000200);

write32(0xff3b0000 + 0x0c10, 0x400040);

/*

* When venc/npu use pvtpll, reboot will fail, because

* pvtpll is reset before venc/npu reset, so venc/npu

* is not completely reset, system will block when access

* NoC in SPL.

*/

write32(0xff3b0000 + 0x1008, 0xffff0018);

write32(0xff3b0000 + 0x1000, 0x00030003);

write32(0xff3b0000 + 0x1038, 0xffff0018);

write32(0xff3b0000 + 0x1030, 0x00030003);

sdelay(20);

/*

* Limits npu max transport packets to 4 for route to scheduler,

* give much more chance for other controllers to access memory.

*/

write32(0xff140080 + 0x0008, 0x4);

/*

* Improve VENC QOS PRIORITY

*/

write32(0xff150000 + 0x0008, 0x303);

}最近编辑记录 xboot (2022-08-18 09:15:24)

离线

楼主 #26 2022-08-18 09:18:08 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

在没有TRM手册情况下,只能参考官方SDK,一点点来编写各种驱动了,算慢慢翻译吧,CLOCK,RESET,GPIO,IRQ,TIMER,这些都得慢慢翻译过来

离线

楼主 #27 2022-08-18 09:23:27 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

RV1106应该带了6个timer,但翻遍SDK,没能找到TIMER的基地址,有个0xff660000这个地址,貌似是基地址,但查看IP版本号又对不上,额,如果不能用TIMER,只能去用cortex-a7自带的timer实现tickless驱动了。

离线

楼主 #29 2022-08-18 11:38:23 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

已实现timer的中断支持,还算利用cortex-a7的timer了,核心代码如下:

#define armv7_read_cntpctl() ({ u32_t val; __asm__ __volatile__("mrc p15, 0, %0, c14, c2, 1" : "=r" (val)); val; })

#define armv7_write_cntpctl(val) __asm__ __volatile__("mcr p15, 0, %0, c14, c2, 1\nisb sy\n" : : "r" (val));

static inline void armv7_timer_start(void)

{

u32_t ctrl = armv7_read_cntpctl();

if(!(ctrl & (1 << 0)))

{

ctrl |= (1 << 0);

armv7_write_cntpctl(ctrl);

}

}

static inline void armv7_timer_stop(void)

{

u32_t ctrl = armv7_read_cntpctl();

if((ctrl & (1 << 0)))

{

ctrl &= ~(1 << 0);

armv7_write_cntpctl(ctrl);

}

}

static inline void armv7_timer_interrupt_enable(void)

{

u32_t ctrl = armv7_read_cntpctl();

if(ctrl & (1 << 1))

{

ctrl &= ~(1 << 1);

armv7_write_cntpctl(ctrl);

}

}

static inline void armv7_timer_interrupt_disable(void)

{

u32_t ctrl = armv7_read_cntpctl();

if(!(ctrl & (1 << 1)))

{

ctrl |= (1 << 1);

armv7_write_cntpctl(ctrl);

}

}

static inline u64_t armv7_timer_frequecy(void)

{

u32_t v;

__asm__ __volatile__("mrc p15, 0, %0, c14, c0, 0" : "=r" (v));

return (v != 0) ? (u64_t)v : 1000000;

}

static inline u64_t armv7_timer_read(void)

{

u32_t l, h;

__asm__ __volatile__("mrrc p15, 0, %0, %1, c14" : "=r" (l), "=r" (h));

return ((u64_t)h << 32) | l;

}

static inline void armv7_timer_compare(uint64_t interval)

{

u64_t last = armv7_timer_read() + interval;

__asm__ __volatile__("mcrr p15, 2, %Q0, %R0, c14" : : "r" (last));

}PPI里面timer中断有4个

#define RV1106_IRQ_HYPERVISOR_TIMER (26)

#define RV1106_IRQ_VIRTUAL_TIMER (27)

#define RV1106_IRQ_SECURE_PHYSICAL_TIMER (29)

#define RV1106_IRQ_NONSECURE_PHYSICAL_TIMER (30)现在需要申请29号中断才可以触发,仅申请30号中断,无法触发,从这一点来看,现在代码运行在加密模式?

引导过程大概如下:

BOOTROM -> DDR.BIN -> XBOOT

BOOTROM 和 DDR.BIN,前在运行在加密模式的可能性比较低,后者很有可能。现在还没有对当前CPU运行模式摸个底。

离线

楼主 #30 2022-08-18 11:44:26 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

关于timer的运行模式,看linux内核,有些平台4个中断全部一起注册,额,这是增强适应性吧。

timer {

compatible = "arm,armv7-timer";

interrupts = <GIC_PPI 13 (GIC_CPU_MASK_SIMPLE(4) | IRQ_TYPE_LEVEL_HIGH)>,

<GIC_PPI 14 (GIC_CPU_MASK_SIMPLE(4) | IRQ_TYPE_LEVEL_HIGH)>,

<GIC_PPI 11 (GIC_CPU_MASK_SIMPLE(4) | IRQ_TYPE_LEVEL_HIGH)>,

<GIC_PPI 10 (GIC_CPU_MASK_SIMPLE(4) | IRQ_TYPE_LEVEL_HIGH)>;

clock-frequency = <24000000>;

};PPI 中断号从16开始,对应就是上面的26,27,29,30,四个中断号

离线

楼主 #31 2022-08-18 11:59:29 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

RV1106内部自带的6个timer不可见,其还带了两个加密模式的stimer,严重怀疑当前CPU工作在加密模式,导致其不可见,当然加密模式的stimer,现在不知道其基地址,所以也无从确认起。

关于搜寻timer基地址,本来是想通过 TIMER_REVISION_6CH = 0x11970006 或 TIMER_REVISION_2CH = 0x11970002 这两个关键信息,写了个程序来遍历的,但访问某些地址空间,触发访问异常,无法继续搜寻,所以,这个思路就没有继续了。

理论上是可以对异常进行处理后,再继续搜寻的。这个问题先放弃了,采用CORTEX-A7内部自带的,也更通用点,实现功能就行,不纠结了。

离线

楼主 #32 2022-08-18 16:05:12 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

RESET驱动,GIC400中断驱动,TICKLESS驱动,GPIO驱动已经编写完了,基本是依据linux里的RV1106相关代码翻译而成。

现在也编写好了GPIO 中断驱动,但发现还是未能触发中断,普通的输入,输出等操作都是OK的。不知哪里还有坑,先放一放。

离线

楼主 #33 2022-08-18 19:01:21 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

编写SARADC驱动,测试通过,其寄存器跟RK3588一致。

https://github.com/xboot/xboot/blob/master/src/arch/arm32/mach-rv1106/driver/adc-rv1106.c

离线

楼主 #34 2022-08-18 19:09:11 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

基于ADC驱动,添加ADC按键驱动,添加如下设备树即可。

"key-adc@0": {

"adc-name": "adc-rv1106.0",

"adc-channel": 0,

"poll-interval-ms": 100,

"keys": [

{ "min-voltage": 0, "max-voltage": 100000, "key-code": 11 }

]

},xboot: /# event

[key-adc.0]: [KeyDown] [11]

[key-adc.0]: [KeyUp] [11]

[key-adc.0]: [KeyDown] [11]

[key-adc.0]: [KeyUp] [11]

[key-adc.0]: [KeyDown] [11]

[key-adc.0]: [KeyUp] [11]

[key-adc.0]: [KeyDown] [11]

[key-adc.0]: [KeyUp] [11]

[key-adc.0]: [KeyDown] [11]

[key-adc.0]: [KeyUp] [11]

[key-adc.0]: [KeyDown] [11]

[key-adc.0]: [KeyUp] [11]

[key-adc.0]: [KeyDown] [11]

[key-adc.0]: [KeyUp] [11]

[key-adc.0]: [KeyDown] [11]

[key-adc.0]: [KeyUp] [11]

[key-adc.0]: [KeyDown] [11]

[key-adc.0]: [KeyUp] [11]离线

楼主 #35 2022-08-19 10:48:17 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

实现RV1106的RTC驱动

/*

* driver/rtc-rv1106.c

*

* Copyright(c) 2007-2022 Jianjun Jiang <8192542@qq.com>

* Official site: http://xboot.org

* Mobile phone: +86-18665388956

* QQ: 8192542

*

* Permission is hereby granted, free of charge, to any person obtaining a copy

* of this software and associated documentation files (the "Software"), to deal

* in the Software without restriction, including without limitation the rights

* to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

* copies of the Software, and to permit persons to whom the Software is

* furnished to do so, subject to the following conditions:

*

* The above copyright notice and this permission notice shall be included in all

* copies or substantial portions of the Software.

*

* THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

* IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

* FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

* AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

* LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

* OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE

* SOFTWARE.

*

*/

#include <xboot.h>

#include <clk/clk.h>

#include <rtc/rtc.h>

enum {

RTC_SET_SECONDS = 0x00,

RTC_SET_MINUTES = 0x04,

RTC_SET_HOURS = 0x08,

RTC_SET_DAYS = 0x0c,

RTC_SET_MONTHS = 0x10,

RTC_SET_YEARL = 0x14,

RTC_SET_YEARH = 0x18,

RTC_SET_WEEKS = 0x1c,

RTC_ALARM_SECONDS = 0x20,

RTC_ALARM_MINUTES = 0x24,

RTC_ALARM_HOURS = 0x28,

RTC_ALARM_DAYS = 0x2c,

RTC_ALARM_MONTHS = 0x30,

RTC_ALARM_YEARL = 0x34,

RTC_ALARM_YEARH = 0x38,

RTC_CTRL = 0x3C,

RTC_STATUS0 = 0x40,

RTC_STATUS1 = 0x44,

RTC_INT0_EN = 0x48,

RTC_INT1_EN = 0x4c,

RTC_MSEC_CTRL = 0x50,

RTC_MSEC_CNT = 0x54,

RTC_COMP_H = 0x58,

RTC_COMP_D = 0x5c,

RTC_COMP_M = 0x60,

RTC_ANALOG_CTRL = 0x64,

RTC_ANALOG_TEST = 0x68,

RTC_LDO_CTRL = 0x6c,

RTC_XO_TRIM0 = 0x70,

RTC_XO_TRIM1 = 0x74,

RTC_VPTAT_TRIM = 0x78,

RTC_ANALOG_EN = 0x7c,

RTC_CLK32K_TEST = 0x80,

RTC_TEST_ST = 0x84,

RTC_TEST_LEN = 0x88,

RTC_CNT_0 = 0x8c,

RTC_CNT_1 = 0x90,

RTC_CNT_2 = 0x94,

RTC_CNT_3 = 0x98,

};

struct rtc_rv1106_pdata_t {

virtual_addr_t virt;

char * clk;

};

static void rtc_update_bits(virtual_addr_t virt, u32_t offset, u32_t mask, u32_t set)

{

u32_t val;

val = read32(virt + offset);

write32(virt + offset, (val & ~mask) | set | 0xc4522900);

}

static bool_t rtc_rv1106_settime(struct rtc_t * rtc, struct rtc_time_t * time)

{

struct rtc_rv1106_pdata_t * pdat = (struct rtc_rv1106_pdata_t *)rtc->priv;

u32_t rtc_data[8];

u32_t status;

int yearh, yearl;

int i;

rtc_data[0] = bin2bcd(time->second) | 0xc4522900;

rtc_data[1] = bin2bcd(time->minute) | 0xc4522900;

rtc_data[2] = bin2bcd(time->hour) | 0xc4522900;

rtc_data[3] = bin2bcd(time->day) | 0xc4522900;

rtc_data[4] = bin2bcd(time->month) | 0xc4522900;

if(time->year > 199)

{

yearh = (time->year - 100) / 100;

yearl = time->year - 100 - yearh * 100;

}

else

{

yearh = 0;

yearl = time->year - 100 - yearh * 100;

}

rtc_data[5] = bin2bcd(yearl) | 0xc4522900;

rtc_data[6] = bin2bcd(yearh) | 0xc4522900;

rtc_data[7] = bin2bcd(time->week) | 0xc4522900;

rtc_update_bits(pdat->virt, RTC_CTRL, (1 << 0), 0);

do {

status = read32(pdat->virt + RTC_STATUS1);

udelay(1);

} while(status & (1 << 0));

for(i = 0; i < 8; i++)

write32(pdat->virt + RTC_SET_SECONDS + (i << 2), rtc_data[i]);

rtc_update_bits(pdat->virt, RTC_CTRL, (1 << 7) | (1 << 0), (1 << 7) | (1 << 0));

do {

status = read32(pdat->virt + RTC_STATUS1);

udelay(1);

} while(!(status & (1 << 0)));

return TRUE;

}

static bool_t rtc_rv1106_gettime(struct rtc_t * rtc, struct rtc_time_t * time)

{

struct rtc_rv1106_pdata_t * pdat = (struct rtc_rv1106_pdata_t *)rtc->priv;

u32_t rtc_data[8];

int i;

for(i = 0; i < 8; i++)

rtc_data[i] = read32(pdat->virt + RTC_SET_SECONDS + (i << 2));

for(i = 0; i < 8; i++)

rtc_data[i] = read32(pdat->virt + RTC_SET_SECONDS + (i << 2));

for(i = 0; i < 8; i++)

rtc_data[i] = read32(pdat->virt + RTC_SET_SECONDS + (i << 2));

time->second = bcd2bin(rtc_data[0] & 0x7f);

time->minute = bcd2bin(rtc_data[1] & 0x7f);

time->hour = bcd2bin(rtc_data[2] & 0x3f);

time->day = bcd2bin(rtc_data[3] & 0x3f);

time->month = bcd2bin(rtc_data[4] & 0x1f);

time->year = (bcd2bin(rtc_data[6] & 0xff)) * 100 + (bcd2bin(rtc_data[5] & 0xff)) + 100;

time->week = bcd2bin(rtc_data[7] & 0x07);

return TRUE;

}

static struct device_t * rtc_rv1106_probe(struct driver_t * drv, struct dtnode_t * n)

{

struct rtc_rv1106_pdata_t * pdat;

struct rtc_t * rtc;

struct device_t * dev;

virtual_addr_t virt = phys_to_virt(dt_read_address(n));

char * clk = dt_read_string(n, "clock-name", NULL);

if(!search_clk(clk))

return NULL;

pdat = malloc(sizeof(struct rtc_rv1106_pdata_t));

if(!pdat)

return NULL;

rtc = malloc(sizeof(struct rtc_t));

if(!rtc)

{

free(pdat);

return NULL;

}

pdat->virt = virt;

pdat->clk = strdup(clk);

rtc->name = alloc_device_name(dt_read_name(n), -1);

rtc->settime = rtc_rv1106_settime;

rtc->gettime = rtc_rv1106_gettime;

rtc->priv = pdat;

clk_enable(pdat->clk);

write32(phys_to_virt(0xff000000) + 0x50000, ((1 << 6) << 16) | (1 << 6));

rtc_update_bits(pdat->virt, RTC_VPTAT_TRIM, (1 << 4), (4 << 1));

rtc_update_bits(pdat->virt, RTC_ANALOG_EN, (1 << 1), 0x00);

rtc_update_bits(pdat->virt, RTC_LDO_CTRL, (1 << 0), (1 << 0));

rtc_update_bits(pdat->virt, RTC_ANALOG_EN, (1 << 5), (1 << 5));

rtc_update_bits(pdat->virt, RTC_CTRL, (1 << 0) | (1 << 7), (1 << 0) | (1 << 7));

if(!(dev = register_rtc(rtc, drv)))

{

clk_disable(pdat->clk);

free(pdat->clk);

free_device_name(rtc->name);

free(rtc->priv);

free(rtc);

return NULL;

}

return dev;

}

static void rtc_rv1106_remove(struct device_t * dev)

{

struct rtc_t * rtc = (struct rtc_t *)dev->priv;

struct rtc_rv1106_pdata_t * pdat = (struct rtc_rv1106_pdata_t *)rtc->priv;

if(rtc)

{

unregister_rtc(rtc);

clk_disable(pdat->clk);

free(pdat->clk);

free_device_name(rtc->name);

free(rtc->priv);

free(rtc);

}

}

static void rtc_rv1106_suspend(struct device_t * dev)

{

}

static void rtc_rv1106_resume(struct device_t * dev)

{

}

static struct driver_t rtc_rv1106 = {

.name = "rtc-rv1106",

.probe = rtc_rv1106_probe,

.remove = rtc_rv1106_remove,

.suspend = rtc_rv1106_suspend,

.resume = rtc_rv1106_resume,

};

static __init void rtc_rv1106_driver_init(void)

{

register_driver(&rtc_rv1106);

}

static __exit void rtc_rv1106_driver_exit(void)

{

unregister_driver(&rtc_rv1106);

}

driver_initcall(rtc_rv1106_driver_init);

driver_exitcall(rtc_rv1106_driver_exit);最近编辑记录 xboot (2022-08-19 10:48:55)

离线

楼主 #36 2022-08-19 10:54:48 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

现在已添加了不少裸机驱动,启动log如下:

DDR Version V1.09 20220630

f947

F

DDRConf2

DDR3, BW=16 Col=10 Bk=8 CS0 Row=13 CS=1 Die BW=16 Size=128MB

924MHz

DDR bin out

█████████████████████████

██ ▄▄▄▄▄ ██▄▀▀▀█ ▄▄▄▄▄ ██

██ █ █ █ ▀▄█ █ █ █ ██

██ █▄▄▄█ ██▄ ██ █▄▄▄█ ██

██▄▄▄▄▄▄▄█▄█ █ █▄▄▄▄▄▄▄██

████▀▄ ▀▄▄█ ▀█▄▀█▀▀ █▀██

███▀▄▀ ▀▄ ▄█▀▀▄▀█ ▀█ ▄███

███▄█▄█▄▄▄▀▀ ▄ ▀ ▄▄ ▀ ██

██ ▄▄▄▄▄ █▄ ▄█▄▀▄████▄▄██

██ █ █ █ ▀█▄█▄▄█ ▄▀█▄██

██ █▄▄▄█ ██▀ █ ▄▄▄▄█▄ ██

██▄▄▄▄▄▄▄███▄██▄▄▄▄▄▄▄███

█████████████████████████

_ _

_ _ | |___ _____ _____ _| |_

\ \/ /| _ | _ | _ |_ _| (C) 2007-2022

) ( | |_| | |_| | |_| | | |____JIANJUN.JIANG__

/_/\_\|_____|_____|_____| |_____________________|

V3.0.0 (Aug 19 2022 - 10:43:57) - [x1106][X1106 Based On RV1106 SOC]

[ 0.000020]Probe device 'blk-romdisk.0' with blk-romdisk

[ 0.000800]Probe device 'xin24m' with clk-fixed

[ 0.000810]Probe device 'xin32k' with clk-fixed

[ 0.000820]Probe device 'clk_rtc_32k' with clk-link

[ 0.000830]Probe device 'apll' with clk-rv1106-pll

[ 0.000840]Probe device 'cpll' with clk-rv1106-pll

[ 0.000850]Probe device 'dpll' with clk-rv1106-pll

[ 0.000860]Probe device 'gpll' with clk-rv1106-pll

[ 0.000870]Probe device 'clk_pvtm_core' with clk-rv1106-gate

[ 0.000880]Probe device 'clk_core_mcu_rtc' with clk-rv1106-gate

[ 0.000890]Probe device 'clk_timer_root' with clk-rv1106-gate

[ 0.000900]Probe device 'hclk_cpu' with clk-rv1106-comp

[ 0.000910]Probe device 'clk_core_mcu' with clk-rv1106-comp

[ 0.000920]Probe device 'clk_50m_src' with clk-rv1106-comp

[ 0.000930]Probe device 'clk_100m_src' with clk-rv1106-comp

[ 0.000940]Probe device 'clk_150m_src' with clk-rv1106-comp

[ 0.000950]Probe device 'clk_200m_src' with clk-rv1106-comp

[ 0.000960]Probe device 'clk_250m_src' with clk-rv1106-comp

[ 0.000970]Probe device 'clk_300m_src' with clk-rv1106-comp

[ 0.000980]Probe device 'clk_339m_src' with clk-rv1106-comp

[ 0.000990]Probe device 'clk_400m_src' with clk-rv1106-comp

[ 0.001000]Probe device 'clk_450m_src' with clk-rv1106-comp

[ 0.001010]Probe device 'clk_500m_src' with clk-rv1106-comp

[ 0.001020]Probe device 'pclk_top_root' with clk-rv1106-comp

[ 0.001030]Probe device 'pclk_peri_root' with clk-rv1106-comp

[ 0.001040]Probe device 'clk_100m_pmu' with clk-rv1106-divider

[ 0.001050]Probe device 'pclk_pmu_root' with clk-rv1106-comp

[ 0.001060]Probe device 'pclk_vi_rtc_root' with clk-rv1106-comp

[ 0.001070]Probe device 'pclk_vi_rtc_phy' with clk-rv1106-gate

[ 0.001080]Probe device 'pclk_vi_rtc_test' with clk-rv1106-gate

[ 0.001090]Probe device 'pclk_i2c0' with clk-rv1106-gate

[ 0.001100]Probe device 'clk_i2c0' with clk-rv1106-comp

[ 0.001110]Probe device 'pclk_i2c1' with clk-rv1106-gate

[ 0.001120]Probe device 'clk_i2c1' with clk-rv1106-comp

[ 0.001130]Probe device 'pclk_i2c2' with clk-rv1106-gate

[ 0.001140]Probe device 'clk_i2c2' with clk-rv1106-comp

[ 0.001150]Probe device 'pclk_i2c3' with clk-rv1106-gate

[ 0.001160]Probe device 'clk_i2c3' with clk-rv1106-comp

[ 0.001170]Probe device 'pclk_i2c4' with clk-rv1106-gate

[ 0.001180]Probe device 'clk_i2c4' with clk-rv1106-comp

[ 0.001190]Probe device 'pclk_timer' with clk-rv1106-gate

[ 0.001200]Probe device 'clk_timer0' with clk-rv1106-gate

[ 0.001210]Probe device 'clk_timer1' with clk-rv1106-gate

[ 0.001220]Probe device 'clk_timer2' with clk-rv1106-gate

[ 0.001230]Probe device 'clk_timer3' with clk-rv1106-gate

[ 0.001240]Probe device 'clk_timer4' with clk-rv1106-gate

[ 0.001250]Probe device 'clk_timer5' with clk-rv1106-gate

[ 0.001260]Probe device 'pclk_stimer' with clk-rv1106-gate

[ 0.001270]Probe device 'clk_stimer0' with clk-rv1106-gate

[ 0.001280]Probe device 'clk_stimer1' with clk-rv1106-gate

[ 0.001290]Probe device 'pclk_saradc' with clk-rv1106-gate

[ 0.001300]Probe device 'clk_saradc' with clk-rv1106-comp

[ 0.001310]Probe device 'clk_uart0_src' with clk-rv1106-comp

[ 0.001320]Probe device 'gate-clk_uart0_src' with clk-rv1106-gate

[ 0.001330]Probe device 'clk_uart0_frac' with clk-rv1106-factor

[ 0.001340]Probe device 'clk_uart0' with clk-rv1106-mux

[ 0.001350]Probe device 'link-uart0' with clk-link

[ 0.001360]Probe device 'link-uart1' with clk-link

[ 0.001370]Probe device 'link-uart2' with clk-link

[ 0.001380]Probe device 'link-uart3' with clk-link

[ 0.001390]Probe device 'link-uart4' with clk-link

[ 0.001400]Probe device 'link-uart5' with clk-link

[ 0.001410]Probe device 'link-wdt' with clk-link

[ 0.001420]Probe device 'reset-rv1106.0' with reset-rv1106

[ 0.001430]Probe device 'reset-rv1106.1' with reset-rv1106

[ 0.001440]Probe device 'reset-rv1106.2' with reset-rv1106

[ 0.001450]Probe device 'reset-rv1106.3' with reset-rv1106

[ 0.001460]Probe device 'reset-rv1106.4' with reset-rv1106

[ 0.001470]Probe device 'reset-rv1106.5' with reset-rv1106

[ 0.001480]Probe device 'reset-rv1106.6' with reset-rv1106

[ 0.001490]Probe device 'reset-rv1106.7' with reset-rv1106

[ 0.001500]Probe device 'reset-rv1106.8' with reset-rv1106

[ 0.001510]Probe device 'reset-rv1106.9' with reset-rv1106

[ 0.001520]Probe device 'reset-rv1106.10' with reset-rv1106

[ 0.001530]Probe device 'reset-rv1106.11' with reset-rv1106

[ 0.001540]Probe device 'reset-rv1106.12' with reset-rv1106

[ 0.001550]Probe device 'reset-rv1106.13' with reset-rv1106

[ 0.001560]Probe device 'reset-rv1106.14' with reset-rv1106

[ 0.001570]Probe device 'reset-rv1106.15' with reset-rv1106

[ 0.001580]Probe device 'reset-rv1106.16' with reset-rv1106

[ 0.001590]Probe device 'reset-rv1106.17' with reset-rv1106

[ 0.001600]Probe device 'reset-rv1106.18' with reset-rv1106

[ 0.001610]Probe device 'reset-rv1106.19' with reset-rv1106

[ 0.001620]Probe device 'reset-rv1106.20' with reset-rv1106

[ 0.001630]Probe device 'reset-rv1106.21' with reset-rv1106

[ 0.001640]Probe device 'reset-rv1106.22' with reset-rv1106

[ 0.001650]Probe device 'reset-rv1106.23' with reset-rv1106

[ 0.001660]Probe device 'reset-rv1106.24' with reset-rv1106

[ 0.001670]Probe device 'reset-rv1106.25' with reset-rv1106

[ 0.001680]Probe device 'reset-rv1106.26' with reset-rv1106

[ 0.001690]Probe device 'irq-gic400.0' with irq-gic400

[ 0.001700]Probe device 'irq-rv1106-gpio.0' with irq-rv1106-gpio

[ 0.001710]Probe device 'irq-rv1106-gpio.1' with irq-rv1106-gpio

[ 0.001720]Probe device 'irq-rv1106-gpio.2' with irq-rv1106-gpio

[ 0.001730]Probe device 'irq-rv1106-gpio.3' with irq-rv1106-gpio

[ 0.001740]Probe device 'irq-rv1106-gpio.4' with irq-rv1106-gpio

[ 0.001750]Probe device 'gpio-rv1106.0' with gpio-rv1106

[ 0.001760]Probe device 'gpio-rv1106.1' with gpio-rv1106

[ 0.001770]Probe device 'gpio-rv1106.2' with gpio-rv1106

[ 0.001780]Probe device 'gpio-rv1106.3' with gpio-rv1106

[ 0.001790]Probe device 'gpio-rv1106.4' with gpio-rv1106

[ 0.001840]Probe device 'adc-rv1106.0' with adc-rv1106

[ 0.001850]Probe device 'ce-armv7-timer.0' with ce-armv7-timer

[ 0.000026]Probe device 'cs-armv7-timer.0' with cs-armv7-timer

[ 0.005833]Probe device 'uart-8250.0' with uarn & SS&S%"٥:ѵr:ѡѵj & SSS%"٥:ѵr:ѡѵj & SS0

[ 0.024936]Probe device 'uart-8250.5' with uart-8250

[ 0.029878]Probe device 'i2c-rv1106.0' with i2c-rv1106

[ 0.034987]Probe device 'i2c-rv1106.1' with i2c-rv1106

[ 0.040098]Probe device 'i2c-rv1106.2' with i2c-rv1106

[ 0.045215]Probe device 'i2c-rv1106.3' with i2c-rv1106

[ 0.050331]Probe device 'i2c-rv1106.4' with i2c-rv1106

[ 0.055455]Probe device 'rtc-rv1106.0' with rtc-rv1106

[ 0.060545]Probe device 'wdg-rv1106.0' with wdg-rv1106

[ 0.065660]Probe device 'key-adc.0' with key-adc

[ 0.070257]Probe device 'led-gpio.0' with led-gpio

[ 0.075014]Probe device 'led-gpio.1' with led-gpio

[ 0.079784]Probe device 'led-gpio.2' with led-gpio

[ 0.084554]Probe device 'ledtrigger-heartbeat.0' with ledtrigger-heartbeat

[ 0.091395]Probe device 'ledtrigger-heartbeat.1' with ledtrigger-heartbeat

[ 0.098242]Probe device 'ledtrigger-heartbeat.2' with ledtrigger-heartbeat

[ 0.105088]Probe device 'console-uart.0' with console-uart

[ 0.111138]mount /private with 'ram' filesystem

xboot: /#

xboot: /#

xboot: /#

xboot: /#

xboot: /# 离线

#37 2022-08-25 12:11:09 分享评论

- czg516@sina.com

- 会员

- 注册时间: 2019-11-27

- 已发帖子: 1

- 积分: 1

Re: RV1103/RV1106 裸奔日记

请问哪里可以购买到开发板及芯片呢

离线

#39 2022-08-31 15:11:36 分享评论

- ifun888

- 会员

- 注册时间: 2022-08-31

- 已发帖子: 1

- 积分: 1

Re: RV1103/RV1106 裸奔日记

想问下大佬,有移植过Uboot到rv1106吗?如何在uboot中显示logo呢?

离线

#40 2022-08-31 16:43:06 分享评论

- 可爱的小盆友们

- 会员

- 注册时间: 2022-04-14

- 已发帖子: 37

- 积分: 23

Re: RV1103/RV1106 裸奔日记

板子在哪里呢?干巴巴看着大佬装逼!

离线

#41 2022-09-01 08:21:09 分享评论

- musich

- 会员

- 注册时间: 2018-04-17

- 已发帖子: 260

- 积分: 292

Re: RV1103/RV1106 裸奔日记

好nb啊

离线

楼主 #43 2022-09-21 20:10:44 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

补充一个准确的说明文件,上面的偏移有些错误

# Rockchip RV1106

## Compile source code and generate the target files at the output directory

```shell

make clean

make CROSS_COMPILE=/path/to/arm-none-linux-gnueabihf- PLATFORM=arm32-rv1106

```

## Enter maskrom mode and using xrock for burning spi nor flash (offset = 0x00010000, sector = 128)

```shell

sudo xrock maskrom rv1106_ddr_924MHz_v1.09.bin rv1106_usbplug_v1.06.bin --rc4-off;

sleep 3;

sudo xrock flash write 128 xbootpak.bin;

sudo xrock reset;

```

## Enter maskrom mode and using xrock for burning spi nand flash (offset = 0x00040000, sector = 512)

```shell

sudo xrock maskrom rv1106_ddr_924MHz_v1.09.bin rv1106_usbplug_v1.06.bin --rc4-off;

sleep 3;

sudo xrock flash write 512 xbootpak.bin;

sudo xrock reset;

```

## Enter maskrom mode and using xrock for burning emmc (offset = 0x00008000, sector = 64)

```shell

sudo xrock maskrom rv1106_ddr_924MHz_v1.09.bin rv1106_usbplug_v1.06.bin --rc4-off;

sleep 3;

sudo xrock flash write 64 xbootpak.bin;

sudo xrock reset;

```

## Download xrock source code

```shell

git clone https://github.com/xboot/xrock.git

```

## Make and install xrock

```shell

make

sudo make install

```离线

#44 2022-09-23 15:13:08 分享评论

- lignin

- 会员

- 注册时间: 2020-03-21

- 已发帖子: 139

- 积分: 128.5

Re: RV1103/RV1106 裸奔日记

眼巴巴的看着rv1106,想玩,貌似功能蛮不错的,要是价格也美丽就好了

离线

#45 2022-09-23 18:39:55 分享评论

- Timaker

- 会员

- 注册时间: 2020-05-18

- 已发帖子: 65

- 积分: 43.5

Re: RV1103/RV1106 裸奔日记

买不到板子,没得玩,难受呀

离线

#46 2022-11-17 19:18:52 分享评论

- abs4567abcd

- 会员

- 注册时间: 2022-11-17

- 已发帖子: 8

- 积分: 8

Re: RV1103/RV1106 裸奔日记

这种邮票孔的核心板特别难拆

离线

#49 2023-03-18 11:46:01 分享评论

- hanshuizhizi

- 会员

- 注册时间: 2023-03-18

- 已发帖子: 1

- 积分: 1

Re: RV1103/RV1106 裸奔日记

这个芯片的ISP调通了吗?

离线

#50 2023-05-17 15:12:13 分享评论

- q994billy1

- 会员

- 注册时间: 2023-05-17

- 已发帖子: 1

- 积分: 1

Re: RV1103/RV1106 裸奔日记

请问rv1126怎么设置从spi nor flash启动

离线

#51 2023-05-18 19:04:52 分享评论

- qdk0901

- 会员

- 注册时间: 2019-04-08

- 已发帖子: 15

- 积分: 8.5

Re: RV1103/RV1106 裸奔日记

hanshuizhizi wrote:

这个芯片的ISP调通了吗?

在xboot上搞isp、编解码这些,难度估计是地狱级

离线

#52 2023-07-03 09:38:05 分享评论

- david.y

- 会员

- 注册时间: 2023-05-15

- 已发帖子: 17

- 积分: 7

Re: RV1103/RV1106 裸奔日记

淘宝这款,便宜而且对接了两款sensor

https://item.taobao.com/item.htm?ft=t&id=696377468895

czg516@sina.com wrote:

请问哪里可以购买到开发板及芯片呢

离线

#53 2023-07-26 14:06:47 分享评论

- suzhouclark

- 会员

- 注册时间: 2022-05-12

- 已发帖子: 4

- 积分: 4

Re: RV1103/RV1106 裸奔日记

Timaker wrote:

xboot wrote:

这个芯片比F133/D1S/T113便宜,有价格优势

好像含税25左右,等大佬出板子

芯片能否给个购买链接?

最近编辑记录 suzhouclark (2023-07-26 14:07:28)

离线

#54 2023-07-26 17:33:53 分享评论

- Gentlepig

- 会员

- 注册时间: 2018-10-24

- 已发帖子: 1,409

- 积分: 1368.5

Re: RV1103/RV1106 裸奔日记

Timaker wrote:

xboot wrote:

这个芯片比F133/D1S/T113便宜,有价格优势

好像含税25左右,等大佬出板子

现在淘宝上搜到的是40。

离线

#56 2023-09-04 16:02:20 分享评论

- yuqingli

- 会员

- 注册时间: 2023-09-04

- 已发帖子: 7

- 积分: 7

Re: RV1103/RV1106 裸奔日记

楼主有没有兴趣研究下 国科微的 GK7205V200 这个才不到 200 也是A7 + 64MB 更具有性价比。并且淘宝能买到元件

离线

#57 2023-09-16 09:47:00 分享评论

- fxman

- 会员

- 注册时间: 2020-08-09

- 已发帖子: 10

- 积分: 10

Re: RV1103/RV1106 裸奔日记

理论上RV1103是不是可以直接用,最近在搞这个0.0

离线

#58 2023-10-11 21:56:15 分享评论

- again

- 会员

- 注册时间: 2022-12-30

- 已发帖子: 18

- 积分: 59

Re: RV1103/RV1106 裸奔日记

fxman wrote:

理论上RV1103是不是可以直接用,最近在搞这个0.0

有没相关资料可以分享下呢?

离线

#60 2023-10-15 14:39:50 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: RV1103/RV1106 裸奔日记

yuqingli wrote:

楼主有没有兴趣研究下 国科微的 GK7205V200 这个才不到 200 也是A7 + 64MB 更具有性价比。并且淘宝能买到元件

这个是不是可以通用以前海思的sdk

离线

#61 2023-11-13 16:23:08 分享评论

- 哈利路亚

- 会员

- 注册时间: 2023-11-13

- 已发帖子: 7

- 积分: 2

Re: RV1103/RV1106 裸奔日记

大佬,到b站上搞个教学视频吧,小白看不懂

离线

#62 2023-11-17 11:01:35 分享评论

- 网络孤客

- 会员

- 注册时间: 2022-06-09

- 已发帖子: 22

- 积分: 7

Re: RV1103/RV1106 裸奔日记

微雪有RV1103板,要近40元

离线

#63 2023-11-17 15:56:52 分享评论

- fubaojun2006

- 会员

- 注册时间: 2022-02-15

- 已发帖子: 11

- 积分: 11

Re: RV1103/RV1106 裸奔日记

没有手册玩裸机,强无敌~

那这芯片没有手册 ,还能不能好好用了

离线

楼主 #64 2024-09-24 16:07:38 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: RV1103/RV1106 裸奔日记

新版xrock支持直接下载裸机代码到ram里,直接执行,而无需烧录,调试效率大大提升。

指令 如下:

xrock extra maskrom --rc4 off --sram rv1106_ddr_924MHz_v1.15.bin --delay 10

xrock extra maskrom-write-arm32 --rc4 off 0x00000000 xstar.bin

xrock extra maskrom-exec-arm32 --rc4 off 0x00000000离线

#65 2024-12-01 20:23:11 分享评论

- david

- 会员

- 注册时间: 2018-03-05

- 已发帖子: 397

- 积分: 328.5

Re: RV1103/RV1106 裸奔日记

是啥限制了1103只能编码4M@30,不能超频当1106么?主要是1106尺寸有点大

离线

#66 2024-12-19 22:13:44 分享评论

- 多箩茜

- 会员

- 注册时间: 2023-06-04

- 已发帖子: 8

- 积分: 3

Re: RV1103/RV1106 裸奔日记

Gentlepig wrote:

用QQ扫了下,该二维码暂不支持识别。

我扫到了德邦快递:lol:

离线

#67 2025-01-13 16:45:06 分享评论

- QINGFENG

- 会员

- 注册时间: 2025-01-13

- 已发帖子: 1

- 积分: 1

Re: RV1103/RV1106 裸奔日记

RV1109怎么样

离线

#68 2025-01-24 16:11:38 分享评论

- bigzhu

- 会员

- 注册时间: 2023-08-30

- 已发帖子: 24

- 积分: 15

Re: RV1103/RV1106 裸奔日记

RK3506G2也出来了

QINGFENG wrote:

RV1109怎么样

离线

东莞哇酷科技有限公司开发