楼主 # 2023-03-16 11:34:04 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

省流:AGRV2K=AG32VF407=RV32IMACF+2K LUT=16.8块钱

相信对国产FPGA的同学应该都听说过AG1280吧,作为淘宝可以随便买的最便宜FPGA,AG1280以7块出头的价格(甚至不是批量价)能够换到1280个LUT的资源,性价比还是很不错的。

最近,AGM又推出了新的产品,这次是AGRV2K,号称是RISC-V+FPGA的组合。那么实际效果如何呢?不要走开,下面会持续更新相关内容。

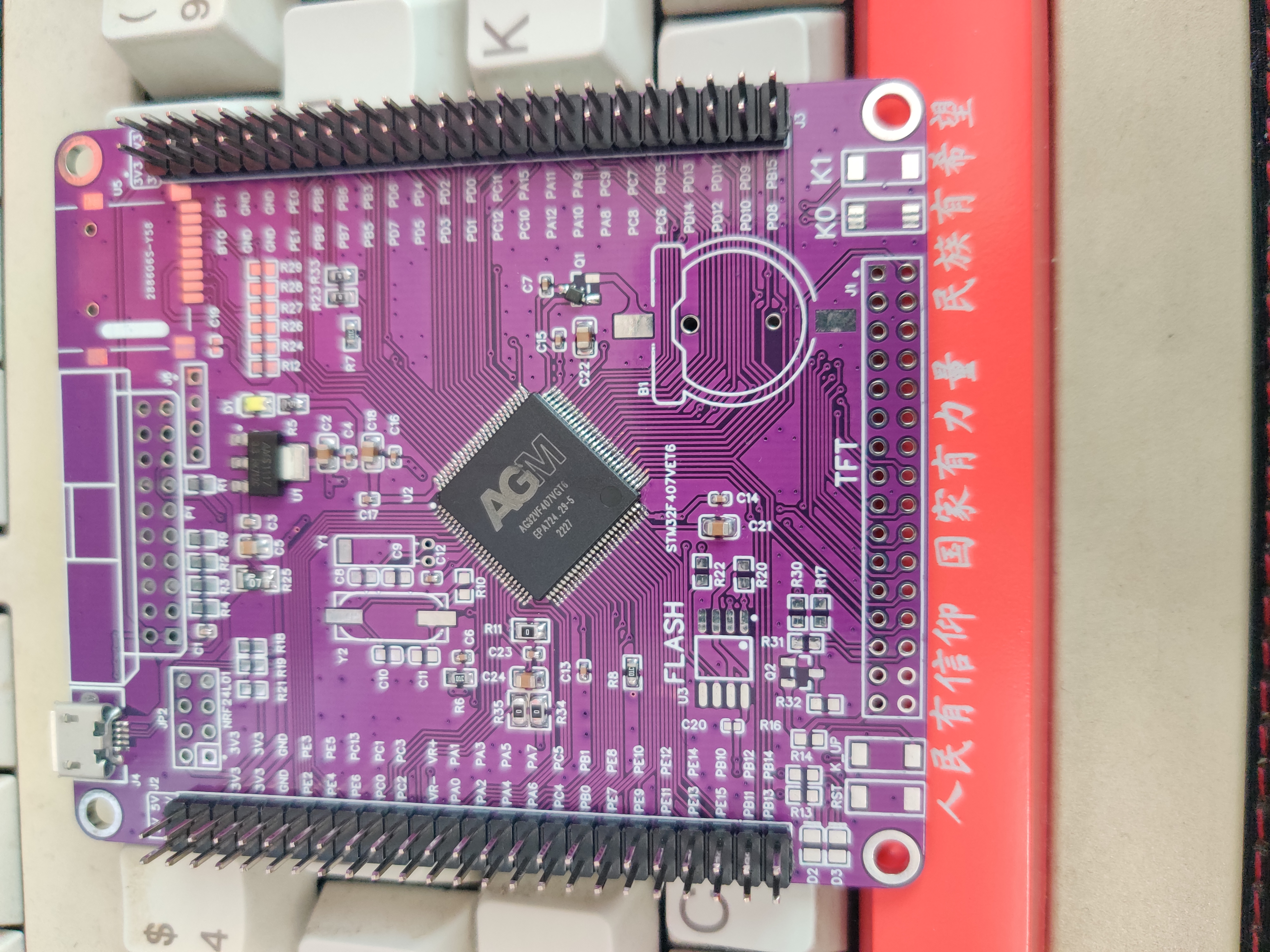

最后来张AGRV2K板子镇楼(是的,因为芯片引脚兼容STM32F407V,所以直接到嘉立创打了个STM32F407V的空板焊上就能用!)

离线

楼主 #1 2023-03-16 11:42:29 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

某天在逛淘宝时,发现AGM店里上了个有趣的芯片:AGRV2K100(CPLD) AGM FPGA CPLD替代Altera EP1270 内嵌MCU,遂买来玩玩。接下来就发生了意想不到的一些事情:

我在早上下了一单,结果晚上到家的时候就发现快递躺着家门口了,这也太效率了。后面了解到他们一天会发两次货,并且刚好有本地仓库,所以当天就收到了,而板子都还没准备好。

收到货的时候,发现并没有收到想要的AGRV2K,反而收到了AG32VF407。后来才知道,原来AGRV32和AG32VF407是同一颗芯片,估计厂家没有重新打标,直接就推了。

发现卖家“发错”之后立刻联系卖家,结果卖家在晚上直接就打电话过来了,详细解释了丝印的问题。后面我也确认过,这两个确实是同款芯片。

来点当时刚刚收到的芯片:

离线

#3 2023-03-16 13:15:43 分享评论

- kekemuyu

- 会员

- 注册时间: 2018-12-13

- 已发帖子: 856

- 积分: 697

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

跟着玩,不知道这点逻辑门能否构建一个简单的cpu

离线

#4 2023-03-16 14:14:55 分享评论

- fxyc87

- 会员

- 注册时间: 2023-03-15

- 已发帖子: 39

- 积分: 45

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

看起来不错的样子,但开发环境是啥?难道用altea的IDE?还是用它自己的IDE?

环境友好不?需要注册码不?

综合稳定不?

下载器用啥?可以兼容么?

AGRV2K100这个内置的MCU是啥?没找到介绍呢?

国产的FPGA资料不是很开放,楼主先玩,玩好了带大家一起玩。

离线

#5 2023-03-16 14:19:44 分享评论

- fxyc87

- 会员

- 注册时间: 2023-03-15

- 已发帖子: 39

- 积分: 45

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

在官网上看这个407介绍,只看到它是个MCU,没说有多少个LE啊?

离线

#6 2023-03-16 14:30:52 分享评论

- fxyc87

- 会员

- 注册时间: 2023-03-15

- 已发帖子: 39

- 积分: 45

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

刚在官网下载一个软件【Supra】,却不知道如何使用,好像软件也太简单了点吧?

离线

#7 2023-03-16 14:34:19 分享评论

- fxyc87

- 会员

- 注册时间: 2023-03-15

- 已发帖子: 39

- 积分: 45

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

在网上了解了一下,

原来这个AGM是要用Altera的quartus软件进行设计,再用它自己的一个工具进行转换。怪不得这么神秘呢。

https://blog.csdn.net/ModernTalking/article/details/126986620?spm=1001.2014.3001.5501

最近编辑记录 fxyc87 (2023-03-16 14:41:57)

离线

#8 2023-03-16 14:37:13 分享评论

- echo

- 会员

- 注册时间: 2020-04-16

- 已发帖子: 364

- 积分: 370.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

这个RISC-V+FPGA应该很好玩,做产品就不推荐了,容易被一棵树吊死。

离线

#9 2023-03-16 14:46:15 分享评论

- jiangchun9981

- 会员

- 注册时间: 2019-07-31

- 已发帖子: 170

- 积分: 130.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

他这个开发,看过文档

流程的用ALTERA那个QUATER软件综合,出网表,然后再用自己的这个SUPRA软件来做最后的处理

现在XILINX的价格下来了,A9双核+28K的ARTIX架构的现在卖19块钱,注意这个可是ARTIX架构,一般人够用了

离线

#10 2023-03-16 15:22:11 分享评论

- dykxjh

- 会员

- 注册时间: 2020-03-25

- 已发帖子: 189

- 积分: 149

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

我反而对AG1280感兴趣了。

离线

#11 2023-03-16 18:09:00 分享评论

- david

- 会员

- 注册时间: 2018-03-05

- 已发帖子: 397

- 积分: 328.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

他这个开发,看过文档

流程的用ALTERA那个QUATER软件综合,出网表,然后再用自己的这个SUPRA软件来做最后的处理

现在XILINX的价格下来了,A9双核+28K的ARTIX架构的现在卖19块钱,注意这个可是ARTIX架构,一般人够用了

啥型号只要19块 是人民币么 一般人能拿到么

离线

#12 2023-03-16 18:42:05 分享评论

- Blueskull

- 会员

- 注册时间: 2020-02-20

- 已发帖子: 458

- 积分: 444.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

现在XILINX的价格下来了,A9双核+28K的ARTIX架构的现在卖19块钱,注意这个可是ARTIX架构,一般人够用了

你那是二手吧,全新Zynq咋会这么便宜。

离线

#13 2023-03-16 22:40:40 分享评论

- vmao

- 会员

- 注册时间: 2021-08-11

- 已发帖子: 8

- 积分: 3

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

他这个开发,看过文档

流程的用ALTERA那个QUATER软件综合,出网表,然后再用自己的这个SUPRA软件来做最后的处理

现在XILINX的价格下来了,A9双核+28K的ARTIX架构的现在卖19块钱,注意这个可是ARTIX架构,一般人够用了

7Z020?

离线

楼主 #14 2023-03-17 01:22:14 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

睡前发一下老板今天(昨天?)刚给的资料,信息量还是比较大的,特别是网盘部分,需要花点时间慢慢啃。

AG1KLPQ48.rar

AG32VF407.rar

AGRV2K.rar

离线

#15 2023-03-17 10:49:14 分享评论

- 达克罗德

- 会员

- 注册时间: 2018-04-10

- 已发帖子: 1,140

- 积分: 1092.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

感觉可以做个音箱,FPGA负责多DMIC不知资源够不

离线

楼主 #16 2023-03-18 00:07:25 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

如果对AGRV2K的工作原理感兴趣,可以打开AgRV_pio\platforms\AgRV\builder\main.py文件,里面详细记录了各个工具的使用方式。

离线

#17 2023-03-18 23:15:52 分享评论

- marshallemon

- 会员

- 注册时间: 2023-03-18

- 已发帖子: 2

- 积分: 2

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

关注一下进度,也买了这个板子,但还不会玩

离线

#18 2023-03-19 01:45:29 分享评论

- libc0607

- 会员

- 注册时间: 2018-12-13

- 已发帖子: 25

- 积分: 48.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

板子还没到 +1,先看了下 SDK,奇妙(

文档里写过的就不说了,试了下流程,编译了 AgRV_pio\platforms\AgRV\examples\custom_ip,这个例子把 FPGA 里的 M9K 挂在了 alta_rv32 的 AHB 上

PIO 打开工程后:

1. PIO 里,Project tasks - dev- Custom - Prepare IP,会在 .\logic 下生成 Quartus 和 Supra 工程;这里 custom_ip.v 是 SDK 给出的,但如果是自己写的话它会根据ve自动生成一个模板 custom_ip_tmpl.v

2. Quartus 里 Compile Design 一下,生成 .\logic\simulation\modelsim\custom_ip.vo

3. Supra 打开 .\logic 下的工程,Tools - Compile, Run 一下,生成 FPGA 部分(不带 alta_rv32)的网表 .\logic\custom_ip\custom_ip.vx

4. PIO 中,Project tasks - dev- Custom - Update Logic,先 gen_vlog,根据你写的引脚分配 .\top.ve 和刚刚 Supra 生成的 .\logic\custom_ip\,生成整个芯片的 top 到 .\.pio\logic\top.vx,然后再由 gen_logic.tcl 布局布线生成码流

5. 生成的时序报告在.\.pio\logic\logic_db\setup*.rpt.gz 和 hold*.rpt.gz 一共四个文件,布局布线后的网表生成到 .\.pio\logic\top_routed.vx,实际烧写到 Flash 最后 100k 处的 bin 是 .\.pio\logic\top.bin (99,944 Bytes)

6. 板子还没到,没法烧写,不过大概执行的内容是在 AgRV_pio\platforms\AgRV\builder\main.py 中与 logic_actions 有关的部分吧(

至于引脚,alta_rv32 貌似只能按照 “AGRV2K 逻辑设置” 文档中的 Function pin 列表来复用,但是这个表的每一行应该是都能通过包一层 FPGA 引出到任意的 PIN(?);USB D+D-则是固定的;

关于引脚分配的更多注意事项,建议直接在 AgRV_pio\packages\framework-agrv_sdk\etc\gen_vlog 中搜索 ErrorOut (雾)

顺便可以看下综合结果,里面集成的 FPGA 有这些资源(其中 BRAM 是 M9K):

Total Logics : 97/2112 ( 4%)

Total LUTs : 97/2112 ( 4%)

Total Registers : 73/2112 ( 3%)

Total Block Rams : 4/ 4 (100%)

Total PLLs : 1/ 1 (100%)

Total Pins : 12/ 128 ( 9%)

Global Signals : 3/ 5 ( 60%)只是试了下流程,上面提到的不一定准确,如果有误还请指出

离线

#19 2023-03-19 11:56:06 分享评论

- 1847123212

- 会员

- 注册时间: 2019-11-21

- 已发帖子: 70

- 积分: 46

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

@libc0607

他们家的fpga就是这么用的,哈哈哈看起来还行2k逻辑做点简单的外设刚刚好

离线

楼主 #20 2023-03-21 00:01:05 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

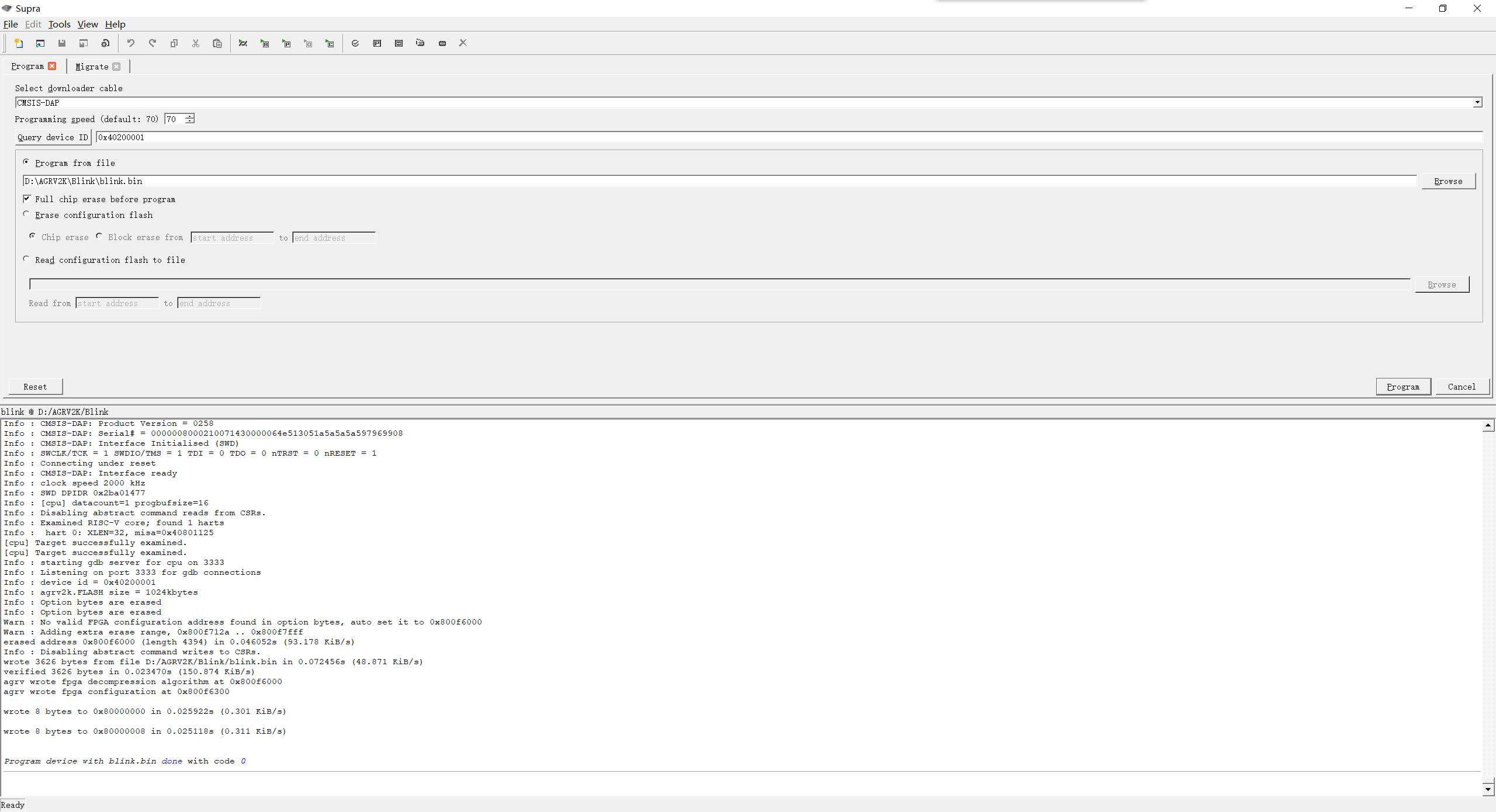

在更新到Supra之后,看起来支持CMSIS-DAP了,这样一来可以搓一个带下崽器的最小系统,好评。

离线

#21 2023-03-21 01:06:23 分享评论

- liberty

- 会员

- 注册时间: 2023-03-05

- 已发帖子: 11

- 积分: 21

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

@vmao

应该是zynq7010吧,7010是28k,7020有85k,20左右应该还是拆机的价,也许是EBAZ2045之类的矿板上的,据说之前才20一张,现在涨60了,按性价比来说还是比较好的选择。

离线

楼主 #22 2023-03-23 00:49:10 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

在更新到Supra之后,看起来支持CMSIS-DAP了,这样一来可以搓一个带下崽器的最小系统,好评。

https://whycan.com/files/members/1510/AGRV32-Supra.png

验证了一下,确实是支持的,而且OpenOCD的版本很新(版本信息是Open On-Chip Debugger 0.11.0+dev-02429-g3c36bfc (2023-02-06-17:01)),可以无bug支持CMSIS-DAP V2.1。

离线

#23 2023-03-23 01:04:35 分享评论

- AGMMicro

- 会员

- 所在地: 上海

- 注册时间: 2023-03-16

- 已发帖子: 3

- 积分: 18

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

这个资料大家可能有用(CPLD和MCU交互的案例),共享给各位

可以参考下ADC,DAC以及比较器,通过AHB总线挂在一起

离线

楼主 #24 2023-03-29 12:11:06 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

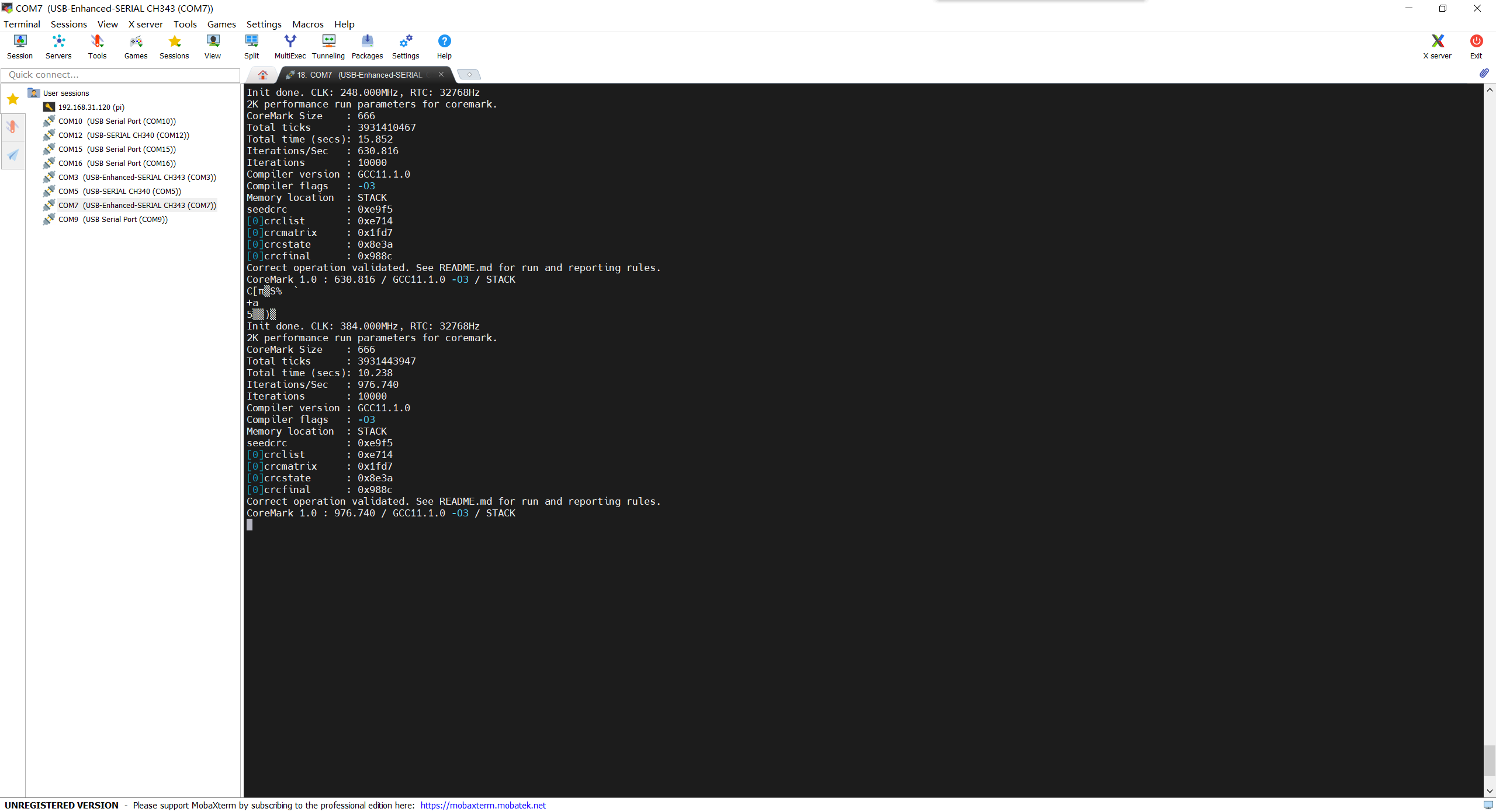

尝试测了一下CoreMark,分数还不错,基本上和STM32F407在一个等级,248MHz(数据手册中最高频率)能到630,384MHz(最高可运行频率)到了976以上,不知道这个分数是否意味着AG32VF407/AGRV2K的Flash有cache或者零等待执行。

CoreMark的工程可以在这里下载:CoreMark.zip,可以通过修改coremark.ve文件中的SYSCLK来调整时钟频率。

离线

#25 2023-03-29 12:26:04 分享评论

- IOsetting

- 会员

- 注册时间: 2022-05-08

- 已发帖子: 59

- 积分: 65

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

这个串口工具是啥?

离线

楼主 #26 2023-03-29 12:39:27 分享评论

- metro

- 会员

- 注册时间: 2019-03-09

- 已发帖子: 445

- 积分: 489

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

这个串口工具是啥?

MobaXterm

离线

#28 2023-04-22 17:38:06 分享评论

- ThinkerMaker

- 会员

- 注册时间: 2020-12-12

- 已发帖子: 4

- 积分: 4

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

@libc0607

老哥可以分享一个custom ip能运行的工程吗,我用的example下的工程编译一直有问题,不知道问题出在哪,不修改他的参数的情况下 只能综合出一个custom ip的项目,然后update的时候会显示io爆了,如果改一个pio.ini下的logic_ip = true参数之后,能正常综合出一个带rv32的top项目,但是综合出来的le占用是0,项目好像有问题,方便留个联系方式交流一下吗

离线

#29 2023-04-23 16:05:13 分享评论

- ThinkerMaker

- 会员

- 注册时间: 2020-12-12

- 已发帖子: 4

- 积分: 4

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

@ThinkerMaker

问题应该是解决了 ,奇奇怪怪的 好像是quartus版本问题,我换了版本之后就没事了,之前ag1k我用没问题啊

离线

#30 2023-04-24 20:52:05 分享评论

- htjw

- 会员

- 注册时间: 2019-04-25

- 已发帖子: 18

- 积分: 8

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

比较好奇2k逻辑资源可以怎样充分利用起来,做出有趣的东西:)

离线

#31 2023-04-27 08:41:47 分享评论

- abutter

- 会员

- 注册时间: 2021-02-04

- 已发帖子: 18

- 积分: 17.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

楼主又更新吗?:)

离线

#32 2023-05-03 22:11:13 分享评论

- szmdao

- 会员

- 注册时间: 2023-05-02

- 已发帖子: 1

- 积分: 1

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

兄弟们,我想用它实现这样一个功能,CPLD部分读取高速ADC的输出,然后直接存在mcu部分的sram里面,不知道应该怎么实现。custom_ip例程是把CPLD的bram挂在AHB上,MCU能直接访问。但跟我想要的还是有点差距呀

离线

#33 2023-05-03 22:39:04 分享评论

- Winston

- 会员

- 注册时间: 2023-03-09

- 已发帖子: 15

- 积分: 45

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

楼主好像没有更新了, 看到好久了

离线

#34 2023-05-04 08:17:55 分享评论

- abutter

- 会员

- 注册时间: 2021-02-04

- 已发帖子: 18

- 积分: 17.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

兄弟们,我想用它实现这样一个功能,CPLD部分读取高速ADC的输出,然后直接存在mcu部分的sram里面,不知道应该怎么实现。custom_ip例程是把CPLD的bram挂在AHB上,MCU能直接访问。但跟我想要的还是有点差距呀

需要知道 AHB matrix 有没有 master 端口给 FPGA/CPLD 用。如果有则需要实现一个 AHB master,然后通过 AHB master 将数据通过 burst 写入 SRAM 里面。

ADC 的带宽/响应时间要求不高的话,接口加 FIFO 一般能满足要求。

离线

#35 2023-05-04 15:10:14 分享评论

- libc0607

- 会员

- 注册时间: 2018-12-13

- 已发帖子: 25

- 积分: 48.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

兄弟们,我想用它实现这样一个功能,CPLD部分读取高速ADC的输出,然后直接存在mcu部分的sram里面,不知道应该怎么实现。custom_ip例程是把CPLD的bram挂在AHB上,MCU能直接访问。但跟我想要的还是有点差距呀

FPGA 部分可以做 AHB Master,看 ram2ahb.v

custom_ip 例程中,验证数据分两部分,后半部分就是 FPGA 作 AHB master,收到 GPIO 上升沿后主动把 BRAM 内容写到 read_buf,这个 read_buf 就是在 MCU 的 SRAM

看文档说 FPGA 的 AHB master 可以访问所有地址,不过我没试。。仅供参考

离线

#36 2023-06-05 23:37:39 分享评论

- Robo_V1

- 会员

- 注册时间: 2023-02-21

- 已发帖子: 3

- 积分: 3

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

这个型号的RTC似乎有问题,具体表现为RTC功能正常,但主电源掉电时备用电池的电流过大,实测采用CR1220(全新时空载电压约3.2V)时其电流超过100uA。由于此现象在手头所有的2片AG32VF407VG与自制的最小系统板、某市售STM32F407核心板;1片AG32VF103CC与某2种不同的市售STM32F103c8核心板上均成功复现,且实测出厂状态(无程序)与写入官方例程(不论是否开启RTC)后均能稳定的观察到此现象,因此怀疑是芯片本身存在硬件bug。已尝试咨询其tb客服,但截至目前(2023/06/05)未得到有效答复。

最近编辑记录 Robo_V1 (2023-06-05 23:44:15)

离线

#37 2023-06-07 23:05:40 分享评论

- Robo_V1

- 会员

- 注册时间: 2023-02-21

- 已发帖子: 3

- 积分: 3

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

@Robo_V1

经客服确认,该现象就是AGRV2K本身的硬件问题所致,不过RTC本身的功能是正常的。

最近编辑记录 Robo_V1 (2023-06-07 23:10:26)

离线

#38 2023-06-12 17:37:25 分享评论

- 1847123212

- 会员

- 注册时间: 2019-11-21

- 已发帖子: 70

- 积分: 46

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

@Robo_V1

经客服确认,该现象就是AGRV2K本身的硬件问题所致,不过RTC本身的功能是正常的。

所以RTC不能接电池,不然一会就废是吧,不过问题不大,如果只是用来做时钟就没事

离线

#39 2023-06-13 09:38:02 分享评论

- XIVN1987

- 会员

- 注册时间: 2019-08-30

- 已发帖子: 271

- 积分: 332.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

@metro

请问是必须用JTAG接口吗?SWD应该不支持吧?

离线

#40 2023-06-14 09:10:13 分享评论

- cheng1986

- 会员

- 注册时间: 2023-06-14

- 已发帖子: 21

- 积分: 31

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

@metro

请问是必须用JTAG接口吗?SWD应该不支持吧?

同时支持SWD和JTAG接口

最近编辑记录 cheng1986 (2023-06-14 09:13:22)

离线

#42 2023-06-15 15:49:50 分享评论

- shi

- 会员

- 注册时间: 2022-10-22

- 已发帖子: 3

- 积分: 8

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

有点好奇这个片子FPGA可不可以抓信号,问了厂家,答复说可以抓,但是并没有详细的资料说明。

离线

#43 2023-06-23 22:42:18 分享评论

- XIVN1987

- 会员

- 注册时间: 2019-08-30

- 已发帖子: 271

- 积分: 332.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

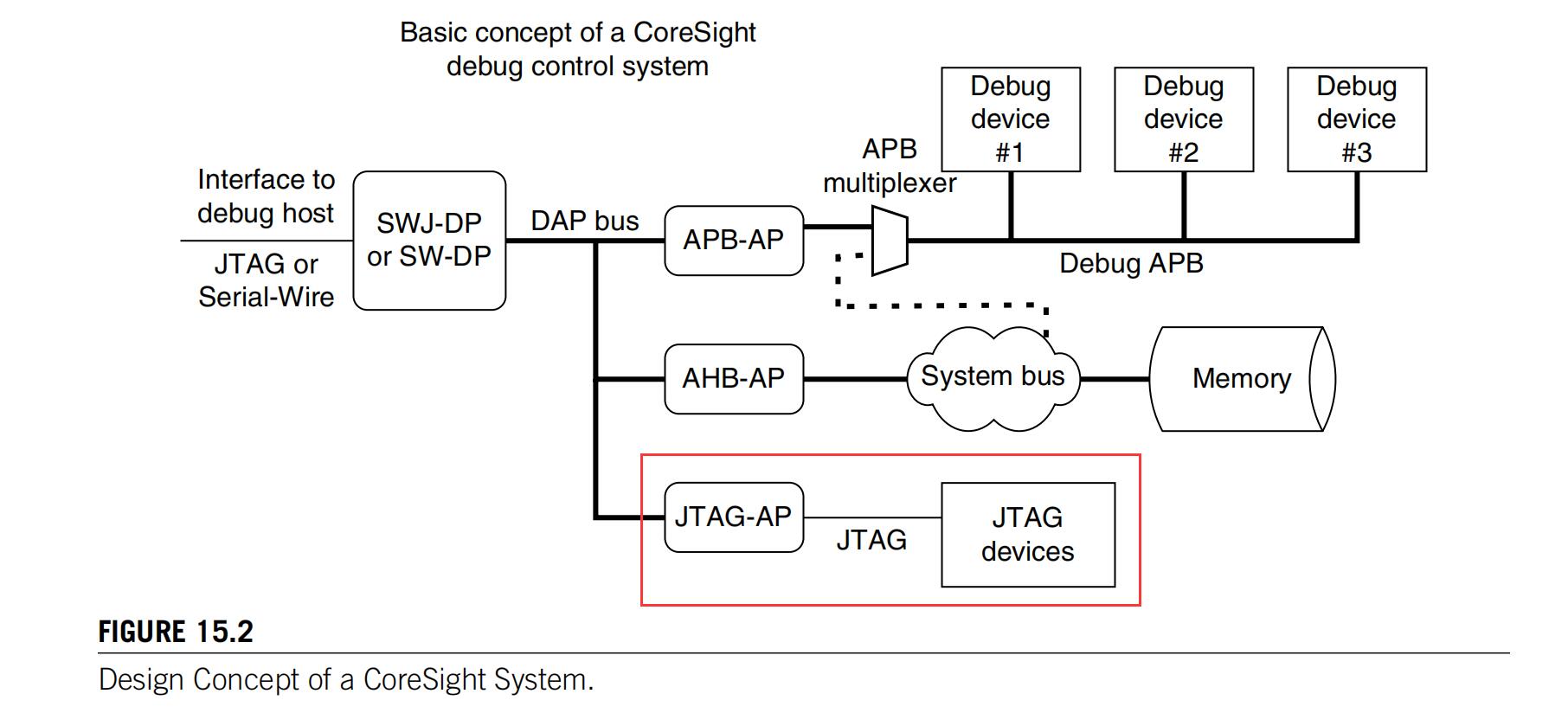

同时支持SWD和JTAG接口

感谢回复,,试了下,SWD 确实可以,,

研究了下,,通过下图猜测,,ARM 的 CoreSight 架构本身就支持通过 SWD 调试 JTAG 设备。。只需要实现 SWJ-DP、DAP bus、JTAG-AP 即可。。

不过 RISC-V 厂商似乎大多数都没使用这种方案,,猜测也许是因为这种用法涉及到 ARM 的专利。。

离线

#44 2023-07-10 12:13:39 分享评论

- tpu

- 会员

- 注册时间: 2020-06-15

- 已发帖子: 40

- 积分: 42.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

datasheet上有提到说,support SDIO/Ethernet。 但从没看到有关SDIO的资料啊。到底有没有SDIO接口呢?

离线

#45 2023-07-10 13:55:06 分享评论

- XIVN1987

- 会员

- 注册时间: 2019-08-30

- 已发帖子: 271

- 积分: 332.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

datasheet上有提到说,support SDIO/Ethernet。 但从没看到有关SDIO的资料啊。到底有没有SDIO接口呢?

问过了,,没有 SDIO,,想用的话用 verilog 自己写一个

离线

#46 2023-07-11 11:38:37 分享评论

- tpu

- 会员

- 注册时间: 2020-06-15

- 已发帖子: 40

- 积分: 42.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

那要写好多东西啊...我看了他的几个模拟功能,原来默认是没有连接到CPU上的,也需要自己写代码连到AHB上面。

离线

#47 2023-08-04 18:00:42 分享评论

- xpulabs

- 会员

- 注册时间: 2021-12-14

- 已发帖子: 6

- 积分: 1

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

这个芯片有没有具体的教程!!!

离线

#48 2023-08-04 22:16:15 分享评论

- AGMMicro

- 会员

- 所在地: 上海

- 注册时间: 2023-03-16

- 已发帖子: 3

- 积分: 18

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

@Robo_V1

您好,关于之前反馈给我们的RTC使用电池会出现掉电问题,目前最新版本的已经全部修复,感谢支持呀~

离线

#49 2023-08-23 14:46:47 分享评论

- happysoul

- 会员

- 注册时间: 2022-08-30

- 已发帖子: 8

- 积分: 28

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

@Robo_V1

您好,关于之前反馈给我们的RTC使用电池会出现掉电问题,目前最新版本的已经全部修复,感谢支持呀~

这。。。软件修复 还是硬件更新啊?

离线

#51 2023-08-25 10:24:15 分享评论

- willX

- 会员

- 注册时间: 2019-09-06

- 已发帖子: 48

- 积分: 28

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

@Robo_V1

您好,关于之前反馈给我们的RTC使用电池会出现掉电问题,目前最新版本的已经全部修复,感谢支持呀~

这不是说硬件问题吗?还能修复?同问详细方案和影响啊。

离线

#52 2023-08-27 22:03:56 分享评论

- AGMMicro

- 会员

- 所在地: 上海

- 注册时间: 2023-03-16

- 已发帖子: 3

- 积分: 18

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

AGMMicro 说:@Robo_V1

您好,关于之前反馈给我们的RTC使用电池会出现掉电问题,目前最新版本的已经全部修复,感谢支持呀~

这。。。软件修复 还是硬件更新啊?

最新批次版本,在硬件方面修复了~

离线

#53 2023-08-29 10:15:59 分享评论

- Copper

- 会员

- 注册时间: 2021-12-29

- 已发帖子: 31

- 积分: 61

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

@metro

亮点可能是RISCV硬核+FPGA。

离线

#55 2023-10-13 14:07:55 分享评论

- LittleQ

- 会员

- 注册时间: 2023-10-13

- 已发帖子: 5

- 积分: 0

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

ADC和DAC的速率能到多少?是直连MCU还是可以通过FPGA给数据?

离线

#56 2023-11-07 17:13:58 分享评论

- tpu

- 会员

- 注册时间: 2020-06-15

- 已发帖子: 40

- 积分: 42.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

离线

#57 2024-02-20 19:50:59 分享评论

- liberty

- 会员

- 注册时间: 2023-03-05

- 已发帖子: 11

- 积分: 21

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

在更新到Supra之后,看起来支持CMSIS-DAP了,这样一来可以搓一个带下崽器的最小系统,好评。

https://whycan.com/files/members/1510/AGRV32-Supra.png

FPGA部分也可以不用JTAG直接用CMSIS-DAP下载?

离线

#58 2024-02-21 11:14:13 分享评论

- echo

- 会员

- 注册时间: 2020-04-16

- 已发帖子: 364

- 积分: 370.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

happysoul 说:AGMMicro 说:@Robo_V1

您好,关于之前反馈给我们的RTC使用电池会出现掉电问题,目前最新版本的已经全部修复,感谢支持呀~

这。。。软件修复 还是硬件更新啊?

最新批次版本,在硬件方面修复了~

资料能否在github放一份?或者别的网盘放一下,百度盘下载限速100kB/s太恶心了。

已经下载下来,把灯点亮了,这个基于platformio的IDE还不错,非常有想法的芯片。

最近编辑记录 echo (2024-02-21 18:48:13)

离线

#59 2024-02-23 17:10:07 分享评论

- echo

- 会员

- 注册时间: 2020-04-16

- 已发帖子: 364

- 积分: 370.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

happysoul 说:AGMMicro 说:@Robo_V1

您好,关于之前反馈给我们的RTC使用电池会出现掉电问题,目前最新版本的已经全部修复,感谢支持呀~

这。。。软件修复 还是硬件更新啊?

最新批次版本,在硬件方面修复了~

实测AG32VF303CCT6,实测FLASH_GetUniqueID()函数读取不到128位的UID,同样依赖FLASH_FlexRead()函数的另外几个API也有问题。

离线

#60 2024-02-23 22:11:33 分享评论

- echo

- 会员

- 注册时间: 2020-04-16

- 已发帖子: 364

- 积分: 370.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

我这边已经评估完了。

总体来讲,这个AGRV2K是个相当偏门的芯片,和STC的32位8051或者迪文的T5L芯片有些类似,可玩性很高,不过做产品就不太推荐了,除非完全适合你的应用场景,就像迪文T5L来做HMI一样,否则还是推荐用专门的MCU芯片。

如果你需要FPGA,这个AGRV2K也不是首选,还是选ALTERA的正经FPGA芯片,然后用AGM的P2P兼容芯片来替代,这样项目风险更低,开发成本也更低。

离线

#61 2024-02-27 11:57:17 分享评论

- whycan.com

- 会员

- 注册时间: 2024-02-27

- 已发帖子: 2

- 积分: 2

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

这个性能很局限吧,fpga规模小点了吧

离线

#62 2024-03-04 14:58:36 分享评论

- zjsx133

- 会员

- 注册时间: 2018-07-23

- 已发帖子: 101

- 积分: 36

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

这个可以做信号处理吗?比如一阶二阶高通/低通滤波?

离线

#63 2024-03-08 19:51:13 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 112

- 积分: 514

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

硬件修复我估计就是ic内部加了二极管,vrtc只进不漏。当然系统上vrtc最好还是外部串联一个电阻限流一下

最近编辑记录 aquasnake (2024-03-08 19:53:14)

离线

#64 2024-03-08 20:08:03 分享评论

- aquasnake

- 会员

- 注册时间: 2024-01-09

- 已发帖子: 112

- 积分: 514

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

@echo

2K LUT的产品估计就是对标lattice MACH XO2.

说的没错,这种融合cpld+mcu的单片机系统适合优化已有的方案custdown,但是如果新项目设计方案选用这种风险较大,CPLD+MCU改动风险小,项目移植性高,过度耦合/集成到单片系统(SOAC,system on a chip)调试和采购都会带来风险增加。因为很难找到类似的别的供应商的产品,一旦设计进去,容易被上游芯片商吊死

离线

#65 2024-04-07 15:02:16 分享评论

- bedouins

- 会员

- 注册时间: 2024-04-03

- 已发帖子: 4

- 积分: 4

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

这个芯片看起来性价比确实不错都集成在一个芯片内方便开发

离线

#66 2024-04-07 15:03:54 分享评论

- bedouins

- 会员

- 注册时间: 2024-04-03

- 已发帖子: 4

- 积分: 4

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

@metro

频率高了势必会不稳定

离线

#67 2024-06-28 11:39:52 分享评论

- 老发

- 会员

- 注册时间: 2018-03-15

- 已发帖子: 31

- 积分: 31

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

@metro

频率高了势必会不稳定

X86的CPU跑数GHz岂不是要天天死机?

离线

#68 2024-06-29 14:39:50 分享评论

- shxyke

- 会员

- 注册时间: 2022-03-02

- 已发帖子: 5

- 积分: 0

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

最近有点想拿这玩意做个软件无线电的,但是官网啥资料都找不到,包括他说的那个cpld编程手册

离线

#69 2024-06-29 17:46:51 分享评论

- AGMtestID

- 会员

- 注册时间: 2024-05-24

- 已发帖子: 5

- 积分: 5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

了解AG32:

1. AG32开发最新文档汇总

网盘:

https://pan.baidu.com/s/1wcBnqnray7bu4IURDIoDDQ?pwd=1205

2. 先阅读网盘下:《AG32用户入门指引.pdf》

准备工作:

1. 搭建mcu开发环境:《AG32开发环境搭建.pdf》

---搭建起来整个开发环境;

2. 第一次使用开发板:《AG32开发板使用入门.pdf》

---点亮led灯,串口输出数据;

3. 熟悉mcu开发环境:《AG32在VSCODE下的使用入门.pdf》

---熟悉mcu的 配置、编写、编译、烧录、仿真、生产;

开发:

1. mcu编程的进阶:《AG32驱动的使用.pdf》

---mcu中各驱动的样例及说明;

2. cpld+mcu的联合编程:

流程介绍:《AG32下fpga和cpld的使用入门.pdf》

cpld和mcu的交互详解:《AG32中cpld的基础.pdf》

进阶:

请参考该网盘下其他文档。

离线

#71 2024-12-05 10:02:34 分享评论

- xiaoerge

- 会员

- 注册时间: 2020-07-16

- 已发帖子: 9

- 积分: 9

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

@AGMtestID

是否有AG10KL144H的资料?谢谢

离线

#72 2024-12-05 16:22:08 分享评论

- cheng1986

- 会员

- 注册时间: 2023-06-14

- 已发帖子: 21

- 积分: 31

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

官网上有:http://www.agm-micro.com/products.aspx?lang=&id=61&p=14

@AGMtestID

是否有AG10KL144H的资料?谢谢

离线

#73 2024-12-06 09:19:22 分享评论

- xiaoerge

- 会员

- 注册时间: 2020-07-16

- 已发帖子: 9

- 积分: 9

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

官网资料太有限了,都是介绍性的,开发相关的资料基本没有

离线

#74 2024-12-06 13:14:06 分享评论

- cheng1986

- 会员

- 注册时间: 2023-06-14

- 已发帖子: 21

- 积分: 31

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

Supra下载——

https://pan.baidu.com/s/1rJiAJHQQCp8WPGSPwCLm1Q?pwd=1234

网盘有相关文档

官网资料太有限了,都是介绍性的,开发相关的资料基本没有

离线

#77 2025-03-30 15:29:13 分享评论

- DerBastian112

- 会员

- 注册时间: 2025-03-30

- 已发帖子: 5

- 积分: 10

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

大家好,

我刚刚遇到 AGRV2k (AG32VF303),发现 FPGA 非常有趣。目前我仍在努力使用该软件,因为不幸的是,该文档非常值得怀疑,而且我只懂德语和英语。我想使用 DAC,但不想使用 RISC-V。我使用了 Quartus 13.1 和 Supra-2023.02.b0-7773ca8a-win64-all。有人成功过仅将 DAC 与 FPGA 一起使用吗? Quartus 总是会帮我优化 alta_dac,导致 supra 无法路由该项目。

问候,

DerBastian112

最近编辑记录 DerBastian112 (2025-03-30 15:30:39)

离线

#78 2025-03-31 11:24:33 分享评论

- qq345340585

- 会员

- 注册时间: 2020-04-06

- 已发帖子: 2

- 积分: 2

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

1280个LUT 这个能做些啥,大家能给点建议吗,之前用的fpga全是10K起步的

离线

#79 2025-03-31 11:31:16 分享评论

- qq345340585

- 会员

- 注册时间: 2020-04-06

- 已发帖子: 2

- 积分: 2

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

最近有点想拿这玩意做个软件无线电的,但是官网啥资料都找不到,包括他说的那个cpld编程手册

这个芯片做软件无线电是使用dac 外接一个压控振荡器来做混频实现吗,楼主现在弄出来没

离线

#80 2025-03-31 14:04:23 分享评论

- DerBastian112

- 会员

- 注册时间: 2025-03-30

- 已发帖子: 5

- 积分: 10

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

AGRV2K 有 2000 LE。虽然不多,但对于很多事情来说已经足够了。 ADC 和 DAC 可免费使用。例如,您可以使用它来播放音乐或录制声音。

但我还没弄清楚如何将它与 Quartus 一起使用。本机开发(使用 yosys)对我来说不起作用。

离线

#82 2025-03-31 22:58:46 分享评论

- libc0607

- 会员

- 注册时间: 2018-12-13

- 已发帖子: 25

- 积分: 48.5

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

AGRV2K 有 2000 LE。虽然不多,但对于很多事情来说已经足够了。 ADC 和 DAC 可免费使用。例如,您可以使用它来播放音乐或录制声音。

但我还没弄清楚如何将它与 Quartus 一起使用。本机开发(使用 yosys)对我来说不起作用。

AFAIK the yosys in Supra is usable since Oct. 2024. (source: https://mp.weixin.qq.com/s/O5G78TIDfhTL-FMSJdwoVw)

Have you ever tried any newer version of Supra? Seems that you're using a quite old one...

最近编辑记录 libc0607 (2025-03-31 22:59:27)

离线

#83 2025-04-02 14:37:53 分享评论

- cheng1986

- 会员

- 注册时间: 2023-06-14

- 已发帖子: 21

- 积分: 31

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

AGRV2K 有 2000 LE。虽然不多,但对于很多事情来说已经足够了。 ADC 和 DAC 可免费使用。例如,您可以使用它来播放音乐或录制声音。

但我还没弄清楚如何将它与 Quartus 一起使用。本机开发(使用 yosys)对我来说不起作用。

可以去这个网站看看例程 http://www.agm-support.com.cn/index.php/%e4%be%8b%e7%a8%8b/

离线

#84 2025-04-02 14:43:05 分享评论

- cheng1986

- 会员

- 注册时间: 2023-06-14

- 已发帖子: 21

- 积分: 31

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

AG32开发软件包及 SDK 下载:

百度网盘:https://pan.baidu.com/s/17bp-zAnsYRuVMRTSSVHN5A&pwd=12ej

离线

#86 2025-04-06 16:01:15 分享评论

- DerBastian112

- 会员

- 注册时间: 2025-03-30

- 已发帖子: 5

- 积分: 10

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

大家好,

我现在非常确定 Quartus 的网络版不起作用。您根本无法创建设计分区。您需要执照。

问候,DerBastian112

离线

#87 2025-07-15 16:43:41 分享评论

- xiaoerge

- 会员

- 注册时间: 2020-07-16

- 已发帖子: 9

- 积分: 9

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

AGRV2K 有 2000 LE。虽然不多,但对于很多事情来说已经足够了。 ADC 和 DAC 可免费使用。例如,您可以使用它来播放音乐或录制声音。

但我还没弄清楚如何将它与 Quartus 一起使用。本机开发(使用 yosys)对我来说不起作用。

从https://pan.baidu.com/s/1wcBnqnray7bu4IURDIoDDQ?pwd=1205下载资料,\\AG32开发资料汇总\cpld-fpga文档\logic例程\2.adc例程(新建cpld空工程并添加adc) 有ADC和DAC的例子,稍微改一改单独用ADC/DAC/CMP都是可以的,我简单测了一下DAC,可以输出指定电压,但是我用DMA循环队列输出波形遇到了问题,发送到67450个数据就停止了,发生DMA错误,DAC模块中实现了类似定时器的功能作为DMA请求信号,翻看寄存器没看太明白DMA错误怎么产生的

离线

#88 2025-10-17 21:51:19 分享评论

- maozheng110

- 会员

- 注册时间: 2024-10-01

- 已发帖子: 34

- 积分: 19

Re: 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片

一般可以做个电机驱动 FPGA用来编解码和过流保护等

离线

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发