楼主 #1 2019-08-20 21:58:53 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

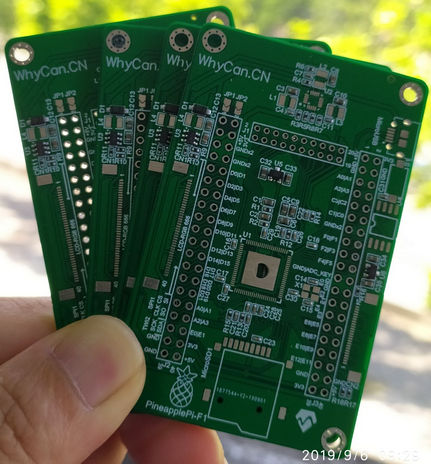

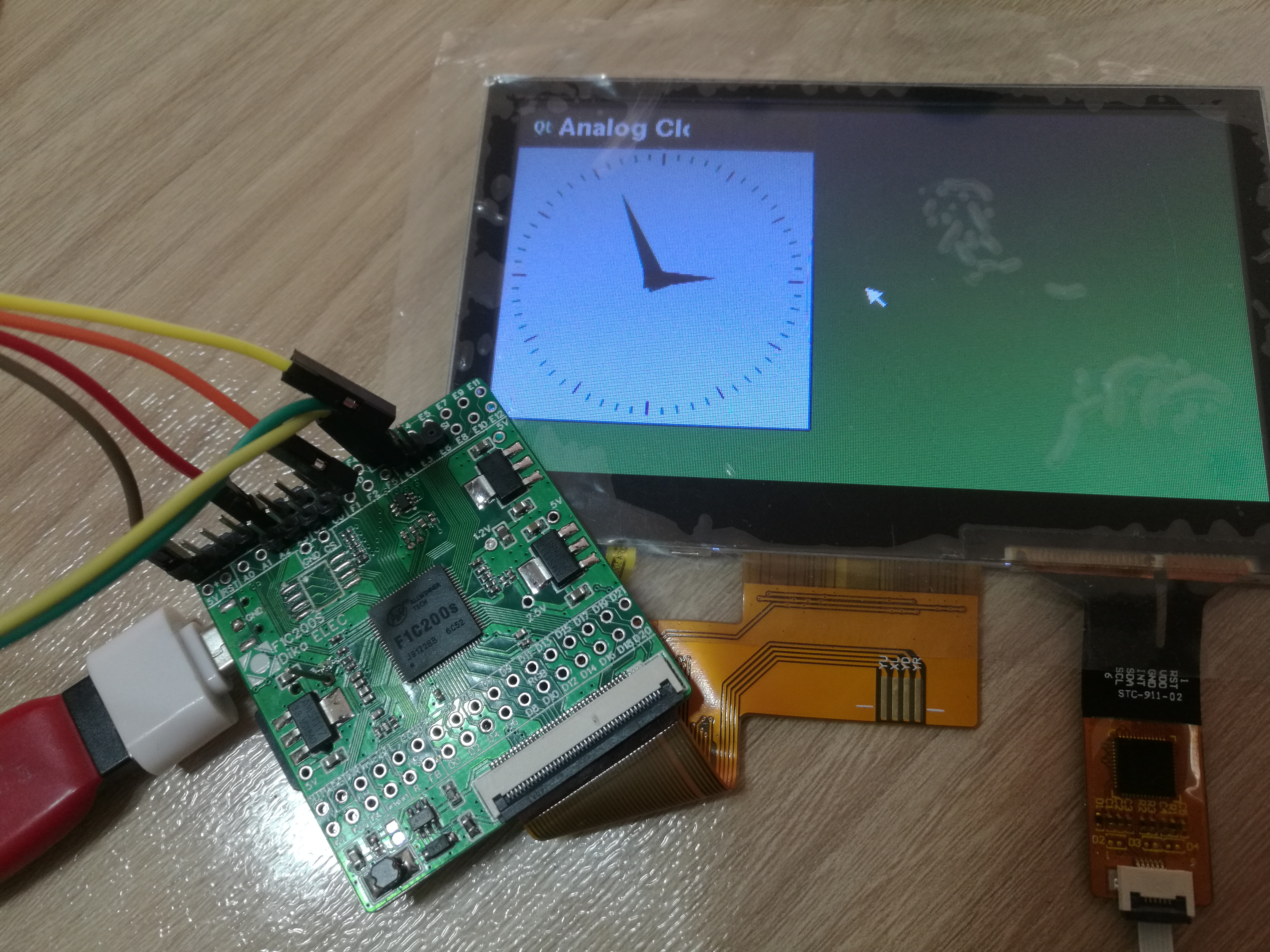

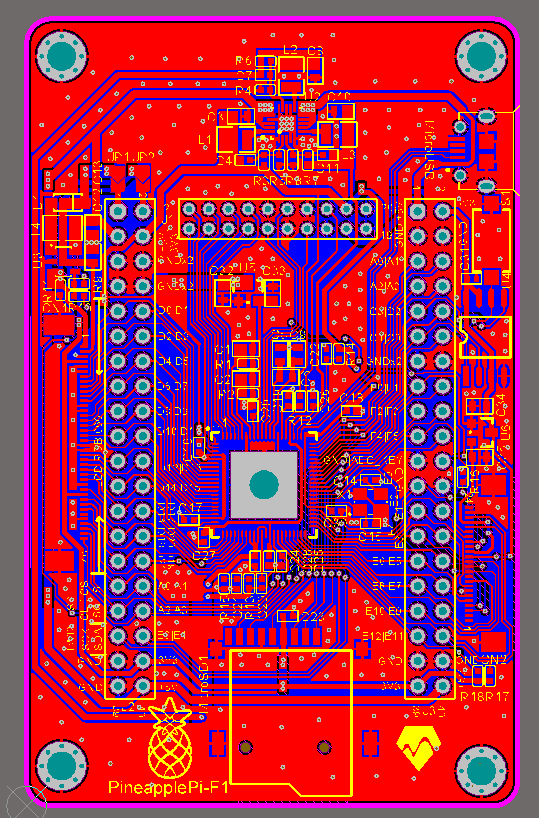

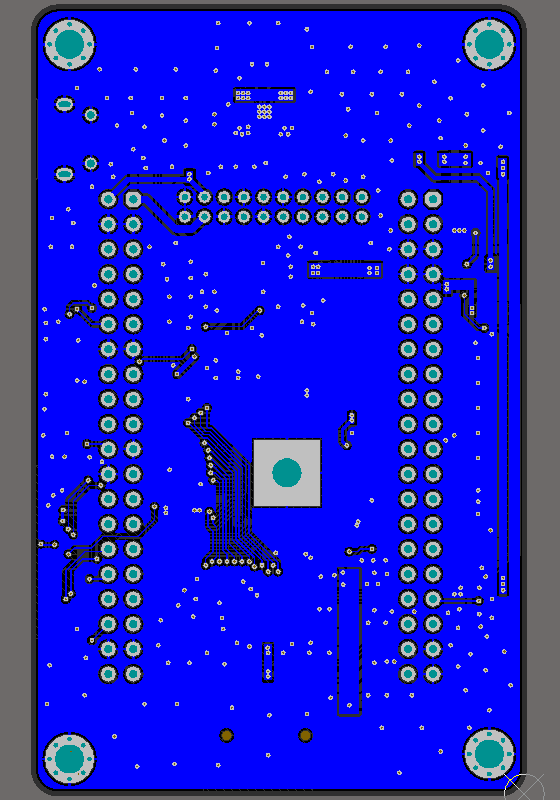

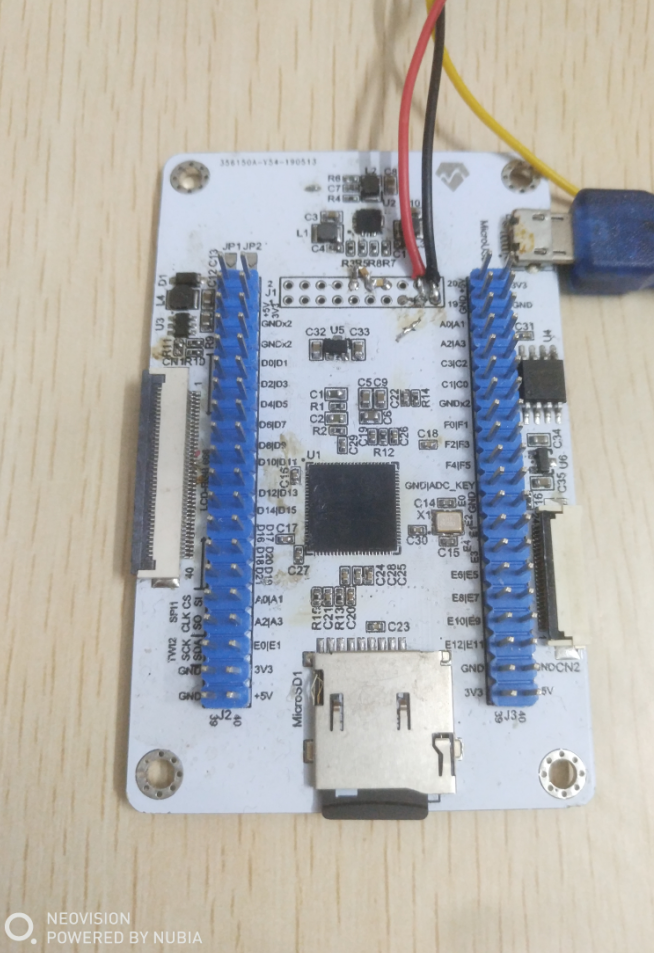

开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

1.板子是两层板,可以之间打样。

2.板子上全部io引出,间距可以插到洞洞板或者面包板上

3.dvp摄像头和RGB屏幕同时引出,支持摄像头采图实时显示

4.音频和视频都引出,方便各种填坑测试

5.四角带M3螺丝孔

6.支持堆叠扩展

7.新的PCB带按键,方便烧录和调试

板子叫做菠萝派,其实菠萝派在5年前就想好了的,logo都做好了,一直没有产出。现在借着F1芯片先出一个菠萝派F1先

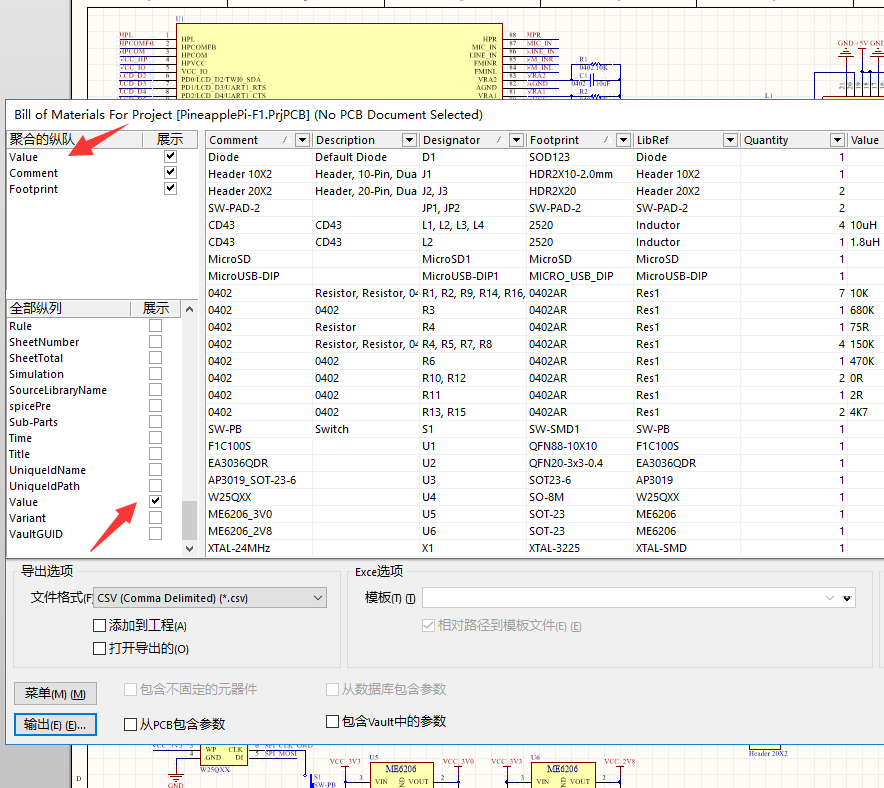

PCB工程By AltiumDesigner09

PineapplePi-F1_PCB.rar

以下是楼主 2019-09-01 25楼更新V2版本:

---------------------------------------------------------------------------

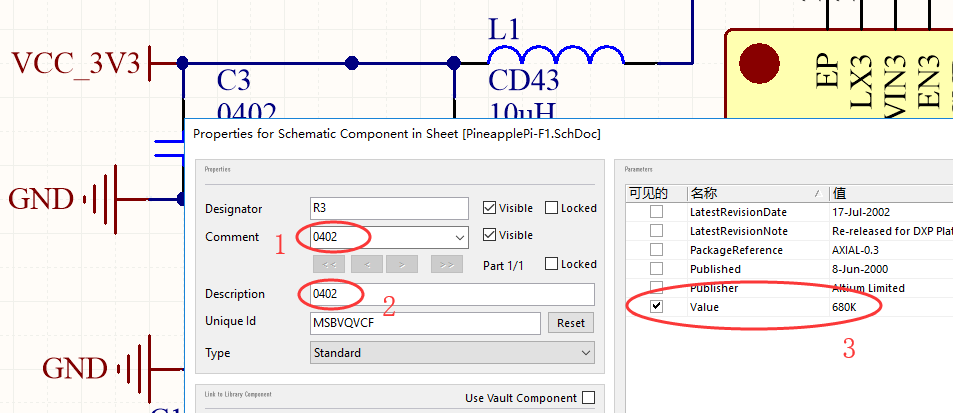

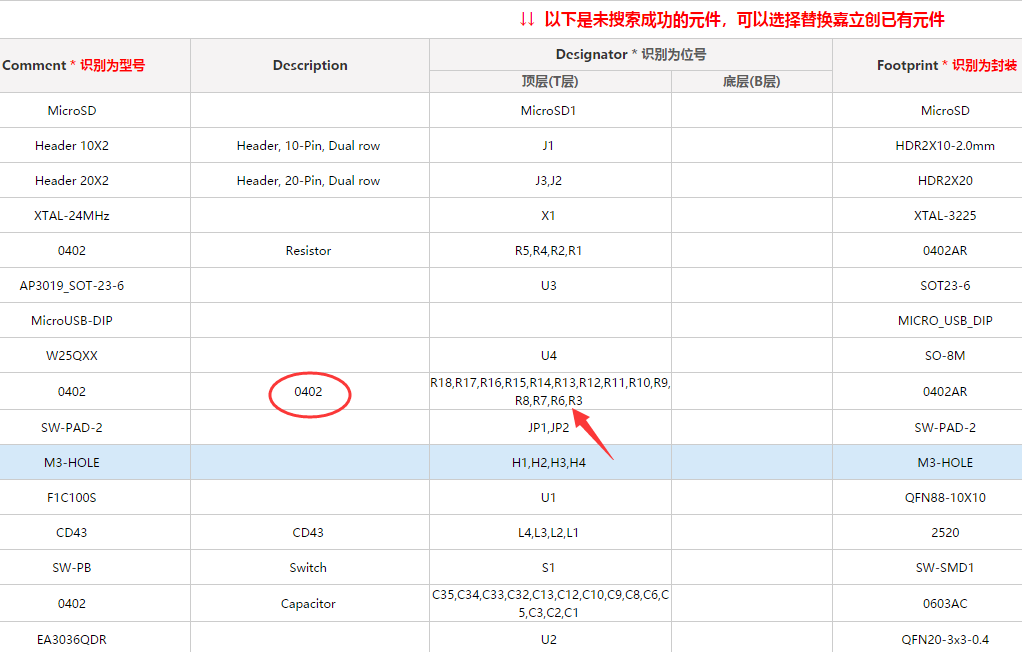

感谢楼主的无私分享, 这是第二版PCB文件:

DXP PCB: PineapplePi-F1_PCB_V2.rar

BOM表(用于JLC SMT): BoloPi-F1_V2.xls

离线

楼主 #2 2019-08-20 21:59:38 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

一楼感谢晕哥提供的坑网平台

离线

#3 2019-08-20 22:33:33 分享评论

- checkout

- 会员

- 注册时间: 2018-11-09

- 已发帖子: 173

- 积分: 168

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

摄像头采集实时显示调通了?

离线

楼主 #5 2019-08-20 22:45:59 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

checkout wrote:

摄像头采集实时显示调通了?

嗯,之前就调好了

离线

楼主 #6 2019-08-20 22:47:36 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

晕哥 wrote:

微凉VeiLiang wrote:

一楼感谢晕哥提供的坑网平台

得感谢包括楼主在内的各位热心网友才行!

啥时候开卖 ^_^ 坐等

这个暂时还没有打算:lol

离线

#7 2019-08-20 23:06:12 分享评论

- checkout

- 会员

- 注册时间: 2018-11-09

- 已发帖子: 173

- 积分: 168

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

犀鸠利

微凉VeiLiang wrote:

checkout wrote:

摄像头采集实时显示调通了?

嗯,之前就调好了

离线

#8 2019-08-21 00:08:11 分享评论

- sblpp

- 会员

- 注册时间: 2018-02-14

- 已发帖子: 165

- 积分: 40

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

感谢楼主分享~~~

非常感谢。能分享下源码吗?谢谢啦。

离线

#9 2019-08-21 09:41:59 分享评论

- Gentlepig

- 会员

- 注册时间: 2018-10-24

- 已发帖子: 1,409

- 积分: 1373.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

感谢分享。

过孔直径是不是有点小?10mil直径。嘉立创双面板过孔直径最小是0.3mm。

还有个疑问,RGB接口是为了方便画线按顺序连到了LCD接口上,那么应该在哪里设置RGB的对应关系呢?因为之前看到的荔枝派nano还有一些唱戏机的接口,都是LCD_D18~D23对应R2~R7,LCD_D10~D15对应G2~G7,LCD_D2~D7对应B2~B7。

最近编辑记录 Gentlepig (2019-08-21 09:55:19)

离线

楼主 #10 2019-08-21 10:13:04 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

sblpp wrote:

感谢楼主分享~~~

非常感谢。能分享下源码吗?谢谢啦。

有源pcb工程文件,f1c的开源代码的话暂时没有,先用网友分享的代码跑

离线

楼主 #11 2019-08-21 10:14:03 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

Gentlepig wrote:

感谢分享。

过孔直径是不是有点小?10mil直径。嘉立创双面板过孔直径最小是0.3mm。

还有个疑问,RGB接口是为了方便画线按顺序连到了LCD接口上,那么应该在哪里设置RGB的对应关系呢?因为之前看到的荔枝派nano还有一些唱戏机的接口,都是LCD_D18~D23对应R2~R7,LCD_D10~D15对应G2~G7,LCD_D2~D7对应B2~B7。

嗯,嘉立创我一直是安装0.2,0.45的标准画的,两层板一样是可以做的。lcd是按照荔枝派的接的

离线

#12 2019-08-21 10:24:57 分享评论

- 超级萌新

- 会员

- 注册时间: 2018-05-04

- 已发帖子: 408

- 积分: 407

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

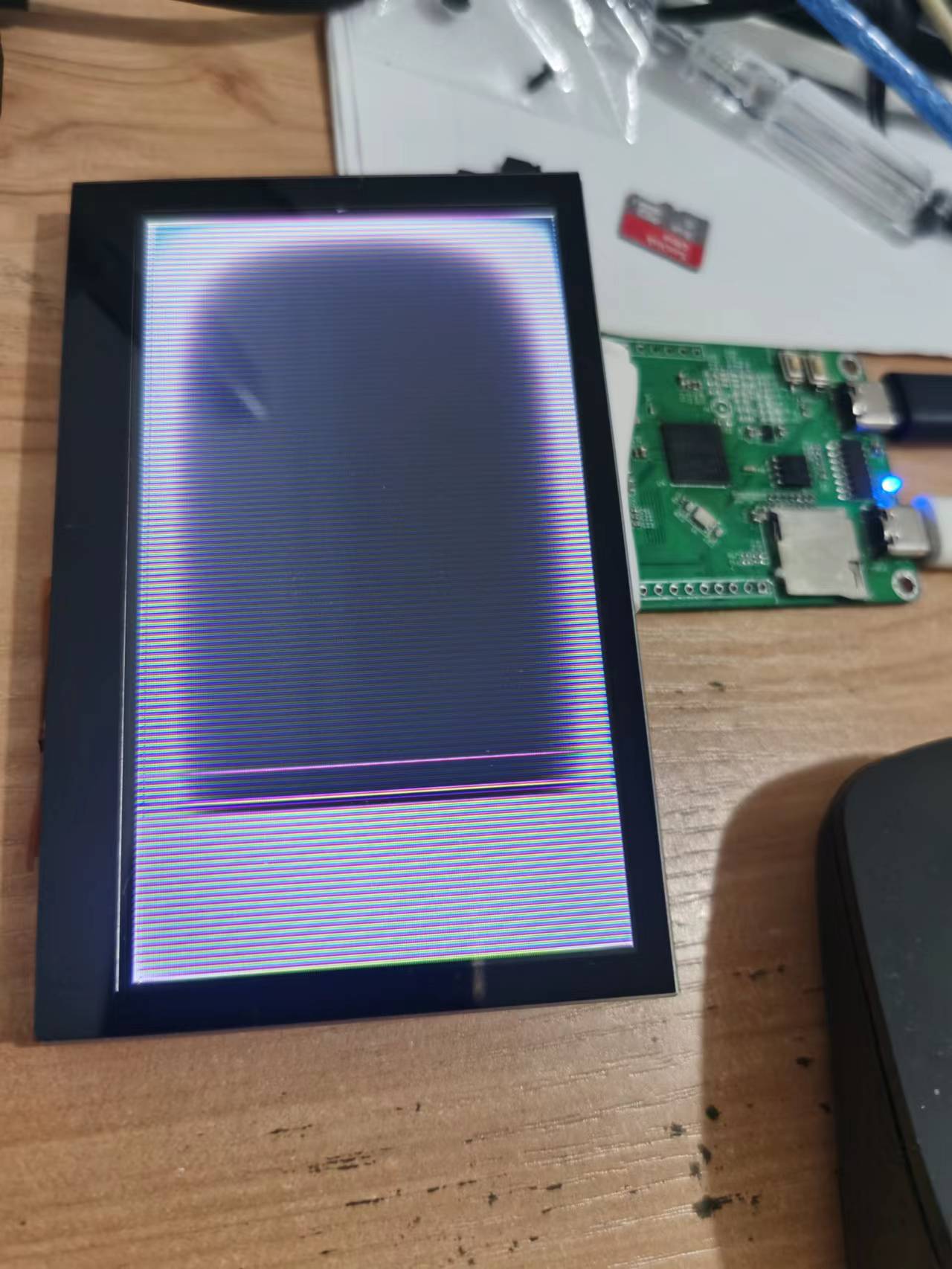

感谢大神,我等伸手党的福音 _

离线

#13 2019-08-21 11:11:46 分享评论

- k455619

- 会员

- 注册时间: 2018-07-29

- 已发帖子: 151

- 积分: 70

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

楼主用的哪款摄像头呢?

离线

#14 2019-08-21 11:39:29 分享评论

- k455619

- 会员

- 注册时间: 2018-07-29

- 已发帖子: 151

- 积分: 70

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

楼主 我有两个问题 :

1.Dvp接口 10脚DGND 没有接地

2.Dvp接口 15脚是VCC2.8V,我看了下0V2640的原理图应该是1.2V吧

离线

#15 2019-08-21 12:00:02 分享评论

- lcfmax

- 会员

- 注册时间: 2018-04-13

- 已发帖子: 329

- 积分: 272.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

不错,没啥时间玩了

离线

#16 2019-08-21 16:18:18 分享评论

- 2B青年欢乐多

- 会员

- 注册时间: 2019-01-08

- 已发帖子: 13

- 积分: 13

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

666,PCB的3D很漂亮

离线

#17 2019-08-21 20:16:04 分享评论

- Quotation

- 会员

- 注册时间: 2018-10-04

- 已发帖子: 305

- 积分: 264.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

谢谢,学习了。用F1C100s画了好几块板了,每次供电部分都布得很纠结。下次学你的做法,在底部焊盘周围走线。

发现我把底部焊盘画的过大了,所以没什么空间走线。

离线

楼主 #19 2019-08-22 17:37:07 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

k455619 wrote:

楼主 我有两个问题 :

1.Dvp接口 10脚DGND 没有接地

2.Dvp接口 15脚是VCC2.8V,我看了下0V2640的原理图应该是1.2V吧

嗯,没说没发现呢,地是要接,我用的sensor内部已经接了,不过这个可以出来打个过孔。

电压可以通过改ldo来改。不过要用两路电压供电的sensor可能就不适合了

离线

#20 2019-08-29 09:07:34 分享评论

- Jmhh247

- 会员

- 注册时间: 2018-12-21

- 已发帖子: 262

- 积分: 262

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

楼主,菠萝派啥时候开卖啊

离线

楼主 #23 2019-09-01 00:12:45 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

晕哥 wrote:

/files/members/3/QQ20190831202648.png

/files/members/3/QQ20190831204951.png

在楼主的耐心指导下, 终于把优惠券花出去了.

非常感谢晕哥吃螃蟹,期待中

离线

楼主 #24 2019-09-01 00:17:51 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

更新了一下。

增加了摄像头DVDD 和 AVDD分开LDO供电,如果DVDD和AVDD一样则可以通过背面的跳线进行端接即可,可不贴DVDD的LDO

修复了14楼的摄像头10脚接地问题

增加了TVIN0脚的输入滤波电路。方便调试TVD

增加了Markpoint,方便贴片

最后附上GitHub项目连接,欢迎star,和 提出修改意见

https://github.com/VeiLiang/BoloPi_PCB

离线

#25 2019-09-01 15:12:09 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,479

- 积分: 9207

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

离线

#26 2019-09-02 09:07:43 分享评论

- IC爬虫

- 会员

- 注册时间: 2018-06-18

- 已发帖子: 27

- 积分: 26.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

感谢楼主的无私分享

离线

#27 2019-09-16 15:45:55 分享评论

- myxiaonia

- 会员

- 注册时间: 2019-06-18

- 已发帖子: 83

- 积分: 51.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

淘宝上卖裸机代码的是您吗?期待你搞定裸机usb

离线

#29 2019-09-21 14:01:45 分享评论

- zenghaibo

- 会员

- 注册时间: 2019-07-15

- 已发帖子: 63

- 积分: 57

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

微凉VeiLiang wrote:

checkout wrote:

摄像头采集实时显示调通了?

嗯,之前就调好了

这个可以分享,学习学习

离线

#30 2019-09-21 14:03:51 分享评论

- zenghaibo

- 会员

- 注册时间: 2019-07-15

- 已发帖子: 63

- 积分: 57

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

zenghaibo wrote:

微凉VeiLiang wrote:

checkout wrote:

摄像头采集实时显示调通了?

嗯,之前就调好了

这个可以分享,学习学习

板子什么可以买到你的样品

离线

#32 2019-09-21 14:47:59 分享评论

- kekemuyu

- 会员

- 注册时间: 2018-12-13

- 已发帖子: 856

- 积分: 697

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

本来想diy的,pcb都提交给嘉利创了,无奈贴片太贵了,5块板子下来要200多了,就这还不加插件的钱呢?就放弃了

离线

楼主 #34 2019-09-21 15:33:10 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

![]()

我朋友在帮忙做这个了,自己手工贴,下周可能会出来十片样品

离线

楼主 #35 2019-09-21 15:33:47 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

晕哥 wrote:

/files/members/3/QQ20190921151654.jpg

@kekemuyu 这是我收到的,还没时间动手,要补焊好些零件,如果有兴趣可以加我QQ赠送两片, 估计坑不少。

想省事还是买荔枝派nano方便,35元一片包邮 ^_^

嘉立创的贴片很是尴尬

离线

#37 2019-09-21 15:40:48 分享评论

- kekemuyu

- 会员

- 注册时间: 2018-12-13

- 已发帖子: 856

- 积分: 697

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

晕哥 wrote:

/files/members/3/QQ20190921151654.jpg

@kekemuyu 这是我收到的,还没时间动手,要补焊好些零件,如果有兴趣可以加我QQ赠送两片, 估计坑不少。

想省事还是买荔枝派nano方便,35元一片包邮 ^_^

感谢老大,我有nano,留给需要的同学吧

最近编辑记录 kekemuyu (2019-09-21 15:42:19)

离线

楼主 #38 2019-09-21 22:31:52 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

晕哥 wrote:

@微凉VeiLiang

还可以预定不?

可以的

离线

#39 2019-09-23 17:17:37 分享评论

- sysclock

- 会员

- 注册时间: 2018-10-21

- 已发帖子: 7

- 积分: 2

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

zan!

大力顶楼主,中国好青年。

离线

#40 2019-09-23 17:51:44 分享评论

- sysclock

- 会员

- 注册时间: 2018-10-21

- 已发帖子: 7

- 积分: 2

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

还可以预定吗?

可以的话,请留一个给我,手机wx 139-1020-0543 谢谢

微凉VeiLiang wrote:

晕哥 wrote:

@微凉VeiLiang

还可以预定不?

可以的

离线

楼主 #41 2019-09-29 17:37:05 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

sysclock wrote:

还可以预定吗?

可以的话,请留一个给我,手机wx 139-1020-0543 谢谢微凉VeiLiang wrote:

晕哥 wrote:

@微凉VeiLiang

还可以预定不?

可以的

可以,出来后我联系你

离线

#42 2019-10-11 10:37:01 分享评论

- cris8259

- 会员

- 注册时间: 2019-09-25

- 已发帖子: 283

- 积分: 82

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

厉害了,顶一个,有没有购买链接

离线

#43 2019-10-31 02:19:21 分享评论

- xufujun6144

- 会员

- 注册时间: 2019-10-31

- 已发帖子: 1

- 积分: 1

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

非常感谢,下载看看

离线

#44 2019-10-31 09:42:01 分享评论

- tianjjff

- 会员

- 注册时间: 2018-12-24

- 已发帖子: 129

- 积分: 22

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

顶一个,感谢楼主!

离线

#45 2019-11-04 18:14:45 分享评论

- billnie

- 会员

- 注册时间: 2018-11-13

- 已发帖子: 48

- 积分: 33

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

@晕哥,最后修改的pcb有问题没有?也准备在上面改一版。适应自己的扩展板

离线

#47 2019-11-19 14:40:16 分享评论

- cris8259

- 会员

- 注册时间: 2019-09-25

- 已发帖子: 283

- 积分: 82

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

板子很漂亮。有没有大神挣个辛苦费帮我也画个小板

离线

#48 2019-11-21 15:54:18 分享评论

- hyfm520

- 会员

- 注册时间: 2019-11-21

- 已发帖子: 1

- 积分: 1

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

感谢楼主的无私分享,板子画的真漂亮。

离线

#49 2020-01-01 11:54:31 分享评论

- wecandump

- 会员

- 注册时间: 2019-12-27

- 已发帖子: 15

- 积分: 15

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

好板子,看着很漂亮,感谢分享学习

离线

#52 2020-01-05 14:40:34 分享评论

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

记录:

OV2640

core:1.2V ±5%

analog:2.5-3.0V

IO:1.7V to 3.3V

总结:使用3.3V需要3个电压

OV5640

core:1.5V ±5%(内置1.5V稳压器)

analog:2.6-3.0V(2.8V typical)

IO:1.8V/2.8V

总结:使用2.8V需要1个电压

GC0308

DVDD28=2.8V/3.3V,其余电压内置稳压器

总结:使用2.8V需要1个电压

最近编辑记录 迪卡 (2020-01-05 14:53:06)

离线

#53 2020-01-05 16:23:00 分享评论

- pla155

- 会员

- 注册时间: 2020-01-05

- 已发帖子: 3

- 积分: 3

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

感谢楼主分享~~~

非常感谢。能分享下源码吗?谢谢啦。

离线

#55 2020-01-16 22:44:53 分享评论

- joyhope

- 会员

- 注册时间: 2020-01-16

- 已发帖子: 39

- 积分: 39

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

这个板子先有卖吗?

离线

#56 2020-02-17 09:13:50 分享评论

- everlink

- 会员

- 注册时间: 2020-02-16

- 已发帖子: 93

- 积分: 93

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

晕哥 wrote:

想省事还是买荔枝派nano方便,35元一片包邮 ^_^

现在还有包邮的吗,打算整。。。。

离线

#57 2020-03-27 16:39:00 分享评论

- sea18c

- 会员

- 注册时间: 2019-08-05

- 已发帖子: 230

- 积分: 222.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

电阻触摸接口有验证吗,好像不对呀。屏接线与荔枝派是反的,一个是RGB,一个是BGR.

离线

#58 2020-03-29 21:58:40 分享评论

- 孤星泪

- 会员

- 注册时间: 2020-03-18

- 已发帖子: 235

- 积分: 231

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

sea18c wrote:

电阻触摸接口有验证吗,好像不对呀。屏接线与荔枝派是反的,一个是RGB,一个是BGR.

有寄存器可以切换, 全志soc设计的时候就考虑这种情况了, 方便布线吧.

离线

#59 2020-03-30 08:54:08 分享评论

- sea18c

- 会员

- 注册时间: 2019-08-05

- 已发帖子: 230

- 积分: 222.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

孤星泪 wrote:

有寄存器可以切换, 全志soc设计的时候就考虑这种情况了, 方便布线吧.

RGB这个我知道,我只是表明它的板与荔枝派是反的

离线

#60 2020-03-31 20:13:14 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,479

- 积分: 9207

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

sea18c wrote:

电阻触摸接口有验证吗,好像不对呀。屏接线与荔枝派是反的,一个是RGB,一个是BGR.

这里有RGB/BGR的切换补丁:

https://gitee.com/jiang_xing/f1c100s_buildroot/blob/master/board/f1c100s/patch/linux_kernel.patch

--- a/arch/arm/boot/dts/suniv-f1c100s.dtsi 2019-08-29 14:30:28.000000000 +0800

+++ b/arch/arm/boot/dts/suniv-f1c100s.dtsi 2020-01-21 19:26:46.466638364 +0800

@@ -4,6 +4,10 @@

* Copyright 2018 Mesih Kilinc <mesihkilinc@gmail.com>

*/

+#include <dt-bindings/interrupt-controller/arm-gic.h>

+#include <dt-bindings/clock/suniv-ccu-f1c100s.h>

+#include <dt-bindings/reset/suniv-ccu-f1c100s.h>

+

/ {

#address-cells = <1>;

#size-cells = <1>;

@@ -31,6 +35,12 @@

device_type = "cpu";

};

};

+

+ de: display-engine {

+ compatible = "allwinner,suniv-f1c100s-display-engine";

+ allwinner,pipelines = <&fe0>;

+ status = "disabled";

+ };

soc {

compatible = "simple-bus";

@@ -62,6 +72,68 @@

};

};

+ spi0: spi@1c05000 {

+ compatible = "allwinner,suniv-spi",

+ "allwinner,sun8i-h3-spi";

+ reg = <0x01c05000 0x1000>;

+ interrupts = <10>;

+ clocks = <&ccu CLK_BUS_SPI0>, <&ccu CLK_BUS_SPI0>;

+ clock-names = "ahb", "mod";

+ resets = <&ccu RST_BUS_SPI0>;

+ status = "disabled";

+ #address-cells = <1>;

+ #size-cells = <0>;

+ };

+

+ spi1: spi@1c06000 {

+ compatible = "allwinner,suniv-spi",

+ "allwinner,sun8i-h3-spi";

+ reg = <0x01c06000 0x1000>;

+ interrupts = <11>;

+ clocks = <&ccu CLK_BUS_SPI1>, <&ccu CLK_BUS_SPI1>;

+ clock-names = "ahb", "mod";

+ resets = <&ccu RST_BUS_SPI1>;

+ status = "disabled";

+ #address-cells = <1>;

+ #size-cells = <0>;

+ };

+

+ tcon0: lcd-controller@1c0c000 {

+ compatible = "allwinner,suniv-f1c100s-tcon";

+ reg = <0x01c0c000 0x1000>;

+ interrupts = <29>;

+ clocks = <&ccu CLK_BUS_LCD>,

+ <&ccu CLK_TCON>;

+ clock-names = "ahb",

+ "tcon-ch0";

+ clock-output-names = "tcon-pixel-clock";

+ resets = <&ccu RST_BUS_LCD>;

+ reset-names = "lcd";

+ status = "disabled";

+

+ ports {

+ #address-cells = <1>;

+ #size-cells = <0>;

+

+ tcon0_in: port@0 {

+ #address-cells = <1>;

+ #size-cells = <0>;

+ reg = <0>;

+

+ tcon0_in_be0: endpoint@0 {

+ reg = <0>;

+ remote-endpoint = <&be0_out_tcon0>;

+ };

+ };

+

+ tcon0_out: port@1 {

+ #address-cells = <1>;

+ #size-cells = <0>;

+ reg = <1>;

+ };

+ };

+ };

+

ccu: clock@1c20000 {

compatible = "allwinner,suniv-f1c100s-ccu";

reg = <0x01c20000 0x400>;

@@ -71,6 +143,19 @@

#reset-cells = <1>;

};

+ i2c0: i2c@1C27000 {

+ compatible = "allwinner,sun6i-a31-i2c";

+ reg = <0x01C27000 0x400>;

+ interrupts = <7>;

+ clocks = <&ccu CLK_BUS_I2C0>;

+ resets = <&ccu RST_BUS_I2C0>;

+ pinctrl-names = "default";

+ pinctrl-0 = <&i2c0_pins>;

+ status = "disabled";

+ #address-cells = <1>;

+ #size-cells = <0>;

+ };

+

intc: interrupt-controller@1c20400 {

compatible = "allwinner,suniv-f1c100s-ic";

reg = <0x01c20400 0x400>;

@@ -82,17 +167,41 @@

compatible = "allwinner,suniv-f1c100s-pinctrl";

reg = <0x01c20800 0x400>;

interrupts = <38>, <39>, <40>;

- clocks = <&ccu 37>, <&osc24M>, <&osc32k>;

+ clocks = <&ccu CLK_BUS_PIO>, <&osc24M>, <&osc32k>;

clock-names = "apb", "hosc", "losc";

gpio-controller;

interrupt-controller;

#interrupt-cells = <3>;

#gpio-cells = <3>;

+ i2c0_pins: i2c0 {

+ pins = "PE11", "PE12";

+ function = "i2c0";

+ };

+

uart0_pe_pins: uart0-pe-pins {

pins = "PE0", "PE1";

function = "uart0";

};

+

+ lcd_rgb666_pins: lcd-rgb666-pins {

+ pins = "PD0", "PD1", "PD2", "PD3", "PD4",

+ "PD5", "PD6", "PD7", "PD8", "PD9",

+ "PD10", "PD11", "PD12", "PD13", "PD14",

+ "PD15", "PD16", "PD17", "PD18", "PD19",

+ "PD20", "PD21";

+ function = "lcd";

+ };

+

+ mmc0_pins: mmc0-pins {

+ pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5";

+ function = "mmc0";

+ };

+

+ spi0_pins_a: spi0-pins-pc {

+ pins = "PC0", "PC1", "PC2", "PC3";

+ function = "spi0";

+ };

};

timer@1c20c00 {

@@ -102,20 +211,49 @@

clocks = <&osc24M>;

};

+ mmc0: mmc@1c0f000 {

+ compatible = "allwinner,suniv-f1c100s-mmc",

+ "allwinner,sun7i-a20-mmc";

+ reg = <0x01c0f000 0x1000>;

+ clocks = <&ccu CLK_BUS_MMC0>,

+ <&ccu CLK_MMC0>,

+ <&ccu CLK_MMC0_OUTPUT>,

+ <&ccu CLK_MMC0_SAMPLE>;

+ clock-names = "ahb",

+ "mmc",

+ "output",

+ "sample";

+ resets = <&ccu RST_BUS_MMC0>;

+ reset-names = "ahb";

+ interrupts = <23>;

+ pinctrl-names = "default";

+ pinctrl-0 = <&mmc0_pins>;

+ status = "disabled";

+ #address-cells = <1>;

+ #size-cells = <0>;

+ };

+

wdt: watchdog@1c20ca0 {

compatible = "allwinner,suniv-f1c100s-wdt",

"allwinner,sun4i-a10-wdt";

reg = <0x01c20ca0 0x20>;

};

+ lradc: lradc@1C23400 {

+ compatible = "allwinner,sun4i-a10-lradc-keys";

+ reg = <0x01C23400 0x400>;

+ interrupts = <22>;

+ status = "disabled";

+ };

+

uart0: serial@1c25000 {

compatible = "snps,dw-apb-uart";

reg = <0x01c25000 0x400>;

interrupts = <1>;

reg-shift = <2>;

reg-io-width = <4>;

- clocks = <&ccu 38>;

- resets = <&ccu 24>;

+ clocks = <&ccu CLK_BUS_UART0>;

+ resets = <&ccu RST_BUS_UART0>;

status = "disabled";

};

@@ -125,8 +263,8 @@

interrupts = <2>;

reg-shift = <2>;

reg-io-width = <4>;

- clocks = <&ccu 39>;

- resets = <&ccu 25>;

+ clocks = <&ccu CLK_BUS_UART1>;

+ resets = <&ccu RST_BUS_UART1>;

status = "disabled";

};

@@ -136,9 +274,107 @@

interrupts = <3>;

reg-shift = <2>;

reg-io-width = <4>;

- clocks = <&ccu 40>;

- resets = <&ccu 26>;

+ clocks = <&ccu CLK_BUS_UART2>;

+ resets = <&ccu RST_BUS_UART2>;

+ status = "disabled";

+ };

+

+ usb_otg: usb@1c13000 {

+ compatible = "allwinner,suniv-musb";

+ reg = <0x01c13000 0x0400>;

+ clocks = <&ccu CLK_BUS_OTG>;

+ resets = <&ccu RST_BUS_OTG>;

+ interrupts = <26>;

+ interrupt-names = "mc";

+ phys = <&usbphy 0>;

+ phy-names = "usb";

+ extcon = <&usbphy 0>;

+ allwinner,sram = <&otg_sram 1>;

+ status = "disabled";

+ };

+

+ usbphy: phy@1c13400 {

+ compatible = "allwinner,suniv-usb-phy";

+ reg = <0x01c13400 0x10>;

+ reg-names = "phy_ctrl";

+ clocks = <&ccu CLK_USB_PHY0>;

+ clock-names = "usb0_phy";

+ resets = <&ccu RST_USB_PHY0>;

+ reset-names = "usb0_reset";

+ #phy-cells = <1>;

+ status = "disabled";

+ };

+

+ fe0: display-frontend@1e00000 {

+ compatible = "allwinner,suniv-f1c100s-display-frontend";

+ reg = <0x01e00000 0x20000>;

+ interrupts = <30>;

+ clocks = <&ccu CLK_BUS_DE_FE>, <&ccu CLK_DE_FE>,

+ <&ccu CLK_DRAM_DE_FE>;

+ clock-names = "ahb", "mod",

+ "ram";

+ resets = <&ccu RST_BUS_DE_FE>;

status = "disabled";

+

+ ports {

+ #address-cells = <1>;

+ #size-cells = <0>;

+

+ fe0_out: port@1 {

+ #address-cells = <1>;

+ #size-cells = <0>;

+ reg = <1>;

+

+ fe0_out_be0: endpoint@0 {

+ reg = <0>;

+ remote-endpoint = <&be0_in_fe0>;

+ };

+ };

+ };

+ };

+

+ be0: display-backend@1e60000 {

+ compatible = "allwinner,suniv-f1c100s-display-backend";

+ reg = <0x01e60000 0x10000>;

+ reg-names = "be";

+ interrupts = <31>;

+ clocks = <&ccu CLK_BUS_DE_BE>, <&ccu CLK_DE_BE>,

+ <&ccu CLK_DRAM_DE_BE>;

+ clock-names = "ahb", "mod",

+ "ram";

+ resets = <&ccu RST_BUS_DE_BE>;

+ reset-names = "be";

+ assigned-clocks = <&ccu CLK_DE_BE>;

+ assigned-clock-rates = <300000000>;

+ rgb-channel-swap = <0>;

+

+ ports {

+ #address-cells = <1>;

+ #size-cells = <0>;

+

+ be0_in: port@0 {

+ #address-cells = <1>;

+ #size-cells = <0>;

+ reg = <0>;

+

+ be0_in_fe0: endpoint@0 {

+ reg = <0>;

+ remote-endpoint = <&fe0_out_be0>;

+ };

+ };

+

+ be0_out: port@1 {

+ #address-cells = <1>;

+ #size-cells = <0>;

+ reg = <1>;

+

+ be0_out_tcon0: endpoint@0 {

+ reg = <0>;

+ remote-endpoint = <&tcon0_in_be0>;

+ };

+ };

+ };

};

};

};

+

--- a/arch/arm/boot/dts/suniv-f1c100s-licheepi-nano.dts 2019-08-29 14:30:28.000000000 +0800

+++ b/arch/arm/boot/dts/suniv-f1c100s-licheepi-nano.dts 2020-01-21 19:26:46.470638361 +0800

@@ -1,10 +1,14 @@

-// SPDX-License-Identifier: (GPL-2.0+ OR X11)

/*

* Copyright 2018 Icenowy Zheng <icenowy@aosc.io>

*/

/dts-v1/;

+

#include "suniv-f1c100s.dtsi"

+#include <dt-bindings/gpio/gpio.h>

+#include <dt-bindings/input/input.h>

+#include <dt-bindings/interrupt-controller/irq.h>

+#include "sunxi-common-regulators.dtsi"

/ {

model = "Lichee Pi Nano";

@@ -12,11 +16,142 @@

aliases {

serial0 = &uart0;

+ spi0 = &spi0;

};

chosen {

stdout-path = "serial0:115200n8";

};

+

+ reg_vcc3v3: vcc3v3 {

+ compatible = "regulator-fixed";

+ regulator-name = "vcc3v3";

+ regulator-min-microvolt = <3300000>;

+ regulator-max-microvolt = <3300000>;

+ };

+

+ panel: panel {

+ compatible = "ampire,am-480272h3tmqw-t01h";

+ #address-cells = <1>;

+ #size-cells = <0>;

+ enable-gpios = <&pio 4 6 GPIO_ACTIVE_HIGH>;

+ power-supply = <®_vcc3v3>;

+

+ port@0 {

+ reg = <0>;

+ #address-cells = <1>;

+ #size-cells = <0>;

+

+ panel_input: endpoint@0 {

+ reg = <0>;

+ remote-endpoint = <&tcon0_out_lcd>;

+ };

+ };

+ };

+};

+

+&otg_sram {

+ status = "okay";

+};

+

+&usb_otg {

+ dr_mode = "otg";

+ status = "okay";

+};

+

+&usbphy {

+ usb0_id_det-gpio = <&pio 4 2 GPIO_ACTIVE_HIGH>; /* PE2 */

+ status = "okay";

+};

+

+&pio {

+ vcc-pc-supply = <®_vcc3v3>;

+ vcc-pd-supply = <®_vcc3v3>;

+ vcc-pe-supply = <®_vcc3v3>;

+ vcc-pf-supply = <®_vcc3v3>;

+};

+

+&be0 {

+ status = "okay";

+};

+

+&de {

+ status = "okay";

+};

+

+&tcon0 {

+ pinctrl-names = "default";

+ pinctrl-0 = <&lcd_rgb666_pins>;

+ status = "okay";

+};

+

+&tcon0_out {

+ tcon0_out_lcd: endpoint@0 {

+ reg = <0>;

+ remote-endpoint = <&panel_input>;

+ };

+};

+

+&i2c0 {

+ pinctrl-0 = <&i2c0_pins>;

+ pinctrl-names = "default";

+ status = "okay";

+};

+

+&mmc0 {

+ vmmc-supply = <®_vcc3v3>;

+ bus-width = <4>;

+ broken-cd;

+ status = "okay";

+};

+

+&pio {

+ ts_reset_pin: ts_reset_pin@0 {

+ pins = "PE9";

+ function = "gpio_out";

+ };

+};

+

+&spi0 {

+ pinctrl-names = "default";

+ pinctrl-0 = <&spi0_pins_a>;

+ status = "okay";

+

+ flash: w25q128@0 {

+ #address-cells = <1>;

+ #size-cells = <1>;

+ compatible = "winbond,w25q128", "jedec,spi-nor";

+ reg = <0>;

+ spi-max-frequency = <50000000>;

+ partitions {

+ compatible = "fixed-partitions";

+ #address-cells = <1>;

+ #size-cells = <1>;

+

+ partition@0 {

+ label = "u-boot";

+ reg = <0x000000 0x100000>;

+ read-only;

+ };

+

+ partition@100000 {

+ label = "dtb";

+ reg = <0x100000 0x10000>;

+ read-only;

+ };

+

+ partition@110000 {

+ label = "kernel";

+ reg = <0x110000 0x400000>;

+ read-only;

+ };

+

+ partition@520000 {

+ label = "rootfs";

+ reg = <0x510000 0xAF0000>;

+ };

+ };

+ };

};

&uart0 {

--- a/drivers/mtd/spi-nor/spi-nor.c 2019-08-29 14:30:28.000000000 +0800

+++ b/drivers/mtd/spi-nor/spi-nor.c 2020-01-21 19:26:46.470638361 +0800

@@ -2118,7 +2118,7 @@

},

{ "w25q80", INFO(0xef5014, 0, 64 * 1024, 16, SECT_4K) },

{ "w25q80bl", INFO(0xef4014, 0, 64 * 1024, 16, SECT_4K) },

- { "w25q128", INFO(0xef4018, 0, 64 * 1024, 256, SECT_4K) },

+ { "w25q128", INFO(0xef4018, 0, 64 * 1024, 256, 0) },

{ "w25q256", INFO(0xef4019, 0, 64 * 1024, 512, SECT_4K | SPI_NOR_DUAL_READ | SPI_NOR_QUAD_READ) },

{ "w25m512jv", INFO(0xef7119, 0, 64 * 1024, 1024,

SECT_4K | SPI_NOR_QUAD_READ | SPI_NOR_DUAL_READ) },

--- a/drivers/gpu/drm/sun4i/sun4i_tcon.c 2019-08-29 14:30:28.000000000 +0800

+++ b/drivers/gpu/drm/sun4i/sun4i_tcon.c 2020-01-21 19:26:46.470638361 +0800

@@ -1419,6 +1419,15 @@

return 0;

}

+static const struct sun4i_tcon_quirks suniv_f1c100s_quirks = {

+ /*

+ * The F1C100s SoC has a second channel in TCON, but the clock input of

+ * it is not documented.

+ */

+ .has_channel_0 = true,

+ /* .has_channel_1 = true, */

+};

+

static const struct sun4i_tcon_quirks sun4i_a10_quirks = {

.has_channel_0 = true,

.has_channel_1 = true,

@@ -1487,6 +1496,7 @@

/* sun4i_drv uses this list to check if a device node is a TCON */

const struct of_device_id sun4i_tcon_of_table[] = {

+ { .compatible = "allwinner,suniv-f1c100s-tcon", .data = &suniv_f1c100s_quirks },

{ .compatible = "allwinner,sun4i-a10-tcon", .data = &sun4i_a10_quirks },

{ .compatible = "allwinner,sun5i-a13-tcon", .data = &sun5i_a13_quirks },

{ .compatible = "allwinner,sun6i-a31-tcon", .data = &sun6i_a31_quirks },

--- a/drivers/gpu/drm/sun4i/sun4i_drv.c 2019-08-29 14:30:28.000000000 +0800

+++ b/drivers/gpu/drm/sun4i/sun4i_drv.c 2020-01-21 19:26:46.470638361 +0800

@@ -164,7 +164,8 @@

static bool sun4i_drv_node_is_frontend(struct device_node *node)

{

- return of_device_is_compatible(node, "allwinner,sun4i-a10-display-frontend") ||

+ return of_device_is_compatible(node, "allwinner,suniv-f1c100s-display-frontend") ||

+ of_device_is_compatible(node, "allwinner,sun4i-a10-display-frontend") ||

of_device_is_compatible(node, "allwinner,sun5i-a13-display-frontend") ||

of_device_is_compatible(node, "allwinner,sun6i-a31-display-frontend") ||

of_device_is_compatible(node, "allwinner,sun7i-a20-display-frontend") ||

@@ -404,6 +405,7 @@

}

static const struct of_device_id sun4i_drv_of_table[] = {

+ { .compatible = "allwinner,suniv-f1c100s-display-engine" },

{ .compatible = "allwinner,sun4i-a10-display-engine" },

{ .compatible = "allwinner,sun5i-a10s-display-engine" },

{ .compatible = "allwinner,sun5i-a13-display-engine" },

--- a/drivers/gpu/drm/sun4i/sunxi_engine.h 2019-08-29 14:30:28.000000000 +0800

+++ b/drivers/gpu/drm/sun4i/sunxi_engine.h 2020-01-21 19:26:46.470638361 +0800

@@ -124,6 +124,7 @@

struct regmap *regs;

int id;

+ int rgb_swap;

/* Engine list management */

struct list_head list;

--- a/drivers/gpu/drm/sun4i/sun4i_backend.h 2019-08-29 14:30:28.000000000 +0800

+++ b/drivers/gpu/drm/sun4i/sun4i_backend.h 2020-01-21 19:30:43.086543111 +0800

@@ -92,6 +92,7 @@

#define SUN4I_BACKEND_LAY_FBFMT_RGB888 (11 << 8)

#define SUN4I_BACKEND_LAY_FBFMT_ARGB4444 (12 << 8)

#define SUN4I_BACKEND_LAY_FBFMT_RGBA4444 (13 << 8)

+#define SUN4I_BACKEND_LAY_RGB_SWAP (1 << 2)

#define SUN4I_BACKEND_DLCDPCTL_REG 0x8b0

#define SUN4I_BACKEND_DLCDPFRMBUF_ADDRCTL_REG 0x8b4

--- a/drivers/gpu/drm/sun4i/sun4i_backend.c 2019-08-29 14:30:28.000000000 +0800

+++ b/drivers/gpu/drm/sun4i/sun4i_backend.c 2020-01-21 19:26:46.542638322 +0800

@@ -293,9 +293,16 @@

return ret;

}

- regmap_update_bits(backend->engine.regs,

- SUN4I_BACKEND_ATTCTL_REG1(layer),

- SUN4I_BACKEND_ATTCTL_REG1_LAY_FBFMT, val);

+ if (backend->engine.rgb_swap) {

+ regmap_update_bits(backend->engine.regs,

+ SUN4I_BACKEND_ATTCTL_REG1(layer),

+ SUN4I_BACKEND_ATTCTL_REG1_LAY_FBFMT | SUN4I_BACKEND_LAY_RGB_SWAP,

+ val | SUN4I_BACKEND_LAY_RGB_SWAP);

+ } else {

+ regmap_update_bits(backend->engine.regs,

+ SUN4I_BACKEND_ATTCTL_REG1(layer),

+ SUN4I_BACKEND_ATTCTL_REG1_LAY_FBFMT, val);

+ }

return 0;

}

@@ -316,10 +323,17 @@

SUN4I_BACKEND_ATTCTL_REG0(layer),

SUN4I_BACKEND_ATTCTL_REG0_LAY_VDOEN,

SUN4I_BACKEND_ATTCTL_REG0_LAY_VDOEN);

-

- regmap_update_bits(backend->engine.regs,

- SUN4I_BACKEND_ATTCTL_REG1(layer),

- SUN4I_BACKEND_ATTCTL_REG1_LAY_FBFMT, val);

+

+ if (backend->engine.rgb_swap) {

+ regmap_update_bits(backend->engine.regs,

+ SUN4I_BACKEND_ATTCTL_REG1(layer),

+ SUN4I_BACKEND_ATTCTL_REG1_LAY_FBFMT | SUN4I_BACKEND_LAY_RGB_SWAP,

+ val | SUN4I_BACKEND_LAY_RGB_SWAP);

+ } else {

+ regmap_update_bits(backend->engine.regs,

+ SUN4I_BACKEND_ATTCTL_REG1(layer),

+ SUN4I_BACKEND_ATTCTL_REG1_LAY_FBFMT, val);

+ }

return 0;

}

@@ -818,6 +832,12 @@

backend->engine.id = sun4i_backend_of_get_id(dev->of_node);

if (backend->engine.id < 0)

return backend->engine.id;

+

+ backend->engine.rgb_swap = 0;

+ if (of_find_property(dev->of_node, "rgb-channel-swap", NULL)) {

+ of_property_read_u32(dev->of_node, "rgb-channel-swap", &backend->engine.rgb_swap);

+ dev_warn(dev, "backend rgb channel swap(%d)\n", backend->engine.rgb_swap);

+ }

backend->frontend = sun4i_backend_find_frontend(drv, dev->of_node);

if (IS_ERR(backend->frontend))

@@ -972,6 +992,9 @@

return 0;

}

+static const struct sun4i_backend_quirks suniv_backend_quirks = {

+};

+

static const struct sun4i_backend_quirks sun4i_backend_quirks = {

.needs_output_muxing = true,

};

@@ -996,6 +1019,10 @@

static const struct of_device_id sun4i_backend_of_table[] = {

{

+ .compatible = "allwinner,suniv-f1c100s-display-backend",

+ .data = &suniv_backend_quirks,

+ },

+ {

.compatible = "allwinner,sun4i-a10-display-backend",

.data = &sun4i_backend_quirks,

},

--- a/drivers/phy/allwinner/phy-sun4i-usb.c 2019-08-29 14:30:28.000000000 +0800

+++ b/drivers/phy/allwinner/phy-sun4i-usb.c 2020-01-21 19:26:46.542638322 +0800

@@ -98,6 +98,7 @@

#define POLL_TIME msecs_to_jiffies(250)

enum sun4i_usb_phy_type {

+ suniv_phy,

sun4i_a10_phy,

sun6i_a31_phy,

sun8i_a33_phy,

@@ -859,6 +860,14 @@

return 0;

}

+static const struct sun4i_usb_phy_cfg suniv_cfg = {

+ .num_phys = 1,

+ .type = suniv_phy,

+ .disc_thresh = 3,

+ .phyctl_offset = REG_PHYCTL_A10,

+ .dedicated_clocks = true,

+};

+

static const struct sun4i_usb_phy_cfg sun4i_a10_cfg = {

.num_phys = 3,

.type = sun4i_a10_phy,

@@ -973,6 +982,7 @@

};

static const struct of_device_id sun4i_usb_phy_of_match[] = {

+ { .compatible = "allwinner,suniv-usb-phy", .data = &suniv_cfg },

{ .compatible = "allwinner,sun4i-a10-usb-phy", .data = &sun4i_a10_cfg },

{ .compatible = "allwinner,sun5i-a13-usb-phy", .data = &sun5i_a13_cfg },

{ .compatible = "allwinner,sun6i-a31-usb-phy", .data = &sun6i_a31_cfg },

--- a/drivers/usb/musb/sunxi.c 2019-08-29 14:30:28.000000000 +0800

+++ b/drivers/usb/musb/sunxi.c 2020-01-21 19:26:46.542638322 +0800

@@ -714,14 +714,16 @@

INIT_WORK(&glue->work, sunxi_musb_work);

glue->host_nb.notifier_call = sunxi_musb_host_notifier;

- if (of_device_is_compatible(np, "allwinner,sun4i-a10-musb"))

+ if (of_device_is_compatible(np, "allwinner,sun4i-a10-musb") ||

+ of_device_is_compatible(np, "allwinner,suniv-musb"))

set_bit(SUNXI_MUSB_FL_HAS_SRAM, &glue->flags);

if (of_device_is_compatible(np, "allwinner,sun6i-a31-musb"))

set_bit(SUNXI_MUSB_FL_HAS_RESET, &glue->flags);

if (of_device_is_compatible(np, "allwinner,sun8i-a33-musb") ||

- of_device_is_compatible(np, "allwinner,sun8i-h3-musb")) {

+ of_device_is_compatible(np, "allwinner,sun8i-h3-musb") ||

+ of_device_is_compatible(np, "allwinner,suniv-musb")) {

set_bit(SUNXI_MUSB_FL_HAS_RESET, &glue->flags);

set_bit(SUNXI_MUSB_FL_NO_CONFIGDATA, &glue->flags);

}

@@ -812,6 +814,7 @@

}

static const struct of_device_id sunxi_musb_match[] = {

+ { .compatible = "allwinner,suniv-musb", },

{ .compatible = "allwinner,sun4i-a10-musb", },

{ .compatible = "allwinner,sun6i-a31-musb", },

{ .compatible = "allwinner,sun8i-a33-musb", },

--- a/drivers/video/fbdev/core/fbcon.c 2019-08-29 14:30:28.000000000 +0800

+++ b/drivers/video/fbdev/core/fbcon.c 2020-01-21 19:26:46.542638322 +0800

@@ -368,6 +368,7 @@

static void fb_flashcursor(struct work_struct *work)

{

+#if 0

struct fb_info *info = container_of(work, struct fb_info, queue);

struct fbcon_ops *ops = info->fbcon_par;

struct vc_data *vc = NULL;

@@ -398,6 +399,7 @@

ops->cursor(vc, info, mode, softback_lines, get_color(vc, info, c, 1),

get_color(vc, info, c, 0));

console_unlock();

+#endif

}

static void cursor_timer_handler(struct timer_list *t)离线

#61 2020-04-10 10:24:34 分享评论

- kerr

- 会员

- 注册时间: 2020-04-08

- 已发帖子: 23

- 积分: 23

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

大神, 请教下, 您的原理图中JP3是什么?

CSI接口 需要两个ME6206? 我看两个VCC2.8都用到

离线

#62 2020-04-13 09:56:30 分享评论

- XZHDJH

- 会员

- 注册时间: 2020-01-18

- 已发帖子: 37

- 积分: 37

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

MARK一下,有计划跟随大佬脚步做一下...

离线

#63 2020-04-16 09:35:50 分享评论

- Quotation

- 会员

- 注册时间: 2018-10-04

- 已发帖子: 305

- 积分: 264.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

kerr wrote:

大神, 请教下, 您的原理图中JP3是什么?

CSI接口 需要两个ME6206? 我看两个VCC2.8都用到

JP3是切换摄像头DVDD的供电,不同摄像头要求的不同。有的用2.8V,就去掉U7,接上JP3。有的不是2.8V的摄像头,则自己换成合适的LDO到U7,打开JP3。

离线

#64 2020-04-28 09:12:47 分享评论

- 1035036848

- 会员

- 注册时间: 2020-04-28

- 已发帖子: 12

- 积分: 12

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

菠萝派?

离线

#65 2020-04-29 11:19:39 分享评论

- zhengjieming

- 会员

- 注册时间: 2020-01-04

- 已发帖子: 12

- 积分: 12

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

下载了不少有用的东西,现在不知道怎么回复,求助

离线

#66 2020-04-29 22:47:46 分享评论

- pkoko

- 会员

- 注册时间: 2020-04-29

- 已发帖子: 21

- 积分: 0.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

楼主,这个原理图有公版的吗?

离线

#67 2020-05-03 03:21:25 分享评论

- art-sys

- 会员

- 注册时间: 2020-05-03

- 已发帖子: 0

- 积分: 0

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

我該如何運行?

离线

#68 2020-05-03 06:09:28 分享评论

- 在路上

- 会员

- 注册时间: 2019-11-14

- 已发帖子: 2

- 积分: 2

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

焊了两次电源都没搞好,难道买了假3036

离线

#69 2020-05-03 19:36:09 分享评论

- jiangshan00000

- 会员

- 注册时间: 2019-12-05

- 已发帖子: 10

- 积分: 0

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

有音频口么?没看到音频口呢?

是扩展板外接么?

离线

#70 2020-05-06 13:19:03 分享评论

- njitnjit

- 会员

- 所在地: 眼中有码

- 注册时间: 2020-05-06

- 已发帖子: 19

- 积分: 5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

什么时候开卖?坐等入手进坑!;)

离线

#71 2020-05-07 21:14:39 分享评论

- grantho

- 会员

- 注册时间: 2020-03-21

- 已发帖子: 71

- 积分: 2.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

你好,请问f1c200s可以兼容吗?我焊的板子电源芯片出来3路电正常,但ddr的svref电压为0v,usb没有反应。

离线

#73 2020-05-07 22:14:38 分享评论

- grantho

- 会员

- 注册时间: 2020-03-21

- 已发帖子: 71

- 积分: 2.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

哇酷小二 wrote:

兼容,只是DRAM容量不同.

我的板子现在VCC-DRAM是2.52v,VCC-CORE是1.09v(电源改了个电阻,按说明书上的),AVCC是3.34v。晶振有起振,24M。插上USB,SPI0的CS有被拉高,手动接地也没反应。USB数据线没有数据,没有反应,使用ubuntu,windows两个系统试了都没反应。焊接过几块板子都一样。还有什么需要注意的吗?

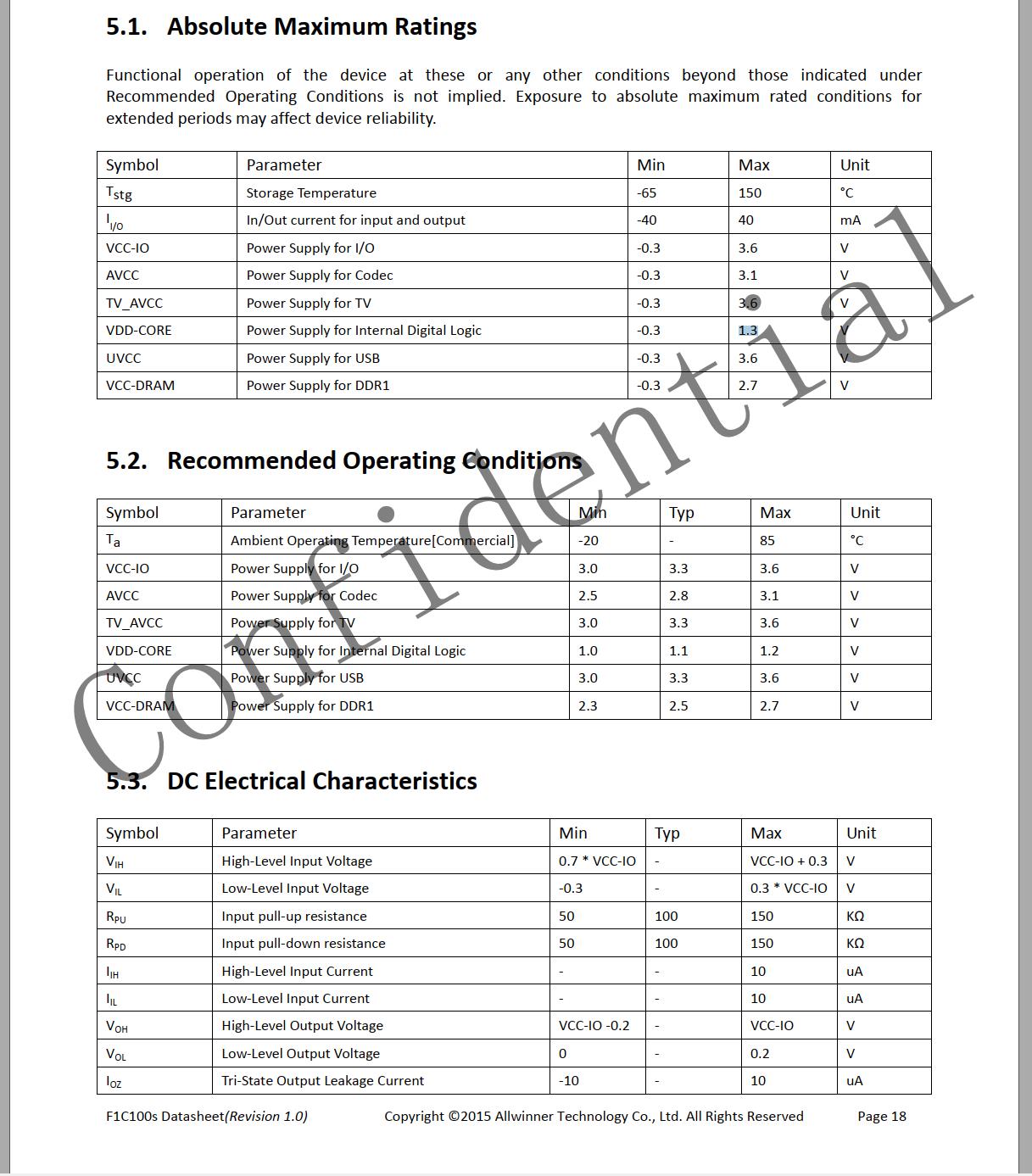

最近编辑记录 grantho (2020-05-07 22:15:10)

离线

#74 2020-05-07 23:55:50 分享评论

- long169

- 会员

- 注册时间: 2020-05-07

- 已发帖子: 2

- 积分: 2

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

正在找相关的资源

离线

#75 2020-05-08 13:46:26 分享评论

- cccsk

- 会员

- 注册时间: 2020-05-08

- 已发帖子: 10

- 积分: 4.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

楼主能出个原理图吗

离线

#76 2020-05-21 18:13:19 分享评论

- heiheizi

- 会员

- 注册时间: 2019-10-25

- 已发帖子: 40

- 积分: 40

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

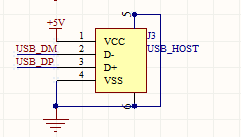

微凉VeiLiang 大神,你画的板子我焊好了,测试三路供电都正常,测试f1c100s的供电条件都达到了 ,可是为何插入电脑,usb不识别,我对比了下荔枝派nano的usb接法,和你的有点不一样,usb id你是悬空未接,nano却是接了一个47k的上拉电阻,应该怎么让电脑识别呢?

,可是为何插入电脑,usb不识别,我对比了下荔枝派nano的usb接法,和你的有点不一样,usb id你是悬空未接,nano却是接了一个47k的上拉电阻,应该怎么让电脑识别呢?

离线

#77 2020-05-21 18:16:59 分享评论

- heiheizi

- 会员

- 注册时间: 2019-10-25

- 已发帖子: 40

- 积分: 40

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

这是我查到的关于usb的资料

USB上的DM,DP拉电阻分析

USB数据端子:

1、DM+:Data Minus,数据负信号;

2、DP -:USB Data Positive,数据正信号;

USB电源端子:

1、VCC(Voltage to Current Converter)正极

2、GND负极(Ground即地线)

usb有主从设备之分,主设备有:pc, 现在市面上的那些插u-disk即可播放mp3的“mp3”之类的,

usb 信号是差分信号,信号线为D+, D-,。 在usb host 端, D+,D- 各接一个15kohm 的下拉电阻, 而在usb device端,这时就有高速低速设备的区别了。usb1.0, 1.1,2.0协议中都有定义高低速设备以满足不同情况的需求,这些在硬件上的区别就是:高速设备:d+ 接一个1.5kohm的上拉电阻,d-不接;低速设备则相反。

这样当usb device 插入到host中时,如果是高速设备,则d+被拉高,d-不变;低速设备则与之相反。这个上拉过程需要大概2.5us的时间,host这这个时间内便检测到了该信号,即可判断有device plug in,和该device的类型,然后开始通讯,枚举。。。等。

USB OTG(on the go)就是既可以做host又可以做client

我们一般是作为client接受pc传输数据,作为host时可以接打印机直接把手机中的照片打印出来

判别是host还是client是靠USB_ID这根pin

当作为client时,USB_ID基本是悬空的(内部有上拉)

如果侦测到USB_ID被拉低,就被认为是作为host,向外输出

所以需要外部client设备把USB_ID拉低

离线

#78 2020-05-22 13:21:15 分享评论

- sea18c

- 会员

- 注册时间: 2019-08-05

- 已发帖子: 230

- 积分: 222.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

heiheizi wrote:

微凉VeiLiang 大神,你画的板子我焊好了,测试三路供电都正常,测试f1c100s的供电条件都达到了/files/members/2228/f1c100s工作条件.jpg,可是为何插入电脑,usb不识别,我对比了下荔枝派nano的usb接法,和你的有点不一样,usb id你是悬空未接,nano却是接了一个47k的上拉电阻,应该怎么让电脑识别呢?

那个usb_id可以不接的,我也参照这个画了一板,能正常使用。

离线

#79 2020-05-22 13:36:33 分享评论

- heiheizi

- 会员

- 注册时间: 2019-10-25

- 已发帖子: 40

- 积分: 40

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

sea18c wrote:

那个usb_id可以不接的,我也参照这个画了一板,能正常使用。

/files/members/1876/123.png

像我这样的问题 可能会出在什么地方?

离线

#80 2020-05-22 14:39:17 分享评论

- chengqy

- 会员

- 注册时间: 2019-12-12

- 已发帖子: 11

- 积分: 5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

感谢楼主分享,最近准备学习画一个f1c100s的板子,疯狂搜索参考中。话说晕哥这个有效回复可太让人为难了,是不是考虑开个灌水区,每次回复都小心翼翼的....

离线

#81 2020-05-23 08:45:58 分享评论

- sea18c

- 会员

- 注册时间: 2019-08-05

- 已发帖子: 230

- 积分: 222.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

heiheizi wrote:

像我这样的问题 可能会出在什么地方?

确认芯片焊接没有问题,我是用风枪+锡膏,没有用锡膏可能会没有焊好哦

离线

#82 2020-05-23 08:48:49 分享评论

- heiheizi

- 会员

- 注册时间: 2019-10-25

- 已发帖子: 40

- 积分: 40

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

sea18c wrote:

确认芯片焊接没有问题,我是用风枪+锡膏,没有用锡膏可能会没有焊好哦

我也是用风枪+锡膏焊接的,我还万用表测试了,接触肯定是好的,我焊接了三块板子都是这样,应该不是焊接问题

离线

楼主 #83 2020-05-23 09:21:22 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

heiheizi wrote:

我也是用风枪+锡膏焊接的,我还万用表测试了,接触肯定是好的,我焊接了三块板子都是这样,应该不是焊接问题

确认下flash短接5脚和6脚上电看看。还有就是Rx不要接着线,因为怕io反供电导致上电不成功

离线

楼主 #84 2020-05-23 09:23:18 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

heiheizi wrote:

这是我查到的关于usb的资料

USB上的DM,DP拉电阻分析

USB数据端子:

1、DM+:Data Minus,数据负信号;

2、DP -:USB Data Positive,数据正信号;

USB电源端子:

1、VCC(Voltage to Current Converter)正极

2、GND负极(Ground即地线)usb有主从设备之分,主设备有:pc, 现在市面上的那些插u-disk即可播放mp3的“mp3”之类的,

usb 信号是差分信号,信号线为D+, D-,。 在usb host 端, D+,D- 各接一个15kohm 的下拉电阻, 而在usb device端,这时就有高速低速设备的区别了。usb1.0, 1.1,2.0协议中都有定义高低速设备以满足不同情况的需求,这些在硬件上的区别就是:高速设备:d+ 接一个1.5kohm的上拉电阻,d-不接;低速设备则相反。

这样当usb device 插入到host中时,如果是高速设备,则d+被拉高,d-不变;低速设备则与之相反。这个上拉过程需要大概2.5us的时间,host这这个时间内便检测到了该信号,即可判断有device plug in,和该device的类型,然后开始通讯,枚举。。。等。

USB OTG(on the go)就是既可以做host又可以做client

我们一般是作为client接受pc传输数据,作为host时可以接打印机直接把手机中的照片打印出来

判别是host还是client是靠USB_ID这根pin

当作为client时,USB_ID基本是悬空的(内部有上拉)

如果侦测到USB_ID被拉低,就被认为是作为host,向外输出

所以需要外部client设备把USB_ID拉低

和ID脚没有关系,usb 外设的id是内置支持软件上下拉的。没有引出来到引脚的

离线

#85 2020-05-23 12:54:43 分享评论

- heiheizi

- 会员

- 注册时间: 2019-10-25

- 已发帖子: 40

- 积分: 40

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

微凉VeiLiang wrote:

确认下flash短接5脚和6脚上电看看。还有就是Rx不要接着线,因为怕io反供电导致上电不成功

短接了5脚和6脚上电还是一样的没反应,Rx没接线。

离线

楼主 #86 2020-05-23 14:15:45 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

heiheizi wrote:

短接了5脚和6脚上电还是一样的没反应,Rx没接线。

那会不会是晶振问题。看看晶振频率,有没有起振

离线

#87 2020-05-23 14:18:33 分享评论

- heiheizi

- 会员

- 注册时间: 2019-10-25

- 已发帖子: 40

- 积分: 40

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

微凉VeiLiang wrote:

那会不会是晶振问题。看看晶振频率,有没有起振

大神,可否方便加个qq,我的76614842

离线

#88 2020-05-23 20:32:27 分享评论

- heiheizi

- 会员

- 注册时间: 2019-10-25

- 已发帖子: 40

- 积分: 40

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

用示波器测量了波形,有起振,频率是24mhz左右

离线

#89 2020-05-23 22:53:19 分享评论

- ifree64

- 会员

- 注册时间: 2019-06-27

- 已发帖子: 74

- 积分: 143.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

grantho wrote:

我的板子现在VCC-DRAM是2.52v,VCC-CORE是1.09v(电源改了个电阻,按说明书上的),AVCC是3.34v。晶振有起振,24M。插上USB,SPI0的CS有被拉高,手动接地也没反应。USB数据线没有数据,没有反应,使用ubuntu,windows两个系统试了都没反应。焊接过几块板子都一样。还有什么需要注意的吗?

请问你现在问题解决了没有?USB ID是怎么处理的呢?

离线

#90 2020-05-24 02:47:56 分享评论

- grantho

- 会员

- 注册时间: 2020-03-21

- 已发帖子: 71

- 积分: 2.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

ifree64 wrote:

请问你现在问题解决了没有?USB ID是怎么处理的呢?

没解决啊,我买了块tiny200先测试一下软件方案。USB ID应该是可以不接的,PC是HOST,USB口就四根线,ID接了也没用。USB ID是用来给主机做识别,区分工作模式的,现在板子肯定是从机。过几天再调调

离线

#91 2020-05-27 10:25:21 分享评论

- lostangel

- 会员

- 注册时间: 2020-05-27

- 已发帖子: 8

- 积分: 8

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

楼主的硬件运行稳定吗?我想来一块试试

离线

#92 2020-05-29 15:14:01 分享评论

- kouten

- 会员

- 注册时间: 2020-05-28

- 已发帖子: 10

- 积分: 9

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

MARK,感谢楼主!

离线

#93 2020-05-30 20:04:56 分享评论

- 悠悠三千载

- 会员

- 注册时间: 2019-11-20

- 已发帖子: 3

- 积分: 3

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

MARK,真心感谢楼主。赞赞赞

离线

#94 2020-06-01 16:02:54 分享评论

- heiheizi

- 会员

- 注册时间: 2019-10-25

- 已发帖子: 40

- 积分: 40

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

usb接上电脑没反应的问题,我重新开了一贴,微凉VeiLiang 大神能否帮看下

离线

#95 2020-06-01 16:20:03 分享评论

- Delei

- 会员

- 注册时间: 2020-03-14

- 已发帖子: 3

- 积分: 3

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

前些天调试了下OWA接口,就是输出S/PDIF信号的那个接口,现在可以和音频同步输出了。^-^ =)

离线

#96 2020-06-02 09:12:28 分享评论

- 房地产

- 会员

- 注册时间: 2020-03-02

- 已发帖子: 27

- 积分: 27

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

最近也在研究f1c100s,参考一下设计文件

离线

#97 2020-06-03 15:16:50 分享评论

- 8629002

- 会员

- 注册时间: 2020-06-02

- 已发帖子: 5

- 积分: 5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

这个菠萝的logo很好看啊,就是白色油墨什么鬼啊,看不见了哈哈哈

离线

#98 2020-06-08 17:56:17 分享评论

- vvi

- 会员

- 注册时间: 2019-12-09

- 已发帖子: 11

- 积分: 6

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

烧录时要短接flash的1、4脚,在这里加一个按键不是更方便些?

离线

楼主 #100 2020-06-08 19:44:18 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

vvi wrote:

烧录时要短接flash的1、4脚,在这里加一个按键不是更方便些?

有留了一个按键。按着按键上电就是进入 fel(按键是短接flash的clk脚到地)

离线

#101 2020-06-09 08:56:41 分享评论

- Timaker

- 会员

- 注册时间: 2020-05-18

- 已发帖子: 65

- 积分: 43.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

有摄像头驱动吗

离线

#102 2020-06-17 12:21:58 分享评论

- tfx

- 会员

- 注册时间: 2020-06-17

- 已发帖子: 0

- 积分: 0

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

感谢楼主的分享

离线

#103 2020-06-21 00:22:05 分享评论

- bjlxjw

- 会员

- 注册时间: 2020-06-21

- 已发帖子: 1

- 积分: 1

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

感谢大神,跟着一起学习了,

离线

#104 2020-07-01 00:20:10 分享评论

- 嘿小毅

- 会员

- 注册时间: 2020-06-29

- 已发帖子: 0

- 积分: 0

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

感谢分享学习,正好用上。

离线

#105 2020-07-15 14:30:01 分享评论

- sync

- 会员

- 注册时间: 2019-12-12

- 已发帖子: 22

- 积分: 17

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

多谢楼主无私,下载学习了

离线

#106 2020-07-15 15:22:10 分享评论

- Sunshine

- 会员

- 注册时间: 2020-07-15

- 已发帖子: 8

- 积分: 8

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

多谢楼主无私,下载学习

离线

#107 2020-07-15 15:30:43 分享评论

- jared1716

- 会员

- 注册时间: 2020-07-15

- 已发帖子: 2

- 积分: 2

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

感谢大神,跟着一起学习了,多谢楼主无私!

离线

#108 2020-07-16 12:22:11 分享评论

- yangjjing29

- 会员

- 注册时间: 2020-07-16

- 已发帖子: 2

- 积分: 2

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

看着还不错,重点是能用起来把,看到做出实物了。

离线

#109 2020-07-16 14:59:40 分享评论

- AYUMI7

- 会员

- 注册时间: 2018-11-24

- 已发帖子: 5

- 积分: 5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

这板子看着真不错 我有个 nano的板子 没有IO引出 回头打个样 挪过来 玩玩

离线

#110 2020-07-21 09:55:28 分享评论

- thinhx2

- 会员

- 注册时间: 2020-07-21

- 已发帖子: 2

- 积分: 2

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

IkY

离线

#111 2020-07-23 14:19:40 分享评论

- 知名企业家黄鹤

- 会员

- 注册时间: 2019-09-30

- 已发帖子: 4

- 积分: 4

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

楼主的EA3036哪儿买的,我淘宝买的3036没输出。

离线

#112 2020-07-25 10:07:51 分享评论

- JEHWHY

- 会员

- 注册时间: 2020-07-25

- 已发帖子: 5

- 积分: 0

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

请问F1C100还会有其它系列的吗?

离线

#113 2020-08-06 22:05:54 分享评论

- upoupil

- 会员

- 注册时间: 2020-08-03

- 已发帖子: 2

- 积分: 2

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

是。下一个系列是“ Allwinner V3S”,在很多方面看起来一样,但更大的dram

离线

#114 2020-08-07 11:30:31 分享评论

- wangweigang0

- 会员

- 注册时间: 2020-08-07

- 已发帖子: 17

- 积分: 47

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

学习下,现在刚开始整f1c100s,想自己话图。

离线

#115 2020-08-08 13:10:05 分享评论

- Pluto

- 会员

- 注册时间: 2020-08-08

- 已发帖子: 1

- 积分: 1

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

感谢楼主的无私分享。。。

离线

#116 2020-08-10 00:46:18 分享评论

- fxman

- 会员

- 注册时间: 2020-08-09

- 已发帖子: 10

- 积分: 10

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

楼主,摄像头代码能否分享一份

离线

#117 2020-08-10 00:49:22 分享评论

- fxman

- 会员

- 注册时间: 2020-08-09

- 已发帖子: 10

- 积分: 10

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

heiheizi wrote:

用示波器测量了波形,有起振,频率是24mhz左右

这个我也遇到了,VRA2,VRA1的电容电阻换成 1uF 和200K就行

离线

#118 2020-08-11 11:31:36 分享评论

- MyWaKeng

- 会员

- 注册时间: 2020-07-14

- 已发帖子: 22

- 积分: 1.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

刚好需要,一个DEMO来参考设计一个板子,楼主及时雨呀。

离线

#119 2020-08-11 16:06:52 分享评论

- 240011814

- 会员

- 注册时间: 2020-08-11

- 已发帖子: 6

- 积分: 1

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

这板子看着真不错 我有个 nano的板子 没有IO引出 回头打个样 挪过来 玩玩

离线

#120 2020-08-11 16:42:53 分享评论

- ljw22676739

- 会员

- 注册时间: 2020-05-07

- 已发帖子: 14

- 积分: 9

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

顶一个!持续关注!

离线

#121 2020-08-11 22:51:10 分享评论

- kesion

- 会员

- 注册时间: 2020-07-03

- 已发帖子: 45

- 积分: 32

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

好东西,支持,,,

离线

#122 2020-08-20 22:36:05 分享评论

- hongyepiaoling

- 会员

- 注册时间: 2019-11-02

- 已发帖子: 2

- 积分: 2

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

这个好 支持

离线

#123 2020-08-22 22:27:40 分享评论

- mcsino

- 会员

- 注册时间: 2019-12-22

- 已发帖子: 21

- 积分: 36

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

强,正需要学习

离线

#124 2020-09-15 18:26:27 分享评论

- yf654987

- 会员

- 注册时间: 2020-09-15

- 已发帖子: 9

- 积分: 9

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

好东西!!!!!!!!!!!!!!!!!!!!!!

离线

#125 2020-09-17 19:45:05 分享评论

- jcdzxh

- 会员

- 注册时间: 2020-09-17

- 已发帖子: 2

- 积分: 2

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

顶起来学习,感谢大神分享

离线

#126 2020-10-04 01:02:44 分享评论

- sawgsxiao

- 会员

- 注册时间: 2020-07-15

- 已发帖子: 2

- 积分: 2

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

老哥,我想参考下 感谢

离线

#127 2020-10-05 22:20:54 分享评论

- xiaoyuanmcu

- 会员

- 注册时间: 2020-03-15

- 已发帖子: 9

- 积分: 9

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

顶起来,好东西,谢谢!!!

离线

#128 2020-10-06 13:26:37 分享评论

- lonerwolf

- 会员

- 注册时间: 2020-09-02

- 已发帖子: 59

- 积分: 56.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

不知道如何下载

离线

#129 2020-12-17 17:44:33 分享评论

- banzhangzzw

- 会员

- 注册时间: 2020-12-17

- 已发帖子: 8

- 积分: 7.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

谢谢分享github连接

离线

#130 2020-12-18 14:03:19 分享评论

- 路飞的小弟

- 会员

- 注册时间: 2020-04-15

- 已发帖子: 1

- 积分: 1

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

感谢老铁的开源分享 没事开始研究

离线

#131 2021-02-20 16:57:26 分享评论

- 通宵敲代码

- 会员

- 所在地: 山东潍坊

- 注册时间: 2021-02-19

- 已发帖子: 10

- 积分: 5.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

支持一下,感谢分享

离线

#132 2021-08-27 13:27:24 分享评论

- 笔走天下

- 会员

- 注册时间: 2021-08-13

- 已发帖子: 126

- 积分: 0.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

赶紧mark一下,下载PCB文件自己diy一下

离线

#133 2021-09-09 16:23:49 分享评论

- 笔走天下

- 会员

- 注册时间: 2021-08-13

- 已发帖子: 126

- 积分: 0.5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

heiheizi wrote:

用示波器测量了波形,有起振,频率是24mhz左右

你好,我的问题可能也是晶振不起振的问题,能加你qq交流下吗

离线

#134 2021-10-02 13:58:01 分享评论

- tgyfish

- 会员

- 注册时间: 2019-10-23

- 已发帖子: 5

- 积分: 28

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

电源树长在了外面,可可爱爱

离线

#135 2021-10-02 14:32:55 分享评论

- tgyfish

- 会员

- 注册时间: 2019-10-23

- 已发帖子: 5

- 积分: 28

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

Quotation wrote:

谢谢,学习了。用F1C100s画了好几块板了,每次供电部分都布得很纠结。下次学你的做法,在底部焊盘周围走线。

发现我把底部焊盘画的过大了,所以没什么空间走线。

HAHAHAHA,我也是这么走的,走线外面太难走了,穿不出去

离线

#136 2021-11-09 11:25:51 分享评论

- CHSHIQING

- 会员

- 注册时间: 2020-11-27

- 已发帖子: 47

- 积分: 2

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

好东西啊,感谢楼主,最近想搞块板子结果芯片全部涨价了

离线

#137 2021-12-08 17:19:51 分享评论

- ccain

- 会员

- 注册时间: 2021-12-08

- 已发帖子: 0

- 积分: 0

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

离线

- 不通过:其他

#138 2022-01-26 23:24:32 分享评论

- shuimogezi

- 会员

- 所在地: 北京

- 注册时间: 2018-07-14

- 已发帖子: 33

- 积分: 26

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

问下,用的这个工程打样的板子回来了,贴的32MB的QSPI FLASH,很大概率的时候经常擦除flash失败导致新固件有很多时候写不进去,请问是怎么回事?

技术狂,追求技术更高层,哈哈哈

离线

#139 2022-01-27 13:53:17 分享评论

- CHSHIQING

- 会员

- 注册时间: 2020-11-27

- 已发帖子: 47

- 积分: 2

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

偶尔烧录启动后卡在starting kernel。。。,但是多按几次重启按钮重启又能起来,有没有大佬知道是啥问题

离线

#143 2022-03-24 19:01:34 分享评论

- lorenzo

- 会员

- 注册时间: 2022-03-24

- 已发帖子: 15

- 积分: 0

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

我也刚画了一块。

引出RGBLCD接口

通过sl2.1A拓展2个USBA口

离线

#145 2022-06-25 13:47:19 分享评论

- future

- 会员

- 注册时间: 2021-11-28

- 已发帖子: 49

- 积分: 26

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

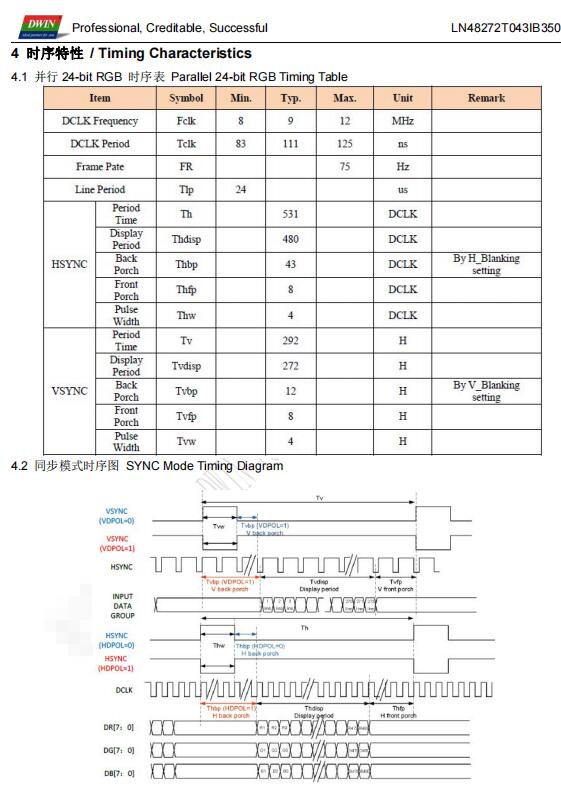

老哥,这个屏幕参数怎么设置,我调了好久换了好几种不同的参数,都灭有正常点亮,用荔枝派官方固件是可以正常显示的。

这是我的屏幕参数:

这是我现在点的样子

离线

#148 2023-02-24 23:19:55 分享评论

- Chengzong

- 会员

- 注册时间: 2022-08-14

- 已发帖子: 5

- 积分: 5

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

我的lsusb都找不到芯片,晶振示波器起振的

离线

#151 2023-03-27 10:03:39 分享评论

- wppw

- 会员

- 注册时间: 2023-03-26

- 已发帖子: 4

- 积分: 4

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

嘉立创下单直接开搞

离线

#154 2024-06-13 17:05:03 分享评论

#159 2025-11-09 20:29:05 分享评论

- STOPCALE

- 会员

- 注册时间: 2025-11-09

- 已发帖子: 4

- 积分: 4

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

f1c200s接摄像头跑cv够吗?

离线

#162 2025-12-06 22:36:46 分享评论

- fcprchris

- 会员

- 注册时间: 2025-12-06

- 已发帖子: 3

- 积分: 13

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

真是个很棒的设计!看起来非常实用。我刚加入这个网站论坛,它已经为我提供了很多有用的信息 ![]() 我在澳大利亚,用翻译功能阅读信息。希望大家欢迎我

我在澳大利亚,用翻译功能阅读信息。希望大家欢迎我 ![]()

离线

#163 2025-12-24 18:22:53 分享评论

- qwb233

- 会员

- 注册时间: 2025-12-24

- 已发帖子: 4

- 积分: 4

Re: 开源自己画的一个F1C100S板子和原理图,摄像头和屏幕同时引出,所有io引出

感谢大神,你f1c100s系统跑的是哪个,linux,裸机,还是rtthread

离线

东莞哇酷科技有限公司开发