楼主 # 2021-11-01 17:41:21 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

XFEL已支持spi nand flash烧写

xfel工具很早就支持了spi nor flash的读写,但spi nand flash的支持一直没提上日程,考虑到F133,D1s的玩家越来越多,这个spi nand flash的支持就迫在眉睫了。经过几天的开发设计,spi nand flash的支持基本完成了。下面是支持的spi nand芯片列表,已经算是尽我所能,找到最全的芯片列表了。当然现在仅测试过MX35LF2GE4AD这颗,其他芯片的验证在遇到具体问题后,再进行调试了。

/* Gigadevice */

{ "GD5F1GQ4UAWxx", 0xc810, 2048, 64, 64, 1024, 1, 1 },

{ "GD5F1GQ4UExIG", 0xc8d1, 2048, 128, 64, 1024, 1, 1 },

{ "GD5F1GQ4UExxH", 0xc8d9, 2048, 64, 64, 1024, 1, 1 },

{ "GD5F1GQ4xAYIG", 0xc8f1, 2048, 64, 64, 1024, 1, 1 },

{ "GD5F2GQ4UExIG", 0xc8d2, 2048, 128, 64, 2048, 1, 1 },

{ "GD5F2GQ5UExxH", 0xc832, 2048, 64, 64, 2048, 1, 1 },

{ "GD5F2GQ4xAYIG", 0xc8f2, 2048, 64, 64, 2048, 1, 1 },

{ "GD5F4GQ4UBxIG", 0xc8d4, 4096, 256, 64, 2048, 1, 1 },

{ "GD5F4GQ4xAYIG", 0xc8f4, 2048, 64, 64, 4096, 1, 1 },

{ "GD5F2GQ5UExxG", 0xc852, 2048, 128, 64, 2048, 1, 1 },

{ "GD5F4GQ4UCxIG", 0xc8b4, 4096, 256, 64, 2048, 1, 1 },

/* Macronix */

{ "MX35LF1GE4AB", 0xc212, 2048, 64, 64, 1024, 1, 1 },

{ "MX35LF1G24AD", 0xc214, 2048, 128, 64, 1024, 1, 1 },

{ "MX31LF1GE4BC", 0xc21e, 2048, 64, 64, 1024, 1, 1 },

{ "MX35LF2GE4AB", 0xc222, 2048, 64, 64, 2048, 1, 1 },

{ "MX35LF2G24AD", 0xc224, 2048, 128, 64, 2048, 1, 1 },

{ "MX35LF2GE4AD", 0xc226, 2048, 128, 64, 2048, 1, 1 },

{ "MX35LF2G14AC", 0xc220, 2048, 64, 64, 2048, 1, 1 },

{ "MX35LF4G24AD", 0xc235, 4096, 256, 64, 2048, 1, 1 },

{ "MX35LF4GE4AD", 0xc237, 4096, 256, 64, 2048, 1, 1 },

/* Micron */

{ "MT29F1G01AAADD", 0x2c12, 2048, 64, 64, 1024, 1, 1 },

{ "MT29F1G01ABAFD", 0x2c14, 2048, 128, 64, 1024, 1, 1 },

{ "MT29F2G01AAAED", 0x2c9f, 2048, 64, 64, 2048, 2, 1 },

{ "MT29F2G01ABAGD", 0x2c24, 2048, 128, 64, 2048, 2, 1 },

{ "MT29F4G01AAADD", 0x2c32, 2048, 64, 64, 4096, 2, 1 },

{ "MT29F4G01ABAFD", 0x2c34, 4096, 256, 64, 2048, 1, 1 },

{ "MT29F4G01ADAGD", 0x2c36, 2048, 128, 64, 2048, 2, 2 },

{ "MT29F8G01ADAFD", 0x2c46, 4096, 256, 64, 2048, 1, 2 },

/* Toshiba */

{ "TC58CVG0S3HRAIG", 0x98c2, 2048, 128, 64, 1024, 1, 1 },

{ "TC58CVG1S3HRAIG", 0x98cb, 2048, 128, 64, 2048, 1, 1 },

{ "TC58CVG2S0HRAIG", 0x98cd, 4096, 256, 64, 2048, 1, 1 },

{ "TC58CVG0S3HRAIJ", 0x98e2, 2048, 128, 64, 1024, 1, 1 },

{ "TC58CVG1S3HRAIJ", 0x98eb, 2048, 128, 64, 2048, 1, 1 },

{ "TC58CVG2S0HRAIJ", 0x98ed, 4096, 256, 64, 2048, 1, 1 },

{ "TH58CVG3S0HRAIJ", 0x98e4, 4096, 256, 64, 4096, 1, 1 },

/* Esmt */

{ "F50L512M41A", 0xc820, 2048, 64, 64, 512, 1, 1 },

{ "F50L1G41A", 0xc821, 2048, 64, 64, 1024, 1, 1 },

{ "F50L1G41LB", 0xc801, 2048, 64, 64, 1024, 1, 1 },

{ "F50L2G41LB", 0xc80a, 2048, 64, 64, 1024, 1, 2 },

/* Fison */

{ "CS11G0T0A0AA", 0x6b00, 2048, 128, 64, 1024, 1, 1 },

{ "CS11G0G0A0AA", 0x6b10, 2048, 128, 64, 1024, 1, 1 },

{ "CS11G0S0A0AA", 0x6b20, 2048, 64, 64, 1024, 1, 1 },

{ "CS11G1T0A0AA", 0x6b01, 2048, 128, 64, 2048, 1, 1 },

{ "CS11G1S0A0AA", 0x6b21, 2048, 64, 64, 2048, 1, 1 },

{ "CS11G2T0A0AA", 0x6b02, 2048, 128, 64, 4096, 1, 1 },

{ "CS11G2S0A0AA", 0x6b22, 2048, 64, 64, 4096, 1, 1 },

/* Etron */

{ "EM73B044VCA", 0xd501, 2048, 64, 64, 512, 1, 1 },

{ "EM73C044SNB", 0xd511, 2048, 120, 64, 1024, 1, 1 },

{ "EM73C044SNF", 0xd509, 2048, 128, 64, 1024, 1, 1 },

{ "EM73C044VCA", 0xd518, 2048, 64, 64, 1024, 1, 1 },

{ "EM73C044SNA", 0xd519, 2048, 64, 128, 512, 1, 1 },

{ "EM73C044VCD", 0xd51c, 2048, 64, 64, 1024, 1, 1 },

{ "EM73C044SND", 0xd51d, 2048, 64, 64, 1024, 1, 1 },

{ "EM73D044SND", 0xd51e, 2048, 64, 64, 2048, 1, 1 },

{ "EM73C044VCC", 0xd522, 2048, 64, 64, 1024, 1, 1 },

{ "EM73C044VCF", 0xd525, 2048, 64, 64, 1024, 1, 1 },

{ "EM73C044SNC", 0xd531, 2048, 128, 64, 1024, 1, 1 },

{ "EM73D044SNC", 0xd50a, 2048, 120, 64, 2048, 1, 1 },

{ "EM73D044SNA", 0xd512, 2048, 128, 64, 2048, 1, 1 },

{ "EM73D044SNF", 0xd510, 2048, 128, 64, 2048, 1, 1 },

{ "EM73D044VCA", 0xd513, 2048, 128, 64, 2048, 1, 1 },

{ "EM73D044VCB", 0xd514, 2048, 64, 64, 2048, 1, 1 },

{ "EM73D044VCD", 0xd517, 2048, 128, 64, 2048, 1, 1 },

{ "EM73D044VCH", 0xd51b, 2048, 64, 64, 2048, 1, 1 },

{ "EM73D044SND", 0xd51d, 2048, 64, 64, 2048, 1, 1 },

{ "EM73D044VCG", 0xd51f, 2048, 64, 64, 2048, 1, 1 },

{ "EM73D044VCE", 0xd520, 2048, 64, 64, 2048, 1, 1 },

{ "EM73D044VCL", 0xd52e, 2048, 128, 64, 2048, 1, 1 },

{ "EM73D044SNB", 0xd532, 2048, 128, 64, 2048, 1, 1 },

{ "EM73E044SNA", 0xd503, 4096, 256, 64, 2048, 1, 1 },

{ "EM73E044SND", 0xd50b, 4096, 240, 64, 2048, 1, 1 },

{ "EM73E044SNB", 0xd523, 4096, 256, 64, 2048, 1, 1 },

{ "EM73E044VCA", 0xd52c, 4096, 256, 64, 2048, 1, 1 },

{ "EM73E044VCB", 0xd52f, 2048, 128, 64, 4096, 1, 1 },

{ "EM73F044SNA", 0xd524, 4096, 256, 64, 4096, 1, 1 },

{ "EM73F044VCA", 0xd52d, 4096, 256, 64, 4096, 1, 1 },

{ "EM73E044SNE", 0xd50e, 4096, 256, 64, 4096, 1, 1 },

{ "EM73C044SNG", 0xd50c, 2048, 120, 64, 1024, 1, 1 },

{ "EM73D044VCN", 0xd50f, 2048, 64, 64, 2048, 1, 1 },

/* Elnec */

{ "FM35Q1GA", 0xe571, 2048, 64, 64, 1024, 1, 1 },

/* Paragon */

{ "PN26G01A", 0xa1e1, 2048, 128, 64, 1024, 1, 1 },

{ "PN26G02A", 0xa1e2, 2048, 128, 64, 2048, 1, 1 },

/* Ato */

{ "ATO25D1GA", 0x9b12, 2048, 64, 64, 1024, 1, 1 },

/* Heyang */

{ "HYF1GQ4U", 0xc951, 2048, 128, 64, 1024, 1, 1 },

{ "HYF2GQ4U", 0xc952, 2048, 128, 64, 2048, 1, 1 },离线

#1 2021-11-01 21:23:10 分享评论

- mango

- 会员

- 所在地: 芒果派1

- 注册时间: 2017-12-02

- 已发帖子: 781

- 积分: 727

离线

#2 2021-11-02 09:21:19 分享评论

- 微凉VeiLiang

- 会员

- 所在地: 深圳

- 注册时间: 2018-10-28

- 已发帖子: 649

- 积分: 539

- 个人网站

Re: XFEL已支持spi nand flash烧写

感谢大佬又解决了一个问题,越来越方便了

离线

#3 2021-11-02 09:50:24 分享评论

- armstrong

- 会员

- 注册时间: 2019-04-10

- 已发帖子: 295

- 积分: 189.5

Re: XFEL已支持spi nand flash烧写

感谢xman

离线

#5 2021-11-03 10:09:20 分享评论

- 小王子&木头人

- 会员

- 注册时间: 2018-05-08

- 已发帖子: 72

- 积分: 4

Re: XFEL已支持spi nand flash烧写

支持一个 再做一回spi nand伸手党

离线

#6 2021-11-03 10:54:59 分享评论

- armstrong

- 会员

- 注册时间: 2019-04-10

- 已发帖子: 295

- 积分: 189.5

Re: XFEL已支持spi nand flash烧写

大佬一个人顶一个团队!

想让xfel支持SD卡读写,可行不?从哪下手?想尝试下!

从xfel源码入手,是电脑和MCU沟通的桥梁。

离线

楼主 #7 2021-11-03 11:07:16 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

写sd卡,貌似直接用读卡器插在电脑上更方便点。如果是Emmc的话,那还是有意义的,思路就是写个sdio的payload,然后通过xfel传输到ram中执行,有了sdio的读写,你就可以基于读写接口操作EMMC了,具体例子可以查看xfel的payload目录,参考里面的spi payload实现,模仿就可以了。

离线

楼主 #9 2021-11-03 13:51:13 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

对于贴在板子上的SD卡,还有一种方案,就是用xfel运行一个小系统,可以是uboot或者linux之类的,然后在里面开启ums功能,这样PC上就可以刷SD卡了,而且速度还快。

最近编辑记录 xboot (2021-11-03 13:51:26)

离线

#10 2021-11-03 22:59:08 分享评论

离线

#11 2021-11-08 16:45:43 分享评论

- memory

- 会员

- 注册时间: 2021-08-11

- 已发帖子: 708

- 积分: 683

Re: XFEL已支持spi nand flash烧写

测试了一下, 目前还不支持A33 FLASH 读写?

离线

楼主 #12 2021-11-08 18:32:41 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

A33还没有payload代码,如果有硬件的话,模仿个V3S的payload就差不多了。

离线

楼主 #13 2021-11-08 18:33:00 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

A33应该就是R16

离线

#14 2021-11-08 18:36:23 分享评论

- memory

- 会员

- 注册时间: 2021-08-11

- 已发帖子: 708

- 积分: 683

Re: XFEL已支持spi nand flash烧写

A33应该就是R16

对,A33 == R16 == X3(SIP 128M)

离线

楼主 #15 2021-11-09 09:23:36 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

因为华邦的spi nand id是3个字节,而绝大部分spi nand id是两个字节,这里扩展了ID的匹配策略,现在支持华邦的spi nand flash了,最新的支持列表如下:

/* Winbond */

{ "W25N512GV", SPINAND_ID(0xef, 0xaa, 0x20), 2048, 64, 64, 512, 1, 1 },

{ "W25N01GV", SPINAND_ID(0xef, 0xaa, 0x21), 2048, 64, 64, 1024, 1, 1 },

{ "W25M02GV", SPINAND_ID(0xef, 0xab, 0x21), 2048, 64, 64, 1024, 1, 2 },

{ "W25N02KV", SPINAND_ID(0xef, 0xaa, 0x22), 2048, 128, 64, 2048, 1, 1 },

/* Gigadevice */

{ "GD5F1GQ4UAWxx", SPINAND_ID(0xc8, 0x10), 2048, 64, 64, 1024, 1, 1 },

{ "GD5F1GQ4UExIG", SPINAND_ID(0xc8, 0xd1), 2048, 128, 64, 1024, 1, 1 },

{ "GD5F1GQ4UExxH", SPINAND_ID(0xc8, 0xd9), 2048, 64, 64, 1024, 1, 1 },

{ "GD5F1GQ4xAYIG", SPINAND_ID(0xc8, 0xf1), 2048, 64, 64, 1024, 1, 1 },

{ "GD5F2GQ4UExIG", SPINAND_ID(0xc8, 0xd2), 2048, 128, 64, 2048, 1, 1 },

{ "GD5F2GQ5UExxH", SPINAND_ID(0xc8, 0x32), 2048, 64, 64, 2048, 1, 1 },

{ "GD5F2GQ4xAYIG", SPINAND_ID(0xc8, 0xf2), 2048, 64, 64, 2048, 1, 1 },

{ "GD5F4GQ4UBxIG", SPINAND_ID(0xc8, 0xd4), 4096, 256, 64, 2048, 1, 1 },

{ "GD5F4GQ4xAYIG", SPINAND_ID(0xc8, 0xf4), 2048, 64, 64, 4096, 1, 1 },

{ "GD5F2GQ5UExxG", SPINAND_ID(0xc8, 0x52), 2048, 128, 64, 2048, 1, 1 },

{ "GD5F4GQ4UCxIG", SPINAND_ID(0xc8, 0xb4), 4096, 256, 64, 2048, 1, 1 },

/* Macronix */

{ "MX35LF1GE4AB", SPINAND_ID(0xc2, 0x12), 2048, 64, 64, 1024, 1, 1 },

{ "MX35LF1G24AD", SPINAND_ID(0xc2, 0x14), 2048, 128, 64, 1024, 1, 1 },

{ "MX31LF1GE4BC", SPINAND_ID(0xc2, 0x1e), 2048, 64, 64, 1024, 1, 1 },

{ "MX35LF2GE4AB", SPINAND_ID(0xc2, 0x22), 2048, 64, 64, 2048, 1, 1 },

{ "MX35LF2G24AD", SPINAND_ID(0xc2, 0x24), 2048, 128, 64, 2048, 1, 1 },

{ "MX35LF2GE4AD", SPINAND_ID(0xc2, 0x26), 2048, 128, 64, 2048, 1, 1 },

{ "MX35LF2G14AC", SPINAND_ID(0xc2, 0x20), 2048, 64, 64, 2048, 1, 1 },

{ "MX35LF4G24AD", SPINAND_ID(0xc2, 0x35), 4096, 256, 64, 2048, 1, 1 },

{ "MX35LF4GE4AD", SPINAND_ID(0xc2, 0x37), 4096, 256, 64, 2048, 1, 1 },

/* Micron */

{ "MT29F1G01AAADD", SPINAND_ID(0x2c, 0x12), 2048, 64, 64, 1024, 1, 1 },

{ "MT29F1G01ABAFD", SPINAND_ID(0x2c, 0x14), 2048, 128, 64, 1024, 1, 1 },

{ "MT29F2G01AAAED", SPINAND_ID(0x2c, 0x9f), 2048, 64, 64, 2048, 2, 1 },

{ "MT29F2G01ABAGD", SPINAND_ID(0x2c, 0x24), 2048, 128, 64, 2048, 2, 1 },

{ "MT29F4G01AAADD", SPINAND_ID(0x2c, 0x32), 2048, 64, 64, 4096, 2, 1 },

{ "MT29F4G01ABAFD", SPINAND_ID(0x2c, 0x34), 4096, 256, 64, 2048, 1, 1 },

{ "MT29F4G01ADAGD", SPINAND_ID(0x2c, 0x36), 2048, 128, 64, 2048, 2, 2 },

{ "MT29F8G01ADAFD", SPINAND_ID(0x2c, 0x46), 4096, 256, 64, 2048, 1, 2 },

/* Toshiba */

{ "TC58CVG0S3HRAIG", SPINAND_ID(0x98, 0xc2), 2048, 128, 64, 1024, 1, 1 },

{ "TC58CVG1S3HRAIG", SPINAND_ID(0x98, 0xcb), 2048, 128, 64, 2048, 1, 1 },

{ "TC58CVG2S0HRAIG", SPINAND_ID(0x98, 0xcd), 4096, 256, 64, 2048, 1, 1 },

{ "TC58CVG0S3HRAIJ", SPINAND_ID(0x98, 0xe2), 2048, 128, 64, 1024, 1, 1 },

{ "TC58CVG1S3HRAIJ", SPINAND_ID(0x98, 0xeb), 2048, 128, 64, 2048, 1, 1 },

{ "TC58CVG2S0HRAIJ", SPINAND_ID(0x98, 0xed), 4096, 256, 64, 2048, 1, 1 },

{ "TH58CVG3S0HRAIJ", SPINAND_ID(0x98, 0xe4), 4096, 256, 64, 4096, 1, 1 },

/* Esmt */

{ "F50L512M41A", SPINAND_ID(0xc8, 0x20), 2048, 64, 64, 512, 1, 1 },

{ "F50L1G41A", SPINAND_ID(0xc8, 0x21), 2048, 64, 64, 1024, 1, 1 },

{ "F50L1G41LB", SPINAND_ID(0xc8, 0x01), 2048, 64, 64, 1024, 1, 1 },

{ "F50L2G41LB", SPINAND_ID(0xc8, 0x0a), 2048, 64, 64, 1024, 1, 2 },

/* Fison */

{ "CS11G0T0A0AA", SPINAND_ID(0x6b, 0x00), 2048, 128, 64, 1024, 1, 1 },

{ "CS11G0G0A0AA", SPINAND_ID(0x6b, 0x10), 2048, 128, 64, 1024, 1, 1 },

{ "CS11G0S0A0AA", SPINAND_ID(0x6b, 0x20), 2048, 64, 64, 1024, 1, 1 },

{ "CS11G1T0A0AA", SPINAND_ID(0x6b, 0x01), 2048, 128, 64, 2048, 1, 1 },

{ "CS11G1S0A0AA", SPINAND_ID(0x6b, 0x21), 2048, 64, 64, 2048, 1, 1 },

{ "CS11G2T0A0AA", SPINAND_ID(0x6b, 0x02), 2048, 128, 64, 4096, 1, 1 },

{ "CS11G2S0A0AA", SPINAND_ID(0x6b, 0x22), 2048, 64, 64, 4096, 1, 1 },

/* Etron */

{ "EM73B044VCA", SPINAND_ID(0xd5, 0x01), 2048, 64, 64, 512, 1, 1 },

{ "EM73C044SNB", SPINAND_ID(0xd5, 0x11), 2048, 120, 64, 1024, 1, 1 },

{ "EM73C044SNF", SPINAND_ID(0xd5, 0x09), 2048, 128, 64, 1024, 1, 1 },

{ "EM73C044VCA", SPINAND_ID(0xd5, 0x18), 2048, 64, 64, 1024, 1, 1 },

{ "EM73C044SNA", SPINAND_ID(0xd5, 0x19), 2048, 64, 128, 512, 1, 1 },

{ "EM73C044VCD", SPINAND_ID(0xd5, 0x1c), 2048, 64, 64, 1024, 1, 1 },

{ "EM73C044SND", SPINAND_ID(0xd5, 0x1d), 2048, 64, 64, 1024, 1, 1 },

{ "EM73D044SND", SPINAND_ID(0xd5, 0x1e), 2048, 64, 64, 2048, 1, 1 },

{ "EM73C044VCC", SPINAND_ID(0xd5, 0x22), 2048, 64, 64, 1024, 1, 1 },

{ "EM73C044VCF", SPINAND_ID(0xd5, 0x25), 2048, 64, 64, 1024, 1, 1 },

{ "EM73C044SNC", SPINAND_ID(0xd5, 0x31), 2048, 128, 64, 1024, 1, 1 },

{ "EM73D044SNC", SPINAND_ID(0xd5, 0x0a), 2048, 120, 64, 2048, 1, 1 },

{ "EM73D044SNA", SPINAND_ID(0xd5, 0x12), 2048, 128, 64, 2048, 1, 1 },

{ "EM73D044SNF", SPINAND_ID(0xd5, 0x10), 2048, 128, 64, 2048, 1, 1 },

{ "EM73D044VCA", SPINAND_ID(0xd5, 0x13), 2048, 128, 64, 2048, 1, 1 },

{ "EM73D044VCB", SPINAND_ID(0xd5, 0x14), 2048, 64, 64, 2048, 1, 1 },

{ "EM73D044VCD", SPINAND_ID(0xd5, 0x17), 2048, 128, 64, 2048, 1, 1 },

{ "EM73D044VCH", SPINAND_ID(0xd5, 0x1b), 2048, 64, 64, 2048, 1, 1 },

{ "EM73D044SND", SPINAND_ID(0xd5, 0x1d), 2048, 64, 64, 2048, 1, 1 },

{ "EM73D044VCG", SPINAND_ID(0xd5, 0x1f), 2048, 64, 64, 2048, 1, 1 },

{ "EM73D044VCE", SPINAND_ID(0xd5, 0x20), 2048, 64, 64, 2048, 1, 1 },

{ "EM73D044VCL", SPINAND_ID(0xd5, 0x2e), 2048, 128, 64, 2048, 1, 1 },

{ "EM73D044SNB", SPINAND_ID(0xd5, 0x32), 2048, 128, 64, 2048, 1, 1 },

{ "EM73E044SNA", SPINAND_ID(0xd5, 0x03), 4096, 256, 64, 2048, 1, 1 },

{ "EM73E044SND", SPINAND_ID(0xd5, 0x0b), 4096, 240, 64, 2048, 1, 1 },

{ "EM73E044SNB", SPINAND_ID(0xd5, 0x23), 4096, 256, 64, 2048, 1, 1 },

{ "EM73E044VCA", SPINAND_ID(0xd5, 0x2c), 4096, 256, 64, 2048, 1, 1 },

{ "EM73E044VCB", SPINAND_ID(0xd5, 0x2f), 2048, 128, 64, 4096, 1, 1 },

{ "EM73F044SNA", SPINAND_ID(0xd5, 0x24), 4096, 256, 64, 4096, 1, 1 },

{ "EM73F044VCA", SPINAND_ID(0xd5, 0x2d), 4096, 256, 64, 4096, 1, 1 },

{ "EM73E044SNE", SPINAND_ID(0xd5, 0x0e), 4096, 256, 64, 4096, 1, 1 },

{ "EM73C044SNG", SPINAND_ID(0xd5, 0x0c), 2048, 120, 64, 1024, 1, 1 },

{ "EM73D044VCN", SPINAND_ID(0xd5, 0x0f), 2048, 64, 64, 2048, 1, 1 },

/* Elnec */

{ "FM35Q1GA", SPINAND_ID(0xe5, 0x71), 2048, 64, 64, 1024, 1, 1 },

/* Paragon */

{ "PN26G01A", SPINAND_ID(0xa1, 0xe1), 2048, 128, 64, 1024, 1, 1 },

{ "PN26G02A", SPINAND_ID(0xa1, 0xe2), 2048, 128, 64, 2048, 1, 1 },

/* Ato */

{ "ATO25D1GA", SPINAND_ID(0x9b, 0x12), 2048, 64, 64, 1024, 1, 1 },

/* Heyang */

{ "HYF1GQ4U", SPINAND_ID(0xc9, 0x51), 2048, 128, 64, 1024, 1, 1 },

{ "HYF2GQ4U", SPINAND_ID(0xc9, 0x52), 2048, 128, 64, 2048, 1, 1 },离线

#16 2021-11-14 04:24:49 分享评论

- sunxiang

- 会员

- 注册时间: 2021-05-05

- 已发帖子: 222

- 积分: 116

Re: XFEL已支持spi nand flash烧写

@xboot

大佬,我在使用F1C200S烧写SPI-NAND-FLASH的过程中出现了,一开始是2MB的速度烧写,到百分之一百的时候突然就又跳到百分之0,这个时候烧写速度就变成了33.33kb/s,后面显示需要大约60分钟。

出现这个问题的原因大概是什么,好困惑。

离线

#17 2021-11-14 04:29:44 分享评论

- sunxiang

- 会员

- 注册时间: 2021-05-05

- 已发帖子: 222

- 积分: 116

Re: XFEL已支持spi nand flash烧写

一开始是

2MB/s ETA 0:32

然后烧到100%就又回到0%

33.33KB/s ETA 62:03

离线

楼主 #18 2021-11-14 08:34:27 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

flash 写入时现在分为两个部分,第一个进度条是擦除进度条,第二个进度条是写入进度条,做了分离处理。注意擦除区域会按最小擦除块来擦,会覆盖到所有待写区域。

离线

楼主 #19 2021-11-14 08:40:16 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

你通过spi 直接写入128M,按照33KB/s,差不多就是一个小时,现象都是正常的。

离线

#20 2021-11-14 09:36:28 分享评论

- sunxiang

- 会员

- 注册时间: 2021-05-05

- 已发帖子: 222

- 积分: 116

Re: XFEL已支持spi nand flash烧写

你通过spi 直接写入128M,按照33KB/s,差不多就是一个小时,现象都是正常的。

我知道了,大佬。那个全志官方的烧写,就是那个phoenixSuit烧V3S的BSP,和xfel都是usb,不知道官方那个为什么那么快,还是说官方有什么捷径没有告诉我们,嘻嘻?

离线

#21 2021-11-14 09:44:48 分享评论

- tigger

- Moderator

- 注册时间: 2021-06-18

- 已发帖子: 172

- 积分: 111

Re: XFEL已支持spi nand flash烧写

@sunxiang

官方那个是先下载一个uboot进去烧吧,可以利用整片DDR?

离线

楼主 #22 2021-11-14 11:35:57 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

phoenixSuit具体有没有使用整片DDR,这个是不清楚的,但可以肯定phoenixSuit一定是加载了一个小loader,可能就是利用uboot,然后再去烧录的,肯定不是纯粹的fel模式烧录的,这个跟你在uboot里启动一个fastboot,然后用fastboot来烧录是类似的。效率肯定高很多。

离线

#23 2021-12-19 08:54:58 分享评论

- yang_AE86

- 会员

- 注册时间: 2021-10-19

- 已发帖子: 18

- 积分: 14

Re: XFEL已支持spi nand flash烧写

@xboot

xboot大佬,请问有xfel支持贴片TF卡烧写的计划吗

离线

楼主 #24 2021-12-20 12:14:40 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

烧录tf这个就没有计划支持了,主要原因还是通过fel协议写入大镜像效率不会太高,很有可能是无法忍受的,所以意义也不大。当然真有这种需求也是可以通过用xfel烧录一个特制的uboot到ram中来实现,比如ums,fastoot,dfu等,这个难度不大,基本研究一下uboot就能搞出来.

离线

#25 2021-12-28 19:23:14 分享评论

- byron1784

- 会员

- 注册时间: 2021-12-27

- 已发帖子: 4

- 积分: 4

Re: XFEL已支持spi nand flash烧写

V3s SPI-NAND 两个问题:

1. 烧入失败率极高,5次,只有一次成功

usb bulk send error================= ] 49.975 KB/s, ETA 03:56

2. 烧入后运行不起来。

U-BOOT 2021版的

设置了SPI-NAND Boot

bootcmd 用过 mtd sf nand 都不行

有大佬救命么

离线

#26 2021-12-28 20:59:00 分享评论

- 忘忘大礼包

- 会员

- 注册时间: 2021-12-27

- 已发帖子: 8

- 积分: 66

Re: XFEL已支持spi nand flash烧写

离线

- 不通过:其他

楼主 #27 2021-12-29 09:05:07 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

@byron1784

估计是你USB线缆相关问题,换好点的线材。

spi nand flash 引导对于xboot用如下命令:

烧写普通镜像到SPI Nand Flash

sudo xfel spinand splwrite 2048 1048576 xboot.bin烧写压缩镜像到SPI Nand Flash

sudo xfel spinand splwrite 2048 1048576 xboot.bin.z离线

楼主 #29 2022-01-12 11:37:13 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

看到pull request了,统筹考虑一下,再合并进去。再探讨一个问题,xfel是否需要增加一个命令,在fel模式下,通过otg口,将芯片变成一个U盘呢,就是xfel内置U盘Payload,这种需求有必要考虑吗?

离线

#30 2022-01-12 12:10:29 分享评论

Re: XFEL已支持spi nand flash烧写

>xfel内置U盘Payload

可以啊,有这个好像SD命令可以不要了。

最好能支持高速USB,现在USB只跑12M太慢了。

FLASH因写写入擦除速度的原因,12M是够用了,但用来接SD或EMMC就不够用了。

或也可以保留。

因为win下面无法访问物理扇区,用win32diskimage,在没分区的时候,是可以访问物理0地址的。

但分了区,就会因分区的原因,无法访问高地址的内容。把分区删除掉,就能又访问物理0地址了。

还是linux dd爽。

最近编辑记录 aozima (2022-01-12 12:11:54)

离线

楼主 #31 2022-01-12 13:37:06 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

我先研究下ums功能,看带宽能有多快,对于45KB的SD命令,总觉得是个残缺,实用性有限。

离线

楼主 #32 2022-01-12 16:54:22 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

发现了一个机关,全志烧录工具,本质上是利用FES模式,FES模式是uboot提供的一个命令,叫做sprite_test,当你手动执行这个命令时,就可以进入FES模式,或者改变get_boot_work_mode函数的返回值为WORK_MODE_USB_PRODUCT,则uboot启动时会自动运行sprite_test命令进入FES模式。FES模式下的USB传输协议与FEL基本一致,一些命令的ID做了改变,并扩展了FLASH相关的指令,也就是说,XFEL仅需增加对FES模式的支持后,就可以实现实现flash烧写了。而且,FES模式下FES_PLATFORM_HW_ID永远是0x00161000,不管是哪种芯片。

FES,FEL模式公共命令:

#define APP_LAYER_COMMEN_CMD_VERIFY_DEV 0x0001

#define APP_LAYER_COMMEN_CMD_SWITCH_ROLE 0x0002

#define APP_LAYER_COMMEN_CMD_IS_READY 0x0003

#define APP_LAYER_COMMEN_CMD_GET_CMD_SET_VER 0x0004

#define APP_LAYER_COMMEN_CMD_DISCONNECT 0x0010FES模式特有的命令:

#define FEX_CMD_fes_trans 0x0201

#define FEX_CMD_fes_run 0x0202

#define FEX_CMD_fes_down 0x0206

#define FEX_CMD_fes_up 0x0207

#define FEX_CMD_fes_verify 0x0208

#define FEX_CMD_fes_query_storage 0x0209

#define FEX_CMD_fes_probe_hardware 0x020A

#define FEX_CMD_fes_flash_set_on 0x020A

#define FEX_CMD_fes_flash_set_off 0x020B

#define FEX_CMD_fes_verify_value 0x020C

#define FEX_CMD_fes_verify_status 0x020D

#define FEX_CMD_fes_flash_size_probe 0x020E

#define FEX_CMD_fes_tool_mode 0x020F

#define FEX_CMD_fes_memset 0x0210

#define FEX_CMD_fes_pmu 0x0211

#define FEX_CMD_fes_unseqmem_read 0x0212

#define FEX_CMD_fes_unseqmem_write 0x0213

#define FEX_CMD_fes_force_erase 0x0220

#define FEX_CMD_fes_force_erase_key 0x0221

#define FEX_CMD_fes_reset_cpu 0x0214

#define FEX_CMD_fes_low_power_manger 0x0215

#define FEX_CMD_fes_query_secure 0x0230

#define FEX_CMD_fes_query_info 0x0231理论上是可以实现用xfel来烧录全志image的,也就是说可以代替全志的PhoenixSuit工具的,但这个工作有多大意义就得打个问号了。

离线

楼主 #33 2022-01-12 19:51:14 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

UMS功能在D1上实验失败,不管是官方uboot还是社区的uboot,都没有能支持ums功能,也就是说,要想用uboot来让全志的芯片支持ums功能,还需要大量工作。看来引入uboot是不靠谱的,需要用tinyusb自己写个U盘的payload? 这工作量就大多了,还有一种思路,加载linux内核,由linux内核来实现UMS功能。

离线

#35 2022-01-14 17:14:40 分享评论

- 岁月快快快

- 会员

- 注册时间: 2021-12-25

- 已发帖子: 61

- 积分: 67

Re: XFEL已支持spi nand flash烧写

@xboot

大佬,用sudo xfel spinand write 0 xboot.bin命令和sudo xfel spinand splwrite 2048 1048576 xboot.bin烧程序进nand flash,

烧成功了,但是都没有启动起来,都是直接进了fel下载模式,用sunxi-fel -p spiflash-write 0 xboot.bin命令也是一样的;用xfel spinand命令也检测到了nand flash的型号和容量,读bin数据出来对比也是完全一样,是还有哪里没操作对吗?

用的nand是华邦的W25N01GV,soc是f1c100s;

最近编辑记录 岁月快快快 (2022-01-14 20:06:16)

离线

#36 2022-01-14 17:17:29 分享评论

- 岁月快快快

- 会员

- 注册时间: 2021-12-25

- 已发帖子: 61

- 积分: 67

Re: XFEL已支持spi nand flash烧写

编译bin文件出来的log提示:The bootloader head has been fixed, spl size is 16384 bytes, 我把split-size改成16384也还是不行:

sudo xfel spinand splwrite 16384 1048576 xboot.bin

离线

#37 2022-01-14 20:27:45 分享评论

- 岁月快快快

- 会员

- 注册时间: 2021-12-25

- 已发帖子: 61

- 积分: 67

Re: XFEL已支持spi nand flash烧写

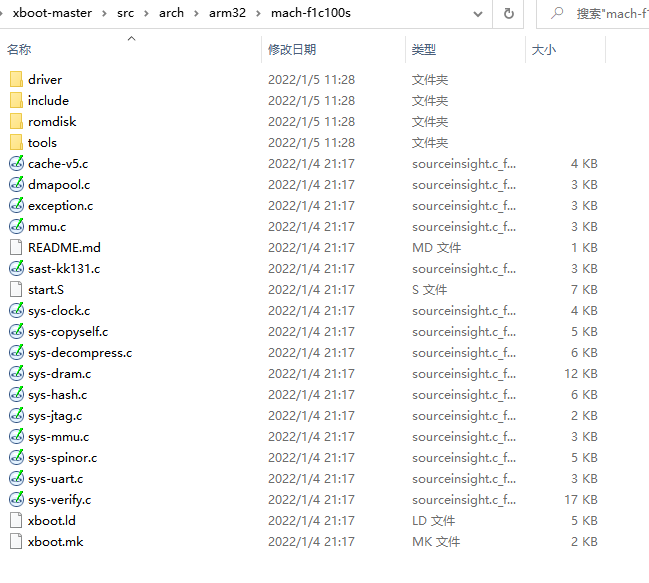

f1c100s目录里面没有sys-spinand.c,感觉可能跟这个有关,加上去再试一下

离线

#38 2022-01-15 11:37:11 分享评论

- 岁月快快快

- 会员

- 注册时间: 2021-12-25

- 已发帖子: 61

- 积分: 67

Re: XFEL已支持spi nand flash烧写

修改了sys-copyself.c

/*

* sys-copyself.c

*

* Copyright(c) 2007-2022 Jianjun Jiang <8192542@qq.com>

* Official site: http://xboot.org

* Mobile phone: +86-18665388956

* QQ: 8192542

*

* Permission is hereby granted, free of charge, to any person obtaining a copy

* of this software and associated documentation files (the "Software"), to deal

* in the Software without restriction, including without limitation the rights

* to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

* copies of the Software, and to permit persons to whom the Software is

* furnished to do so, subject to the following conditions:

*

* The above copyright notice and this permission notice shall be included in all

* copies or substantial portions of the Software.

*

* THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

* IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

* FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

* AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

* LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

* OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE

* SOFTWARE.

*

*/

#include <xboot.h>

extern unsigned char __image_start[];

extern unsigned char __image_end[];

extern unsigned char __heap_start[];

extern void return_to_fel(void);

extern void sys_mmu_init(void);

extern void sys_uart_putc(char c);

extern void sys_decompress(char * src, int slen, char * dst, int dlen);

extern int sys_hash(char * buf, int len, char * sha256);

extern int sys_verify(char * public, char * sha256, char * signature);

extern void sys_spinor_init(void);

extern void sys_spinor_exit(void);

extern void sys_spinor_read(int addr, void * buf, int count);

extern void sys_spinand_init(void);

extern void sys_spinand_exit(void);

extern void sys_spinand_read(int addr, void * buf, int count);

struct zdesc_t { /* Total 256 bytes */

uint8_t magic[4]; /* ZBL! */

uint8_t signature[64]; /* Ecdsa256 signature of sha256 */

uint8_t sha256[32]; /* Sha256 hash */

uint8_t majoy; /* Majoy version */

uint8_t minior; /* Minior version */

uint8_t patch; /* Patch version */

uint8_t csize[4]; /* Compress size of image */

uint8_t dsize[4]; /* Decompress size of image */

uint8_t pubkey[33]; /* Ecdsa256 public key */

uint8_t message[112]; /* Message additionally */

};

enum {

BOOT_DEVICE_FEL = 0,

BOOT_DEVICE_SPINOR,

BOOT_DEVICE_SPINAND,

BOOT_DEVICE_SDCARD,

};

static int get_boot_device(void)

{

u32_t * t = (void *)0x00000058;

if(t[0] == 0x3)

return BOOT_DEVICE_SPINOR;

else if(t[0] == 0x4)

return BOOT_DEVICE_SPINAND;

else if(t[0] == 0x0)

return BOOT_DEVICE_SDCARD;

else if(t[0] == 0x1)

return BOOT_DEVICE_FEL;

return BOOT_DEVICE_SPINOR;

}

void sys_copyself(void)

{

int d = get_boot_device();

if(d == BOOT_DEVICE_FEL)

{

sys_uart_putc('B');

sys_uart_putc('o');

sys_uart_putc('o');

sys_uart_putc('t');

sys_uart_putc(' ');

sys_uart_putc('t');

sys_uart_putc('o');

sys_uart_putc(' ');

sys_uart_putc('F');

sys_uart_putc('E');

sys_uart_putc('L');

sys_uart_putc(' ');

sys_uart_putc('m');

sys_uart_putc('o');

sys_uart_putc('d');

sys_uart_putc('e');

sys_uart_putc('\r');

sys_uart_putc('\n');

return_to_fel();

}

else if(d == BOOT_DEVICE_SPINOR)

{

struct zdesc_t * z = (struct zdesc_t *)__heap_start;

void * mem = (void *)__image_start;

void * tmp = (void *)z + sizeof(struct zdesc_t);

uint32_t size = __image_end - __image_start;

sys_mmu_init();

sys_spinor_init();

sys_spinor_read(24576, z, sizeof(struct zdesc_t));

sys_spinor_exit();

if((z->magic[0] == 'Z') && (z->magic[1] == 'B') && (z->magic[2] == 'L') && (z->magic[3] == '!'))

{

//if(sys_verify((char *)z->pubkey, (char *)z->sha256, (char *)z->signature))

{

uint32_t csize = (z->csize[0] << 24) | (z->csize[1] << 16) | (z->csize[2] << 8) | (z->csize[3] << 0);

uint32_t dsize = (z->dsize[0] << 24) | (z->dsize[1] << 16) | (z->dsize[2] << 8) | (z->dsize[3] << 0);

sys_spinor_init();

sys_spinor_read(24576 + sizeof(struct zdesc_t), tmp, csize);

sys_spinor_exit();

//if(sys_hash((char *)(&z->majoy), (sizeof(struct zdesc_t) - 100) + csize, (char *)z->sha256))

{

sys_decompress(tmp, csize, mem, dsize);

}

}

}

else

{

sys_spinor_init();

sys_spinor_read(0, mem, size);

sys_spinor_exit();

}

}

else if(d == BOOT_DEVICE_SPINAND)

{

struct zdesc_t * z = (struct zdesc_t *)__heap_start;

void * mem = (void *)__image_start;

void * tmp = (void *)z + sizeof(struct zdesc_t);

uint32_t size = __image_end - __image_start;

sys_spinand_init();

sys_spinand_read(1048576 + 65536, z, sizeof(struct zdesc_t));

sys_spinand_exit();

if((z->magic[0] == 'Z') && (z->magic[1] == 'B') && (z->magic[2] == 'L') && (z->magic[3] == '!'))

{

//if(sys_verify((char *)z->pubkey, (char *)z->sha256, (char *)z->signature))

{

uint32_t csize = (z->csize[0] << 24) | (z->csize[1] << 16) | (z->csize[2] << 8) | (z->csize[3] << 0);

uint32_t dsize = (z->dsize[0] << 24) | (z->dsize[1] << 16) | (z->dsize[2] << 8) | (z->dsize[3] << 0);

sys_spinand_init();

sys_spinand_read(1048576 + 65536 + sizeof(struct zdesc_t), tmp, csize);

sys_spinand_exit();

//if(sys_hash((char *)(&z->majoy), (sizeof(struct zdesc_t) - 100) + csize, (char *)z->sha256))

{

sys_decompress(tmp, csize, mem, dsize);

}

}

}

else

{

sys_spinand_init();

sys_spinand_read(1048576, mem, size);

sys_spinand_exit();

}

}

else if(d == BOOT_DEVICE_SDCARD)

{

}

}修改并加入sys-spinand.c

/*

* sys-spinand.c

*

* Copyright(c) 2007-2022 Jianjun Jiang <8192542@qq.com>

* Official site: http://xboot.org

* Mobile phone: +86-18665388956

* QQ: 8192542

*

* Permission is hereby granted, free of charge, to any person obtaining a copy

* of this software and associated documentation files (the "Software"), to deal

* in the Software without restriction, including without limitation the rights

* to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

* copies of the Software, and to permit persons to whom the Software is

* furnished to do so, subject to the following conditions:

*

* The above copyright notice and this permission notice shall be included in all

* copies or substantial portions of the Software.

*

* THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

* IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

* FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE

* AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER

* LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM,

* OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE

* SOFTWARE.

*

*/

#include <xboot.h>

/*

* Default spi nand page size: 2048(11), 4096(12)

*/

#define SPINAND_PAGE_BITS (11)

#define SPINAND_PAGE_MASK ((1 << SPINAND_PAGE_BITS) - 1)

#define SPINAND_PAGE_SIZE (1 << SPINAND_PAGE_BITS)

enum {

SPI_GCR = 0x04,

SPI_TCR = 0x08,

SPI_IER = 0x10,

SPI_ISR = 0x14,

SPI_FCR = 0x18,

SPI_FSR = 0x1c,

SPI_WCR = 0x20,

SPI_CCR = 0x24,

SPI_MBC = 0x30,

SPI_MTC = 0x34,

SPI_BCC = 0x38,

SPI_TXD = 0x200,

SPI_RXD = 0x300,

};

void sys_spinand_init(void)

{

virtual_addr_t addr;

u32_t val;

/* Config GPIOC0, GPIOC1, GPIOC2 and GPIOC3 */

addr = 0x01c20848 + 0x00;

val = read32(addr);

val &= ~(0xf << ((0 & 0x7) << 2));

val |= ((0x2 & 0x7) << ((0 & 0x7) << 2));

write32(addr, val);

val = read32(addr);

val &= ~(0xf << ((1 & 0x7) << 2));

val |= ((0x2 & 0x7) << ((1 & 0x7) << 2));

write32(addr, val);

val = read32(addr);

val &= ~(0xf << ((2 & 0x7) << 2));

val |= ((0x2 & 0x7) << ((2 & 0x7) << 2));

write32(addr, val);

val = read32(addr);

val &= ~(0xf << ((3 & 0x7) << 2));

val |= ((0x2 & 0x7) << ((3 & 0x7) << 2));

write32(addr, val);

/* Deassert spi0 reset */

addr = 0x01c202c0;

val = read32(addr);

val |= (1 << 20);

write32(addr, val);

/* Open the spi0 bus gate */

addr = 0x01c20000 + 0x60;

val = read32(addr);

val |= (1 << 20);

write32(addr, val);

/* Set spi clock rate control register, divided by 4 */

addr = 0x01c05000;

write32(addr + SPI_CCR, 0x00001001);

/* Enable spi0 and do a soft reset */

addr = 0x01c05000;

val = read32(addr + SPI_GCR);

val |= (1 << 31) | (1 << 7) | (1 << 1) | (1 << 0);

write32(addr + SPI_GCR, val);

while(read32(addr + SPI_GCR) & (1 << 31));

val = read32(addr + SPI_TCR);

val &= ~(0x3 << 0);

val |= (1 << 6) | (1 << 2);

write32(addr + SPI_TCR, val);

val = read32(addr + SPI_FCR);

val |= (1 << 31) | (1 << 15);

write32(addr + SPI_FCR, val);

}

void sys_spinand_exit(void)

{

virtual_addr_t addr = 0x01c05000;

u32_t val;

/* Disable the spi0 controller */

val = read32(addr + SPI_GCR);

val &= ~((1 << 1) | (1 << 0));

write32(addr + SPI_GCR, val);

}

static void sys_spi_select(void)

{

virtual_addr_t addr = 0x01c05000;

u32_t val;

val = read32(addr + SPI_TCR);

val &= ~((0x3 << 4) | (0x1 << 7));

val |= ((0 & 0x3) << 4) | (0x0 << 7);

write32(addr + SPI_TCR, val);

}

static void sys_spi_deselect(void)

{

virtual_addr_t addr = 0x01c05000;

u32_t val;

val = read32(addr + SPI_TCR);

val &= ~((0x3 << 4) | (0x1 << 7));

val |= ((0 & 0x3) << 4) | (0x1 << 7);

write32(addr + SPI_TCR, val);

}

static void sys_spi_write_txbuf(u8_t * buf, int len)

{

virtual_addr_t addr = 0x01c05000;

int i;

write32(addr + SPI_MTC, len & 0xffffff);

write32(addr + SPI_BCC, len & 0xffffff);

if(buf)

{

for(i = 0; i < len; i++)

write8(addr + SPI_TXD, *buf++);

}

else

{

for(i = 0; i < len; i++)

write8(addr + SPI_TXD, 0xff);

}

}

static int sys_spi_transfer(void * txbuf, void * rxbuf, int len)

{

virtual_addr_t addr = 0x01c05000;

int count = len;

u8_t * tx = txbuf;

u8_t * rx = rxbuf;

u8_t val;

int n, i;

while(count > 0)

{

n = (count <= 64) ? count : 64;

write32(addr + SPI_MBC, n);

sys_spi_write_txbuf(tx, n);

write32(addr + SPI_TCR, read32(addr + SPI_TCR) | (1 << 31));

while((read32(addr + SPI_FSR) & 0xff) < n);

for(i = 0; i < n; i++)

{

val = read8(addr + SPI_RXD);

if(rx)

*rx++ = val;

}

if(tx)

tx += n;

count -= n;

}

return len;

}

static int sys_spi_write_then_read(void * txbuf, int txlen, void * rxbuf, int rxlen)

{

if(sys_spi_transfer(txbuf, NULL, txlen) != txlen)

return -1;

if(sys_spi_transfer(NULL, rxbuf, rxlen) != rxlen)

return -1;

return 0;

}

static void sys_spinand_wait(void)

{

u8_t tx[2];

u8_t rx[1];

tx[0] = 0x0f;

tx[1] = 0xc0;

do {

sys_spi_select();

sys_spi_write_then_read(tx, 2, rx, 1);

sys_spi_deselect();

} while((rx[0] & 0x1) == 0x1);

}

void sys_spinand_read(int addr, void * buf, int count)

{

u8_t tx[4];

u32_t pa, ca;

int n;

while(count > 0)

{

pa = addr >> SPINAND_PAGE_BITS;

ca = addr & SPINAND_PAGE_MASK;

n = count > (SPINAND_PAGE_SIZE - ca) ? (SPINAND_PAGE_SIZE - ca) : count;

tx[0] = 0x13;

tx[1] = (u8_t)(pa >> 16);

tx[2] = (u8_t)(pa >> 8);

tx[3] = (u8_t)(pa >> 0);

sys_spi_select();

sys_spi_write_then_read(tx, 4, 0, 0);

sys_spi_deselect();

sys_spinand_wait();

tx[0] = 0x03;

tx[1] = (u8_t)(ca >> 8);

tx[2] = (u8_t)(ca >> 0);

tx[3] = 0x0;

sys_spi_select();

sys_spi_write_then_read(tx, 4, buf, n);

sys_spi_deselect();

sys_spinand_wait();

addr += n;

buf += n;

count -= n;

}

}还是起不来,start.S也要改么,还是漏掉了哪个文件没修改![]()

离线

楼主 #39 2022-01-15 17:31:37 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

你指令参数错误了,参考f133的烧录指令

sudo xfel spinand splwrite 2048 1048576 xboot.bin这个意思是spi nand 每个扇区仅使用2KB,如果多余的话,就留空,然后完整镜像放置在1MB位置,splwrite,会在1MB之前复制尽可能多的spl备份,包括0地址也会放一个,存在多份,每个扇区使用2KB还是1KB这个由芯片的brom决定

离线

楼主 #40 2022-01-15 17:35:39 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

F1C100S的话,貌似每个page仅使用1kB,还有一个细节需要注意,就是你spinand的page大小,sys-spinand.c文件里面有个define

/*

* Default spi nand page size: 2048(11), 4096(12)

*/

#define SPINAND_PAGE_BITS (11)

#define SPINAND_PAGE_MASK ((1 << SPINAND_PAGE_BITS) - 1)

#define SPINAND_PAGE_SIZE (1 << SPINAND_PAGE_BITS)离线

楼主 #41 2022-01-15 17:39:32 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

还有一个需要注意的地方自拷贝完整镜像放在1MB偏移的地方,只要注意这些细节,spi nand 就可以引导了。

else if(d == BOOT_DEVICE_SPINAND)

{

struct zdesc_t * z = (struct zdesc_t *)__heap_start;

void * mem = (void *)__image_start;

void * tmp = (void *)z + sizeof(struct zdesc_t);

uint32_t size = __image_end - __image_start;

sys_spinand_init();

sys_spinand_read(1048576 + 65536, z, sizeof(struct zdesc_t));

sys_spinand_exit();

if((z->magic[0] == 'Z') && (z->magic[1] == 'B') && (z->magic[2] == 'L') && (z->magic[3] == '!'))

{

//if(sys_verify((char *)z->pubkey, (char *)z->sha256, (char *)z->signature))

{

uint32_t csize = (z->csize[0] << 24) | (z->csize[1] << 16) | (z->csize[2] << 8) | (z->csize[3] << 0);

uint32_t dsize = (z->dsize[0] << 24) | (z->dsize[1] << 16) | (z->dsize[2] << 8) | (z->dsize[3] << 0);

sys_spinand_init();

sys_spinand_read(1048576 + 65536 + sizeof(struct zdesc_t), tmp, csize);

sys_spinand_exit();

//if(sys_hash((char *)(&z->majoy), (sizeof(struct zdesc_t) - 100) + csize, (char *)z->sha256))

{

sys_decompress(tmp, csize, mem, dsize);

}

}

}

else

{

sys_spinand_init();

sys_spinand_read(1048576, mem, size);

sys_spinand_exit();

}

}离线

#42 2022-01-17 15:14:54 分享评论

- HongSang

- 会员

- 注册时间: 2021-08-12

- 已发帖子: 42

- 积分: 11.5

Re: XFEL已支持spi nand flash烧写

您好请问我如何使用xfel在f1c200s上烧写nand镜像 这里有u-boot.bin zImage dtb和rootfs

离线

#43 2022-01-17 16:06:38 分享评论

- 岁月快快快

- 会员

- 注册时间: 2021-12-25

- 已发帖子: 61

- 积分: 67

Re: XFEL已支持spi nand flash烧写

2048 改成1024,就不进fel下载模式了,但是遇到了个奇怪的问题:

sys-copyself.c:

void test(void)

{

sys_uart_putc('t');

sys_uart_putc('e');

sys_uart_putc('s');

sys_uart_putc('t');

sys_uart_putc(' ');

}

...

else if(d == BOOT_DEVICE_SPINAND)

{

struct zdesc_t * z = (struct zdesc_t *)__heap_start;

void * mem = (void *)__image_start;

void * tmp = (void *)z + sizeof(struct zdesc_t);

uint32_t size = __image_end - __image_start;

//mprintf("enter BOOT_DEVICE_SPINAND !");

sys_uart_putc('1');

sys_uart_putc('6');

sys_uart_putc('6');

sys_uart_putc(' ');

#if 0

sys_spinand_init();

sys_spinand_read(1048576 + 65536, z, sizeof(struct zdesc_t));

sys_spinand_exit();

if((z->magic[0] == 'Z') && (z->magic[1] == 'B') && (z->magic[2] == 'L') && (z->magic[3] == '!'))

{

//if(sys_verify((char *)z->pubkey, (char *)z->sha256, (char *)z->signature))

{

uint32_t csize = (z->csize[0] << 24) | (z->csize[1] << 16) | (z->csize[2] << 8) | (z->csize[3] << 0);

uint32_t dsize = (z->dsize[0] << 24) | (z->dsize[1] << 16) | (z->dsize[2] << 8) | (z->dsize[3] << 0);

sys_spinand_init();

sys_spinand_read(1048576 + 65536 + sizeof(struct zdesc_t), tmp, csize);

sys_spinand_exit();

//if(sys_hash((char *)(&z->majoy), (sizeof(struct zdesc_t) - 100) + csize, (char *)z->sha256))

{

sys_decompress(tmp, csize, mem, dsize);

}

}

}

else

#endif

{

//mprintf("enter line180 !");

test();

nandTest();

sys_uart_putc('1');

sys_uart_putc('9');

sys_uart_putc('4');

sys_uart_putc(' ');

nandTest();

sys_spinand_init();

spinand_read(1048576, mem, size);

spinand_exit();

}

}

else if(d == BOOT_DEVICE_SDCARD)

{

}

...

sys-spinand.c:

void nandTest(void)

{

}sys-copyself.c自拷贝函数中如果调用了sys-spinand.c中的函数就会导致程序像挂掉一样;

测试代码中test()函数之后调用sys-spinand.c中的空函数nandTest(),后面的打印信息“194”就打不出来了,如果不调用nandTest(),就可以正常的打印出

“194”;把测试代码去掉,在sys_spinand_init()函数最开始的地方加上的打印信息,也没有打印出来,所以我推断调了sys-spinand.c中的函数之后程序就挂掉了,没有拷贝成功;

打印信息:

把spi部分的代码全部搬到sys-copyself.c中,就可以正常启动了![]()

不过启动速度有点慢,用了将近5秒才起来,有什么优化办法吗,还是说nand启动就是这么慢的

最近编辑记录 岁月快快快 (2022-01-17 17:05:14)

离线

#44 2022-01-17 16:30:24 分享评论

- HongSang

- 会员

- 注册时间: 2021-08-12

- 已发帖子: 42

- 积分: 11.5

Re: XFEL已支持spi nand flash烧写

@岁月快快快

您好 烧写完能启动吗 可以分享下这两个文件吗

离线

#45 2022-01-17 16:55:43 分享评论

- 岁月快快快

- 会员

- 注册时间: 2021-12-25

- 已发帖子: 61

- 积分: 67

Re: XFEL已支持spi nand flash烧写

@岁月快快快

您好 烧写完能启动吗 可以分享下这两个文件吗

离线

#46 2022-01-17 17:23:24 分享评论

- HongSang

- 会员

- 注册时间: 2021-08-12

- 已发帖子: 42

- 积分: 11.5

Re: XFEL已支持spi nand flash烧写

HongSang 说:@岁月快快快

您好 烧写完能启动吗 可以分享下这两个文件吗

thank you very much

离线

楼主 #47 2022-01-17 18:11:50 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

贴一段之前的总结:

不是对齐问题,这种sys-开头的文件,是需要用特别的编程手段的,因为这些程序的链接地址都是在DDR中,而实际运行地址是在SRAM中,需要实现成地址无关的程序,而系统刚启动,什么环境都不具备,C执行环境,更是不完整的,所以只能用特别编程手段。

一般有一下注意点:

1,不要使用已初始化数据段

2,不要使用未初始化数据段

3,不要使用switch case语句,可以用if elseif 代替

4,不要使用全局变量,仅使用局部变量

5,局部变量的初始化,用代码实现,会编译成立即数赋值

6,只能使用栈空间,其他什么都不可以使用

7,不要调用任何外部库,比如工具链里的C库等。

只要按这种要求,编程,编译出来的代码,都是地址无关的,SPL代码是很特殊的,谨记运行地址不是链接地址,就明白为何需要这样处理了。

当然,这种限制,也导致编程要求较高,如果不想挑战自己,就链接两次,做两个程序吧,BL1->BL2,这种,你看某些芯片的引导链,那么长,就是因为这种原因。

独立的一个程序,支持引导,自举,换到DDR空间,要求是很高的。这种编程技巧,算挑战性编程。

离线

楼主 #48 2022-01-17 18:17:20 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

你的代码需要拷贝到sys-copyself.c里,大概率是链接脚本没修改正确。添加一下就可以解决你的问题了。

.text :

{

PROVIDE(__image_start = .);

PROVIDE(__text_start = .);

PROVIDE(__spl_start = .);

.obj/arch/arm32/mach-f1c100s/start.o (.text*)

.obj/arch/arm32/lib/memcpy.o (.text*)

.obj/arch/arm32/lib/memset.o (.text*)

.obj/arch/arm32/mach-f1c100s/sys-jtag.o (.text*)

.obj/arch/arm32/mach-f1c100s/sys-uart.o (.text*)

.obj/arch/arm32/mach-f1c100s/sys-clock.o (.text*)

.obj/arch/arm32/mach-f1c100s/sys-dram.o (.text*)

.obj/arch/arm32/mach-f1c100s/sys-mmu.o (.text*)

.obj/arch/arm32/mach-f1c100s/sys-decompress.o (.text*)

.obj/arch/arm32/mach-f1c100s/sys-hash.o (.text*)

.obj/arch/arm32/mach-f1c100s/sys-verify.o (.text*)

.obj/arch/arm32/mach-f1c100s/sys-spinor.o (.text*)

.obj/arch/arm32/mach-f1c100s/sys-copyself.o (.text*)

PROVIDE(__spl_end = .);

*(.text*)

*(.init.text)

*(.exit.text)

*(.glue*)

*(.note.gnu.build-id)

PROVIDE(__text_end = .);

} > ram离线

#49 2022-01-17 21:04:32 分享评论

- 岁月快快快

- 会员

- 注册时间: 2021-12-25

- 已发帖子: 61

- 积分: 67

Re: XFEL已支持spi nand flash烧写

get 多谢大佬![]()

离线

#50 2022-01-19 23:48:00 分享评论

- grantho

- 会员

- 注册时间: 2020-03-21

- 已发帖子: 71

- 积分: 2.5

Re: XFEL已支持spi nand flash烧写

厉害,剩下的就是f133相关的驱动了,裸机,rtt如果完善点就完美了

离线

#51 2022-01-25 05:06:17 分享评论

- Zaboy

- 会员

- 注册时间: 2021-12-16

- 已发帖子: 2

- 积分: 3

Re: XFEL已支持spi nand flash烧写

Hello. It was possible to fill in the firmware with nand memory. Moreover, spi nand page size: 2048, and flashed with the xfel spinand splwrite 1024 1048576 xboot.bin command. Everything started!!! But now the image does not fit on the screen. Where in the code can I adjust the screen resolution?

最近编辑记录 Zaboy (2022-01-25 05:07:53)

离线

楼主 #52 2022-01-25 12:48:17 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

https://gitee.com/xboot/xboot/blob/master/src/arch/riscv64/mach-f133/romdisk/boot/mangopi.json

modify json device tree.

"fb-f133-rgb@0x05000000": {

"clock-name-de": "link-de",

"clock-name-tconlcd": "link-tconlcd",

"reset-de": 16,

"reset-tconlcd": 912,

"width": 800,

"height": 480,

"physical-width": 216,

"physical-height": 135,

"bits-per-pixel": 18,

"clock-frequency": 33000000,

"hfront-porch": 40,

"hback-porch": 87,

"hsync-len": 1,

"vfront-porch": 13,

"vback-porch": 31,

"vsync-len": 1,

"hsync-active": false,

"vsync-active": false,

"den-active": true,

"clk-active": true,

"backlight": null

},离线

#53 2022-01-25 12:52:43 分享评论

- xiongxinjian

- 会员

- 注册时间: 2019-01-13

- 已发帖子: 43

- 积分: 13

Re: XFEL已支持spi nand flash烧写

离线

- 不通过:其他

#54 2022-01-26 13:48:13 分享评论

- wangyw_swxk

- 会员

- 注册时间: 2022-01-26

- 已发帖子: 4

- 积分: 4

Re: XFEL已支持spi nand flash烧写

还是用SD卡,更新程序文件。

离线

#55 2022-01-26 15:31:57 分享评论

- Zaboy

- 会员

- 注册时间: 2021-12-16

- 已发帖子: 2

- 积分: 3

Re: XFEL已支持spi nand flash烧写

@xboot

Thanks! Now the logo fits on the screen!!!

But now the interface does not fit

JSON -

"fb-f1c200s@0": {

"clock-name-defe": "link-defe",

"clock-name-debe": "link-debe",

"clock-name-tcon": "link-tcon",

"reset-defe": 46,

"reset-debe": 44,

"reset-tcon": 36,

"width": 480,

"height": 272,

"physical-width": 216,

"physical-height": 135,

"clock-frequency": 33000000,

"hfront-porch": 40,

"hback-porch": 87,

"hsync-len": 1,

"vfront-porch": 13,

"vback-porch": 31,

"vsync-len": 1,

"hsync-active": false,

"vsync-active": false,

"den-active": true,

"clk-active": true,

"backlight": "led-pwm-bl.0"

},

最近编辑记录 Zaboy (2022-01-26 19:25:14)

离线

#56 2022-03-21 00:40:18 分享评论

- xmadc

- 会员

- 注册时间: 2022-03-19

- 已发帖子: 1

- 积分: 1

Re: XFEL已支持spi nand flash烧写

MQ f133 用xfel 烧写xboot 到spinand,重新启动只有下面的信息:

xfel spinand splwrite 2048 1048576 output/xboot.bin

ZQ value = 0x30***********

get_pmu_exist() = 4294967295

ddr_efuse_type: 0xa

[AUTO DEBUG] single rank and full DQ!

ddr_efuse_type: 0xa

[AUTO DEBUG] rank 0 row = 13

[AUTO DEBUG] rank 0 bank = 4

[AUTO DEBUG] rank 0 page size = 2 KB

DRAM BOOT DRIVE INFO: %s

DRAM CLK = 528 MHz

DRAM Type = 2 (2:DDR2,3:DDR3)

DRAMC read ODT off.

DRAM ODT off.

ddr_efuse_type: 0xa

DRAM SIZE =64 M

DRAM simple test OK.但是烧写进DRAM是可以正常启动的,改了下json还打印出了nand 信息。

_ _

_ _ | |___ _____ _____ _| |_

\ \/ /| _ | _ | _ |_ _| (C) 2007-2022

) ( | |_| | |_| | |_| | | |____JIANJUN.JIANG__

/_/\_\|_____|_____|_____| |_____________________|

V3.0.0 (Mar 21 2022 - 00:01:49) - [mangopi][MangoPi-MQ Based On Allwinner F133 SOC]

[ 0.000020]Probe device 'blk-romdisk.0' with blk-romdisk

[ 0.000800]Probe device 'ext-32k' with clk-fixed

[ 0.000810]Probe device 'rc-16m' with clk-fixed

[ 0.000820]Probe device 'dcxo24m' with clk-fixed

[ 0.000830]Probe device 'ext32k-gate' with clk-gate

[ 0.000840]Probe device 'iosc' with clk-gate

[ 0.000850]Probe device 'iosc-div32k' with clk-fixed-factor

[ 0.000860]Probe device 'osc32k' with clk-mux

[ 0.000870]Probe device 'dcxo24m-div32k-gate' with clk-gate

[ 0.000880]Probe device 'dcxo24m-div32k' with clk-fixed-factor

[ 0.000890]Probe device 'rtc32k' with clk-mux

[ 0.000900]Probe device 'rtc-1k' with clk-fixed-factor

[ 0.000910]Probe device 'pll-cpux' with clk-f133-pll

[ 0.000920]Probe device 'pll-ddr0' with clk-f133-pll

[ 0.000930]Probe device 'pll-periph0-parent' with clk-f133-pll

[ 0.000940]Probe device 'pll-video0' with clk-f133-pll

[ 0.000950]Probe device 'pll-video1' with clk-f133-pll

[ 0.000960]Probe device 'pll-ve' with clk-f133-pll

[ 0.000970]Probe device 'pll-audio0-4x' with clk-f133-pll

[ 0.000980]Probe device 'pll-audio1' with clk-f133-pll

[ 0.000990]Probe device 'pll-cpux-div' with clk-ratio

[ 0.001000]Probe device 'pll-periph0-2x' with clk-divider

[ 0.001010]Probe device 'pll-periph0-800m' with clk-divider

[ 0.001020]Probe device 'pll-periph0' with clk-fixed-factor

[ 0.001030]Probe device 'pll-periph0-div3' with clk-fixed-factor

[ 0.001040]Probe device 'pll-video0-4x' with clk-fixed-factor

[ 0.001050]Probe device 'pll-video0-2x' with clk-fixed-factor

[ 0.001060]Probe device 'pll-video1-4x' with clk-fixed-factor

[ 0.001070]Probe device 'pll-video1-2x' with clk-fixed-factor

[ 0.001080]Probe device 'pll-audio0-2x' with clk-fixed-factor

[ 0.001090]Probe device 'pll-audio0' with clk-fixed-factor

[ 0.001100]Probe device 'pll-audio1-div5' with clk-divider

[ 0.001110]Probe device 'pll-audio1-div2' with clk-divider

[ 0.001120]Probe device 'mux-psi' with clk-mux

[ 0.001130]Probe device 'div-psi' with clk-divider

[ 0.001140]Probe device 'psi-ahb' with clk-ratio

[ 0.001150]Probe device 'mux-apb0' with clk-mux

[ 0.001160]Probe device 'div-apb0' with clk-divider

[ 0.001170]Probe device 'apb0' with clk-ratio

[ 0.001180]Probe device 'mux-apb1' with clk-mux

[ 0.001190]Probe device 'div-apb1' with clk-divider

[ 0.001200]Probe device 'apb1' with clk-ratio

[ 0.001210]Probe device 'mux-riscv' with clk-mux

[ 0.001220]Probe device 'riscv' with clk-divider

[ 0.001230]Probe device 'riscv-axi' with clk-divider

[ 0.001240]Probe device 'mux-timer0' with clk-mux

[ 0.001250]Probe device 'timer0' with clk-ratio

[ 0.001260]Probe device 'mux-timer1' with clk-mux

[ 0.001270]Probe device 'timer1' with clk-ratio

[ 0.001280]Probe device 'mux-spi0' with clk-mux

[ 0.001290]Probe device 'div-spi0' with clk-divider

[ 0.001300]Probe device 'radio-spi0' with clk-ratio

[ 0.001310]Probe device 'gate-spi0' with clk-gate

[ 0.001320]Probe device 'spi0' with clk-gate

[ 0.001330]Probe device 'mux-spi1' with clk-mux

[ 0.001340]Probe device 'div-spi1' with clk-divider

[ 0.001350]Probe device 'radio-spi1' with clk-ratio

[ 0.001360]Probe device 'gate-spi1' with clk-gate

[ 0.001370]Probe device 'spi1' with clk-gate

[ 0.001380]Probe device 'mux-sdmmc0' with clk-mux

[ 0.001390]Probe device 'div-sdmmc0' with clk-divider

[ 0.001400]Probe device 'radio-sdmmc0' with clk-ratio

[ 0.001410]Probe device 'gate-sdmmc0' with clk-gate

[ 0.001420]Probe device 'mux-sdmmc1' with clk-mux

[ 0.001430]Probe device 'div-sdmmc1' with clk-divider

[ 0.001440]Probe device 'radio-sdmmc1' with clk-ratio

[ 0.001450]Probe device 'gate-sdmmc1' with clk-gate

[ 0.001460]Probe device 'mux-sdmmc2' with clk-mux

[ 0.001470]Probe device 'div-sdmmc2' with clk-divider

[ 0.001480]Probe device 'radio-sdmmc2' with clk-ratio

[ 0.001490]Probe device 'gate-sdmmc2' with clk-gate

[ 0.001500]Probe device 'mux-ledc' with clk-mux

[ 0.001510]Probe device 'div-ledc' with clk-divider

[ 0.001520]Probe device 'radio-ledc' with clk-ratio

[ 0.001530]Probe device 'ledc' with clk-gate

[ 0.001540]Probe device 'mux-tpadc' with clk-mux

[ 0.001550]Probe device 'gate-tpadc' with clk-gate

[ 0.001560]Probe device 'link-tpadc' with clk-link

[ 0.001570]Probe device 'mux-de' with clk-mux

[ 0.001580]Probe device 'div-de' with clk-divider

[ 0.001590]Probe device 'gate-de' with clk-gate

[ 0.001600]Probe device 'link-de' with clk-link

[ 0.001610]Probe device 'mux-tconlcd' with clk-mux

[ 0.001620]Probe device 'div-tconlcd' with clk-divider

[ 0.001630]Probe device 'ratio-tconlcd' with clk-ratio

[ 0.001640]Probe device 'gate-tconlcd' with clk-gate

[ 0.001650]Probe device 'link-tconlcd' with clk-link

[ 0.001660]Probe device 'bus-pwm' with clk-gate

[ 0.001670]Probe device 'bus-iommu' with clk-gate

[ 0.001680]Probe device 'bus-ir-tx' with clk-gate

[ 0.001690]Probe device 'bus-gpadc' with clk-gate

[ 0.001700]Probe device 'bus-ths' with clk-gate

[ 0.001710]Probe device 'bus-spdif' with clk-gate

[ 0.001720]Probe device 'bus-dmic' with clk-gate

[ 0.001730]Probe device 'bus-audio-codec' with clk-gate

[ 0.001740]Probe device 'bus-tpadc' with clk-gate

[ 0.001750]Probe device 'bus-tzma' with clk-gate

[ 0.001760]Probe device 'bus-uart0' with clk-gate

[ 0.001770]Probe device 'bus-uart1' with clk-gate

[ 0.001780]Probe device 'bus-uart2' with clk-gate

[ 0.001790]Probe device 'bus-uart3' with clk-gate

[ 0.001800]Probe device 'bus-uart4' with clk-gate

[ 0.001810]Probe device 'bus-uart5' with clk-gate

[ 0.001820]Probe device 'bus-i2c0' with clk-gate

[ 0.001830]Probe device 'bus-i2c1' with clk-gate

[ 0.001840]Probe device 'bus-i2c2' with clk-gate

[ 0.001850]Probe device 'bus-i2c3' with clk-gate

[ 0.001860]Probe device 'bus-can0' with clk-gate

[ 0.001870]Probe device 'bus-can1' with clk-gate

[ 0.001880]Probe device 'bus-i2s0' with clk-gate

[ 0.001890]Probe device 'bus-i2s1' with clk-gate

[ 0.001900]Probe device 'bus-i2s2' with clk-gate

[ 0.001910]Probe device 'bus-de' with clk-gate

[ 0.001920]Probe device 'bus-di' with clk-gate

[ 0.001930]Probe device 'bus-g2d' with clk-gate

[ 0.001940]Probe device 'bus-ce' with clk-gate

[ 0.001950]Probe device 'bus-ve' with clk-gate

[ 0.001960]Probe device 'bus-dma' with clk-gate

[ 0.001970]Probe device 'bus-msgbox0' with clk-gate

[ 0.001980]Probe device 'bus-msgbox1' with clk-gate

[ 0.001990]Probe device 'bus-msgbox2' with clk-gate

[ 0.002000]Probe device 'bus-spinlock' with clk-gate

[ 0.002010]Probe device 'bus-hstimer' with clk-gate

[ 0.002020]Probe device 'bus-dbg' with clk-gate

[ 0.002030]Probe device 'bus-dram' with clk-gate

[ 0.002040]Probe device 'bus-mmc0' with clk-gate

[ 0.002050]Probe device 'bus-mmc1' with clk-gate

[ 0.002060]Probe device 'bus-mmc2' with clk-gate

[ 0.002070]Probe device 'bus-emac0' with clk-gate

[ 0.002080]Probe device 'bus-ohci0' with clk-gate

[ 0.002090]Probe device 'bus-ohci1' with clk-gate

[ 0.002100]Probe device 'bus-ehci0' with clk-gate

[ 0.002110]Probe device 'bus-ehci1' with clk-gate

[ 0.002120]Probe device 'bus-otg' with clk-gate

[ 0.002130]Probe device 'bus-lradc' with clk-gate

[ 0.002140]Probe device 'bus-dpss-top' with clk-gate

[ 0.002150]Probe device 'bus-hdmi' with clk-gate

[ 0.002160]Probe device 'bus-mipi-dsi' with clk-gate

[ 0.002170]Probe device 'bus-tcon-lcd' with clk-gate

[ 0.002180]Probe device 'bus-tcon-tv' with clk-gate

[ 0.002190]Probe device 'bus-tve-top' with clk-gate

[ 0.002200]Probe device 'bus-tve' with clk-gate

[ 0.002210]Probe device 'bus-tvd-top' with clk-gate

[ 0.002220]Probe device 'bus-tvd' with clk-gate

[ 0.002230]Probe device 'bus-ledc' with clk-gate

[ 0.002240]Probe device 'bus-csi' with clk-gate

[ 0.002250]Probe device 'bus-dsp-cfg' with clk-gate

[ 0.002260]Probe device 'bus-riscv-cfg' with clk-gate

[ 0.002270]Probe device 'wdg' with clk-link

[ 0.002280]Probe device 'reset-f133.0' with reset-f133

[ 0.002290]Probe device 'reset-f133.1' with reset-f133

[ 0.002300]Probe device 'reset-f133.2' with reset-f133

[ 0.002310]Probe device 'reset-f133.3' with reset-f133

[ 0.002320]Probe device 'reset-f133.4' with reset-f133

[ 0.002330]Probe device 'reset-f133.5' with reset-f133

[ 0.002340]Probe device 'reset-f133.6' with reset-f133

[ 0.002350]Probe device 'reset-f133.7' with reset-f133

[ 0.002360]Probe device 'reset-f133.8' with reset-f133

[ 0.002370]Probe device 'reset-f133.9' with reset-f133

[ 0.002380]Probe device 'reset-f133.10' with reset-f133

[ 0.002390]Probe device 'reset-f133.11' with reset-f133

[ 0.002400]Probe device 'reset-f133.12' with reset-f133

[ 0.002410]Probe device 'reset-f133.13' with reset-f133

[ 0.002420]Probe device 'reset-f133.14' with reset-f133

[ 0.002430]Probe device 'reset-f133.15' with reset-f133

[ 0.002440]Probe device 'reset-f133.16' with reset-f133

[ 0.002450]Probe device 'reset-f133.17' with reset-f133

[ 0.002460]Probe device 'reset-f133.18' with reset-f133

[ 0.002470]Probe device 'reset-f133.19' with reset-f133

[ 0.002480]Probe device 'reset-f133.20' with reset-f133

[ 0.002490]Probe device 'reset-f133.21' with reset-f133

[ 0.002500]Probe device 'reset-f133.22' with reset-f133

[ 0.002510]Probe device 'reset-f133.23' with reset-f133

[ 0.002520]Probe device 'reset-f133.24' with reset-f133

[ 0.002530]Probe device 'reset-f133.25' with reset-f133

[ 0.002540]Probe device 'reset-f133.26' with reset-f133

[ 0.002550]Probe device 'reset-f133.27' with reset-f133

[ 0.002560]Probe device 'reset-f133.28' with reset-f133

[ 0.002570]Probe device 'reset-f133.29' with reset-f133

[ 0.002580]Probe device 'reset-f133.30' with reset-f133

[ 0.002590]Probe device 'reset-f133.31' with reset-f133

[ 0.002600]Probe device 'reset-f133.32' with reset-f133

[ 0.002610]Probe device 'reset-f133.33' with reset-f133

[ 0.002620]Probe device 'reset-f133.34' with reset-f133

[ 0.002630]Probe device 'reset-f133.35' with reset-f133

[ 0.002640]Probe device 'reset-f133.36' with reset-f133

[ 0.002650]Probe device 'reset-f133.37' with reset-f133

[ 0.002660]Probe device 'irq-f133.0' with irq-f133

[ 0.002670]Probe device 'irq-f133-gpio.0' with irq-f133-gpio

[ 0.002680]Probe device 'irq-f133-gpio.1' with irq-f133-gpio

[ 0.002690]Probe device 'irq-f133-gpio.2' with irq-f133-gpio

[ 0.002700]Probe device 'irq-f133-gpio.3' with irq-f133-gpio

[ 0.002710]Probe device 'irq-f133-gpio.4' with irq-f133-gpio

[ 0.002720]Probe device 'irq-f133-gpio.5' with irq-f133-gpio

[ 0.002730]Probe device 'gpio-f133.0' with gpio-f133

[ 0.002740]Probe device 'gpio-f133.1' with gpio-f133

[ 0.002750]Probe device 'gpio-f133.2' with gpio-f133

[ 0.002760]Probe device 'gpio-f133.3' with gpio-f133

[ 0.002770]Probe device 'gpio-f133.4' with gpio-f133

[ 0.002780]Probe device 'gpio-f133.5' with gpio-f133

[ 0.002830]Probe device 'dma-f133.0' with dma-f133

[ 0.002880]Probe device 'adc-f133.0' with adc-f133

[ 0.002890]Probe device 'ce-f133-timer.0' with ce-f133-timer

[ 0.000027]Probe device 'cs-f133-timer.0' with cs-f133-timer

[ 0.005681]Probe device 'uart-16550.0' with uart-16550

[ 0.011122]Probe device 'uart-16550.1' with uart-16550

[ 0.016491]Probe device 'uart-16550.2' with uart-16550

[ 0.021606]Probe device 'uart-16550.3' with uart-16550

[ 0.026976]Probe device 'uart-16550.4' with uart-16550

[ 0.032098]Probe device 'uart-16550.5' with uart-16550

[ 0.037196]Probe device 'i2c-f133.0' with i2c-f133

[ 0.041958]Probe device 'i2c-f133.1' with i2c-f133

[ 0.046729]Probe device 'i2c-f133.2' with i2c-f133

[ 0.051729]Probe device 'i2c-f133.3' with i2c-f133

[ 0.056521]Probe device 'spi-f133.0' with spi-f133

[ 0.161552]Found spi nand flash 'MX35LF2G14AC' with 256.000MB

[ 0.167466]Found partition:

[ 0.170387] 0x0000000000000000 ~ 0x000000000fffffff 256.000MB - blk-spinand.0

[ 0.177596] 0x0000000000000000 ~ 0x00000000003fffff 4.000MB - blk-spinand.0.xboot

[ 0.185309] 0x0000000000400000 ~ 0x000000000fffffff 252.000MB - blk-spinand.0.private

[ 0.193570]Probe device 'blk-spinand.0' with blk-spinand

[ 0.303537]Probe device 'sdhci-f133.0' with sdhci-f133

[ 0.308815]Probe device 'rtc-f133.0' with rtc-f133

[ 0.313573]Probe device 'wdg-f133.0' with wdg-f133

[ 0.318299]Probe device 'ldoa' with regulator-f133-ldo

[ 0.323657]Probe device 'ldob' with regulator-f133-ldo

[ 0.344906]Fail to probe device with ts-gt911

[ 0.351045]Probe device 'fb-f133-rgb.0' with fb-f133-rgb

[ 0.356539]Probe device 'console-uart.0' with console-uart

[ 0.363816]mount /private with 'ram' filesystem

Press any key to stop auto boot: 0.000

xboot: /# 编译命令

make CROSS_COMPILE=~/bin/Xuantie-900-gcc-elf-newlib-x86_64-V2.2.4/bin/riscv64-unknown-elf- PLATFORM=riscv64-f133串口打印了下,应该是没有进xboot_main(), 大佬看下这可能是什么原因?

离线

楼主 #57 2022-03-21 17:24:35 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

看具体操作没看出啥问题,难道spi nand坏块了?

离线

#58 2022-04-14 15:36:04 分享评论

- yang_max007

- 会员

- 注册时间: 2022-04-14

- 已发帖子: 3

- 积分: 3

Re: XFEL已支持spi nand flash烧写

@xboot

大神,能支持一下S3 的 spi nand flash 改型号吗

离线

楼主 #59 2022-04-15 15:19:34 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

S3是完整支持的

离线

#60 2022-06-26 15:41:00 分享评论

- jlzheng

- 会员

- 注册时间: 2022-03-02

- 已发帖子: 4

- 积分: 5

Re: XFEL已支持spi nand flash烧写

@xboot 感谢提供xfel工具。我用的是一块V3s+MX35LF1GE4AB spinand, 碰到个奇怪的问题。用xfel 直接写入或擦除后写入都会读不出来,但是擦除后下电再上电,然后写入就能成功读出。请教下这是什么原因?谢谢。

离线

楼主 #61 2022-06-27 09:58:57 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

@xboot 感谢提供xfel工具。我用的是一块V3s+MX35LF1GE4AB spinand, 碰到个奇怪的问题。用xfel 直接写入或擦除后写入都会读不出来,但是擦除后下电再上电,然后写入就能成功读出。请教下这是什么原因?谢谢。

你的意思是写入后,需要掉电下,才能正常读出来?否则,读不出来?

用最新的xfel了吗?

离线

#62 2022-06-27 15:10:21 分享评论

- jlzheng

- 会员

- 注册时间: 2022-03-02

- 已发帖子: 4

- 积分: 5

Re: XFEL已支持spi nand flash烧写

@xboot 谢谢回复。是需要全片擦除后重新上电,才能写入成功并正常读出。如果直接写入(也会自动擦除)或先擦除后写入都不能正常读出(应该是写入虽然报了100%成功但实际没有成功)。使用了最新版本,芯片检测正常,不管是否断电,写入过程都会显示擦除100%完成,写入100%完成。

最近编辑记录 jlzheng (2022-06-27 15:21:19)

离线

#63 2022-06-27 15:50:30 分享评论

- jlzheng

- 会员

- 注册时间: 2022-03-02

- 已发帖子: 4

- 积分: 5

Re: XFEL已支持spi nand flash烧写

C:\xfel-windows-v1.2.9>xfel spinand

Found spi nand flash 'MX35LF1GE4AB' with 134217728 bytes

C:\xfel-windows-v1.2.9>xfel spinand splwrite 1024 0 sunxi-spl.bin

100% [================================================] 128.000 KB, 98.663 KB/s

C:\xfel-windows-v1.2.9>xfel spinand write 0x20000 u-boot.img

100% [================================================] 427.879 KB, 96.931 KB/s

C:\xfel-windows-v1.2.9>xfel spinand write 0x100000 sun8i-v3s-licheepi-zero-dock.dtb

100% [================================================] 12.109 KB, 109.700 KB/s

C:\xfel-windows-v1.2.9>xfel spinand write 0x120000 zImage

100% [================================================] 4.875 MB, 96.847 KB/s

启动时读出会失败:

NAND read: device 0 offset 0x100000, size 0x10000

NAND read from offset 100000 failed -74

0 bytes read: ERROR

NAND read: device 0 offset 0x120000, size 0x800000

NAND read from offset 120000 failed -74

0 bytes read: ERROR

但如果整片擦除:

C:\xfel-windows-v1.2.9>xfel spinand erase 0 0x8000000

100% [================================================] 128.000 MB, 17.756 MB/s

然后重新上电再写入,启动时就能正常读出:

NAND read: device 0 offset 0x100000, size 0x10000

65536 bytes read: OK

NAND read: device 0 offset 0x120000, size 0x800000

8388608 bytes read: OK

最近编辑记录 jlzheng (2022-06-27 15:54:43)

离线

楼主 #64 2022-06-27 19:10:20 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

有其他spi nand吗?是否也是同样的现象,还是仅仅是个别spi nand有这种问题?

离线

#65 2022-06-27 22:48:39 分享评论

- jlzheng

- 会员

- 注册时间: 2022-03-02

- 已发帖子: 4

- 积分: 5

Re: XFEL已支持spi nand flash烧写

同型号的试过3块,都这样。

我查了一下,-74是ecc错误。这个ecc要擦除后下电才能真正擦除?

最近编辑记录 jlzheng (2022-06-27 23:14:16)

离线

楼主 #66 2022-06-28 11:23:11 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: XFEL已支持spi nand flash烧写

估计还是某些型号的spi nand在操作上有些特殊,可以对照手册研究下,看是否能解决这个问题。

离线

#67 2023-05-24 16:46:55 分享评论

- qiujian2021

- 会员

- 注册时间: 2023-05-18

- 已发帖子: 3

- 积分: 3

Re: XFEL已支持spi nand flash烧写

@Zaboy ,

How to define : "led-pwm-bl.0" ?

JSON -

"fb-f1c200s@0": {

"clock-name-defe": "link-defe",

"clock-name-debe": "link-debe",

"clock-name-tcon": "link-tcon",

"reset-defe": 46,

"reset-debe": 44,

"reset-tcon": 36,

"width": 480,

"height": 272,

"physical-width": 216,

"physical-height": 135,

"clock-frequency": 33000000,

"hfront-porch": 40,

"hback-porch": 87,

"hsync-len": 1,

"vfront-porch": 13,

"vback-porch": 31,

"vsync-len": 1,

"hsync-active": false,

"vsync-active": false,

"den-active": true,

"clk-active": true,

"backlight": "led-pwm-bl.0"

},

最近编辑记录 qiujian2021 (2023-05-24 16:48:00)

离线

#68 2023-06-07 16:33:58 分享评论

- tangloong

- 会员

- 注册时间: 2023-04-11

- 已发帖子: 213

- 积分: 192

Re: XFEL已支持spi nand flash烧写

很奇怪 我用

xfel spinand splwrite 1024 0x00000000 boot.bin

xfel spinand write 0x00010000 rtthread.bin

每次都清空了 例如 两条命名都执行的话 0-1M空间就全是FF了,要是再单独执行写入boot,1M之后的空间就成FF了

咋样才能执行前不擦除呢?或者同事写入两个文件 nand Flash是 GD5F1GQ4UAYIG

离线

#69 2024-03-12 18:41:51 分享评论

Re: XFEL已支持spi nand flash烧写

@tangloong

很奇怪 我用

xfel spinand splwrite 1024 0x00000000 boot.bin

xfel spinand write 0x00010000 rtthread.bin

每次都清空了 例如 两条命名都执行的话 0-1M空间就全是FF了,要是再单独执行写入boot,1M之后的空间就成FF了

咋样才能执行前不擦除呢?或者同事写入两个文件 nand Flash是 GD5F1GQ4UAYIG

1. 先要将 boot.bin 的跳转改到 0x00020000;

2. 再将 rtthread.bin 写到 0x00020000;

因单独执行写入boot.bin 会自动先擦128K,然后再写入的

xfel spinand splwrite 0x00000000 boot.bin

xfel spinand write 0x00020000 rtthread.bin

这样写入的和读出的数据一致了,但不知为什么还是跑不起来?

离线

#70 2024-04-23 21:54:24 分享评论

- oneofzero

- 会员

- 注册时间: 2022-10-18

- 已发帖子: 7

- 积分: 7

Re: XFEL已支持spi nand flash烧写

xboot t113 怎么从sd卡启动?测试在内存运行ok。我这个板子没有flash。只有sd卡。。。

离线

#72 2025-02-17 10:29:34 分享评论

- KoGu

- 会员

- 注册时间: 2024-08-15

- 已发帖子: 5

- 积分: 5

Re: XFEL已支持spi nand flash烧写

请问一下,我在linux下clone了源码,然后我添加里的自己板子上的flash型号,我要怎么编译出win10下使用的exe呢?

离线

#73 2025-02-17 10:54:04 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,449

- 积分: 9202

Re: XFEL已支持spi nand flash烧写

请问一下,我在linux下clone了源码,然后我添加里的自己板子上的flash型号,我要怎么编译出win10下使用的exe呢?

用 MSVC2017 编译 XFEL 项目

https://whycan.com/t_6660.html

离线

#74 2025-03-13 09:14:51 分享评论

- liubuf

- 会员

- 注册时间: 2024-10-22

- 已发帖子: 16

- 积分: 6

Re: XFEL已支持spi nand flash烧写

这个支持emmc烧写么

离线

#75 2025-05-08 20:54:43 分享评论

- ShadChen

- 会员

- 注册时间: 2025-01-02

- 已发帖子: 5

- 积分: 4

Re: XFEL已支持spi nand flash烧写

请问目前有计划支持T536和T527吗?

离线

#76 2026-01-14 10:39:40 分享评论

- Kaelon

- 会员

- 注册时间: 2026-01-14

- 已发帖子: 1

- 积分: 1

Re: XFEL已支持spi nand flash烧写

佬,怎么生成烧录v3s所需要的bin文件呢?

离线

#77 2026-01-14 11:47:16 分享评论

- 晕哥

- 管理员

- 所在地: wechat: whycan_cn

- 注册时间: 2017-09-06

- 已发帖子: 9,449

- 积分: 9202

Re: XFEL已支持spi nand flash烧写

佬,怎么生成烧录v3s所需要的bin文件呢?

(V3s/V3x/S3/S3L/R11通吃)小智V3s开发板smallwitpi lite u-boot/linux/buildroot测试

https://whycan.com/t_7248.html

离线

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发