楼主 # 2024-10-30 17:50:53 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

T113-I ddr初始化失败[悬赏200块]

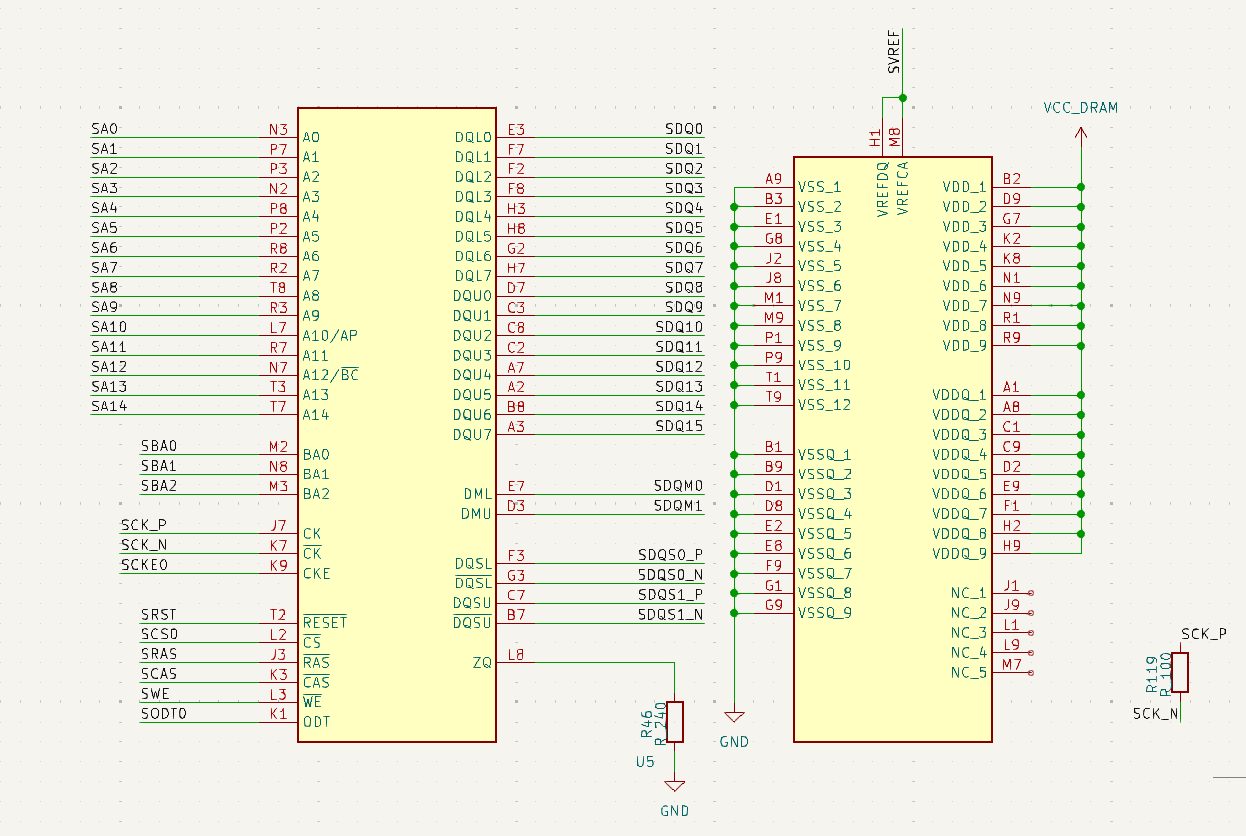

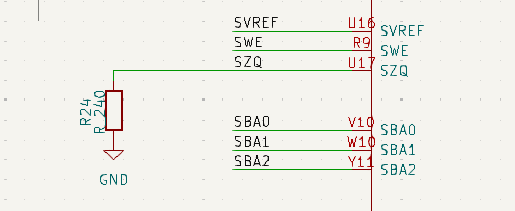

自己做了个板子测试T113-I, ddr3用了NT5CC256M16ER和F60C1A0004都试过了,spl启动的时候识别不到dram,试过降低频率,降低到120M也不行。焊接是过得回流焊,几块都是一样反应。VDRAM=1.33V, vref=0.66v, 电压看起来都正常,封装检查过很多次了,应该没有问题。有没有大哥帮忙分析下什么问题,悬赏200块解决问题。

[96]HELLO! BOOT0 is starting!

[99]BOOT0 commit : 09b36272

[102]set pll start

[108]periph0 has been enabled

[111]set pll end

[112][pmu]: bus read error

[115]board init ok

[117]enable_jtag

[118]DRAM only have internal ZQ!!

[122]get_pmu_exist() = -1

[124]ddr_efuse_type: 0x0

[127]mark_id: 0x34

[129]trefi:7.8ms

[131]DX0 state:1

[133]DX1 state:1

[134][ERROR DEBUG] auto scan dram rank&width fail !

[139]init dram fail

最近编辑记录 aeo1234 (2024-10-30 19:55:35)

离线

#1 2024-10-31 13:17:14 分享评论

- wupaul2001

- 会员

- 注册时间: 2019-09-30

- 已发帖子: 307

- 积分: 275

Re: T113-I ddr初始化失败[悬赏200块]

dram的配置参数不对,先用DragonHD调试

离线

#2 2024-10-31 13:28:31 分享评论

- wupaul2001

- 会员

- 注册时间: 2019-09-30

- 已发帖子: 307

- 积分: 275

Re: T113-I ddr初始化失败[悬赏200块]

离线

楼主 #3 2024-10-31 16:20:45 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

dram的配置参数不对,先用DragonHD调试

Round : 1

Running : DDR3-uart_init

uart init finish!

Running : DDR3-dram_init

DragonHD V3.0,dram init fail! channel0----(byte0 erro:1,byte1 erro:1,byte2 erro:0,byte3 erro:0)

parameter Fail:[DDR3-dram_init] .看起来两个byte都不通,是硬件问题可能较大吗。不过焊了几块都这样,难绷啊:(

离线

#4 2024-11-02 14:00:35 分享评论

- wupaul2001

- 会员

- 注册时间: 2019-09-30

- 已发帖子: 307

- 积分: 275

Re: T113-I ddr初始化失败[悬赏200块]

@aeo1234

选看看参数是否不对?位宽等等,具体你可以在DragonHD的dram_init右击修改。

最近编辑记录 wupaul2001 (2024-11-02 14:02:45)

离线

#5 2024-11-08 16:52:42 分享评论

- kst_zlj

- 会员

- 注册时间: 2024-11-06

- 已发帖子: 5

- 积分: 0

Re: T113-I ddr初始化失败[悬赏200块]

DDR3 供电不是1.5么

离线

楼主 #6 2024-11-09 14:46:29 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

DDR3 供电不是1.5么

焊的是ddr3l,电压是1.35

离线

楼主 #7 2024-11-09 14:46:53 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

@aeo1234

选看看参数是否不对?位宽等等,具体你可以在DragonHD的dram_init右击修改。

目前看起来是原理图不对,完全不能识别

离线

#8 2024-11-11 14:04:30 分享评论

- suibian

- 会员

- 注册时间: 2023-03-24

- 已发帖子: 21

- 积分: 41

Re: T113-I ddr初始化失败[悬赏200块]

哈哈,200要归我了。

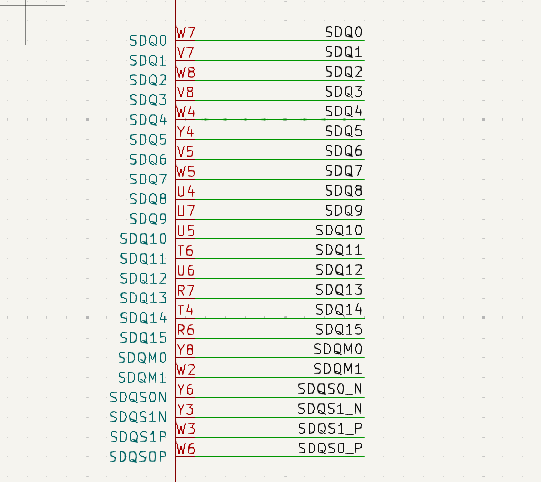

找到全志的参考原理图调整数据线的线序,你这个线序不对。

离线

#9 2024-11-11 14:09:21 分享评论

- suibian

- 会员

- 注册时间: 2023-03-24

- 已发帖子: 21

- 积分: 41

Re: T113-I ddr初始化失败[悬赏200块]

离线

#13 2024-11-18 12:25:46 分享评论

- Gentlepig

- 会员

- 注册时间: 2018-10-24

- 已发帖子: 1,409

- 积分: 1373.5

Re: T113-I ddr初始化失败[悬赏200块]

哈哈,200要归我了。

找到全志的参考原理图调整数据线的线序,你这个线序不对。

没看明白,看了下官方这个图,数据线是一一对应的,地址线倒是打乱了。

楼主截图只截出了数据线,貌似和官方原理图一样的,地址线没截出来。

离线

#14 2024-11-18 15:03:39 分享评论

- as86455011

- 会员

- 注册时间: 2018-11-20

- 已发帖子: 33

- 积分: 4

Re: T113-I ddr初始化失败[悬赏200块]

楼主可以从2个方便入手,

1、校对一下原理图(kicad好评)

2、layout有无问题

离线

楼主 #15 2024-11-18 15:24:54 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

哈哈,200要归我了。

找到全志的参考原理图调整数据线的线序,你这个线序不对。

确实很诡异,我淘宝买了一个哪吒开发板的资料包。30块,正在打样中,还不知道行不行

离线

楼主 #16 2024-11-18 15:25:26 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

suibian 说:哈哈,200要归我了。

找到全志的参考原理图调整数据线的线序,你这个线序不对。@aeo1234 请问楼主你的问题解决了吗?

已给楼主发 email

还没有,还在改版打样中

离线

楼主 #17 2024-11-18 15:30:30 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

@Gentlepig

这是淘宝30块钱买的哪吒开发板的原理图,我看和楼上发的官方资料差不多,那个线序是乱的,有没有大佬知道是为什么,是原理图封装故意标错了吗

D1-H_SCHEMATIC_NEZA_V1_2.pdf

D1-H_package.zip

离线

楼主 #18 2024-11-18 15:38:32 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

哈哈,200要归我了。

找到全志的参考原理图调整数据线的线序,你这个线序不对。

不要说我是标题党。只是你回答太晚了。这期间我买了一堆开发板和资料研究,不缺这点钱哈,这些开发板全新我都没退货,有需要二手的可以找我,5折。

至于那个线序到底行不行,才改完,还在嘉立创打样,有待验证,要是成功了在v你200

最近编辑记录 aeo1234 (2024-11-18 15:40:04)

离线

楼主 #19 2024-11-18 15:45:32 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

@Gentlepig

一比一对着接线已知不行,之前这个就是完全对着接的。焊接肯定没问题

离线

#20 2024-11-18 17:00:08 分享评论

- Gentlepig

- 会员

- 注册时间: 2018-10-24

- 已发帖子: 1,409

- 积分: 1373.5

Re: T113-I ddr初始化失败[悬赏200块]

创龙开发板多少钱出?

----------------------------

算啦,才想起来创龙的t113i板没有rgb接口。

最近编辑记录 Gentlepig (2024-11-18 17:03:09)

离线

#21 2024-11-19 16:11:23 分享评论

- suibian

- 会员

- 注册时间: 2023-03-24

- 已发帖子: 21

- 积分: 41

Re: T113-I ddr初始化失败[悬赏200块]

昨天有点忙没上论坛看。首先我是说错了,不是数据线调线,应该是地址线调线。

然后简单解释下调线的原因:

1、为了layout的时候不出现因为交叉而引起过多的打过孔,在设计的时候会故意把线序做调整;

2、地址、数据线调线是DDR的特性;在其他平台比如NXP的IMX系列设计也有同样的设计。

3、全志的DDR驱动是闭源的,所以只能按照全志的参考原理图调线。

最后,关于DDR layout。如果有参考设计,直接1:1把参考设计的走线和层叠复制过来是最管用的,因为这是验证过的。如果自行layout,必须严格做好等长和参考层。如果打板回来出现DDR初始化失败,在排除了电源和时钟的问题之后,可以适当降频尝试。我看到很多大佬自己打板的频率都不是芯片宣称的频率,包括稚辉君。

离线

#22 2024-11-20 21:26:13 分享评论

- anguodeng

- 会员

- 注册时间: 2024-05-24

- 已发帖子: 7

- 积分: 2

Re: T113-I ddr初始化失败[悬赏200块]

我也是买了一堆的开发板,最后用的创龙的核心板自己打的底板,改了一下网络芯片搞了现大半年。

离线

#23 2024-11-21 08:56:48 分享评论

- Gentlepig

- 会员

- 注册时间: 2018-10-24

- 已发帖子: 1,409

- 积分: 1373.5

Re: T113-I ddr初始化失败[悬赏200块]

@Gentlepig

一比一对着接线已知不行,之前这个就是完全对着接的。焊接肯定没问题

那么之前的板,地址线,是一一对应的吗?

后来是如何改的?

还没走过ddr线,好奇。好像看imx6ul官方板地址线也不是一一对应的,这个必须软件上也做对应调整吗?

-----------------------------

下载了imx6ul原理图,地址线是一一对应的,数据线是打乱了的...

0 4 7 3 1 5 6 2 8 9 10 11 12 13 14 15.

最近编辑记录 Gentlepig (2024-11-21 10:02:53)

离线

#24 2024-11-22 15:21:54 分享评论

- vectorspace

- 会员

- 注册时间: 2022-10-27

- 已发帖子: 17

- 积分: 47

Re: T113-I ddr初始化失败[悬赏200块]

我感觉都没有说清楚,这200应该归我,不过楼主认可我的答案准确的话,可以直接把钱捐赠给whycan论坛。

一个图是DDR2的接线,一个是DDR3的接线。楼主的是DDR2的接线图。

不要问我怎么知道的,说起来都是泪

https://bbs.aw-ol.com/topic/4528/t113-i-%E5%8D%95%E7%89%871x16-ddr3-%E7%A1%AC%E4%BB%B6%E8%AE%BE%E8%AE%A1?_=1732260098201&lang=zh-CN

离线

楼主 #25 2024-12-09 20:12:41 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

@suibian

验证完。最近我同时打了三块板验证,一块是直接用买的哪个开发板原理一gerber打样,一个是在之前的pcb改了按照evb改了线序,还有个是在evb的基础再次组内交换字节顺序的数据线,交换了少量地址线(没有交换控制线)。经过验证全部可以启动,线序交换是符合理论预期的。在对比最早的一版,对着接线不行是因为引脚是错的。不过楼下说的内存类型不对是否正确有待考证

离线

楼主 #26 2024-12-09 20:14:38 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

@vectorspace

我验证了确实封装引脚是错的, 但是是否内存类型错误有待考证,没有在任何资料看到过。不过我感觉可能性较大,认可此答案1/2。 发支付码,打钱1/2.

离线

楼主 #27 2024-12-09 20:17:42 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

@suibian

和走线这些其实关系不大,经过我三板验证,以及研究了买的图纸,芯片做了内部等长,组内只需要简易等长岂可,注意时钟线差分,4层都能随便走,目前频率打满非常正常。 不过嘉立创6层甚至比4层还便宜。 上面发的原理图有效, 认可此答案1/2。 发支付码,打钱1/2。

离线

#28 2024-12-11 16:46:08 分享评论

- suibian

- 会员

- 注册时间: 2023-03-24

- 已发帖子: 21

- 积分: 41

Re: T113-I ddr初始化失败[悬赏200块]

@aeo1234

恭喜这位道友验证成功。

从你实测的结果看,调线并不影响此问题的解决。我觉得原因应该是DDR本身就是可以随机读取存储random acess memory,所以调换线序不会影响系统使用。

未能从根源解决你的问题,打钱就不必了。能调通板子是最好的。

离线

#29 2024-12-19 14:54:21 分享评论

- vectorspace

- 会员

- 注册时间: 2022-10-27

- 已发帖子: 17

- 积分: 47

Re: T113-I ddr初始化失败[悬赏200块]

ok!我的这份请楼主直接转打赏给whycan论坛支持论坛建设。

祝楼主身体健康,长命百岁:lol

最近编辑记录 vectorspace (2024-12-19 14:55:19)

离线

楼主 #30 2024-12-20 22:17:05 分享评论

- aeo1234

- 会员

- 注册时间: 2024-10-17

- 已发帖子: 13

- 积分: 24

Re: T113-I ddr初始化失败[悬赏200块]

论坛打给谁,二维码,打钱

离线

#31 2025-01-02 16:01:16 分享评论

- ymh2008

- 会员

- 注册时间: 2025-01-02

- 已发帖子: 11

- 积分: 16

Re: T113-I ddr初始化失败[悬赏200块]

软件里应该可以调整线序,与原理图一致。我们这边eMMC未按demo板挂在PC上,而是挂在了PF,通过调软件解决

离线

#32 2025-08-07 15:49:18 分享评论

- wjh_bh

- 会员

- 注册时间: 2025-05-16

- 已发帖子: 2

- 积分: 12

Re: T113-I ddr初始化失败[悬赏200块]

遇到一个问题,想请教下,如果DDR3芯片是128M16 或256M16这种位宽的(如楼主说的NT5CC256M16ER和F60C1A0004这两款芯片),只有14或15根地址线,就是DDR3这边没有A14或A15,而T113-i主控这边又用到了这两根线,应该怎样处理呢?

离线

#33 2025-11-20 13:29:48 分享评论

- a06041114

- 会员

- 注册时间: 2021-01-18

- 已发帖子: 23

- 积分: 18

Re: T113-I ddr初始化失败[悬赏200块]

最后正确的DDR3接线是什么?是按照原厂的EVB接线就可以吗

离线

#34 2025-11-20 18:03:29 分享评论

- geekchun

- 会员

- 注册时间: 2020-11-11

- 已发帖子: 80

- 积分: 110

Re: T113-I ddr初始化失败[悬赏200块]

我看下来的理解应该是的,接DDR2和DDR3时,SOC这边引脚分配有所不同,所以要按EVB画。

不知道对不对

离线

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发