楼主 #1 2021-02-15 22:13:38 分享评论

- SigmaStarStudy

- 会员

- 注册时间: 2021-02-15

- 已发帖子: 34

- 积分: 34

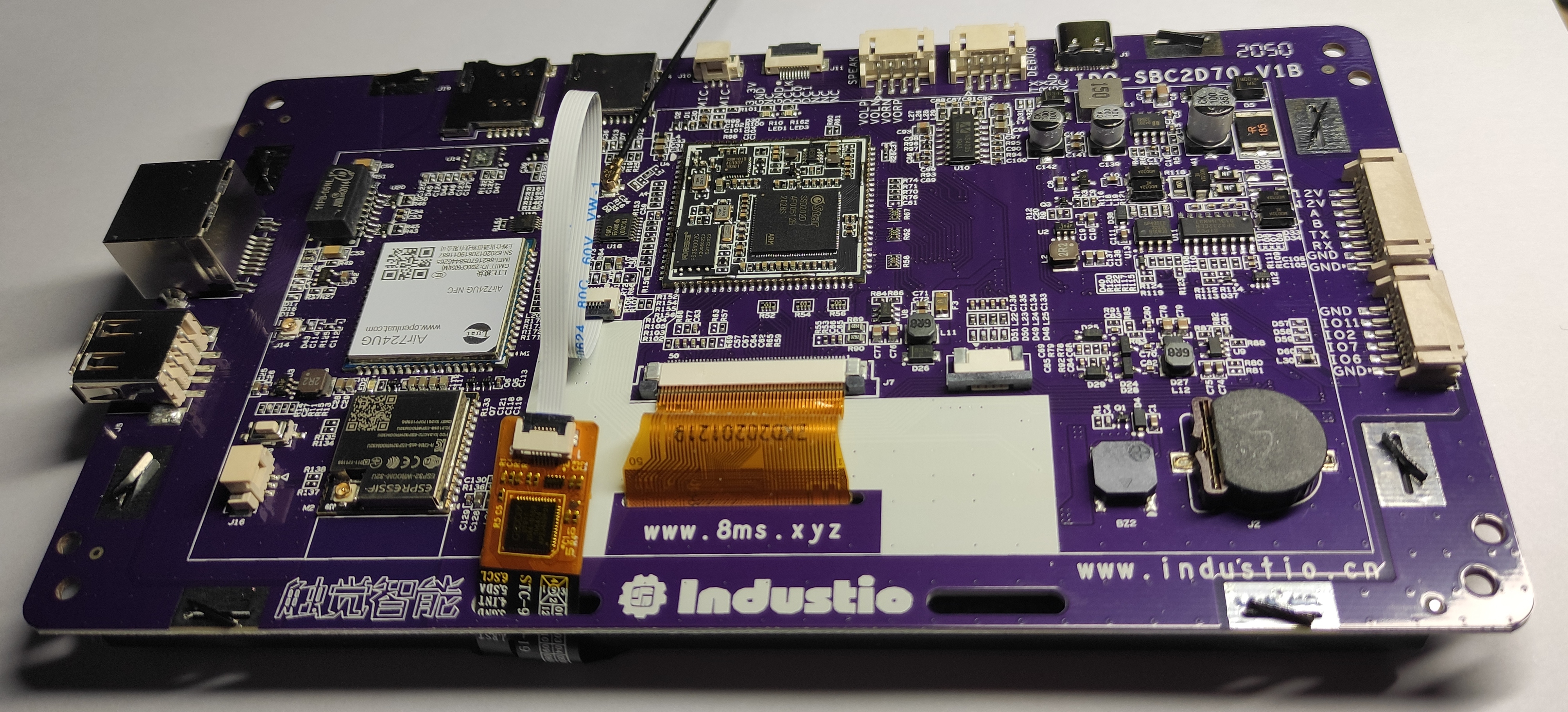

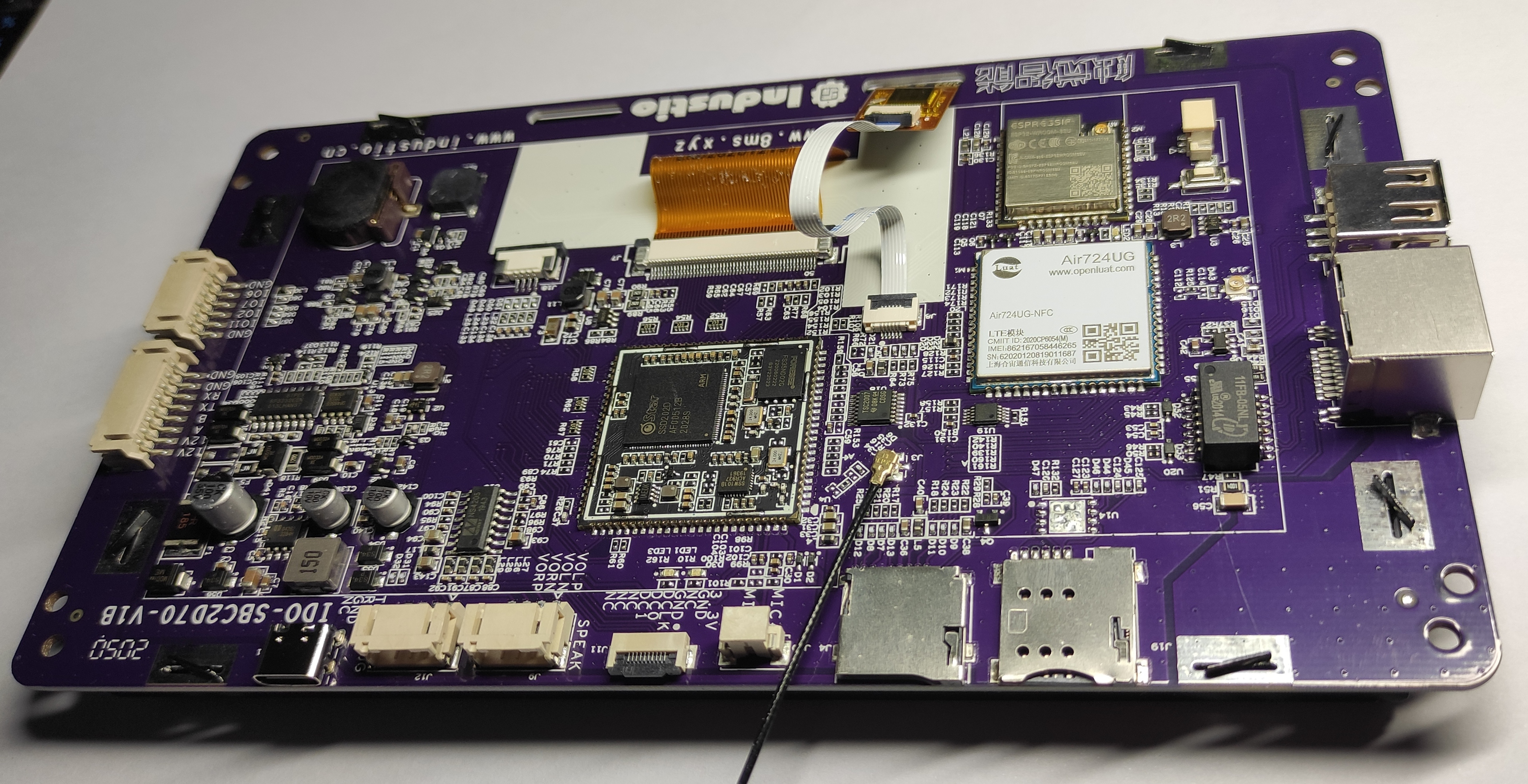

启明云端的7寸 1024*600 LCD SSD202 开发板从入门到放弃

购买链接: https://item.taobao.com/item.htm?id=631665290641

mma使用参考.pdf

Memory Layout介绍.pdf

Wi-Fi功能启用说明.pdf

纯净版linux配置SOP.pdf

BOOT LOGO以及显示参数使用参考.pdf

SSD201 DDR&FLASH使用评估介绍.pdf

Read Chip Uuid SOP.pdf

busybox裁剪参考.pdf

display/点屏列表.xlsx

display/展频计算.xlsx

display/点屏参考.pdf

display/panel开发参考.pdf

display/SSC/ssc_ttl_mipidsi_hdmitx.xlsx

display/SSD20X换屏参SOP.pdf

display/PQ/SStar PQ tool SOP.pdf

display/PQ/pq.ini

display/PQ/SStar_PQtool/SStar_PQtool.INI

display/PQ/SStar_PQtool/ReadDump.txt

display/PQ/SStar_PQtool.zip

audio/顺芯codec调试流程.pdf

audio/Sstar音频调试指导手册.pdf

audio/Audio_tunning_guide_1.1.pdf

audio/智能语音拾音模块设计要求.pdf

audio/SSD201_Demo板音频使用说明.pdf

快速启动开发参考文档.pdf

MI软件架构图.pdf

Verify_Sample说明.pdf

SSD201 HW Checklist V6.xlsx

SSD20X软件打开HDMI SOP.pdf

SSD20X功耗调整指引.pdf

Ota打包和升级.pdf

添加触摸屏参考.pdf

SDK makefile架构 & rootfs制作流程.pdf

Zram开发参考.pdf

env分区掉电保护机制.pdf

perf/perf_bin.rar

perf/perf使用参考.pdf

分区介绍文档 .pdf

MultiPlayer/FFMPEG常用命令介绍.pdf

MultiPlayer/FFMPEG播放器媒体规格.pdf

flashlist/flash_list.xlsx

fuart & uart流控使用参考.pdf

应用程序死机debug/arm-linux-gnu-gdb.rar

应用程序死机debug/应用程序死机debug参考.pdf

网络/SSD20X WIFI AP桥接模式使用方法.pdf

网络/iperf使用参考.pdf

网络/WiFi编译使用指南.pdf

网络/wifi ap & sta同时开启使用参考.pdf

网络/SSD20X 打开DNS & DHCP说明.pdf

网络/SSD20X双网口转发数据测试方法.pdf

网络/wifi sta & ap桥接上网使用参考.pdf

EMMC配置说明.pdf

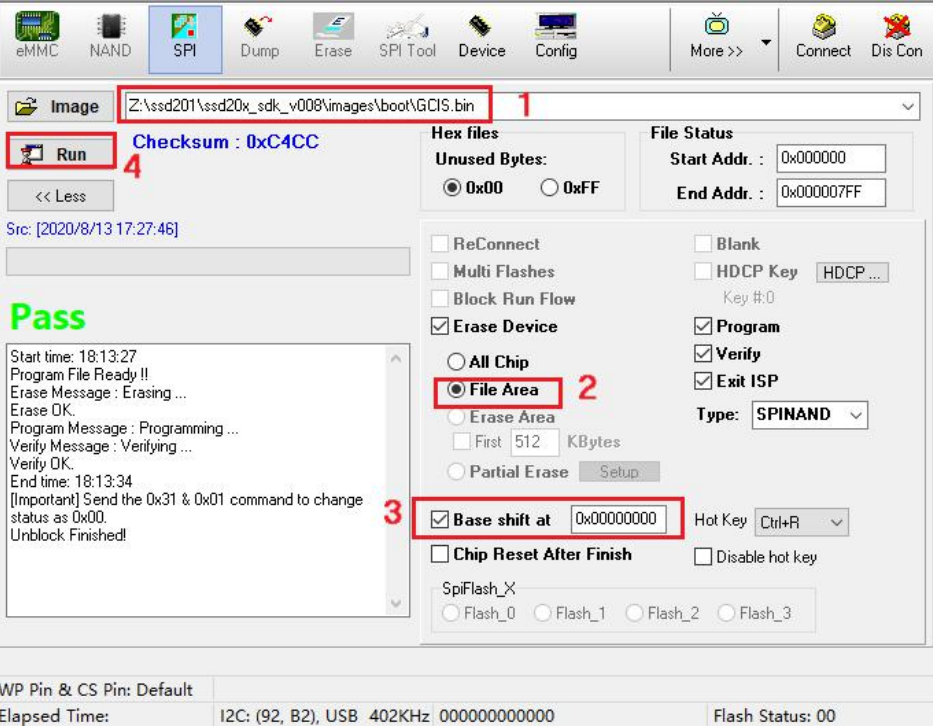

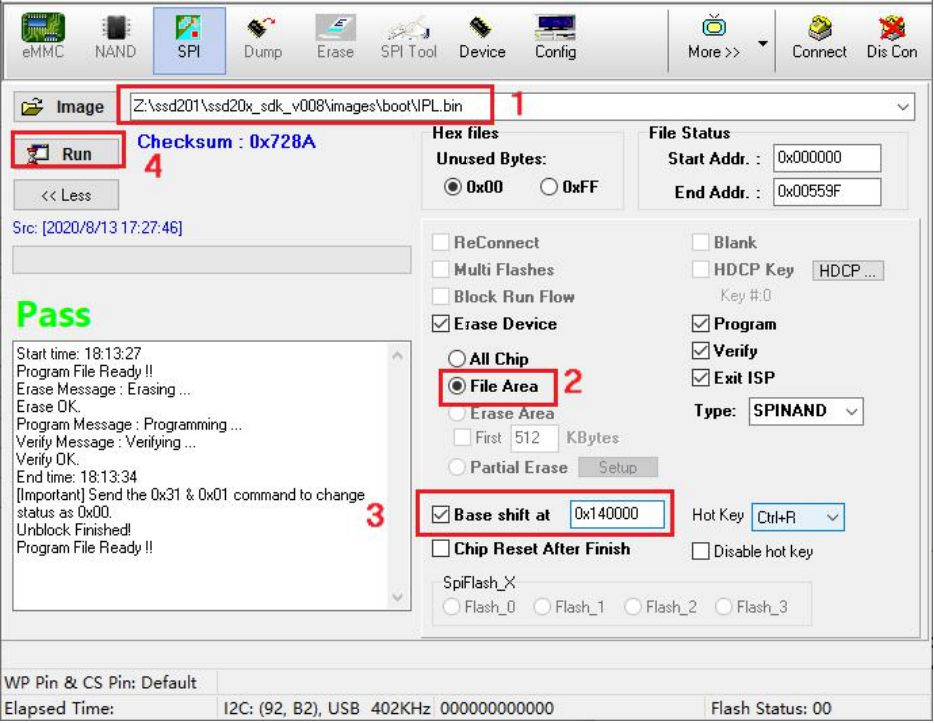

spinand母片制作/Spinand母片制作.pdf

spinand母片制作/flash_list.xlsx

spinand母片制作/SPI NOR母片制作.pdf

Ko & so裁剪.pdf

GUI/framebuf/framebuf开发参考.pdf

GUI/minigui/minigui1.3.1编程指南.pdf

GUI/minigui/MINIGUI-USER-MANUAL-V3.0-5C.pdf

GUI/minigui/第21章-MiniGUI图形界面设计.ppt

GUI/minigui/MiniGUI特性说明书(精).pdf

GUI/minigui/MiniGui 开发包指引.pdf

fastboot客户开发使用参考.pdf

hw/GPIO 使用参考.pdf

hw/PWM 使用参考.pdf

hw/WATCHDOG 使用参考.pdf

hw/SPI 使用参考.pdf

hw/SAR使用参考.pdf

hw/RTC 使用参考.pdf

hw/UART使用参考.pdf

hw/I2C 使用参考.pdf

hw/Timer 使用参考.pdf

USB Upgrade SOP.pdf

Default_env设置机制.pdf

API/MI_WLAN_API.pdf

API/MI_VDEC_API.pdf

API/MI_HDMI_API.pdf

API/MI_VENC_API.pdf

API/MI_FB_API.pdf

API/MI_PANEL_API.pdf

API/MI_DISP_API.pdf

API/MI_AO_API.pdf

API/MI_SYS_API.pdf

API/MI_GFX_API.pdf

API/MI_AI_API.pdf

API/MI_VDISP_API.pdf

API/MI_DIVP_API.pdf

MI_调试手册.pdf

SpiNor母片制作/SpiNor母片制作.pdf

SpiNor母片制作/make_nor_bin.txt

4G/移远EC200T 4G模组使用参考.pdf

wifi sta & ap桥接上网使用参考.pdf

双网口配置使用说明.pdf

出厂固件开机日志:

IPL g5da0ceb

D-1e

HW Reset

miupll_233MHz

MIU0 zq=0x003c

miu_bw_set

utmi_1_init done

utmi_2_init done

utmi_3_init done

usbpll init done......

cpupll init done

SPI 54M

clk_init done

P1 USB_rterm trim=0x0000

P1 USB_HS_TX_CURRENT trim=0x0001

P2 USB_rterm trim=0x0000

P2 USB_HS_TX_CURRENT trim=0x0001

P3 USB_rterm trim=0x0000

P3 USB_HS_TX_CURRENT trim=0x0001

PM_vol_bgap trim=0x0005

GCR_SAR_DATA trim=0x018f

ETH 10T output swing trim=0x0000

ETH 100T output swing trim=0x0010

ETH RX input impedance trim=0x0000

ETH TX output impedance trim=0x0001

MIPI_HS_RTERM trim=0x0001

MIPI_LP_RTERM trim=0x0000

128MB

BIST0_0001-OK

Enable MMU and CACHE

Load IPL_CUST from SPINAND

QUAD MODE ENABLE

Checksum OK

IPL_CUST g5da0ceb

runUBOOT()

runUBOOT()

[SPINAND]

SPI 54M

Load UBOOT from SPINAND

-Verify UBOOT CRC32 passed!

-Decompress UBOOT XZ

decomp_size=0x000a12a4

Disable MMU and D-cache before jump to UBOOT▒

U-Boot 2015.01 (Dec 14 2020 - 17:22:37)

Version: I2g#######

Watchdog enabled

I2C: ready

DRAM:

WARNING: Caches not enabled

SPINAND: _MDrv_SPINAND_GET_INFO: Found SPINAND INFO

(0xCD) (0xEB) (0x11)

SPINAND: board_nand_init: CIS contains part info

256 MiB

MMC: MStar SD/MMC: 0

In: serial

Out: serial

Err: serial

Net: MAC Address 00:30:1B:BA:02:DB

Auto-Negotiation...

Link Status Speed:10 Full-duplex:0

Status Error!

sstar_emac

bootcheck start

fore uup u8KeyPad_KeyVal [0xffff]

BootMode 0

Saving Environment to NAND...

Erasing NAND...

Erasing at 0x440000 -- 100% complete.

Writing to NAND... OK

NAND read: device 0 offset 0x4c0000, size 0x60000

Time:39991 us, speed:9832 KB/s

393216 bytes read: OK

gpio debug MHal_GPIO_Pad_Set: pin=8

gpio[8] is 1

NAND read: device 0 offset 0x520000, size 0x500000

Time:521749 us, speed:10048 KB/s

5242880 bytes read: OK

gpio debug MHal_GPIO_Pad_Set: pin=8

gpio[8] is 1

## Booting kernel from Legacy Image at 22000000 ...

Image Name: MVX4##I2M#g#######KL_LX409##[BR:

Image Type: ARM Linux Kernel Image (lzma compressed)

Data Size: 2437200 Bytes = 2.3 MiB

Load Address: 20008000

Entry Point: 20008000

Verifying Checksum ... OK

-usb_stop(USB_PORT0)

-usb_stop(USB_PORT1)

-usb_stop(USB_PORT2)

Uncompressing Kernel Image ...

[XZ] !!!reserved 0x21000000 length=0x 1000000 for xz!!

XZ: uncompressed size=0x4da000, ret=7

OK

atags:0x20000000

Starting kernel ...

Booting Linux on physical CPU 0x0

Linux version 4.9.84 (ronnie@wt_rd_server) (gcc version 8.2.1 20180802 (GNU Toolchain for the A-profile Architecture 8.2-2018-08 (arm-rel-8.23)) ) #61 SMP PREEMPT Mon Dec 14 17:22:44 CST 2020

CPU: ARMv7 Processor [410fc075] revision 5 (ARMv7), cr=50c5387d

CPU: div instructions available: patching division code

CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cache

early_atags_to_fdt() success

OF: fdt:Machine model: INFINITY2M SSC011A-S01A-S

LXmem is 0x7f00000 PHYS_OFFSET is 0x20000000

Add mem start 0x20000000 size 0x7f00000!!!!

LX_MEM = 0x20000000, 0x7f00000

LX_MEM2 = 0x0, 0x0

LX_MEM3 = 0x0, 0x0

EMAC_LEN= 0x0

DRAM_LEN= 0x0

deal_with_reserved_mmap memblock_reserve success mmap_reserved_config[0].reserved_start=

0x27c00000

deal_with_reserve_mma_heap memblock_reserve success mma_config[0].reserved_start=

0x26c00000

cma: Reserved 2 MiB at 0x26a00000

Memory policy: Data cache writealloc

percpu: Embedded 14 pages/cpu @c68bc000 s25112 r8192 d24040 u57344

Built 1 zonelists in Zone order, mobility grouping on. Total pages: 28162

Kernel command line: console=ttyS0,115200 ubi.mtd=UBI,2048 root=ubi:rootfs rw rootfstype=ubifs init=/linuxrc rootwait=1 LX_MEM=0x7f00000 mma_heap=mma_heap_name0,miu=0,sz=0x1000000 mma_memblock_remove=1 highres=off mmap_reserved=fb,miu=0,sz=0x300000,max_start_off=0x7C00000,max_end_off=0x7F00000 mtdparts=nand0:384k@1280k(IPL0),384k(IPL1),384k(IPL_CUST0),384k(IPL_CUST1),768k(UBOOT0),768k(UBOOT1),384k(ENV0),0x20000(KEY_CUST),0x60000(LOGO),0x500000(KERNEL),0x500000(RECOVERY),-(UBI)

PID hash table entries: 512 (order: -1, 2048 bytes)

Dentry cache hash table entries: 16384 (order: 4, 65536 bytes)

Inode-cache hash table entries: 8192 (order: 3, 32768 bytes)

Memory: 102132K/113664K available (2894K kernel code, 249K rwdata, 1488K rodata, 172K init, 171K bss, 9484K reserved, 2048K cma-reserved)

Virtual kernel memory layout:

vector : 0xffff0000 - 0xffff1000 ( 4 kB)

fixmap : 0xffc00000 - 0xfff00000 (3072 kB)

vmalloc : 0xc8000000 - 0xff800000 ( 888 MB)

lowmem : 0xc0000000 - 0xc7f00000 ( 127 MB)

modules : 0xbf800000 - 0xc0000000 ( 8 MB)

.text : 0xc0008000 - 0xc02dba90 (2895 kB)

.init : 0xc0477000 - 0xc04a2000 ( 172 kB)

.data : 0xc04a2000 - 0xc04e05e8 ( 250 kB)

.bss : 0xc04e2000 - 0xc050cc98 ( 172 kB)

SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=2, Nodes=1

Preemptible hierarchical RCU implementation.

Build-time adjustment of leaf fanout to 32.

RCU restricting CPUs from NR_CPUS=4 to nr_cpu_ids=2.

RCU: Adjusting geometry for rcu_fanout_leaf=32, nr_cpu_ids=2

NR_IRQS:16 nr_irqs:16 16

ms_init_main_intc: np->name=ms_main_intc, parent=gic

ms_init_pm_intc: np->name=ms_pm_intc, parent=ms_main_intc

ss_init_gpi_intc: np->name=ms_gpi_intc, parent=ms_main_intc

Find CLK_cpupll_clk, hook ms_cpuclk_ops

arm_arch_timer: Architected cp15 timer(s) running at 6.00MHz (virt).

clocksource: arch_sys_counter: mask: 0xffffffffffffff max_cycles: 0x1623fa770, max_idle_ns: 440795202238 ns

sched_clock: 56 bits at 6MHz, resolution 166ns, wraps every 4398046511055ns

Switching to timer-based delay loop, resolution 166ns

Console: colour dummy device 80x30

console [ttyS0] enabled

Calibrating delay loop (skipped), value calculated using timer frequency.. 12.00 BogoMIPS (lpj=60000)

pid_max: default: 4096 minimum: 301

Mount-cache hash table entries: 1024 (order: 0, 4096 bytes)

Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes)

CPU: Testing write buffer coherency: ok

CPU0: update cpu_capacity 1024

CPU0: thread -1, cpu 0, socket 0, mpidr 80000000

Setting up static identity map for 0x20008240 - 0x20008270

CPU1: update cpu_capacity 1024

CPU1: thread -1, cpu 1, socket 0, mpidr 80000001

Brought up 2 CPUs

SMP: Total of 2 processors activated (24.00 BogoMIPS).

CPU: All CPU(s) started in SVC mode.

devtmpfs: initialized

VFP support v0.3: implementor 41 architecture 2 part 30 variant 7 rev 5

clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604462750000 ns

futex hash table entries: 16 (order: -2, 1024 bytes)

NET: Registered protocol family 16

DMA: preallocated 256 KiB pool for atomic coherent allocations

Version : MVX4##I2M#g#######KL_LX409##[BR:g]#XVM

GPIO: probe end[ss_gpi_intc_domain_alloc] hw:42 -> v:43

[MS_PM_INTC] hw:20 -> v:51

[Padmux]reset Pad_87(reg 0x101e09; mask0x7) to DMIC_MODE_2(org: I2C0_MODE_1)

hw-breakpoint: found 5 (+1 reserved) breakpoint and 4 watchpoint registers.

hw-breakpoint: maximum watchpoint size is 8 bytes.

SCSI subsystem initialized

usbcore: registered new interface driver usbfs

usbcore: registered new interface driver hub

usbcore: registered new device driver usb

Linux video capture interface: v2.00

clocksource: Switched to clocksource arch_sys_counter

NET: Registered protocol family 2

TCP established hash table entries: 1024 (order: 0, 4096 bytes)

TCP bind hash table entries: 1024 (order: 2, 20480 bytes)

TCP: Hash tables configured (established 1024 bind 1024)

UDP hash table entries: 128 (order: 0, 6144 bytes)

UDP-Lite hash table entries: 128 (order: 0, 6144 bytes)

NET: Registered protocol family 1

hw perfevents: enabled with armv7_cortex_a7 PMU driver, 5 counters available

workingset: timestamp_bits=30 max_order=15 bucket_order=0

squashfs: version 4.0 (2009/01/31) Phillip Lougher

jffs2: version 2.2. © 2001-2006 Red Hat, Inc.

io scheduler noop registered

io scheduler deadline registered (default)

cust-io-ctrl soc:ido_io_ctrl: Device tree not define of gpio-bz0

[Padmux]reset Pad_47(reg 0x101e03; mask0x70) to GPIO(org: UART0_MODE_1)

cust-io-ctrl soc:ido_io_ctrl: Device tree not define of gpio-usb-en

sd_pwr init ok

cust-io-ctrl soc:ido_io_ctrl: Device tree not define of gpio-rs485-ctrl

cust-io-ctrl soc:ido_io_ctrl: Device tree not define of gpio-y1

cust-io-ctrl soc:ido_io_ctrl: Device tree not define of gpio-y2

cust-io-ctrl soc:ido_io_ctrl: Device tree not define of gpio-zero

cust-io-ctrl soc:ido_io_ctrl: Device tree not define of gpio-wifi-reset

cust_io_ctrl complete!

libphy: Fixed MDIO Bus: probed

CAN device driver interface

PPP generic driver version 2.4.2

PPP BSD Compression module registered

PPP Deflate Compression module registered

PPP MPPE Compression module registered

NET: Registered protocol family 24

usbcore: registered new interface driver usb-storage

usbcore: registered new interface driver usbserial

usbcore: registered new interface driver usbserial_generic

usbserial: USB Serial support registered for generic

usbcore: registered new interface driver option

usbserial: USB Serial support registered for GSM modem (1-port)

mousedev: PS/2 mouse device common for all mice

[ss_gpi_intc_domain_alloc] hw:58 -> v:58

i2c /dev entries driver

usbcore: registered new interface driver uvcvideo

USB Video Class driver (1.1.1)

ledtrig-cpu: registered to indicate activity on CPUs

usbcore: registered new interface driver usbhid

usbhid: USB HID core driver

1f221000.uart0: ttyS0 at MMIO 0x0 (irq = 30, base_baud = 10800000) is a unknown

1f221200.uart1: ttyS1 at MMIO 0x0 (irq = 31, base_baud = 10800000) is a unknown

1f220400.uart2: ttyS2 at MMIO 0x0 (irq = 32, base_baud = 10800000) is a unknown

1f221400.uart2: ttyS3 at MMIO 0x0 (irq = 33, base_baud = 10800000) is a unknown

[Core Voltage] check_voltage_valid: Not support 0mV, use 900mV

>> [sdmmc] ms_sdmmc_probe

[Padmux]reset Pad_51(reg 0x101e08; mask0x300) to GPIO(org: SDIO_MODE_1)

>> [sdmmc_0] Probe Platform Devices

MSYS: DMEM request: [emac0_buff]:0x00000812

MSYS: DMEM request: [emac0_buff]:0x00000812 success, CPU phy:@0x26A43000, virt:@0xC6A43000

libphy: mdio: probed

mdio_bus mdio-bus@emac0: /soc/emac0/mdio-bus@emac0/ethernet-phy@0 has invalid PHY address

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 0

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 1

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 2

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 3

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 4

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 5

Goodix-TS 1-005d: ID 911, version: 1060

Goodix-TS 1-005d: Direct firmware load for goodix_911_cfg.bin failed with error -2

input: Goodix Capacitive TouchScreen as /devices/soc0/soc/1f223200.i2c1/i2c-1/1-005d/input/input0

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 6

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 7

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 8

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 9

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 10

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 11

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 12

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 13

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 14

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 15

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 16

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 17

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 18

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 19

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 20

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 21

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 22

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 23

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 24

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 25

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 26

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 27

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 28

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 29

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 30

mdio_bus mdio-bus@emac0: scan phy ethernet-phy at address 31

[emac_phy_connect][3204] connected mac emac0 to PHY at mdio-bus@emac0:00 [uid=11112222, driver=SStar 10/100 Ethernet Phy]

MSYS: DMEM request: [emac1_buff]:0x00060812

MSYS: DMEM request: [emac1_buff]:0x00060812 success, CPU phy:@0x26A50000, virt:@0xC6A50000

libphy: mdio: probed

mdio_bus mdio-bus@emac1: /soc/emac1/mdio-bus@emac1/ethernet-phy@1 has invalid PHY address

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 0

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 1

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 2

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 3

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 4

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 5

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 6

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 7

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 8

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 9

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 10

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 11

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 12

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 13

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 14

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 15

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 16

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 17

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 18

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 19

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 20

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 21

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 22

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 23

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 24

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 25

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 26

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 27

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 28

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 29

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 30

mdio_bus mdio-bus@emac1: scan phy ethernet-phy at address 31

[emac_phy_connect][3204] connected mac emac1 to PHY at mdio-bus@emac1:00 [uid=00000000, driver=Generic PHY]

ms_rtcpwc 1f006800.rtcpwc: rtc core: registered 1f006800.rtcpwc as rtc0

[ms_cpufreq_init] Current clk=1005326304

mstar_spinand_probe: mstar_spinand enableClock

MSYS: DMEM request: [BDMA]:0x00000840

MSYS: DMEM request: [BDMA]:0x00000840 success, CPU phy:@0x26A44000, virt:@0xC6A44000

MDrv_SPINAND_Init: Detected ID: MID =cd, DID =eb

_dumpNandInformation:warning, Bytes / Page : 2048

_dumpNandInformation:warning, Pages / Block: 64

_dumpNandInformation:warning, Sector/ Page : 512

_dumpNandInformation:warning, Spare / Page : 64

_dumpNandInformation:warning, Current config r:4 w:4 drv:1

mstar_spinand_probe: Magic memcmp pass

mstar_spinand_probe: Get partition (Block 0 : page 1)

mstar_spinand_probe: CIS contains part info

mstar_spinand_probe: Before nand_scan()...

12 cmdlinepart partitions found on MTD device nand0

mstar_spinand_probe: Mtd parts parse

Creating 12 MTD partitions on "nand0":

0x000000140000-0x0000001a0000 : "IPL0"

0x0000001a0000-0x000000200000 : "IPL1"

0x000000200000-0x000000260000 : "IPL_CUST0"

0x000000260000-0x0000002c0000 : "IPL_CUST1"

0x0000002c0000-0x000000380000 : "UBOOT0"

0x000000380000-0x000000440000 : "UBOOT1"

0x000000440000-0x0000004a0000 : "ENV0"

0x0000004a0000-0x0000004c0000 : "KEY_CUST"

0x0000004c0000-0x000000520000 : "LOGO"

0x000000520000-0x000000a20000 : "KERNEL"

0x000000a20000-0x000000f20000 : "RECOVERY"

0x000000f20000-0x000010000000 : "UBI"

NET: Registered protocol family 17

can: controller area network core (rev 20120528 abi 9)

NET: Registered protocol family 29

can: raw protocol (rev 20120528)

can: broadcast manager protocol (rev 20161123 t)

can: netlink gateway (rev 20130117) max_hops=1

ThumbEE CPU extension supported.

Registering SWP/SWPB emulation handler

ubi0: attaching mtd11

ubi0: scanning is finished

ubi0: attached mtd11 (name "UBI", size 240 MiB)

ubi0: PEB size: 131072 bytes (128 KiB), LEB size: 126976 bytes

ubi0: min./max. I/O unit sizes: 2048/2048, sub-page size 2048

ubi0: VID header offset: 2048 (aligned 2048), data offset: 4096

ubi0: good PEBs: 1927, bad PEBs: 0, corrupted PEBs: 0

ubi0: user volume: 4, internal volumes: 1, max. volumes count: 128

ubi0: max/mean erase counter: 2/1, WL threshold: 4096, image sequence number: 0

ubi0: available PEBs: 23, total reserved PEBs: 1904, PEBs reserved for bad PEB handling: 40

ubi0: background thread "ubi_bgt0d" started, PID 684

Please set rtc timer (hwclock -w)

ms_rtcpwc 1f006800.rtcpwc: setting system clock to 1970-01-01 00:00:01 UTC (1)

OF: fdt:not creating '/sys/firmware/fdt': CRC check failed

UBIFS (ubi0:0): background thread "ubifs_bgt0_0" started, PID 687

UBIFS (ubi0:0): recovery needed

UBIFS (ubi0:0): recovery completed

UBIFS (ubi0:0): UBIFS: mounted UBI device 0, volume 0, name "rootfs"

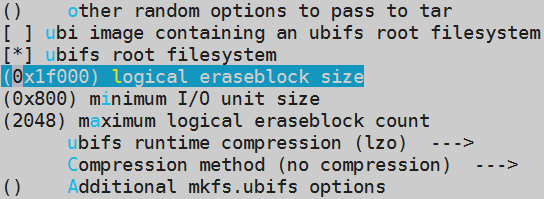

UBIFS (ubi0:0): LEB size: 126976 bytes (124 KiB), min./max. I/O unit sizes: 2048 bytes/2048 bytes

UBIFS (ubi0:0): FS size: 205320192 bytes (195 MiB, 1617 LEBs), journal size 9023488 bytes (8 MiB, 72 LEBs)

UBIFS (ubi0:0): reserved for root: 0 bytes (0 KiB)

UBIFS (ubi0:0): media format: w4/r0 (latest is w4/r0), UUID BB60053E-265F-489A-BBA2-E23FCCB53856, small LPT model

VFS: Mounted root (ubifs filesystem) on device 0:13.

devtmpfs: mounted

This architecture does not have kernel memory protection.

mount: can't find devpts in /etc/fstab

mount: mounting none on /sys failed: Device or resource busy

mount: mounting none on /sys/kernel/debug/ failed: Device or resource busy

UBIFS (ubi0:1): background thread "ubifs_bgt0_1" started, PID 708

UBIFS (ubi0:1): recovery needed

UBIFS (ubi0:1): recovery completed

UBIFS (ubi0:1): UBIFS: mounted UBI device 0, volume 1, name "miservice"

UBIFS (ubi0:1): LEB size: 126976 bytes (124 KiB), min./max. I/O unit sizes: 2048 bytes/2048 bytes

UBIFS (ubi0:1): FS size: 9269248 bytes (8 MiB, 73 LEBs), journal size 1650688 bytes (1 MiB, 13 LEBs)

UBIFS (ubi0:1): reserved for root: 0 bytes (0 KiB)

UBIFS (ubi0:1): media format: w4/r0 (latest is w4/r0), UUID 31366479-B49E-485F-80FE-DFCB66B51986, small LPT model

UBIFS (ubi0:2): background thread "ubifs_bgt0_2" started, PID 711

UBIFS (ubi0:2): recovery needed

UBIFS (ubi0:2): recovery completed

UBIFS (ubi0:2): UBIFS: mounted UBI device 0, volume 2, name "customer"

UBIFS (ubi0:2): LEB size: 126976 bytes (124 KiB), min./max. I/O unit sizes: 2048 bytes/2048 bytes

UBIFS (ubi0:2): FS size: 4063232 bytes (3 MiB, 32 LEBs), journal size 1142785 bytes (1 MiB, 8 LEBs)

UBIFS (ubi0:2): reserved for root: 0 bytes (0 KiB)

UBIFS (ubi0:2): media format: w4/r0 (latest is w4/r0), UUID 0BABC81B-8AEC-4DA9-BE30-EC9F477955A0, small LPT model

UBIFS (ubi0:3): background thread "ubifs_bgt0_3" started, PID 714

UBIFS (ubi0:3): recovery needed

UBIFS (ubi0:3): recovery completed

UBIFS (ubi0:3): UBIFS: mounted UBI device 0, volume 3, name "appconfigs"

UBIFS (ubi0:3): LEB size: 126976 bytes (124 KiB), min./max. I/O unit sizes: 2048 bytes/2048 bytes

UBIFS (ubi0:3): FS size: 4063232 bytes (3 MiB, 32 LEBs), journal size 1142785 bytes (1 MiB, 8 LEBs)

UBIFS (ubi0:3): reserved for root: 0 bytes (0 KiB)

UBIFS (ubi0:3): media format: w4/r0 (latest is w4/r0), UUID 962D6689-38D7-4433-B862-005B5E537CBD, small LPT model

[1]+ Done busybox telnetd

RPC: Registered named UNIX socket transport module.

RPC: Registered udp transport module.

RPC: Registered tcp transport module.

RPC: Registered tcp NFSv4.1 backchannel transport module.

ntfs: driver 2.1.32 [Flags: R/O MODULE].

insmod: can't read '/config/modules/4.9.84/usb-common.ko': No such file or directory

insmod: can't read '/config/modules/4.9.84/usbcore.ko': Noehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver

such file or diehci monitor start running

Mstar_ehc_init version:20180309

rectory

Sstar-ehci-2 H.W init

Titania3_series_start_ehc start

[USB] config miu select [70] [e8] [ef] [ef]

[USB] enable miu lower bound address subtraction

[USB] init squelch level 0x2

[USB] no platform_data, device tree coming

[USB][EHC] dma coherent_mask 0xffffffffffffffff mask 0xffffffffffffffff

BC disable

[USB] soc:Sstar-ehci-2 irq --> 38

Sstar-ehci-2 soc:Sstar-ehci-2: EHCI Host Controller

Sstar-ehci-2 soc:Sstar-ehci-2: new USB bus registered, assigned bus number 1

Sstar-ehci-2 soc:Sstar-ehci-2: irq 38, io mem 0xfd285000

usb usb1: New USB device found, idVendor=1d6b, idProduct=0002

usb usb1: New USB device strings: Mfr=3, Product=2, SerialNumber=1

usb usb1: Product: EHCI Host Controller

usb usb1: Manufacturer: Linux 4.9.84 ehci_hcd

usb usb1: SerialNumber: mstar

hub 1-0:1.0: USB hub found

hub 1-0:1.0: 1 port detected

Sstar-ehci-1 H.W init

Titania3_series_start_ehc start

[USB] config miu select [70] [e8] [ef] [ef]

[USB] enable miu lower bound address subtraction

[USB] init squelch level 0x2

[USB] no platform_data, device tree coming

[USB][EHC] dma coherent_mask 0xffffffffffffffff mask 0xffffffffffffffff

BC disable

[USB] soc:Sstar-ehci-1 irq --> 37

Sstar-ehci-1 soc:Sstar-ehci-1: EHCI Host Controller

Sstar-ehci-1 soc:Sstar-ehci-1: new USB bus registered, assigned bus number 2

Sstar-ehci-1 soc:Sstar-ehci-1: irq 37, io mem 0xfd284800

usb usb2: New USB device found, idVendor=1d6b, idProduct=0002

usb usb2: New USB device strings: Mfr=3, Product=2, SerialNumber=1

usb usb2: Product: EHCI Host Controller

usb usb2: Manufacturer: Linux 4.9.84 ehci_hcd

usb usb2: SerialNumber: mstar

hub 2-0:1.0: USB hub found

hub 2-0:1.0: 1 port detected

insmod: can't read '/config/modules/4.9.84/usb-storage.ko': No such file or directory

insmod: can't read '/confMSYS: DMEM request: [AESDMA_ENG]:0x00001000

ig/modules/4.9.8MSYS: DMEM request: [AESDMA_ENG]:0x00001000 success, CPU phy:@0x26A4B000, virt:@0xC6A4B000

4/usbhid.ko': NoMSYS: DMEM request: [AESDMA_ENG1]:0x00001000

such file or diMSYS: DMEM request: [AESDMA_ENG1]:0x00001000 success, CPU phy:@0x26A4C000, virt:@0xC6A4C000

rectory

mhal: loading out-of-tree module taints kernel.

mhal: module license 'PROPRIETARY' taints kernel.

Disabling lock debugging due to kernel taint

==20180309==> hub_port_init 1 #0

Plug in USB Port2

mhal driver init

jpe driver probed

DivpProcInit 515

module [sys] init

MI_SYSCFG_SetupMmapLoader default_config_path:/config/config_tool, argv1:/config/load_mmap,argv2:/config/mmap.ini

==20180309==> hub_port_init 1 #0

Plug in USB Port1

Function = init_glob_miu_kranges, Line = 604, Insert KProtect for LX @ MIU: 0

Function = init_glob_miu_kranges, Line = 613, [INIT] for LX0 kprotect: from 0x20000000 to 0x27F00000, using block 0

config...... strPath:/config/config_tool, argv0:/config/load_config

function:parese_Cmdline,pCmd_Section:0x7f00000

mm

a_

he

ap

_n

am

e0

miu=0,sz=1000000 reserved_start=26c00000

r_front->miuBlockIndex:0,r_front->start_cpu_bus_pa:0x20000000,r_front->start_cpu_bus_pa+r_front->length:0x26c00000

r_back->miuBlockIndex:1,r_back->start_cpu_bus_pa:0x27c00000,r_back->start_cpu_bus_pa+r_back->length:0x27f00000

mi_sys_mma_allocator_create success, heap_base_addr=26c00000 length=1000000

Kernel CONFIG_HZ = 100

Sigmastar Module version: project_commit.866b490 sdk_commit.341badc build_time.20200714212826

usb 1-1: new high-speed USB device number 2 using Sstar-ehci-2

module [gfx] init

module [divp] init

module [vdec] init

module [ao] init

module [disp] init

usb 2-1: new high-speed USB device number 2 using Sstar-ehci-1

drv_ccif_cpu_init :c8580000

request_irq failed

module [ai] init

module [venc] init Jul 14 2020 21:29:05

module [panel] init

[GOP]HalGopUpdateGwinParam 720: GOP_id=011 not support

[GOP]HalGopSetArgb1555Alpha 1208: GOPId=0x11 not support

[GOP]HalGopSetArgb1555Alpha 1208: GOPId=0x11 not support

usb 1-1: New USB device found, idVendor=1782, idProduct=4e00

usb 1-1: New USB device strings: Mfr=1, Product=2, SerialNumber=0

usb 1-1: Product: UNISOC-8910

usb 1-1: Manufacturer: UNISOC

option 1-1:1.2: GSM modem (1-port) converter detected

usb 1-1: GSM modem (1-port) converter now attached to ttyUSB0

option 1-1:1.3: GSM modem (1-port) converter detected

usb 1-1: GSM modem (1-port) converter now attached to ttyUSB1

option 1-1:1.4: GSM modem (1-port) converter detected

/ # usb 1-1: GSM modem (1-port) converter now attached to ttyUSB2

usb 2-1: New USB device found, idVendor=1b20, idProduct=8888

usb 2-1: New USB device strings: Mfr=16, Product=32, SerialNumber=0

usb 2-1: Product: SigmaStarWIFI

usb 2-1: Manufacturer: SigmaStar inc

client [848] connected, module:sys

DISP width: 1024client [848] connected, module:disp

,height: 600

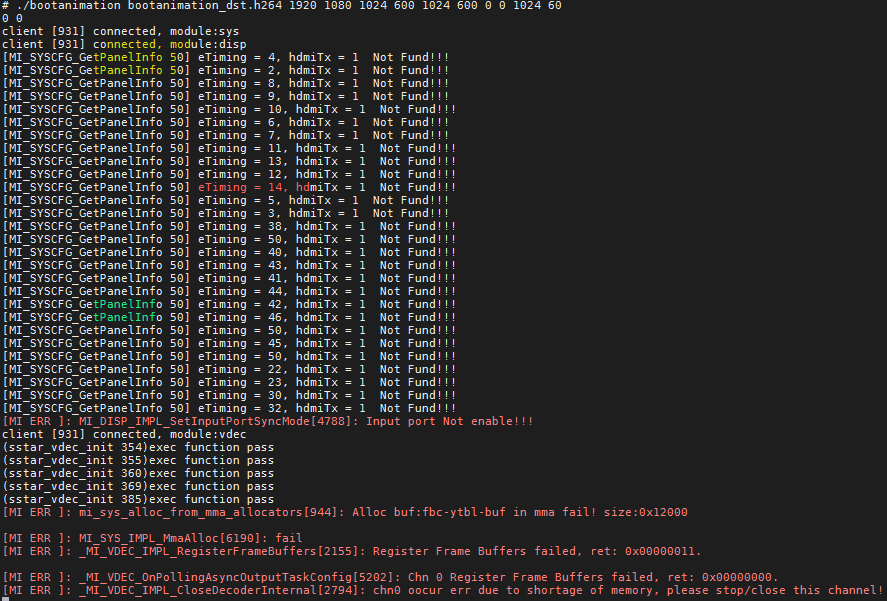

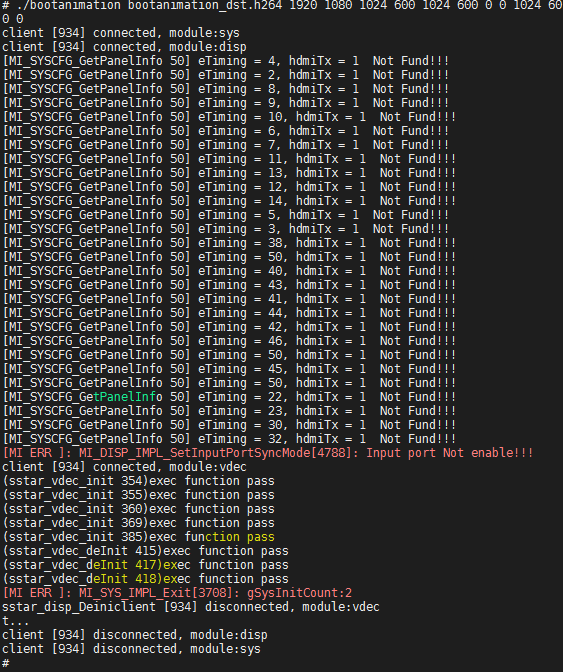

[MI_SYSCFG_GetPanelInfo 50] eTiming = 4, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 2, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 8, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 9, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 10, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 6, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 7, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 11, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 13, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 12, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 14, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 5, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 3, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 38, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 50, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 40, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 43, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 41, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 44, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 42, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 46, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 50, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 45, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 50, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 22, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 23, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 30, hdmiTx = 1 Not Fund!!!

[MI_SYSCFG_GetPanelInfo 50] eTiming = 32, hdmiTx = 1 Not Fund!!!

client [848] connected, module:panel

[MI_PANEL_Init][332]LCD environment is Invalid

Freeing fb memory: 3072K

sstar_FB_SetBlending 416 u8GOP=1,u8win=0 aType=1 u8constAlpha=255

The framebuffer device was opened successfulrandom: fast init done

ly.

1024x600, 32bpp

The framebuffer device was mapped to memory successfully.

Menu inited

Menu inited

Menu inited

Menu inited

Menu inited

Menu inited

Menu inited

Menu inited

Menu inited

Menu inited

Menu inited

Menu inited

Menu inited

Menu inited

Menu initedbootargs 传入mtd分区参数:

mtdparts=nand0:384k@1280k(IPL0),384k(IPL1),384k(IPL_CUST0),384k(IPL_CUST1),768k(UBOOT0),768k(UBOOT1),384k(ENV0),0x20000(KEY_CUST),0x60000(LOGO),0x500000(KERNEL),0x500000(RECOVERY),-(UBI)查看分区:

# cat /proc/mtd

dev: size erasesize name

mtd0: 00060000 00020000 "IPL0"

mtd1: 00060000 00020000 "IPL1"

mtd2: 00060000 00020000 "IPL_CUST0"

mtd3: 00060000 00020000 "IPL_CUST1"

mtd4: 000c0000 00020000 "UBOOT0"

mtd5: 000c0000 00020000 "UBOOT1"

mtd6: 00060000 00020000 "ENV0"

mtd7: 00020000 00020000 "KEY_CUST"

mtd8: 00060000 00020000 "LOGO"

mtd9: 00500000 00020000 "KERNEL"

mtd10: 00500000 00020000 "RECOVERY"

mtd11: 0f0e0000 00020000 "UBI"感谢 深圳市启明云端科技 友情赠送的7寸电容 4G & WIFI SSD202 开发板

http://whycan.com/t_5891.html

离线

楼主 #2 2021-02-15 22:17:02 分享评论

- SigmaStarStudy

- 会员

- 注册时间: 2021-02-15

- 已发帖子: 34

- 积分: 34

Re: 启明云端的7寸 1024*600 LCD SSD202 开发板从入门到放弃

文件系统没有gt911固件:

/lib/firmware/goodix_911_cfg.bin但是触摸屏正常使用

离线

楼主 #3 2021-02-15 22:41:33 分享评论

- SigmaStarStudy

- 会员

- 注册时间: 2021-02-15

- 已发帖子: 34

- 积分: 34

Re: 启明云端的7寸 1024*600 LCD SSD202 开发板从入门到放弃

http://doc.industio.com/docs/ssd20x-system/page_3-1

Creating 12 MTD partitions on "nand0":

0x000000140000-0x0000001a0000 : "IPL0"

0x0000001a0000-0x000000200000 : "IPL1"

0x000000200000-0x000000260000 : "IPL_CUST0"

0x000000260000-0x0000002c0000 : "IPL_CUST1"

0x0000002c0000-0x000000380000 : "UBOOT0"

0x000000380000-0x000000440000 : "UBOOT1"

0x000000440000-0x0000004a0000 : "ENV0"

0x0000004a0000-0x0000004c0000 : "KEY_CUST"

0x0000004c0000-0x000000520000 : "LOGO"

0x000000520000-0x000000a20000 : "KERNEL"

0x000000a20000-0x000000f20000 : "RECOVERY"

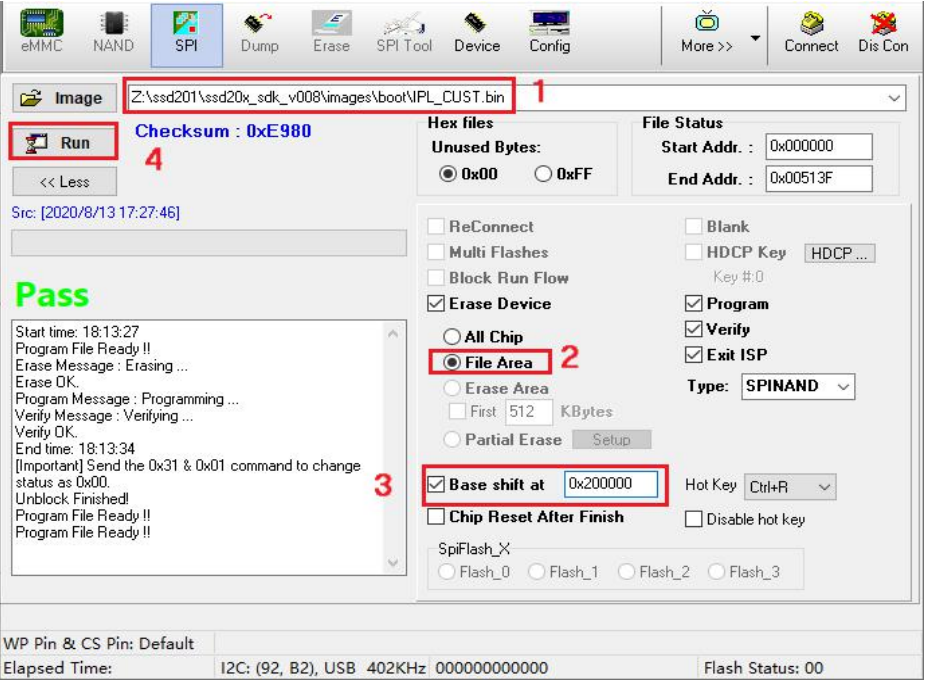

0x000000f20000-0x000010000000 : "UBI"IPL, IPL_CUST, UBOOT的烧录地址和kenerl log刚好能对应起来.

现在问题来了, 为什么 IPL, IPL_CUST, UBOOT 这三个都有两份一模一样的?

是备份? 考虑 NAND 不稳定?

离线

楼主 #4 2021-02-15 22:48:38 分享评论

- SigmaStarStudy

- 会员

- 注册时间: 2021-02-15

- 已发帖子: 34

- 积分: 34

Re: 启明云端的7寸 1024*600 LCD SSD202 开发板从入门到放弃

/ # md5sum /dev/mtd?

08ace1d6f8478a7ac01d2220f92a9e13 /dev/mtd0

08ace1d6f8478a7ac01d2220f92a9e13 /dev/mtd1

9f0f2a94ce8c49a0508332cc293d2ac1 /dev/mtd2

9f0f2a94ce8c49a0508332cc293d2ac1 /dev/mtd3

be23156a61bf9e56f8f076a7ad04b79f /dev/mtd4

be23156a61bf9e56f8f076a7ad04b79f /dev/mtd5

9e614c5a18d012b32033c1d809371110 /dev/mtd6

41d2e2c0c0edfccf76fa1c3e38bc1cf2 /dev/mtd7

e63040f23d8a2f4a6ef1d448f519d1d5 /dev/mtd8

96af93c2d08e63f63ab92643d536156a /dev/mtd9

/ # md5sum /dev/mtd??

96af93c2d08e63f63ab92643d536156a /dev/mtd10

d8dc4e69bffcd9dae5d09ce5279b9214 /dev/mtd11直接用md5sum获取分区的校验码, 果然备份分区与原分区数据一模一样.

好奇, 怎么判断原分区数据出错呢?

离线

楼主 #5 2021-02-15 22:52:11 分享评论

- SigmaStarStudy

- 会员

- 注册时间: 2021-02-15

- 已发帖子: 34

- 积分: 34

Re: 启明云端的7寸 1024*600 LCD SSD202 开发板从入门到放弃

/ # mount

ubi:rootfs on / type ubifs (rw,relatime)

devtmpfs on /dev type devtmpfs (rw,relatime,size=51064k,nr_inodes=12766,mode=755)

proc on /proc type proc (rw,relatime)

sysfs on /sys type sysfs (rw,relatime)

tmpfs on /tmp type tmpfs (rw,relatime,size=52088k,nr_inodes=13022)

var on /var type tmpfs (rw,relatime,size=52088k,nr_inodes=13022)

vendor on /vendor type tmpfs (rw,relatime,size=52088k,nr_inodes=13022)

none on /sys/kernel/debug type debugfs (rw,relatime)

mdev on /dev type tmpfs (rw,relatime,size=52088k,nr_inodes=13022)

ubi0:miservice on /config type ubifs (rw,relatime)

ubi0:customer on /customer type ubifs (rw,relatime)

ubi0:appconfigs on /appconfigs type ubifs (rw,relatime)

devpts on /dev/pts type devpts (rw,relatime,mode=600,ptmxmode=000)

/ #

/ #

/ #

/ # df

Filesystem 1K-blocks Used Available Use% Mounted on

ubi:rootfs 184756 33404 151352 18% /

devtmpfs 52088 0 52088 0% /dev

tmpfs 52088 0 52088 0% /tmp

var 52088 0 52088 0% /var

vendor 52088 0 52088 0% /vendor

mdev 52088 0 52088 0% /dev

ubi0:miservice 7680 5652 2028 74% /config

ubi0:customer 2980 164 2816 6% /customer

ubi0:appconfigs 2980 24 2956 1% /appconfigs

/ #对 ubifs 文件系统还是不熟, 慢慢学吧.

离线

楼主 #6 2021-02-15 22:56:41 分享评论

- SigmaStarStudy

- 会员

- 注册时间: 2021-02-15

- 已发帖子: 34

- 积分: 34

Re: 启明云端的7寸 1024*600 LCD SSD202 开发板从入门到放弃

http://doc.industio.com/docs/ssd201-sbc2d07/ssd201-sbc2d07-1ck3kjs5io40s

# cat /proc/mtd

dev: size erasesize name

mtd0: 00060000 00020000 "IPL0"

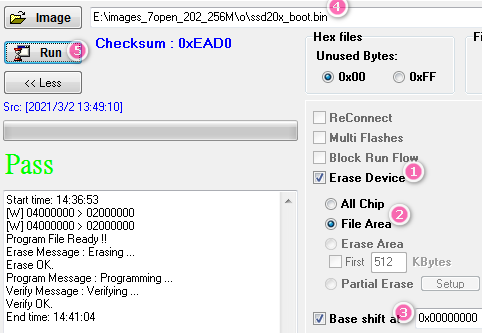

mtd1: 00060000 00020000 "IPL1"大概知道 为什么第一个分区不是 地址0 开始了, 因为前面还有一个 cis.bin

离线

楼主 #7 2021-02-15 23:22:24 分享评论

- SigmaStarStudy

- 会员

- 注册时间: 2021-02-15

- 已发帖子: 34

- 积分: 34

Re: 启明云端的7寸 1024*600 LCD SSD202 开发板从入门到放弃

SSD20x 大部分驱动程序在这个目录: drivers/sstar/

$ tree drivers/sstar/

drivers/sstar/

├── adaptor

│ ├── linux-rtos-adaptor.c

│ └── Makefile

├── bdma

│ ├── built-in.o

│ ├── infinity2

│ │ ├── hal_bdma.c

│ │ ├── hal_bdma.h

│ │ ├── kernel_bdma.h

│ │ └── Makefile

│ ├── infinity2m

│ │ ├── built-in.o

│ │ ├── hal_bdma.c

│ │ ├── hal_bdma.h

│ │ ├── hal_bdma.o

│ │ ├── kernel_bdma.h

│ │ ├── Makefile

│ │ ├── modules.builtin

│ │ └── modules.order

│ ├── infinity3

│ │ ├── hal_bdma.c

│ │ ├── hal_bdma.h

│ │ ├── kernel_bdma.h

│ │ └── Makefile

│ ├── infinity5

│ │ ├── hal_bdma.c

│ │ ├── hal_bdma.h

│ │ ├── kernel_bdma.h

│ │ └── Makefile

│ ├── infinity6

│ │ ├── hal_bdma.c

│ │ ├── hal_bdma.h

│ │ ├── kernel_bdma.h

│ │ └── Makefile

│ ├── infinity6b0

│ │ ├── hal_bdma.c

│ │ ├── hal_bdma.h

│ │ ├── kernel_bdma.h

│ │ └── Makefile

│ ├── infinity6e

│ │ ├── hal_bdma.c

│ │ ├── hal_bdma.h

│ │ ├── kernel_bdma.h

│ │ └── Makefile

│ ├── Kconfig

│ ├── Makefile

│ ├── modules.builtin

│ └── modules.order

├── built-in.o

├── cambricon

│ ├── Kconfig

│ └── Makefile

├── cam_clkgen

│ ├── built-in.o

│ ├── cam_clkgen.c

│ ├── cam_clkgen.o

│ ├── Makefile

│ ├── modules.builtin

│ └── modules.order

├── camdriver

│ ├── Kconfig

│ └── Makefile

├── cam_drv_buffer

│ ├── built-in.o

│ ├── cam_drv_buffer.mak

│ ├── HISTORY

│ ├── Makefile

│ ├── Makefile_Linux_user

│ ├── modules.builtin

│ ├── modules.order

│ ├── pub

│ │ └── cam_drv_buffer.h

│ └── src

│ ├── cam_drv_buffer.c

│ ├── cam_drv_buffer.o

│ ├── cam_drv_export.c

│ └── cam_drv_export.o

├── cam_drv_poll

│ ├── built-in.o

│ ├── cam_drv_poll.mak

│ ├── Makefile

│ ├── modules.builtin

│ ├── modules.order

│ ├── pub

│ │ └── cam_drv_poll.h

│ ├── sample_driver

│ │ ├── inc

│ │ │ └── mdrv_pollsample_module.h

│ │ ├── Makefile

│ │ ├── pub

│ │ │ └── mdrv_pollsample_io.h

│ │ ├── src

│ │ │ └── drv

│ │ │ ├── common

│ │ │ │ └── drv_pollsample_dev.c

│ │ │ ├── linux

│ │ │ │ ├── drv_pollsample_export.c

│ │ │ │ └── drv_pollsample_module.c

│ │ │ └── rtk

│ │ │ └── drv_pollsample_module.c

│ │ └── test

│ │ └── camdrvpolltest

│ │ ├── cam_drv_poll_test.c

│ │ └── Makefile

│ └── src

│ ├── cam_drv_poll.c

│ └── cam_drv_poll.o

├── cam_fs_wrapper

│ ├── built-in.o

│ ├── cam_fs_wrapper.mak

│ ├── HISTORY

│ ├── Makefile

│ ├── Makefile_lib

│ ├── modules.builtin

│ ├── modules.order

│ ├── pub

│ │ └── cam_fs_wrapper.h

│ ├── src

│ │ ├── cam_fs_export.c

│ │ ├── cam_fs_export.o

│ │ ├── cam_fs_wrapper.c

│ │ └── cam_fs_wrapper.o

│ └── test

│ ├── cam_fs_linux_kernel_test.c

│ ├── cam_fs_linux_user_test.c

│ └── Makefile

├── cam_os_wrapper

│ ├── built-in.o

│ ├── cam_os_wrapper.mak

│ ├── HISTORY

│ ├── Makefile

│ ├── Makefile_lib

│ ├── modules.builtin

│ ├── modules.order

│ ├── pub

│ │ ├── cam_os_util_bitmap.h

│ │ ├── cam_os_util_bug.h

│ │ ├── cam_os_util.h

│ │ ├── cam_os_util_hash.h

│ │ ├── cam_os_util_ioctl.h

│ │ ├── cam_os_util_list.h

│ │ ├── cam_os_util_string.h

│ │ └── cam_os_wrapper.h

│ ├── src

│ │ ├── cam_os_export.c

│ │ ├── cam_os_export.o

│ │ ├── cam_os_informal_idr.c

│ │ ├── cam_os_informal_idr.o

│ │ ├── cam_os_wrapper.c

│ │ └── cam_os_wrapper.o

│ └── test

│ ├── cam_os_wrapper_linux_kernel_test.c

│ ├── cam_os_wrapper_test.c

│ ├── cam_os_wrapper_test.h

│ └── Makefile

├── cam_sysfs

│ ├── built-in.o

│ ├── cam_sysfs.c

│ ├── cam_sysfs.o

│ ├── Makefile

│ ├── modules.builtin

│ └── modules.order

├── ceva_link

│ ├── boot_loader.c

│ ├── boot_loader.h

│ ├── ceva_linkdrv.c

│ ├── ceva_linkdrv-generic.h

│ ├── ceva_linkdrv.h

│ ├── ceva_linkdrv_proc.c

│ ├── ceva_linkdrv_proc.h

│ ├── ceva_linkdrv_shared_process_protected_db_def_copy.h

│ ├── ceva_linkdrv_xm6.c

│ ├── ceva_linkdrv_xm6.h

│ ├── drv_debug.h

│ ├── file_access.c

│ ├── file_access.h

│ ├── hal_ceva.c

│ ├── hal_ceva.h

│ ├── hal_ceva_reg.h

│ ├── hal_cpm.c

│ ├── hal_cpm.h

│ ├── hal_debug.h

│ ├── hal_intr_ctrl.c

│ ├── hal_intr_ctrl.h

│ ├── hal_intr_ctrl_reg.h

│ ├── hal_timer.c

│ ├── hal_timer.h

│ ├── jni

│ │ └── test.c

│ ├── Kconfig

│ ├── Makefile

│ ├── protected_mem_db.c

│ └── protected_mem_db.h

├── clk

│ ├── built-in.o

│ ├── cedric

│ │ ├── clk.c

│ │ └── Makefile

│ ├── infinity

│ │ ├── Makefile

│ │ └── ms_complex_clk.c

│ ├── infinity2

│ │ ├── Makefile

│ │ └── ms_complex_clk.c

│ ├── infinity2m

│ │ ├── built-in.o

│ │ ├── Makefile

│ │ ├── modules.builtin

│ │ ├── modules.order

│ │ ├── ms_complex_clk.c

│ │ └── ms_complex_clk.o

│ ├── infinity3

│ │ ├── Makefile

│ │ └── ms_complex_clk.c

│ ├── infinity5

│ │ ├── Makefile

│ │ └── ms_complex_clk.c

│ ├── infinity6

│ │ ├── Makefile

│ │ └── ms_complex_clk.c

│ ├── infinity6b0

│ │ ├── Makefile

│ │ └── ms_complex_clk.c

│ ├── infinity6e

│ │ ├── Makefile

│ │ └── ms_complex_clk.c

│ ├── Kconfig

│ ├── Makefile

│ ├── modules.builtin

│ ├── modules.order

│ ├── ms_composite_clk.c

│ ├── ms_composite_clk.o

│ └── ms_usclk.c

├── clocksource

│ ├── built-in.o

│ ├── Kconfig

│ ├── Makefile

│ ├── modules.builtin

│ ├── modules.order

│ ├── ms_arm_gt_clocksource.c

│ └── ms_piu_timer.c

├── cpu

│ ├── built-in.o

│ ├── Makefile

│ ├── memory.c

│ ├── mem-ory.o

│ ├── memory.o

│ ├── modules.builtin

│ └── modules.order

├── cpufreq

│ ├── built-in.o

│ ├── infinity

│ │ └── cpufreq.c

│ ├── infinity2m

│ │ ├── cpufreq.c

│ │ └── cpufreq.o

│ ├── infinity3

│ │ └── cpufreq.c

│ ├── infinity5

│ │ └── cpufreq.c

│ ├── infinity6

│ │ └── cpufreq.c

│ ├── infinity6b0

│ │ └── cpufreq.c

│ ├── infinity6e

│ │ └── cpufreq.c

│ ├── Kconfig

│ ├── Makefile

│ ├── modules.builtin

│ └── modules.order

├── crypto

│ ├── built-in.o

│ ├── cryptodev

│ │ ├── authenc.c

│ │ ├── authenc.o

│ │ ├── AUTHORS

│ │ ├── built-in.o

│ │ ├── cipherapi.h

│ │ ├── COPYING

│ │ ├── cryptlib.c

│ │ ├── cryptlib.h

│ │ ├── cryptlib.o

│ │ ├── crypto

│ │ │ └── cryptodev.h

│ │ ├── cryptodev_int.h

│ │ ├── cryptodev.ko

│ │ ├── cryptodev.mod.c

│ │ ├── cryptodev.mod.o

│ │ ├── cryptodev.o

│ │ ├── examples

│ │ │ ├── aes.c

│ │ │ ├── aes-gcm.c

│ │ │ ├── aes-gcm.h

│ │ │ ├── aes.h

│ │ │ ├── aes-sha1.c

│ │ │ ├── aes-sha1.h

│ │ │ ├── readme

│ │ │ ├── sha.c

│ │ │ ├── sha-copy.c

│ │ │ ├── sha-copy.h

│ │ │ └── sha.h

│ │ ├── INSTALL

│ │ ├── ioctl.c

│ │ ├── ioctl.o

│ │ ├── main.c

│ │ ├── main.o

│ │ ├── Makefile

│ │ ├── modules.order

│ │ ├── NEWS

│ │ ├── README

│ │ ├── util.c

│ │ ├── util.h

│ │ ├── util.o

│ │ ├── version.h

│ │ ├── zc.c

│ │ ├── zc.h

│ │ └── zc.o

│ ├── hal

│ │ ├── infinity2m

│ │ │ └── halAESDMA.h

│ │ ├── infinity3

│ │ │ └── halAESDMA.h

│ │ ├── infinity5

│ │ │ └── halAESDMA.h

│ │ ├── infinity6

│ │ │ └── halAESDMA.h

│ │ ├── infinity6b0

│ │ │ └── halAESDMA.h

│ │ └── infinity6e

│ │ └── halAESDMA.h

│ ├── halAESDMA.c

│ ├── halAESDMA.o

│ ├── Kconfig

│ ├── Makefile

│ ├── mdrv_aes.c

│ ├── mdrv_aes.h

│ ├── mdrv_aes.o

│ ├── mdrv_cipher.c

│ ├── mdrv_cipher.o

│ ├── mdrv_crypto.ko

│ ├── mdrv_crypto.mod.c

│ ├── mdrv_crypto.mod.o

│ ├── mdrv_crypto.o

│ ├── mdrv_rsa.c

│ ├── mdrv_rsa.h

│ ├── mdrv_rsa.o

│ ├── mdrv_sha.c

│ ├── mdrv_sha.o

│ └── modules.order

├── dualos

│ ├── drv_dualos.c

│ ├── interos_call.h

│ ├── lock.h

│ ├── Makefile

│ ├── rlink.h

│ ├── rsq.c

│ ├── rsq.h

│ ├── sw_sem.c

│ └── sw_sem.h

├── emac

│ ├── built-in.o

│ ├── hal

│ │ ├── infinity2

│ │ │ ├── mhal_emac.c

│ │ │ ├── mhal_emac.h

│ │ │ └── mhal_rng_reg.h

│ │ ├── infinity2m

│ │ │ ├── mhal_emac.c

│ │ │ ├── mhal_emac.h

│ │ │ ├── mhal_emac.o

│ │ │ └── mhal_rng_reg.h

│ │ ├── infinity3

│ │ │ ├── mhal_emac.c

│ │ │ ├── mhal_emac.h

│ │ │ └── mhal_rng_reg.h

│ │ ├── infinity5

│ │ │ ├── mhal_emac.c

│ │ │ ├── mhal_emac.h

│ │ │ └── mhal_rng_reg.h

│ │ ├── infinity6

│ │ │ ├── mhal_emac.c

│ │ │ ├── mhal_emac.h

│ │ │ └── mhal_rng_reg.h

│ │ ├── infinity6b0

│ │ │ ├── mhal_emac.c

│ │ │ ├── mhal_emac.h

│ │ │ └── mhal_rng_reg.h

│ │ └── infinity6e

│ │ ├── mhal_emac.c

│ │ ├── mhal_emac.h

│ │ └── mhal_rng_reg.h

│ ├── Kconfig

│ ├── kdrv_emac.o

│ ├── Makefile

│ ├── mdrv_emac.c

│ ├── mdrv_emac.h

│ ├── mdrv_emac.o

│ ├── modules.builtin

│ ├── modules.order

│ ├── Mstar_emac_problem_shooting_v0 .doc

│ └── policy.txt

├── emmc

│ ├── cedric

│ │ ├── eMMCDrv

│ │ │ ├── inc

│ │ │ │ ├── api

│ │ │ │ │ └── drv_eMMC.h

│ │ │ │ ├── common

│ │ │ │ │ ├── eMMC_err_codes.h

│ │ │ │ │ ├── eMMC.h

│ │ │ │ │ ├── eMMC_hal.h

│ │ │ │ │ └── eMMC_utl.h

│ │ │ │ └── config

│ │ │ │ ├── eMMC_cedric_linux.h

│ │ │ │ ├── eMMC_chicago_linux.h

│ │ │ │ ├── eMMC_config.h

│ │ │ │ ├── eMMC_eagle_linux.h

│ │ │ │ ├── eMMC_edison_linux.h

│ │ │ │ ├── eMMC_eiffel_linux.h

│ │ │ │ ├── eMMC_einstein_linux.h

│ │ │ │ └── eMMC_reg.h

│ │ │ └── src

│ │ │ ├── api

│ │ │ │ └── eMMC_prg.c

│ │ │ ├── common

│ │ │ │ ├── cmd_mstar_emmc_bootloader.txt

│ │ │ │ ├── eMMC_hal.c

│ │ │ │ ├── eMMC_ip_verify.c

│ │ │ │ └── eMMC_utl.c

│ │ │ └── config

│ │ │ └── eMMC_platform.c

│ │ ├── Makefile

│ │ ├── mstar_mci.c

│ │ └── mstar_mci.h

│ ├── chicago

│ │ ├── eMMCDrv

│ │ │ ├── inc

│ │ │ │ ├── api

│ │ │ │ │ └── drv_eMMC.h

│ │ │ │ ├── common

│ │ │ │ │ ├── eMMC_err_codes.h

│ │ │ │ │ ├── eMMC.h

│ │ │ │ │ ├── eMMC_hal.h

│ │ │ │ │ └── eMMC_utl.h

│ │ │ │ └── config

│ │ │ │ ├── eMMC_cedric_linux.h

│ │ │ │ ├── eMMC_chicago_linux.h

│ │ │ │ ├── eMMC_config.h

│ │ │ │ ├── eMMC_eagle_linux.h

│ │ │ │ ├── eMMC_edison_linux.h

│ │ │ │ ├── eMMC_eiffel_linux.h

│ │ │ │ ├── eMMC_einstein_linux.h

│ │ │ │ └── eMMC_reg.h

│ │ │ └── src

│ │ │ ├── api

│ │ │ │ └── eMMC_prg.c

│ │ │ ├── common

│ │ │ │ ├── cmd_mstar_emmc_bootloader.txt

│ │ │ │ ├── eMMC_hal.c

│ │ │ │ ├── eMMC_ip_verify.c

│ │ │ │ └── eMMC_utl.c

│ │ │ └── config

│ │ │ └── eMMC_platform.c

│ │ ├── Makefile

│ │ ├── mstar_mci.c

│ │ └── mstar_mci.h

│ ├── Kconfig

│ ├── Makefile

│ └── unify_driver

│ ├── inc

│ │ ├── api

│ │ │ └── drv_eMMC.h

│ │ ├── common

│ │ │ ├── eMMC_err_codes.h

│ │ │ ├── eMMC.h

│ │ │ ├── eMMC_hal.h

│ │ │ └── eMMC_utl.h

│ │ ├── config

│ │ │ ├── eMMC_config.h

│ │ │ ├── eMMC_reg.h

│ │ │ └── eMMC_reg_v5.h

│ │ ├── infinity2m

│ │ │ └── eMMC_linux.h

│ │ ├── infinity3

│ │ │ └── eMMC_linux.h

│ │ ├── infinity5

│ │ │ └── eMMC_linux.h

│ │ ├── infinity6

│ │ │ └── eMMC_linux.h

│ │ └── infinity6e

│ │ └── eMMC_linux.h

│ ├── Makefile

│ ├── mmc.lds

│ ├── mstar_mci.c

│ ├── mstar_mci.h

│ ├── mstar_mci_v5.c

│ └── src

│ ├── api

│ │ └── eMMC_prg.c

│ ├── common

│ │ ├── eMMC_hal.c

│ │ ├── eMMC_hal_speed.c

│ │ ├── eMMC_hal_v5.c

│ │ ├── eMMC_ip_verify.c

│ │ └── eMMC_utl.c

│ └── config

│ └── eMMC_platform.c

├── flash_isp

│ ├── built-in.o

│ ├── drvDeviceInfo.c

│ ├── drvDeviceInfo.h

│ ├── drvDeviceInfo.o

│ ├── drvSERFLASH.c

│ ├── drvSERFLASH.h

│ ├── drvSERFLASH.o

│ ├── include

│ │ └── MsTypes.h

│ ├── infinity2

│ │ ├── halSERFLASH.c

│ │ ├── halSERFLASH.h

│ │ └── regSERFLASH.h

│ ├── infinity2m

│ │ ├── halSERFLASH.c

│ │ ├── halSERFLASH.h

│ │ ├── halSERFLASH.o

│ │ └── regSERFLASH.h

│ ├── infinity3

│ │ ├── halSERFLASH.c

│ │ ├── halSERFLASH.h

│ │ └── regSERFLASH.h

│ ├── infinity5

│ │ ├── halSERFLASH.c

│ │ ├── halSERFLASH.h

│ │ └── regSERFLASH.h

│ ├── infinity6

│ │ ├── halSERFLASH.c

│ │ ├── halSERFLASH.h

│ │ └── regSERFLASH.h

│ ├── infinity6b0

│ │ ├── halSERFLASH.c

│ │ ├── halSERFLASH.h

│ │ └── regSERFLASH.h

│ ├── infinity6e

│ │ ├── halSERFLASH.c

│ │ ├── halSERFLASH.h

│ │ └── regSERFLASH.h

│ ├── Kconfig

│ ├── Makefile

│ ├── modules.builtin

│ ├── modules.order

│ ├── mtd_serflash.c

│ ├── mtd_serflash.o

│ ├── mxp_flash.c

│ ├── mxp_flash.o

│ ├── part_mxp.c

│ ├── part_mxp.h

│ └── part_mxp.o

├── gmac

│ ├── drv_mdio_sw.c

│ ├── hal

│ │ ├── infinity2

│ │ │ ├── mhal_gmac.c.old

│ │ │ ├── mhal_gmac.h.old

│ │ │ ├── mhal_gmac_v3.c

│ │ │ ├── mhal_gmac_v3.h

│ │ │ └── mhal_rng_reg.h

│ │ └── kano

│ │ ├── mhal_gmac.c

│ │ ├── mhal_gmac.h

│ │ ├── mhal_gmac_v3.c

│ │ ├── mhal_gmac_v3.h

│ │ └── mhal_rng_reg.h

│ ├── Kconfig

│ ├── Kconfig.old

│ ├── Makefile

│ ├── mdrv_gmac.c.old

│ ├── mdrv_gmac.h.old

│ ├── mdrv_gmac_v2.c.old

│ ├── mdrv_gmac_v3.c

│ └── mdrv_gmac_v3.h

├── gpio

│ ├── built-in.o

│ ├── cedric

│ │ ├── Makefile

│ │ ├── mhal_gpio.c

│ │ ├── mhal_gpio.h

│ │ └── mhal_gpio_reg.h

│ ├── infinity

│ │ ├── Makefile

│ │ ├── mhal_gpio.c

│ │ ├── mhal_gpio.h

│ │ └── mhal_gpio_reg.h

│ ├── infinity2

│ │ ├── GPIO_TABLE.h

│ │ ├── Makefile

│ │ ├── mhal_gpio.c

│ │ ├── mhal_gpio.h

│ │ ├── mhal_gpio_reg.h

│ │ └── mhal_pinmux.c

│ ├── infinity2m

│ │ ├── built-in.o

│ │ ├── chiptop_reg.h

│ │ ├── gpio_table.c

│ │ ├── gpio_table.h

│ │ ├── gpio_table.o

│ │ ├── Makefile

│ │ ├── mhal_gpio.c

│ │ ├── mhal_gpio.h

│ │ ├── mhal_gpio.o

│ │ ├── mhal_pinmux.c

│ │ ├── mhal_pinmux.h

│ │ ├── mhal_pinmux.o

│ │ ├── modules.builtin

│ │ ├── modules.order

│ │ ├── padmux_tables.c

│ │ ├── padmux_tables.h

│ │ ├── padmux_tables.o

│ │ └── pmsleep_reg.h

│ ├── infinity3

│ │ ├── mhal_gpio.c

│ │ ├── mhal_gpio.h

│ │ ├── mhal_gpio_reg.h

│ │ └── mhal_pinmux.c

│ ├── infinity5

│ │ ├── Makefile

│ │ ├── mhal_gpio.c

│ │ ├── mhal_gpio.h

│ │ ├── mhal_gpio_reg.h

│ │ └── mhal_pinmux.c

│ ├── infinity6

│ │ ├── Makefile

│ │ ├── mhal_gpio.c

│ │ ├── mhal_gpio.h

│ │ ├── mhal_pinmux.c

│ │ └── mhal_pinmux.h

│ ├── infinity6b0

│ │ ├── Makefile

│ │ ├── mhal_gpio.c

│ │ ├── mhal_gpio.h

│ │ ├── mhal_pinmux.c

│ │ └── mhal_pinmux.h

│ ├── infinity6e

│ │ ├── Makefile

│ │ ├── mhal_gpio.c

│ │ ├── mhal_gpio.h

│ │ ├── mhal_pinmux.c

│ │ └── mhal_pinmux.h

│ ├── Kconfig

│ ├── Makefile

│ ├── mdrv_gpio.c

│ ├── mdrv_gpio_io.c

│ ├── mdrv_gpio_io.o

│ ├── mdrv_gpio.o

│ ├── mdrv_sw_iic.c

│ ├── mdrv_sw_iic.h

│ ├── modules.builtin

│ ├── modules.order

│ ├── ms_gpioi2c.c

│ └── test

│ ├── gpio_irq_test.c

│ └── Makefile

├── gpio_key_sample

│ ├── gpio_key_driver

│ │ ├── gpio_key_driver.c

│ │ └── Makefile

│ ├── kernel_gpio_key_patch

│ │ └── drivers

│ │ └── input

│ │ └── keyboard

│ │ └── gpio_keys.c

│ ├── key_test.c

│ └── readme.txt

├── GUIDELINE.doc

├── i2c

│ ├── built-in.o

│ ├── cedric

│ │ ├── Makefile

│ │ ├── mhal_iic.c

│ │ ├── mhal_iic.h

│ │ └── mhal_iic_reg.h

│ ├── infinity

│ │ ├── Makefile

│ │ ├── mhal_iic.c

│ │ ├── mhal_iic.h

│ │ └── mhal_iic_reg.h

│ ├── infinity2

│ │ ├── Makefile

│ │ ├── mhal_iic.c

│ │ ├── mhal_iic.h

│ │ └── mhal_iic_reg.h

│ ├── infinity2m

│ │ ├── Makefile

│ │ ├── mhal_iic.c

│ │ ├── mhal_iic.h

│ │ ├── mhal_iic.o

│ │ └── mhal_iic_reg.h

│ ├── infinity3

│ │ ├── Makefile

│ │ ├── mhal_iic.c

│ │ ├── mhal_iic.h

│ │ └── mhal_iic_reg.h

│ ├── infinity5

│ │ ├── Makefile

│ │ ├── mhal_iic.c

│ │ ├── mhal_iic.h

│ │ └── mhal_iic_reg.h

│ ├── infinity6

│ │ ├── Makefile

│ │ ├── mhal_iic.c

│ │ ├── mhal_iic.h

│ │ └── mhal_iic_reg.h

│ ├── infinity6b0

│ │ ├── Makefile

│ │ ├── mhal_iic.c

│ │ ├── mhal_iic.h

│ │ └── mhal_iic_reg.h

│ ├── infinity6e

│ │ ├── Makefile

│ │ ├── mhal_iic.c

│ │ ├── mhal_iic.h

│ │ └── mhal_iic_reg.h

│ ├── Kconfig

│ ├── Makefile

│ ├── modules.builtin

│ ├── modules.order

│ ├── ms_iic.c

│ ├── ms_iic.h

│ └── ms_iic.o

├── include

│ ├── cam_clkgen.h

│ ├── cam_dev_wrapper.h

│ ├── cam_drv_buffer.h

│ ├── cam_drv_poll.h

│ ├── cam_fs_wrapper.h

│ ├── cam_os_util_bitmap.h

│ ├── cam_os_util_bug.h

│ ├── cam_os_util.h

│ ├── cam_os_util_hash.h

│ ├── cam_os_util_ioctl.h

│ ├── cam_os_util_list.h

│ ├── cam_os_util_string.h

│ ├── cam_os_wrapper.h

│ ├── cam_sysfs.h

│ ├── cam_sysfs.h.bak

│ ├── ceva_linkdrv-generic.h

│ ├── drvcmdq_io.h

│ ├── drv_dualos.h

│ ├── drv_isrcb.h

│ ├── infinity2

│ │ ├── gpi-irqs.h

│ │ ├── gpio.h

│ │ ├── irqs.h

│ │ ├── Kconfig

│ │ ├── mcm_id.h

│ │ ├── mdrv_miu.h

│ │ ├── mhal_miu.h

│ │ ├── padmux.h

│ │ ├── powerDown

│ │ │ ├── AVDD3P3_USB_P0

│ │ │ │ ├── 1_Infinity2_usb20_p0_pd.h

│ │ │ │ ├── 2_Infinity2_upll_p0_pd.h

│ │ │ │ ├── 3_Infinity2_gmacpll_pd.h

│ │ │ │ ├── 4_Infinity2_cevapll_pd.h

│ │ │ │ ├── 5_Infinity2_extaupll_pd.h

│ │ │ │ └── 6_Infinity2_hdmi2txpll_pd.h

│ │ │ ├── AVDD3P3_USB_P1

│ │ │ │ ├── 1_Infinity2_usb20_p0_pd.h

│ │ │ │ ├── 2_Infinity2_upll_p0_pd.h

│ │ │ │ ├── 3_Infinity2_mipspll_pd.h

│ │ │ │ ├── 4_Infinity2_isppll_pd.h

│ │ │ │ ├── 5_Infinity2_hicodecpll_pd.h

│ │ │ │ └── 6_Infinity2_evdpll_pd.h

│ │ │ ├── AVDD3P3_USB_P2

│ │ │ │ ├── 1_Infinity2_usb20_p0_pd.h

│ │ │ │ ├── 2_Infinity2_upll_p2_pd.h

│ │ │ │ └── 3_Infinity2_miu128pll_pd.h

│ │ │ ├── AVDD3P3_USB_P3

│ │ │ │ └── 1_Infinity2_usb20_p3_pd.h

│ │ │ ├── AVDD_MIPI_TX

│ │ │ │ ├── 1_Infinity2_mipi_combotx_pd.h

│ │ │ │ ├── 2_Infinity2_mpll_pd.h

│ │ │ │ └── 3_Infinity2_lpll_pd.h

│ │ │ ├── ETH_TX_100T_RANDOM.h

│ │ │ ├── ETH_TX_10T_ALL_ONE.h

│ │ │ ├── ETH_TX_10T_LTP.h

│ │ │ ├── ETH_TX_10T_TP_IDL.h

│ │ │ ├── Infinity2_mipi_rx_pd

│ │ │ │ ├── Infinity2_mipi_rx_p0_pd.h

│ │ │ │ ├── Infinity2_mipi_rx_p1_pd.h

│ │ │ │ ├── Infinity2_mipi_rx_p2_pd.h

│ │ │ │ └── Infinity2_mipi_rx_p3_pd.h

│ │ │ ├── U3CP_CP0_CP7_pattern_p0.h

│ │ │ ├── U3CP_CP0_CP7_pattern_p1.h

│ │ │ ├── U3PCIE_CP0_CP7_pattern_m_PHY_p0.h

│ │ │ ├── U3PCIE_CP0_CP7_pattern_m_PHY_p1.h

│ │ │ ├── USB20_verification_pattern_TSTPG_FS_v2.h

│ │ │ └── USB20_verification_pattern_TSTPG_v2.h

│ │ ├── reg_clks.h

│ │ ├── registers.h

│ │ ├── regMIU.h

│ │ └── vcore_dvfs.h

│ ├── infinity2m

│ │ ├── cpu_freq.h

│ │ ├── gpi-irqs.h

│ │ ├── gpio.h

│ │ ├── irqs.h

│ │ ├── Kconfig

│ │ ├── mcm_id.h

│ │ ├── mdrv_miu.h

│ │ ├── mhal_miu.h

│ │ ├── padmux.h

│ │ ├── reg_clks.h

│ │ ├── registers.h

│ │ ├── regMIU.h

│ │ └── voltage_ctrl_demander.h

│ ├── infinity3

│ │ ├── cpu_freq.h

│ │ ├── gpio.h

│ │ ├── irqs.h

│ │ ├── Kconfig

│ │ ├── mcm_id.h

│ │ ├── padmux.h

│ │ ├── reg_clks.h

│ │ └── registers.h

│ ├── infinity5

│ │ ├── cpu_freq.h

│ │ ├── gpio.h

│ │ ├── irqs.h

│ │ ├── Kconfig

│ │ ├── mcm_id.h

│ │ ├── mdrv_miu.h

│ │ ├── mhal_miu.h

│ │ ├── padmux.h

│ │ ├── reg_clks.h

│ │ ├── registers.h

│ │ ├── regMIU.h

│ │ └── voltage_ctrl_demander.h

│ ├── infinity6

│ │ ├── cpu_freq.h

│ │ ├── gpi-irqs.h

│ │ ├── gpio.h

│ │ ├── irqs.h

│ │ ├── Kconfig

│ │ ├── mcm_id.h

│ │ ├── mdrv_miu.h

│ │ ├── mhal_miu.h

│ │ ├── padmux.h

│ │ ├── pmsleep-irqs.h

│ │ ├── reg_clks.h

│ │ ├── registers.h

│ │ ├── regMIU.h

│ │ └── voltage_ctrl_demander.h

│ ├── infinity6b0

│ │ ├── cpu_freq.h

│ │ ├── gpi-irqs.h

│ │ ├── gpio.h

│ │ ├── irqs.h

│ │ ├── Kconfig

│ │ ├── mcm_id.h

│ │ ├── mdrv_miu.h

│ │ ├── mhal_miu.h

│ │ ├── padmux.h

│ │ ├── pmsleep-irqs.h

│ │ ├── reg_clks.h

│ │ ├── registers.h

│ │ ├── regMIU.h

│ │ └── voltage_ctrl_demander.h

│ ├── infinity6e

│ │ ├── cpu_freq.h

│ │ ├── gpi-irqs.h

│ │ ├── gpio.h

│ │ ├── iopow.h

│ │ ├── irqs.h

│ │ ├── Kconfig

│ │ ├── mcm_id.h

│ │ ├── mdrv_miu.h

│ │ ├── mhal_miu.h

│ │ ├── padmux.h

│ │ ├── pmsleep-irqs.h

│ │ ├── reg_clks.h

│ │ ├── registers.h

│ │ ├── regMIU.h

│ │ └── voltage_ctrl_demander.h

│ ├── mdrv_API_version.h

│ ├── mdrv_cipher.h

│ ├── mdrv_device_id.h

│ ├── mdrv_fb_io.h

│ ├── mdrv_fb_st.h

│ ├── mdrv_gpio.h

│ ├── mdrv_gpio_io.h

│ ├── mdrv_hvsp_io.h

│ ├── mdrv_hvsp_io_i3.h

│ ├── mdrv_hvsp_io_i3_st.h

│ ├── mdrv_hvsp_io_st.h

│ ├── mdrv_isp_io.h

│ ├── mdrv_isp_io_st.h

│ ├── mdrv_ive_io.h

│ ├── mdrv_ive_io_st.h

│ ├── mdrv_jpe_io.h

│ ├── mdrv_jpe_io_st.h

│ ├── mdrv_mfe_io.h

│ ├── mdrv_mma_heap.h

│ ├── mdrv_mmfe_io.h

│ ├── mdrv_mmfe_st.h

│ ├── mdrv_msys_io.h

│ ├── mdrv_msys_io_st.h

│ ├── mdrv_mvhe_io.h

│ ├── mdrv_mvhe_st.h

│ ├── mdrv_padmux.h

│ ├── mdrv_pnl_io.h

│ ├── mdrv_pnl_io_st.h

│ ├── mdrv_puse.h

│ ├── mdrv_rqct_io.h

│ ├── mdrv_rqct_st.h

│ ├── mdrv_sar_io.h

│ ├── mdrv_sca_io.h

│ ├── mdrv_sca_st.h

│ ├── mdrv_scldma_io.h

│ ├── mdrv_scldma_io_i3.h

│ ├── mdrv_scldma_io_i3_st.h

│ ├── mdrv_scldma_io_st.h

│ ├── mdrv_sound_io.h

│ ├── mdrv_system.h

│ ├── mdrv_system_st.h

│ ├── mdrv_types.h

│ ├── mdrv_verchk.h

│ ├── mdrv_video.h

│ ├── mdrv_vip_io.h

│ ├── mdrv_vip_io_i3.h

│ ├── mdrv_vip_io_i3_st.h

│ ├── mdrv_vip_io_st.h

│ ├── mdrv_warp_io.h

│ ├── mdrv_warp_io_st.h

│ ├── mdrv_xpm_io.h

│ ├── mdrv_xpm_io_st.h

│ ├── ms_msys.h

│ ├── ms_platform.h

│ ├── _ms_private.h

│ ├── mstar_chip.h

│ ├── mst_platform.h

│ ├── ms_types.h

│ ├── MsTypes.h

│ ├── ms_version.h

│ ├── prom.h

│ ├── region_substract.h

│ ├── vcore_defs.h

│ └── voltage_ctrl.h

├── iopower

│ ├── Kconfig

│ ├── Makefile

│ └── mdrv_iopower.c

├── ir

│ ├── include

│ │ ├── IR_CONFIG.h

│ │ └── IR_MSTAR_DTV.h

│ ├── Kconfig

│ ├── Makefile

│ ├── ms_ir.c

│ ├── ms_ir.h

│ └── reg_ir.h

├── ircut

│ ├── Kconfig

│ ├── Makefile

│ └── ms_ircut.c

├── irqchip

│ ├── built-in.o

│ ├── infinity2

│ │ ├── irqchip.c

│ │ ├── irqchip_i2.c

│ │ ├── irq-gpi.c

│ │ ├── irq-pmsleep.c

│ │ └── Makefile

│ ├── infinity2m

│ │ ├── built-in.o

│ │ ├── irqchip.c

│ │ ├── irqchip.o

│ │ ├── irq-gpi.c

│ │ ├── irq-gpi.o

│ │ ├── irq-pmsleep.c

│ │ ├── irq-pmsleep.o

│ │ ├── Makefile

│ │ ├── modules.builtin

│ │ └── modules.order

│ ├── infinity3

│ │ └── irqchip.c

│ ├── infinity5

│ │ ├── irqchip.c

│ │ └── Makefile

│ ├── infinity6

│ │ ├── irqchip.c

│ │ ├── irq-gpi.c

│ │ ├── irq-pmsleep.c

│ │ └── Makefile

│ ├── infinity6b0

│ │ ├── irqchip.c

│ │ ├── irq-gpi.c

│ │ ├── irq-pmsleep.c

│ │ └── Makefile

│ ├── infinity6e

│ │ ├── irqchip.c

│ │ ├── irq-gpi.c

│ │ ├── irq-pmsleep.c

│ │ └── Makefile

│ ├── Kconfig

│ ├── Makefile

│ ├── modules.builtin

│ └── modules.order

├── isrcb

│ ├── drv

│ │ ├── pub

│ │ │ └── drv_isrcb.h

│ │ └── src

│ │ ├── common

│ │ │ └── drv_isrcb.c

│ │ └── linux

│ │ └── drv_isrcb_module.c

│ ├── Kconfig

│ └── Makefile

├── ive

│ ├── drv_ive.c

│ ├── drv_ive.h

│ ├── hal_clk.c

│ ├── hal_clk.h

│ ├── hal_debug.h

│ ├── hal_ive.c

│ ├── hal_ive.h

│ ├── hal_ive_reg.h

│ ├── hal_ive_simulate.c

│ ├── hal_ive_simulate.h

│ ├── Kconfig

│ ├── Makefile

│ ├── mdrv_ive.c

│ └── mdrv_ive.h

├── Kconfig

├── Makefile

├── miu

│ ├── built-in.o

│ ├── infinity2

│ │ ├── mdrv_miu.c

│ │ └── mhal_miu.c

│ ├── infinity2m

│ │ ├── mdrv_miu.c

│ │ ├── mdrv_miu.o

│ │ ├── mhal_miu.c

│ │ └── mhal_miu.o

│ ├── infinity5

│ │ ├── mdrv_miu.c

│ │ └── mhal_miu.c

│ ├── infinity6

│ │ ├── mdrv_miu.c

│ │ └── mhal_miu.c

│ ├── infinity6b0

│ │ ├── mdrv_miu.c

│ │ └── mhal_miu.c

│ ├── infinity6e

│ │ ├── mdrv_miu.c

│ │ └── mhal_miu.c

│ ├── Kconfig

│ ├── Makefile

│ ├── mdrv-miu.o

│ ├── modules.builtin

│ ├── modules.order

│ └── MsTypes.h

├── mma_heap

│ ├── built-in.o

│ ├── Kconfig

│ ├── Makefile

│ ├── mdrv_mma_heap.c

│ ├── mdrv_mma_heap.o

│ ├── mdrv-mma_heap.o

│ ├── modules.builtin

│ ├── modules.order

│ ├── region_substract.c

│ └── region_substract.o

├── modules.builtin

├── modules.order

├── movedma

│ ├── built-in.o

│ ├── hal_movedma.c

│ ├── hal_movedma.h

│ ├── hal_movedma.o

│ ├── Kconfig

│ ├── kernel_movedma.h

│ ├── Makefile

│ ├── modules.builtin

│ └── modules.order

├── msys

│ ├── arm.include

│ ├── built-in.o

│ ├── infinity2

│ │ └── platform_msys.c

│ ├── infinity2m

│ │ ├── platform_msys.c

│ │ └── platform_msys.o

│ ├── infinity5

│ │ └── platform_msys.c

│ ├── infinity6

│ │ └── platform_msys.c

│ ├── infinity6b0

│ │ └── platform_msys.c

│ ├── infinity6e

│ │ └── platform_msys.c

│ ├── Kconfig

│ ├── macro.include

│ ├── Makefile

│ ├── memcpy.S

│ ├── miu_monitor.c

│ ├── modules.builtin

│ ├── modules.order

│ ├── ms_msys.c

│ ├── ms_msys_dma_wrapper.c

│ ├── ms_msys_dma_wrapper.o

│ ├── ms_msys_irq_stat.c

│ ├── ms_msys_irq_stat.o

│ ├── ms_msys_log.c

│ ├── ms_msys_memory_bench.c

│ ├── ms_msys_miu_protect.c

│ ├── ms_msys.o

│ ├── ms_msys_perf_test.c

│ └── platform_msys.h

├── netphy

│ ├── built-in.o

│ ├── Kconfig

│ ├── Makefile

│ ├── modules.builtin

│ ├── modules.order

│ ├── sstar_100_phy.c

│ └── sstar_100_phy.o

├── noe

│ ├── drv

│ │ ├── eth

│ │ │ ├── Kconfig

│ │ │ ├── Makefile

│ │ │ ├── mdrv_noe.c

│ │ │ ├── mdrv_noe_config.h

│ │ │ ├── mdrv_noe_def.h

│ │ │ ├── mdrv_noe_dma.h

│ │ │ ├── mdrv_noe_ethtool.c

│ │ │ ├── mdrv_noe_ethtool.h

│ │ │ ├── mdrv_noe.h

│ │ │ ├── mdrv_noe_ioctl.h

│ │ │ ├── mdrv_noe_log.c

│ │ │ ├── mdrv_noe_log.h

│ │ │ ├── mdrv_noe_lro.c

│ │ │ ├── mdrv_noe_lro.h

│ │ │ ├── mdrv_noe_lro_proc.c

│ │ │ ├── mdrv_noe_mac.c

│ │ │ ├── mdrv_noe_mac.h

│ │ │ ├── mdrv_noe_nat.h

│ │ │ ├── mdrv_noe_pdma.c

│ │ │ ├── mdrv_noe_phy.c

│ │ │ ├── mdrv_noe_phy.h

│ │ │ ├── mdrv_noe_proc.c

│ │ │ ├── mdrv_noe_proc.h

│ │ │ ├── mdrv_noe_qdma.c

│ │ │ ├── mdrv_noe_utils.c

│ │ │ └── mdrv_noe_utils.h

│ │ └── nat

│ │ ├── hook

│ │ │ ├── Makefile

│ │ │ └── mdrv_hook.c

│ │ └── hw_nat

│ │ ├── Kconfig

│ │ ├── Makefile

│ │ ├── mdrv_hwnat_api.c

│ │ ├── mdrv_hwnat_api.h

│ │ ├── mdrv_hwnat.c

│ │ ├── mdrv_hwnat_config.h

│ │ ├── mdrv_hwnat_define.h

│ │ ├── mdrv_hwnat_fast_path.h

│ │ ├── mdrv_hwnat_foe.c

│ │ ├── mdrv_hwnat_foe.h

│ │ ├── mdrv_hwnat.h

│ │ ├── mdrv_hwnat_ioctl.c

│ │ ├── mdrv_hwnat_ioctl.h

│ │ ├── mdrv_hwnat_log.c

│ │ ├── mdrv_hwnat_log.h

│ │ ├── mdrv_hwnat_mcast.c

│ │ ├── mdrv_hwnat_mcast.h

│ │ ├── mdrv_hwnat_util.c

│ │ └── mdrv_hwnat_util.h

│ ├── hal

│ │ └── infinity2

│ │ ├── mhal_hwnat.c

│ │ ├── mhal_hwnat_cfg.h

│ │ ├── mhal_hwnat_entry.h

│ │ ├── mhal_hwnat.h

│ │ ├── mhal_noe.c

│ │ ├── mhal_noe.c.an

│ │ ├── mhal_noe_dma.h

│ │ ├── mhal_noe.h

│ │ ├── mhal_noe_lro.h

│ │ ├── mhal_noe_reg.h

│ │ └── mhal_porting.h

│ ├── Kconfig

│ └── Makefile

├── notify

│ ├── Kconfig

│ ├── Makefile

│ └── ms_notify.c

├── padmux

│ ├── built-in.o

│ ├── Kconfig

│ ├── Makefile

│ ├── mdrv_padmux.c

│ ├── mdrv_padmux.o

│ ├── modules.builtin

│ └── modules.order

├── pwm

│ ├── infinity

│ │ ├── mhal_pwm.c

│ │ └── mhal_pwm.h

│ ├── infinity2

│ │ ├── mhal_pwm.c

│ │ └── mhal_pwm.h

│ ├── infinity2m

│ │ ├── mhal_pwm.c

│ │ └── mhal_pwm.h

│ ├── infinity3

│ │ ├── mhal_pwm.c

│ │ └── mhal_pwm.h

│ ├── infinity5

│ │ ├── mhal_pwm.c

│ │ └── mhal_pwm.h

│ ├── infinity6

│ │ ├── mhal_pwm.c

│ │ └── mhal_pwm.h

│ ├── infinity6b0

│ │ ├── mhal_pwm.c

│ │ └── mhal_pwm.h

│ ├── infinity6e

│ │ ├── mhal_pwm.c

│ │ └── mhal_pwm.h

│ ├── Kconfig

│ ├── Makefile

│ └── mdrv_pwm.c

├── rebootstate

│ ├── Kconfig

│ ├── Makefile

│ └── reboot_state.c

├── rtc

│ ├── Kconfig

│ ├── Makefile

│ ├── ms_rtc.c

│ ├── ms_rtcpwc.c

│ └── reg

│ └── reg_rtcpwc.h

├── samples

│ ├── ajtc.c

│ ├── ajts.c

│ ├── build_riu.sh

│ ├── dmem.c

│ ├── README

│ ├── regio.c

│ ├── regio.png

│ ├── riu.c

│ ├── unametest.c

│ └── us_ticks.c

├── sar

│ ├── Kconfig

│ ├── Makefile

│ ├── mdrv_sar.c

│ └── mdrv_sar.h

├── sata_host

│ ├── bench

│ │ ├── Makefile

│ │ └── sata_bench.c

│ ├── bench_test

│ │ ├── drv

│ │ │ ├── mhal_sata_bench_test.c

│ │ │ └── mhal_sata_bench_test.h

│ │ ├── include

│ │ │ ├── mdrv_sata_io.h

│ │ │ └── mdrv_sata_io_st.h

│ │ ├── Makefile

│ │ ├── mdrv_sata.h

│ │ ├── mdrv_sata_io.c

│ │ └── verify

│ │ ├── Makefile

│ │ ├── sata_test

│ │ ├── sata_test.c

│ │ └── sata_test.h

│ ├── built-in.o

│ ├── infinity2

│ │ ├── mhal_sata_host_ahci.c

│ │ ├── mhal_sata_host_ahci.h

│ │ ├── mhal_sata_host.c

│ │ └── mhal_sata_host.h

│ ├── infinity2m

│ │ ├── mhal_sata_host_ahci.c

│ │ ├── mhal_sata_host_ahci.h

│ │ ├── mhal_sata_host_ahci.o

│ │ ├── mhal_sata_host.c

│ │ ├── mhal_sata_host.h

│ │ └── mhal_sata_host.o

│ ├── Kconfig

│ ├── Makefile

│ ├── mdr_sata_host_ahci_platform1.c

│ ├── mdr_sata_host_ahci_platform.c

│ ├── mdr_sata_host_ahci_platform.o

│ ├── mdrv_sata_host1.c

│ ├── mdrv_sata_host_ahci1.c

│ ├── mdrv_sata_host_ahci.c

│ ├── mdrv_sata_host_ahci.h

│ ├── mdrv_sata_host.c

│ ├── mdrv_sata_host.h

│ ├── mdrv-sata-host.ko

│ ├── mdrv-sata-host.mod.c

│ ├── mdrv-sata-host.mod.o

│ ├── mdrv-sata-host.o

│ ├── modules.builtin

│ └── modules.order

├── sdmmc

│ ├── built-in.o

│ ├── inc

│ │ ├── hal_card_base.h

│ │ ├── hal_card_intr_v5.h

│ │ ├── hal_card_platform.h

│ │ ├── hal_card_regs.h

│ │ ├── hal_card_regs_v5.h

│ │ ├── hal_card_timer.h

│ │ ├── hal_sdmmc_v5.h

│ │ ├── infinity2m

│ │ │ ├── hal_card_platform_config.h

│ │ │ ├── hal_card_platform_pri_config.h

│ │ │ └── hal_card_platform_regs.h

│ │ ├── infinity5

│ │ │ ├── hal_card_platform_config.h

│ │ │ ├── hal_card_platform_pri_config.h

│ │ │ └── hal_card_platform_regs.h

│ │ ├── infinity6

│ │ │ ├── hal_card_platform_config.h

│ │ │ ├── hal_card_platform_pri_config.h

│ │ │ └── hal_card_platform_regs.h

│ │ ├── infinity6b0

│ │ │ ├── hal_card_platform_config.h

│ │ │ ├── hal_card_platform_pri_config.h

│ │ │ └── hal_card_platform_regs.h

│ │ ├── infinity6e

│ │ │ ├── hal_card_platform_config.h

│ │ │ ├── hal_card_platform_pri_config.h

│ │ │ └── hal_card_platform_regs.h

│ │ └── ms_sdmmc_lnx.h

│ ├── Kconfig

│ ├── kdrv_sdmmc.o

│ ├── Makefile

│ ├── modules.builtin

│ ├── modules.order

│ ├── ms_sdmmc_lnx.c

│ ├── ms_sdmmc_lnx.o

│ └── src

│ ├── hal_card_intr_v5.c

│ ├── hal_card_intr_v5.o

│ ├── hal_card_regs.c

│ ├── hal_card_regs.o

│ ├── hal_card_timer.c

│ ├── hal_card_timer.o

│ ├── hal_sdmmc_v5.c

│ ├── hal_sdmmc_v5.o

│ ├── infinity2m

│ │ ├── hal_card_platform.c

│ │ └── hal_card_platform.o

│ ├── infinity5

│ │ └── hal_card_platform.c

│ ├── infinity6

│ │ └── hal_card_platform.c

│ ├── infinity6b0

│ │ └── hal_card_platform.c

│ └── infinity6e

│ └── hal_card_platform.c

├── serial

│ ├── built-in.o

│ ├── infinity2

│ │ ├── ms_uart.h

│ │ └── uart_pads.c

│ ├── infinity2m

│ │ ├── ms_uart.h

│ │ ├── uart_pads.c

│ │ └── uart_pads.o

│ ├── infinity3e

│ │ ├── ms_uart.h

│ │ └── uart_pads.c

│ ├── infinity5

│ │ ├── ms_uart.h

│ │ └── uart_pads.c

│ ├── infinity6

│ │ ├── ms_uart.h

│ │ └── uart_pads.c

│ ├── infinity6b0

│ │ ├── ms_uart.h

│ │ └── uart_pads.c

│ ├── infinity6e

│ │ ├── ms_uart.h

│ │ └── uart_pads.c

│ ├── Kconfig

│ ├── Makefile

│ ├── modules.builtin

│ ├── modules.order

│ ├── ms_uart.c

│ └── ms_uart.o

├── spi

│ ├── infinity2

│ │ ├── Makefile

│ │ ├── mdrv_spi.c

│ │ └── mdrv_spi.h

│ ├── infinity2m

│ │ ├── Makefile

│ │ └── mspi.c

│ ├── infinity3

│ │ ├── Makefile

│ │ └── mspi.c

│ ├── infinity5

│ │ ├── Makefile

│ │ └── mspi.c

│ ├── infinity6

│ │ ├── Makefile

│ │ └── mspi.c

│ ├── infinity6b0

│ │ ├── Makefile

│ │ └── mspi.c

│ ├── infinity6e

│ │ ├── Makefile

│ │ └── mspi.c

│ ├── Kconfig

│ └── Makefile

├── spinand

│ ├── built-in.o

│ ├── drv

│ │ ├── inc

│ │ │ ├── mdrv_spinand_command.h

│ │ │ └── mdrv_spinand_common.h

│ │ ├── mdrv_spinand.c

│ │ ├── mdrv_spinand.h

│ │ ├── mdrv_spinand_hal.c

│ │ ├── mdrv_spinand_hal.h

│ │ ├── mdrv_spinand_hal.o

│ │ └── mdrv_spinand.o

│ ├── hal

│ │ ├── infinity2

│ │ │ ├── mhal_spinand.c

│ │ │ ├── mhal_spinand_chip_config.c

│ │ │ ├── mhal_spinand.h

│ │ │ └── reg_spinand.h

│ │ ├── infinity2m

│ │ │ ├── mhal_spinand_chip_config.c

│ │ │ ├── mhal_spinand_chip_config.o

│ │ │ ├── mhal_spinand.h

│ │ │ └── reg_spinand.h

│ │ ├── infinity3

│ │ │ ├── mhal_spinand_chip_config.c

│ │ │ ├── mhal_spinand.h

│ │ │ └── reg_spinand.h

│ │ ├── infinity5

│ │ │ ├── mhal_spinand_chip_config.c

│ │ │ ├── mhal_spinand.h

│ │ │ └── reg_spinand.h

│ │ ├── infinity6

│ │ │ ├── mhal_spinand_chip_config.c

│ │ │ ├── mhal_spinand.h

│ │ │ └── reg_spinand.h

│ │ ├── infinity6b0

│ │ │ ├── mhal_spinand_chip_config.c

│ │ │ ├── mhal_spinand.h

│ │ │ └── reg_spinand.h

│ │ ├── infinity6e

│ │ │ ├── mhal_spinand_chip_config.c

│ │ │ ├── mhal_spinand.h

│ │ │ └── reg_spinand.h

│ │ ├── mhal_spinand.c

│ │ └── mhal_spinand.o

│ ├── Kconfig

│ ├── kdrv_spinand.o

│ ├── Makefile

│ ├── modules.builtin

│ └── modules.order

├── usb

│ ├── gadget

│ │ └── udc

│ │ └── usb20

│ │ ├── include

│ │ │ ├── infinity5

│ │ │ │ └── msb250x_udc_common.h

│ │ │ ├── infinity6

│ │ │ │ └── msb250x_udc_common.h

│ │ │ ├── infinity6b0

│ │ │ │ └── msb250x_udc_common.h

│ │ │ ├── infinity6e

│ │ │ │ └── msb250x_udc_common.h

│ │ │ ├── msb250x_dma.h

│ │ │ ├── msb250x_ep.h

│ │ │ ├── msb250x_gadget.h

│ │ │ ├── msb250x_udc.h

│ │ │ └── msb250x_udc_reg.h

│ │ ├── Kconfig

│ │ ├── Makefile

│ │ └── src

│ │ ├── msb250x_dma.c

│ │ ├── msb250x_ep.c

│ │ ├── msb250x_gadget.c

│ │ └── msb250x_udc.c

│ ├── host

│ │ ├── bc-mstar.c

│ │ ├── bc-mstar.h

│ │ ├── bc-mstar.o

│ │ ├── built-in.o

│ │ ├── ehci-mstar.c

│ │ ├── ehci-mstar.h

│ │ ├── infinity2

│ │ │ ├── ehci-mstar-chip.h

│ │ │ ├── Makefile

│ │ │ ├── usb_pad.c

│ │ │ ├── usb_pad.h

│ │ │ └── usb_patch_mstar.h

│ │ ├── infinity2m

│ │ │ ├── built-in.o

│ │ │ ├── ehci-mstar-chip.h

│ │ │ ├── Makefile

│ │ │ ├── modules.builtin

│ │ │ ├── modules.order

│ │ │ ├── usb_pad.c

│ │ │ ├── usb_pad.h

│ │ │ ├── usb_pad.o

│ │ │ └── usb_patch_mstar.h

│ │ ├── infinity3

│ │ │ ├── Makefile

│ │ │ └── ms_usb.c

│ │ ├── infinity5

│ │ │ ├── ehci-mstar-chip.h

│ │ │ ├── Makefile

│ │ │ ├── usb_pad.c