- 首页

- » 搜索

- » echo 发表的帖子

#1 Re: Xilinx/Altera/FPGA/CPLD/Verilog » AG RV2K 调试 » 2025-12-10 10:19:33

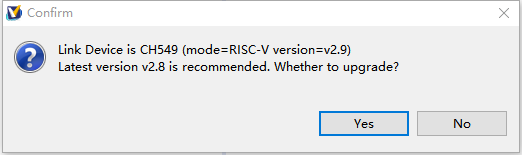

AGRV2K的这个HSI精度太低了,官方手册说的额是校准后5%。校准似乎是根据调试工具的CLK时钟,大部分CMSIS-DAP的CLK时钟是软件实现,根本就不准,我实测1M出来690k,误差超过30%。

用最新的2025.11版本的Supra可以用HSE作为时钟输入了,时钟精度很高。不过尝试用HSE作为PLL输入失败了。

手册上说:PLL 输入时钟管脚要选 IO_GB 管脚,即全局时钟管脚。否则编译会出错,无法布线到 PLL 输入信号。如果HSE不能作为PLL输入那么可用性会大打折扣。

这个AGRV2K芯片内部RISC-V挺鸡肋的,完全不如WCH的RISC-V芯片好用,单纯做CPLD还有一些价值。能用无源晶振也比传统CPLD要好一些,要是PLL支持无源晶振时钟输入就更好了。

#2 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 发现个好玩的东东:Flash ID伪造器 这个原理简单,但TB上好像没得卖 » 2025-10-21 14:29:14

#3 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 发现个好玩的东东:Flash ID伪造器 这个原理简单,但TB上好像没得卖 » 2025-10-20 20:46:52

#4 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 发现个好玩的东东:Flash ID伪造器 这个原理简单,但TB上好像没得卖 » 2025-10-20 20:12:58

#5 Re: Xilinx/Altera/FPGA/CPLD/Verilog » 分享一个国产CPLD/FPGA芯片资料:AGM的AG1280Q48 » 2024-12-10 12:42:22

太湖飞人 说:这个芯片很好,但有一个缺点就是一种电压搞不定,也就是核电压和IO电压不一样

现在这个已经停产了,用AG32的CPLD模式——AGRV2K

https://whycan.com/files/members/14582/c390ad3c4f35964a6ab035da1e9a943.png

停产会给客户带来很多麻烦,ALTERA很多产品十几年甚至几十年都能买到。

#8 Re: 全志 SOC » 有没有tf卡座接口的sd芯片啊? » 2024-08-19 18:32:29

#9 Re: 全志 SOC » 有没有tf卡座接口的sd芯片啊? » 2024-08-18 22:24:22

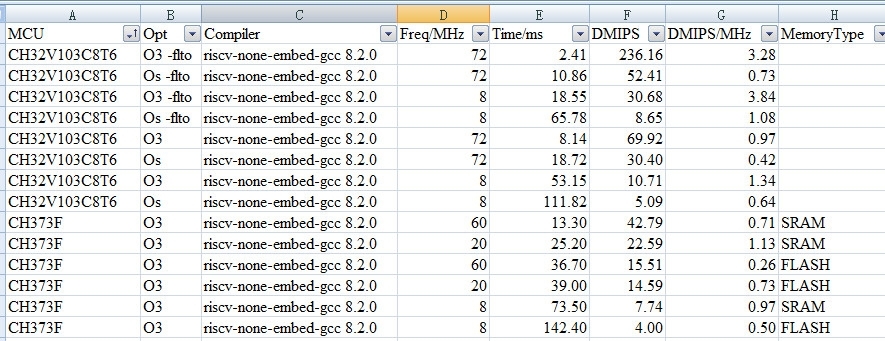

#10 Re: RISC-V » RISC-V代码密度相比Cortex-M差距明显 » 2024-05-21 10:36:41

#11 Re: RISC-V » RISC-V代码密度相比Cortex-M差距明显 » 2024-05-21 10:35:35

#16 Re: RK3288/RK3399/RK1108 » 为什么瑞芯微公开资料这么少呢 » 2024-03-26 14:26:14

#17 Re: RK3288/RK3399/RK1108 » 为什么瑞芯微公开资料这么少呢 » 2024-03-26 14:23:05

#18 Re: RK3288/RK3399/RK1108 » 为什么瑞芯微公开资料这么少呢 » 2024-03-26 10:20:22

#19 Re: 易百纳技术社区 » 【易百纳】电梯物联网之梯控相机方案-防止电瓶车进电梯 » 2024-02-26 17:01:47

#21 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片 » 2024-02-23 22:11:33

#22 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片 » 2024-02-23 17:10:07

#23 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片 » 2024-02-21 11:14:13

#25 Re: 全志 SOC » 坛友们请问非常便宜的具有唯一ID的FLASH芯片有什么推荐? » 2024-01-23 14:27:34

#26 Re: 全志 SOC » 这个电路好魔幻, 是如何工作的? » 2024-01-21 10:55:58

#29 Re: RK3288/RK3399/RK1108 » 为什么瑞芯微公开资料这么少呢 » 2024-01-10 14:51:18

#31 Re: RK3288/RK3399/RK1108 » 为什么瑞芯微公开资料这么少呢 » 2024-01-10 08:28:24

@echo

厂家和开发者是合作关系,互相依赖互相获益。你这说法满满的对立关系啊,这样的厂家恐怕真不应该活着

你这话没问题,但是有个前提,必须是合格的开发者,起码应该看过datasheet和usermanual,会用搜索引擎搜索问题。即使提问,也不应该问已有文档上的内容。事实上这个行业充满了新手、小白,伸手党,半桶水,他们会把datasheet上的已经写了的问题一个个问你,把你搞到崩溃,别问我怎么知道的。

合格的开发者可能连10%都没有,这里面大多数还是在公司上班的,可以拿到厂家的技术支持。合格的个人开发者可能连2%都没有。

所以厂家选择不公开资料虽然合格的个人开发者觉得不爽,但是从厂家的角度来考虑完全可以理解。

#32 Re: RK3288/RK3399/RK1108 » 为什么瑞芯微公开资料这么少呢 » 2024-01-10 08:17:00

#33 Re: RK3288/RK3399/RK1108 » 为什么瑞芯微公开资料这么少呢 » 2024-01-10 08:14:41

#34 Re: RK3288/RK3399/RK1108 » 为什么瑞芯微公开资料这么少呢 » 2024-01-10 08:10:35

#35 Re: RK3288/RK3399/RK1108 » 为什么瑞芯微公开资料这么少呢 » 2024-01-09 16:47:26

#36 Re: RK3288/RK3399/RK1108 » 为什么瑞芯微公开资料这么少呢 » 2024-01-09 16:44:34

#37 Re: RK3288/RK3399/RK1108 » 为什么瑞芯微公开资料这么少呢 » 2024-01-09 16:40:34

#39 Re: RK3288/RK3399/RK1108 » 为什么瑞芯微公开资料这么少呢 » 2024-01-07 12:26:25

#40 Re: RK3288/RK3399/RK1108 » 为什么瑞芯微公开资料这么少呢 » 2024-01-07 12:20:41

#41 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 下载了一些开源飞控源码看,为何用freertos的这么少。 » 2023-12-25 10:39:25

@echo

少在那误导了。

https://baike.baidu.com/item/Rtems/6985412

https://baike.baidu.com/item/vxworks?fromModule=lemma_search-box

看看哪个不是用在可靠性极高的地方。

你自己多踩一些坑就明白了

#42 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 下载了一些开源飞控源码看,为何用freertos的这么少。 » 2023-12-22 21:41:22

#43 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 花了小半天 搭了个全新版本 eclipse + gcc ... » 2023-12-22 15:35:34

#45 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 下载了一些开源飞控源码看,为何用freertos的这么少。 » 2023-12-16 10:28:36

#46 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 下载了一些开源飞控源码看,为何用freertos的这么少。 » 2023-12-15 17:43:40

#47 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 是时候告别CSDN了! » 2023-11-22 08:08:39

#50 Re: RK3288/RK3399/RK1108 » 为什么瑞芯微公开资料这么少呢 » 2023-10-17 10:20:28

#52 Re: RK3288/RK3399/RK1108 » 为什么瑞芯微公开资料这么少呢 » 2023-10-12 16:47:46

#54 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 是时候告别CSDN了! » 2023-09-03 19:45:37

#55 Re: Cortex M0/M3/M4/M7 » 国产M7来了,分享datasheet » 2023-08-16 10:33:35

#56 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 正点原子出逻辑分析仪了,,和DSLogic一样,也是基于 sigrok 开源解码方案。。 » 2023-07-21 22:07:47

#61 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 不要买淘宝上面10元以下的FT232/PL2303 USB转TTL串口线,不要买,不要买,不要买!!! » 2023-06-15 10:32:54

#63 Re: Cortex M0/M3/M4/M7 » 国产M7来了,分享datasheet » 2023-05-12 11:20:35

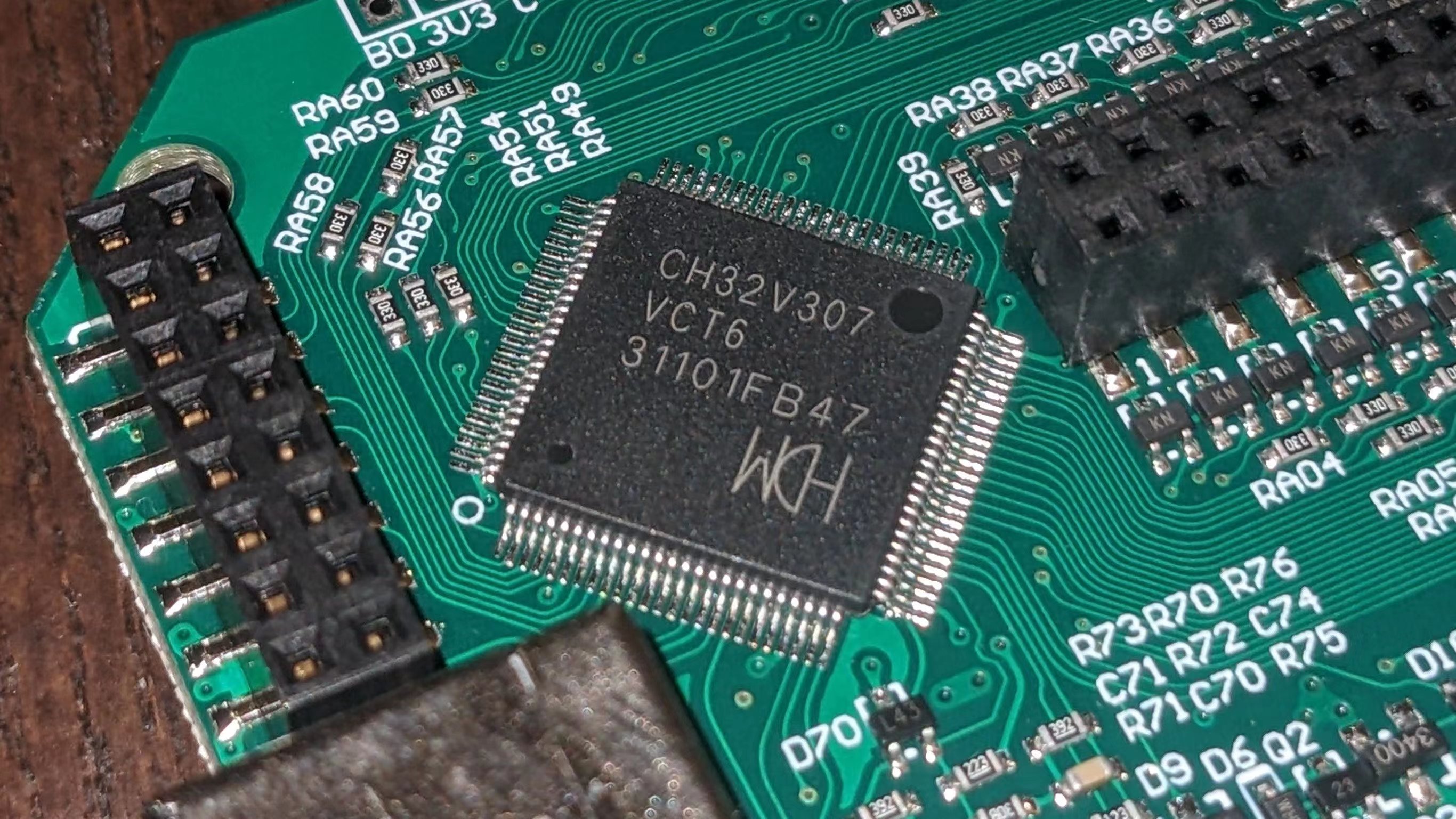

USBHS 集成了 HS PHY,,牛啊,,这点比 STM32H7 强多了

还好吧,CH32V307早都支持了

#64 Re: Cortex M0/M3/M4/M7 » 国产M7来了,分享datasheet » 2023-05-12 11:19:47

也不知道 CAN CAN_STAT RS 问题 修了没

参考:

https://zhuanlan.zhihu.com/p/453181148

https://bbs.21ic.com/icview-3190724-1-1.html

你这两个链接,都是我的文章

#65 Cortex M0/M3/M4/M7 » 国产M7来了,分享datasheet » 2023-05-11 18:28:28

- echo

- 回复: 15

兆易创新推出GD32H737/757/759系列Cortex®-M7内核超高性能MCU

中国北京(2023年5月11日)——业界领先的半导体器件供应商兆易创新GigaDevice (股票代码 603986) 今日宣布,正式推出中国首款基于Arm® Cortex®-M7内核的GD32H737/757/759系列超高性能微控制器。

GD32H7系列MCU具备卓越的处理能效、丰富连接特性及多重安全机制,以先进工艺制程和优化的成本控制,全面释放高级应用的创新潜力。全新产品组合包括3个系列共27个型号,提供176脚和100脚BGA封装,176脚、144脚和100脚LQFP封装等五种选择,将于5月底陆续开放样片和开发板卡申请,10月起正式量产供货。

GD32H7可广泛用于数字信号处理、电机变频、电源、储能系统、无人机、音频视频、图形图像等各类应用。得益于超高主频以及大存储容量,该系列MCU也适用于机器学习和人工智能等诸多高端创新场景。

GD32H759xx_Datasheet_Rev1.0.pdf

GD32H737xx_Datasheet_Rev1.0.pdf

#66 Re: Cortex M0/M3/M4/M7 » 求推荐宽供电范围,而且带USB的单片机 » 2023-05-01 21:03:01

#69 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 怒开新坑,自制低成本高速USB分析仪(随缘更新) » 2023-03-22 12:11:13

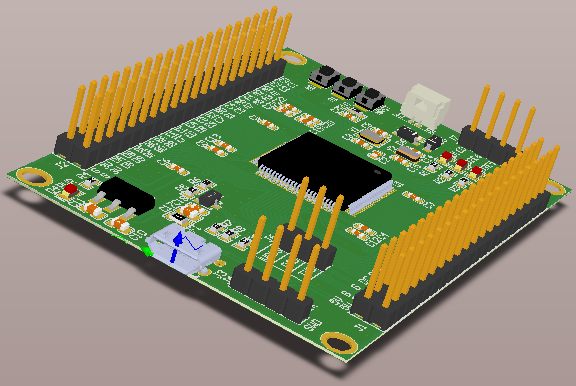

趁下班时间画了一版,大家猜猜这是什么方案😏

https://whycan.com/files/members/1510/AQUA-Lite.png

为啥你们都喜欢用TypeC,USB2.0 HS也只需要D+D-两个信号,MicroUSB足够了,TypeC多出来一堆无用管脚,焊接麻烦,体积还大。

#70 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 【新玩具get】AGM AGRV2K,16.8块钱的MCU+FPGA二合一芯片 » 2023-03-16 14:37:13

#71 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 怒开新坑,自制低成本高速USB分析仪(随缘更新) » 2023-03-09 07:58:50

#72 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 怒开新坑,自制低成本高速USB分析仪(随缘更新) » 2023-03-07 19:52:33

#73 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 怒开新坑,自制低成本高速USB分析仪(随缘更新) » 2023-03-07 08:16:47

#79 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 怒开新坑,自制低成本高速USB分析仪(随缘更新) » 2023-02-28 19:44:54

#81 Re: RISC-V » CH32V系列非0等待区使用及简陋的性能测试 » 2023-01-31 22:48:55

#83 Re: RISC-V » RISC-V不支持非对齐地址访问非常坑 » 2023-01-05 22:43:54

#84 Re: RISC-V » RISC-V不支持非对齐地址访问非常坑 » 2023-01-05 18:41:20

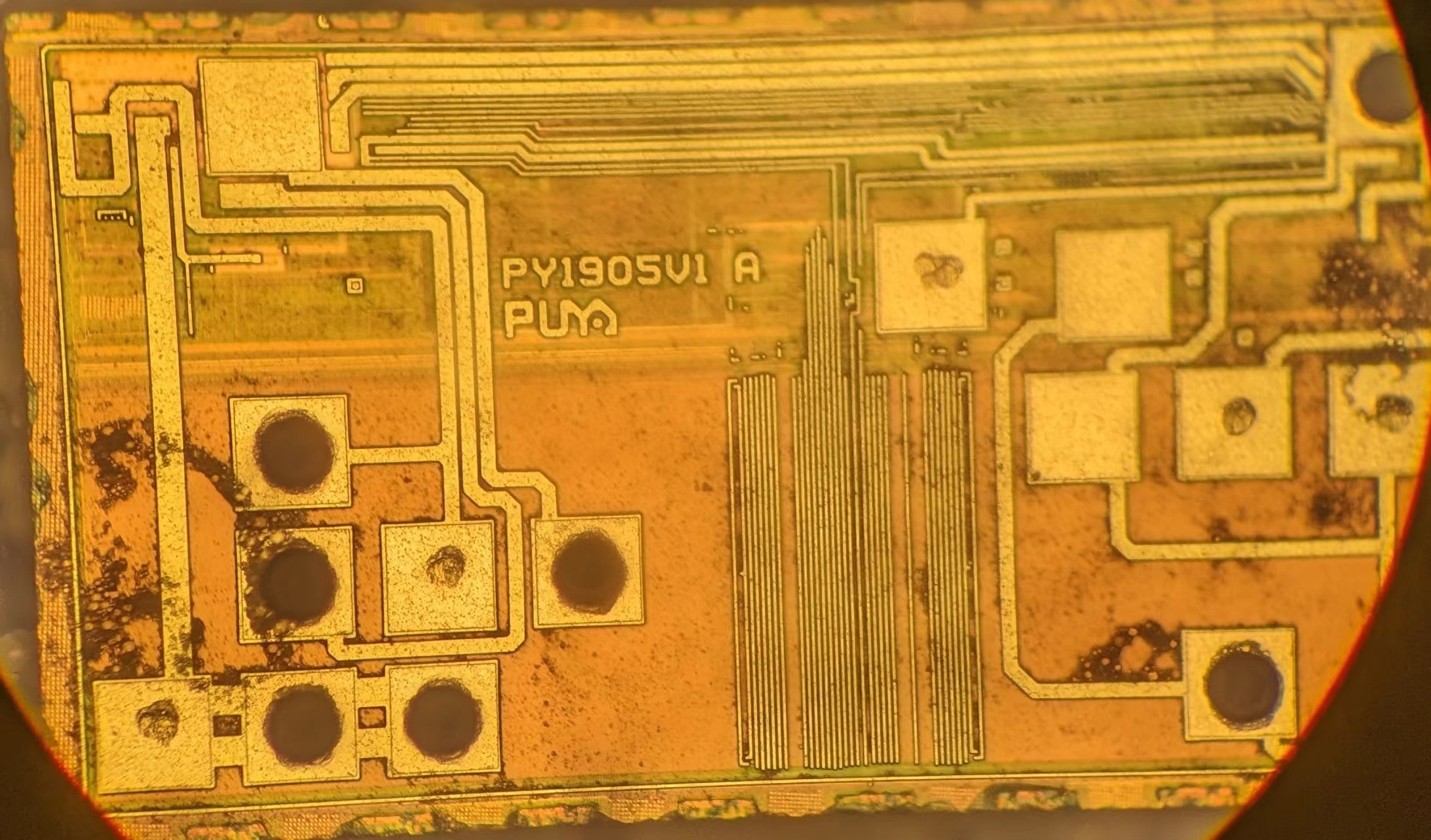

#97 Re: RISC-V » CH32V307内置SPI FLASH来自普冉 » 2022-11-16 10:49:12

补充一下,普冉的这个FLASH技术叫做SONOS,来自Cypress,和华邦兆易他们的不一样。下面是两篇介绍文章:

#98 Re: RISC-V » CH32V307内置SPI FLASH来自普冉 » 2022-11-14 09:32:55

@海石生风

普冉的这个FLASH烧录按页来编程,速度很快。像传统的STM32那样4字节编程速度就慢很多了。为此我专门重写了自己的固件升级算法。以下是一些朋友提供的消息,真假自辩,感觉没啥问题。

Puya用了一种新的工艺,和传统的NorFlash不同,cypress授权的,国内很多Flash小厂在用。

erase时间短,program时间长,page program的时间应该是2ms,小于一个page的,比如写

1个字节,时间也是2ms。

仔细看手册你会发现WCH的MCU内置FLASH都提供快速编程功能,就是页编程,和PY32的内置闪存一样,PY32甚至手册上只提到支持页编程。

#100 Re: RISC-V » RISC-V核心的SoC有没有已经在产品上广泛使用的型号? » 2022-11-08 14:11:21

#101 Re: RISC-V » RISC-V核心的SoC有没有已经在产品上广泛使用的型号? » 2022-11-08 08:42:11

#102 RISC-V » GCC 12把CSR相关指令放到扩展Zicsr中了 » 2022-11-08 08:39:44

- echo

- 回复: 1

用GCC 12的时候提示找不到csrrw这些指令,查了下,原来20191213版本的spec把csr相关指令放到Zicsr扩展中了。原文如下:

While CSRs are primarily used by the privileged architecture, there are several uses in unprivi-

leged code including for counters and timers, and for floating-point status.

The counters and timers are no longer considered mandatory parts of the standard base

ISAs, and so the CSR instructions required to access them have been moved out of the base ISA

chapter into this separate chapter.

问题是,CSR中不光有计数器和定时器呀,还有别的寄存器,比如mstatus、mepc、mcause、mtvec等等,这些寄存器都是必不可少的。

扩展的意思是可以不用,难道不用Zicsr指令能构建一颗能用的MCU?退一步来说即使是定时器和计数器作为强制部分也没什么不妥,隔壁ARM的SysTick计数器也是核心的一部分。

RISC-V这个CSR感觉和51的SFR有点神似,标准定义访问这段空间的指令和一些通用的寄存器,厂家再根据自己的需要进行扩展,增加一些寄存器,但是访问这些寄存器的指令肯定是必不可少的,不太理解CSR访问指令为什么要作为扩展。大家怎么理解?

#105 Re: Cortex M0/M3/M4/M7 » 国产王炸中的战斗机-普冉py32f003/py32f030(价格6毛起步) » 2022-10-31 20:33:48

@echo

真的假的,8脚的无法恢复了吗?这设计有点...

avr的tiny13a可以任意使用io,并不影响isp下载

也能恢复,用户固件做个自杀功能就行了,比如开启读保护然后再解除读保护,固件就自杀了,闪存为空,默认启用SWD接口可以烧录。

我曾经SO-8的固件开启了读保护,没法解除,因为找不到他们那个PY-LINK,又没有BOOT0,没法用ISP工具,后来用我自己的GDLink手动解除了读保护。最后给固件做了自杀功能,就没有问题了。

CH32V003也有个坑,没有他们那个LinkE是没法烧录的,芯片为空片的时候,CH32V003并不会停在内置bootloader等待连接,而是跳转APP,导致没法使用ISP。因为没有boot0,ISP也依赖用户程序跳转到内置bootloader,我目前测试还有问题,跳转内置bootloader以后ISP工具没法连接,不知道是WCHISPTool 3.4的问题还是芯片的问题。

两颗芯片,感觉还是PY32F003更好一些,虽然价格稍微贵一些,但是存储容量大得多,能做的事情多的多,M0+比RV32EC好多了,后者连乘法器都没有,现在比较感兴趣的是CH32V003这个RV32EC核心面积能有多小。CH32V003内置的2+16k实在是太小了,要是能出4+32k的版本应用场合能多很多。

#108 Re: RISC-V » WCH又搞了个性价比王炸CH32V003 » 2022-10-30 14:47:31

手头的CH32V003盘完了,几个要注意的地方说一下:

中断向量表要对齐到1kB地址,如果要设计bootloader就要非常注意

这颗芯片只支持机器模式,虽然启动文件设置mstatus为0x80,但是实际运行以后读取mstatus为0x1888

不支持硬件乘法器,这一点就不如M0了

2+16kB的存储太有限了,只能做非常简单的任务

linkE调试器的单线调试模式挺好用,WCHISPTool暂时还没支持CH32V003

-flto选项可以大大减小代码体积,接近M0的LTO优化体积,不过开启-flto以后代码运行还是有问题,是gcc 8.2.0的问题,不知道WCH什么时候能更新gcc

附CH32V003的CSR列表:

marchid = 0xDC68D841

mimpid = 0xDC688001

mstatus = 0x00001888

misa = 0x40800014

mtvec = 0x08000003

mscratch = 0x00000000

mepc = 0x0800205C

mcause = 0x8000000C

mvendorid = 0x00000000

mhartid = 0x00000000还有几个样片,有想玩的朋友可以送一片,这颗芯片和STM8S003封装和电源脚位置都一样,直接把STM8S003拆了换上去就行。

由于邮费远大于芯片价值,所以从我这里买东西的朋友报whycan暗号可以送一片,淘宝或者闲鱼都可以。

#113 Re: RISC-V » WCH又搞了个性价比王炸CH32V003 » 2022-10-18 12:03:06

#114 Re: RISC-V » WCH又搞了个性价比王炸CH32V003 » 2022-10-15 14:15:10

#115 Re: RISC-V » WCH又搞了个性价比王炸CH32V003 » 2022-10-14 21:30:09

#117 Re: RISC-V » WCH又搞了个性价比王炸CH32V003 » 2022-10-13 17:05:11

#118 RISC-V » WCH又搞了个性价比王炸CH32V003 » 2022-10-13 09:47:59

- echo

- 回复: 28

国产的RISC-V还是得看WCH,这不又丢了个王炸出来CH32V003,介绍链接:

https://www.wch.cn/products/CH32V003.html

说它是王炸不是因为性能有多强,而是性价比爆炸,据说只要五毛钱,你没听错,是五毛钱,还是RMB,某些人发个帖子就能赚到一颗。

性能方面,核心是RISC-V最高48M,RV32EC指令集,性能就不指望了,只希望代码密度能表现好一点。

存储方面,2kB SRAM和16kB FLASH,闪存要是能到32kB使用范围能更广一些。

电源方面,支持3.3V和5V,简单的应用场合可以不用LDO了。

外设方面,1个10位ADC,1个运放,1个DMA,1个高级定时器,1个通用定时器,还是蛮全的。

通讯接口方面,USART、SPI、I2C各一个,接口挺全,数量都是1个。这个价格下USB和CAN这种复杂接口就不用奢望了。

调试接口方面,和STM8那个SWIM接口类似的串行单线。

封装方面提供了SO-8、SO-16、QFN-20、TSSOP-20四种封装,其中QFN-20封装为3x3mm,0.4mm间距,尺寸非常小。

竞品方面:

TSSOP-20对标STM8S003F3P6,N76E003AT20,复位、电源、调试这些管脚布局相同,可以直接P2P替换。

SOP-8对标STM8S001J3M3,电源脚布局完全一样,可以直接P2P替换,还去掉VCAP那个管脚多了个IO。

最后说一下开发工具,他们提供的那个MounRiver还是挺好用的,要是能把gcc赶紧升级一下就好了,目前的8.2.0还是有些问题。

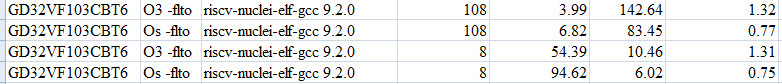

#119 Re: RISC-V » RISC-V代码密度相比Cortex-M差距明显 » 2022-10-11 14:40:04

#120 Re: RISC-V » RISC-V代码密度相比Cortex-M差距明显 » 2022-10-10 22:29:21

#123 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 沁恒ch565w测试 USB3.0速度和千兆以太网速度 » 2022-09-27 21:59:15

#131 Re: Xilinx/Altera/FPGA/CPLD/Verilog » 分享一个CH552可用的USB-Blaster固件 » 2022-08-14 17:22:58

清理了一下旧固件,放个最新的。

CH552_Blaster_v22.2.27.7z

偶尔用的话,用这个CH552版本的USB-Blaster就足够了。经常用的话建议买CH546或者CH571版本的USB-Blaster,速度要快得多。

#133 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » daplink的swclk信号为什么需要用到两个单片机管脚? » 2022-08-04 16:30:37

#134 Re: Xilinx/Altera/FPGA/CPLD/Verilog » 分享一个CH552可用的USB-Blaster固件 » 2022-07-29 11:03:21

:)用楼主的固件做了个迷你版的USB Blaster

https://whycan.com/files/members/3241/mmexport1656044754257.jpg

随便用个CH552开发板就可以

#135 Re: 全志 SOC » V3s这么强显示能力, 不搞个示波器可惜了,接什么ADC好呢? » 2022-07-20 21:36:52

#136 Re: 全志 SOC » V3s这么强显示能力, 不搞个示波器可惜了,接什么ADC好呢? » 2022-07-20 16:59:10

#137 Re: 全志 SOC » V3s这么强显示能力, 不搞个示波器可惜了,接什么ADC好呢? » 2022-07-20 16:43:30

#138 Re: 全志 SOC » V3s这么强显示能力, 不搞个示波器可惜了,接什么ADC好呢? » 2022-07-20 16:39:31

#139 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 众人拾柴-魔改SPI为一主多从高速总线【迪卡总线】 » 2022-07-17 19:39:18

#140 Re: 全志 SOC » V3s这么强显示能力, 不搞个示波器可惜了,接什么ADC好呢? » 2022-07-17 11:31:40

#141 Re: RISC-V » 基于CH32V307的高速USB转JTAG下载器 » 2022-07-17 10:08:44

@metro

这些10MB+的bitstream本来就是极少的场景。调试器上完全派不上用场。SignalTapII这类片上逻辑分析仪用USBFS也足够了,我用CH552做的USB-Blaster也可以胜任。这些调试器一边是USB,另外一边是JTAG或者SWD,也是单端串行时钟,并且要使用杜邦线或者排线连接,TCK时钟频率不可能太高,十几M最多几十M撑死了。频率越高兼容性可靠性越差,用户越容易骂娘。使用480M的USBHS完全就是大炮轰蚊子,没有任何必要。

另外TCK和SWCLK这边如果软件IO模拟时序,那速度完全不行,要喂饱USBFS必须硬件SPI+DMA来优化,这个还是有一定难度的,做得好的并不多。

高速USB的最佳应用是各种USB逻辑分析仪,这些设备对USBHS的带宽使用比较充分。

#142 Re: RISC-V » 基于CH32V307的高速USB转JTAG下载器 » 2022-07-16 22:12:59

#143 Re: RISC-V » 基于CH32V307的高速USB转JTAG下载器 » 2022-07-15 22:51:01

#144 Re: RISC-V » 基于CH32V307的高速USB转JTAG下载器 » 2022-07-15 17:24:48

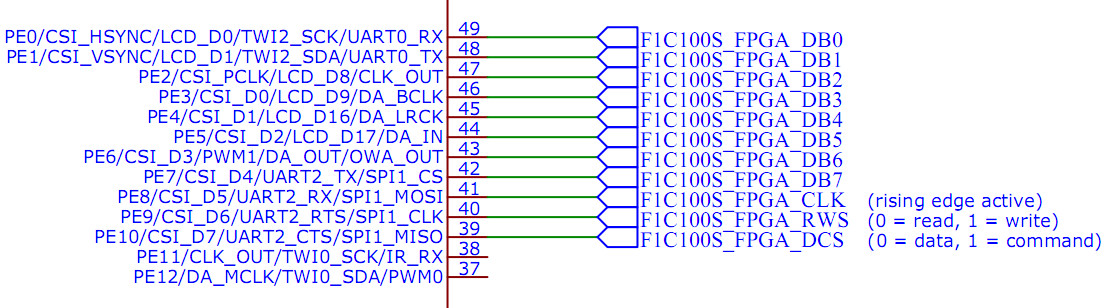

#151 Re: 全志 SOC » 发现一个有意思的东西,4.3寸触摸屏,用的F1C200S » 2022-04-28 19:15:21

#152 Re: 全志 SOC » 发现一个有意思的东西,4.3寸触摸屏,用的F1C200S » 2022-04-28 12:59:18

echo 说:@zhang235hai

我这里版本更新的3.3.3.5781不支持,奇怪得很。方便共享一下McgsPro 3.3.2.6187版本吗?

好大的附件,还是用网盘分享吧,给晕哥节省一点带宽费用。附件3.3.2.6187版本和更新的3.3.3.5781都在网盘中了。

链接: https://pan.baidu.com/s/1zw1reH_mrnzAA1aDxHDVrA?pwd=uuc2 提取码: uuc2

#153 Re: 全志 SOC » 发现一个有意思的东西,4.3寸触摸屏,用的F1C200S » 2022-04-28 10:47:35

#154 Re: 全志 SOC » 发现一个有意思的东西,4.3寸触摸屏,用的F1C200S » 2022-04-28 09:27:02

#155 Re: 全志 SOC » 发现一个有意思的东西,4.3寸触摸屏,用的F1C200S » 2022-04-27 20:55:58

#156 Re: 全志 SOC » 发现一个有意思的东西,4.3寸触摸屏,用的F1C200S » 2022-04-27 20:48:29

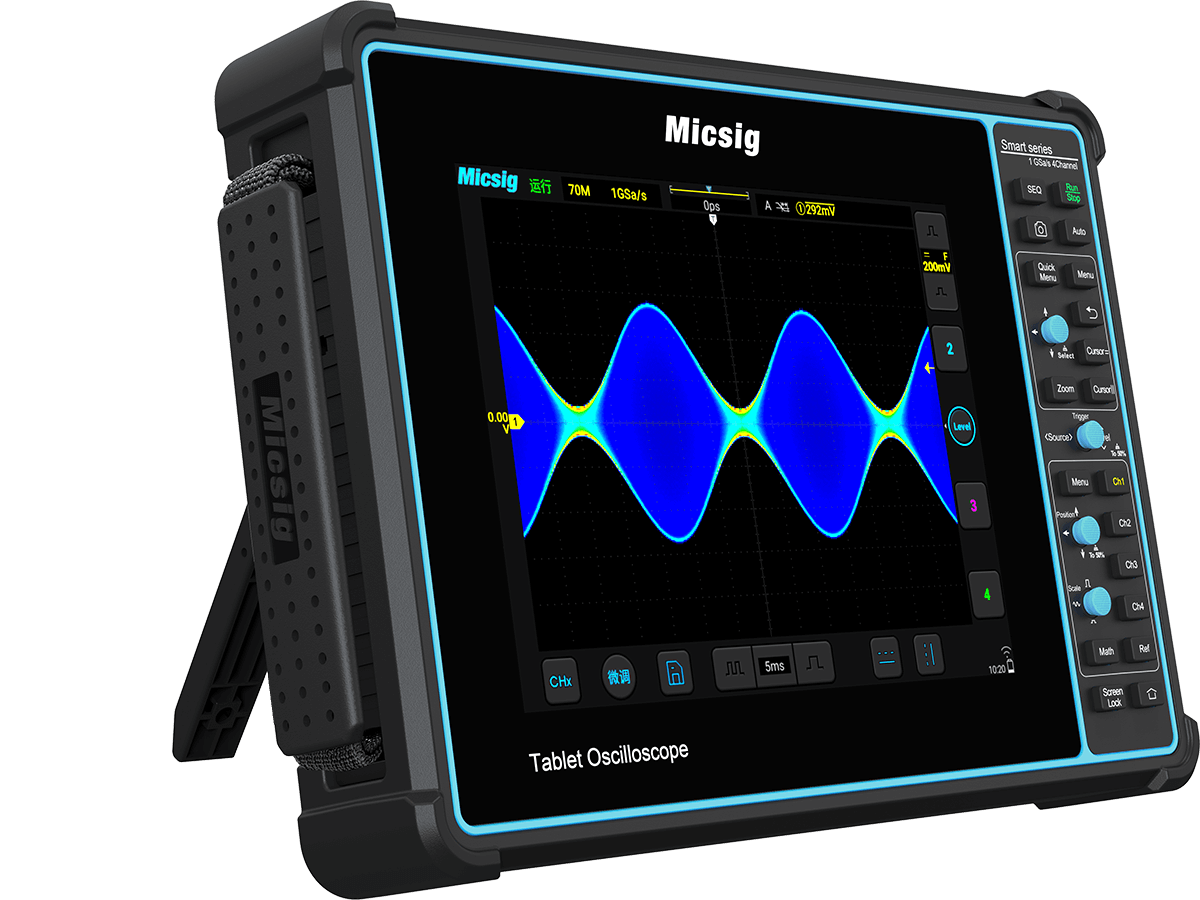

#159 RK3288/RK3399/RK1108 » Micsig的STO1004示波器使用了RK3568 » 2022-04-23 23:09:14

- echo

- 回复: 9

这款示波器,

https://www.micsig.com.cn/product5/

SoC用的是RK3568,4xA55@2.0G,这个4小核配置广泛用在目前的手机SoC上。

2GB DDR4内存,32GB eMMC,SOC+DDR4+eMMC在一片核心板上。

看RK3568发布时间也就一年而已,产品上市还挺快的。

#161 Re: 全志 SOC » 今天发现新全志芯片XR32F429 » 2022-04-03 07:51:31

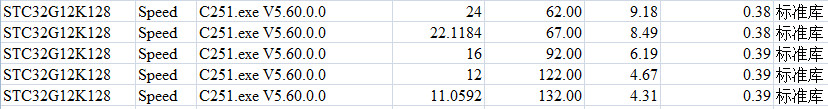

#167 Re: 8051/STC8/AT89C51/N76E003 » STC32G12K128的Dhrystone性能测试 » 2022-03-17 09:42:10

STC32G性能提升主要是内存架构优化带来的,在同样的22.1184M主频和速度优化时:

STC8G用时235ms,成绩0.109DMIPS/MHz

STC32G用时67ms,成绩0.384DMIPS/MHz,相对提升0.384/0.109=3.523倍

STC32G内存模型切换为Large后用时189ms,成绩0.136DMIPS/MHz,相对提升0.136/0.109=1.248倍

https://zhuanlan.zhihu.com/p/482337395

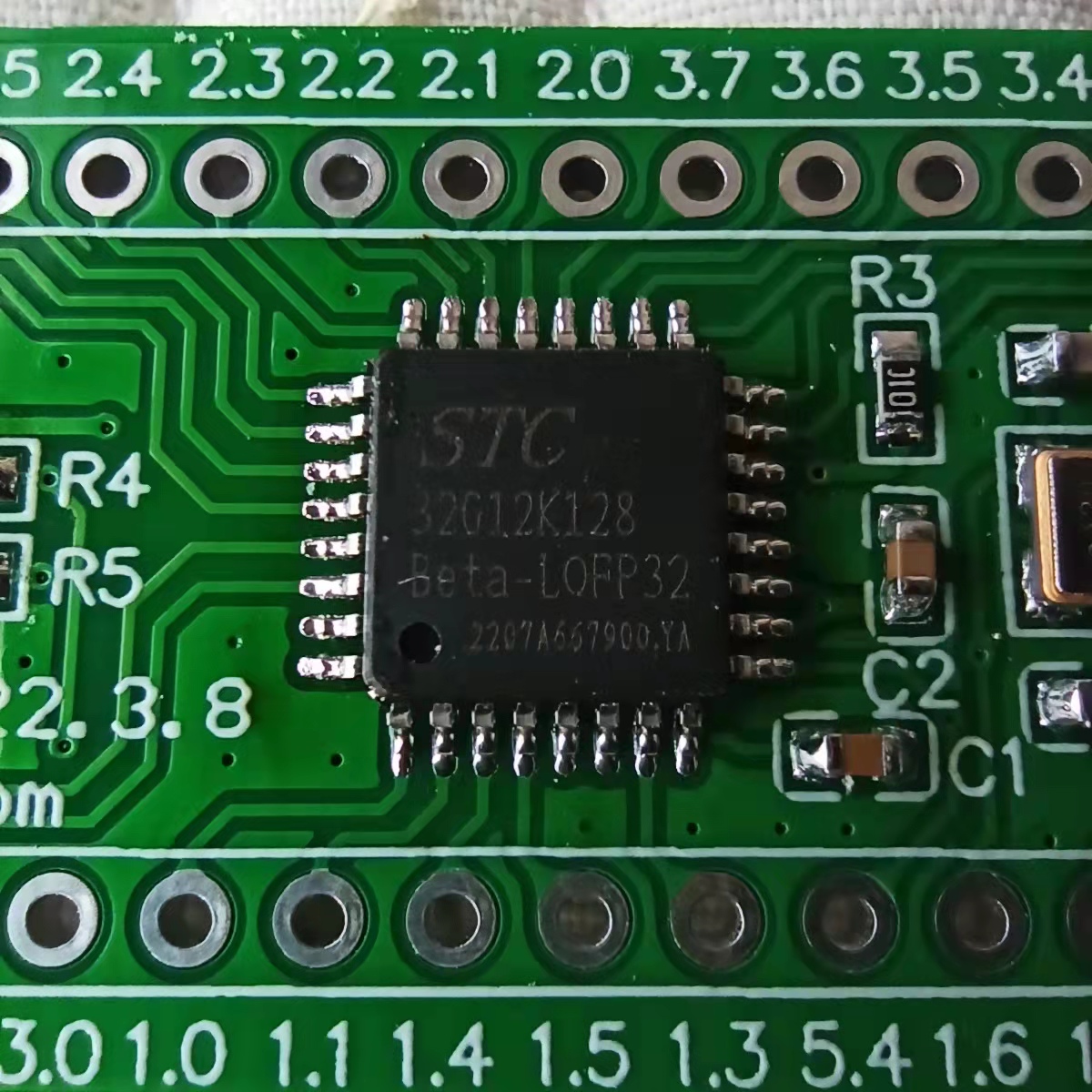

#170 8051/STC8/AT89C51/N76E003 » STC32G12K128的Dhrystone性能测试 » 2022-03-14 18:14:27

- echo

- 回复: 11

这款号称32位的8051,实际上就是Intel的C251架构,向下兼容8051,地址空间扩展到了24位,堆栈空间扩展到了16位共64kB,扩大了内部SARM(edata)数据复制速度也有了很大提高,解决了8051架构的一些弊端。

STC花了很大力气宣传,芯片刚刚到手不久,板子打好测一下性能,看看是不是和他们宣传的一样好。

软件还是使用Dhrystone,编译器C251.exe 版本v5.60.0.0,速度优化,使用标准库。

第一次测试结果376ms,奇怪,怎么比8位的8051还慢?查了好久,原来WTST寄存器搞的鬼,复位值是最大值7,加了7个等待,手册建议35M主频以下改为0,修改为0重新测试,速度果然快了很多,结果如下。

结论就是大约0.38DMIPS/MHz,这个结果和ARM在 https://www.keil.com/benchmarks/c251_bmark.asp 这个文章中的测试结果是一致的。这就是C251架构的性能了,比8051提高很多,然而在现代一众32位MCU中显然不算入流。

其实我对这个来自古代的C251核心一点兴趣都没有,现代的Cortex-M和RISC-V比它要好得多,买这个芯片主要是想看看它的USB和两个CAN表现如何,尤其是两个CAN,从寄存器接口来看,就是内置了两片SJA1000控制器,光这两个CAN都值回票价了,具体如何,有待以后分解。

最后再吐槽下这个C251编译器,不知道是因为用户太少还是什么原因,真的是不太好用,很多标准C库函数没有实现,比如strstr,strtok,strtoul,都要自己实现。

一个结构体中定义的一个函数指针,指向实际的函数,它也分析不出来,然后报L57警告,实际呢又能运行,也就是函数并没有被优化掉,让人困惑。

*** WARNING L57: UNCALLED FUNCTION, IGNORED FOR OVERLAY PROCESS

#171 Re: RISC-V » WCH的RISC-V居然跑出了3.84DMIPS/MHz的成绩... » 2022-03-12 11:30:19

@Blueskull WCH官方人员确认了GCC的这个问题。他们也是“持续关注GCC对此类问题的更新情况”

https://bbs.21ic.com/icview-3204494-1-1.html

而且有朋友也用7.2.0版本的GCC发现了同样的问题。

https://zhuanlan.zhihu.com/p/478423323

-flto选项对RISC-V还是很重要的,因为RISC-V的代码密度本身就非常拉胯

#172 Re: RISC-V » WCH的RISC-V居然跑出了3.84DMIPS/MHz的成绩... » 2022-03-12 11:23:12

#173 Re: RISC-V » WCH的RISC-V居然跑出了3.84DMIPS/MHz的成绩... » 2022-03-12 11:21:48

#174 Re: RISC-V » WCH的RISC-V居然跑出了3.84DMIPS/MHz的成绩... » 2022-03-12 09:42:32

#175 Re: RISC-V » WCH的RISC-V居然跑出了3.84DMIPS/MHz的成绩... » 2022-03-12 09:31:26

#181 Re: Cortex M0/M3/M4/M7 » 一个GD32E103的USB硬件bug » 2022-01-17 12:31:14

#182 Cortex M0/M3/M4/M7 » 一个GD32E103的USB硬件bug » 2022-01-16 21:07:01

- echo

- 回复: 3

使用某个双向端点来通讯,比如端点2,我们记为EP2_OUT和EP2_IN,分别处理主机的OUT和IN请求。设备收到主机OUT请求以后,应答ACK,然后设置EP2_OUT的TF中断标志,中断延迟大约6us或者更少一些。

如果在6us中断延迟时间内没有EP2_IN的IN请求,或者即使有IN请求,设备EP2_IN没有准备好,应答NAK,那一切正常。我的应用中实际测试EP2_OUT响应ACK以后,大约0.6us以后主机就会发送IN请求,刚好落在6us的中断延迟时间内。这时候如果设备EP2_IN端点准备好,那么就开始响应EP2_IN请求,给主机发送数据,发送完成主机应答ACK,触发EP2_IN的TF中断标志,正常触发中断,这个中断会把它前面EP2_OUT的中断标志冲掉,导致丢失前面的EP2_OUT传输完成中断。

usb的固件库代码我看过是可以同时处理同一个端点OUT和IN两个TF中断标志的,所以问题大概率在USB硬件。目前该问题还未得到官方确认。这个问题在USB实际通讯速率不高的问题,极少出现,大流量的通讯的时候会出现,概率几十万分之一吧,没有什么规律,所以定位起来十分困难。

#183 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 请教CH579的网络,不用库自己初始化的问题 » 2022-01-09 09:47:17

#184 Re: Cortex M0/M3/M4/M7 » 说说航顺的M0--优秀的国产替代 » 2022-01-06 23:02:16

#185 Re: Cortex M0/M3/M4/M7 » 一个GD32的CAN外设硬件bug » 2022-01-05 17:30:27

#186 Re: Cortex M0/M3/M4/M7 » 一个GD32的CAN外设硬件bug » 2022-01-05 08:46:36

#187 Re: Cortex M0/M3/M4/M7 » 一个GD32的CAN外设硬件bug » 2022-01-05 00:38:51

#188 Re: Cortex M0/M3/M4/M7 » 一个GD32的CAN外设硬件bug » 2022-01-04 23:38:03

#189 Re: Cortex M0/M3/M4/M7 » 一个GD32的CAN外设硬件bug » 2022-01-04 23:34:57

#190 Re: Cortex M0/M3/M4/M7 » 一个GD32的CAN外设硬件bug » 2022-01-04 19:25:43

#191 Cortex M0/M3/M4/M7 » 一个GD32的CAN外设硬件bug » 2022-01-04 15:44:34

- echo

- 回复: 18

测试过GD32E103,GD32F303,都有这个问题,其它型号有待确认,大概率GD32全系CAN外设都有这个问题。

CAN状态寄存器的bit9 RS表示接收状态,实际测试,CAN初始化退出睡眠模式以后RS位就是1,进入初始化模式以后RS位清零,退出初始化模式以后RS=1

然后整个使用过程中这个RS位一直都是1,本来这个位是指示CAN硬件有没有在接收数据的,现在完全失去了意义。

CAN的一帧很长,需要上百个位,持续数百微秒,硬件接收完了完整一帧才会放入FIFO,软件才能查询到,所以如果软件想知道硬件是否在接收数据,这个接收指示位就很重要,如果这个位行为异常,软件通过RX管脚来判断是否CAN正在接收数据非常困难。

实测STM32和AT32的这个RS位行为是正常的,只有接收数据的时候才会置1,可以判断CAN的接收状态。

联系过GD原厂,确认了这个问题,GD32的CAN外设无法通过硬件判断CAN外设是否在接收数据,还有更坏的消息:原厂不认为这是bug,也不打算在新产品型号中更改。

好消息是他们的CAN IP是自研的,所以这个bug应该是GD32芯片独有的,不会影响其它厂商的产品。

附和原厂技术人员沟通记录:

GD:我找人测了下,默认是处于接收状态,如果是发送数据时,会处于发送状态,发的时候会变 0,其他都是1

ME:这种行为模式没有用处,因为实际需要的是硬件在接收数据才置1,而且其它厂家人家也是这么定义的

GD:设计就是这样,那就只能别这么用

ME:那应该如何判断CAN硬件在接收数据?有别的方法也行

GD:没有办法,就我跟你说的判断帧数量

ME:我说过了,没法根据帧判断,CAN总线在接受数据的时候,数据还没进FIFO,一帧接收完了才会进FIFO

GD:我知道你意思,那就无解啦,无法识别正在接收状态

ME:好吧,只能尽量避免用这个芯片了,这个IP不知道是自研的还是外购的,STM32F103是没有这个问题的

GD:自研

ME:那别家应该没这个问题,你们可以对比下友商的产品

GD:知道,设计人员对这个理解与别人有偏差,这就跟485接口类似

ME:就是受了RS485的影响,485不支持多主,发送完数据要设置为接收,问题CAN是支持多主的,没有这个问题,所以是芯片bug,不是特性

GD:485没有仲裁机制,CAN有仲裁机制,现在这个特性你认为是BUG那就是,他不影响正常使用,只是你刚好想要用的点有点特殊,无法满足你的应用场景

ME:这个位相当于没有,是不是bug,你们要确认,涉及到新芯片是否会更新的问题。

GD:我回你了啊,我们设计是我跟你说的那样,这个你能理解为他是bug,也能理解为他为设计特性

ME:我明白了,那就是以后新型号也不会更改。

#192 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 盗版CH340的被判刑了 » 2021-12-25 21:27:33

#193 ESP32/ESP8266 » 打造极致性价比 乐鑫科技发布 ESP32-C2 » 2021-12-24 18:25:07

- echo

- 回复: 1

感觉会比ESP8266更便宜,内置FLASH的版本也终于不把FLASH引脚引出来了。QFN24封装4x4。

https://www.espressif.com/zh-hans/news/ESP32-C2

乐鑫宣布推出低功耗、低成本的 ESP32-C2 芯片,比 ESP8266 面积更小、性能更强。ESP32-C2 在满足简单物联网应用需求的基础上,进一步优化成本,能够为用户提供一个极具性价比的开发平台。值得一提的是,乐鑫的射频技术实现重要突破,可达到 1024-QAM 技术指标,未来将为客户提供更多高性能的产品选择。

ESP32-C2 集成 2.4 GHz Wi-Fi 和支持长距离的 Bluetooth 5 (LE),搭载 RISC-V 32 位单核处理器,时钟频率高达 120 MHz,内置 272 KB SRAM (16 KB 专用于 cache) 和 576 KB ROM,具有 14 个可编程 GPIO 管脚,支持 SPI、UART、I2C、GDMA 和 PWM。

#195 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 盗版CH340的被判刑了 » 2021-12-23 00:30:48

dgtg 说:啥都没改吗?

改改管脚也行啊..直接抄的版图,啥都没改。WCH也抄别人的,pin兼容的CP2102N,CP2104和FTDI的产品,但是WCH只是抄功能,设计实现都是自己搞的,不涉及侵权,类似GD32抄STM32。

管脚兼容,我觉得不算是抄。举几个极端点的例子,电阻都是2条腿,SOT-23的MOS管,gds三个管脚排列都是一样的,没有人觉得生产电阻和MOS管是抄。同样的485/CAN的PHY芯片,SO-8封装管脚排列也完全一样。MCU相比之下可能只是管脚多了一点,没有本质差异。当然MCU也有SO-8封装的,甚至SOT-23-6也有。

#196 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 盗版CH340的被判刑了 » 2021-12-21 16:04:55

#197 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 盗版CH340的被判刑了 » 2021-12-21 15:53:12

#198 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 盗版CH340的被判刑了 » 2021-12-21 09:42:23

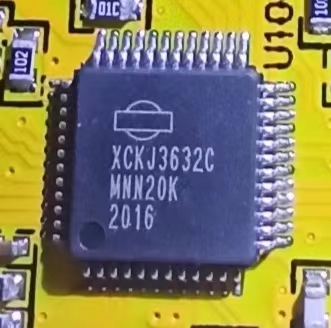

上海国*,芯片命名G开头的。

http://www.gco__.com.cn/

#199 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 盗版CH340的被判刑了 » 2021-12-21 09:38:59

- echo

- 回复: 29

重点:专业公司,直接逆向,相似度100%,GC9034,价格730/830=0.88元

http://www.jmzscqlvshi.com/300.html

沁恒公司生产的CH340芯片自2011年上市销售以来深受业内人士喜爱,一跃成为业界值得信赖的国产高端芯片。正因如此,CH340芯片暗中成为了企图不劳而获的不法人员眼中的新“财路”。

2016年,G公司销售人员陶某,在进行市场调研和推广中发现CH340芯片销量大,遂从市场获取正版CH340芯片交予G公司负责公司生产经营等事务的总经理许某,在未获得沁恒公司授权许可的情况下,决定反向破解CH340芯片并对外销售。于是委托其他公司对CH340芯片各层电路布图进行破解,提取GDS文件,再生产掩模工具、生产晶圆、封装,后以G公司GC9034型号芯片名义对外销售。

2016年9月至2019年12月,G公司共销售侵犯沁恒公司著作权的GC9034芯片共计830余万个,销售金额人民币730余万元,上述收益均归G公司单位所有。

#200 Re: 全志 SOC » 网站需要改革,放开文件下载权限(不需要与积分挂钩) » 2021-12-10 09:23:45

- 首页

- » 搜索

- » echo 发表的帖子

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发