- 首页

- » 搜索

- » AICxia 发表的帖子

页次: 1

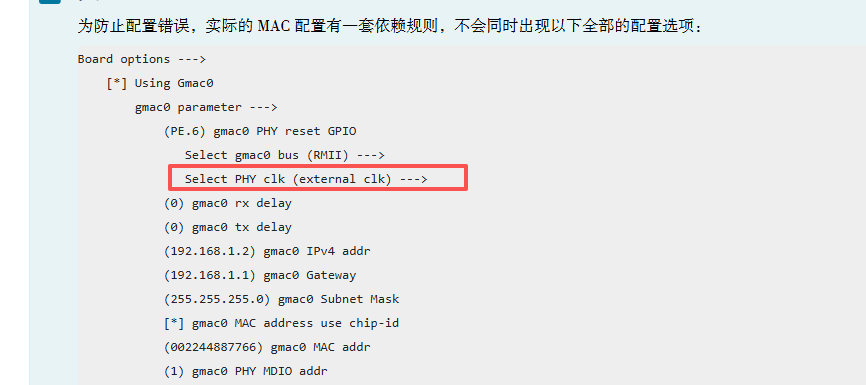

#1 Re: 工业芯 匠芯创 » D21X 以太网驱动是不是有bug呢? 时通时不通 » 2026-04-10 13:54:48

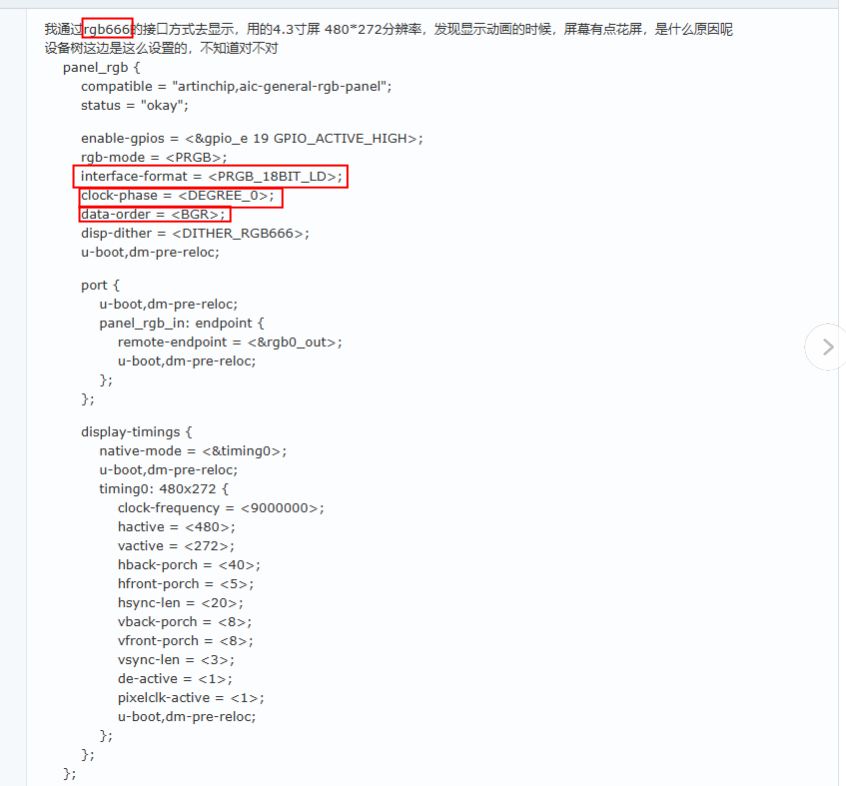

#3 Re: 工业芯 匠芯创 » d12 RGB565硬件接线方式 » 2026-03-16 17:29:07

#7 Re: 工业芯 匠芯创 » 编译错误 » 2026-02-02 16:05:23

https://gitee.com/artinchip/baremetal/tree/master/tools/scripts,gitee 上是有的,需要看一下对应目录上是否有这个文件

#8 Re: 工业芯 匠芯创 » D211DBV重启的瞬间 程序没有运行 PC.4引脚会置高 » 2026-01-28 15:36:48

https://aicdoc.artinchip.com/topics/ic/sid/sid-function-d21x.html

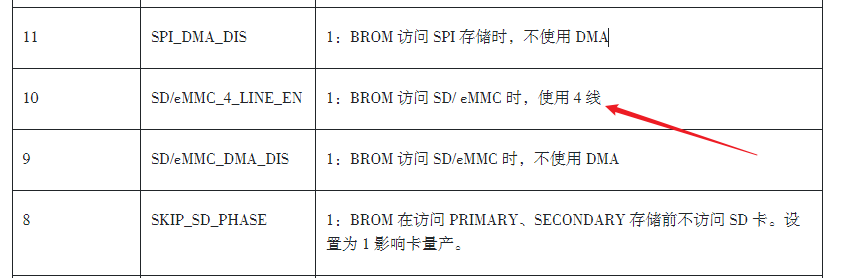

可以看一下 BROM eFuse 是否有使能4线 SD/eMMC 启动。默认是没有使能的。这个 bit 设置为1之后,就会使用到 PC.4 PIN 脚。

可以通过 AiBurn 工具的 【擦写模式】查看。或者直接读取寄存器 0x19010230 bit10

#9 Re: 工业芯 匠芯创 » D133CBS用UART6进行串口收发通信该怎么做 » 2026-01-19 17:15:05

#10 Re: 工业芯 匠芯创 » D121-HMI board 测试RTP外设,结果不正确 » 2026-01-16 15:32:03

1. 3.3V采样电压值不对的问题:原因可能是test_rtp_adc 转换采样值为电压值时使用的ADC参考电压是从芯片读取出来的,从打印结果上看,读取的芯片参考电压应该是2.5V,可以在bsp/artinchip/hal/adcim/hal_adcim.c:hal_adcim_adc2voltage函数增加打印,看看函数内部局部变量 st_voltage 读取的值是多少,如果与实际参考电压3.3V不一致,则考虑将读取参考电压那一行代码注释掉,然后再测试一下;

2. 0V采样值转换超出范围的问题:将 test_rtp_adc.c:rtp_get_data 函数里的 cal_param、adc_info.data 变量打印一下,看看值是多少,应该是采样值比较小,转换时考虑了校准和偏移,校准后的采样值小于0导致的

#11 Re: 工业芯 匠芯创 » 参考test—psadc例程自己照写了一个,但是跑不过去 » 2026-01-08 14:51:15

#12 Re: 工业芯 匠芯创 » 参考test—psadc例程自己照写了一个,但是跑不过去 » 2026-01-08 14:27:41

#13 Re: 工业芯 匠芯创 » D21x用户手册 MIPI DSI寄存器说明 » 2026-01-08 10:05:05

#14 Re: 工业芯 匠芯创 » AiUIBuilder 2.0.2 字体裁剪问题 » 2025-12-23 14:58:06

#15 Re: 工业芯 匠芯创 » D12 G2D 绘制小矩形速度巨慢 » 2025-12-23 14:55:11

#16 Re: 工业芯 匠芯创 » windows usb 驱动 demo » 2025-12-09 14:08:26

#18 Re: 工业芯 匠芯创 » D211BBV 无法烧录 » 2025-11-14 14:15:57

#20 Re: 工业芯 匠芯创 » D211显示问题,求助 » 2025-11-03 10:40:10

#21 Re: 工业芯 匠芯创 » D211使用Linux SDK出现网络phy(RTL8201F) 偶尔 Link is Down, Link is Up现象 » 2025-10-29 14:23:17

#24 Re: 工业芯 匠芯创 » 如何点亮我的mipi屏幕 » 2025-10-28 14:39:18

#25 Re: 工业芯 匠芯创 » 官方配套的芯片工具能否推出支持Linux版本的? » 2025-10-21 15:47:03

#26 Re: 工业芯 匠芯创 » 请问在Luban Lite里怎么使用FreeRTOS系统? » 2025-10-21 15:44:55

#28 Re: 工业芯 匠芯创 » 在D13上面开启sqlite3数据库和freeMODBUS功能,并且用modubs读取数据存入sqlite3,用sd进行文件存储,怎么设置? » 2025-09-25 17:06:46

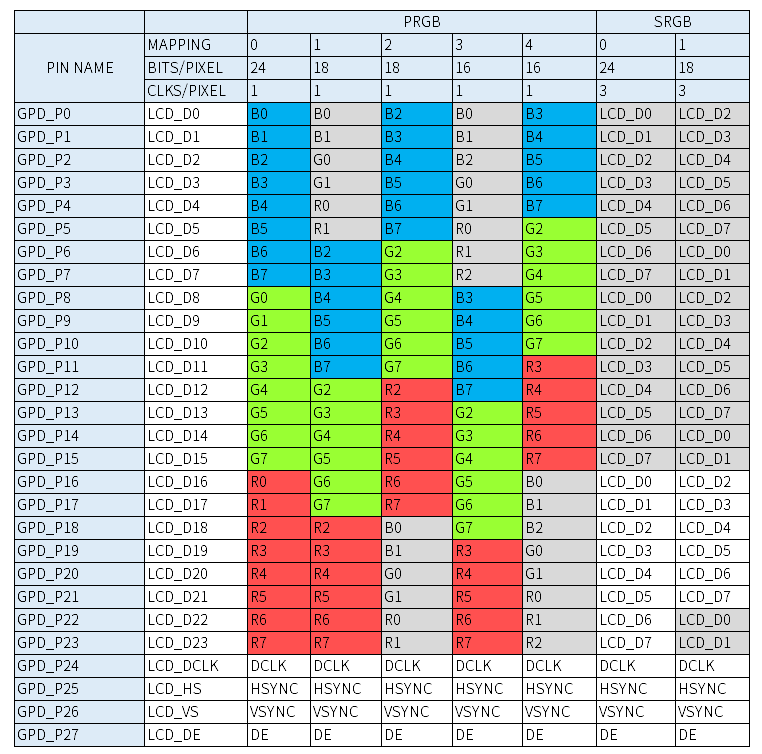

#30 Re: 工业芯 匠芯创 » D121 的luban-lite 支持RGB666吗 » 2025-09-11 09:31:17

#31 Re: 工业芯 匠芯创 » 编译官方d211-master-V1.3.0-鲁班 SDK LVGL 开启FFmpeg库对MP4播放解码,编译出现如下问题,怎么解决 » 2025-09-09 15:35:14

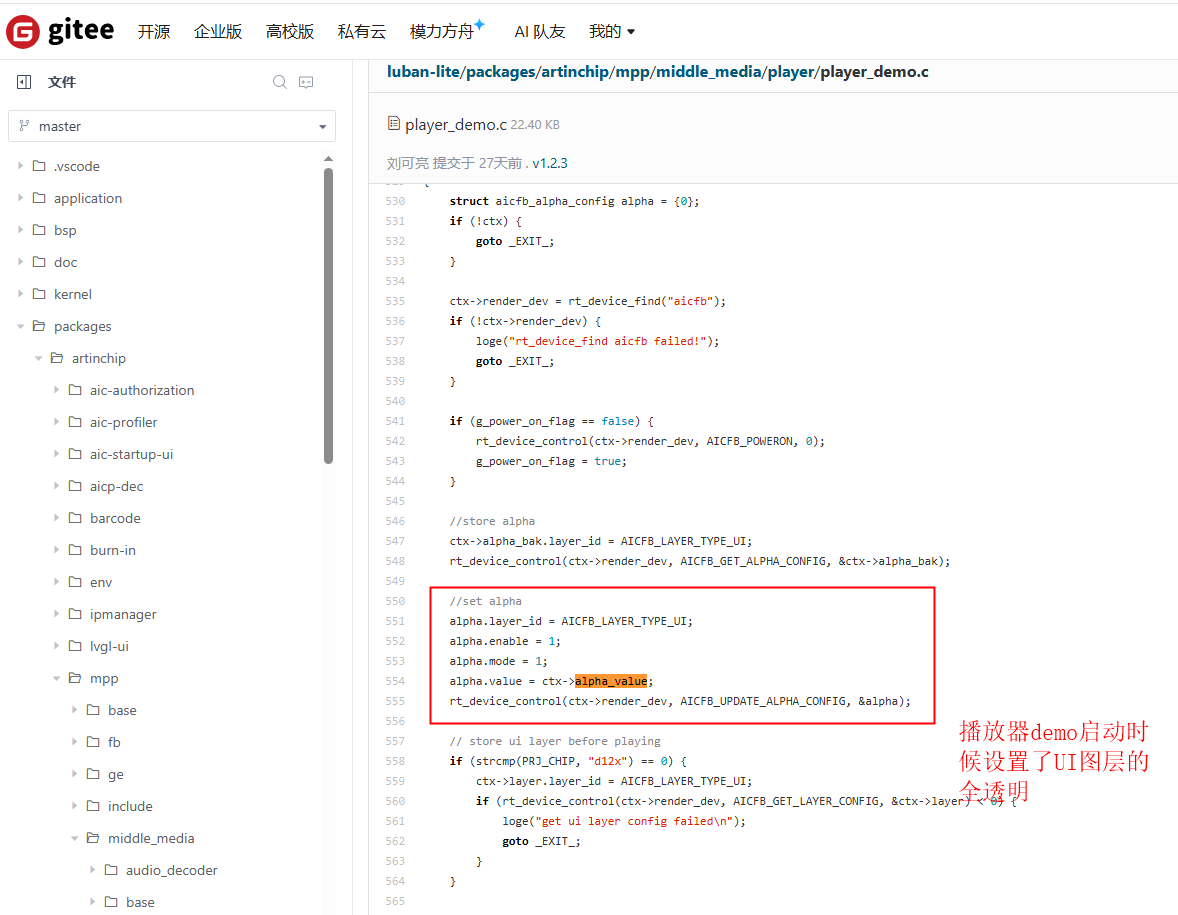

1. 目前luban上LVGL不支持ffmpeg进行视频播放

2. 如果需要播放视频可以参考: https://gitee.com/artinchip/d211/blob/master/source/artinchip/lvgl-ui/aic_demo/aic_player_demo/aic_player_demo.c ,用我们的aic_player控件进行视频播放

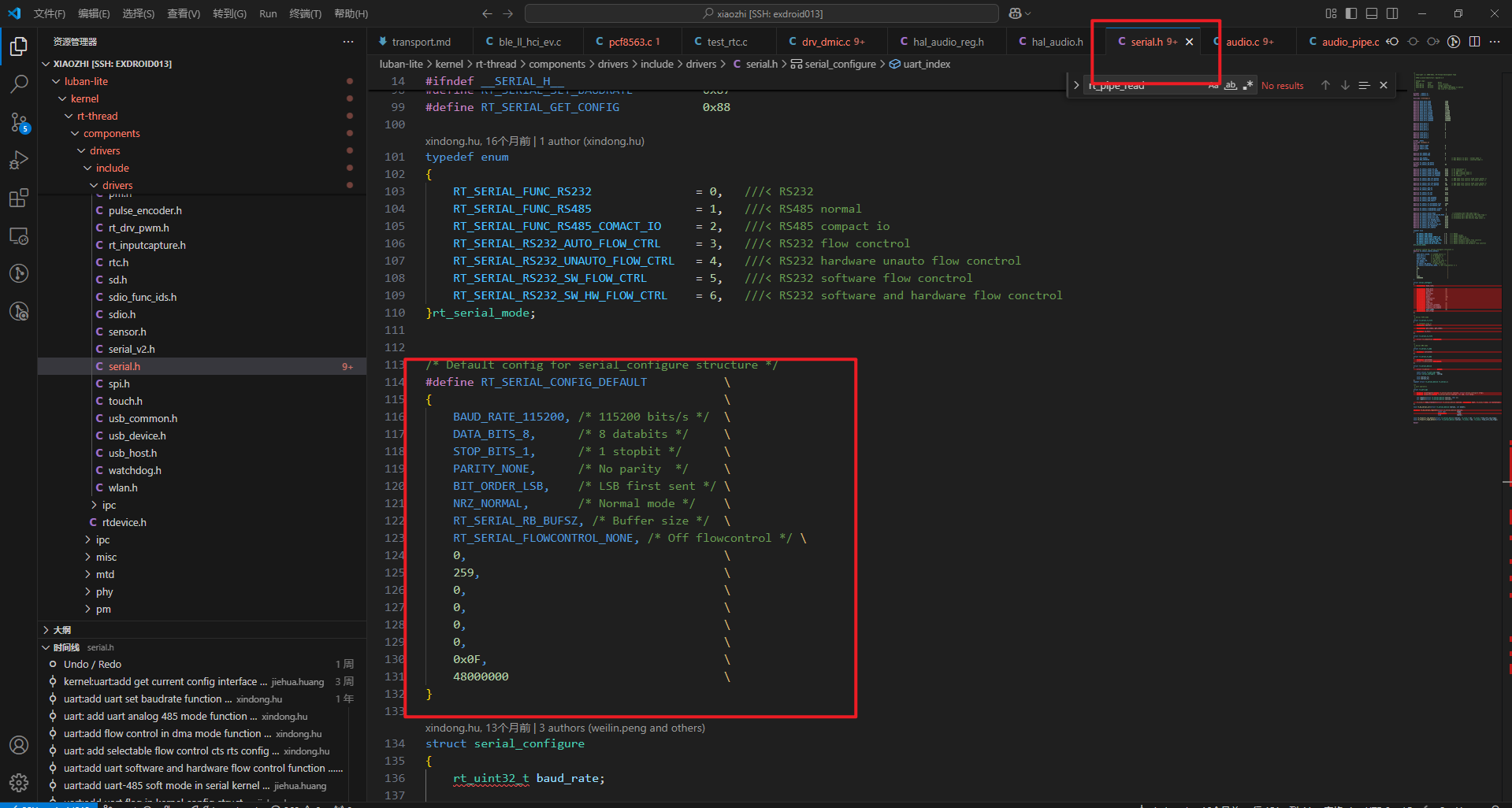

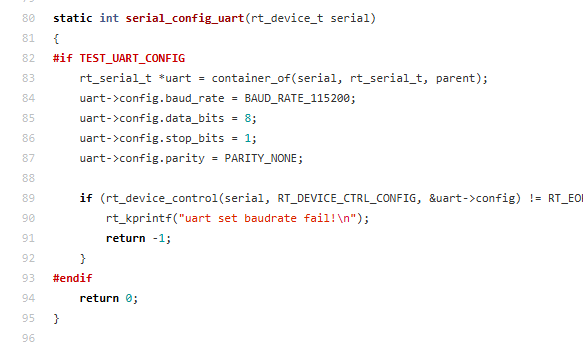

#32 Re: 工业芯 匠芯创 » 关于串口发送中断的问题 » 2025-09-09 14:03:15

#33 Re: 工业芯 匠芯创 » 关于ADC采样的问题 » 2025-08-18 16:11:27

#34 Re: 工业芯 匠芯创 » LVDS和mipi接口能否做为输入 » 2025-08-06 14:41:23

#35 Re: 工业芯 匠芯创 » 串口使用DMA的问题 » 2025-08-06 14:39:52

#36 Re: 工业芯 匠芯创 » D133 PNG连续解码报错 如何解决 » 2025-08-05 15:22:59

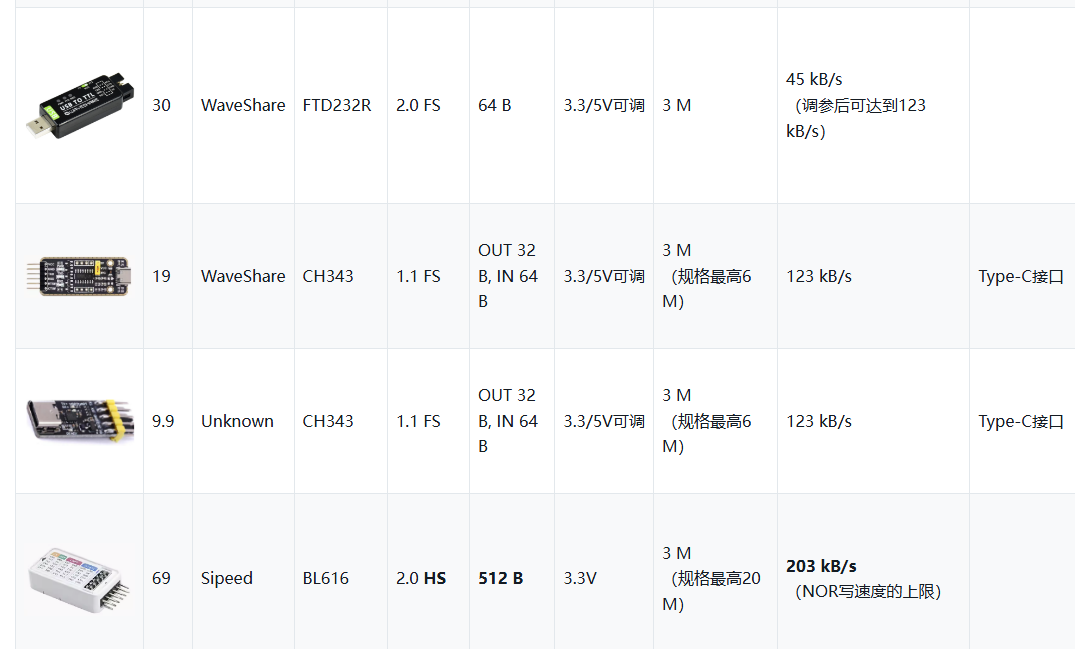

#38 Re: 工业芯 匠芯创 » 使用PQ 工具调试的时候特别容易断开连接怎么解决 » 2025-07-14 14:17:16

#39 Re: 工业芯 匠芯创 » 如何使用D13X 的 GE的格式转换,例如ARGB8888转RGB565 » 2025-07-10 09:07:08

1. 参考设置图像搬移blt参数中的src和dst的format即可,实现不同格式的转换:

https://gitee.com/artinchip/luban-lite/blob/master/packages/artinchip/mpp/mpp_test/pic_dec_test.c

2. pic_dec_test.c中图像搬移代码示例,可以设置原图和目标图的format不一样

blt.src_buf.buf_type = MPP_PHY_ADDR;

blt.src_buf.phy_addr[0] = (u32)(long)src_buf;

blt.src_buf.format = info->format; // MPP_FMT_ARGB_8888

blt.src_buf.stride[0] = info->stride; // src stride信息要填写正确, 需要 8 bytes对齐

blt.src_buf.size.width = info->width;

blt.src_buf.size.height = info->height;

blt.dst_buf.buf_type = MPP_PHY_ADDR;

blt.dst_buf.phy_addr[0] = (u32)(long)dst_buf;

blt.dst_buf.format = info->format; // MPP_FMT_RGB_R65

blt.dst_buf.stride[0] = info->stride; // dst stride信息要填写正确, 需要 8 bytes对齐

blt.dst_buf.size.width = info->width;

blt.dst_buf.size.height = info->height;

ge_bitblt(&blt);

#41 Re: 工业芯 匠芯创 » D211里linux开发usb驱动dma映射失败 » 2025-06-25 13:48:09

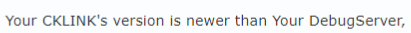

#42 Re: 工业芯 匠芯创 » ICE在线仿真死机问题 » 2025-06-24 10:32:52

#43 Re: 工业芯 匠芯创 » HRPWM 功能功能使用 » 2025-06-19 16:51:02

#44 Re: 工业芯 匠芯创 » d121bbv程序下载 » 2025-06-16 17:52:43

#45 Re: 工业芯 匠芯创 » D133EBS能输出静态相位差的方波吗? » 2025-06-16 16:23:21

#46 Re: 工业芯 匠芯创 » D133EBS能输出静态相位差的方波吗? » 2025-06-12 17:10:10

#48 Re: 工业芯 匠芯创 » d121bbv程序下载 » 2025-06-11 15:30:00

#51 Re: 工业芯 匠芯创 » D13CBS LVGL+FreeType多次显示不同汉字导致内存增加 » 2025-05-23 15:20:52

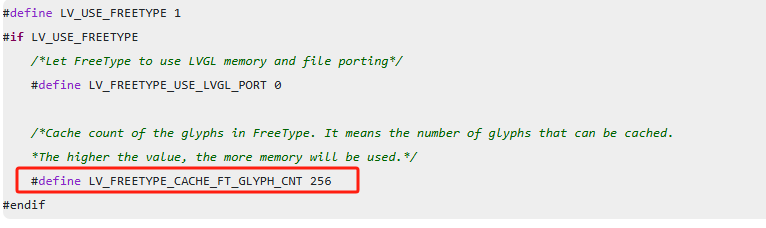

1. 在LVGL V9中可以在 lv_conf.h中配置字体缓存的个数

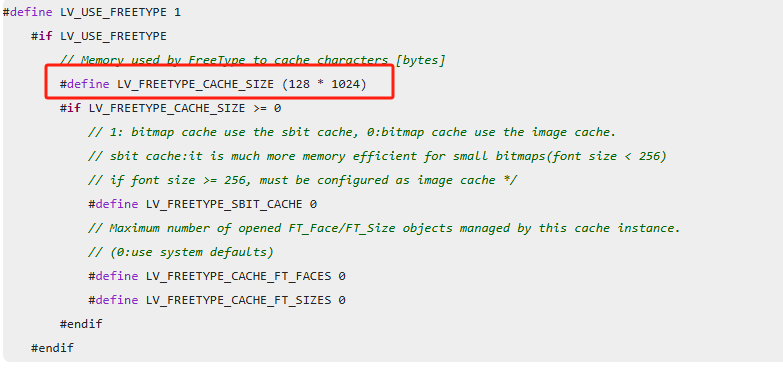

2. 在LVGL V8中也可以在 lv_conf.h中配置字体缓存的size

3. 可以通过调整 freetype的缓存配置参数,来调整最大的缓存占用量,目前只能设置缓存的上限,不能自己去释放缓存空间

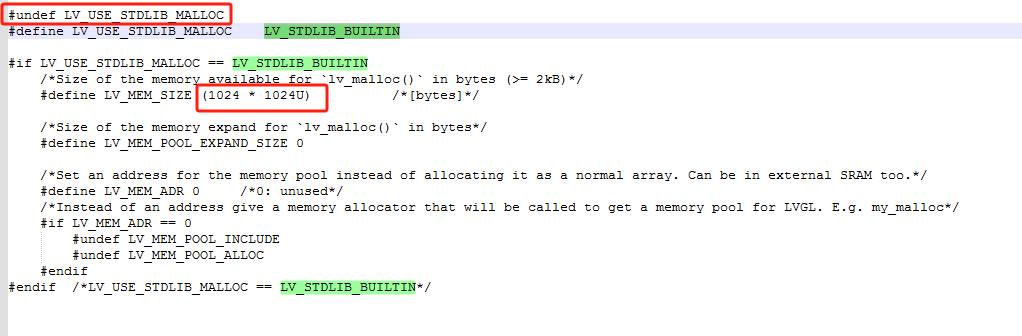

4. 目前lvgl自身的运行也会从sys heap中申请内存,freetype也会从 sys heap中申请内存,可以调整LVGL用自身的堆管理(预留一块静态数据块),不用sys heap,为 freetype流出更多内存使用,在 LVGL V9中lv_conf.h添加如下配置,示例中是预留了1MB的空间,可以根据实际需要调整

#52 Re: 工业芯 匠芯创 » d13x的lcd接口和pbus不能同时使用吗 » 2025-05-13 13:47:14

#54 Re: 工业芯 匠芯创 » luban-lite-master lvgl9触摸操作偶发性死机 » 2025-04-23 10:34:17

1. 从打印信息看是 freetype申请不到内存了,可以改变一下LVGL的内存配置

2. 可以修改一下luban-lite/packages/artinchip/lvgl-ui/lvgl_v9/lvgl/env_support/rt-thread/lv_rt_thread_conf.h

配置LVGL内存使用LV_STDLIB_BUILTIN方式,给的参考中 LV_MEM_SIZE配置成了2MB,可以根据实际情况去修改 lv_rt_thread_conf.zip

#55 Re: 工业芯 匠芯创 » D133EBS-wifi不通-参照过可搜到所有资料 » 2025-04-22 11:19:17

连接成功后,dhcp申请需要一些时间,建议重新启动dhcp client后稍等几秒再使用ifconfig查看。另外你那边网络环境这么干净吗?竟然只扫到两个ap,可以和手机扫描出来的比对一下。忽略5G频段的AP,如果与手机扫描出来的差距很大,建议检查一下板子的天线。

建议将lwip中的IP debug使能这样能看到板子与路由器的交互信息,这样能更直观的看到有没有收到路由器的dhcp回复。

可以使用lwip 的socket接口进行编程,这个网络上随便都能找到参考的。如果是http客户端,建议可以使用rtt的webclient,这样较为简单。

wifi的启动、扫描、连接、断开等接口都可以参考“wlan”命令的实现,也可以直接查看/bsp/peripheral/wireless/realtek/Realtek_WIFI_driver_porting_guide_v1.0.doc文档。

编码时建议独立出一个“wifi控制线程”,保证所有的wifi操作都在同一线程中完成。

#56 Re: 工业芯 匠芯创 » D133 lvgl开机启动慢 » 2025-04-21 15:07:02

#60 Re: 工业芯 匠芯创 » D133EBSrgb脚位跟EPWM冲突的问题, » 2025-04-10 10:59:01

#62 Re: 工业芯 匠芯创 » luban-lite中lvgl 9.1.0适配有bug,GE经常出错! » 2025-04-02 14:00:28

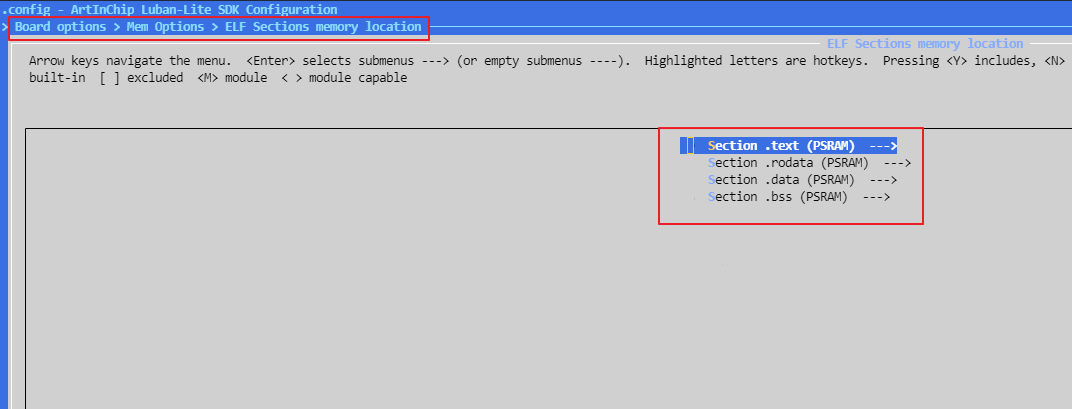

1. 通过现象猜测现在应该用的是D13x系列芯片

2. 看代码中图片的加载方式是用的静态数组,有可能是存储在SRAM中的,GE不支持从SRAM中读取数据,可以检查一下配置 ELF mem配置,选择PSRAM,

也可以更新一下给的patch,如果数据在SRAM中,回退为软件处理流程:

修改文件路径:packages/artinchip/lvgl-ui/lvgl_v9/lv_drivers/lv_ge2d/lv_draw_ge2d.c

3. 使用静态数组的图片,当图片比较大的时候,可能会占用比较多的存储空间,使用时候需要注意一下

4. 当图片比较多的时候,推荐用 png/jpg格式图片,放在外部flash中,会动态加载

5. 可以参考luban-lite\packages\artinchip\lvgl-ui\aic_demo\dashboard_demo 中从外部文件系统读取图片的配置方式

6. 也可以用我们的UI设计工具进行UI设计:https://aicdoc.artinchip.com

#65 Re: 工业芯 匠芯创 » 怎么进行bringUp? » 2025-03-11 09:55:11

#66 Re: 工业芯 匠芯创 » d122xx 类型产品有计划移植ardunio开发嘛 » 2024-12-30 15:30:16

#67 Re: 工业芯 匠芯创 » 如果我要画一个D133的开发板,SDK怎么选择... » 2024-12-30 14:30:45

#68 Re: 工业芯 匠芯创 » 有哪些soc支持ufs » 2024-12-24 09:59:23

#70 Re: 工业芯 匠芯创 » 一维码+二维码识别方案 » 2024-12-12 08:53:06

#71 Re: 工业芯 匠芯创 » AWTK UI在D21x RTOS SDK平台上性能非常差,平移动画非常卡!什么原因? » 2024-11-27 15:14:56

您好,已经发布了,工具下载地址: https://gitee.com/artinchip/tools

#72 Re: 工业芯 匠芯创 » D133/D211 TF卡的写入速度 » 2024-11-26 14:15:19

#73 Re: 工业芯 匠芯创 » D133CBS QSPI/SPI的使用 » 2024-11-11 15:23:47

#74 Re: 工业芯 匠芯创 » D133CBS QSPI/SPI的使用 » 2024-11-11 15:22:23

#75 Re: 工业芯 匠芯创 » D133 SDk里面怎么没有mmc的target配置呀 » 2024-11-08 17:54:15

#76 Re: 工业芯 匠芯创 » D21x 的引脚GMAC0_TRIG, GMAC0_PPSO, GMAC1_TRIG, GMAC1_PPSO的作用是什么? » 2024-11-05 10:26:48

#77 Re: 工业芯 匠芯创 » D213ECV 使用 Aiburn 无法烧录 » 2024-10-23 13:47:09

#78 Re: 工业芯 匠芯创 » 这个函数我我如何调用?csi_dcache_clean_invalid_range() » 2024-10-22 09:01:57

CPU 和 DMA 设备之间的交互需要手工操作 Cache,例如:

发送方向:CPU 写数据到内存,为了确保数据全部写入到了内存需要 Clean Cache(只会 Clean 有过写操作的 Cache, Dirty 置位),然后才能启动 DMA 设备从内存读数据。

接收方向:DMA 设备写入数据到内存,为了确保 CPU 能读到最新的数据需要先 Invalid Cache (清除所有已加载的 Cache, Valid 置位),然后才能启动 CPU 从内存读数据。

csi_dcache_clean_invalid_range() = Clean Cache + Invalid Cache,这个操作的主要目的是用于数据方向不明确的情况下的一个 Cache 同步动作。但是通常也可以当成 Clean Cache 操作来使用。

另外 Cache 的基本操作单位为 CacheLine,我们 64bit CPU 的 CacheLine 为 64 字节, 32bit CPU 的 CacheLine 为 32 字节。在操作 Cache 时起始地址和长度都必须 CacheLine 对齐。

Cache 参考文档:

https://cloud.tencent.com.cn/developer/article/2315608

#79 Re: 工业芯 匠芯创 » luban-lite的lwip组件编译失败 » 2024-10-18 16:51:24

Luban-lite不仅支持RT-Thread,而且支持uC/OS-ii、freeRTOS和裸机环境,这些都是需要支持以太网协议栈的。所以我们设计之初就将lwIP单独分离出来,并且这样也方便随时与lwIP主线同步,不用受RT-Thread的限制。

至于常用的一些应用协议,如HTTPD、webclient、MQTT、PTPD等协议我们目前都是支持的,并且也有量产产品在使用。

这样的缺点就是大家在熟悉Luban-lite SDK的过程中会感到些许复杂,但是使用起来是很稳定的,就Luban-lite发布以来,我们基本没有收到过关于以太网软件问题的反馈。此外我们也写了非常详细的文档对我们的SDK做了说明,我们也在做其他尝试期望能够降低Luban-lite的复杂度,大家可以期待一下!

#81 Re: 工业芯 匠芯创 » 请教如何定位D133程序崩溃的位置 » 2024-10-11 17:49:06

#82 Re: 工业芯 匠芯创 » D133的bootloader怎么选择2.b项 » 2024-10-11 15:15:10

#83 Re: 工业芯 匠芯创 » d122xx。文档资料没更新啊哥 » 2024-10-08 11:31:16

#84 Re: 工业芯 匠芯创 » d122xx。文档资料没更新啊哥 » 2024-09-30 16:06:17

#87 Re: 工业芯 匠芯创 » D213怎么接千兆? » 2024-09-23 15:21:26

这个需要找phy厂家要原理图,我们的接口是通用的,和我们对接上就可以,如果您需要D213的原理图可以去gitee上下载我们的官方文档,

#88 Re: 工业芯 匠芯创 » D133EBS使用 » 2024-09-19 15:57:33

您可以直接从gitee 官网上 ( https://gitee.com/keqian/luban-lite )将我们的SDK下载下来进行编译,选择 d13x_demo88-nor_v1.0.0 ,不需要做其他更改,就可以获取到D133EBS镜像文件

#89 Re: 工业芯 匠芯创 » Linux系统驱动步进电机方案探索 » 2024-09-13 15:29:47

#91 Re: 工业芯 匠芯创 » D133功耗大概什么情况 » 2024-08-12 10:27:05

页次: 1

- 首页

- » 搜索

- » AICxia 发表的帖子

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发