楼主 # 2021-06-10 21:35:30 分享评论

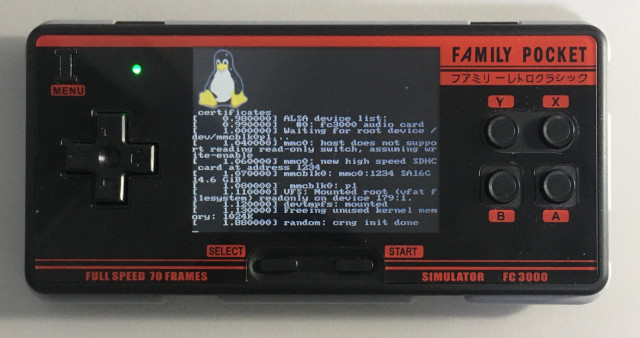

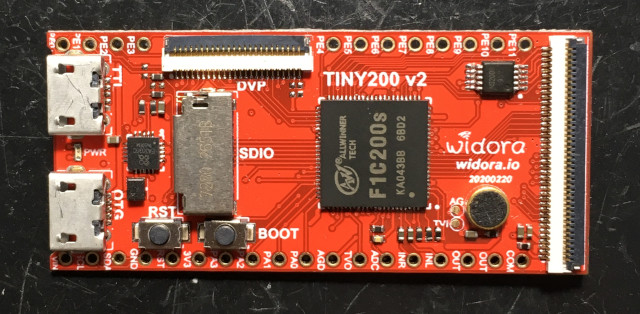

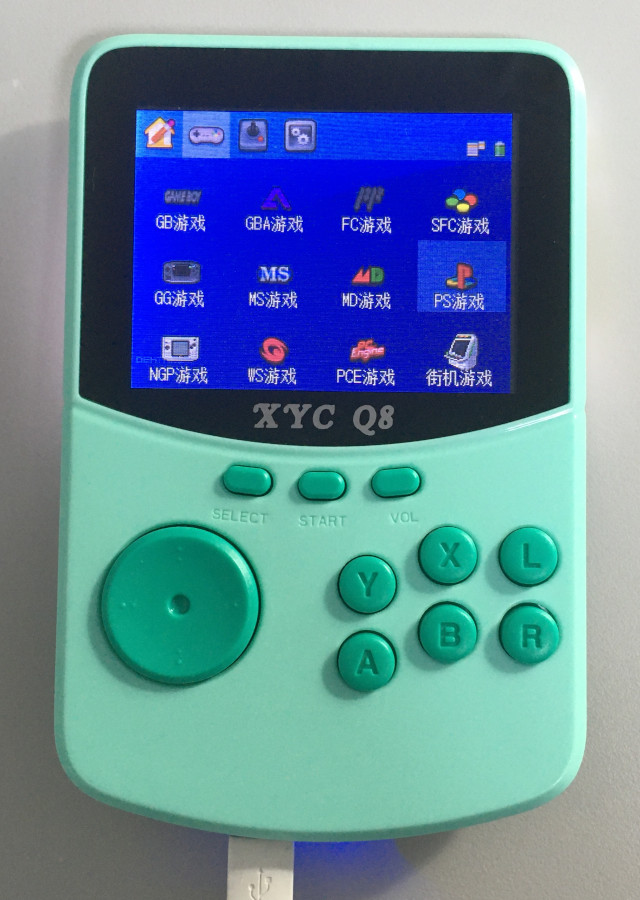

研究FC3000掌機的開源可行性

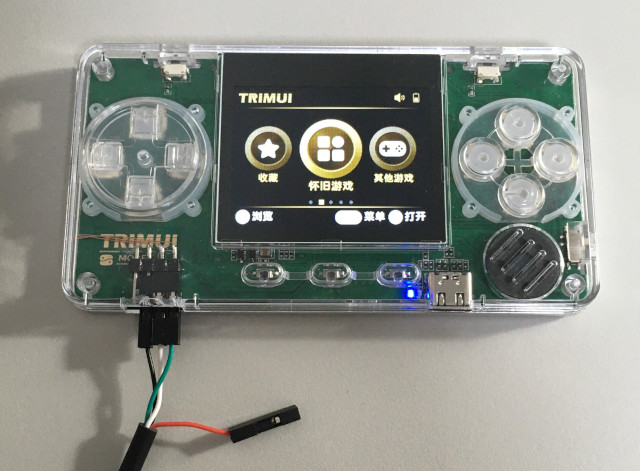

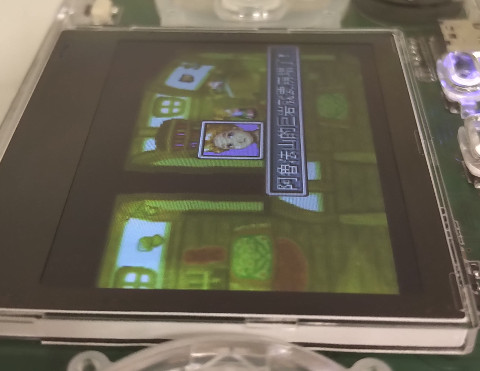

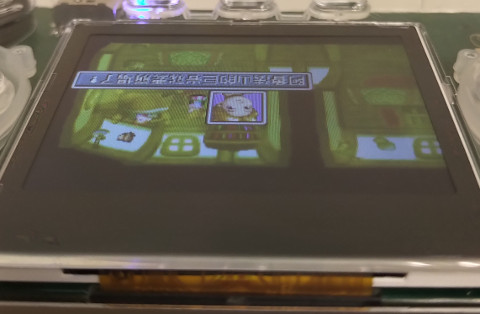

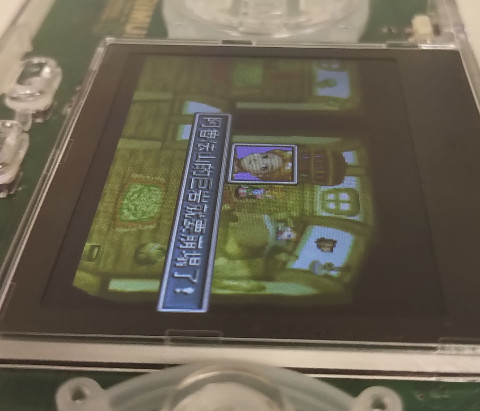

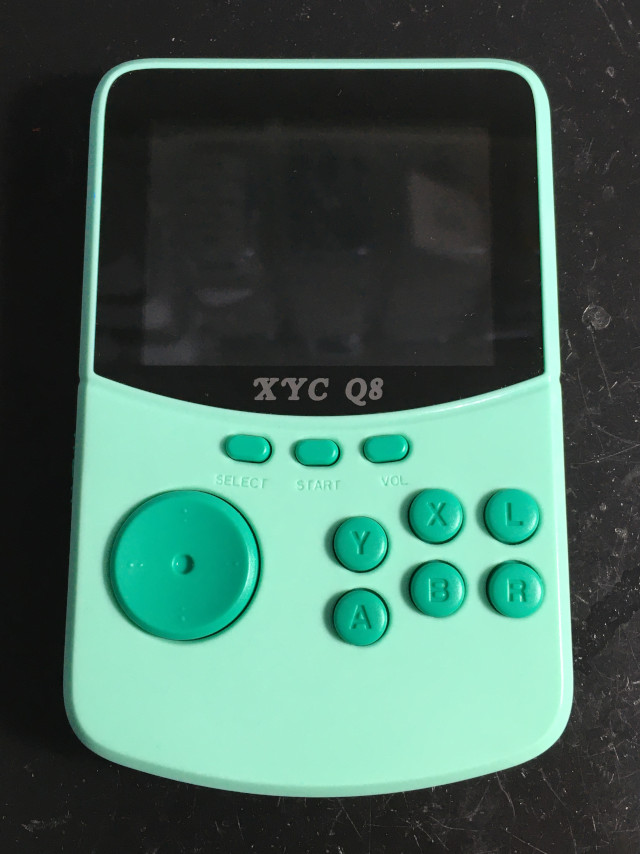

簡要規格

CPU:M900 XCM2010GP40 (全志F1C100S)

RAM:32MB

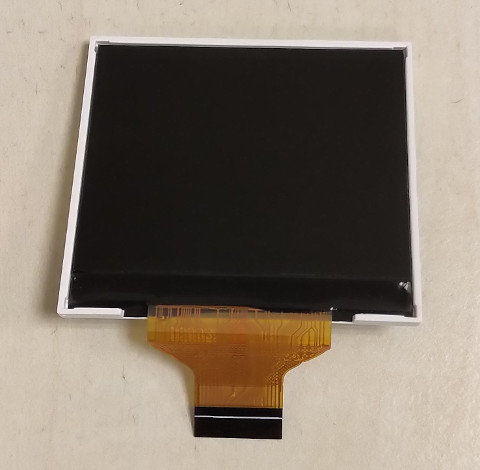

屏幕:3.0吋 320x240解析度

卡槽:MicroSD

按鍵:十字鍵、4顆按鍵、Start、Select、L、R、電源鍵、音量鍵

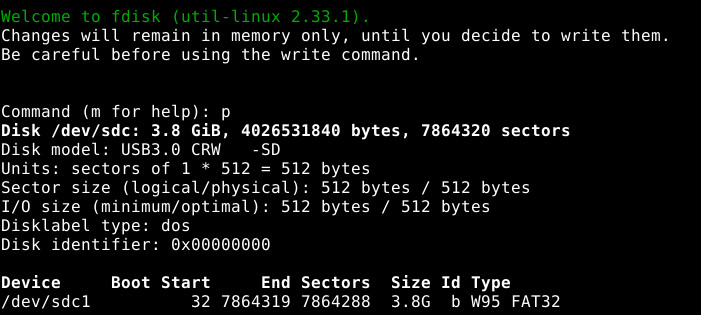

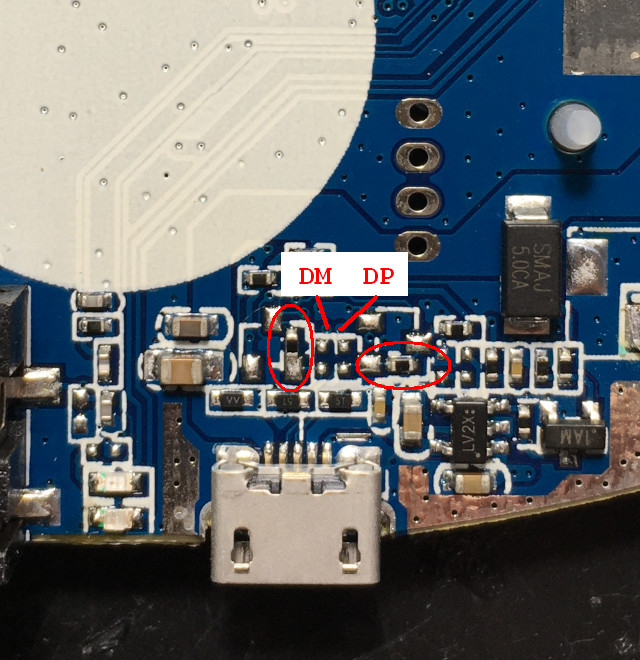

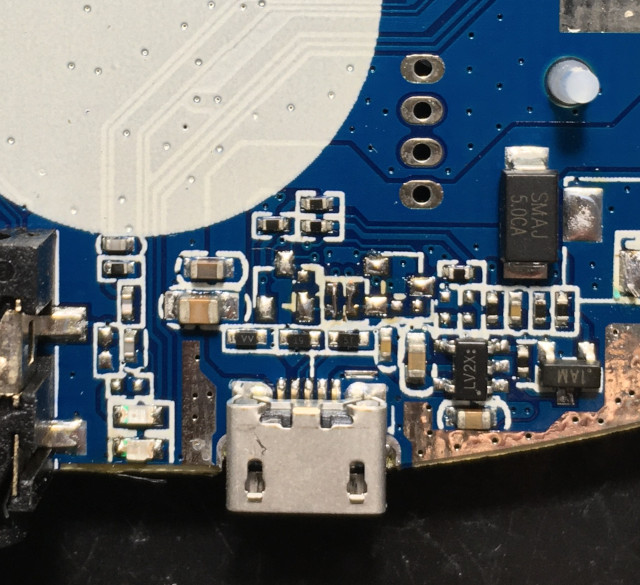

USB:充電功能(並沒有連接到USB DP、DM)

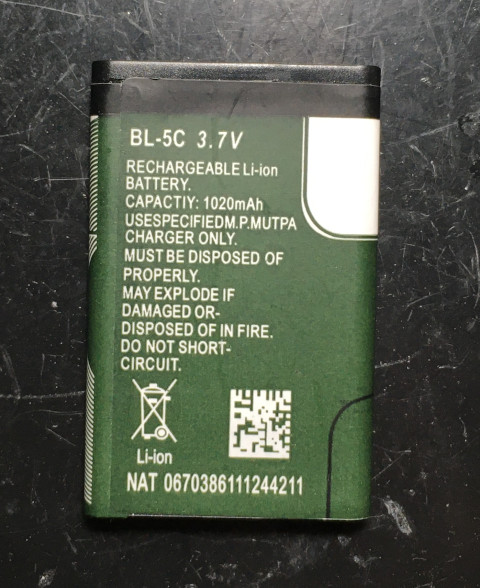

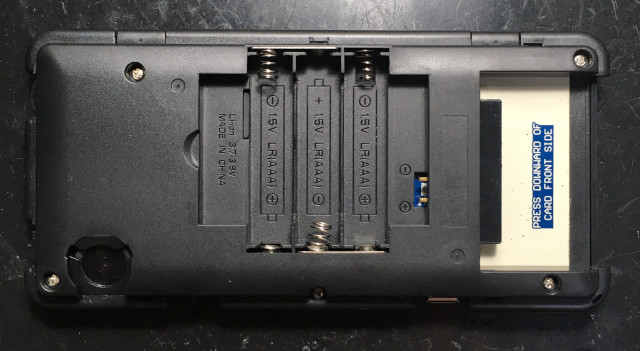

電池:3.7V 1100mA或AAA x 3

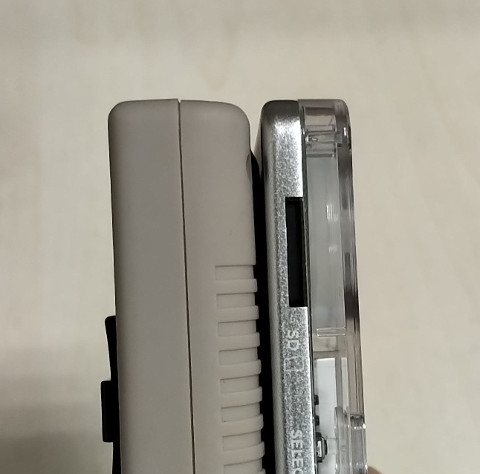

尺寸:140mm x 68mm x 18mm

重量:110克

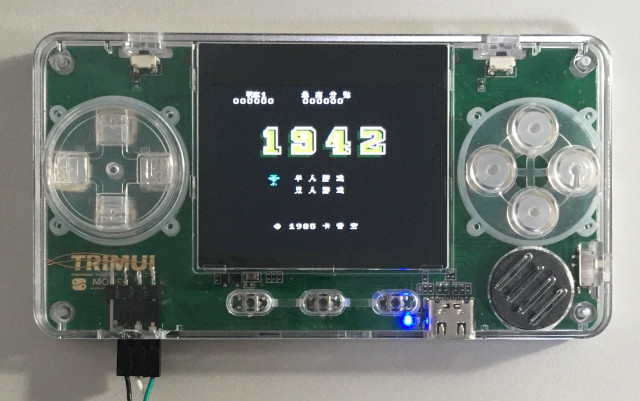

正面

下邊

側邊

上邊

側邊

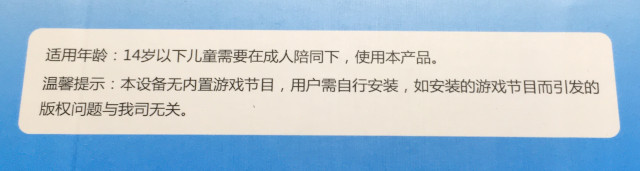

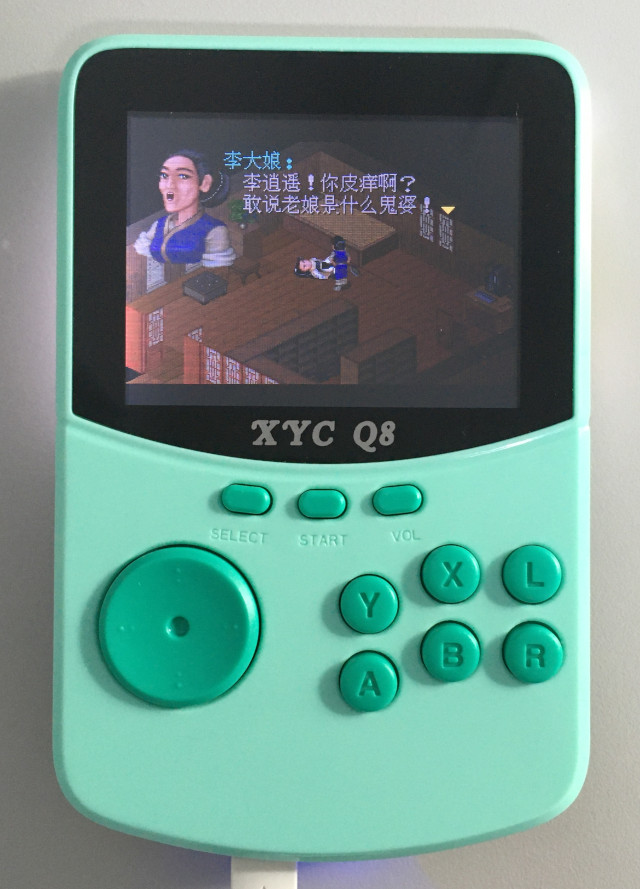

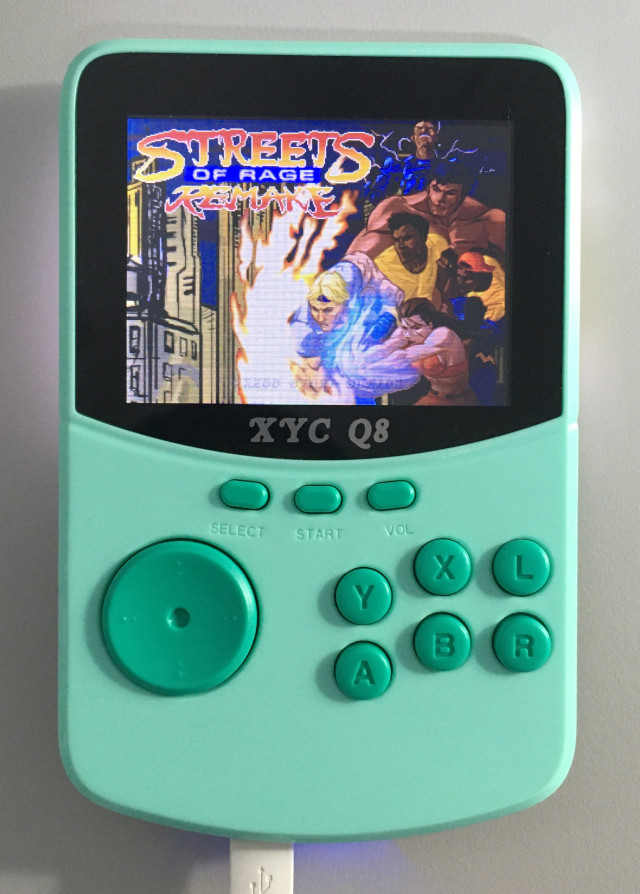

相當感謝背包胖雄告知司徒這台掌機的存在,於是司徒上淘寶看了一下,發現一台才115 RMB,這也太便宜了吧!比起現今的開源掌機,動不動就350 RMB起跳,司徒覺得這麼貴的開源掌機已經變味了,強調的東西已經不是當初開源掌機訴求的模擬樂趣,反而是花錢收藏的詭異現象,除非是司徒相當喜愛的外觀(如:Wiz掌機),否則司徒有錢也不願意購買現今那種昂貴的掌機,不過可能太久沒有買掌機了,司徒竟然不小心,手滑買了4台FC3000掌機

這質感真的相當不錯,完全對得起這個價格

另一個配色也相當好看

Micro USB、AV輸出

沒有東西

L、R按鍵,這設計真是...

電源按鍵、音量按鍵

背面摸起來還蠻舒服的

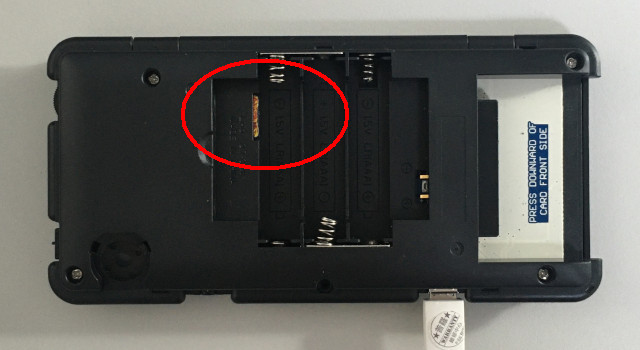

這空間相當適合改機

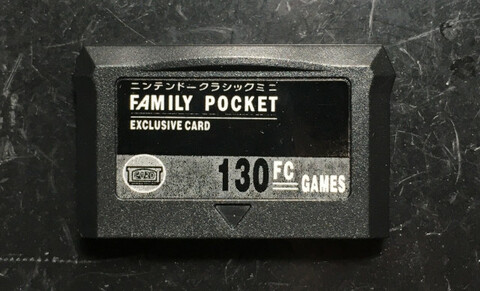

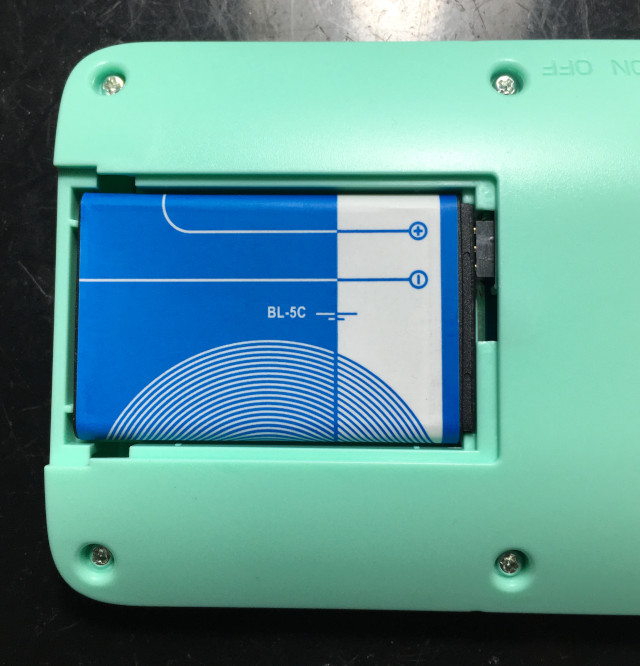

電池和卡帶

BL-5C電池

這卡帶是用來回味童年的嗎?

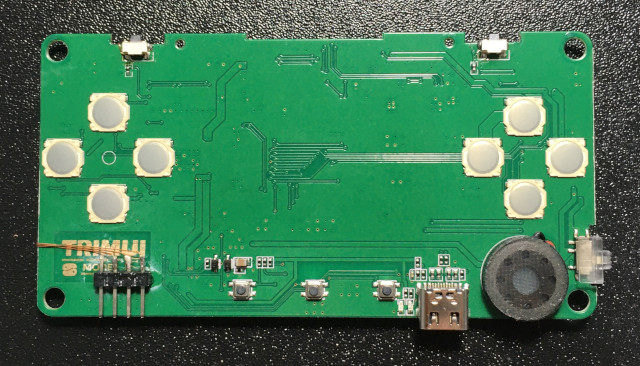

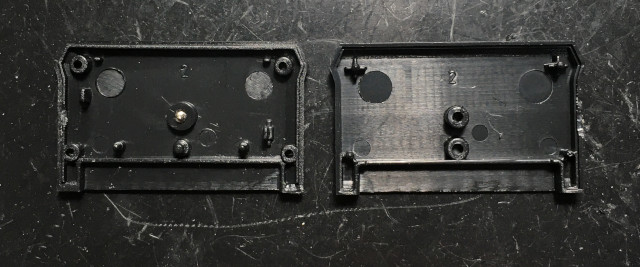

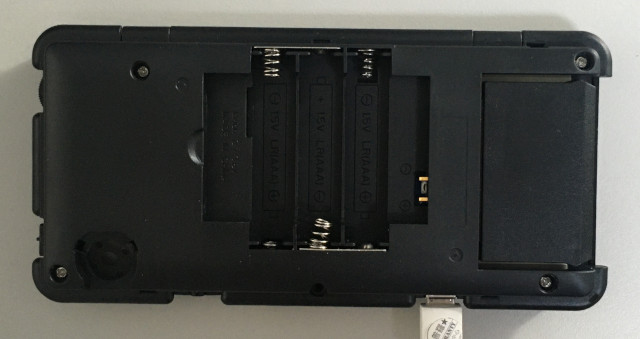

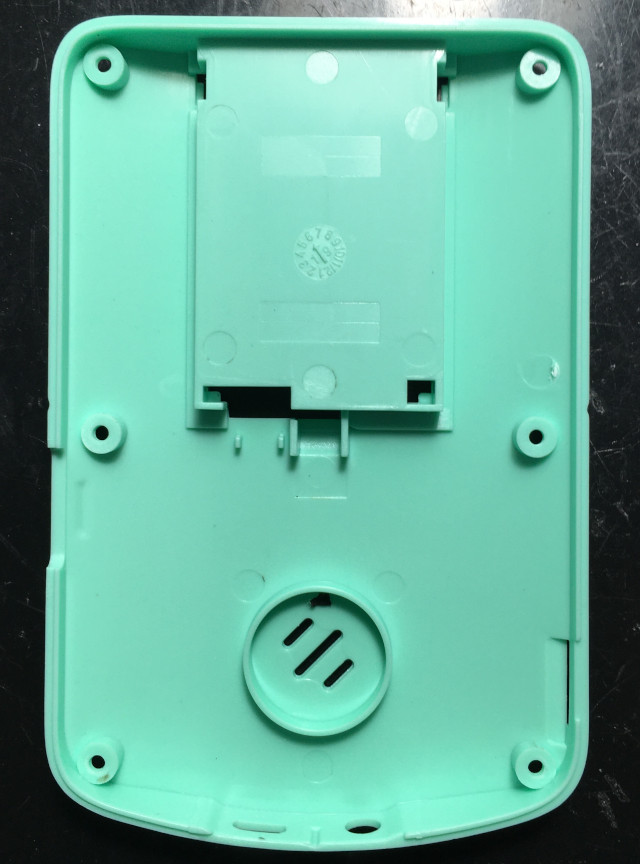

背面

竟然有螺絲,不過,當看到時,已經被司徒爆力拆解了

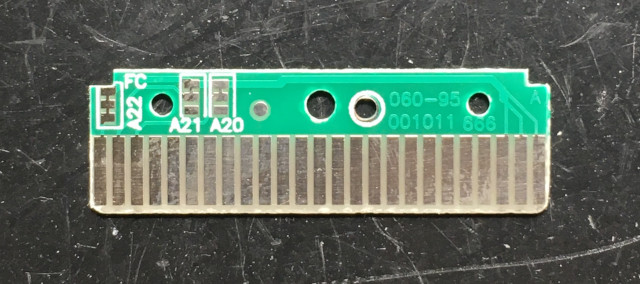

A21?這難道是1MB記憶體擴充?

背面

司徒已經很久沒有看到這長的螺絲了...

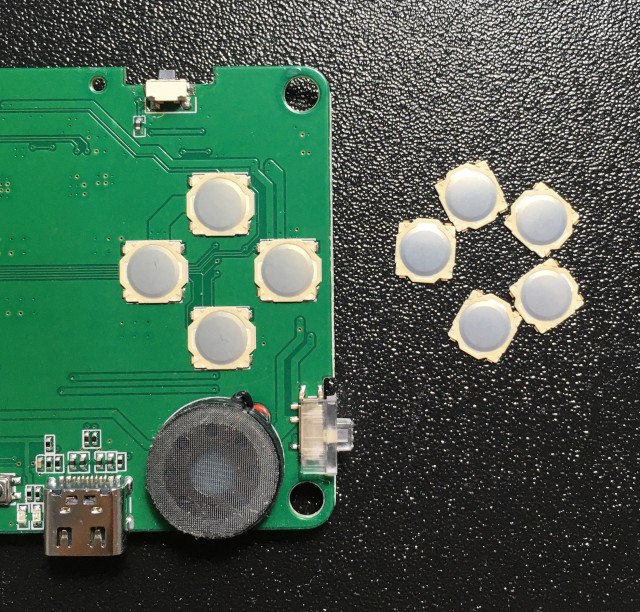

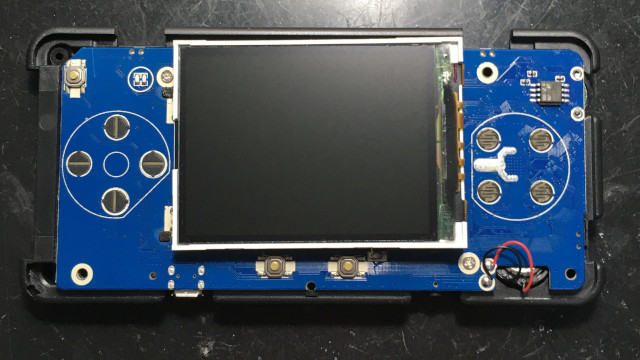

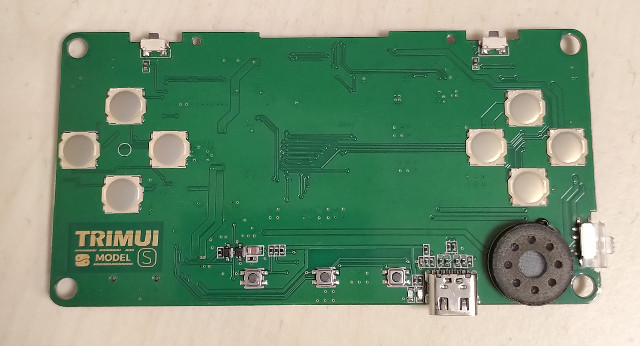

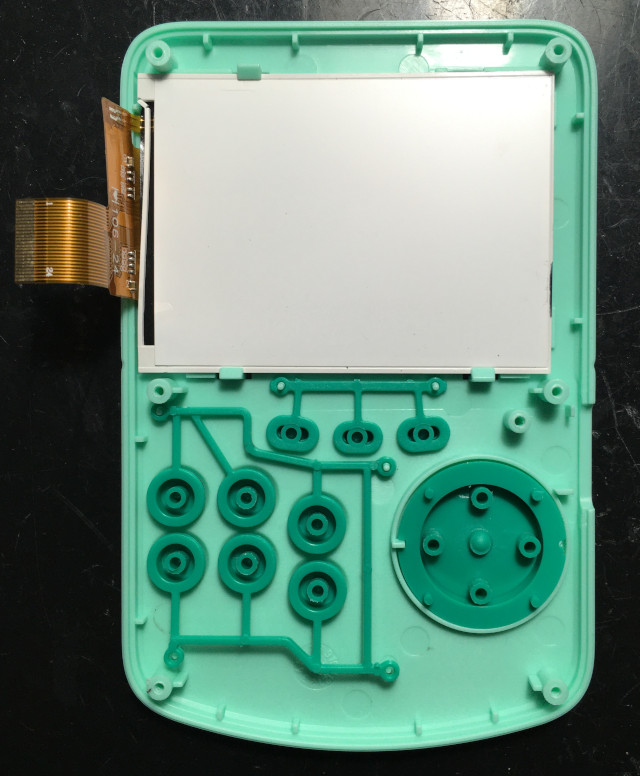

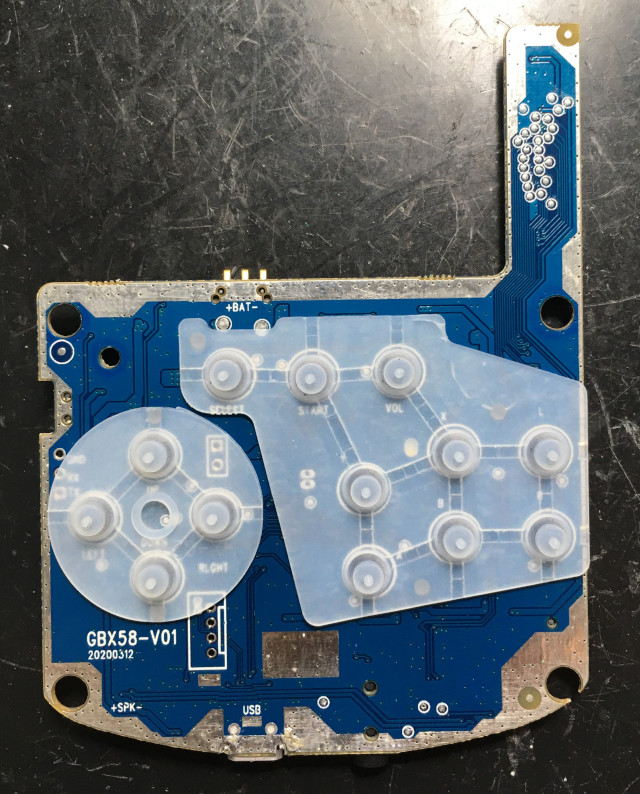

A面

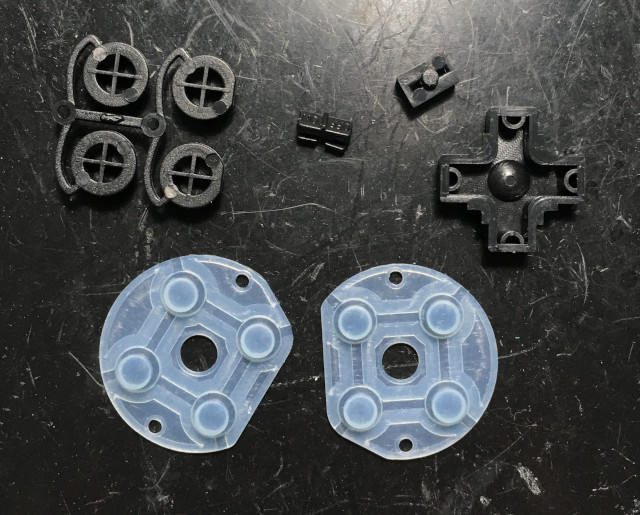

按鍵導電膠,這導電膠有點軟

十字鍵缺乏支撐點

正面

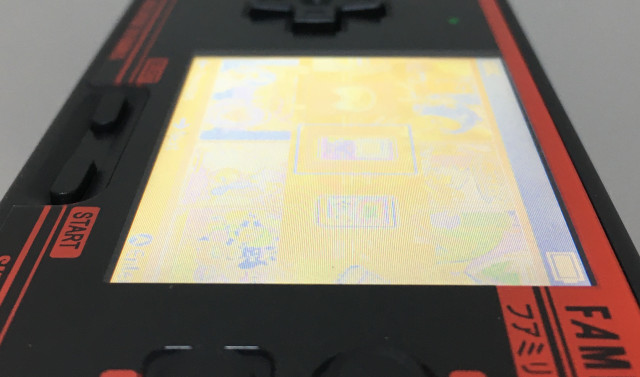

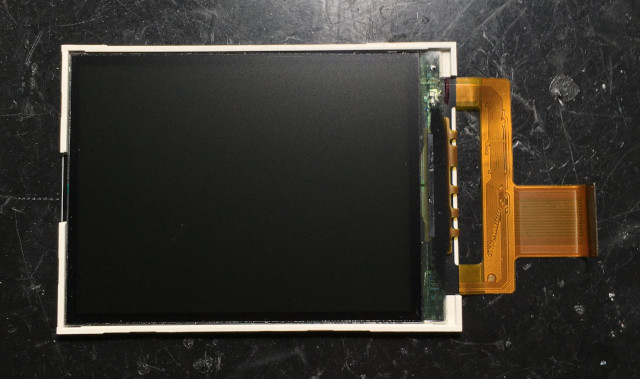

霧面屏

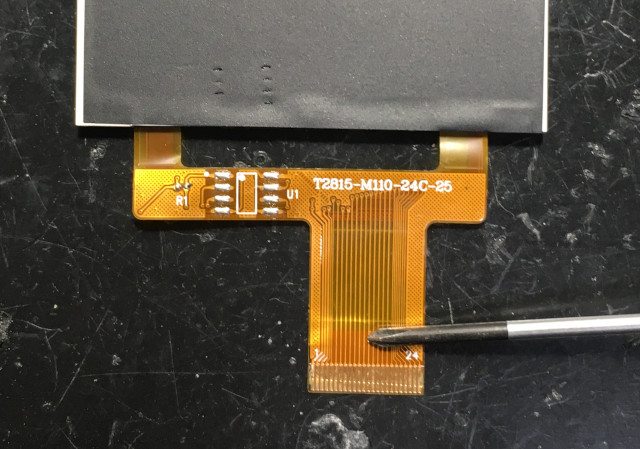

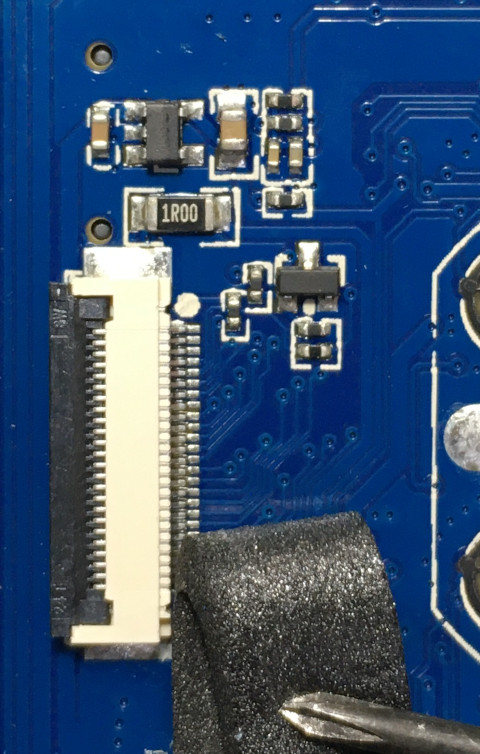

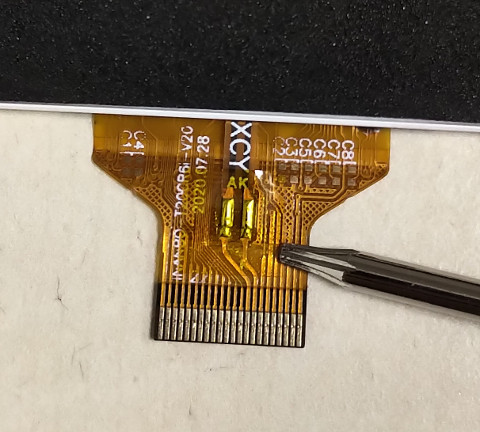

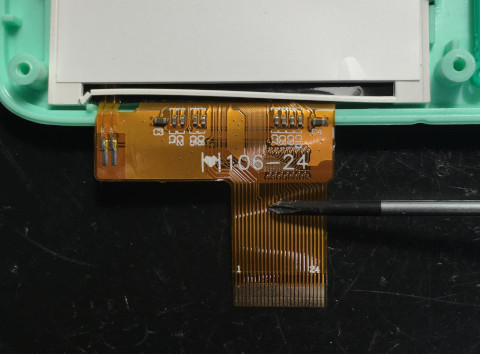

24Pin排線

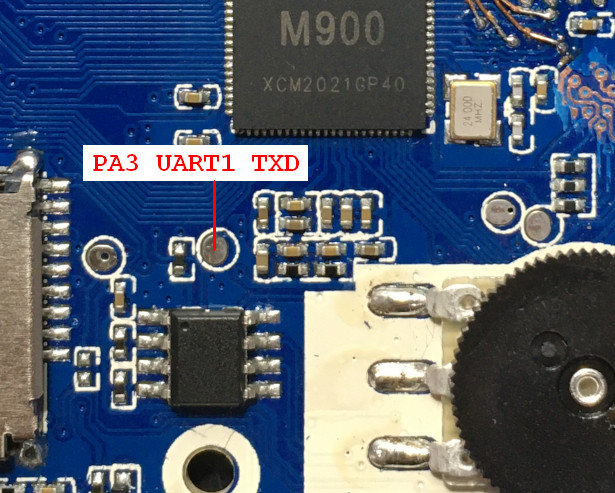

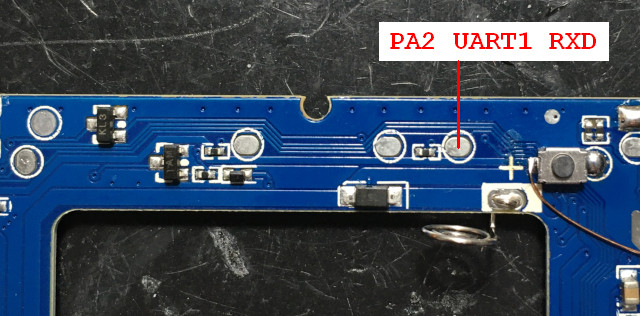

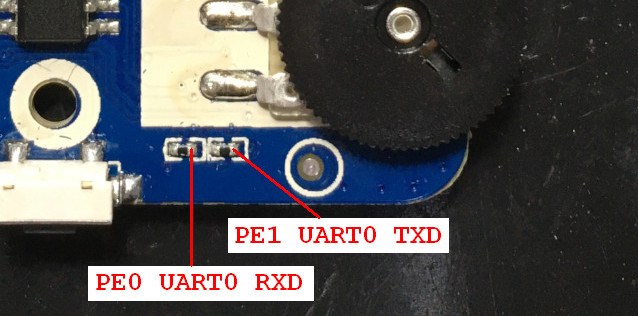

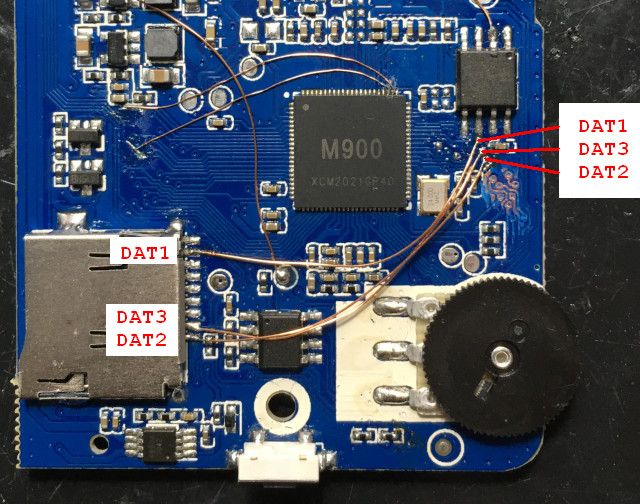

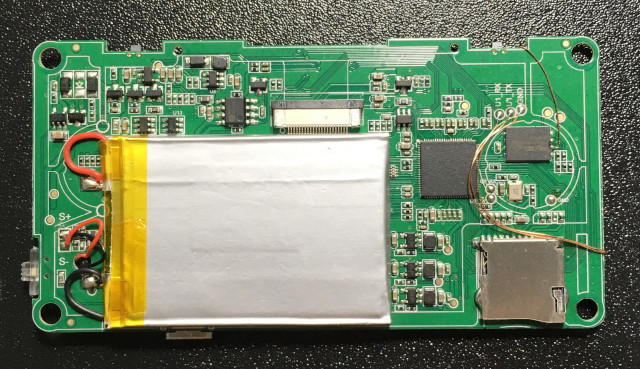

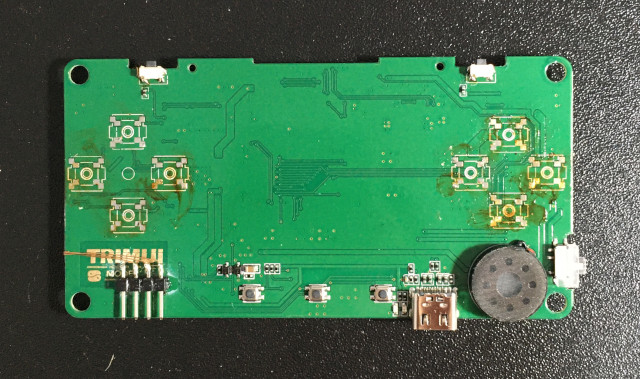

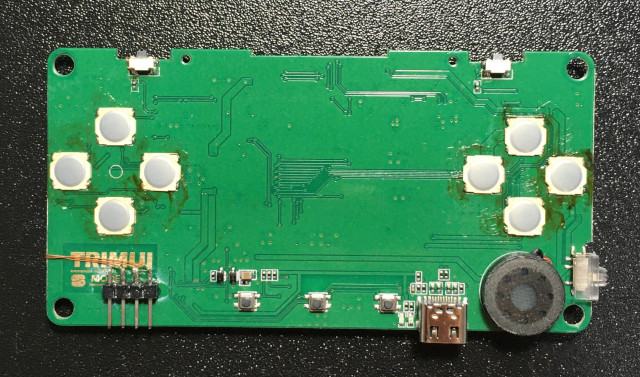

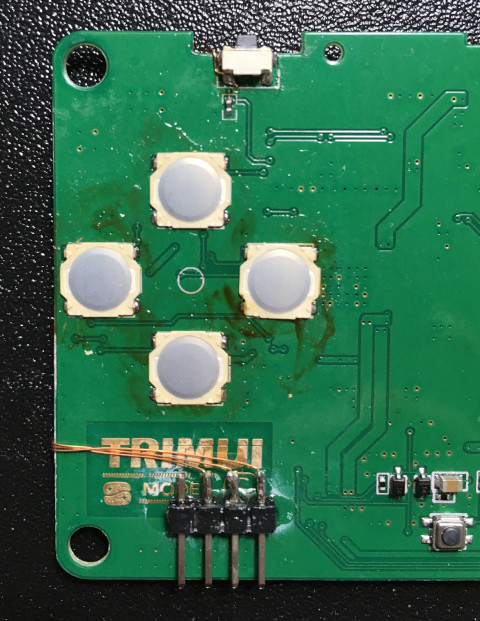

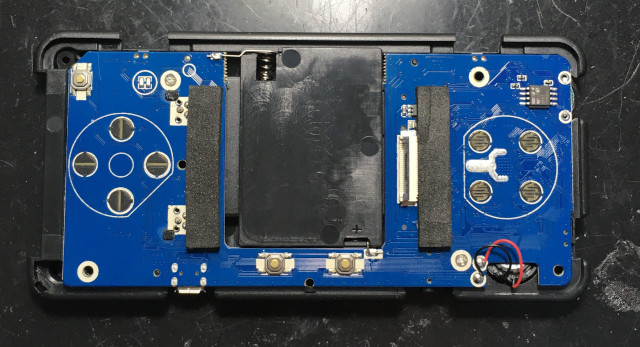

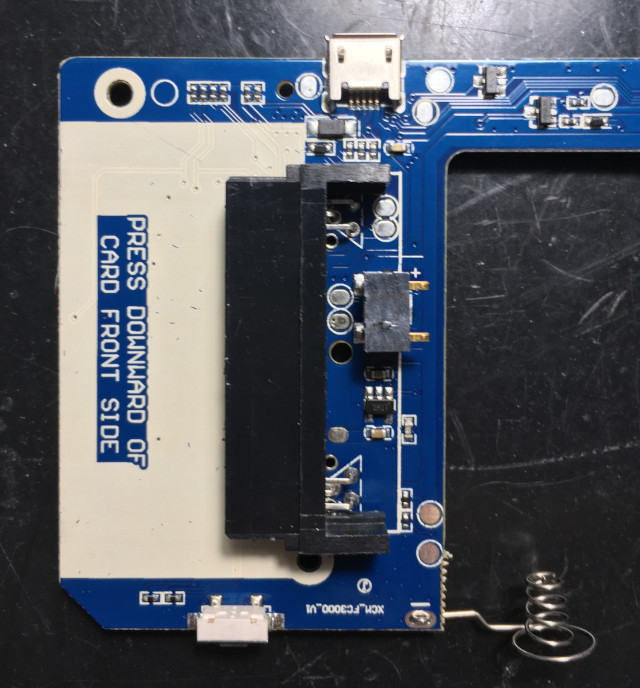

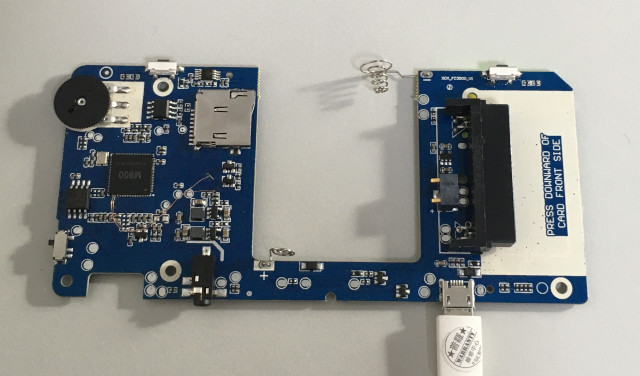

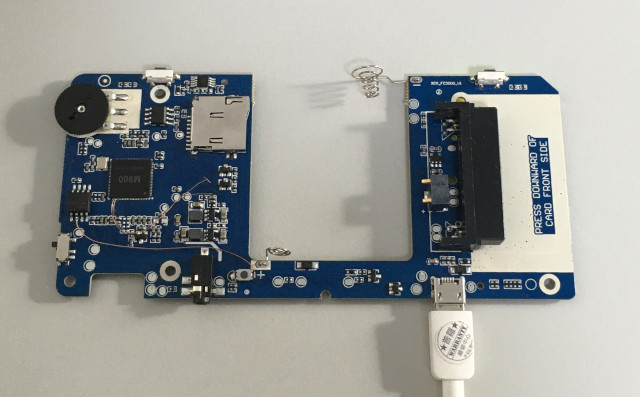

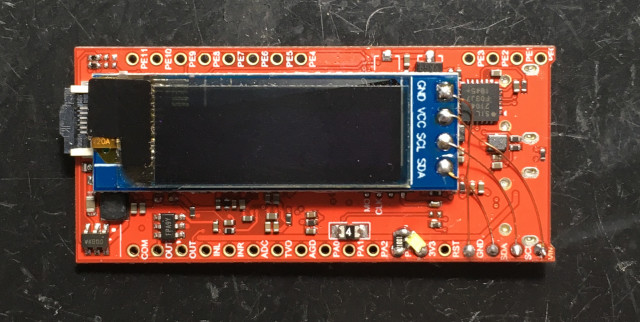

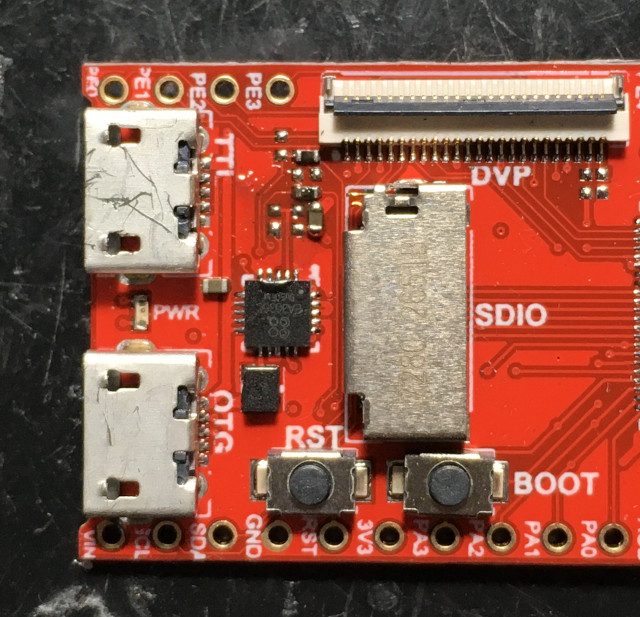

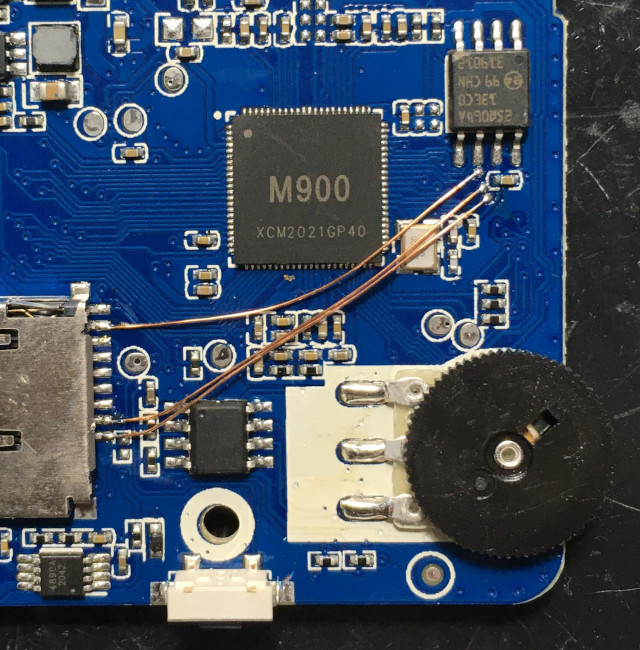

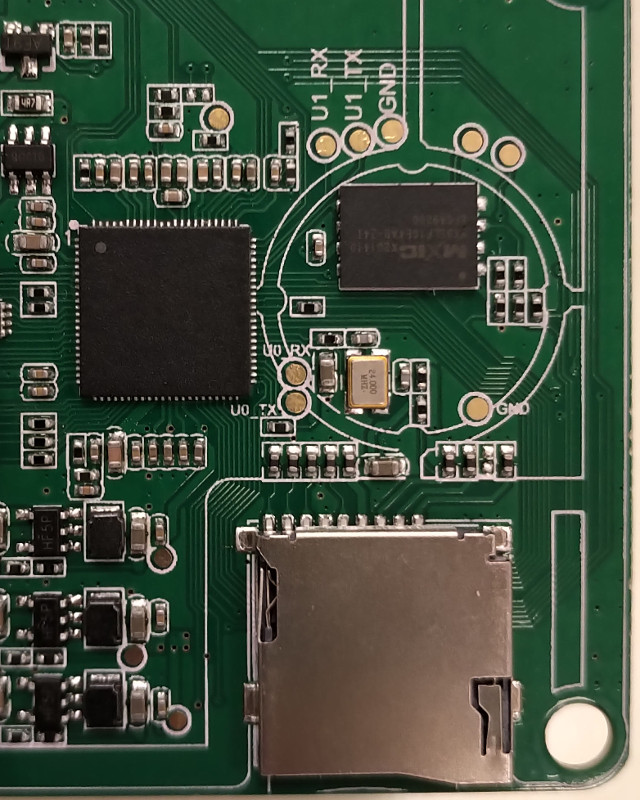

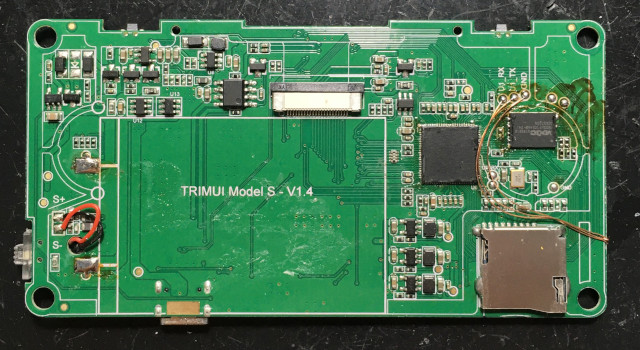

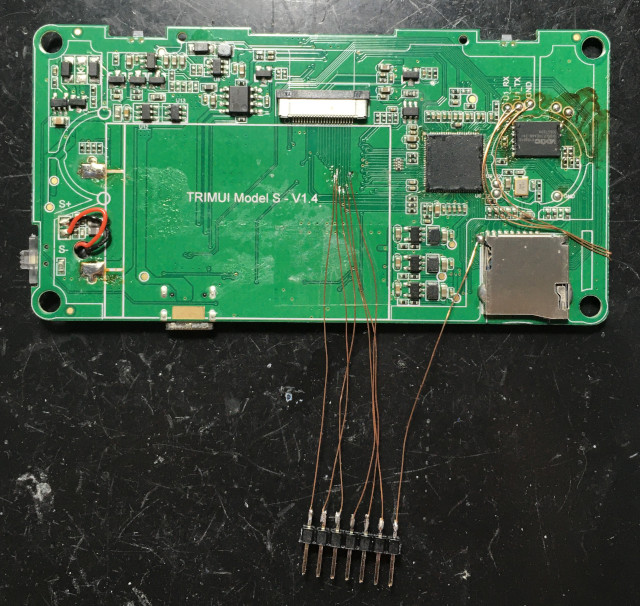

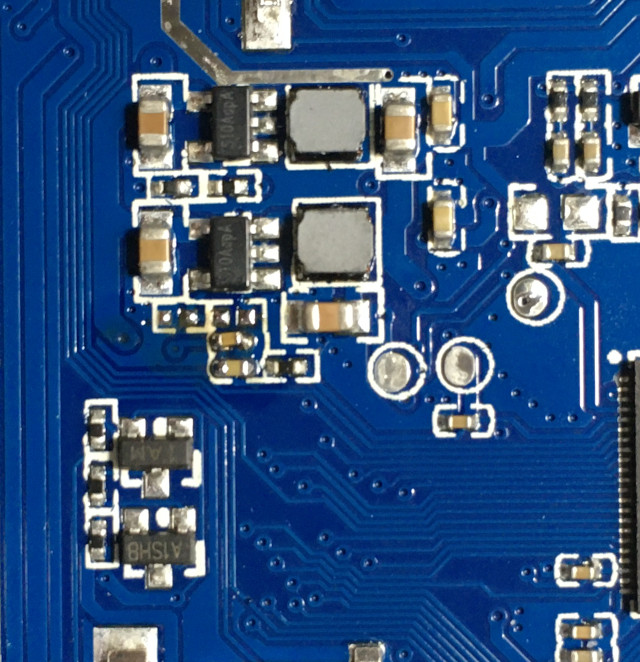

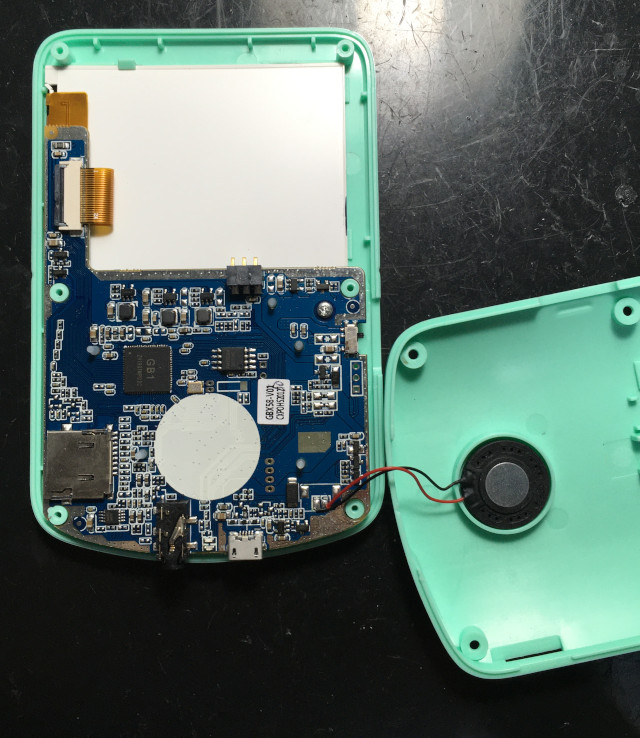

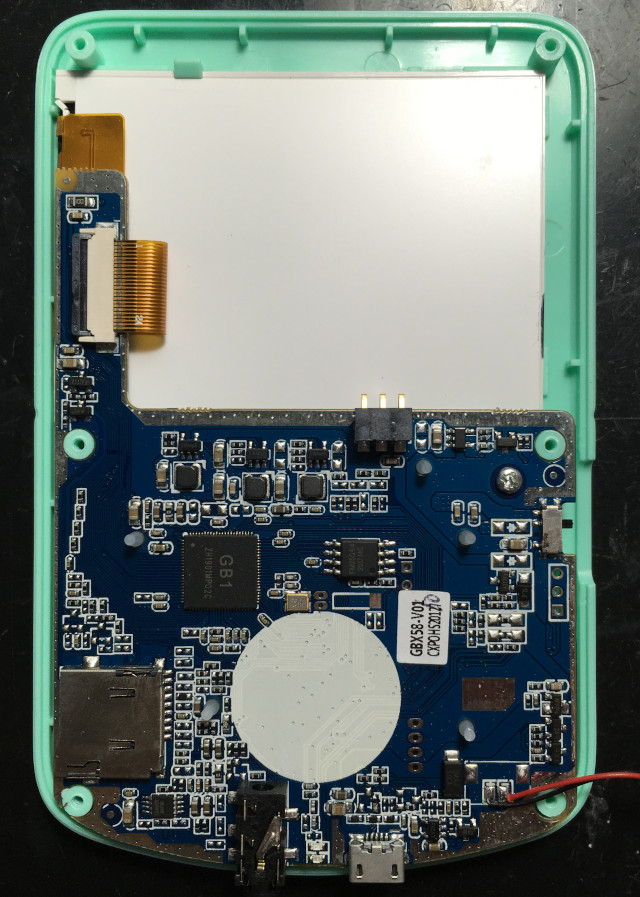

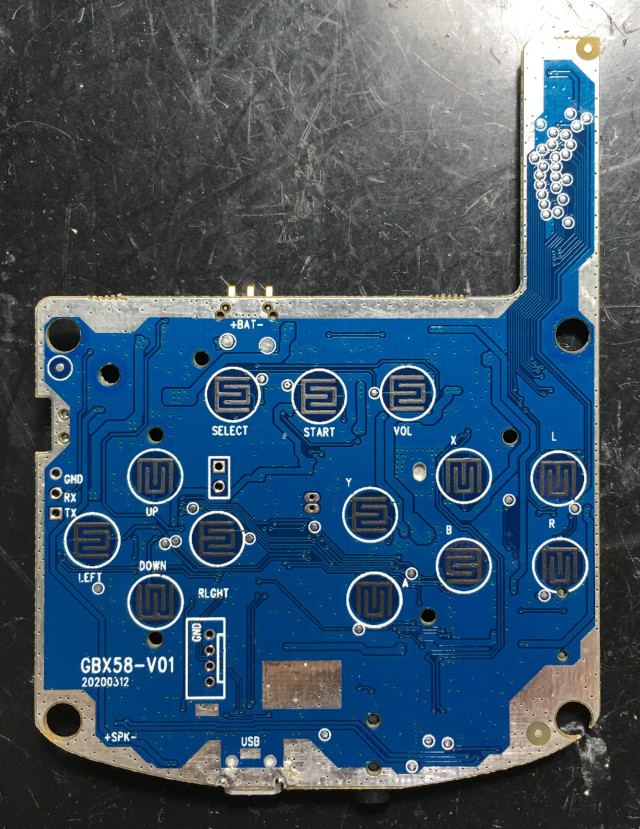

PCB

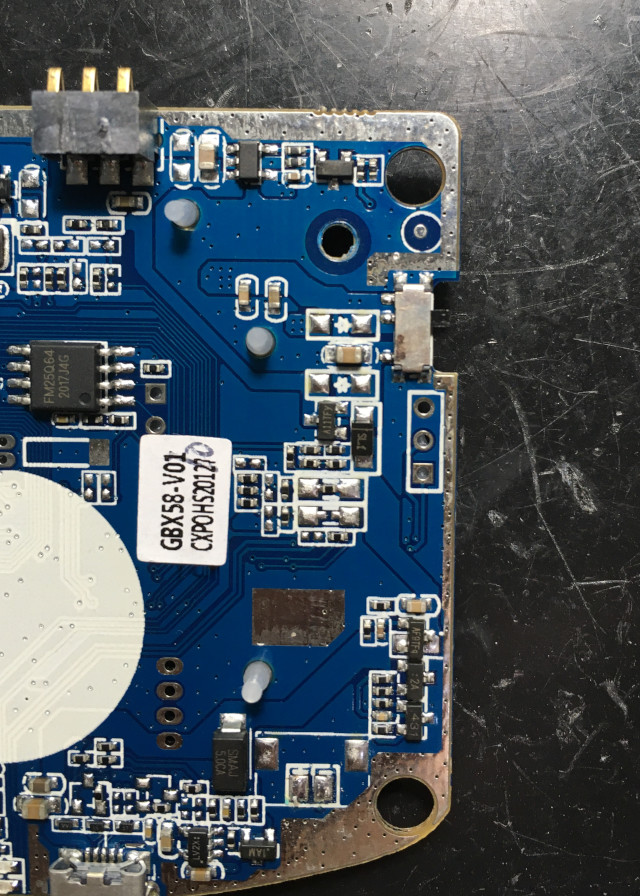

背光電路

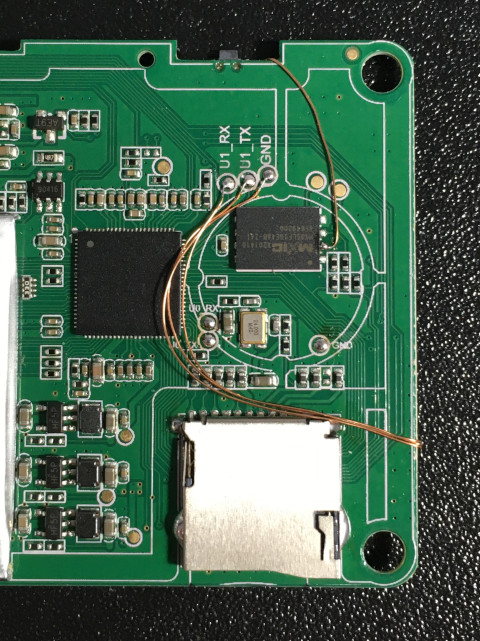

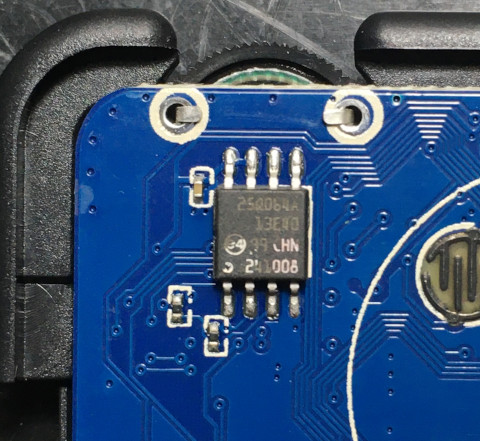

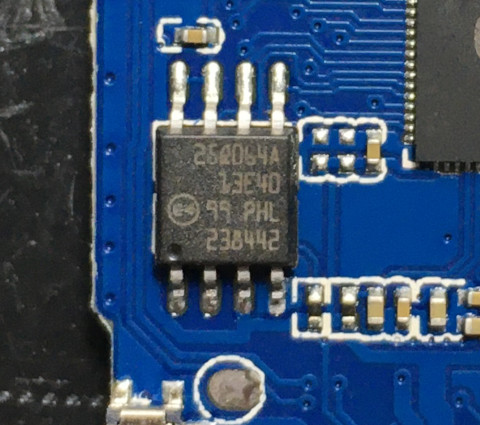

25Q064A

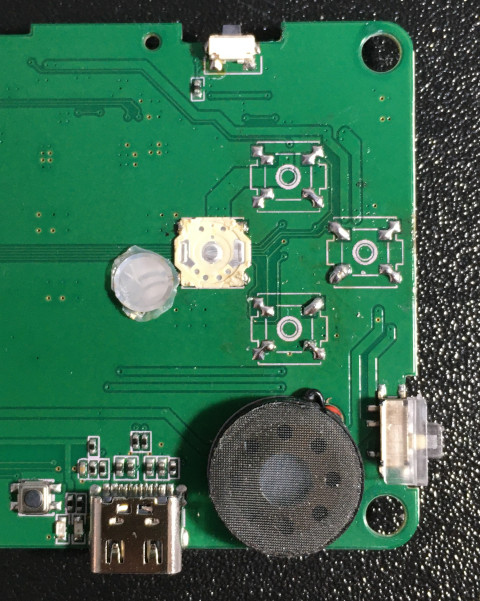

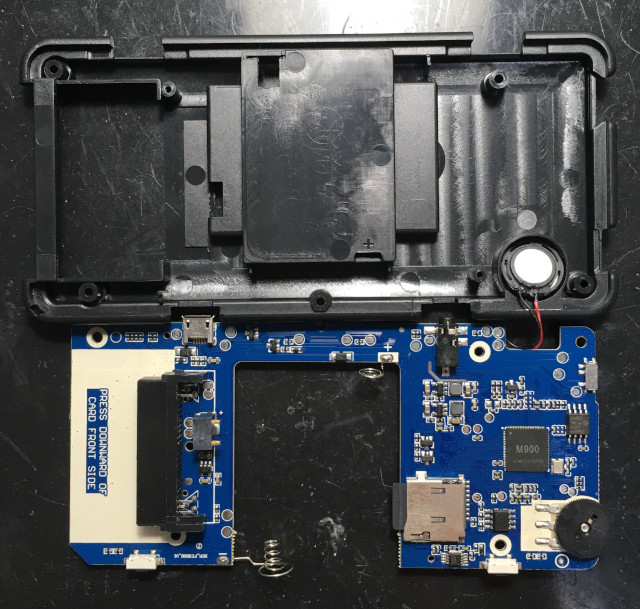

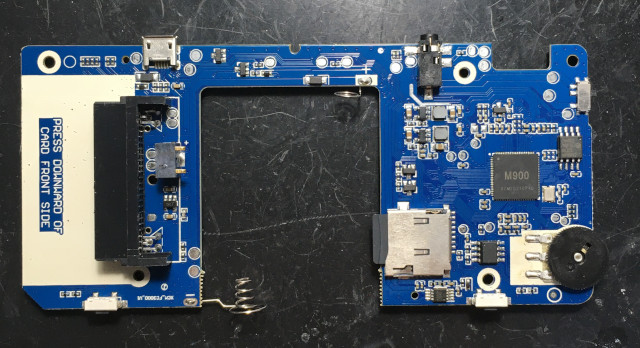

PCB

斜面喇吧

PCB

側邊

側邊

另一顆25Q064A

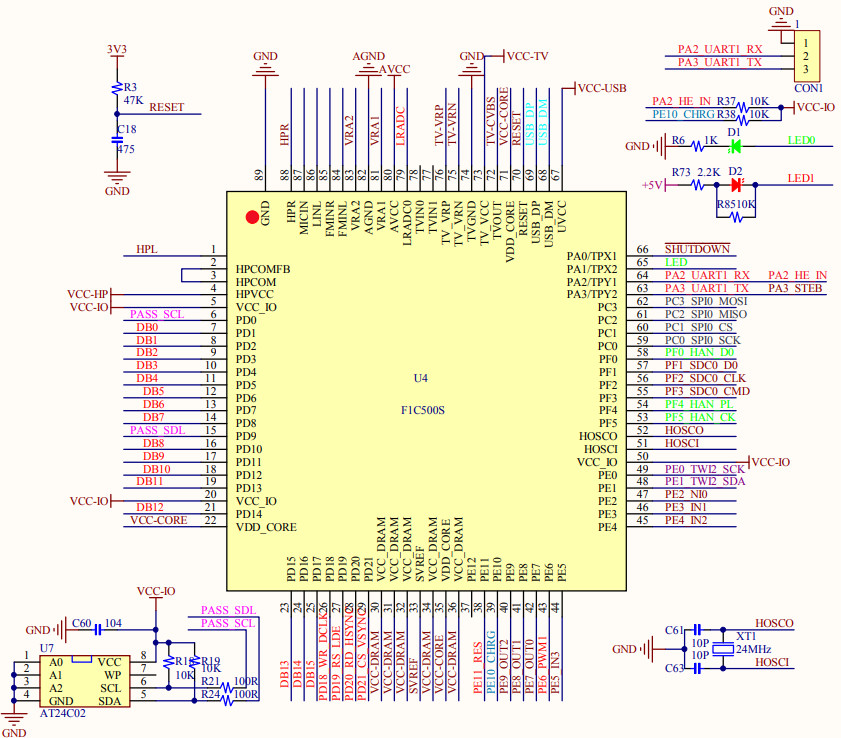

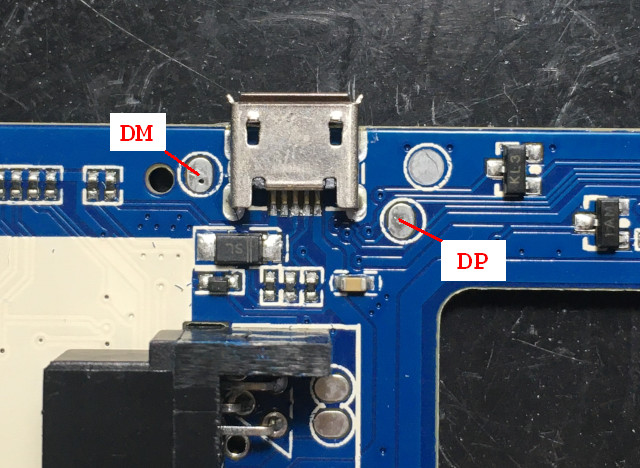

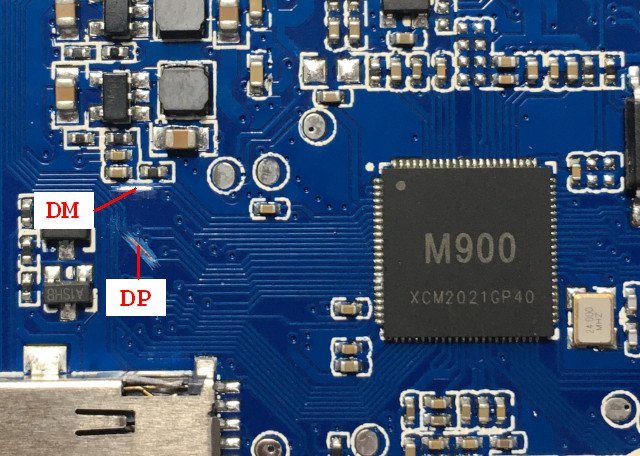

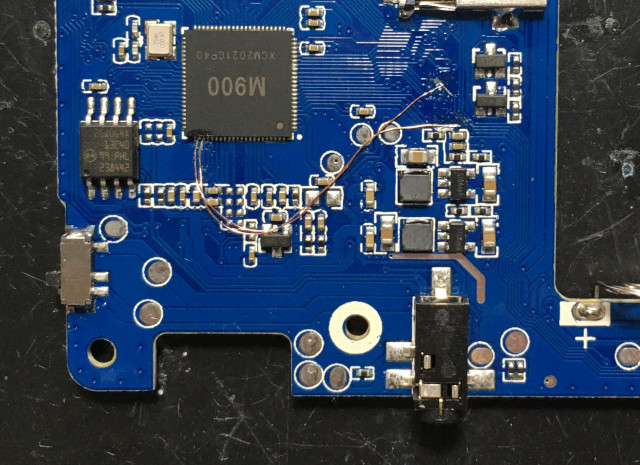

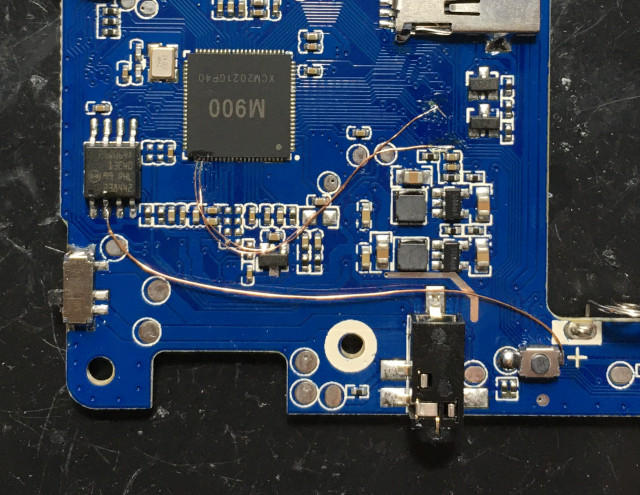

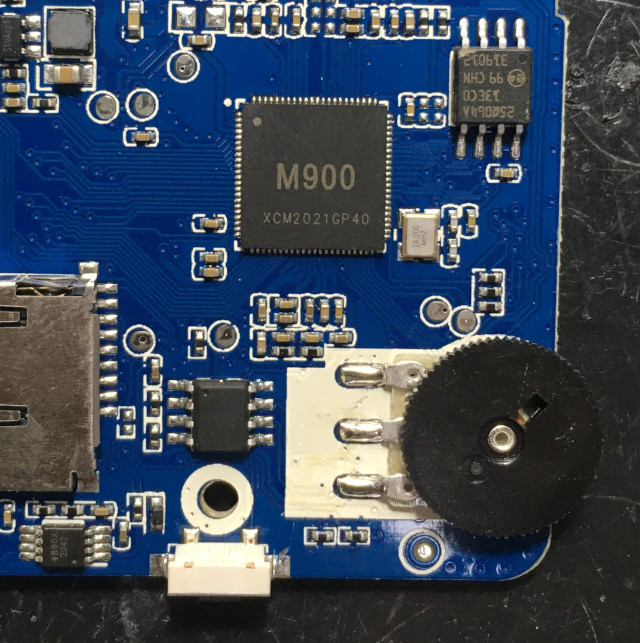

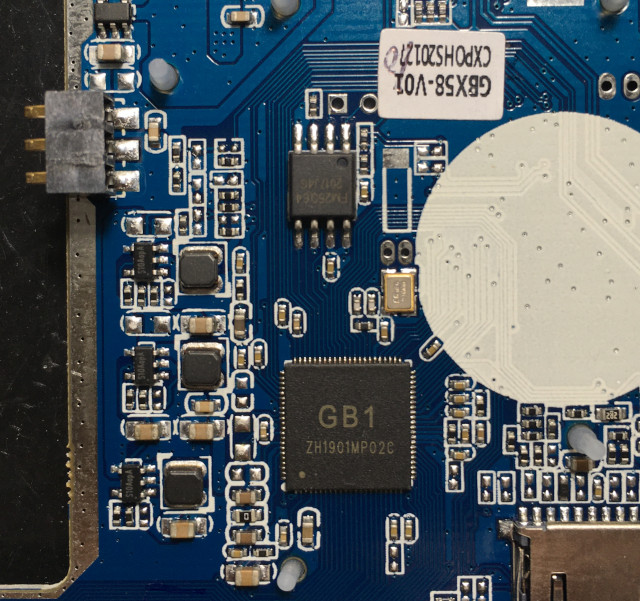

M900,其實仔細一看腳位,對照一下Miyoo電路圖,就知道是Allwinner F1C100S

2腳、3腳短路

30腳、31腳、32腳是DRAM-VCC

51腳、52腳是振盪器

59腳、60腳、61腳、62腳是啟動SPI Flash

Miyoo電路圖

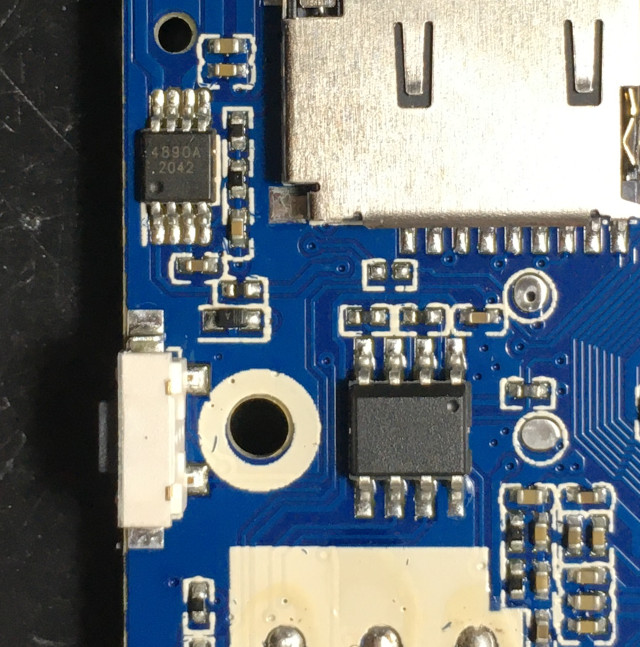

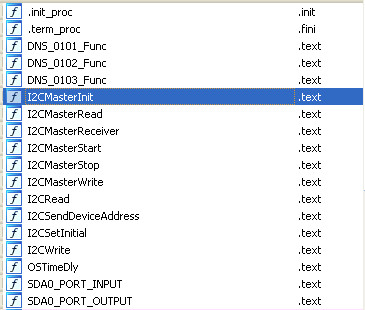

LM4890、加密IC

MicroSD

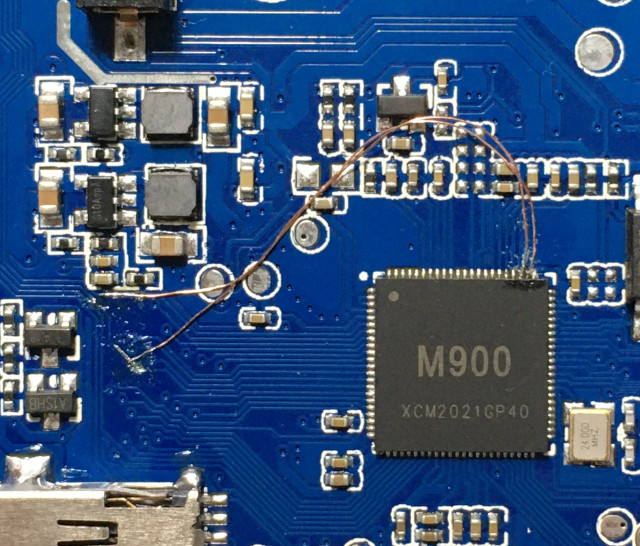

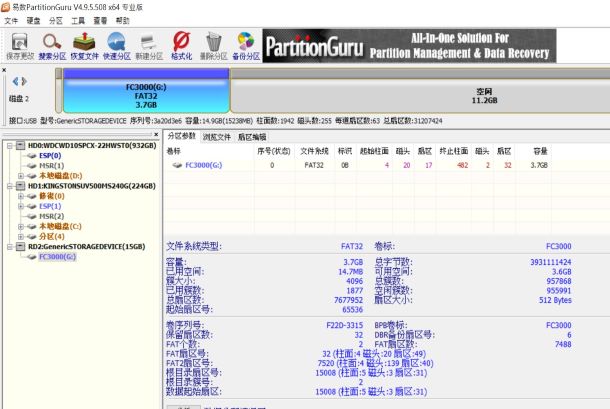

這張MicroSDC看來只存放模擬器相關的東西

离线

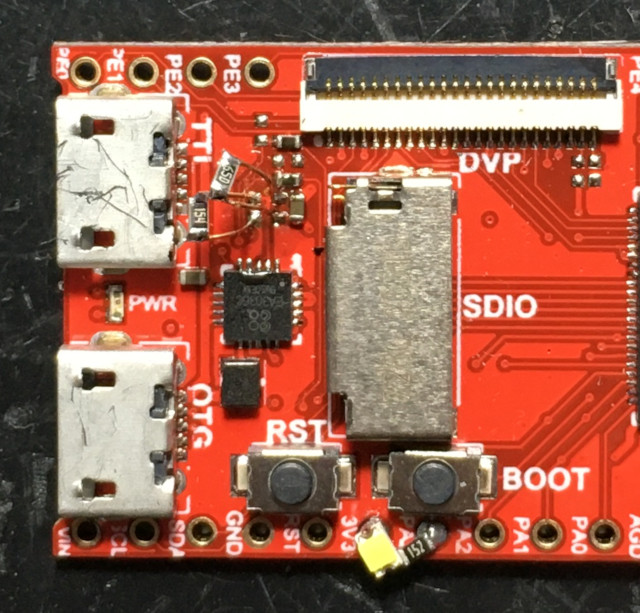

楼主 #1 2021-06-10 22:27:14 分享评论

Re: 研究FC3000掌機的開源可行性

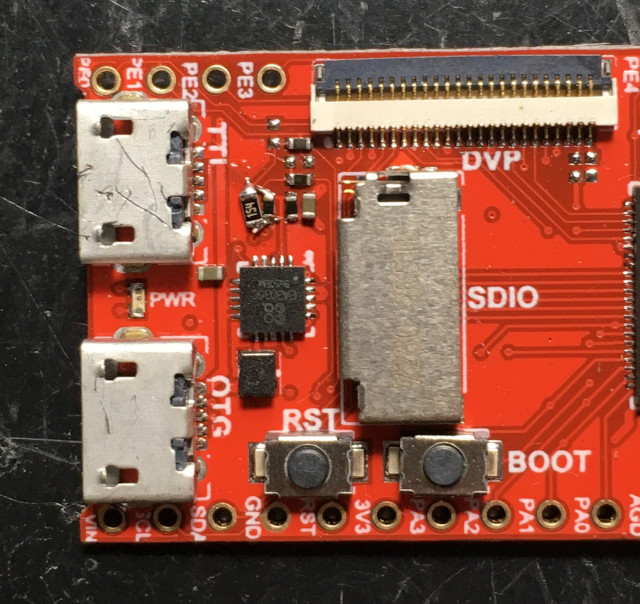

原本的USB D-是接到PD0、D+是接到PD9

為了可以進行USB下載,司徒只好把線割了

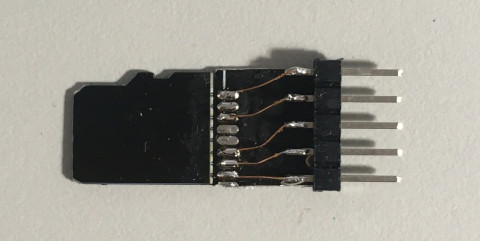

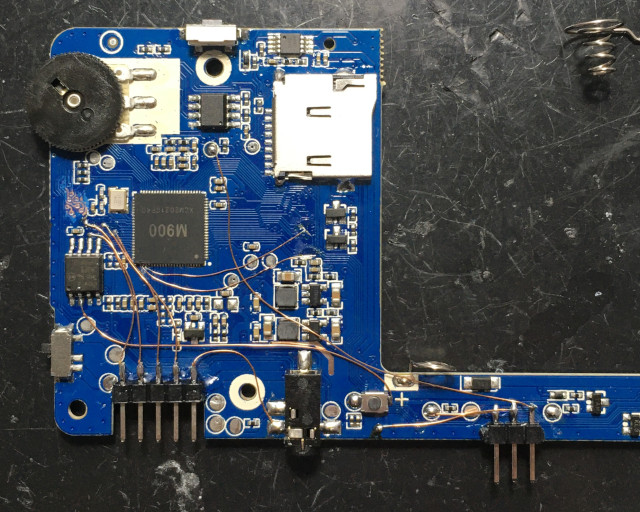

跳線

接著短路SPI Flash第1腳跟第2腳,然後上電

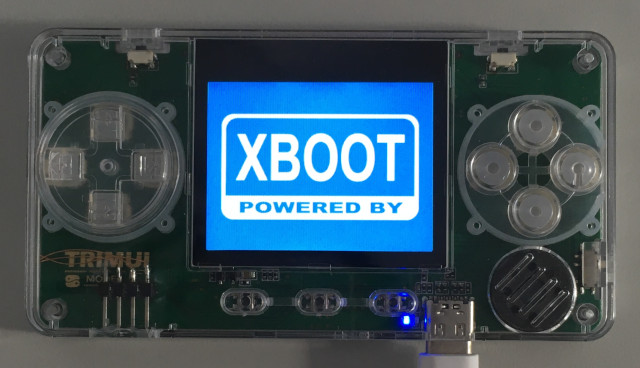

進入燒錄模式

$ sudo dmesg -c

[50227.418454] usb 1-1: USB disconnect, device number 115

[50302.847603] usb 1-1: new full-speed USB device number 116 using xhci_hcd

[50302.996616] usb 1-1: New USB device found, idVendor=1f3a, idProduct=efe8, bcdDevice= 2.b3

[50302.996620] usb 1-1: New USB device strings: Mfr=0, Product=0, SerialNumber=0

$ lsusb

Bus 001 Device 116: ID 1f3a:efe8 Onda (unverified) V972 tablet in flashing mode离线

#3 2021-06-11 08:13:28 分享评论

- 三木同子

- 会员

- 注册时间: 2020-06-09

- 已发帖子: 42

- 积分: 32

Re: 研究FC3000掌機的開源可行性

不知道为什么图片都看不到

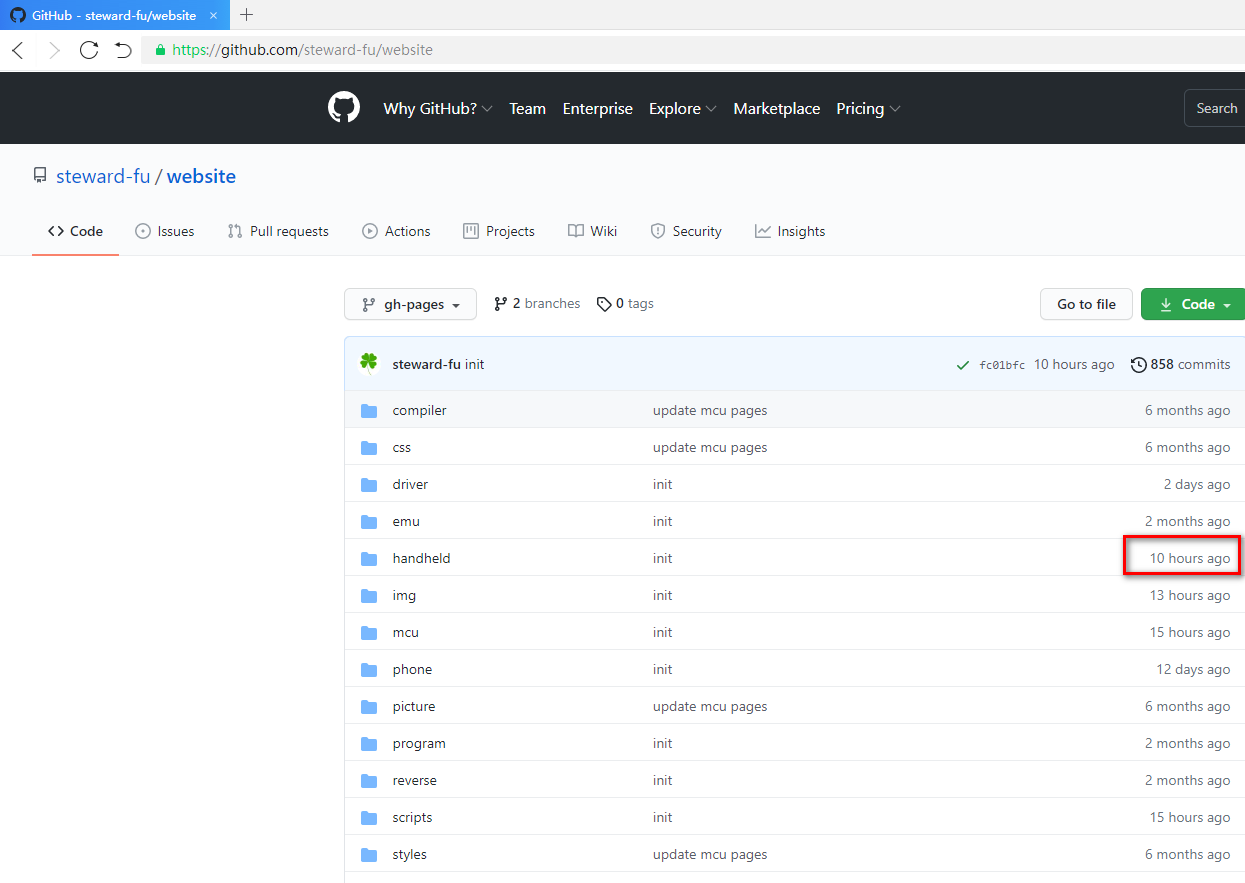

其实都有关注司徒的网站,但不知道更新了什么,每次都要先从github看时间,再去网站查看对应的更新

离线

楼主 #4 2021-06-11 08:47:57 分享评论

楼主 #5 2021-06-11 09:02:34 分享评论

楼主 #6 2021-06-11 10:11:33 分享评论

Re: 研究FC3000掌機的開源可行性

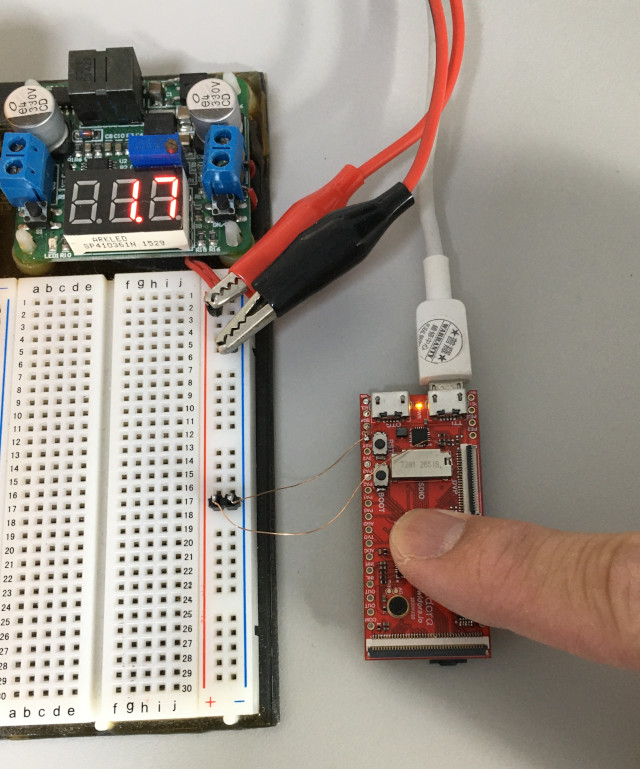

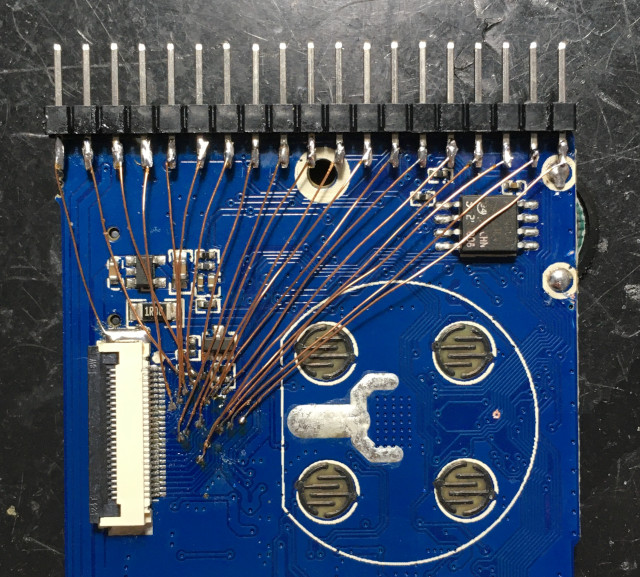

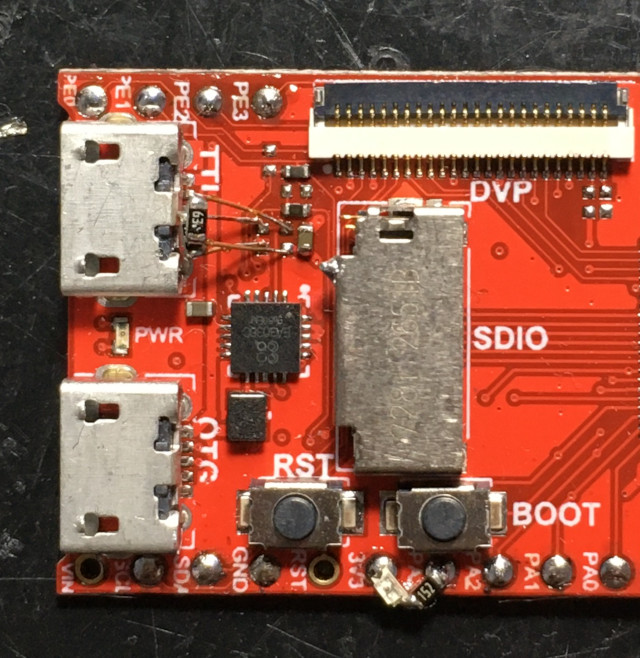

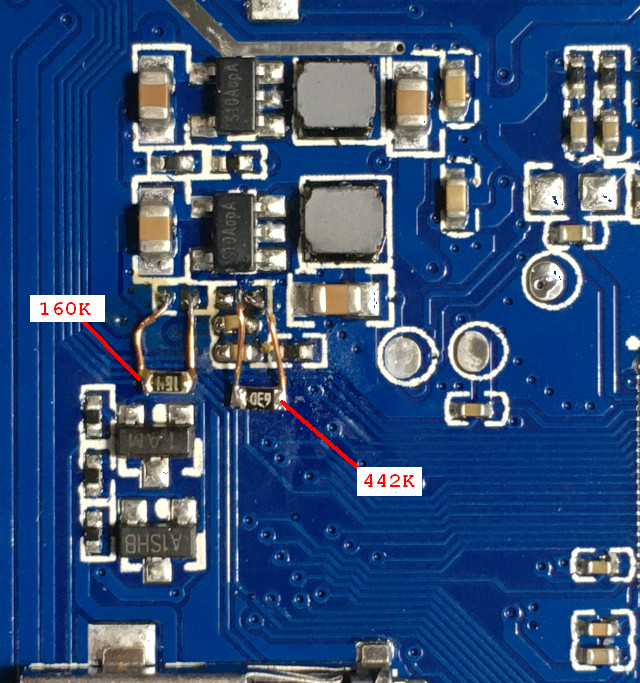

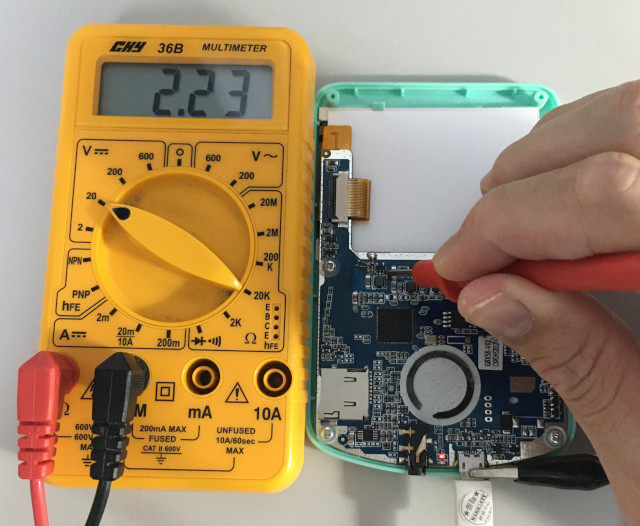

司徒量測了一下按鍵,發現沒有適合可用,因此,決定焊接一顆獨立燒錄按鍵,因此,找到一塊風水寶地

完成,之後只要按下按鍵開機,即可進入燒錄模式

進入燒錄模式

執行如下命令

$ sunxi-fel -p spiflash-read 0 8388608 boot_spiflash.img

100% [================================================] 8389 kB, 193.6 kB/s离线

楼主 #7 2021-06-11 12:55:29 分享评论

Re: 研究FC3000掌機的開源可行性

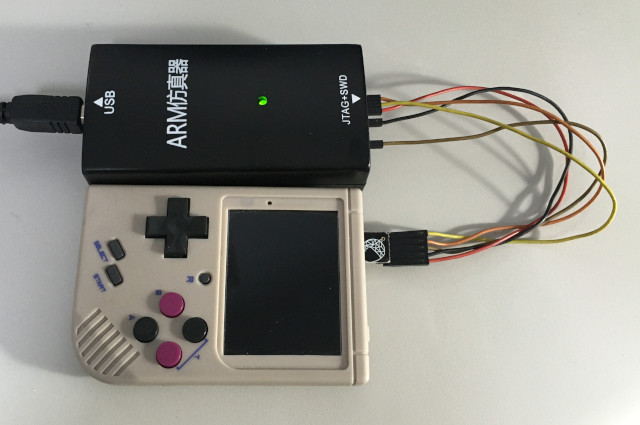

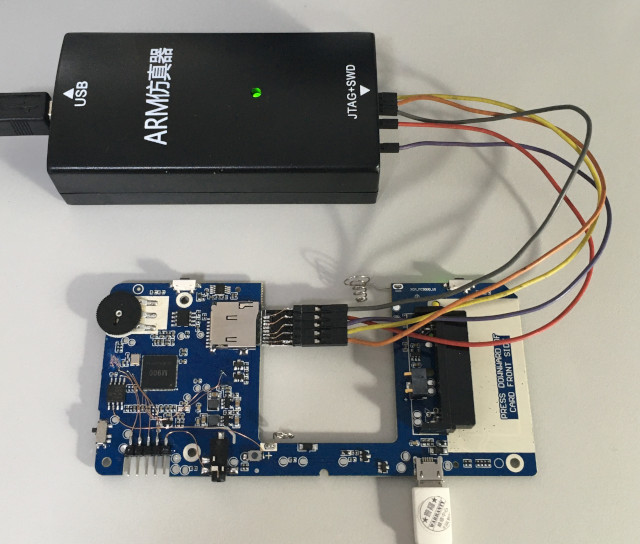

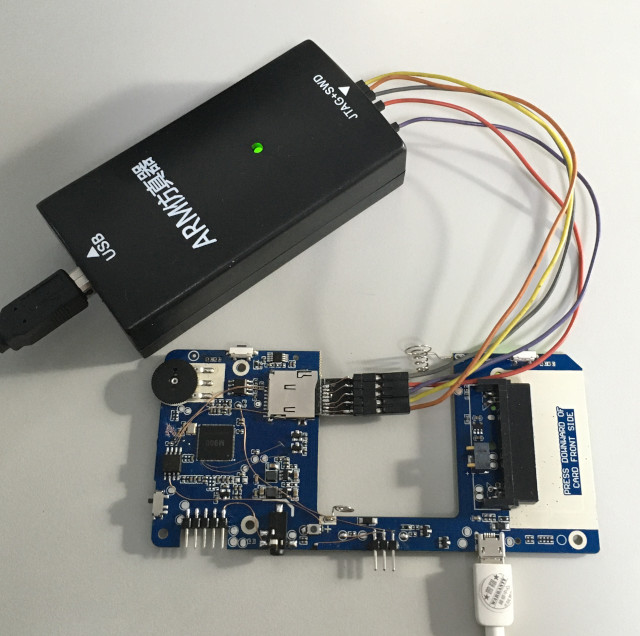

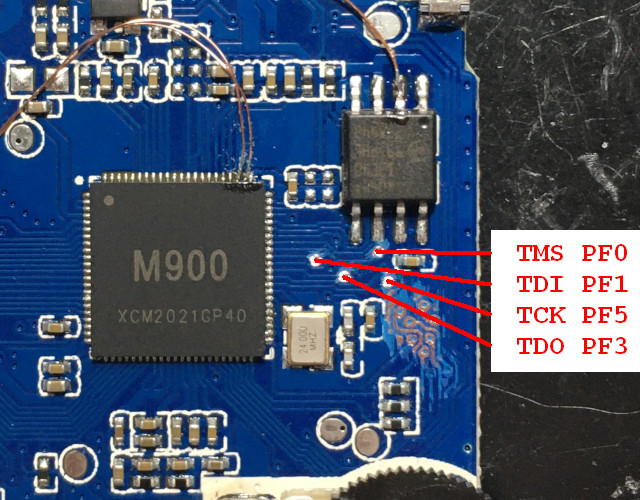

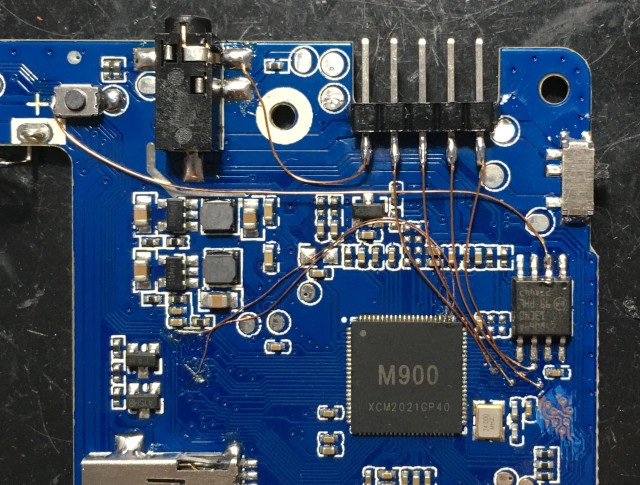

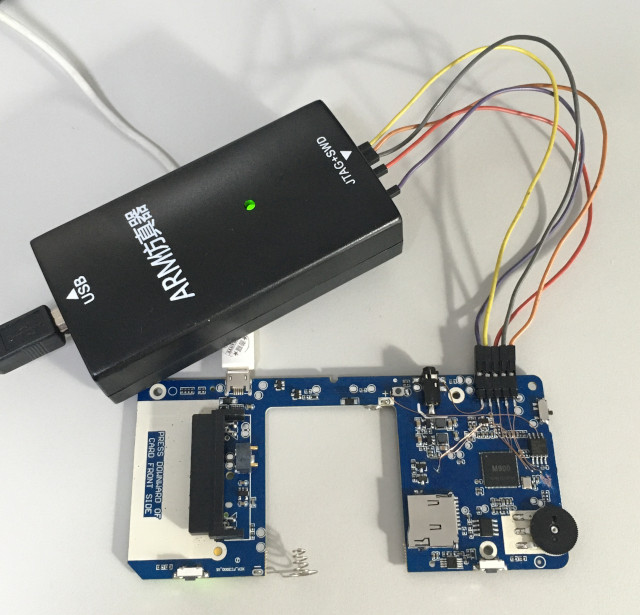

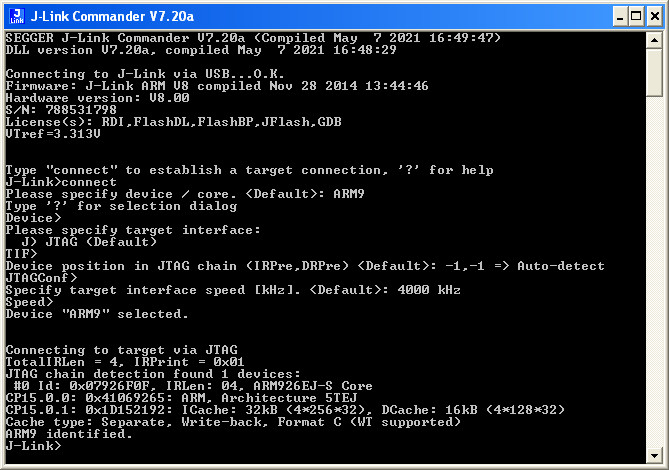

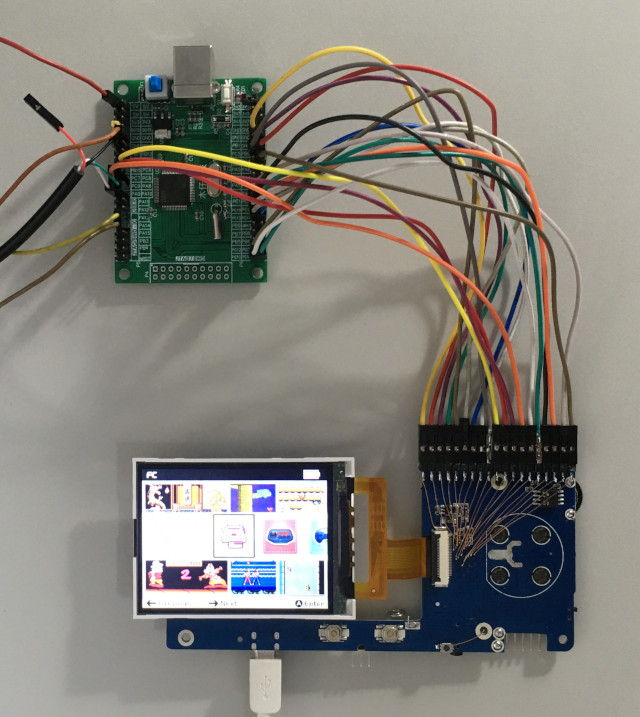

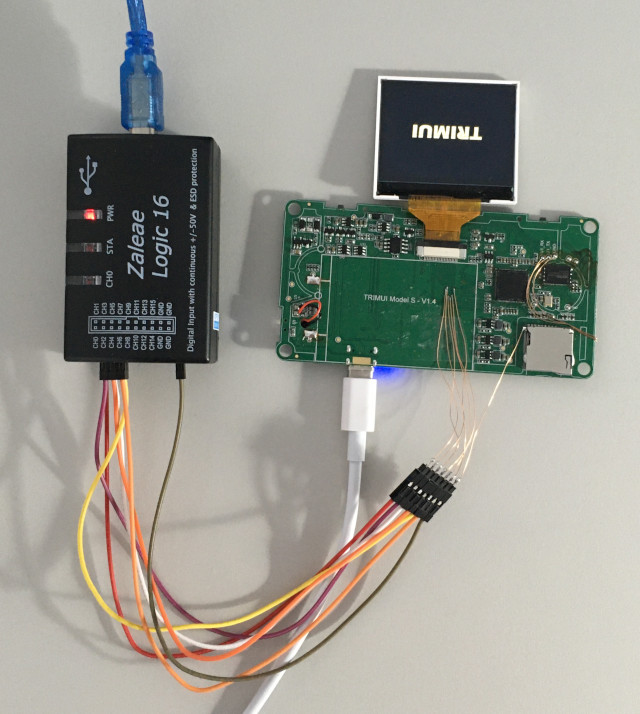

正所謂工欲善其事,必先利其器,目前已經確定CPU是F1C100S,也就是可以確定百分百可以把開源的東西移植上來,畢竟有荔枝派Nano這麼優秀的開源專案在,不過,如果可以把點屏的事情搞定,那才可以稱得上一部比較完美的開源掌機,因此,司徒參考暈哥其他篇文章關於JTAG的介紹,也製作了JTAG連接,這樣至少就可以開始單步除錯原廠的韌體程式

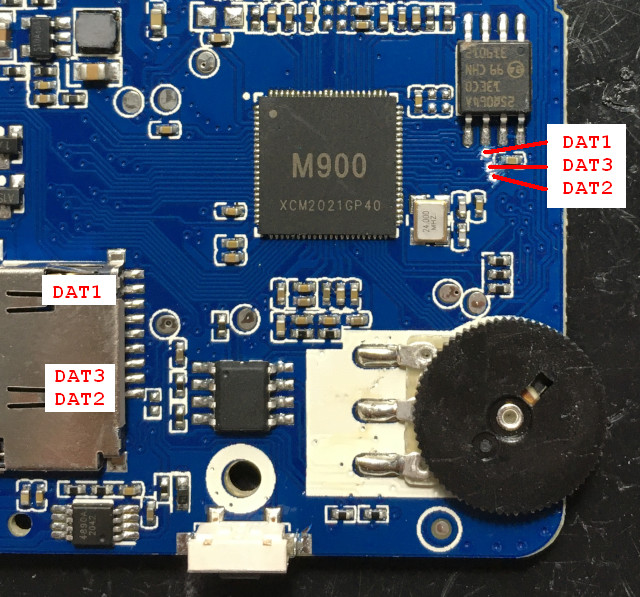

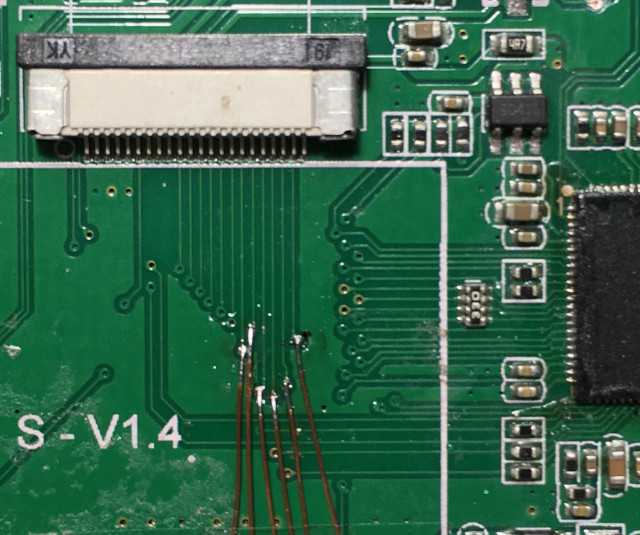

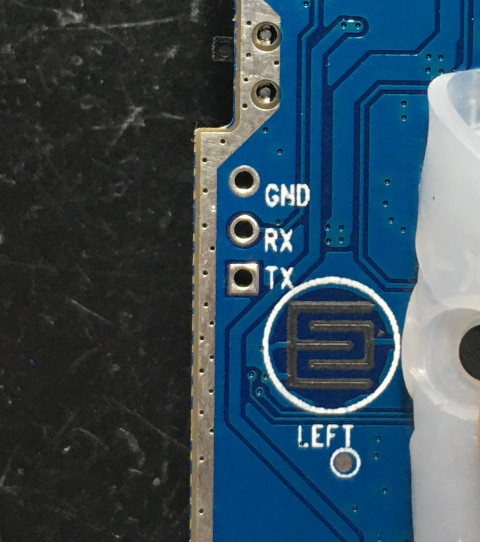

由於JTAG腳位與MicroSD卡腳位共用,但是,司徒量測後,發現有幾根腳位並沒有拉到MicroSD,因此,司徒只好找尋一下焊點

跳線

接著,請先拔掉JTAG的USB電源,然後,讓F1C100S進入燒錄模式,接著連接JATG USB電源

連接成功

离线

楼主 #9 2021-06-11 13:08:50 分享评论

楼主 #10 2021-06-11 13:17:58 分享评论

#11 2021-06-11 14:57:43 分享评论

- 怀旧堂

- 会员

- 注册时间: 2021-06-11

- 已发帖子: 17

- 积分: 310

Re: 研究FC3000掌機的開源可行性

@司徒

听闻司徒大佬捣鼓新开源机,特意注册账号来膜拜大佬,

竟然也是100s,那不就是miyoo换壳么,

搞出来也和miyoo一样啊,大佬为何不直接再优化下miyoo的系统呢?

最近编辑记录 怀旧堂 (2021-06-11 15:00:07)

离线

楼主 #12 2021-06-11 15:23:50 分享评论

#13 2021-06-11 16:32:31 分享评论

- xk100

- 会员

- 注册时间: 2018-12-13

- 已发帖子: 75

- 积分: 58.5

Re: 研究FC3000掌機的開源可行性

感谢分享。

离线

楼主 #14 2021-06-11 17:26:42 分享评论

#15 2021-06-11 19:07:25 分享评论

- shawn.d

- 会员

- 注册时间: 2020-09-12

- 已发帖子: 164

- 积分: 85

Re: 研究FC3000掌機的開源可行性

看了这么些年司徒的帖子,司徒基本上还是这个套路。

离线

楼主 #16 2021-06-11 20:28:04 分享评论

#17 2021-06-11 20:57:10 分享评论

- cube

- 会员

- 注册时间: 2021-03-11

- 已发帖子: 288

- 积分: 202.5

Re: 研究FC3000掌機的開源可行性

@司徒

司徒大佬别介意,"套路"在大陆我认为是中性词,没有感情色彩。

离线

楼主 #18 2021-06-11 21:14:56 分享评论

#19 2021-06-11 23:03:09 分享评论

- sblpp

- 会员

- 注册时间: 2018-02-14

- 已发帖子: 165

- 积分: 40

Re: 研究FC3000掌機的開源可行性

感谢大佬分享

离线

#20 2021-06-11 23:23:48 分享评论

- 三木同子

- 会员

- 注册时间: 2020-06-09

- 已发帖子: 42

- 积分: 32

Re: 研究FC3000掌機的開源可行性

shawn.d wrote:

看了这么些年司徒的帖子,司徒基本上还是这个套路。

一步步记录,方便以后查看,特别是遇到问题后心路历程

离线

楼主 #21 2021-06-12 08:31:07 分享评论

Re: 研究FC3000掌機的開源可行性

@三木同子

真心感謝幫忙整理這個文件

2018-12-27 ~ 2019-04-22是當初Miyoo開發開源的時間,在短短不到半年的時間,擠出那個開源系統,確實太倉促,很多東西都沒有好好製作,因此,此次結合FC3000以及小橫米(PocketGo),司徒會把整個開發開源的週期拉長到一年的時間,這次看看有無機會把一些系統以及模擬器都再次優化,意思就是,當大家進入whycan論壇時,就會常常看到這個貼子,哈

我也把當初移植Linux到Miyoo的過程放到GitHub,供需要的人可以參考

Miyoo掌機 移植Linux系統和模擬器.pdf

离线

#22 2021-06-12 08:43:48 分享评论

- shawn.d

- 会员

- 注册时间: 2020-09-12

- 已发帖子: 164

- 积分: 85

Re: 研究FC3000掌機的開源可行性

@司徒

没诈骗这个意思。是指固定作业模式。

离线

楼主 #23 2021-06-12 08:54:47 分享评论

楼主 #24 2021-06-12 09:26:17 分享评论

Re: 研究FC3000掌機的開源可行性

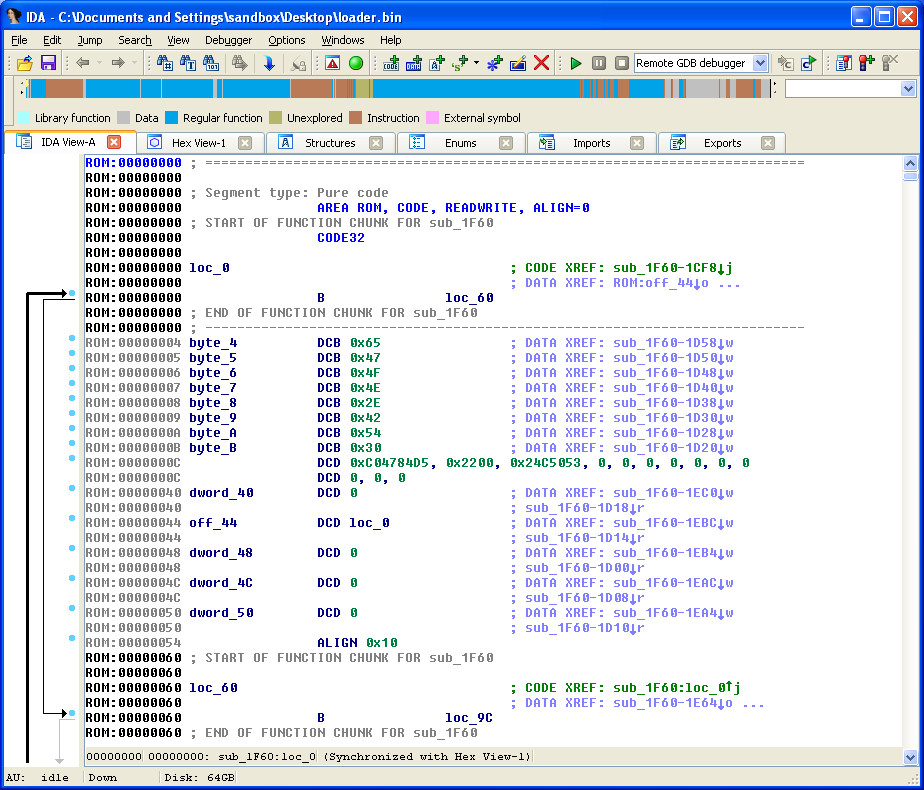

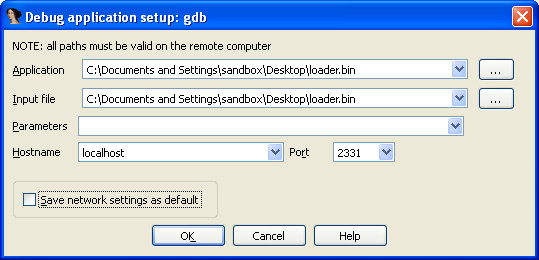

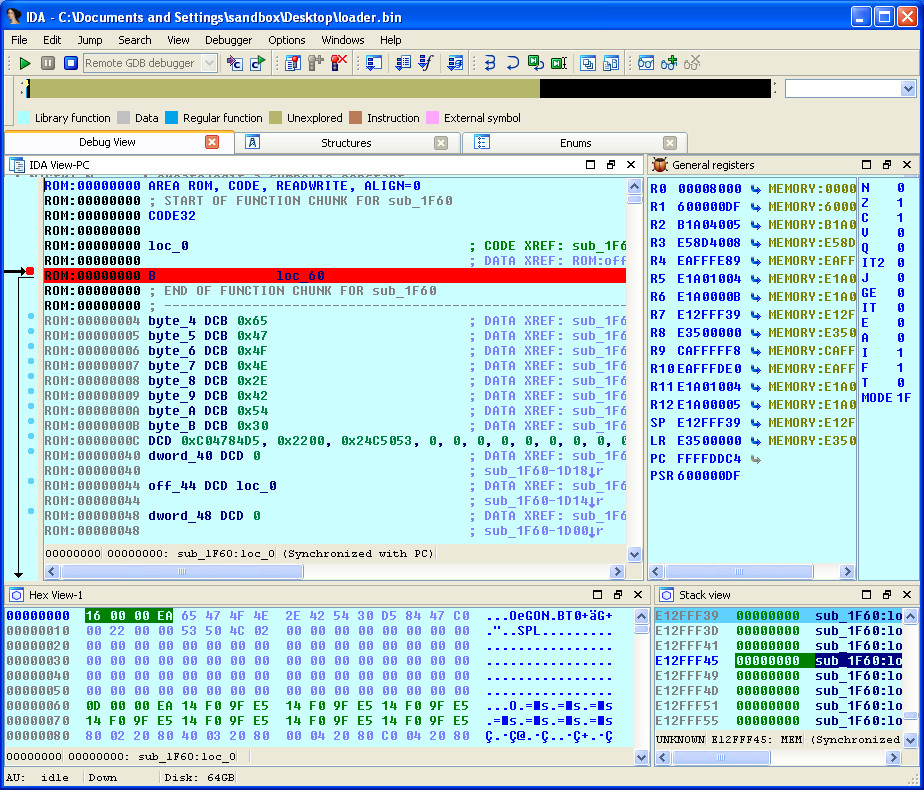

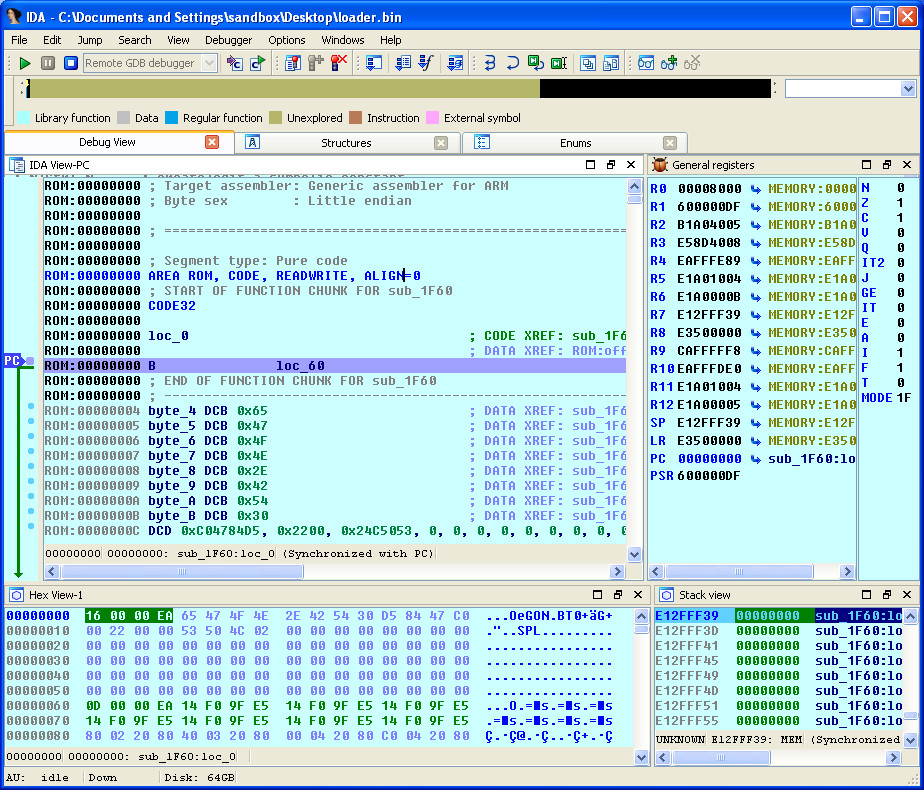

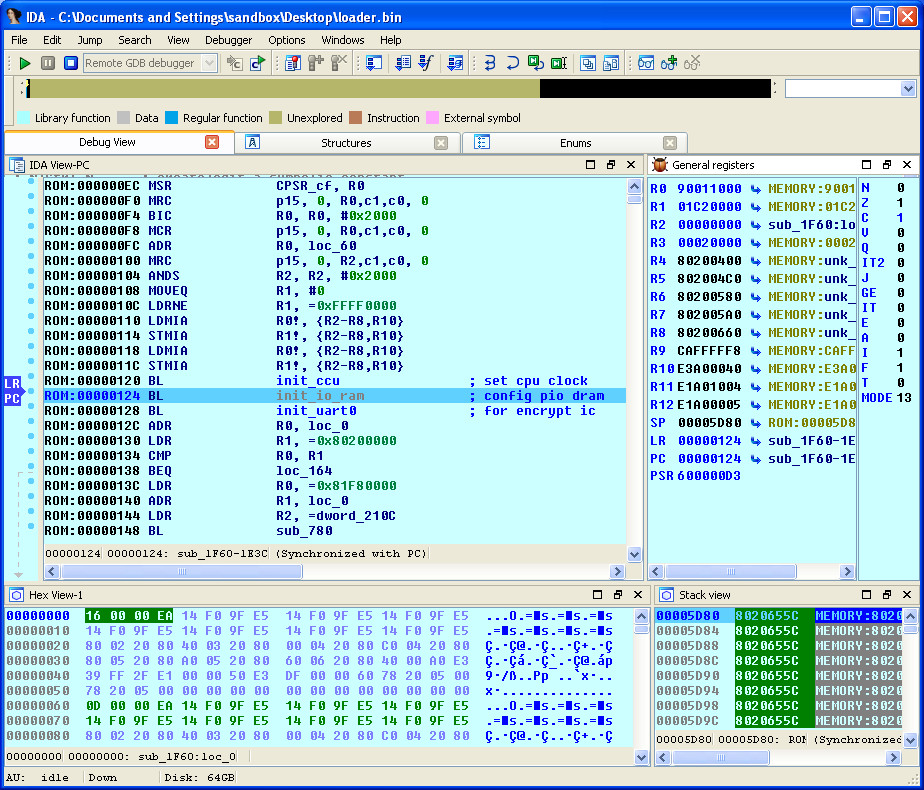

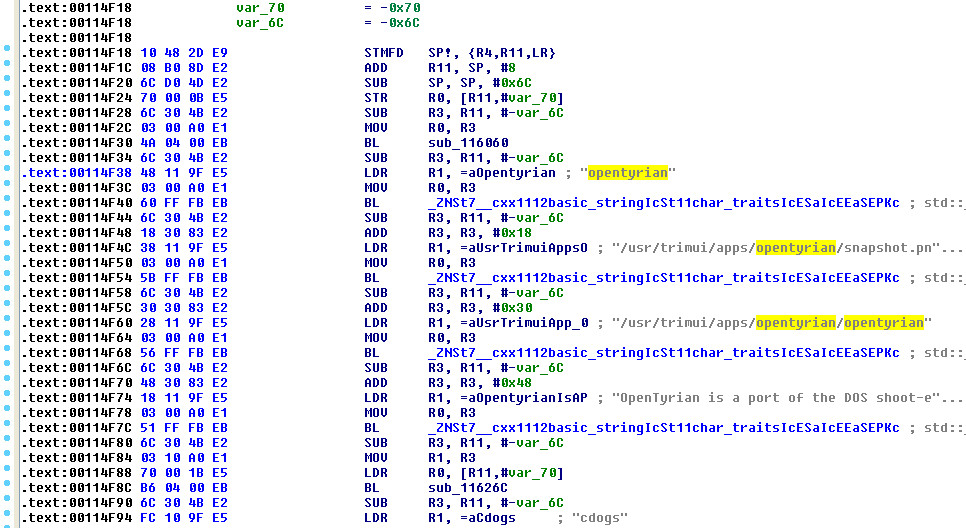

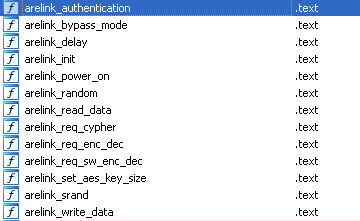

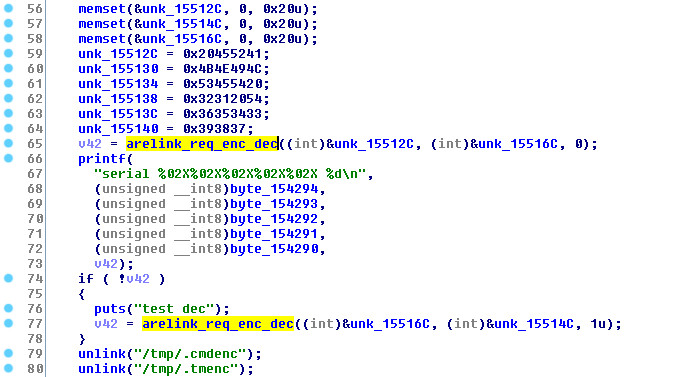

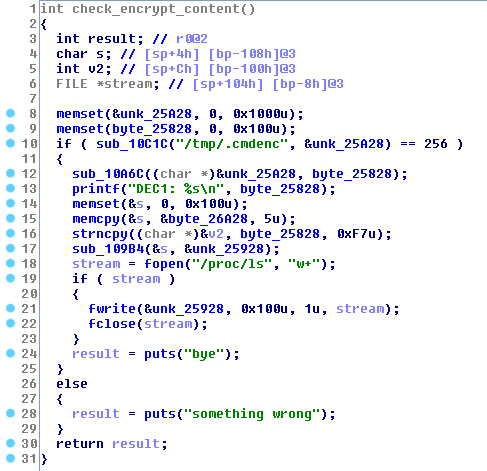

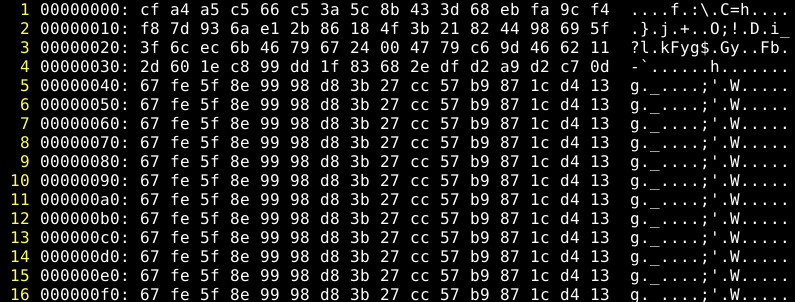

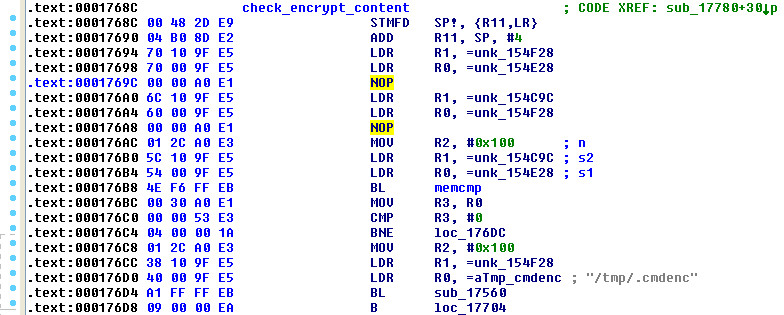

接著,我們必須找出屏的初始化代碼,這樣才可以順利進到下一個步驟,不過,要找出初始化代碼是一個困難點,因為就司徒所知,官方韌體有加密IC保護,因此,我們有可能會被加密IC繞圈圈,不過,總是要先試試才知道困難點

接著開始Debug官方韌體程式,由於BROM只有32KB,加上韌體程式在前面就會把主要ROM複製到0x80000000,因此,抓前面32KB就可以,注意此時SPI Flash要燒錄官方原本的韌體,這樣才可以讓它加載到0x80000000

$ dd if=boot_spiflash.img of=loader.bin bs=1K count=32

32+0 records in

32+0 records out

32768 bytes (33 kB, 32 KiB) copied, 0.000192325 s, 170 MB/s接著拔除JTAG接線,讓F1C100S進入燒錄模式,接著連接JTAG並且使用如下命令載入程式

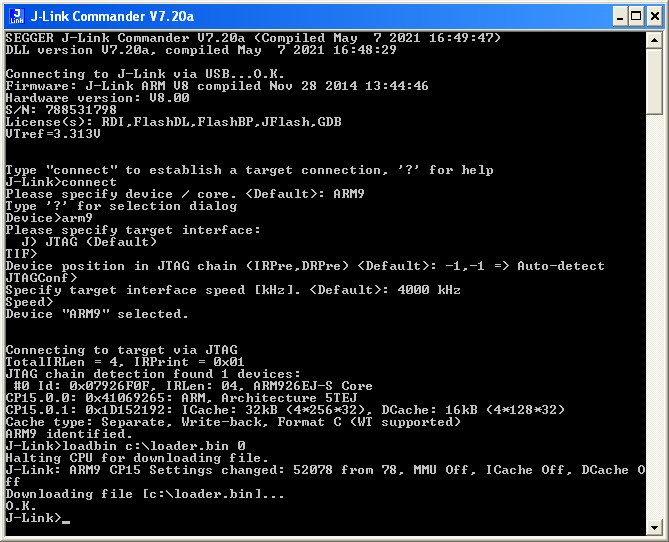

接著開啟J-Link GDB Server,記得選ARM9晶片

Listening on TCP/IP port 2331

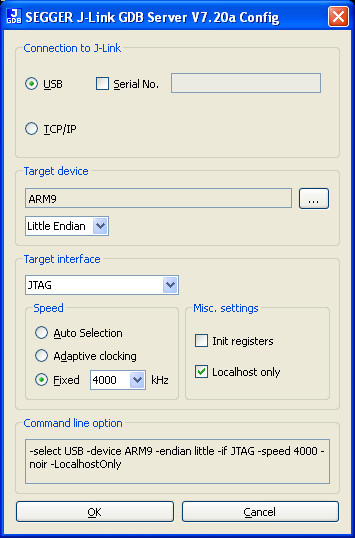

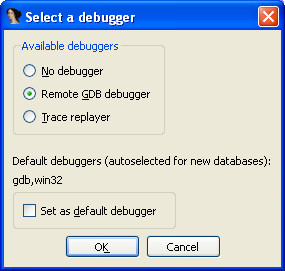

接著使用IDA Pro載入loader.bin

Debugger > Switch debugger...

連接到localhost 2331

目前PC還是在BROM,設定斷點在0x00000000

按下F9,讓它跑到斷點位置

接著就可以開始單步

跳轉到0x81f80164

不知道是否為山寨板J-Link仿真器的問題,司徒發現,常常Debug到一半就跑飛了,哈,這叫我如何是好呢...

离线

#25 2021-06-12 09:53:20 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: 研究FC3000掌機的開源可行性

司徒,不要debug了,这里有原始码,不要怀疑,这个loader的源头都在这里。

https://github.com/xboot/xboot/blob/master/src/arch/arm32/mach-f1c100s/start.S

离线

#26 2021-06-12 09:54:22 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: 研究FC3000掌機的開源可行性

/* Initial system clock, ddr add uart */

bl sys_clock_init

bl sys_dram_init

bl sys_uart_init

/* Boot speed up, leave slower sram */

adr r0, _start

ldr r1, =_start

cmp r0, r1

beq _speedup

ldr r0, =0x81f80000

adr r1, _start

ldr r2, =__spl_size

bl memcpy

ldr r0, =_speedup

ldr r1, =_start

sub r0, r0, r1

ldr r1, =0x81f80000

add r0, r0, r1

mov pc, r0

_speedup:

nop

/* Copyself to link address */

adr r0, _start

ldr r1, =_start

cmp r0, r1

beq 1f

bl sys_copyself

1: nop离线

楼主 #28 2021-06-12 10:15:06 分享评论

Re: 研究FC3000掌機的開源可行性

@xboot

我要找出屏的初始化代碼或者初始數據,我逆了一些代碼後,發現有一些代碼跟xboot很像,但是又不是完全一樣,你應該早點來的告訴我的,哈,這個FC3000掌機的作者應該是在你的xboot QQ群,你可以幫我問下,是否可以給我屏的初始化代碼嗎?這樣我就可以跳過這個步驟,繼續往下走,哈,不然,要找出屏的初始化代碼,可能會花上一些時間,感謝啦

@哇酷小二

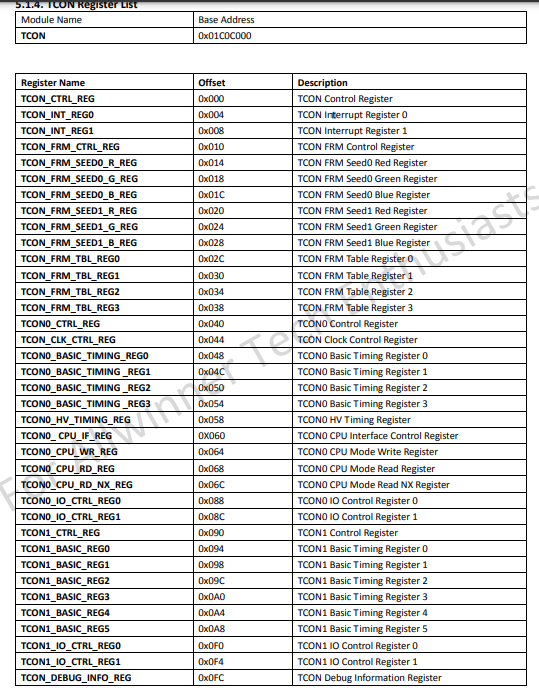

這個屏應該是CPU Interface,你看看可不可以幫忙找出TCON設定以及輸出那段在哪?感謝啦

SPI Flash Image

离线

#29 2021-06-12 10:30:22 分享评论

- luali

- 会员

- 注册时间: 2021-04-24

- 已发帖子: 4

- 积分: 2

Re: 研究FC3000掌機的開源可行性

CPU接口的3寸24pin的320x240,掐指一算可能是st7789

司徒可以尝试一下量第3脚,看看是不是背光

离线

楼主 #30 2021-06-12 10:48:45 分享评论

Re: 研究FC3000掌機的開源可行性

@luali

敢問閣下是否為加藤鷹傳人,你這一掐指果真厲害,屏的背光控制是第三腳位沒錯,由PE6腳位控制,那這樣我用ST7789來點屏看看,感謝

測試代碼

.global _start

.equ GPIO_BASE, 0x01c20800

.equ PE_CFG0, (GPIO_BASE + (4 * 0x24) + 0x00)

.equ PE_DATA, (GPIO_BASE + (4 * 0x24) + 0x10)

.arm

.text

_start:

.long 0xea000016

.byte 'e', 'G', 'O', 'N', '.', 'B', 'T', '0'

.long 0, __spl_size

.byte 'S', 'P', 'L', 2

.long 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

_vector:

b reset

b .

b .

b .

b .

b .

b .

b .

reset:

ldr r0, =PE_CFG0

ldr r1, =0x1000000

str r1, [r0]

ldr r0, =PE_DATA

0:

ldr r2, =100000

1:

subs r2, #1

bne 1b

eor r1, #(1 << 6)

str r1, [r0]

b 0b

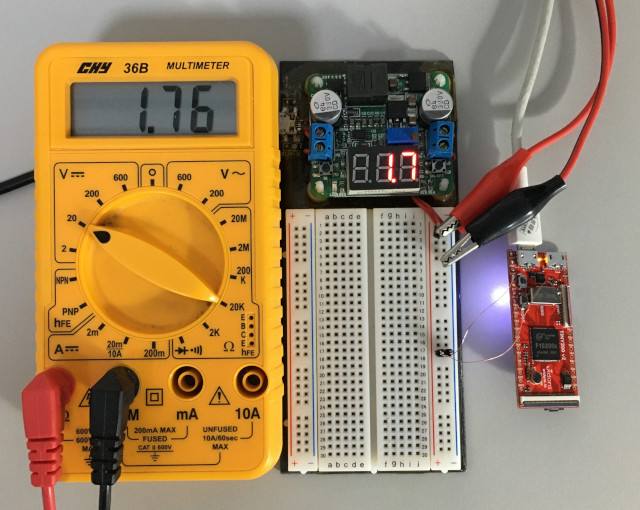

.end可以成功控制屏的背光

离线

#31 2021-06-12 11:38:27 分享评论

- luali

- 会员

- 注册时间: 2021-04-24

- 已发帖子: 4

- 积分: 2

Re: 研究FC3000掌機的開源可行性

@司徒

假如第三脚是背光的话,引脚定义如下所示。其他你懂的:

1 VDD

2 GND

3 LEDA

4 /RESET

5 /CS

6 /RS

7 /WR

8 /RD

9 DB0

10 DB1

11 DB2

12 DB3

13 DB4

14 DB5

15 DB6

16 DB7

17 DB8

18 DB9

19 DB10

20 DB11

21 DB12

22 DB13

23 DB14

24 DB15

离线

#32 2021-06-12 14:50:03 分享评论

- cube

- 会员

- 注册时间: 2021-03-11

- 已发帖子: 288

- 积分: 202.5

Re: 研究FC3000掌機的開源可行性

1👈哈0OpdX6isw3P信 https://m.tb.cn/h.4ubAd45?sm=c24df6 十年老店FC3000掌上游戏机V2私模M3掌机复古SUP拳皇儿童双人手柄

司徒大佬,是这个吗?

离线

楼主 #33 2021-06-12 16:31:13 分享评论

楼主 #34 2021-06-12 16:35:01 分享评论

Re: 研究FC3000掌機的開源可行性

目前使用ST7789的初始化代碼測試,發現還是無法點亮這個屏,而量測後的屏腳位,我也感覺怪怪的,因為那個DB順序好像有點故意把高低5 Bits做交換,雖然我也測試了高低5 Bits交換,但是,還是一樣點不亮這個屏,不過,就目前量測的腳位來看,這個屏沒有TS腳位(Tear),所以這個屏應該是有閃屏問題才是,目前F1C100S系列掌機(PocketGo, Miyoo, Q90, V90, Trimui),就我可以看到的資料,就只有PocketGo是可以解掉閃屏問題,因為它有TS腳位

Pin-01 VDD

Pin-02 GND

Pin-03 LEDA PE6

Pin-04 RST PE11

Pin-05 CS PD21

Pin-06 RS PD19

Pin-07 WR PD18

Pin-08 VDD

Pin-09 DB11 PD13

Pin-10 DB12 PD14

Pin-11 DB13 PD15

Pin-12 DB14 PD16

Pin-13 DB15 PD17

Pin-14 DB5 PD6

Pin-15 DB6 PD7

Pin-16 DB7 PD8

Pin-17 DB8 PD10

Pin-18 DB9 PD11

Pin-19 DB10 PD12

Pin-20 DB0 PD1

Pin-21 DB1 PD2

Pin-22 DB2 PD3

Pin-23 DB3 PD4

Pin-24 DB4 PD5測試代碼

.global _start

.equiv PIO_BASE, 0x01c20800

.equiv PD, (0x24 * 3)

.equiv PE, (0x24 * 4)

.equiv PIO_CFG0, 0x00

.equiv PIO_CFG1, 0x04

.equiv PIO_CFG2, 0x08

.equiv PIO_DATA, 0x10

.equiv LCD_CS, (1 << 21)

.equiv LCD_RS, (1 << 19)

.equiv LCD_WR, (1 << 18)

.equiv LCD_RST, (1 << 11)

.equiv LCD_BL, (1 << 6)

/*

Pin-01 VDD

Pin-02 GND

Pin-03 LEDA PE6

Pin-04 RST PE11

Pin-05 CS PD21

Pin-06 RS PD19

Pin-07 WR PD18

Pin-08 VDD

Pin-09 DB11 PD13

Pin-10 DB12 PD14

Pin-11 DB13 PD15

Pin-12 DB14 PD16

Pin-13 DB15 PD17

Pin-14 DB5 PD6

Pin-15 DB6 PD7

Pin-16 DB7 PD8

Pin-17 DB8 PD10

Pin-18 DB9 PD11

Pin-19 DB10 PD12

Pin-20 DB0 PD1

Pin-21 DB1 PD2

Pin-22 DB2 PD3

Pin-23 DB3 PD4

Pin-24 DB4 PD5

*/

.arm

.text

_start:

.long 0xea000016

.byte 'e', 'G', 'O', 'N', '.', 'B', 'T', '0'

.long 0, __spl_size

.byte 'S', 'P', 'L', 2

.long 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

_vector:

b reset

b .

b .

b .

b .

b .

b .

b .

reset:

mov sp, #0x1000

ldr r1, =0x11111111

ldr r4, =PIO_BASE + PD

str r1, [r4, #PIO_CFG0]

str r1, [r4, #PIO_CFG1]

str r1, [r4, #PIO_CFG2]

ldr r4, =PIO_BASE + PE

str r1, [r4, #PIO_CFG0]

str r1, [r4, #PIO_CFG1]

ldr r1, =0xffffffff

ldr r4, =PIO_BASE + PD

str r1, [r4, #PIO_DATA]

ldr r4, =PIO_BASE + PE

str r1, [r4, #PIO_DATA]

bl lcd_rst

ldr r0, =0x11

bl lcd_cmd

ldr r0, =1000

bl delay

ldr r0, =0x36

bl lcd_cmd

ldr r0, =0xb0

bl lcd_dat

ldr r0, =0x3a

bl lcd_cmd

ldr r0, =0x05

bl lcd_dat

ldr r0, =0x2a

bl lcd_cmd

ldr r0, =0x00

bl lcd_dat

ldr r0, =0x00

bl lcd_dat

ldr r0, =0x01

bl lcd_dat

ldr r0, =0x3f

bl lcd_dat

ldr r0, =0x2b

bl lcd_cmd

ldr r0, =0x00

bl lcd_dat

ldr r0, =0x00

bl lcd_dat

ldr r0, =0x00

bl lcd_dat

ldr r0, =0xef

bl lcd_dat

ldr r0, =0xb2

bl lcd_cmd

ldr r0, =116

bl lcd_dat

ldr r0, =16

bl lcd_dat

ldr r0, =0x01

bl lcd_dat

ldr r0, =0x33

bl lcd_dat

ldr r0, =0x33

bl lcd_dat

ldr r0, =0xb7

bl lcd_cmd

ldr r0, =0x35

bl lcd_dat

ldr r0, =0xb8

bl lcd_cmd

ldr r0, =0x2f

bl lcd_dat

ldr r0, =0x2b

bl lcd_dat

ldr r0, =0x2f

bl lcd_dat

ldr r0, =0xbb

bl lcd_cmd

ldr r0, =0x15

bl lcd_dat

ldr r0, =0xc0

bl lcd_cmd

ldr r0, =0x3c

bl lcd_dat

ldr r0, =0x35

bl lcd_cmd

ldr r0, =0x00

bl lcd_dat

ldr r0, =0xc2

bl lcd_cmd

ldr r0, =0x01

bl lcd_dat

ldr r0, =0xc3

bl lcd_cmd

ldr r0, =0x13

bl lcd_dat

ldr r0, =0xc4

bl lcd_cmd

ldr r0, =0x20

bl lcd_dat

ldr r0, =0xc6

bl lcd_cmd

ldr r0, =0x07

bl lcd_dat

ldr r0, =0xd0

bl lcd_cmd

ldr r0, =0xa4

bl lcd_dat

ldr r0, =0xa1

bl lcd_dat

ldr r0, =0xe8

bl lcd_cmd

ldr r0, =0x03

bl lcd_dat

ldr r0, =0xe9

bl lcd_cmd

ldr r0, =0x0d

bl lcd_dat

ldr r0, =0x12

bl lcd_dat

ldr r0, =0x00

bl lcd_dat

ldr r0, =0xe0

bl lcd_cmd

ldr r0, =0xd0

bl lcd_dat

ldr r0, =0x08

bl lcd_dat

ldr r0, =0x10

bl lcd_dat

ldr r0, =0x0d

bl lcd_dat

ldr r0, =0x0c

bl lcd_dat

ldr r0, =0x07

bl lcd_dat

ldr r0, =0x37

bl lcd_dat

ldr r0, =0x53

bl lcd_dat

ldr r0, =0x4c

bl lcd_dat

ldr r0, =0x39

bl lcd_dat

ldr r0, =0x15

bl lcd_dat

ldr r0, =0x15

bl lcd_dat

ldr r0, =0x2a

bl lcd_dat

ldr r0, =0x2d

bl lcd_dat

ldr r0, =0xe1

bl lcd_cmd

ldr r0, =0xd0

bl lcd_dat

ldr r0, =0x0d

bl lcd_dat

ldr r0, =0x12

bl lcd_dat

ldr r0, =0x08

bl lcd_dat

ldr r0, =0x08

bl lcd_dat

ldr r0, =0x15

bl lcd_dat

ldr r0, =0x34

bl lcd_dat

ldr r0, =0x34

bl lcd_dat

ldr r0, =0x4a

bl lcd_dat

ldr r0, =0x36

bl lcd_dat

ldr r0, =0x12

bl lcd_dat

ldr r0, =0x13

bl lcd_dat

ldr r0, =0x2b

bl lcd_dat

ldr r0, =0x2f

bl lcd_dat

ldr r0, =0x29

bl lcd_cmd

ldr r0, =0x2c

bl lcd_cmd

ldr r4, =640

ldr r5, =0xf800

0:

mov r0, r5

bl lcd_dat

subs r4, #1

bne 0b

ldr r4, =PIO_BASE + PE

ldr r5, =0xffffffff

0:

eor r5, #LCD_BL

str r5, [r4, #PIO_DATA]

ldr r0, =50000

bl delay

b 0b

delay:

push {lr}

0:

subs r0, #1

bne 0b

pop {pc}

lcd_rst:

push {r4, r5, lr}

ldr r4, =PIO_BASE + PE

ldr r5, =0xffffffff

str r5, [r4, #PIO_DATA]

ldr r0, =10000

bl delay

bic r5, #LCD_RST

str r5, [r4, #PIO_DATA]

ldr r0, =10000

bl delay

orr r5, #LCD_RST

str r5, [r4, #PIO_DATA]

ldr r0, =10000

bl delay

pop {r4, r5, pc}

lcd_wr:

push {r4, r5, lr}

ldr r4, =PIO_BASE + PD

/*

mov r2, r0, lsl #11

and r2, #(0x1f << 11)

mov r3, r0, lsr #11

and r3, #0x1f

orr r2, r3

and r3, r0, #0x7e0

orr r2, r3

mov r0, r2

*/

and r2, r0, #0x00ff

and r3, r0, #0xff00

lsl r2, #1

lsl r3, #2

mov r5, #0

orr r5, r1

orr r5, r2

orr r5, r3

str r5, [r4, #PIO_DATA]

ldr r0, =100

bl delay

bic r5, #LCD_WR

str r5, [r4, #PIO_DATA]

ldr r0, =100

bl delay

orr r5, #LCD_WR | LCD_CS

str r5, [r4, #PIO_DATA]

ldr r0, =100

bl delay

pop {r4, r5, pc}

lcd_dat:

push {lr}

mov r1, #LCD_WR | LCD_RS

bl lcd_wr

pop {pc}

lcd_cmd:

push {lr}

mov r1, #LCD_WR

bl lcd_wr

pop {pc}

.end离线

楼主 #35 2021-06-13 21:58:32 分享评论

Re: 研究FC3000掌機的開源可行性

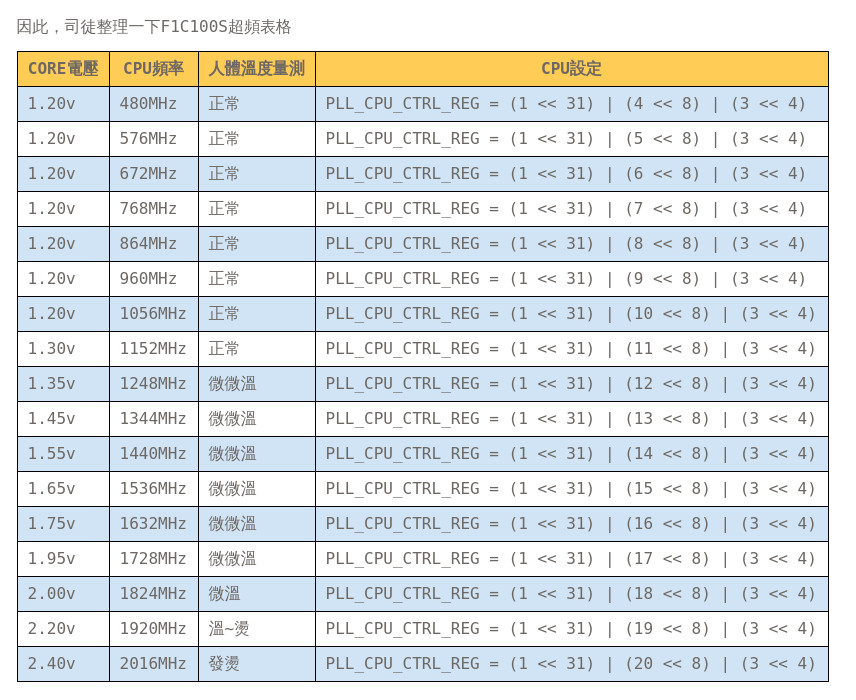

正所謂風水輪流轉,一定有其道理,人的一生,總是高低起伏,在低處得到的經驗總是特別珍貴,今天司徒就來訴說一下得到的經驗值(F1C100S超頻到1.2GHz)

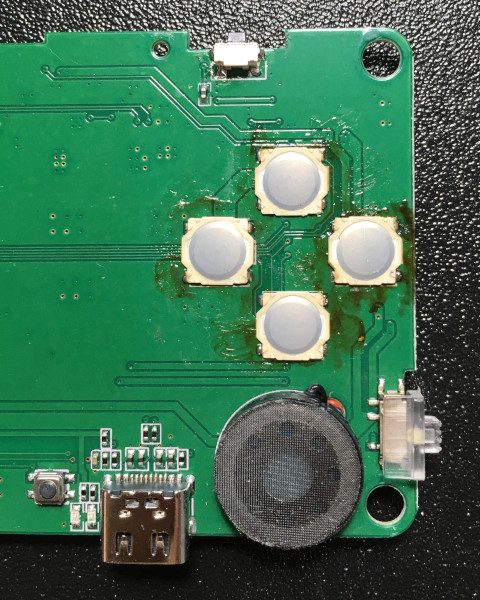

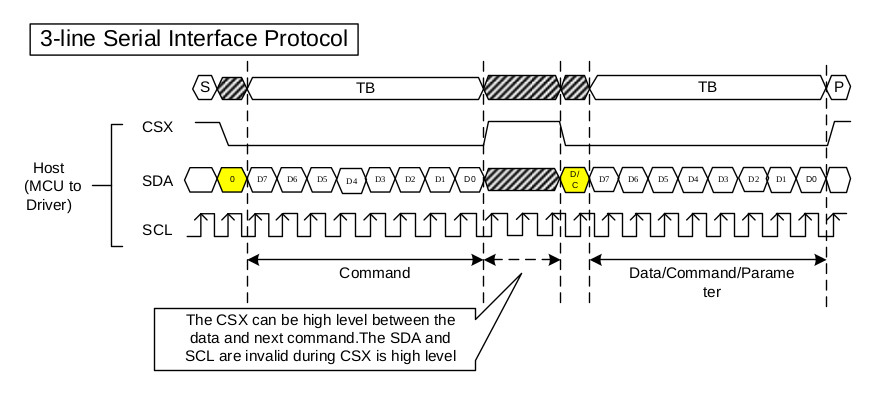

基本上,可以使用如下幾種方式,把屏的初始化資料找出來:

使用J-Link Debug官方韌體程式

使用QEMU跑官方韌體程式,然後把存取暫存器的內容Dump出來 (不過需要破解加密IC)

使用邏輯分析儀

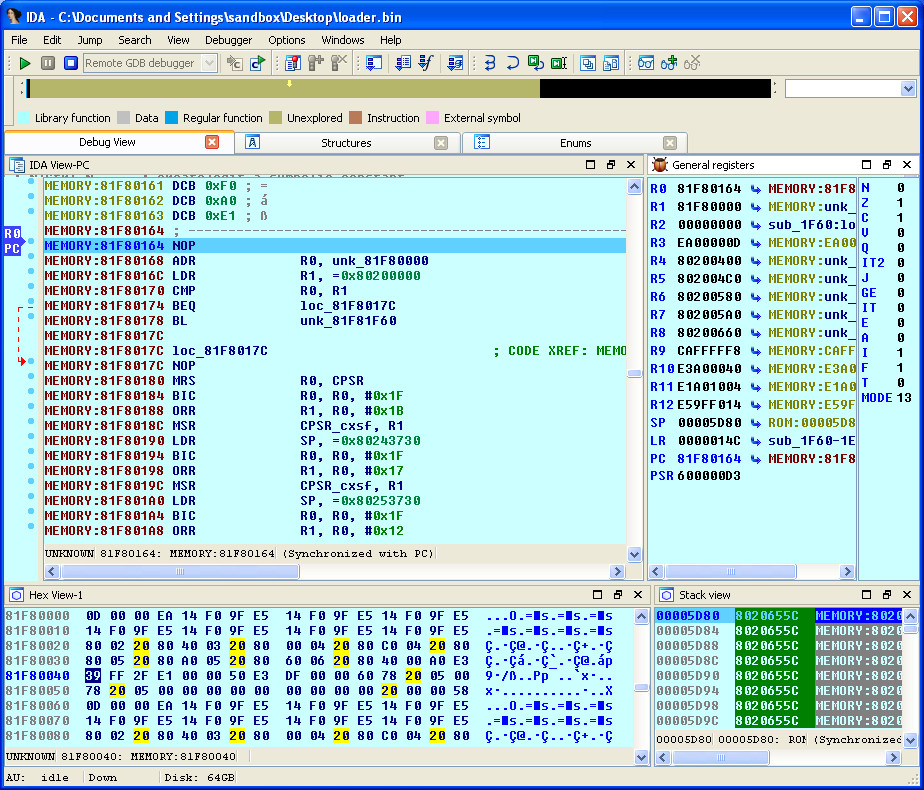

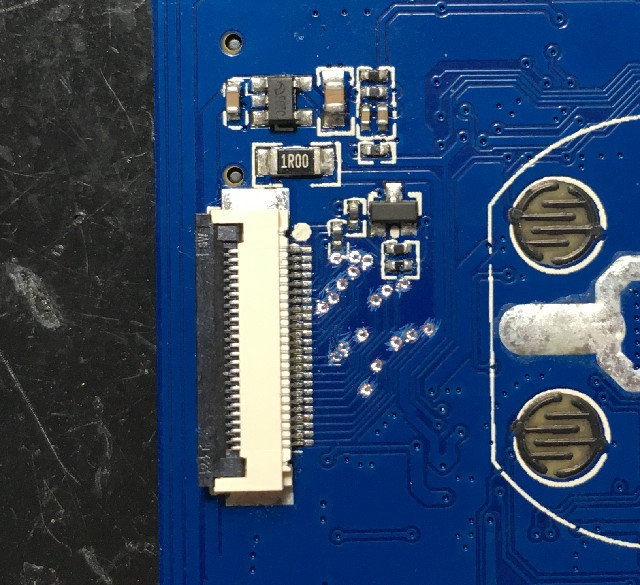

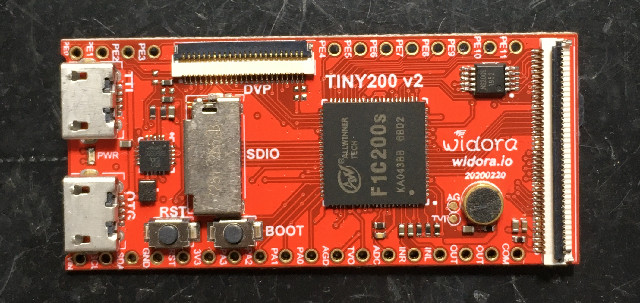

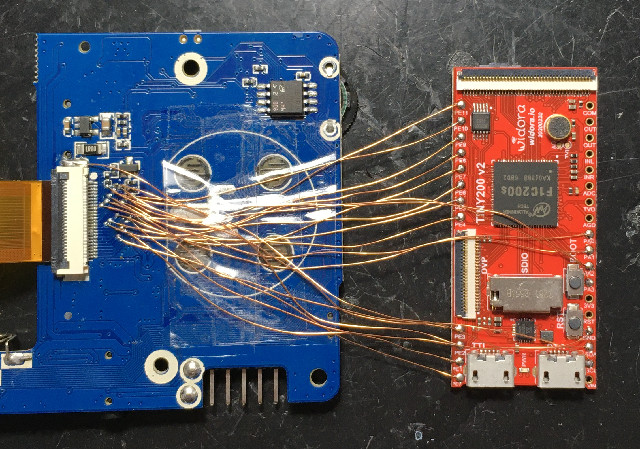

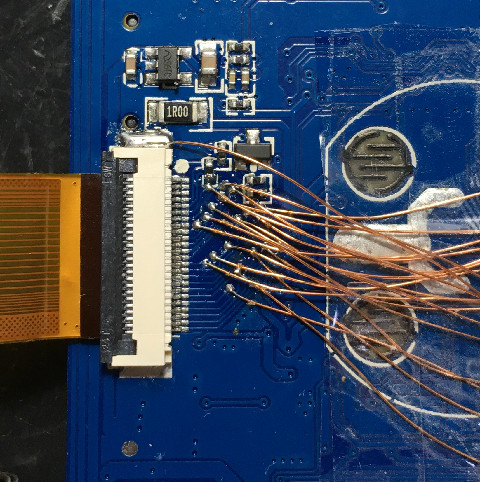

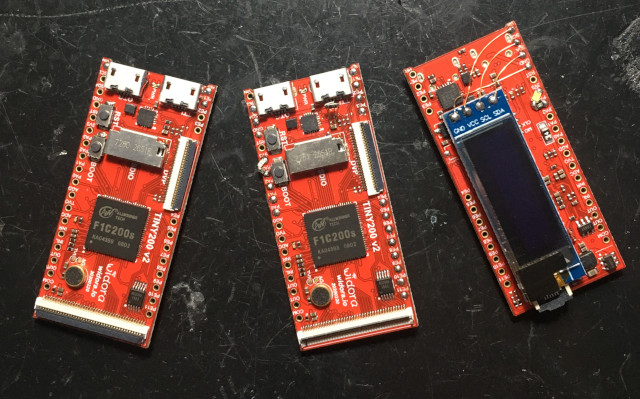

雖然第一種方式是司徒覺得最好的方式,可惜那個山寨J-Link在Debug官方韌體程式時,常常跑飛,所以目前只能先放棄第一種方式,至於第二種方式,看似簡單,不過需要花一些時間,雖然司徒在最新版QEMU有找到支援Orangepi-PC開發板(Allwinner H3),不過要改成F1C100S還是需要一點點時間,所以司徒接下來想測試一下邏輯分析儀的部份,不過司徒手上剛好沒有專用的邏輯分析儀,因此,司徒想使用芒果派F1C200S來當作分析儀使用,於是開始製作過程

括除焊點

勇敢的芒果派站了出來

腳位

Pin-01 VDD

Pin-02 GND

Pin-03 LEDA PE6

Pin-04 RST PE11

Pin-05 CS PD21

Pin-06 RS PD19 => (F1C200S)PD12

Pin-07 WR PD18 => (F1C200S)PD0

Pin-08 VDD

Pin-09 DB11 PD13 => (F1C200S)PE11

Pin-10 DB12 PD14 => (F1C200S)PA0

Pin-11 DB13 PD15 => (F1C200S)PA1

Pin-12 DB14 PD16 => (F1C200S)PA2

Pin-13 DB15 PD17 => (F1C200S)PA3

Pin-14 DB5 PD6 => (F1C200S)PE5

Pin-15 DB6 PD7 => (F1C200S)PE6

Pin-16 DB7 PD8 => (F1C200S)PE7

Pin-17 DB8 PD10 => (F1C200S)PE8

Pin-18 DB9 PD11 => (F1C200S)PE9

Pin-19 DB10 PD12 => (F1C200S)PE10

Pin-20 DB0 PD1 => (F1C200S)PE0

Pin-21 DB1 PD2 => (F1C200S)PE1

Pin-22 DB2 PD3 => (F1C200S)PE2

Pin-23 DB3 PD4 => (F1C200S)PE3

Pin-24 DB4 PD5 => (F1C200S)PE4跳線

測試程式

.global _start

.equiv CCU_BASE, 0x01c20000

.equiv GPIO_BASE, 0x01c20800

.equiv UART1_BASE, 0x01c25400

.equiv PLL_PERIPH_CTRL_REG, 0x0028

.equiv AHB_APB_HCLKC_CFG_REG, 0x0054

.equiv BUS_CLK_GATING_REG2, 0x0068

.equiv BUS_SOFT_RST_REG2, 0x02d0

.equiv PA, (0x24 * 0)

.equiv PB, (0x24 * 1)

.equiv PC, (0x24 * 2)

.equiv PD, (0x24 * 3)

.equiv PE, (0x24 * 4)

.equiv PORT_CFG0, 0x00

.equiv PORT_CFG1, 0x04

.equiv PORT_CFG2, 0x08

.equiv PORT_DATA, 0x10

.equiv PORT_PUL0, 0x1c

.equiv PORT_PUL1, 0x20

.equiv UART_RBR, 0x00

.equiv UART_DLL, 0x00

.equiv UART_DLH, 0x04

.equiv UART_IER, 0x04

.equiv UART_IIR, 0x08

.equiv UART_LCR, 0x0c

.equiv UART_MCR, 0x10

.equiv UART_USR, 0x7c

.arm

.text

_start:

.long 0xea000016

.byte 'e', 'G', 'O', 'N', '.', 'B', 'T', '0'

.long 0, __spl_size

.byte 'S', 'P', 'L', 2

.long 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

_vector:

b reset

b .

b .

b .

b .

b .

b .

b .

reset:

ldr r0, =CCU_BASE

ldr r1, =0x80041800

str r1, [r0, #PLL_PERIPH_CTRL_REG]

ldr r1, =0x00003180

str r1, [r0, #AHB_APB_HCLKC_CFG_REG]

ldr r4, =GPIO_BASE

mov r1, #0x00000000

str r1, [r4, #(PA + PORT_CFG0)]

str r1, [r4, #(PC + PORT_CFG0)]

str r1, [r4, #(PD + PORT_CFG0)]

str r1, [r4, #(PD + PORT_CFG1)]

str r1, [r4, #(PE + PORT_CFG0)]

str r1, [r4, #(PE + PORT_CFG1)]

ldr r1, =0x55555555

str r1, [r4, #(PD + PORT_PUL0)]

str r1, [r4, #(PD + PORT_PUL1)]

str r1, [r4, #(PE + PORT_PUL0)]

str r1, [r4, #(PE + PORT_PUL1)]

ldr r5, =0x4000

ldr r6, =64

mov r1, #0

mov r2, r5

mov r3, r6

0:

str r1, [r2]

add r2, #4

subs r3, #4

bne 0b

ldr r4, =GPIO_BASE

0:

ldr r1, [r4, #(PD + PORT_DATA)]

ands r1, #(1 << 0)

bne 0b

mov r1, #0

ldr r2, [r4, #(PD + PORT_DATA)]

and r2, #(1 << 12)

lsl r2, #20

orr r1, r2

ldr r2, [r4, #(PA + PORT_DATA)]

and r2, #0x07

lsl r2, #12

orr r1, r2

ldr r2, [r4, #(PE + PORT_DATA)]

ldr r3, =0x7ff

and r2, r3

orr r1, r2

str r1, [r5]

1:

ldr r1, [r4, #(PD + PORT_DATA)]

ands r1, #(1 << 0)

beq 1b

add r5, #4

subs r6, #4

bne 0b

bl uart_init

ldr r0, =0x11223344

bl uart_4byte

ldr r5, =0x4000

ldr r6, =64

0:

ldr r0, [r5]

bl uart_4byte

ldr r0, =0xaa

bl uart_byte

add r5, #4

subs r6, #4

bne 0b

b .

uart_init:

push {r4, lr}

ldr r4, =CCU_BASE

ldr r1, =(1 << 21)

str r1, [r4, #BUS_CLK_GATING_REG2]

str r1, [r4, #BUS_SOFT_RST_REG2]

ldr r4, =GPIO_BASE

ldr r1, =0x5500

str r1, [r4, #(PA + PORT_CFG0)]

ldr r4, =UART1_BASE

ldr r1, =0x00

str r1, [r4, #UART_IER]

ldr r1, =0xf7

str r1, [r4, #UART_IIR]

ldr r1, =0x00

str r1, [r4, #UART_MCR]

ldr r1, [r4, #UART_LCR]

orr r1, #(1 << 7)

str r1, [r4, #UART_LCR]

ldr r1, =54

str r1, [r4, #UART_DLL]

ldr r1, =0x00

str r1, [r4, #UART_DLH]

ldr r1, [r4, #UART_LCR]

bic r1, #(1 << 7)

str r1, [r4, #UART_LCR]

ldr r1, [r4, #UART_LCR]

bic r1, #0x1f

orr r1, #0x03

str r1, [r4, #UART_LCR]

pop {r4, pc}

uart_byte:

push {r4, lr}

ldr r4, =UART1_BASE

1:

ldr r1, [r4, #UART_USR]

tst r1, #(1 << 1)

beq 1b

strb r0, [r4, #UART_RBR]

pop {r4, pc}

uart_4byte:

push {r4, lr}

mov r4, r0

lsr r0, #24

bl uart_byte

mov r0, r4

lsr r0, #16

bl uart_byte

mov r0, r4

lsr r0, #8

bl uart_byte

mov r0, r4

bl uart_byte

pop {r4, pc}

.endP.S. PA3先拔除

但是詭異的事情發生了,每次量測到的資料竟然都不一樣

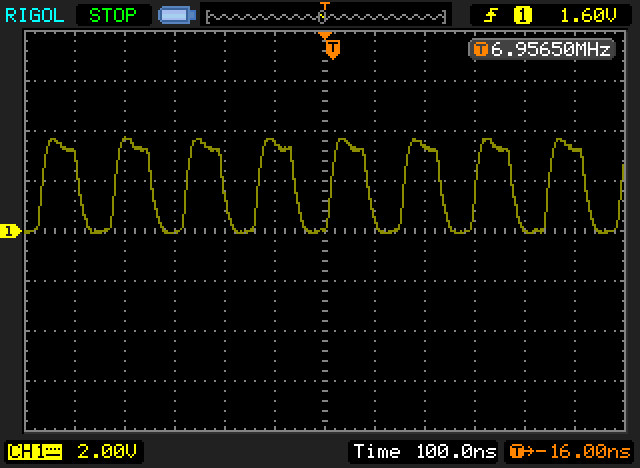

於是,司徒寫了一個GPIO Toggle量測

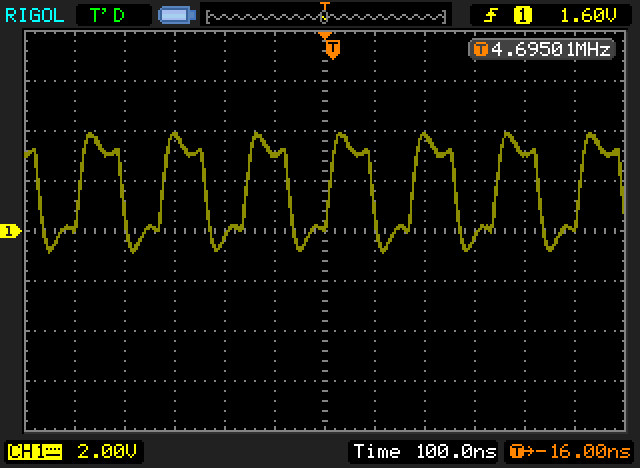

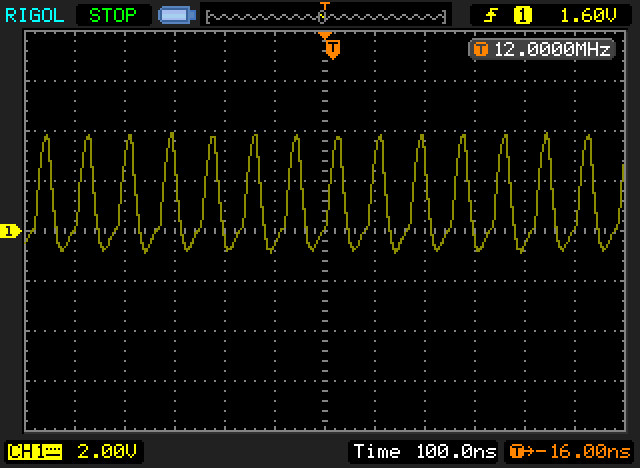

F1C200S I/O速度只有2.8MHz...

屏的LCD_WR速度則是4.7MHz,難怪取出來的資料每次都不一樣,因為,最低取樣頻率至少要是原生的兩倍...

司徒心想,這種事情嚇不倒我,從小被嚇到大,CPU 602MHz跑不動,那就幫你超頻到900MHz,總該脫胎換骨了吧!於是,劇情繼續往下走...

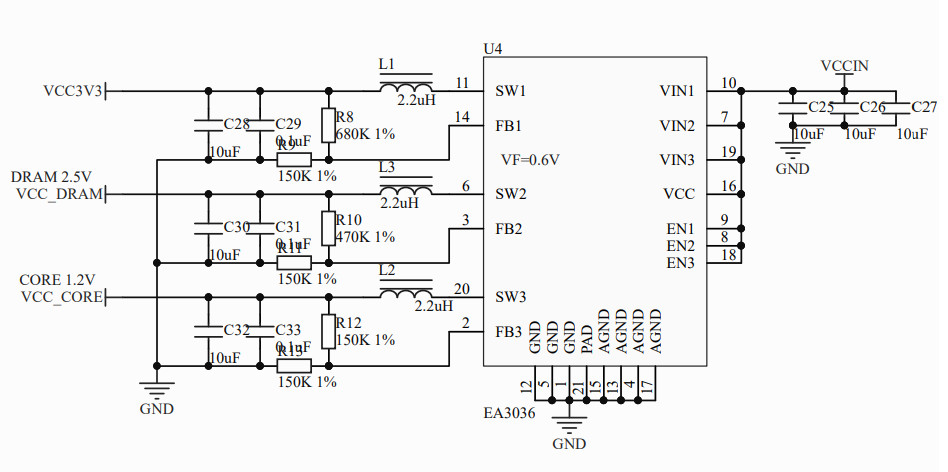

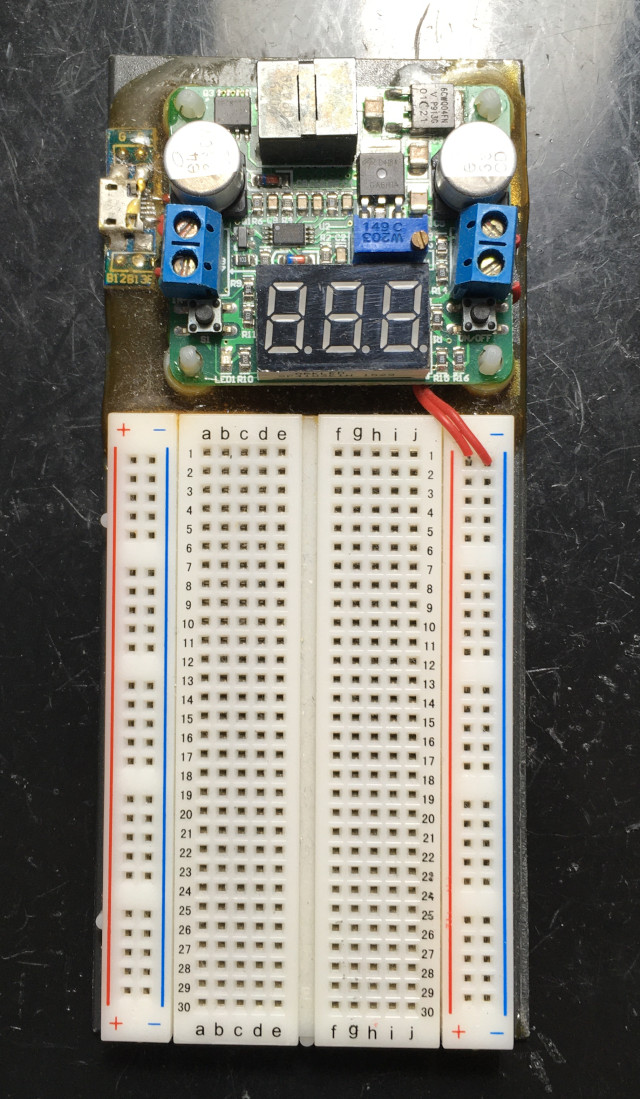

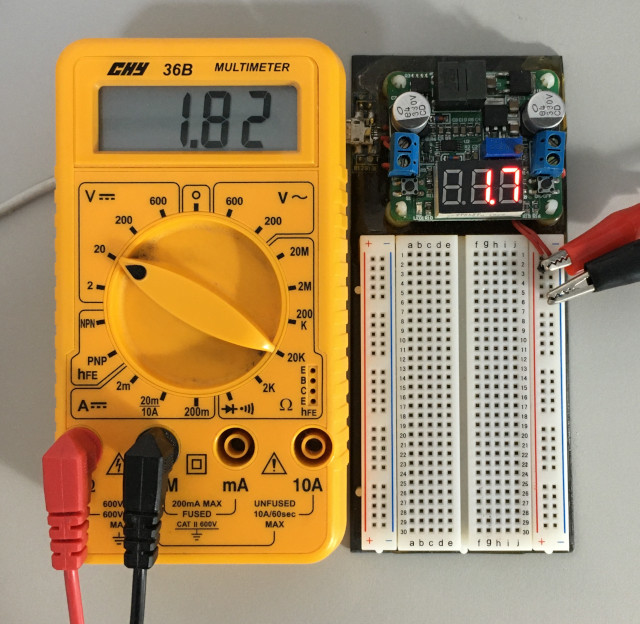

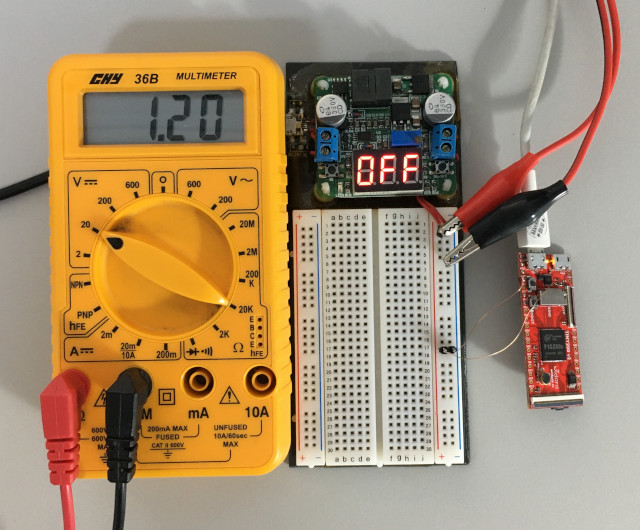

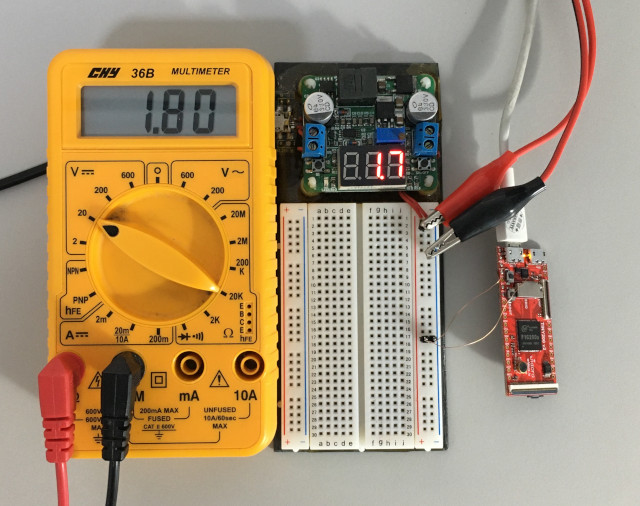

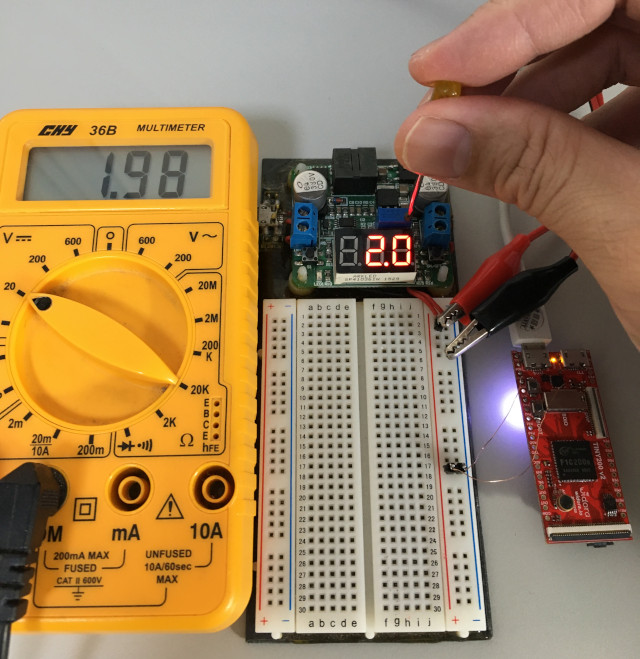

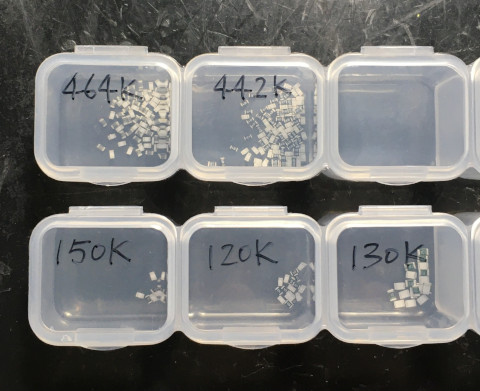

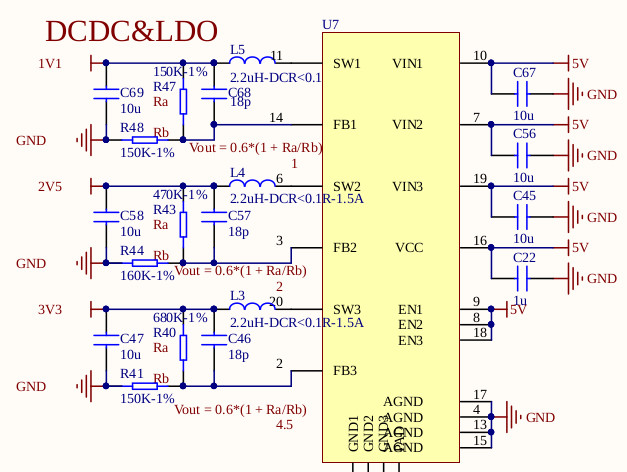

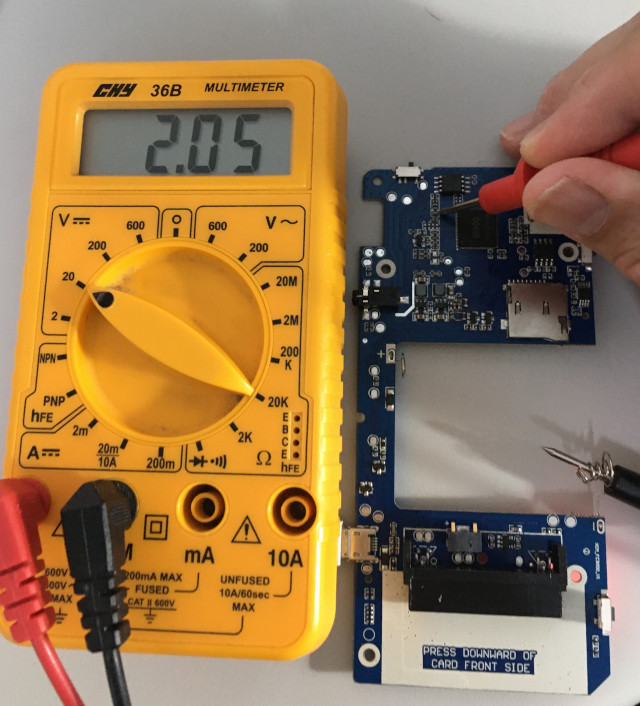

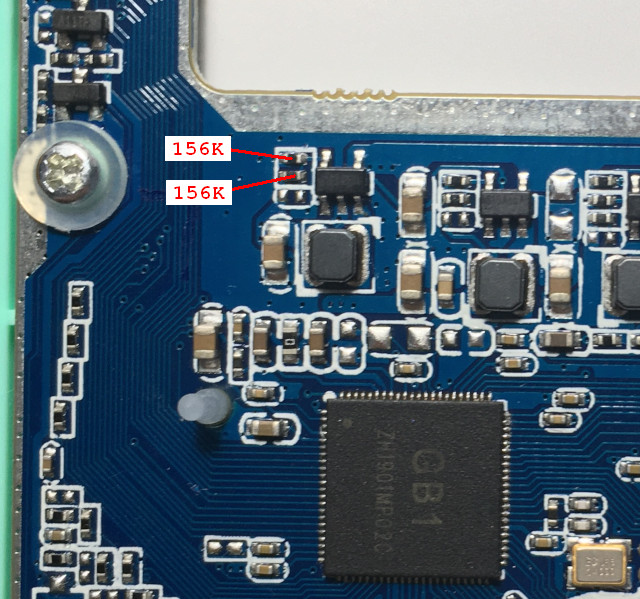

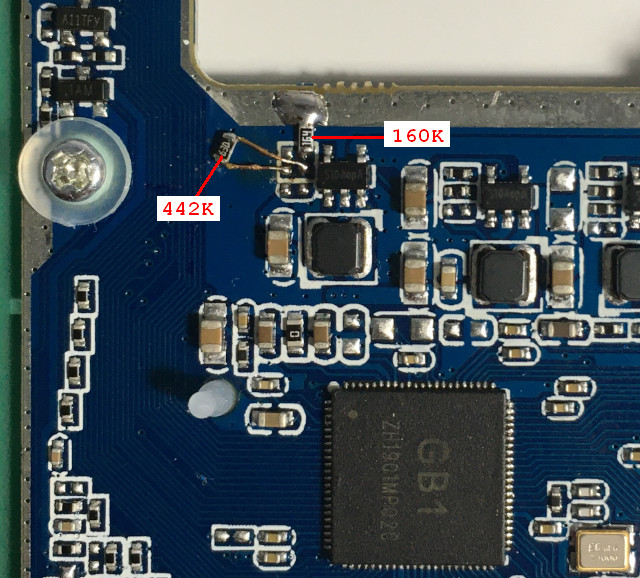

VCC_CORE電壓足夠,才可以做超頻的動作,VCC_CORE是由EA3036供電,目前是1.2V

電壓計算方式如下,從公式可以得知,只要把R13改成75K,輸出電壓就可以變成 0.6 * (150K / 75K) + 0.6 = 1.8V

絲印位置

幸好司徒有夠多芒果派開發板...

焊接

確定電壓是1.8V

CPU速度計算公式

PLL = (24MHz*N*K)/(M*P)

N = 13

K = 4

M = 1

P = 1

PLL = (24MHz*13*4)/(1*1) = 1248MHz測試程式

.global _start

.equiv CCU_BASE, 0x01c20000

.equiv GPIO_BASE, 0x01c20800

.equiv PLL_CPU_CTRL_REG, 0x0000

.equiv PLL_PERIPH_CTRL_REG, 0x0028

.equiv AHB_APB_HCLKC_CFG_REG, 0x0054

.equiv BUS_CLK_GATING_REG2, 0x0068

.equiv BUS_SOFT_RST_REG2, 0x02d0

.equiv PD, (0x24 * 3)

.equiv PORT_CFG0, 0x00

.equiv PORT_CFG1, 0x04

.equiv PORT_CFG2, 0x08

.equiv PORT_DATA, 0x10

.equiv PORT_PUL0, 0x1c

.equiv PORT_PUL1, 0x20

.arm

.text

_start:

.long 0xea000016

.byte 'e', 'G', 'O', 'N', '.', 'B', 'T', '0'

.long 0, __spl_size

.byte 'S', 'P', 'L', 2

.long 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

_vector:

b reset

b .

b .

b .

b .

b .

b .

b .

reset:

ldr r4, =CCU_BASE

ldr r1, =(1 << 31) | (12 << 8) | (3 << 4)

str r1, [r4, #PLL_CPU_CTRL_REG]

0:

ldr r1, [r4, #PLL_CPU_CTRL_REG]

tst r1, #(1 << 28)

beq 0b

ldr r1, =(1 << 31) | (1 << 18) | (31 << 8)

str r1, [r4, #PLL_PERIPH_CTRL_REG]

0:

ldr r1, [r4, #PLL_PERIPH_CTRL_REG]

tst r1, #(1 << 28)

beq 0b

ldr r1, =(3 << 12)

str r1, [r4, #AHB_APB_HCLKC_CFG_REG]

ldr r4, =GPIO_BASE

mov r1, #1

str r1, [r4, #(PD + PORT_CFG0)]

0:

eor r1, #1

str r1, [r4, #(PD + PORT_DATA)]

b 0b

.end接著測量一下I/O速度

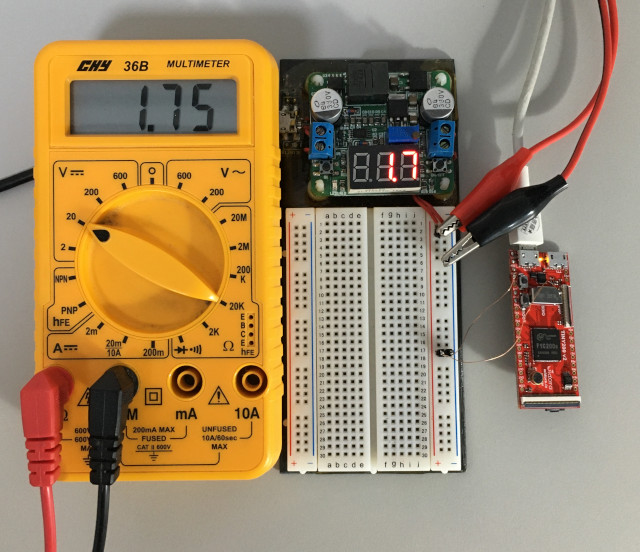

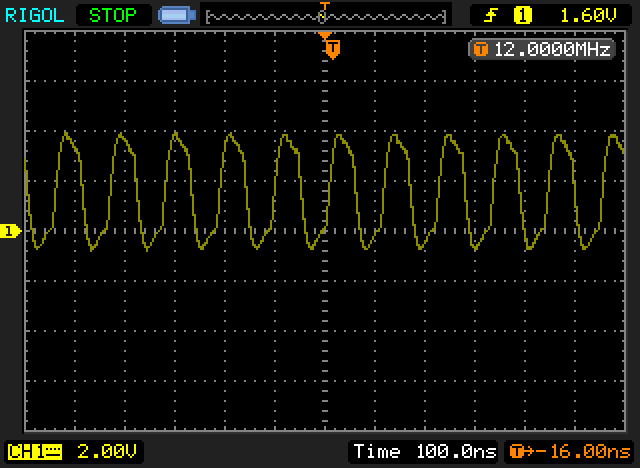

I/O速度為2.8MHz,不過CPU速度已經可以跑到1.2GHz,如果電壓再繼續增加,司徒相信CPU還可以操到更高,因為官方說最高可以到2.6GHz

司徒心想,端午節吃完粽子,應該可以繼續開幹...

离线

#36 2021-06-13 22:38:15 分享评论

- kekemuyu

- 会员

- 注册时间: 2018-12-13

- 已发帖子: 856

- 积分: 697

Re: 研究FC3000掌機的開源可行性

非常欣赏司徒的探索精神,比打怪升级还过瘾!!! 持续关注

离线

楼主 #37 2021-06-14 12:28:25 分享评论

Re: 研究FC3000掌機的開源可行性

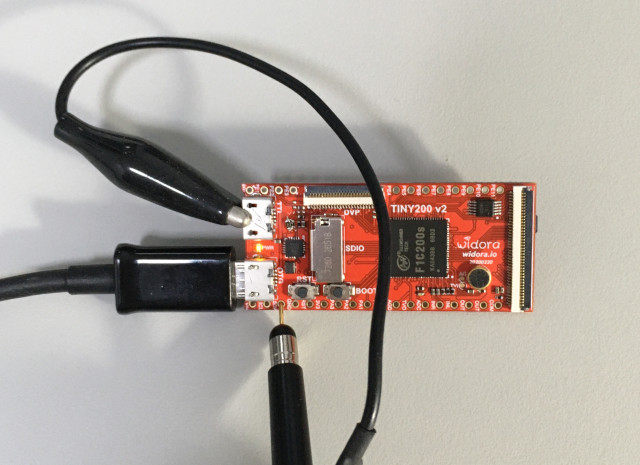

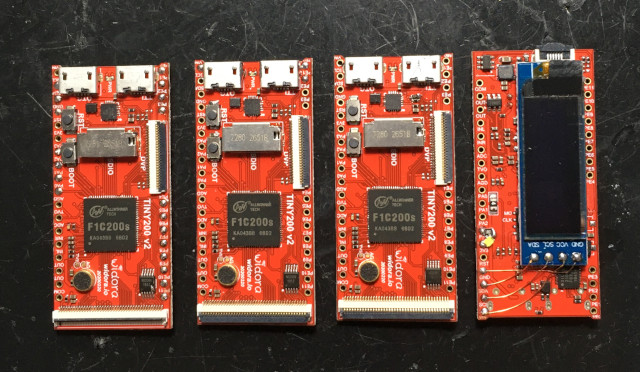

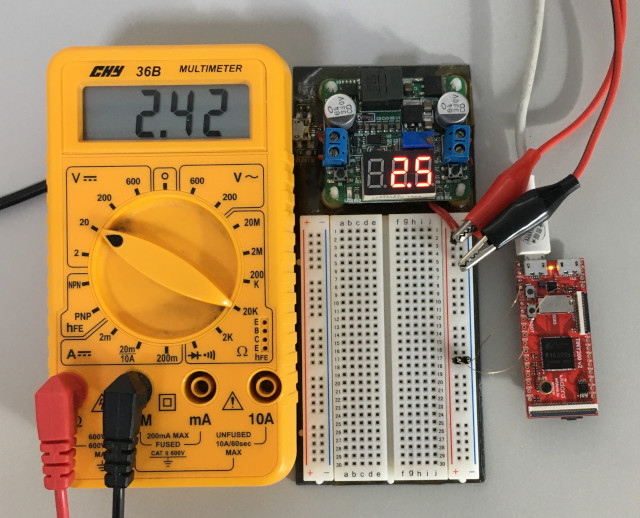

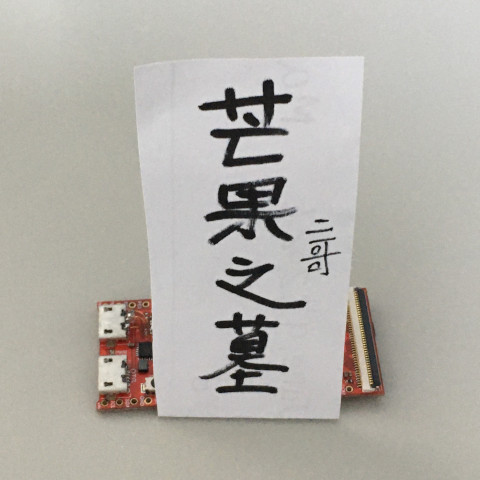

今天是端午佳節,祝福大家端午快樂,小弟再次贈上一個實驗數據,F1C100S CORE 2.4V 可以超頻到2.0GHz ,過程如下分析

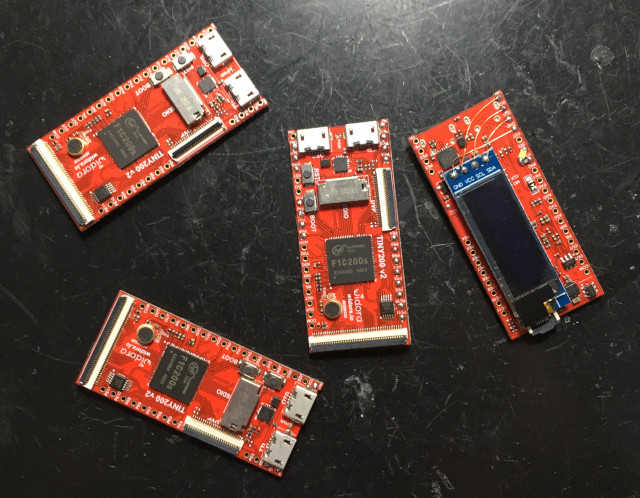

既然官方說最高可以超頻到2.6GHz,那最高到底可以超到多少呢?基於這個好奇心,司徒決定研究一下超頻,因此,司徒找來芒果四兄弟

首先挺身而出的是芒果大哥,大哥深知,超頻可以會讓自己變成一隻燒雞,剛好今天是端午佳節,明年的今天可能會是自己的清明節...

由於司徒並沒有太多精密電阻做分壓測試,因此,趕緊從隔壁找來老王協助

為了避免發生榨妻的嫌疑,司徒量測一下老王的電壓,果然,老王還是無法信任...

遺憾的是,司徒手上剛好沒有溫度測量器,因此,勇敢的五姊妹挺身而出,由二姐負責量測...

芒果派果然值得信任,固定輸出1.2V

接著,司徒開始從1.8V測試

啟動後,吃掉0.05V

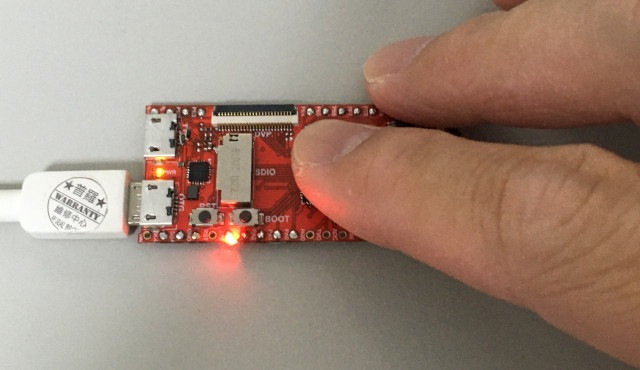

確定LED可以閃爍,代表此時的CPU頻率是可以工作的

測試程式

.global _start

.equiv CCU_BASE, 0x01c20000

.equiv GPIO_BASE, 0x01c20800

.equiv PLL_CPU_CTRL_REG, 0x0000

.equiv PLL_PERIPH_CTRL_REG, 0x0028

.equiv AHB_APB_HCLKC_CFG_REG, 0x0054

.equiv BUS_CLK_GATING_REG2, 0x0068

.equiv BUS_SOFT_RST_REG2, 0x02d0

.equiv PA, (0x24 * 0)

.equiv PORT_CFG0, 0x00

.equiv PORT_DATA, 0x10

.arm

.text

_start:

.long 0xea000016

.byte 'e', 'G', 'O', 'N', '.', 'B', 'T', '0'

.long 0, __spl_size

.byte 'S', 'P', 'L', 2

.long 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

_vector:

b reset

b .

b .

b .

b .

b .

b .

b .

reset:

ldr r4, =CCU_BASE

ldr r1, =(1 << 31) | (20 << 8) | (3 << 4)

str r1, [r4, #PLL_CPU_CTRL_REG]

0:

ldr r1, [r4, #PLL_CPU_CTRL_REG]

tst r1, #(1 << 28)

beq 0b

ldr r0, =GPIO_BASE

ldr r1, =0x1000

str r1, [r0, #(PA + PORT_CFG0)]

0:

eor r1, #8

str r1, [r0, #(PA + PORT_DATA)]

ldr r2, =1000000

1:

subs r2, #1

bne 1b

b 0b

.endP.S. 在最早的測試,司徒忘記N最大只有到31,因此,在此次測試,司徒先把K設定成3,然後依序調整N,上面的程式:24MHz N K = 24MHz 21 4 = 2016MHz

接著就開始慢慢調整電壓測試,找出該CPU頻率下,最低可以接受的電壓

二姐持續量測溫度...

最後,司徒測試發現,電壓2.4V時,CPU可以超頻到2016MHz,此時CPU還可以正常運作,不過已經呈現發燙的狀態(可憐的二姐),可以加上散熱片使用,而電壓再往上增加時,CPU已經無法運作

最後,芒果四兄弟依然健在

幸好二姐也平安無事

F1C200S在2.0GHz下,I/O速度可以多快呢?答案是7MHz

离线

楼主 #38 2021-06-14 12:41:42 分享评论

#39 2021-06-14 14:04:52 分享评论

- unturned3

- 会员

- 注册时间: 2020-07-01

- 已发帖子: 272

- 积分: 301

Re: 研究FC3000掌機的開源可行性

大佬,为什么表格里的频率单位是Hz?不应该是MHz吗?

还真不知道 arm926ej-s 能超频到2GHz…… 大佬们真是要彻底榨干这颗芯片啊

离线

楼主 #40 2021-06-14 14:30:21 分享评论

#41 2021-06-14 14:40:32 分享评论

- kekemuyu

- 会员

- 注册时间: 2018-12-13

- 已发帖子: 856

- 积分: 697

Re: 研究FC3000掌機的開源可行性

v3s是不是也能上2g

离线

#42 2021-06-14 15:01:23 分享评论

- shawn.d

- 会员

- 注册时间: 2020-09-12

- 已发帖子: 164

- 积分: 85

Re: 研究FC3000掌機的開源可行性

司徒 wrote:

如果F1C100S可以長時間運作在2.0GHz下,那這顆CPU也真是有無窮的潛力,這樣小橫米(PocketGo)要跑順PS1模擬器,看來日子不遠已!

ddr ram会是一个问题,它跑不快。

离线

#43 2021-06-14 15:15:59 分享评论

- thindcna

- 会员

- 注册时间: 2020-04-25

- 已发帖子: 36

- 积分: 10.5

Re: 研究FC3000掌機的開源可行性

这个研究很有趣

离线

楼主 #44 2021-06-14 15:54:50 分享评论

楼主 #45 2021-06-14 20:45:03 分享评论

Re: 研究FC3000掌機的開源可行性

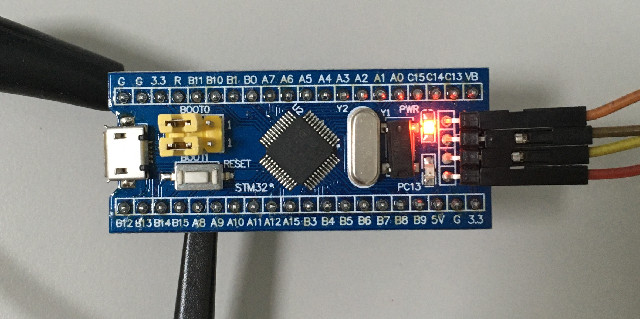

司徒目前還是處於低潮,不過,物極必反,司徒相信應該快要可以飛龍在天了~

司徒目前準備使用STM32F103當作邏輯分析儀使用,因此,使用STM32F103開發板,Toggle I/O測試一下,發現速度只有別人的2/3,雖然目前這個速度應該是夠用,不過如果有人知道問題在哪,在麻煩告知一下司徒,過程如下說明

Ref: https://stackoverflow.com/questions/59708656/stm32f103c8-gpio-speed-limit

STM32F103測試程式(PLL 128MHz)

.thumb

.cpu cortex-m3

.syntax unified

.equiv GPIOA_CRL, 0x40010800

.equiv GPIOA_CRH, 0x40010804

.equiv GPIOA_IDR, 0x40010808

.equiv GPIOA_ODR, 0x4001080c

.equiv GPIOC_CRL, 0x40011000

.equiv GPIOC_CRH, 0x40011004

.equiv GPIOC_IDR, 0x40011008

.equiv GPIOC_ODR, 0x4001100c

.equiv RCC_CR, 0x40021000

.equiv RCC_CFGR, 0x40021004

.equiv RCC_APB2ENR, 0x40021018

.equiv FLASH_ACR, 0x40022000

.equiv STACKINIT, 0x20005000

.global _start

.section .text

.org 0x0

.word STACKINIT

.word _start

.org 0x100

.align 2

.thumb_func

_start:

bl rcc_init

bl flash_init

ldr r4, =RCC_APB2ENR

ldr r1, =(1 << 2)

str r1, [r4]

ldr r4, =GPIOA_CRH

ldr r1, =(3 << 0)

str r1, [r4]

ldr r4, =GPIOA_ODR

ldr r1, =0xffffffff

ldr r2, =0x00000000

0:

str r1, [r4]

str r2, [r4]

@eor r2, #(1 << 8)

@str r2, [r4]

b 0b

.align 2

.thumb_func

rcc_init:

push {r4, lr}

ldr r4, =RCC_CR

mov r1, #(1 << 16)

str r1, [r4]

0:

ldr r1, [r4]

tst r1, #(1 << 17)

bne 0b

ldr r4, =RCC_CFGR

@mov r1, #(7 << 18) @ 72MHz

mov r1, #(14 << 18) @ 128MHz

orr r1, #(1 << 16)

str r1, [r4]

ldr r4, =RCC_CR

ldr r1, [r4]

orr r1, #(1 << 24)

str r1, [r4]

0:

ldr r1, [r4]

tst r1, #(1 << 25)

bne 0b

ldr r4, =RCC_CFGR

ldr r1, [r4]

orr r1, #2

str r1, [r4]

0:

ldr r1, [r4]

tst r1, #(1 << 3)

bne 0b

pop {r4, pc}

.align

.thumb_func

flash_init:

push {r4, lr}

ldr r4, =FLASH_ACR

mov r1, #0x32

str r1, [r4]

pop {r4, pc}

.endPA8輸出

PLL 72MHz時,I/O Toggle可以達到12MHz,不過,stackoverflow的人說可以達到18MHz

PLL 128MHz時,I/O Toggle可以達到21MHz,不過,stackoverflow的人說可以達到36MHz

值得注意的是eor指令比str指令更耗時間,多了一倍指令週期,如下是PLL 128MHz時,使用eor指令的I/O Toggle速度

离线

#46 2021-06-14 21:08:20 分享评论

- kekemuyu

- 会员

- 注册时间: 2018-12-13

- 已发帖子: 856

- 积分: 697

Re: 研究FC3000掌機的開源可行性

发现司徒的测试代码都是汇编,最近在研究汇编,向大神看齐

最近编辑记录 kekemuyu (2021-06-14 21:09:07)

离线

楼主 #47 2021-06-14 23:06:23 分享评论

Re: 研究FC3000掌機的開源可行性

以下純屬個人看法

在有限的時間內,盡可能去學習Assembly,才能夠更貼近你想看的那個東西,更了解它,

因為Assembly是最接近機器的語言,不過卻是離你最遠的語言

或許有人認為司徒老掉牙,還在守舊,現今GNU GCC編譯器只要打開O3旗標,

用C語言都可以寫的比你的Assembly還要高效率

關鍵技術總是藏在底層,選擇看什麼東西或者寫什麼東西,那是個人自由,

埋藏在GNU GCC後面的東西,你可能不知道,或許也不想知道,總之,技術就是藏在別人手上

有些人寫出來的C語言總是特別高效,但是,有些人寫出來的C語言效率卻是相當糟糕,

這其中的奧妙不知道有幾個人仔細想過

學習Assembly,不見得要放棄C語言,學習東西不是在為了要放棄另一個東西做準備

總之,學習態度、處事態度,決定一切,也決定你的人生走向

共勉之~

离线

#48 2021-06-15 00:01:53 分享评论

- kekemuyu

- 会员

- 注册时间: 2018-12-13

- 已发帖子: 856

- 积分: 697

Re: 研究FC3000掌機的開源可行性

从来不以功利目的去学习技术,只是跟随兴趣。学习汇编也是对计算机底层的兴趣,从学编程的第一天开始就对操作系统、编译原理感兴趣。

最近研究汇编也是为了学习写汇编器、编译器。前几天刚把avr的汇编器的词法分析部分写完。写汇编器之前,想参考一下开源的汇编器,发现除了gcc的,很少有人专门写一个汇编器了(除了cpu设计公司,甚至他们也是给gcc写个后端)。有意思的是看到了一个avr的开源汇编器是pascal写的,分析了一下竟然没有按照编译原理写,硬是靠自己的想法堆出来了。它的地址:http://www.avr-asm-tutorial.net/gavrasm/index_en.html,有兴趣可以看一下。

最近编辑记录 kekemuyu (2021-06-15 00:08:40)

离线

楼主 #49 2021-06-15 08:37:11 分享评论

#50 2021-06-15 12:49:55 分享评论

- kekemuyu

- 会员

- 注册时间: 2018-12-13

- 已发帖子: 856

- 积分: 697

Re: 研究FC3000掌機的開源可行性

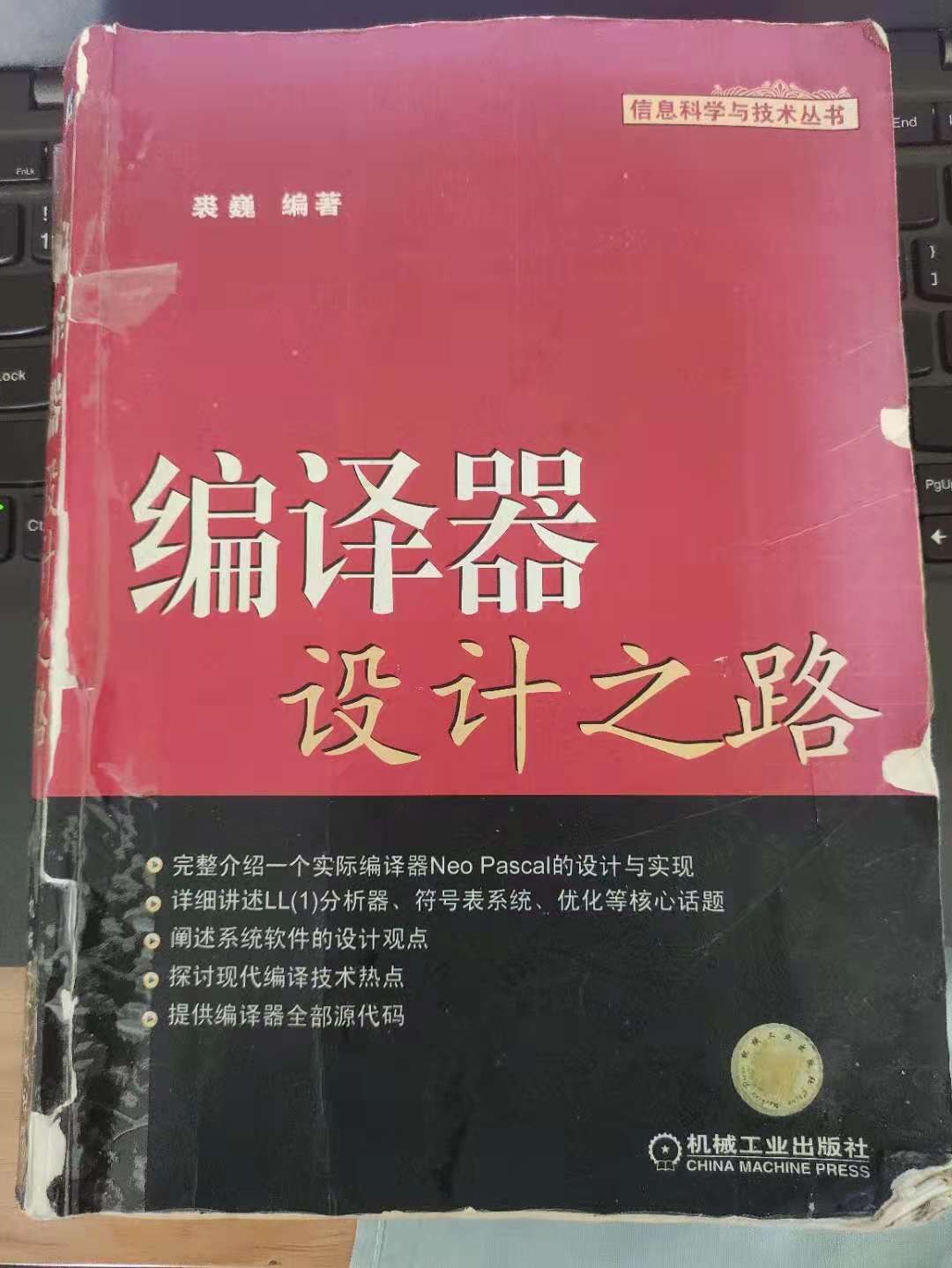

如果不介意编程语言,我推荐《编译器设计之路》这本书。这是一本实战的书,里面有pascal编译器的完整实现及源码。代码量不大,很适合入门。

这个编译器的源码是c++实现,源码地址:https://sourceforge.net/projects/neopascal/

最近编辑记录 kekemuyu (2021-06-15 12:52:56)

离线

楼主 #51 2021-06-15 17:23:57 分享评论

Re: 研究FC3000掌機的開源可行性

司徒還是一樣處於低潮,測試STM32F103後,發現還是不行,取到的資料,還是會有不一致的問題,雖然嘗試取兩次、三次做平均,但是,時間似乎不允許,因此,司徒短期很難飛龍在天了~

重新跳線

接著開始測試,將LCD_WR接到PB1,經由負緣觸發中斷時,接著將PC的資料寫到RAM,讀取完64Bytes後,透過UART傳回電腦

STM32F103測試程式(PB0:LCD_RS, PB1:LCD_WR, PC:LCD_DB)

.thumb

.cpu cortex-m3

.syntax unified

.equiv NVIC_ISER0, 0xe000e100

.equiv AFIO_EXTICR1, 0x40010008

.equiv EXTI_IMR, 0x40010400

.equiv EXTI_EMR, 0x40010404

.equiv EXTI_RTSR, 0x40010408

.equiv EXTI_FTSR, 0x4001040c

.equiv EXTI_SWIER, 0x40010410

.equiv EXTI_PR, 0x40010414

.equiv GPIOA_CRL, 0x40010800

.equiv GPIOA_CRH, 0x40010804

.equiv GPIOA_IDR, 0x40010808

.equiv GPIOA_ODR, 0x4001080c

.equiv GPIOB_CRL, 0x40010c00

.equiv GPIOB_CRH, 0x40010c04

.equiv GPIOB_IDR, 0x40010c08

.equiv GPIOB_ODR, 0x40010c0c

.equiv GPIOC_CRL, 0x40011000

.equiv GPIOC_CRH, 0x40011004

.equiv GPIOC_IDR, 0x40011008

.equiv GPIOC_ODR, 0x4001100c

.equiv RCC_CR, 0x40021000

.equiv RCC_CFGR, 0x40021004

.equiv RCC_APB2ENR, 0x40021018

.equiv FLASH_ACR, 0x40022000

.equiv UART1_SR, 0x40013800

.equiv UART1_DR, 0x40013804

.equiv UART1_BRR, 0x40013808

.equiv UART1_CR1, 0x4001380c

.equiv UART1_CR2, 0x40013810

.equiv UART1_CR3, 0x40013814

.equiv STACKINIT, 0x20005000

.global _start

.section .text

.org 0x0000

.word STACKINIT

.word _start

.org 0x005c

.word _exti1

.org 0x0200

.align 2

.thumb_func

_exti1:

push {r4, lr}

ldrh r1, [r7]

strh r1, [r5, #2]!

ldrh r2, [r8]

strh r2, [r5, #2]!

ldr r4, =EXTI_PR

mov r1, #(1 << 1)

str r1, [r4]

pop {r4, pc}

.align 2

.thumb_func

_start:

bl rcc_init

bl flash_init

bl uart_init

ldr r4, =RCC_APB2ENR

ldr r1, [r4]

orr r1, #(1 << 4) | (1 << 3) | (1 << 2)

str r1, [r4]

ldr r4, =GPIOB_CRL

ldr r1, =0x88888888

str r1, [r4]

ldr r4, =GPIOB_CRH

ldr r1, =0x88888888

str r1, [r4]

ldr r4, =GPIOC_CRL

ldr r1, =0x88888888

str r1, [r4]

ldr r4, =GPIOC_CRH

ldr r1, =0x88888888

str r1, [r4]

ldr r4, =EXTI_IMR

ldr r1, =(1 << 1)

str r1, [r4]

ldr r4, =EXTI_EMR

ldr r1, =(1 << 1)

str r1, [r4]

ldr r4, =EXTI_FTSR

ldr r1, =(1 << 1)

str r1, [r4]

ldr r4, =AFIO_EXTICR1

ldr r1, =(1 << 4)

str r1, [r4]

ldr r5, =buf

ldr r6, =buf

ldr r7, =GPIOB_IDR

ldr r8, =GPIOC_IDR

ldr r4, =NVIC_ISER0

ldr r1, =(1 << 7)

str r1, [r4]

add r6, #(64 * 2 * 2)

0:

cmp r5, r6

bcc 0b

ldr r4, =NVIC_ISER0

mov r1, #0

str r1, [r4]

ldr r4, =AFIO_EXTICR1

mov r1, #0

str r1, [r4]

ldr r5, =buf

ldr r6, =64

0:

ldrh r1, [r5, #2]!

lsl r1, #31

eor r0, r0

ldrh r0, [r5, #2]!

orr r0, r1

bl uart_4byte

subs r6, #1

bne 0b

ldr r0, =0x11223344

bl uart_4byte

b .

.align 2

.thumb_func

uart_init:

push {r4, lr}

ldr r4, =RCC_APB2ENR

ldr r1, [r4]

ldr r2, =(1 << 14) | (1 << 2) | (1 << 0)

orr r1, r2

str r1, [r4]

ldr r4, =GPIOA_CRH

ldr r1, [r4]

bic r1, #0xff0

orr r1, #0x4b0

str r1, [r4]

ldr r4, =UART1_BRR

@ldr r1, =(39 << 4) | (1 << 0) @ 115200bps 72MHz

ldr r1, =(69 << 4) | (7 << 0) @ 115200bps 128MHz

str r1, [r4]

ldr r4, =UART1_CR1

ldr r1, =(1 << 13) | (1 << 3)

str r1, [r4]

pop {r4, pc}

.align 2

.thumb_func

uart_byte:

push {r4, lr}

ldr r4, =UART1_SR

0:

ldr r1, [r4]

tst r1, #(1 << 7)

beq 0b

ldr r4, =UART1_DR

str r0, [r4]

pop {r4, pc}

.align 2

.thumb_func

uart_4byte:

push {r4, lr}

mov r4, r0

lsr r0, #24

bl uart_byte

mov r0, r4

lsr r0, #16

bl uart_byte

mov r0, r4

lsr r0, #8

bl uart_byte

mov r0, r4

bl uart_byte

pop {r4, pc}

.align 2

.thumb_func

rcc_init:

push {r4, lr}

ldr r4, =RCC_CR

ldr r1, =(1 << 26) | (1 << 16)

str r1, [r4]

0:

ldr r1, [r4]

tst r1, #(1 << 17)

bne 0b

ldr r4, =RCC_CFGR

@mov r1, #(7 << 18) @ 72MHz

mov r1, #(14 << 18) @ 128MHz

orr r1, #(1 << 16)

str r1, [r4]

ldr r4, =RCC_CR

ldr r1, [r4]

orr r1, #(1 << 24)

str r1, [r4]

0:

ldr r1, [r4]

tst r1, #(1 << 25)

bne 0b

ldr r4, =RCC_CFGR

ldr r1, [r4]

orr r1, #2

str r1, [r4]

0:

ldr r1, [r4]

tst r1, #(1 << 3)

bne 0b

pop {r4, pc}

.align 2

.thumb_func

flash_init:

push {r4, lr}

ldr r4, =FLASH_ACR

mov r1, #0x32

str r1, [r4]

pop {r4, pc}

.data

.align 2

buf: .skip (64 * 2 * 2)

.end測試後發現,資料還是會有不一致的狀況,因此,STM32F103目前無法勝任這個任務...

离线

#52 2021-06-15 17:31:53 分享评论

- xboot

- 会员

- 注册时间: 2019-10-15

- 已发帖子: 715

- 积分: 448

Re: 研究FC3000掌機的開源可行性

直接上逻辑分析仪吧,专用工具也就在这个时候用的,现在不用,啥时候用。

离线

楼主 #53 2021-06-15 17:45:10 分享评论

#54 2021-06-15 20:11:16 分享评论

- 三木同子

- 会员

- 注册时间: 2020-06-09

- 已发帖子: 42

- 积分: 32

Re: 研究FC3000掌機的開源可行性

@司徒

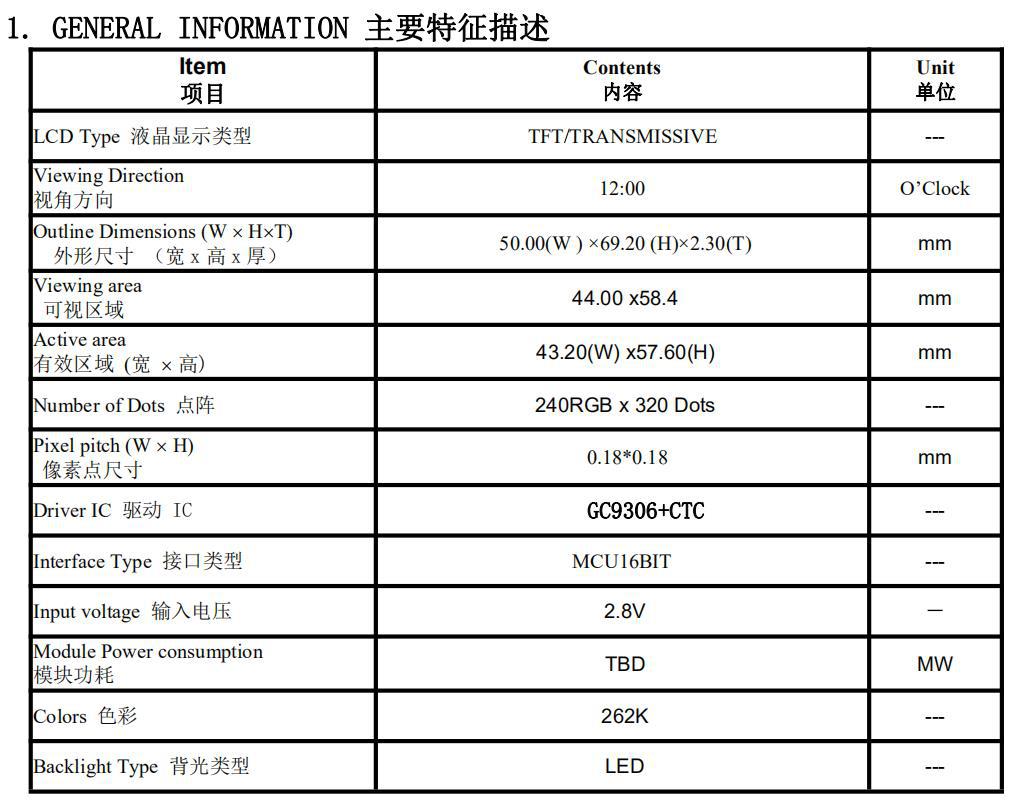

如果知道显示屏的驱动芯片有帮助吗?

可以试试这个驱动,可能是这个芯片:GC9306

这个是驱动参考文章

https://blog.csdn.net/zhoubingda/article/details/107993689

DS由于没有积分无法下载,放个链接

https://download.csdn.net/download/doctoryi/11707588

一个长得很像的屏拆解

https://www.bilibili.com/video/BV1HT4y1F7tE

https://www.bilibili.com/video/av370221820/

https://www.mydigit.cn/forum.php?mod=viewthread&tid=69269

https://haokan.baidu.com/v?pd=wisenatural&vid=10566489192155907891

https://www.gcores.com/articles/119028

另外,这个屏应该是2.8寸且分辨率为240*320(也就是常说的竖屏),商家为了显示大,宣传的3.0寸,3.0寸可能是指带塑料框的尺寸

最近编辑记录 三木同子 (2021-06-15 20:24:49)

离线

#55 2021-06-15 20:41:35 分享评论

- shawn.d

- 会员

- 注册时间: 2020-09-12

- 已发帖子: 164

- 积分: 85

Re: 研究FC3000掌機的開源可行性

司徒 wrote:

因為還沒到貨...

如果你在深圳,可以到我这里直接取一个先用着,坐标南山。

如果你手上有一个FPGA开发板,写两行代码就可以实现这个抓取。两倍采样率是采不清楚的,至少需要4~5倍,理想情况下10倍。

其实我还是没搞懂,你都搞过miyoo了,还搞这个干嘛?无非就是换了个屏嘛,没啥技术乐趣,不过你超频那段还是蛮有意思的。

最近编辑记录 shawn.d (2021-06-15 20:42:44)

离线

楼主 #56 2021-06-15 22:26:29 分享评论

Re: 研究FC3000掌機的開源可行性

@三木同子

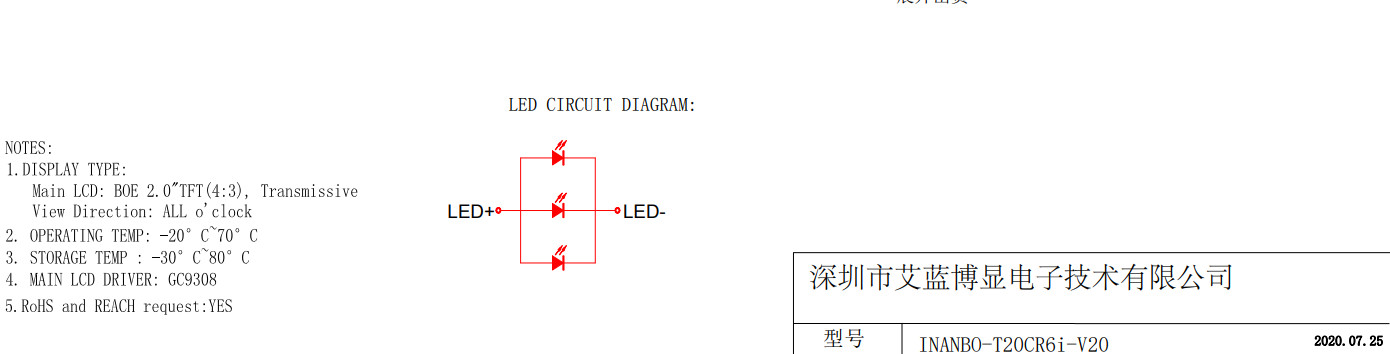

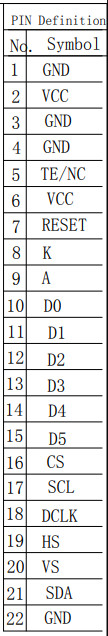

相當感謝你,GC9306,有意思,TRIMUI則是使用GC9308,我找時間試試,相當感謝你的資源

@shawn.d

感謝你,可惜,我目前在台灣,只是不知道何時才可以收到邏輯分析儀...

我下午找了許久,有找到一片FPGA開發板,MAX II有接上50MHZ振盪器,我正想用這片,我需要抓取後,儲存64 Bytes,透過UART回傳,你可以給我代碼嗎,不然我就要慢慢刻出來,哈

其實,我以前搞過Miyoo是沒錯,不過,之前沒有好好把一些東西弄好,不管是效能或者是代碼整潔,加上也沒有很了解F1C100S這顆晶片,因此,我這次野心比較大,我想要從頭把Bootloader、Kernel、系統、模擬器,盡我可能的重新整理一遍,重寫或者重新移植,至少這是我目前想做的,所以我才會從頭搞起,而不是直接針對Miyoo系統再繼續,當然我不是說放棄之前的東西,我只是想要從頭整理一遍,所以對象比較偏向是我個人的移植開源路程,哈

針對這個標題研究FC3000掌機的開源可行性,我心想我應該是已經做到了,因為確定CPU是F1C100S後,基本上,就鐵定可以開源了,只是說,能夠開源到哪種程度

加上我之前也說過,連Miyoo也會一起更新,所以這個貼子就會變得很混亂,因為裡面有FC3000的東西,也有Miyoo的東西,哈,所以,我打算把這個貼子,當作是F1C100S系列掌機的移植過程,意思就是,FC3000掌機、Miyoo掌機、Q8掌機、Trimui掌機,就都寫在這個貼子上面,一起更新好了,前期只要把屏以及按鍵搞定,後續就可以通吃了,哈,所以這樣就變得比較有意思,但是,我想,應該會更混亂,哈

离线

楼主 #57 2021-06-15 23:14:53 分享评论

Re: 研究FC3000掌機的開源可行性

@三木同子

我測試了GC9300、GC9306初始化代碼,不過還是一樣點不亮這個屏,我也仔細多次檢查代碼,應該是沒問題才是,總之,先感謝你的資訊,我在努力找找

GC9306測試代碼,供日後需要使用

.global _start

.equiv PIO_BASE, 0x01c20800

.equiv PD, (0x24 * 3)

.equiv PE, (0x24 * 4)

.equiv PIO_CFG0, 0x00

.equiv PIO_CFG1, 0x04

.equiv PIO_CFG2, 0x08

.equiv PIO_DATA, 0x10

.equiv LCD_CS, (1 << 21)

.equiv LCD_RS, (1 << 19)

.equiv LCD_WR, (1 << 18)

.equiv LCD_RST, (1 << 11)

.equiv LCD_BL, (1 << 6)

/*

Pin-01 VDD

Pin-02 GND

Pin-03 LEDA PE6

Pin-04 RST PE11

Pin-05 CS PD21

Pin-06 RS PD19

Pin-07 WR PD18

Pin-08 VDD

Pin-09 DB11 PD13

Pin-10 DB12 PD14

Pin-11 DB13 PD15

Pin-12 DB14 PD16

Pin-13 DB15 PD17

Pin-14 DB5 PD6

Pin-15 DB6 PD7

Pin-16 DB7 PD8

Pin-17 DB8 PD10

Pin-18 DB9 PD11

Pin-19 DB10 PD12

Pin-20 DB0 PD1

Pin-21 DB1 PD2

Pin-22 DB2 PD3

Pin-23 DB3 PD4

Pin-24 DB4 PD5

*/

.arm

.text

_start:

.long 0xea000016

.byte 'e', 'G', 'O', 'N', '.', 'B', 'T', '0'

.long 0, __spl_size

.byte 'S', 'P', 'L', 2

.long 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

_vector:

b reset

b .

b .

b .

b .

b .

b .

b .

reset:

ldr r4, =PIO_BASE + PD

ldr r1, =0x11111111

str r1, [r4, #PIO_CFG0]

str r1, [r4, #PIO_CFG1]

str r1, [r4, #PIO_CFG2]

ldr r4, =PIO_BASE + PE

ldr r1, =0x11111111

str r1, [r4, #PIO_CFG0]

str r1, [r4, #PIO_CFG1]

ldr r4, =PIO_BASE + PD

ldr r1, =0xffffffff

str r1, [r4, #PIO_DATA]

ldr r4, =PIO_BASE + PE

ldr r1, =0xffffffff

str r1, [r4, #PIO_DATA]

bl lcd_rst

ldr r0, =0xfe

bl lcd_cmd

ldr r0, =0xef

bl lcd_cmd

ldr r0, =0x36

bl lcd_cmd

ldr r0, =0x28

bl lcd_dat

ldr r0, =0x3a

bl lcd_cmd

ldr r0, =0x05

bl lcd_dat

ldr r0, =0xa4

bl lcd_cmd

ldr r0, =0x44

bl lcd_dat

ldr r0, =0x44

bl lcd_dat

ldr r0, =0xa5

bl lcd_cmd

ldr r0, =0x42

bl lcd_dat

ldr r0, =0x42

bl lcd_dat

ldr r0, =0xaa

bl lcd_cmd

ldr r0, =0x88

bl lcd_dat

ldr r0, =0x88

bl lcd_dat

ldr r0, =0xe8

bl lcd_cmd

ldr r0, =0x11

bl lcd_dat

ldr r0, =0x0b

bl lcd_dat

ldr r0, =0xe3

bl lcd_cmd

ldr r0, =0x01

bl lcd_dat

ldr r0, =0x10

bl lcd_dat

ldr r0, =0xff

bl lcd_cmd

ldr r0, =0x61

bl lcd_dat

ldr r0, =0xac

bl lcd_cmd

ldr r0, =0x00

bl lcd_dat

ldr r0, =0xad

bl lcd_cmd

ldr r0, =0x33

bl lcd_dat

ldr r0, =0xae

bl lcd_cmd

ldr r0, =0x2b

bl lcd_dat

ldr r0, =0xaf

bl lcd_cmd

ldr r0, =0x55

bl lcd_dat

ldr r0, =0xa6

bl lcd_cmd

ldr r0, =0x2a

bl lcd_dat

ldr r0, =0x2a

bl lcd_dat

ldr r0, =0xa7

bl lcd_cmd

ldr r0, =0x2b

bl lcd_dat

ldr r0, =0x2b

bl lcd_dat

ldr r0, =0xa8

bl lcd_cmd

ldr r0, =0x18

bl lcd_dat

ldr r0, =0x18

bl lcd_dat

ldr r0, =0xa9

bl lcd_cmd

ldr r0, =0x2a

bl lcd_dat

ldr r0, =0x2a

bl lcd_dat

ldr r0, =0x2b

bl lcd_cmd

ldr r0, =0x00

bl lcd_dat

ldr r0, =0x00

bl lcd_dat

ldr r0, =0x00

bl lcd_dat

ldr r0, =0xef

bl lcd_dat

ldr r0, =0x2a

bl lcd_cmd

ldr r0, =0x00

bl lcd_dat

ldr r0, =0x00

bl lcd_dat

ldr r0, =0x01

bl lcd_dat

ldr r0, =0x3f

bl lcd_dat

ldr r0, =0x2c

bl lcd_cmd

ldr r0, =0xf0

bl lcd_cmd

ldr r0, =0x02

bl lcd_dat

ldr r0, =0x01

bl lcd_dat

ldr r0, =0x00

bl lcd_dat

ldr r0, =0x06

bl lcd_dat

ldr r0, =0x09

bl lcd_dat

ldr r0, =0x0c

bl lcd_dat

ldr r0, =0xf1

bl lcd_cmd

ldr r0, =0x01

bl lcd_dat

ldr r0, =0x03

bl lcd_dat

ldr r0, =0x00

bl lcd_dat

ldr r0, =0x3a

bl lcd_dat

ldr r0, =0x3e

bl lcd_dat

ldr r0, =0x09

bl lcd_dat

ldr r0, =0xf2

bl lcd_cmd

ldr r0, =0x0c

bl lcd_dat

ldr r0, =0x09

bl lcd_dat

ldr r0, =0x26

bl lcd_dat

ldr r0, =0x07

bl lcd_dat

ldr r0, =0x07

bl lcd_dat

ldr r0, =0x30

bl lcd_dat

ldr r0, =0xf3

bl lcd_cmd

ldr r0, =0x09

bl lcd_dat

ldr r0, =0x06

bl lcd_dat

ldr r0, =0x57

bl lcd_dat

ldr r0, =0x03

bl lcd_dat

ldr r0, =0x03

bl lcd_dat

ldr r0, =0x6b

bl lcd_dat

ldr r0, =0xf4

bl lcd_cmd

ldr r0, =0x0d

bl lcd_dat

ldr r0, =0x1d

bl lcd_dat

ldr r0, =0x1c

bl lcd_dat

ldr r0, =0x06

bl lcd_dat

ldr r0, =0x08

bl lcd_dat

ldr r0, =0x0f

bl lcd_dat

ldr r0, =0xf5

bl lcd_cmd

ldr r0, =0x0c

bl lcd_dat

ldr r0, =0x05

bl lcd_dat

ldr r0, =0x06

bl lcd_dat

ldr r0, =0x33

bl lcd_dat

ldr r0, =0x31

bl lcd_dat

ldr r0, =0x0f

bl lcd_dat

ldr r0, =0x11

bl lcd_cmd

ldr r0, =10000

bl delay

ldr r0, =0x29

bl lcd_cmd

ldr r0, =10000

bl delay

ldr r0, =0x2c

bl lcd_cmd

ldr r4, =320*30

ldr r5, =0xf800

0:

mov r0, r5

bl lcd_dat

subs r4, #1

bne 0b

ldr r4, =PIO_BASE + PE

ldr r5, =0xffffffff

0:

eor r5, #LCD_BL

str r5, [r4, #PIO_DATA]

ldr r0, =50000

bl delay

b 0b

delay:

push {lr}

0:

subs r0, #1

bne 0b

pop {pc}

lcd_rst:

push {r4, r5, lr}

ldr r4, =PIO_BASE + PE

ldr r5, =0xffffffff

str r5, [r4, #PIO_DATA]

ldr r0, =10000

bl delay

bic r5, #LCD_RST

str r5, [r4, #PIO_DATA]

ldr r0, =10000

bl delay

orr r5, #LCD_RST

str r5, [r4, #PIO_DATA]

ldr r0, =10000

bl delay

pop {r4, r5, pc}

lcd_wr:

push {r4, r5, lr}

ldr r4, =PIO_BASE + PD

/*

mov r2, r0, lsl #11

and r2, #(0x1f << 11)

mov r3, r0, lsr #11

and r3, #0x1f

orr r2, r3

and r3, r0, #0x7e0

orr r2, r3

mov r0, r2

*/

and r2, r0, #0x00ff

and r3, r0, #0xff00

lsl r2, #1

lsl r3, #2

mov r5, #0

orr r5, r1

orr r5, r2

orr r5, r3

str r5, [r4, #PIO_DATA]

ldr r0, =100

bl delay

bic r5, #LCD_CS

str r5, [r4, #PIO_DATA]

ldr r0, =100

bl delay

bic r5, #LCD_WR

str r5, [r4, #PIO_DATA]

ldr r0, =100

bl delay

orr r5, #LCD_WR

str r5, [r4, #PIO_DATA]

ldr r0, =100

bl delay

orr r5, #LCD_CS

str r5, [r4, #PIO_DATA]

ldr r0, =100

bl delay

pop {r4, r5, pc}

lcd_dat:

push {lr}

mov r1, #LCD_CS | LCD_WR | LCD_RS

bl lcd_wr

pop {pc}

lcd_cmd:

push {lr}

mov r1, #LCD_CS | LCD_WR

bl lcd_wr

pop {pc}

.end离线

#58 2021-06-16 08:17:10 分享评论

- shawn.d

- 会员

- 注册时间: 2020-09-12

- 已发帖子: 164

- 积分: 85

Re: 研究FC3000掌機的開源可行性

@司徒

如果你的MAX ii 是EPM570以上的,内部有PLL,可以倍频,如果是240,那就没办法用signaltap。在可以用signalTap的情况下,最简单的做法是将所有其它信号用屏的时钟寄存两拍即可,不需要使用板载时钟,也不用使用PLL,然后用signaltap把这些寄存信号采出来。signaltap的数据可以直接导出到matlab进行解码啥的。导出的csv文件,你可以用python或者C++来处理解码。

最近编辑记录 shawn.d (2021-06-16 08:36:10)

离线

#59 2021-06-16 08:19:40 分享评论

- dso_2019

- 会员

- 注册时间: 2019-10-13

- 已发帖子: 39

- 积分: 3.5

Re: 研究FC3000掌機的開源可行性

膜拜,牛人,破解高手

离线

#60 2021-06-16 08:28:55 分享评论

- skywalk00

- 会员

- 注册时间: 2021-04-01

- 已发帖子: 20

- 积分: 15.5

Re: 研究FC3000掌機的開源可行性

我也觉得司徒大神搞这个机器没意思,大神对F1C100S这个芯片研究很厉害了 ,这个和荔枝派NANO一样,还不如搞个荔枝派NANO能用的游戏系统,直接烧录镜像就可以用,而且支持各尺寸的SPI屏,方便大家DIY各种各样的游戏机。

离线

楼主 #61 2021-06-16 09:25:05 分享评论

#62 2021-06-16 10:12:55 分享评论

- zzm24

- 会员

- 注册时间: 2018-05-07

- 已发帖子: 127

- 积分: 89

Re: 研究FC3000掌機的開源可行性

财务自由的人才能有兴趣了,我看这屏像这个

https://item.taobao.com/item.htm?id=625742759811

话说我尝试超频,CORE VDD上1.6V电压才能超到900M,再高就不启动了.有空再试试2.4V.如果能到2GHz,这颗芯片就好玩多了

离线

#63 2021-06-16 10:16:22 分享评论

- skywalk00

- 会员

- 注册时间: 2021-04-01

- 已发帖子: 20

- 积分: 15.5

Re: 研究FC3000掌機的開源可行性

我无意冒犯司徒大神,树莓派我只玩过ZEROW,功耗大,而且烧录LAKKA或RECALBOX,玩游戏非常卡,记忆中只有FC、世嘉MEGA DRIVE游戏流畅一些,GBA都卡,而且性价比不高,现在单片树莓派ZERO W价格接近200元人民币了,而且树莓派3代4代价格更高,国产的ORANGEPAI PC性能不错,跑LAKKA顺畅连PSP都可以模拟,但功耗太高,发热量巨大,不太适合掌机,F1C100S的机器我有小霸王Q2升级版(我是贴吧发拆机哪个,当时跟大神还有短暂交流)V90游戏机,我惊叹于司徒大神开发的系统,基本秒开,而且在处理器频率不高的情况下,V90游戏机 702MHZ就可以流畅模拟PS1游戏了(当然有些游戏得跳帧),而且还可以超频,荔枝派NANO就是F1C100S的开发板,所以才会有这种想法。

离线

楼主 #64 2021-06-16 15:52:43 分享评论

Re: 研究FC3000掌機的開源可行性

@shawn.d

感謝,我的是EPM240,在邏輯分析儀來之前,我來寫看看,哈

@skywalk00

原來那個人是你,我正好要找你,因為你說小霸王Q2也是F1C100S ? 你可以測試一下Miyoo系統嗎,看看可不可以跑起來嗎 ?

@zzm24

感謝你的資訊,經過我測試,這個屏應該不是GC9306,另外超頻部份,下面說明

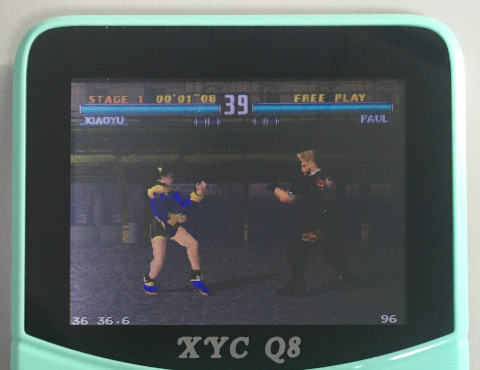

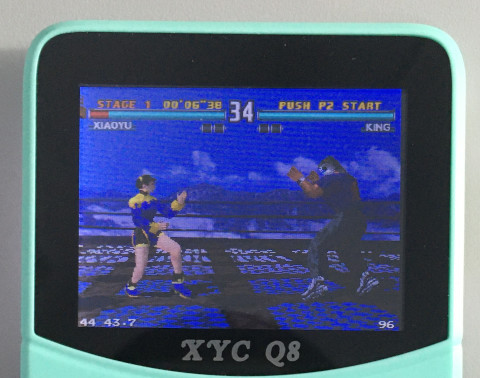

司徒也在懷疑是否LCD輸出那部份有問題,於是測試下R61520在Miyoo上,確實可以跑得

測試Q8掌機的HX8357C,也是可以點亮屏

將FC3000的屏拿到Q8掌機測試,結果還是點不亮,共測試GC9300、GC9306、ST7789、HX8357C、R61520初始化程式,還是不行...

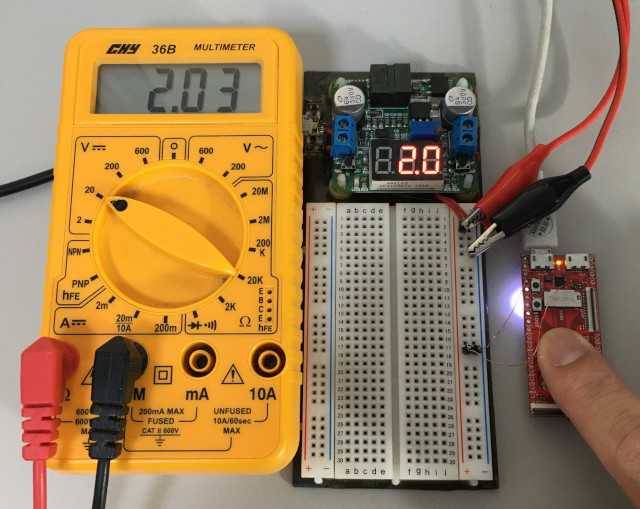

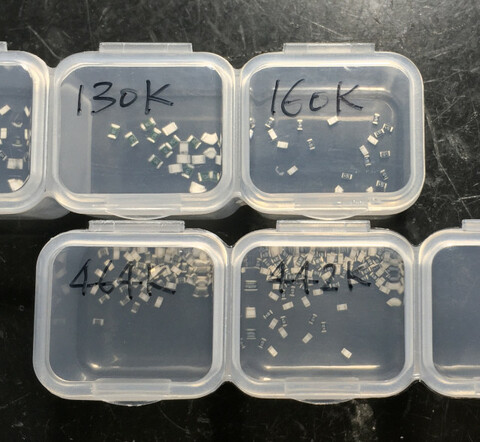

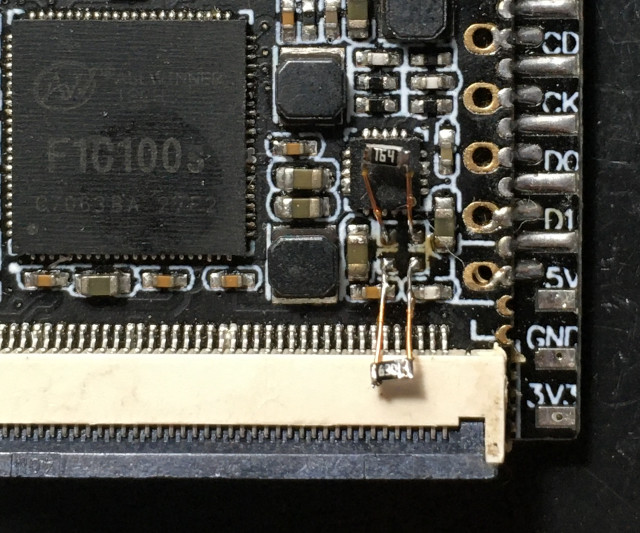

同場加映,司徒決定測試一下F1C100S超頻的持久度,這問題,真是一個老男人心中的痛...,於是,司徒找來幾顆精密電阻,0.6 * (464K / 150K) + 0.6 = 2.456V

2.456V,雖然多了0.056V,不過應該差不多,這個電壓是司徒之前測試,F1C100S最大可以承受的電壓

接著,司徒再度詢問芒果四兄弟,此時,勇敢的二哥二話不說,馬上挺身而出

移除R12、R13

0.6 * (464K / 150K) + 0.6 = 2.456V,司徒也幫二哥焊接一顆光明燈,期許實驗平安順利

既然,芒果都由二哥出戰了,於是司徒詢問三姐的意願,三姐說它不適合拍照,司徒不相信,要求三姐給一張照片證明

恩,三姐還是不要出戰好了,不然,司徒可能會變成殘障人士...

於是,司徒請來金大哥,聽說金大哥練過金鐘罩...

開始測驗,CPU=2016MHz,二哥忍耐一下,馬上就可以脫離苦海了...

二哥的光明燈開始閃爍

6秒後...,芒果二哥終於離開人間,再怎麼連接USB,都無法進入燒錄模式,願二哥安祥...

於是,司徒找來另外的精密點組,442K電阻配上160K電阻,0.6 * (442K / 160K) + 0.6 = 2.2575V

此時,三哥默默走了出來,司徒替三哥治裝...,0.6 * (442K / 160K) + 0.6 = 2.2575V

三哥開始...

CPU=2016MHz,10秒後掛點,不過插入USB,還是可以進入燒錄模式,因此,電壓2.2575V是不會燒毀F1C100S的保險電壓,而司徒測試CPU=1920MHz,三哥竟然撐過60秒,三哥真男人

60秒後,二姐馬上量測溫度,果然會燙...

於是,小護士準備幫三哥打針,可惜司徒臨時找不到散熱片...

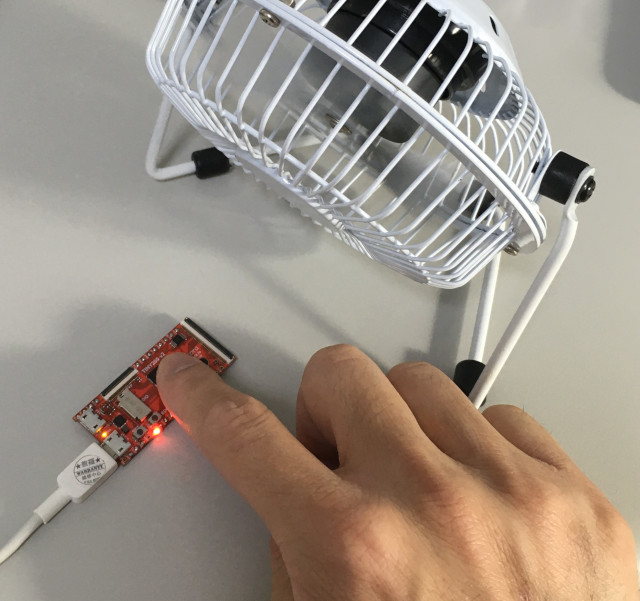

那就只好電風扇伺候...

二姐測量溫度,果然還是有點燙,不過,CPU=1920MHz,跑了三分鐘,依然沒有問題,因此,司徒覺得1920MHz,加上散熱片,應該是可以拿來使用的

僅存的芒果三兄弟

測試代碼

.global _start

.equiv CCU_BASE, 0x01c20000

.equiv GPIO_BASE, 0x01c20800

.equiv PLL_CPU_CTRL_REG, 0x0000

.equiv PLL_PERIPH_CTRL_REG, 0x0028

.equiv AHB_APB_HCLKC_CFG_REG, 0x0054

.equiv BUS_CLK_GATING_REG2, 0x0068

.equiv BUS_SOFT_RST_REG2, 0x02d0

.equiv PA, (0x24 * 0)

.equiv PORT_CFG0, 0x00

.equiv PORT_DATA, 0x10

.arm

.text

_start:

.long 0xea000016

.byte 'e', 'G', 'O', 'N', '.', 'B', 'T', '0'

.long 0, __spl_size

.byte 'S', 'P', 'L', 2

.long 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

_vector:

b reset

b .

b .

b .

b .

b .

b .

b .

reset:

ldr r4, =CCU_BASE

ldr r1, =(1 << 31) | (19 << 8) | (3 << 4)

str r1, [r4, #PLL_CPU_CTRL_REG]

0:

ldr r1, [r4, #PLL_CPU_CTRL_REG]

tst r1, #(1 << 28)

beq 0b

ldr r0, =GPIO_BASE

ldr r1, =0x1000

str r1, [r0, #(PA + PORT_CFG0)]

0:

ldr r1, =0x08

str r1, [r0, #(PA + PORT_DATA)]

ldr r2, =500000

1:

subs r2, #1

bne 1b

ldr r1, =0x00

str r1, [r0, #(PA + PORT_DATA)]

ldr r2, =500000

2:

subs r2, #1

bne 2b

b 0b

.end**結論:

CPU=2016MHz,需要找出臨界電壓,容易燒毀,不建議使用

CPU=1920MHz,F1C100S加上散熱片,可以跑,目前只有測試GPIO Toggle,只在芒果派上測試,其他開發板不保證電壓如表格一樣**

离线

#65 2021-06-16 16:25:21 分享评论

- skywalk00

- 会员

- 注册时间: 2021-04-01

- 已发帖子: 20

- 积分: 15.5

Re: 研究FC3000掌機的開源可行性

我试过小霸王Q2升级版直接插V90翻盖游戏机(我那款叫POWKIDDY不过应该一样)的内存卡,结果灯亮黑屏,我猜可能要把华邦八脚的SPI FALSH吹掉再试试,一直没时间搞,等我把他用风枪吹掉再试一试。

离线

楼主 #66 2021-06-16 16:37:17 分享评论

#67 2021-06-16 18:10:22 分享评论

- shawn.d

- 会员

- 注册时间: 2020-09-12

- 已发帖子: 164

- 积分: 85

Re: 研究FC3000掌機的開源可行性

@司徒

EPM240不支持内嵌逻辑分析仪,如果只是想UARTl输出,可以用下面这个现成的代码。前端打两拍或三拍采一下,用FIFO更好,时钟要用屏的时钟,不要用板载的。

https://opencores.org/projects/uart16550

离线

楼主 #68 2021-06-16 18:35:37 分享评论

Re: 研究FC3000掌機的開源可行性

@shawn.d

好,我找時間試試,感謝

荔枝姐詢問司徒,為何最近都在搞芒果哥?這問題...,司徒如何啟齒...

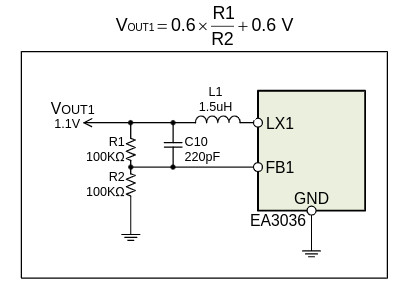

目前VCC_CORE=1.1V,超頻首要工作就是加大電壓,電壓公式:0.6 * (R47 / R48) + 0.6)

R47、R48位置

移除R47、R48

R47=442K、R48=160K,0.6 * (442K / 160K) + 0.6 = 2.2575V

CPU=2016MHz,三秒就掛了,於是,電風扇伺候,CPU=1920MHz,可以跑I/O Toggle了...

司徒一摸荔枝姐,這...溫度怎麼比芒果哥還要激情...

測試程式

.global _start

.equiv CCU_BASE, 0x01c20000

.equiv GPIO_BASE, 0x01c20800

.equiv PLL_CPU_CTRL_REG, 0x0000

.equiv PLL_PERIPH_CTRL_REG, 0x0028

.equiv AHB_APB_HCLKC_CFG_REG, 0x0054

.equiv BUS_CLK_GATING_REG2, 0x0068

.equiv BUS_SOFT_RST_REG2, 0x02d0

.equiv PE, (0x24 * 4)

.equiv PORT_CFG0, 0x00

.equiv PORT_DATA, 0x10

.arm

.text

_start:

.long 0xea000016

.byte 'e', 'G', 'O', 'N', '.', 'B', 'T', '0'

.long 0, __spl_size

.byte 'S', 'P', 'L', 2

.long 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

_vector:

b reset

b .

b .

b .

b .

b .

b .

b .

reset:

ldr r4, =CCU_BASE

ldr r1, =(1 << 31) | (19 << 8) | (3 << 4)

str r1, [r4, #PLL_CPU_CTRL_REG]

0:

ldr r1, [r4, #PLL_CPU_CTRL_REG]

tst r1, #(1 << 28)

beq 0b

ldr r0, =GPIO_BASE

ldr r1, =0x10000

str r1, [r0, #(PE + PORT_CFG0)]

0:

eor r1, #0x10

str r1, [r0, #(PE + PORT_DATA)]

ldr r2, =500000

1:

subs r2, #1

bne 1b

b 0b

.end**結論:

荔枝派一樣可以超頻到1.9GHz,只是溫度感覺比芒果派稍微高一點,錯覺?**

离线

楼主 #69 2021-06-18 11:54:14 分享评论

Re: 研究FC3000掌機的開源可行性

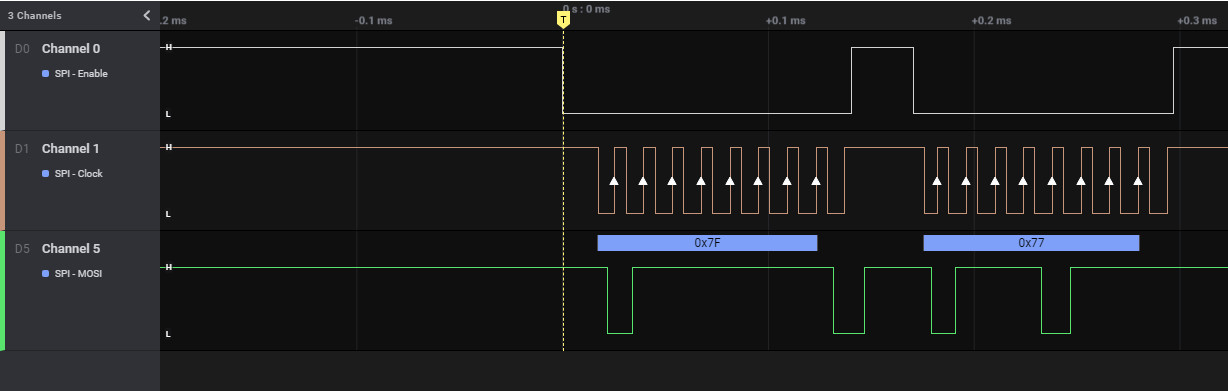

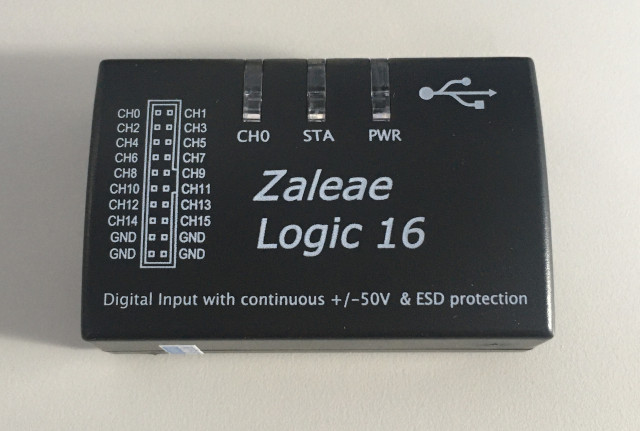

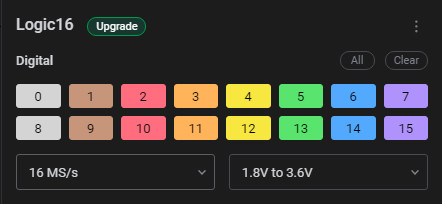

司徒買一台山寨Saleae Logic 16,體積很迷你

不過,同時開啟16通道時,取樣率只有16MS/s...

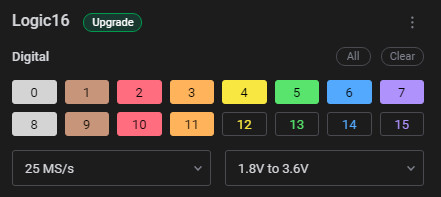

在測試過16通道16MS/s取樣率後,司徒發現每次取的資料都有變動,資料不一致性有點大,這邏輯分析儀...,於是,司徒改成使用12通道25MS/s的取樣率

測試幾次後,發現資料不一致性還是有,不過已經好很多了,不過LCD是16Bits,在加上LCD_WR、LCD_RS,需要18通道才行,於是司徒分兩次擷取

低位元資料(取5次):LCD_RS、LCD_WR、LCD_DB0~LCD_DB9

高位元資料(取5次):LCD_RS、LCD_WR、LCD_DB6~LCD_DB15

擷取後,把高位元資料進行排列,假定這些多餘的資料為雜訊,手動濾掉

低位元資料進行排列,假定這些多餘的資料為雜訊,手動濾掉

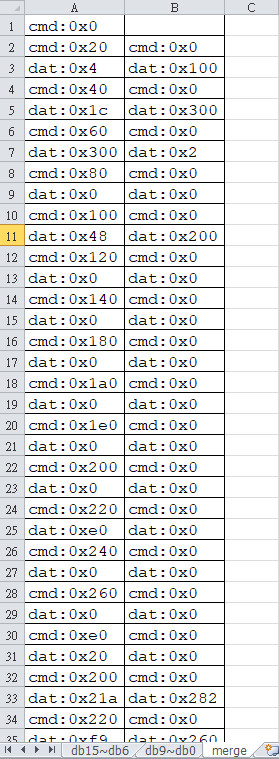

再做合併時,發現低位元資料少一筆,這...,不過,仔細一看,資料都是一筆CMD、一筆DAT,然後LCD_DB6~LCD_DB9是疊加取樣,因此,交叉比對後,發現第一筆高位元資料是雜訊

合併後的初始化命令

CMD:0x800

DAT:0x100

CMD:0x1000

DAT:0x700

CMD:0x1800

DAT:0xc002

CMD:0x2000

DAT:0x0

CMD:0x4000

DAT:0x1200

CMD:0x4800

DAT:0x0

CMD:0x5000

DAT:0x0

CMD:0x6000

DAT:0x0

CMD:0x6800

DAT:0x0

CMD:0x7800

DAT:0x0

CMD:0x8000

DAT:0x0

CMD:0x8800

DAT:0x3800

CMD:0x9000

DAT:0x0

CMD:0x9800

DAT:0x0

CMD:0x3800

DAT:0x800

CMD:0x8000

DAT:0x8682

CMD:0x8800

DAT:0x3e60

CMD:0x9000

DAT:0xc080

CMD:0x9800

DAT:0x603

CMD:0x4820

DAT:0xf000

CMD:0x5820

DAT:0x7000

CMD:0x20

DAT:0x0

CMD:0x820

DAT:0x0

CMD:0x8020

DAT:0x0

CMD:0x8820

DAT:0x3d00

CMD:0x9020

DAT:0x2000

CMD:0xa820

DAT:0x2a00

CMD:0xb020

DAT:0x2000

CMD:0xb820

DAT:0x3b00

CMD:0xc020

DAT:0x1000

CMD:0xc820

DAT:0x3f00

CMD:0xe020

DAT:0x1500

CMD:0xe820

DAT:0x2000

CMD:0x8040

DAT:0x0

CMD:0x8840

DAT:0x78e0

CMD:0x9040

DAT:0x0

CMD:0x9840

DAT:0xf920

CMD:0x60

DAT:0x714

CMD:0x860

DAT:0x800

CMD:0x5060

DAT:0x0

CMD:0x80

DAT:0x0

CMD:0x880

DAT:0x0

CMD:0x1080

DAT:0x0

CMD:0x1880

DAT:0x0

CMD:0x2080

DAT:0x0

CMD:0x2880

DAT:0x0

CMD:0x8080

DAT:0x8000

CMD:0x9080

DAT:0x600

CMD:0x1800

DAT:0x4020

CMD:0x3800

DAT:0x9920

CMD:0x8040

DAT:0x0

CMD:0x8840

DAT:0x78e0

CMD:0x9040

DAT:0x0

CMD:0x9840

DAT:0xf920

CMD:0x20

DAT:0x78e0

CMD:0x820

DAT:0x0

CMD:0x1020

DAT:0x0測試程式

.global _start

.equiv PIO_BASE, 0x01c20800

.equiv PD, (0x24 * 3)

.equiv PE, (0x24 * 4)

.equiv PIO_CFG0, 0x00

.equiv PIO_CFG1, 0x04

.equiv PIO_CFG2, 0x08

.equiv PIO_DATA, 0x10

.equiv LCD_CS, (1 << 21)

.equiv LCD_RD, (1 << 20)

.equiv LCD_RS, (1 << 19)

.equiv LCD_WR, (1 << 18)

.equiv LCD_RST, (1 << 11)

.equiv LCD_BL, (1 << 6)

.arm

.text

_start:

.long 0xea000016

.byte 'e', 'G', 'O', 'N', '.', 'B', 'T', '0'

.long 0, __spl_size

.byte 'S', 'P', 'L', 2

.long 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0

_vector:

b reset

b .

b .

b .

b .

b .

b .

b .

reset:

ldr r4, =PIO_BASE + PD

ldr r1, =0x11111111

str r1, [r4, #PIO_CFG0]

str r1, [r4, #PIO_CFG1]

ldr r1, =0x00111111

str r1, [r4, #PIO_CFG2]

ldr r4, =PIO_BASE + PE

ldr r1, [r4, #PIO_CFG0]

bic r1, #0xf000000

orr r1, #0x1000000

str r1, [r4, #PIO_CFG0]

ldr r1, [r4, #PIO_CFG1]

bic r1, #0xf000

orr r1, #0x1000

str r1, [r4, #PIO_CFG1]

ldr r4, =PIO_BASE + PD

ldr r1, =0xffffffff

str r1, [r4, #PIO_DATA]

ldr r4, =PIO_BASE + PE

ldr r1, =0xffffffff

str r1, [r4, #PIO_DATA]

bl lcd_rst

ldr r0, =0x800

bl lcd_cmd

ldr r0, =0x100

bl lcd_dat

ldr r0, =0x1000

bl lcd_cmd

ldr r0, =0x700

bl lcd_dat

ldr r0, =0x1800

bl lcd_cmd

ldr r0, =0xc002

bl lcd_dat

ldr r0, =0x2000

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x4000

bl lcd_cmd

ldr r0, =0x1200

bl lcd_dat

ldr r0, =0x4800

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x5000

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x6000

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x6800

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x7800

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x8000

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x8800

bl lcd_cmd

ldr r0, =0x3800

bl lcd_dat

ldr r0, =0x9000

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x9800

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x3800

bl lcd_cmd

ldr r0, =0x800

bl lcd_dat

ldr r0, =0x8000

bl lcd_cmd

ldr r0, =0x8682

bl lcd_dat

ldr r0, =0x8800

bl lcd_cmd

ldr r0, =0x3e60

bl lcd_dat

ldr r0, =0x9000

bl lcd_cmd

ldr r0, =0xc080

bl lcd_dat

ldr r0, =0x9800

bl lcd_cmd

ldr r0, =0x603

bl lcd_dat

ldr r0, =0x4820

bl lcd_cmd

ldr r0, =0xf000

bl lcd_dat

ldr r0, =0x5820

bl lcd_cmd

ldr r0, =0x7000

bl lcd_dat

ldr r0, =0x20

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x820

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x8020

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x8820

bl lcd_cmd

ldr r0, =0x3d00

bl lcd_dat

ldr r0, =0x9020

bl lcd_cmd

ldr r0, =0x2000

bl lcd_dat

ldr r0, =0xa820

bl lcd_cmd

ldr r0, =0x2a00

bl lcd_dat

ldr r0, =0xb020

bl lcd_cmd

ldr r0, =0x2000

bl lcd_dat

ldr r0, =0xb820

bl lcd_cmd

ldr r0, =0x3b00

bl lcd_dat

ldr r0, =0xc020

bl lcd_cmd

ldr r0, =0x1000

bl lcd_dat

ldr r0, =0xc820

bl lcd_cmd

ldr r0, =0x3f00

bl lcd_dat

ldr r0, =0xe020

bl lcd_cmd

ldr r0, =0x1500

bl lcd_dat

ldr r0, =0xe820

bl lcd_cmd

ldr r0, =0x2000

bl lcd_dat

ldr r0, =0x8040

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x8840

bl lcd_cmd

ldr r0, =0x78e0

bl lcd_dat

ldr r0, =0x9040

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x9840

bl lcd_cmd

ldr r0, =0xf920

bl lcd_dat

ldr r0, =0x60

bl lcd_cmd

ldr r0, =0x714

bl lcd_dat

ldr r0, =0x860

bl lcd_cmd

ldr r0, =0x800

bl lcd_dat

ldr r0, =0x5060

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x80

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x880

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x1080

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x1880

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x2080

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x2880

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x8080

bl lcd_cmd

ldr r0, =0x8000

bl lcd_dat

ldr r0, =0x9080

bl lcd_cmd

ldr r0, =0x600

bl lcd_dat

ldr r0, =0x1800

bl lcd_cmd

ldr r0, =0x4020

bl lcd_dat

ldr r0, =0x3800

bl lcd_cmd

ldr r0, =0x9920

bl lcd_dat

ldr r0, =0x8040

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x8840

bl lcd_cmd

ldr r0, =0x78e0

bl lcd_dat

ldr r0, =0x9040

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x9840

bl lcd_cmd

ldr r0, =0xf920

bl lcd_dat

ldr r0, =0x20

bl lcd_cmd

ldr r0, =0x78e0

bl lcd_dat

ldr r0, =0x820

bl lcd_cmd

ldr r0, =0x0

bl lcd_dat

ldr r0, =0x1020

bl lcd_cmd

ldr r4, =320*80

ldr r5, =0x1f

0:

mov r0, r5

bl lcd_dat

subs r4, #1

bne 0b

ldr r4, =320*80

ldr r5, =0x7e0

0:

mov r0, r5

bl lcd_dat

subs r4, #1

bne 0b

ldr r4, =320*80

ldr r5, =0xf800

0:

mov r0, r5

bl lcd_dat

subs r4, #1

bne 0b

b .

delay:

push {lr}

0:

subs r0, #1

bne 0b

pop {pc}

lcd_rst:

push {r4, r5, lr}

ldr r4, =PIO_BASE + PE

ldr r5, =0xffffffff

bic r5, #LCD_RST

str r5, [r4, #PIO_DATA]

ldr r0, =10000

bl delay

orr r5, #LCD_RST

str r5, [r4, #PIO_DATA]

ldr r0, =10000

bl delay

pop {r4, r5, pc}

lcd_wr:

push {r4, r5, lr}

ldr r4, =PIO_BASE + PD

and r2, r0, #0x00ff

and r3, r0, #0xff00

lsl r2, #1

lsl r3, #2

eor r5, r5

orr r5, r1

orr r5, r2

orr r5, r3

orr r5, #LCD_RD

str r5, [r4, #PIO_DATA]

orr r5, #LCD_WR

str r5, [r4, #PIO_DATA]

pop {r4, r5, pc}

lcd_dat:

push {lr}

mov r1, #LCD_RS

bl lcd_wr

pop {pc}

lcd_cmd:

push {lr}

mov r1, #0

bl lcd_wr

pop {pc}

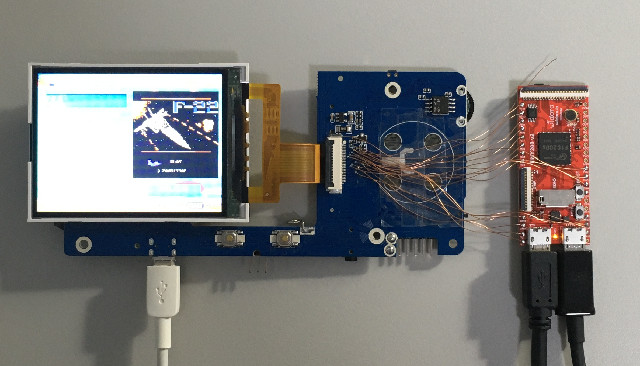

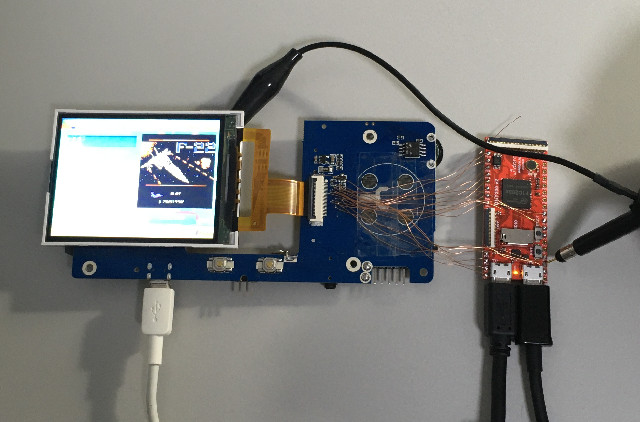

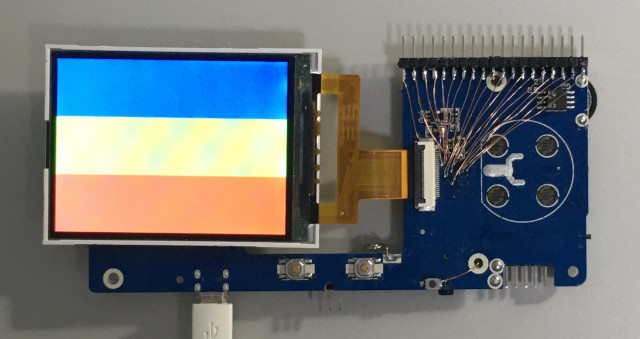

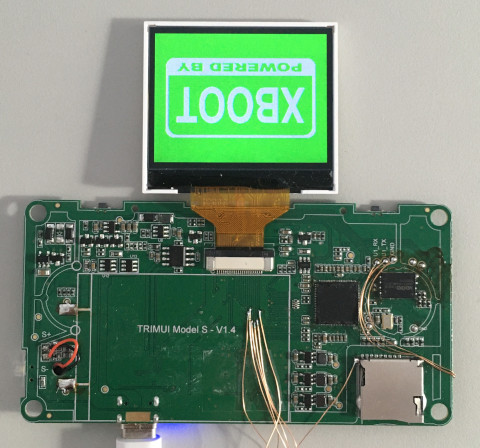

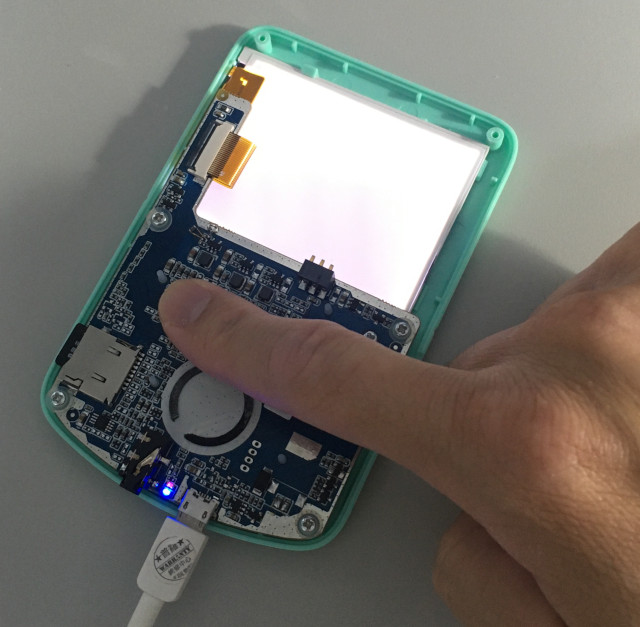

.end感動的一刻

离线

楼主 #70 2021-06-18 14:22:59 分享评论

Re: 研究FC3000掌機的開源可行性

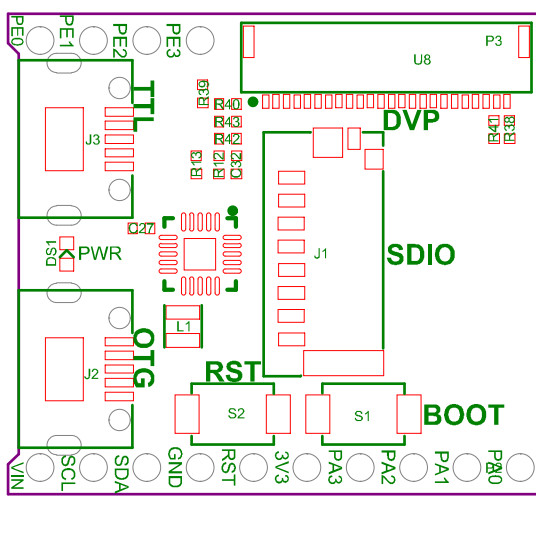

接著司徒花了一些時間,把腳位找了出來,這樣FC3000掌機就進入備戰狀態了~

UP PF0

DOWN PF5

LEFT PF4

RIGHT PE2

A PE3

B PE4

X PE5

Y PA3

I BTA54C(Pin3)

BAT54C(Pin1)PA2

R PA2, 1AM-C(Pin3)

L PA1, 1AM-C(Pin3)

START PE12, BAT54C(Pin2)

SELECT PE12, BAT54C(Pin1)

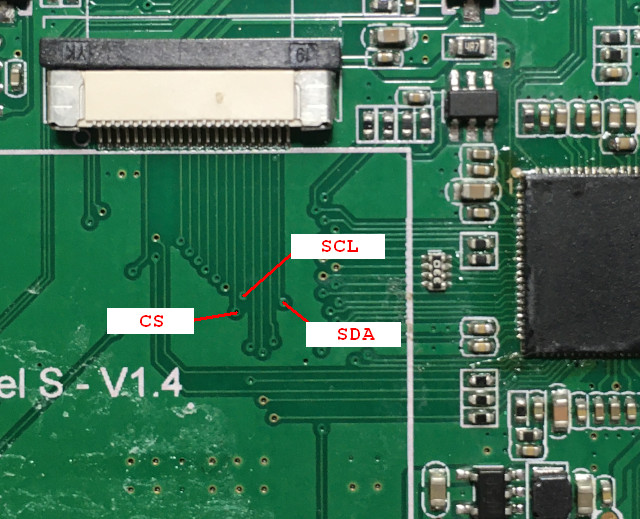

Encrypt IC(Pin6) I2C_SCK PE0

Encrypt IC(Pin7) I2C_SDA PE1

Encrypt IC(Pin2) Blue LED-

LTH7 CHRG Red LED-

MicroSD D0 PF1

MicroSD CLK PF2

MicroSD CMD PF3

Boot SPI Flash CS PC1

Boot SPI Flash MISO PC2

Boot SPI Flash MOSI PC3

Boot SPI Flash SCK PC0

SPI Flash CS PE7

SPI Flash MISO PE10

SPI Flash MOSI PE8

SPI Flash CLK PE9

LCD BK PE6

LCD RST PE11

LCD CS PD21

LCD RS PD19

LCD WR PD18

LCD DB11 PD13

LCD DB12 PD14

LCD DB13 PD15

LCD DB14 PD16

LCD DB15 PD17

LCD DB5 PD6

LCD DB6 PD7

LCD DB7 PD8

LCD DB8 PD10

LCD DB9 PD11

LCD DB10 PD12

LCD DB0 PD1

LCD DB1 PD2

LCD DB2 PD3

LCD DB3 PD4

LCD DB4 PD5离线

#71 2021-06-18 14:28:21 分享评论

- cube

- 会员

- 注册时间: 2021-03-11

- 已发帖子: 288

- 积分: 202.5

Re: 研究FC3000掌機的開源可行性

🍀司徒🍀大佬真牛🐂

请问液晶的驱动芯片确定了吗?

离线

楼主 #72 2021-06-18 14:34:33 分享评论

楼主 #73 2021-06-18 14:42:57 分享评论

Re: 研究FC3000掌機的開源可行性

如果有玩家想要讓FC3000掌機跑Linux系統,需要飛三根線,這是最少的改機步驟

接著需要改機,否則無法從MicroSD開機

需要跳三根線

這樣就可以從MicroSD開機

不要插入卡帶,MicroSD卡的位置很方便替換

fc3000_lcd_test.img

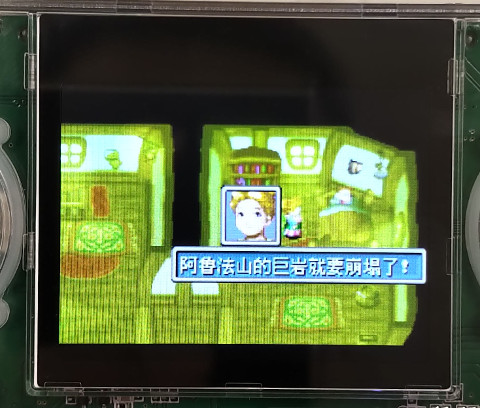

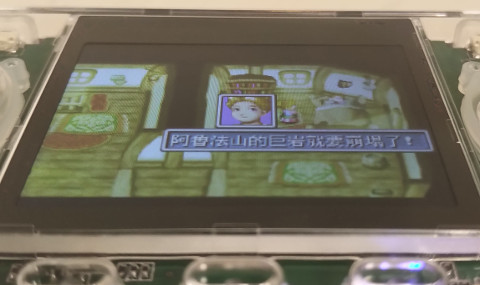

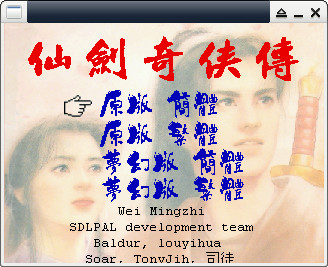

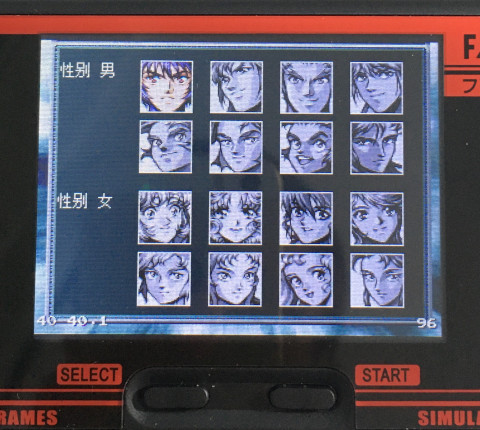

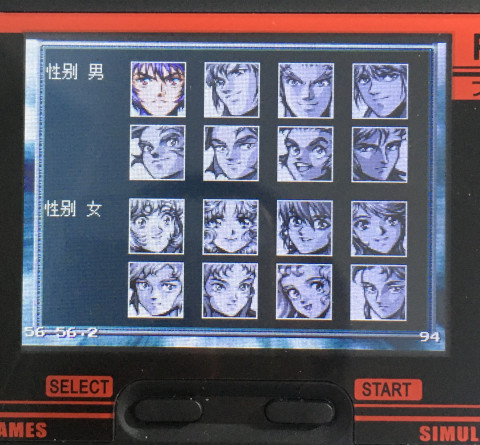

下載fc3000_lcd_test.img,直接DD到MicroSD即可,插入MicroSD卡後,開機上電,這樣就可以測試是否改機完成,屏會一直換顏色

使用原本官方MicroSD開機,則可以進入原本系統

插入卡帶

則開機進入NES遊戲畫面,做到這一步,FC3000掌機已經具備跑Linux系統的能力,因此,一般玩家想要讓FC3000掌機可以具備跑Linux的能力,只要跳三根線即可

离线

#74 2021-06-18 16:17:28 分享评论

- xk100

- 会员

- 注册时间: 2018-12-13

- 已发帖子: 75

- 积分: 58.5

Re: 研究FC3000掌機的開源可行性

大神认真的精神令人佩服。

离线

#75 2021-06-18 16:53:46 分享评论

- 怀旧堂

- 会员

- 注册时间: 2021-06-11

- 已发帖子: 17

- 积分: 310

Re: 研究FC3000掌機的開源可行性

几天没关注,进展这么快啦,大佬就是大佬。

司徒大佬啥时也搞搞funkeys啊?V3S比100S强大的多啊。

论坛有人发帖了。

发现一个蛮精致的开源掌机叫FunKey,使用的V3s

离线

楼主 #76 2021-06-18 17:52:23 分享评论

#77 2021-06-18 19:47:39 分享评论

- shawn.d

- 会员

- 注册时间: 2020-09-12

- 已发帖子: 164

- 积分: 85

Re: 研究FC3000掌機的開源可行性

@司徒

这就飞龙在天了,哈哈!

离线

楼主 #78 2021-06-18 21:10:51 分享评论

Re: 研究FC3000掌機的開源可行性

確實有飛龍在天的感覺,難怪司徒昨晚在夢境之中有雙飛的感覺,雙龍飛舞的意思,不要誤會

能夠走到這一步,小弟在此感謝所有幫助過的人

FC3000掌機的目標很明確,就是要跑Linux Kernel,因此,司徒需要一個Bootloader用來載入Kernel,

而這個Bootloader的動作也很明確,就是初始化DRAM,然後從MicroSD載入Kernel,跳轉Kernel,

司徒要訂一個很嚴格的目標:FC3000掌機上電後,執行完Kernel,UART顯示Login畫面,必須在一秒內,執行完畢

看似不太可能,不過總是要試試才知道~

目前在應用上,最熱門就是UBoot,不過,UBoot真的太肥、太大了,XBoot也需要瘦身,司徒在whycan有看到一些人,自己做精簡版Bootloader,不過,司徒最後決定自己幹一個超精簡Bootloader給FC3000掌機專用,所以,可能幾個月後,才會在更新了~哈

离线

#79 2021-06-18 21:24:04 分享评论

- kekemuyu

- 会员

- 注册时间: 2018-12-13

- 已发帖子: 856

- 积分: 697

Re: 研究FC3000掌機的開源可行性

@司徒

只是引导linux,坛子里有人做过了。代码才3k,https://whycan.com/t_5060.html

离线

楼主 #80 2021-06-19 10:43:22 分享评论

楼主 #81 2021-06-19 12:03:51 分享评论

Re: 研究FC3000掌機的開源可行性

司徒原本沈浸在雙飛的感覺之中,心情愉悅,於是爽爽的寫FC3000程式,結果,竟然吃土了!

今天就來分享一下遇到的問題

目前FC3000掌機已經可以從MicroSD開機執行,於是,司徒依照個人慣例,都會把一些基本I/O程式練習一遍

所以,第一個測試就是點屏,這個沒有問題,第二個測試程式則是UART,結果竟然卡關...

但是,一樣的程式燒到SPI Flash竟然可以執行,司徒編譯後的Binary程式大小只有512 Bytes

後來交叉測試,發現F1C100S只會從MicroSD載入大於512 Bytes的Binary程式,意思就是寫到MicroSD的程式必須大於等於1024 Bytes,這也是為何司徒的短小測試程式無法從MicroSD執行的原因,SPI Flash就沒有這個限制,跟大家分享一下~

离线

楼主 #82 2021-06-25 10:27:13 分享评论

Re: 研究FC3000掌機的開源可行性

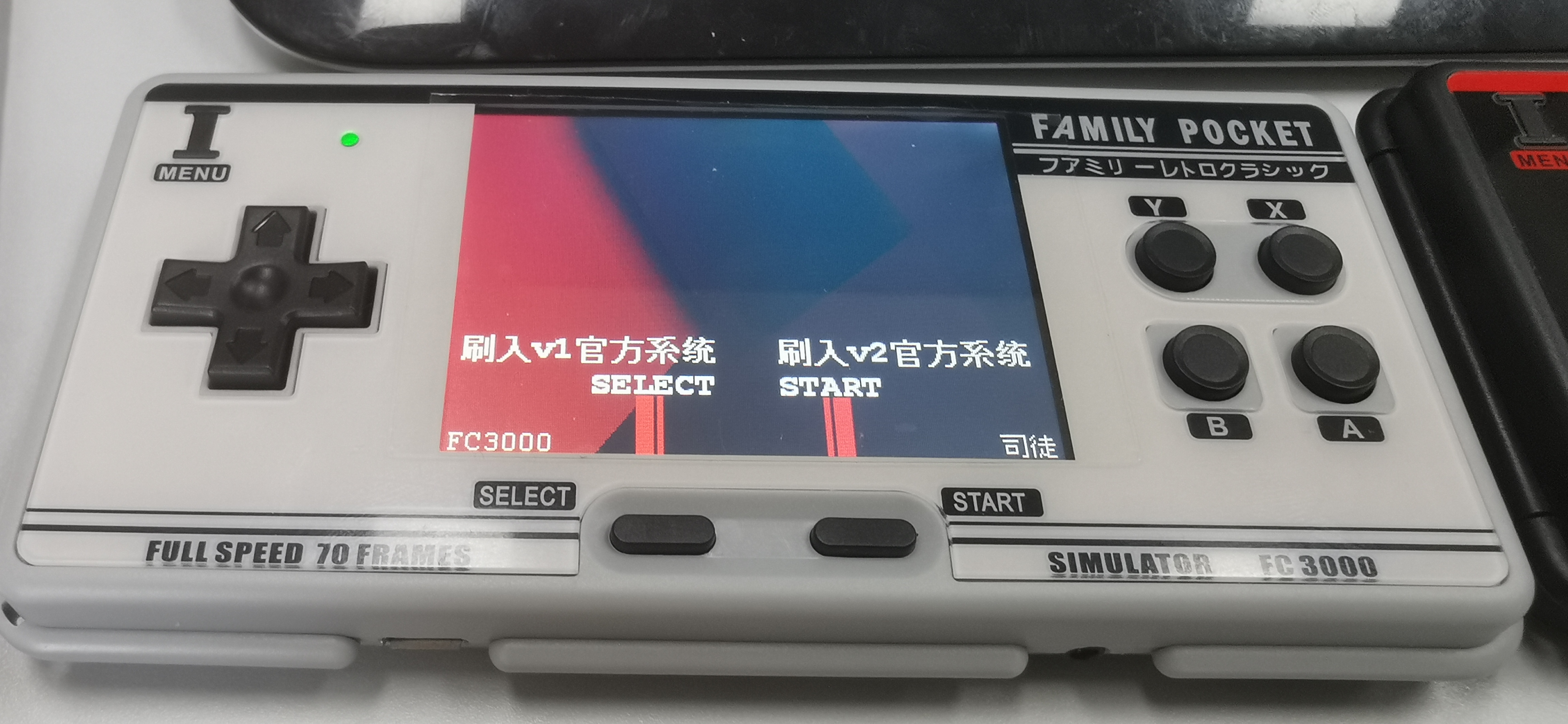

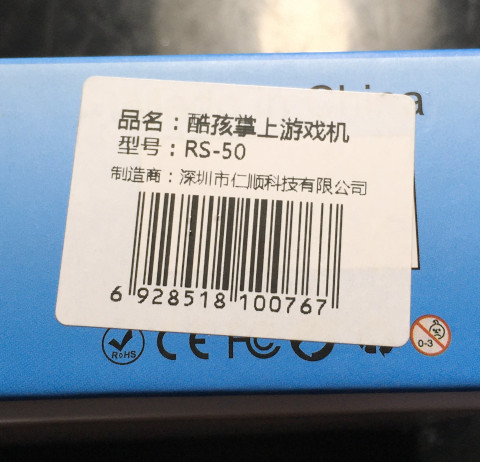

哈!真是相當對不起有改機的玩家,因為,經過司徒測試,FC3000掌機其實不需要改機就可以安裝Linux系統,因為F1C100S支援MicroSD 1bit/SPI模式開機

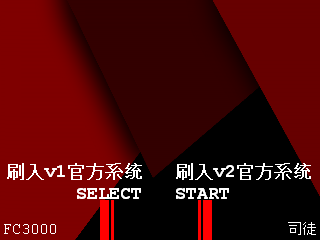

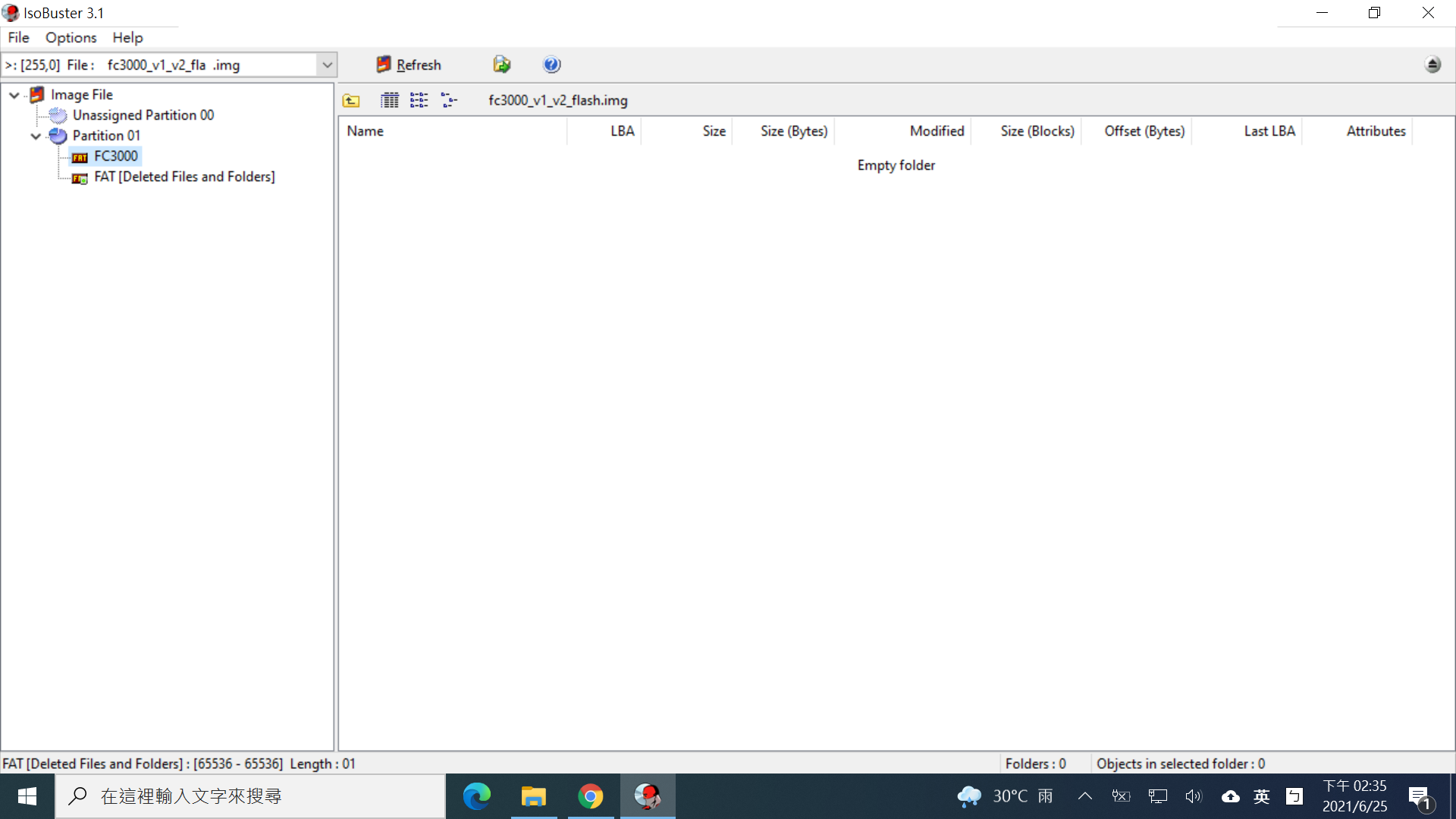

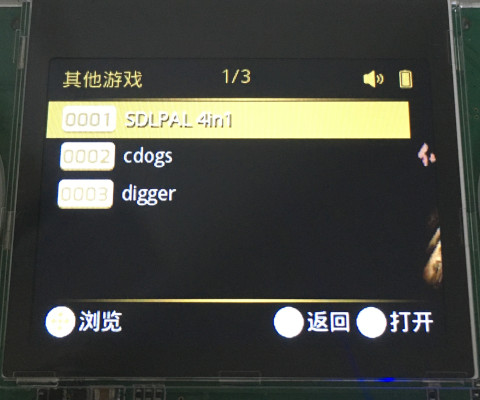

經過幾天奮戰,司徒的自幹Bootloader已經差不多了,然而,司徒這才發現FC3000 V2版本的機器,硬件跟V1版本一模一樣,只有SPI Flash不一樣,所以,司徒決定先來幹一件事情,那就是製作V1、V2系統升級程序,哈,有點擋人財路的感覺,司徒只是個人興趣愛好研究,請勿將此程序作為商業用途

步驟如下:

解壓縮後,將fc3000_v1_v2_flash.img直接燒錄到MicroSD

$ sudo dd if=fc3000_v1_v2_flash.img of=/dev/sdX bs=1M && sync && sync

64+0 records in

64+0 records out

67108864 bytes (67 MB, 64 MiB) copied, 6.40316 s, 10.5 MB/sP.S. sdX為當下的MicroSD位置

司徒目前只有測試SanDisk記憶卡

移除卡帶

插入剛剛燒錄完成的MicroSD

插入電池,開機上電

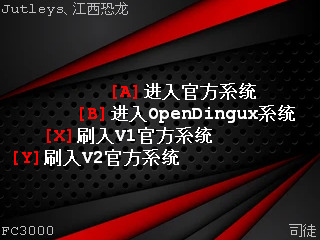

按下SELECT:刷入v1版本官方系統(8大模擬器)

按下START:刷入v2版本官方系統(10大模擬器)

更新時間大約3分鐘

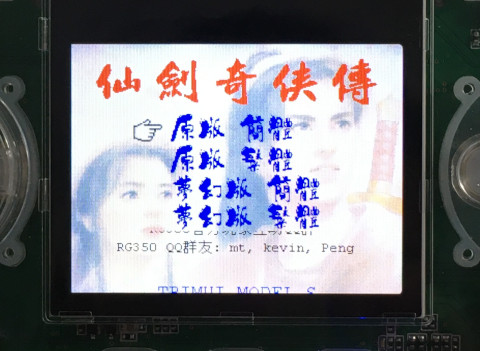

完成

v1版本系統(8大模擬器)

v2版本系統(10大模擬器)

既然Bootloader都自幹完畢了,那司徒接下來就準備要開始移植Linux Kernel,目前有三種可行方式:

使用當初司徒移植給Miyoo的Linux Kernel (Linux Kernel 4.14.0)

從荔枝派GitHub官網Clone移植 (Linux Kernel 5.2)

從目前最新的Linux Kernel從頭移植 (Linux Kernel 5.12.9)

為了榨乾F1C100S效能,司徒最後決定從目前最新的Linux Kernel 5.12.9從頭移植,所以可能幾個月後,司徒才會在更新了!哈哈~

不過,移植Linux Kernel需要一些時間,因此,司徒也會把預定的四台掌機(FC3000、Q8、TRIMUI、PocketGo)做整理,因此,當移植累了,司徒就會整理這四台掌機,讓這四台掌機都處於備戰狀態(硬體都解析出來),所以接下來,可能是混亂的開始,哈~

离线

#83 2021-06-25 10:48:02 分享评论

- skywalk00

- 会员

- 注册时间: 2021-04-01

- 已发帖子: 20

- 积分: 15.5

Re: 研究FC3000掌機的開源可行性

非常感谢司徒大神,为我们带来这么多可以玩的东西,特别是您的掌机网站,对我们来说可是无价之宝喔!详细的拆解过程以及何种芯片主控何种屏幕,对于我们这些爱拆机爱DIY的业余无线电玩家,可以避免走很多弯路,非常感谢!

离线

楼主 #84 2021-06-25 11:57:35 分享评论

#85 2021-06-25 12:53:26 分享评论

- masahiko

- 会员

- 注册时间: 2021-06-24

- 已发帖子: 13

- 积分: 22

Re: 研究FC3000掌機的開源可行性

司徒先生,我用 Win32DiskImager 燒入 fc3000_v1_v2_flash.img檔 後 fc3000 開機黑屏,沒有升級的選擇畫面

檢查寫入完成的 SD CARD ,發現裡面只有一個空的fc3000 分區,裡面沒有資料,請問是哪裡操做有問題?

感謝您

离线

楼主 #86 2021-06-25 13:42:33 分享评论

楼主 #87 2021-06-25 13:46:04 分享评论

#88 2021-06-25 15:06:36 分享评论

- masahiko

- 会员

- 注册时间: 2021-06-24

- 已发帖子: 13

- 积分: 22

Re: 研究FC3000掌機的開源可行性

司徒先生日安,不好意思再度麻煩你,我用Apacer 8G ,ADATA 64G ,SanDisk 32GB 測試也都一樣黑屏,會不會是因為我使用的是FC3000 V1版本機器的關係?

另外,是否麻煩你再上傳一次 fc3000_v1_v2_flash.img檔,因為我怎麼檢查它都是空的

再次感謝你

离线

楼主 #89 2021-06-25 15:20:08 分享评论

Re: 研究FC3000掌機的開源可行性

我重新上傳了一份:https://github.com/steward-fu/fc3000/releases/download/v1.0/fc3000_v1_v2_flash.img

你可以使用SHA1工具算一下檔案

fc3000_v1_v2_flash.img: a9d34ff94169f5a3f2afa768345540156c99d501

如果還是無法一樣進入燒錄選單的話,那~就遵照老天的旨意吧~

离线

楼主 #90 2021-06-25 15:25:13 分享评论

#91 2021-06-25 16:23:57 分享评论

- masahiko

- 会员

- 注册时间: 2021-06-24

- 已发帖子: 13

- 积分: 22

Re: 研究FC3000掌機的開源可行性

司徒先生日安,跟你回報一下,結果還是黑屏無法進入燒錄選單,真的是天意如此,感謝你的耐心回復

离线

楼主 #92 2021-06-25 17:10:37 分享评论

#93 2021-06-25 21:05:57 分享评论

- akting

- 会员

- 注册时间: 2021-06-25

- 已发帖子: 4

- 积分: 2

Re: 研究FC3000掌機的開源可行性

太棒了,看司徒大大折腾的过程就已经是种享受,感谢你

离线

楼主 #94 2021-06-25 22:37:56 分享评论

Re: 研究FC3000掌機的開源可行性

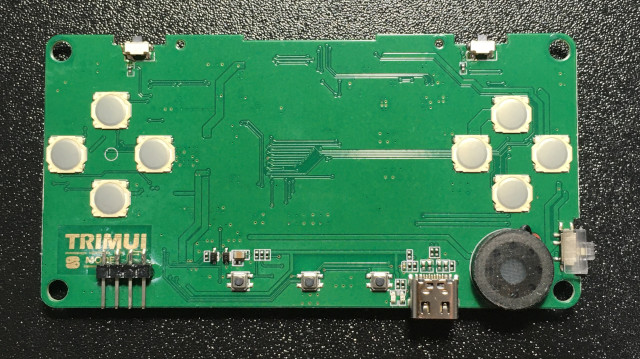

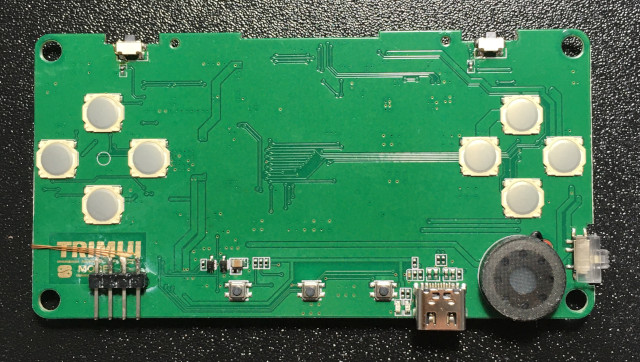

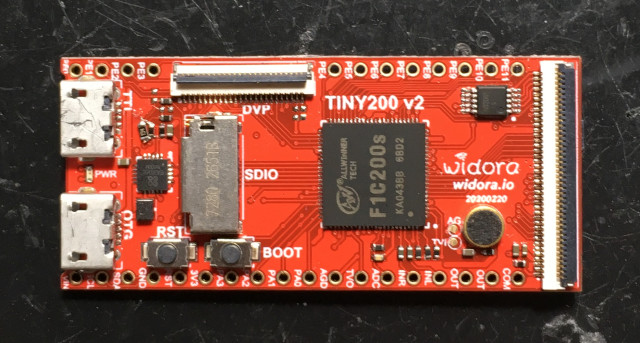

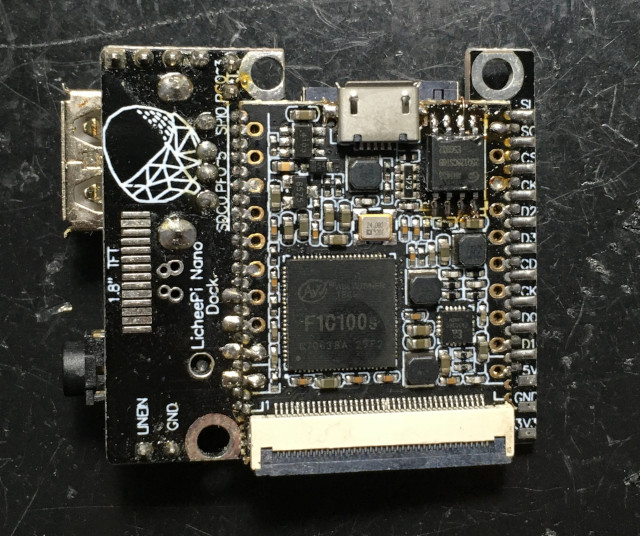

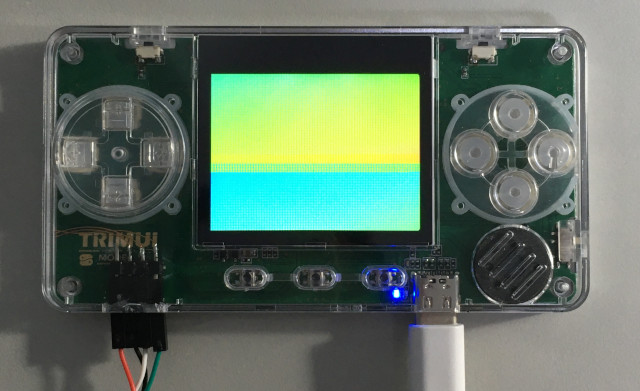

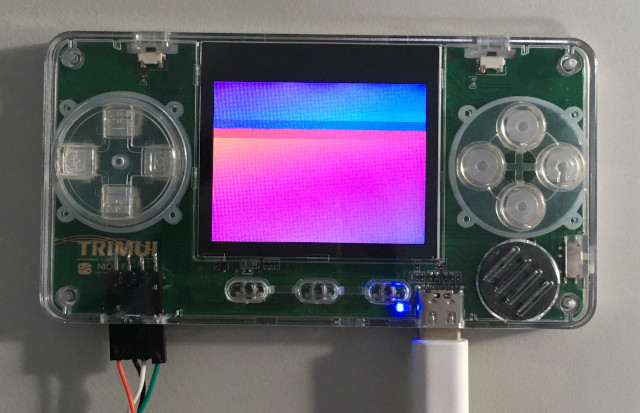

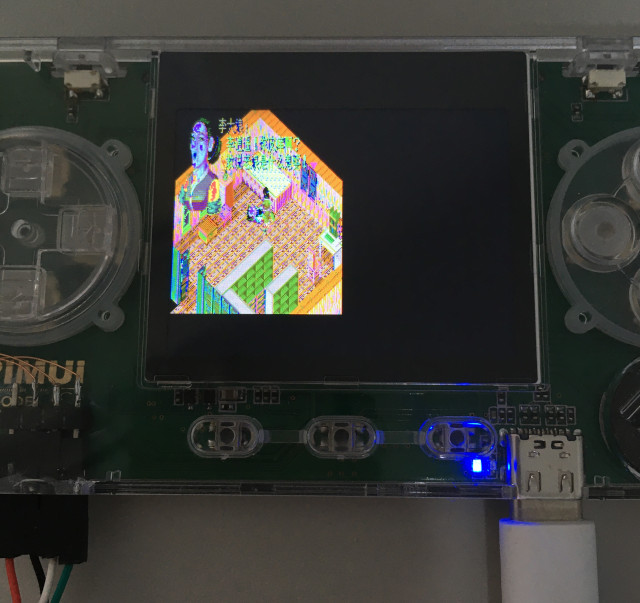

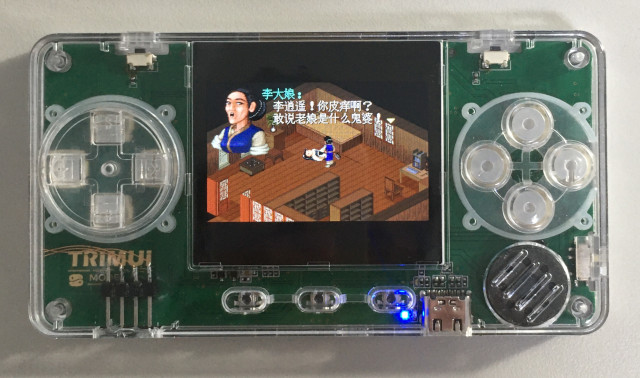

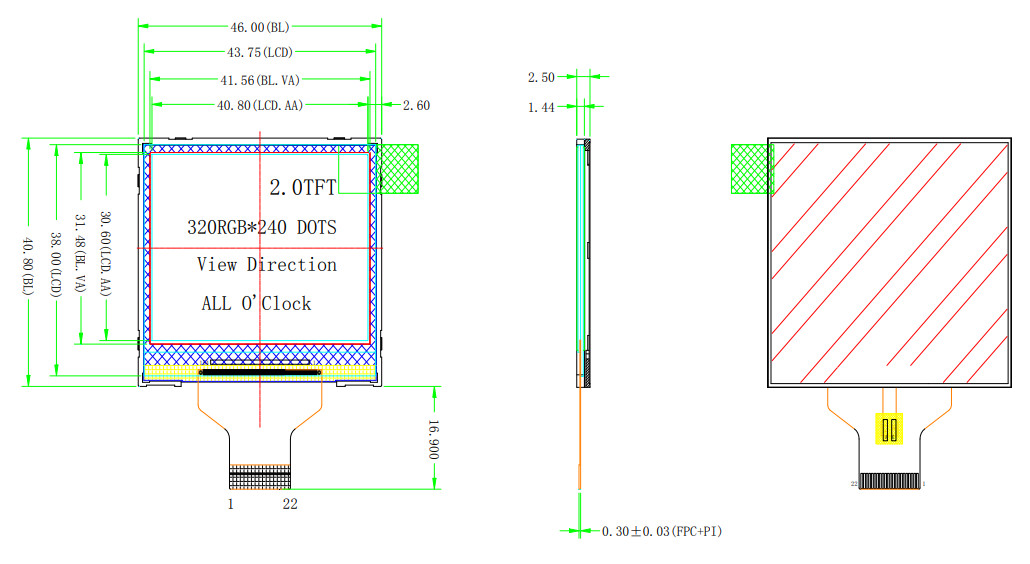

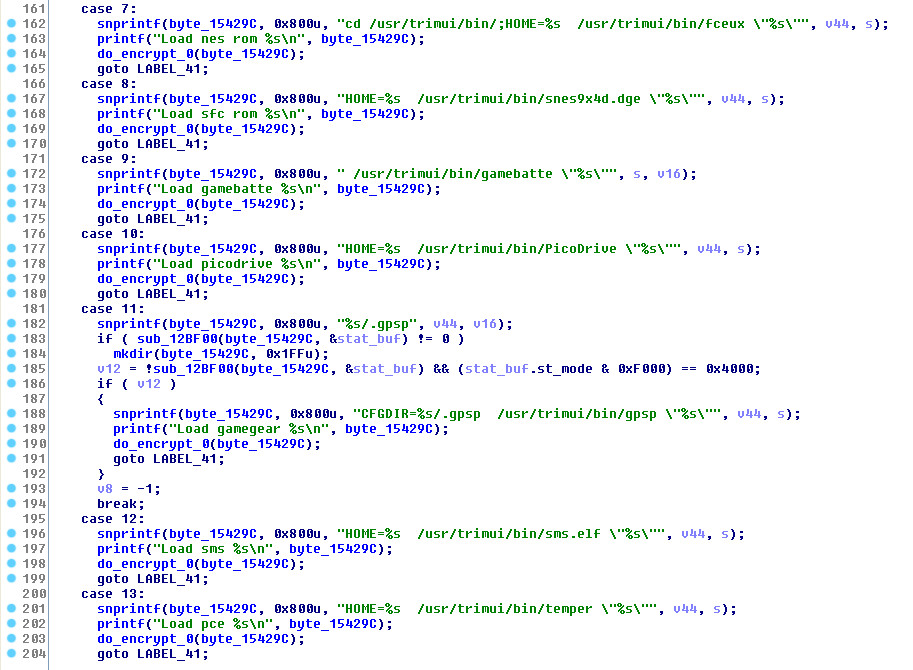

司徒接下來除了把重點鎖定在移植Linux Kernel之外,也同時鎖定另一台機器,那就是TRIMUI掌機,這台掌機使用F1C200S當作CPU,不過,司徒比較喜愛的是他的大小尺寸,相當便攜,可惜的是,司徒曾經試著聯繫廠商提供源代碼,一直沒有得到回覆(預期結果),當然,司徒只想知道TRIMUI掌機是否會閃屏,因為就司徒手上的資料,這台掌機應該也是有閃屏問題(8Bits BUS,沒有TE),為了解決這個好奇心,司徒又開始折騰...

四台F1C100S系列掌機比較

價格便宜:Q8 > FC3000 > TRIMUI > PocketGo

容易攜帶:TRIMUI > PocketGo > Q8 > FC3000

實際可玩:PocketGo > TRIMUI > FC3000 > Q8

有閃屏問題:FC3000、Q8

沒有閃屏問題:PocketGo

全視角屏幕:PocketGo、TRIMUI

司徒的目標很明確,就是要確定TRIMUI掌機是否有閃屏問題,而PocketGo掌機已經由司徒確定可以解決閃屏問題,只是司徒目前手上沒有PocketGo掌機,因此,重新下單,所以Q8掌機、PocektGo掌機的研究順序排位在最後

TRIMUI屏視角

TRIMUI大小比較

TRIMUI拆機

磨掉型號的IC(F1C200S)、MX35LF1GE4AB-241

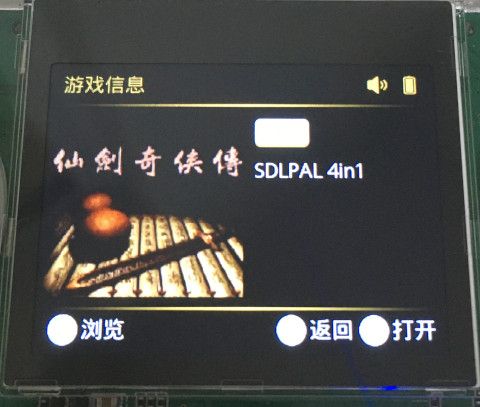

INANBO-T20CR6I-V20 2.0" IPS 320x240

离线

楼主 #95 2021-06-25 22:59:02 分享评论

楼主 #96 2021-06-25 23:04:04 分享评论

楼主 #97 2021-06-26 11:35:08 分享评论

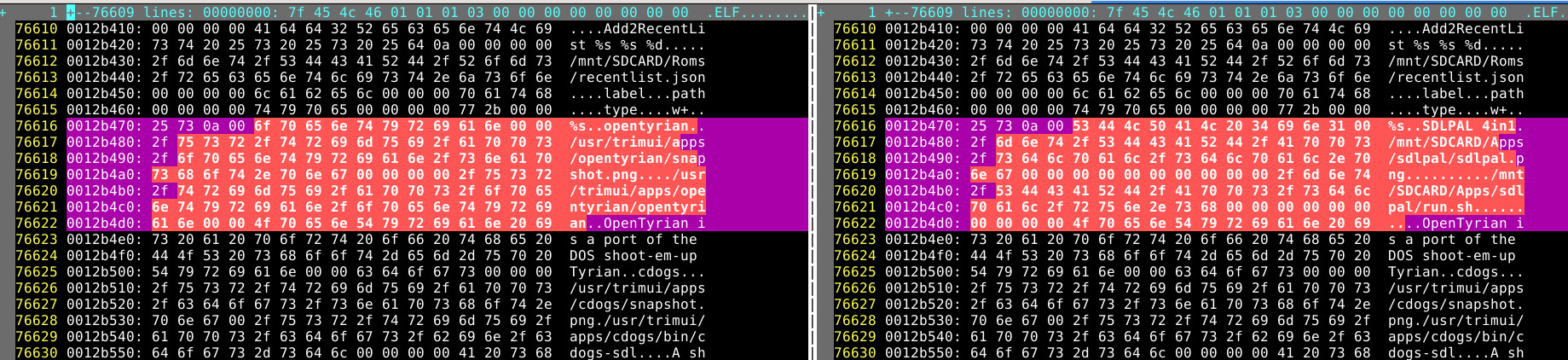

Re: 研究FC3000掌機的開源可行性

目前司徒的TRIMUI掌機是無法進入系統的,其實更正確的說,應該是司徒把它搞掛了~司徒嘗試使用官方建議方式,安裝燒錄軟體進行燒錄,可惜,司徒一直無法燒錄成功,於是,司徒心想,那就寫一個Bootloadert程式,用來把官方固件寫回NAND Flash就好,但是,司徒看了一下官方固件,發現格式怪怪的,於是開始挖掘這口乾枯的深井....

Ref:

https://github.com/Ithamar/awutils

https://stackoverflow.com/questions/48872746/what-is-an-imagewty-firmware-format

官方燒錄檔案 trimui_model_S_dark_V0.105_en.img

$ xxd trimui_model_S_dark_V0.105_en.img | head

00000000: 494d 4147 4557 5459 0003 0000 6000 0000 IMAGEWTY....`...

00000010: 0000 d004 3402 1000 00c8 5606 0000 0000 ....4.....V.....

00000020: 0004 0000 3412 0000 4387 0000 0001 0000 ....4...C.......

00000030: 0001 0000 0100 0000 0004 0000 1c00 0000 ................

00000040: 0004 0000 0000 0000 0000 0000 0000 0000 ................

00000050: 0000 0000 0000 0000 0000 0000 0000 0000 ................

00000060: 00c1 8449 10d9 a471 4011 e4b9 9069 4421 ...I...q@....iD!

00000070: 00e1 c4a9 9079 6451 4031 2419 1009 0401 .....ydQ@1$.....

00000080: 0001 0409 1019 2431 4051 6479 90a9 c4e1 ......$1@Qdy....

00000090: 0021 4469 90b9 e411 4071 a4d9 1049 84c1 .!Di....@q...I..官方固件是IMAGEWTY格式,於是司徒找到awutils工具,可以用來拆解

$ cd

$ git clone https://github.com/Ithamar/awutils

$ cd awutils

$ gcc parsecfg.c twofish.c rc6.c awimage.c -o awimage -I.解開 trimui_model_S_dark_V0.105_en.img

$ ./awimage ../trimui_model_S_dark_V0.105_en.img

./awimage: unpacking ../trimui_model_S_dark_V0.105_en.img to ../trimui_model_S_dark_V0.105_en.img.dump

Extracting: COMMON SYS_CONFIG100000 (45841, 45856)

Extracting: COMMON SYS_CONFIG_BIN00 (28672, 28672)

Extracting: COMMON SPLIT_0000000000 (512, 512)

Extracting: COMMON SYS_CONFIG000000 (3119, 3120)

Extracting: COMMON DTB_CONFIG000000 (50176, 50176)

Extracting: BOOT BOOT0_0000000000 (16384, 16384)

Extracting: 12345678 1234567890BOOT_0 (32768, 32768)

Extracting: 12345678 UBOOT_0000000000 (671744, 671744)

Extracting: 12345678 TOC1_00000000000 (8, 16)

Extracting: 12345678 TOC0_00000000000 (8, 16)

Extracting: FES FES_1-0000000000 (11648, 11648)

Extracting: 12345678 BOOTPKG-00000000 (753664, 753664)

Extracting: PXTOOLSB XXXXXXXXXXXXXXXX (147968, 147968)

Extracting: UPFLYTLS XXXXXXXXXXXXXXXX (165019, 165024)

Extracting: UPFLTL32 XXXXXXXXXXXXXXXX (150847, 150848)

Extracting: 12345678 1234567890CARDTL (73216, 73216)

Extracting: 12345678 1234567890SCRIPT (1758, 1760)

Extracting: 12345678 1234567890___MBR (65536, 65536)

Extracting: 12345678 1234567890DLINFO (16384, 16384)

Extracting: 12345678 1234567890ARISC (15, 16)

Extracting: RFSFAT16 BOOTLOGO_FEX0000 (153738, 153744)

Extracting: RFSFAT16 VBOOTLOGO_FEX000 (4, 16)

Extracting: RFSFAT16 ENV_FEX000000000 (131072, 131072)

Extracting: RFSFAT16 VENV_FEX00000000 (4, 16)

Extracting: RFSFAT16 BOOT_FEX00000000 (3124088, 3124096)

Extracting: RFSFAT16 VBOOT_FEX0000000 (4, 16)

Extracting: RFSFAT16 ROOTFS_FEX000000 (100663296, 100663296)

Extracting: RFSFAT16 VROOTFS_FEX00000 (4, 16)結果竟然不小心發現了 uImage 和 DTB,哈~感謝老天的恩賜!

$ file * | grep -i Linux

RFSFAT16_BOOT_FEX00000000: u-boot legacy uImage, ARM OpenWrt Linux-3.10.65, Linux/ARM, OS Kernel Image (Not compressed), 3124024 bytes, Thu Jan 1 00:00:00 1970, Load Address: 0x80008000, Entry Point: 0x80008000, Header CRC: 0x1877E4E2, Data CRC: 0x8DD5320A

RFSFAT16_ROOTFS_FEX000000: Linux rev 1.0 ext2 filesystem data, UUID=57f8f4bc-abf4-655f-bf67-946fc0f9f25b (extents) (large files)

$ strings RFSFAT16_BOOT_FEX00000000 | grep Linux

ARM OpenWrt Linux-3.10.65

Uncompressing Linux...

Linux Documentah

LinuxOpenWRT 3.10.65 ? 真假,哈~

提取 zImage

$ dd if=RFSFAT16_BOOT_FEX00000000 of=zImage bs=1 skip=64

3124024+0 records in

3124024+0 records out

3124024 bytes (3.1 MB, 3.0 MiB) copied, 5.43237 s, 575 kB/s

$ file zImage

zImage: Linux kernel ARM boot executable zImage (little-endian)這個zImage似乎有點怪怪的,因為並沒有找到gzip的Header

接著看一下DTB

$ file "COMMON _DTB_CONFIG000000"

COMMON _DTB_CONFIG000000: Device Tree Blob version 17, size=45683, boot CPU=0, string block size=7371, DT structure block size=38240

$ cp "COMMON _DTB_CONFIG000000" dtb

$ dtc -I dtb -O dts -f dtb -o trimui.dts

$ vim trimui.dts

lcd0@0 {

allwinner,pins = "PD3\0PD4\0PD5\0PD6\0PD7\0PD8\0PD18\0PD20\0PD21";

allwinner,function = "lcd0";

allwinner,pname = "lcdd5\0lcdd6\0lcdd7\0lcdd10\0lcdd11\0lcdd12\0lcdclk\0lcdhsync\0lcdvsync";

sdc0@0 {

allwinner,pins = "PF0\0PF1\0PF2\0PF3\0PF4\0PF5";

lcd0@01c0c000 {

lcd_x = < 0x140 >;

lcd_y = < 0xf0 >;

lcd_width = < 0x32 >;

lcd_height = < 0x25 >;

lcd_pwm_used = < 0x01 >;

lcd_pwm_ch = < 0x01 >;

lcd_hbp = < 0x26 >;

lcd_ht = < 0x465 >;

lcd_hspw = < 0x12 >;

lcd_vbp = < 0x06 >;

lcd_vt = < 0x11e >;

lcd_vspw = < 0x04 >;

lcd_cpu_if = < 0x00 >;

keyboard {

compatible = "allwinner,keyboard_2000mv";

chosen {

bootargs = "earlyprintk=sunxi-uart,0x01c25000 loglevel=8 initcall_debug=1 console=ttyS0 init=/init";lcd_cpu_if = < 0x00 >,不是CPU屏?哈~有趣有趣,司徒越來越激情了~哈

离线

#98 2021-06-26 17:07:47 分享评论

- 光明之歌

- 会员

- 注册时间: 2021-06-26

- 已发帖子: 11

- 积分: 15

Re: 研究FC3000掌機的開源可行性

感谢司徒大佬能够分享你的工作成果。今天在群里看到你在折腾FC3000,特地跑过来看一下。去年入手FC3000之后感觉还真的挺不错的,目前市场上的机器清一色都是右边十字形排列的四颗按键,我个人就是想要这种仿FC手柄排列方式的按键来玩FC或者GB一类的老游戏。可惜最遗憾的是原系统没有调整屏幕比例的选项,让我玩着太难受。如今有能刷机的希望,真是太开心了。

离线

楼主 #99 2021-06-26 18:56:57 分享评论

#100 2021-06-26 19:58:08 分享评论

- masahiko

- 会员

- 注册时间: 2021-06-24

- 已发帖子: 13

- 积分: 22

Re: 研究FC3000掌機的開源可行性

...我手上這台 也許,可能,就是 IPS版本.....

難怪之前的升級檔怎樣都不能用

最近编辑记录 masahiko (2021-06-26 20:41:35)

离线

楼主 #101 2021-06-26 20:27:18 分享评论

#102 2021-06-26 20:53:05 分享评论

- masahiko

- 会员

- 注册时间: 2021-06-24

- 已发帖子: 13

- 积分: 22

Re: 研究FC3000掌機的開源可行性

我在蝦皮買的,不過剛剛查了一下,賣家已經沒賣了,以下是當時的訊息,你參考一下

离线

楼主 #103 2021-06-26 22:07:49 分享评论

Re: 研究FC3000掌機的開源可行性

台灣!真高興能夠在此遇到~

能夠幫我一個忙嗎?把這個fc300_ips_dump.img.7z解壓縮後,寫到MicroSD,然後插入你的機器,開機後會黑屏,然後開始dump spi flash,大約五分鐘後,屏的背光會開始閃爍,此時,代表完成dump,關機後,把MicroSD裡面的v1com.img傳給我,感謝~

https://github.com/steward-fu/fc3000/releases/download/v1.0/fc300_ips_dump.img.7z

离线

#104 2021-06-27 01:17:40 分享评论

- huanxing

- 会员

- 注册时间: 2021-06-27

- 已发帖子: 33

- 积分: 34.5

Re: 研究FC3000掌機的開源可行性

看到司徒大哥再次燃起激情,也有很多大神级响应,感到非常高兴!小白只有旁观同感喜悦!大哥加油!

离线

#105 2021-06-27 07:24:40 分享评论

楼主 #106 2021-06-27 08:55:34 分享评论

#107 2021-06-27 09:30:24 分享评论

- masahiko

- 会员

- 注册时间: 2021-06-24

- 已发帖子: 13

- 积分: 22

Re: 研究FC3000掌機的開源可行性

沒有,開機後背光沒亮,最後背光也沒有閃爍,完全黑屏,我是等到十分鐘後才關機取出dump rom

离线

楼主 #108 2021-06-27 10:08:12 分享评论

Re: 研究FC3000掌機的開源可行性

如果有時間,可以在幫忙測試一下這一版嗎?

https://github.com/steward-fu/fc3000/releases/download/v1.0/ips_fc3000_dump_0627_1.img.7z

步驟:

解壓縮後,寫到MicroSD

插入MicroSD到IPS FC3000

上電 (黑屏)

開始Dump Stock ROM (還是黑屏狀態)

五分鐘後,背光要開始閃爍

關機,把v1rom.img給我

离线

#109 2021-06-27 11:10:13 分享评论

- fanelwin

- 会员

- 注册时间: 2021-06-27

- 已发帖子: 21

- 积分: 15.5

Re: 研究FC3000掌機的開源可行性

司徒大佬,TRIMUI已经有几个外国人制作了前端,增加了好些模拟器,也能进行超频,不知道对你的开发有没有帮助

https://nitroxyz.com/archives/trimuigmenunx-210611_21006121.html

离线

#110 2021-06-27 11:37:53 分享评论

- masahiko

- 会员

- 注册时间: 2021-06-24

- 已发帖子: 13

- 积分: 22

Re: 研究FC3000掌機的開源可行性

ips_fc3000_dump_0627_1.img 燒入測試狀況和上次一樣,開機後背光沒亮,最後背光也沒有閃爍,完全黑屏,一樣等到十分鐘後才關機取出dump rom

dump rom 檔案如附件,請查收

离线

楼主 #111 2021-06-27 11:41:28 分享评论

Re: 研究FC3000掌機的開源可行性