- 首页

- » 搜索

- » ArtInChip 发表的帖子

#1 Re: 工业芯 匠芯创 » AiUIBuilder 下载 » 2026-04-01 13:42:54

#2 Re: 工业芯 匠芯创 » 匠芯创 D211,7寸mipi屏核心板 » 2026-01-31 09:45:50

tomas wrote:

跑分例程:34帧。这是旋转90度的。如果不旋转,可再加4,5帧。

该核心板用的是d211,叠封ddr2,如果是ddr3,可再加4,5帧。

/files/members/14212/77d217ccf2123c7f6d660c207a0eeb5.jpg

最新SDK有优化

#6 Re: 工业芯 匠芯创 » D13x有电机FOC硬件外设? » 2025-12-23 19:26:43

#8 Re: 工业芯 匠芯创 » 使用PQ 工具调试的时候特别容易断开连接怎么解决 » 2025-07-16 19:20:55

#9 Re: 工业芯 匠芯创 » 请教一下,D13x如何对接FreeRTOS? » 2025-07-16 19:20:21

#11 Re: 工业芯 匠芯创 » 官方SDK编译不通过 » 2025-06-09 09:31:35

#13 Re: 工业芯 匠芯创 » 关于QSPI驱动的问题 » 2025-04-21 22:34:11

#14 Re: 工业芯 匠芯创 » D13图片存储问题 » 2025-04-21 22:33:07

#15 Re: 工业芯 匠芯创 » 付费请人指导用D215点mipi屏幕 » 2025-03-21 10:08:07

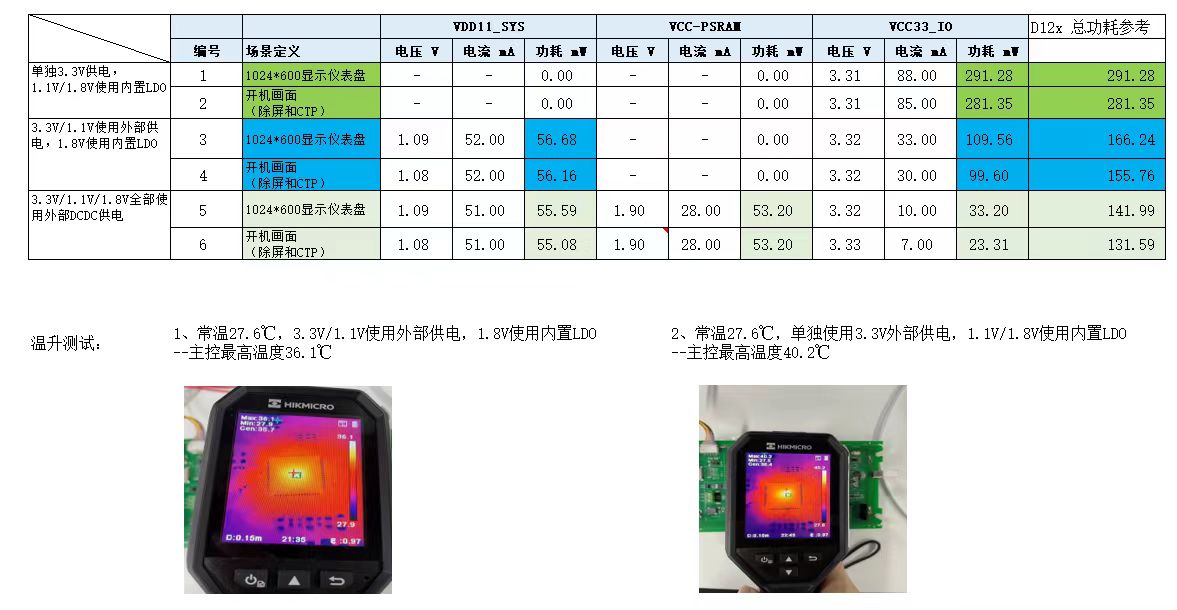

#16 Re: 工业芯 匠芯创 » D213的点屏能力有多强(实测) » 2025-03-21 10:07:18

#17 Re: 工业芯 匠芯创 » 分享d12x d13x ui-builder生成的程序文件 » 2025-03-12 14:46:40

#18 Re: 工业芯 匠芯创 » 关于GUI工具的选型建议 » 2025-03-12 14:44:46

#19 Re: 工业芯 匠芯创 » D211XXX USB副屏驱动 » 2025-01-11 23:49:27

#20 Re: 工业芯 匠芯创 » D211XXX USB副屏驱动 » 2025-01-07 09:49:54

#21 Re: 工业芯 匠芯创 » Luban-lite支持通过USB接4G模块吗? » 2025-01-02 09:25:40

#22 Re: 工业芯 匠芯创 » d122xx 类型产品有计划移植ardunio开发嘛 » 2024-12-30 23:09:48

#24 Re: 工业芯 匠芯创 » 一维码+二维码识别方案 » 2024-12-19 19:19:52

#25 Re: 工业芯 匠芯创 » 一维码+二维码识别方案 » 2024-12-17 17:33:50

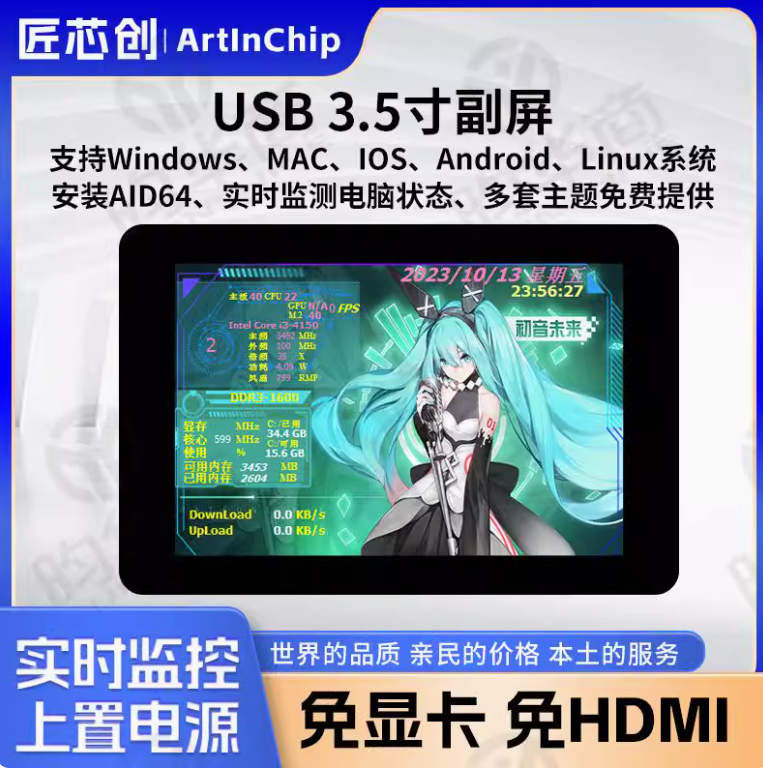

#26 Re: 工业芯 匠芯创 » 新芯片,D215BBV,USB 扩展屏,支持aida64,欢迎大家把玩 » 2024-12-05 09:35:37

hzy wrote:

这个有文档介绍吗?windows 11不识别,

/files/members/9208/artinchip_usb_device.png

搜了下没找到哪里可以下这个驱动

设备第一次插入时,提示U盘挂载,驱动在这个U盘里面,后续1月份会微软windows10、11免驱了,直接windows更新补丁就可以支持。

#28 Re: 工业芯 匠芯创 » D133 SDk里面怎么没有mmc的target配置呀 » 2024-11-22 14:41:20

#29 Re: 工业芯 匠芯创 » 匠芯创 D211,7寸mipi屏核心板 » 2024-11-20 14:34:12

#31 Re: 工业芯 匠芯创 » D133CBV开发板以太网插着重启不正常 » 2024-11-14 19:42:06

#32 工业芯 匠芯创 » 新芯片,D215BBV,USB 扩展屏,支持aida64,欢迎大家把玩 » 2024-11-13 15:32:45

- ArtInChip

- 回复: 14

目前支持windows10、11

后续支持macOS、树莓派、统信、鸿蒙、android、IOS

USB一线通显卡模式

#33 Re: 工业芯 匠芯创 » G73x 和M6800支持Qspi从节点么? » 2024-11-13 14:01:40

#34 Re: 工业芯 匠芯创 » 有哪些开源的支持RTOS的SDIO wifi模块? » 2024-11-11 13:27:04

#35 Re: 工业芯 匠芯创 » luban-lite的lwip组件编译失败 » 2024-10-17 12:53:12

#36 Re: 工业芯 匠芯创 » 请教下Linux下研发的工具和各种文档 » 2024-10-17 12:51:24

#37 Re: 工业芯 匠芯创 » Jlink能连D133么 » 2024-10-17 12:47:37

#38 Re: 工业芯 匠芯创 » 看到gitee有D215了 » 2024-09-18 12:32:58

#39 Re: 工业芯 匠芯创 » D211的CAN通讯如何避免死机 » 2024-09-18 09:03:07

#40 Re: 工业芯 匠芯创 » 请教下Linux下研发的工具和各种文档 » 2024-09-18 09:00:14

你好,工具提供了EXE的不对吗?那要提供什么格式?

烧录工具是有的,建议先看文档和手册,里面有比较清晰的步骤。

https://aicdoc.artinchip.com/topics/product/d21x-quick-start-d21x.html

#41 Re: 工业芯 匠芯创 » Linux系统驱动步进电机方案探索 » 2024-09-14 18:09:11

#42 Re: 工业芯 匠芯创 » D133CBS接mipi屏 » 2024-09-09 17:53:09

#43 Re: 工业芯 匠芯创 » 请问D133CBS有公开的EDA原理图么 » 2024-09-06 18:14:51

#44 Re: 工业芯 匠芯创 » D133支持的摄像头芯片 » 2024-09-06 18:14:28

#45 Re: 工业芯 匠芯创 » 请问Linux下D213ECV跑LVGL帧率这么低正常吗? » 2024-08-16 00:23:27

#46 Re: 工业芯 匠芯创 » 匠芯创 D211,7寸mipi屏核心板 » 2024-08-14 11:07:30

#49 Re: 工业芯 匠芯创 » 请问Linux下D213ECV跑LVGL帧率这么低正常吗? » 2024-07-30 13:07:39

#51 Re: 工业芯 匠芯创 » 基于D211BBX的第一张工程板 » 2024-07-26 23:43:11

#54 Re: 工业芯 匠芯创 » 关于CPU的说明-更名说明 » 2024-07-13 21:30:10

#55 工业芯 匠芯创 » 关于CPU的说明-更名说明 » 2024-07-13 17:54:17

#56 Re: 工业芯 匠芯创 » 开始进入平头哥的双千兆网时代 » 2024-07-12 20:24:26

#57 Re: 工业芯 匠芯创 » 关于匠心创技术支持的问题 » 2024-07-03 21:54:35

#58 Re: 工业芯 匠芯创 » 关于匠心创技术支持的问题 » 2024-07-03 21:54:22

#60 Re: 工业芯 匠芯创 » 匠芯创 D211,7寸mipi屏核心板 » 2024-06-28 20:19:27

#61 Re: 工业芯 匠芯创 » RISC-V工业级高可靠性人机交互MPU D21x系列Datasheet » 2024-06-28 20:06:14

xuqm wrote:

D21x系列有openwrt的案例吗

#62 Re: 工业芯 匠芯创 » 匠芯创 D211,7寸mipi屏核心板 » 2024-06-20 17:27:06

#64 Re: 工业芯 匠芯创 » 评估板和样片购买方式说明,匠芯创ArtInChip » 2024-06-15 23:08:45

#65 Re: 工业芯 匠芯创 » f1c200s 和 D213 图形性能对比 » 2024-06-15 23:08:06

#66 Re: 工业芯 匠芯创 » 基于D211BBX的第一张工程板 » 2024-06-15 16:21:28

#67 Re: 工业芯 匠芯创 » luban-lite不支持D133BAS吗? » 2024-06-11 18:53:51

#69 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2024-06-08 00:20:53

lyf25146 wrote:

D12X或D133 能播放视频吗?MP4格式之类的?

可以的,用官方的视频转换工具转换一下就能播放。

工具下载地址:

https://gitee.com/artinchip/tools/blob/master/AiVideo-1.0.0_setup.zip

#72 Re: 工业芯 匠芯创 » D133 Eclipse工程在Linux系统下编译的解决办法 » 2024-06-05 11:37:42

#73 Re: 工业芯 匠芯创 » D211DCV跑Linux系统,最低需要多大的存储器 » 2024-05-26 21:08:03

#75 Re: 工业芯 匠芯创 » D133 Eclipse工程在Linux系统下编译的解决办法 » 2024-05-17 08:28:31

#76 工业芯 匠芯创 » 一牛网联合匠芯创举办“双禹盛泰杯”-基于RISC-V架构的泛工业应用创新大赛(最高奖金20000元) » 2024-05-13 18:31:26

- ArtInChip

- 回复: 3

https://www.16rd.com/writings-864438-1.html

报名规则

参赛选手:面向企业、创客团队、工程师、高校等人士,不限个人或团体形式参赛。

报名方式:

在线提交作品主题、基本设计思路、主要解决的问题以及创新点即可报名参赛,具体方案不限。

报名信息审核通过后即安排邮寄开发板套件或芯片,每个参赛组可以免费获取10pcs D13x芯片或者2pcs D12x核心板,二选一。

报名网址:https://bbs.16rd.com/thread-615174-1-1.html

报名微信:19168984579

#77 Re: 工业芯 匠芯创 » 工业级芯片之三问三答:可靠性和稳定性是匠芯创产品在软件端的核心指标 » 2024-04-24 17:07:15

regbbs wrote:

对网站再提点意见, https://www.artinchip.com/knowledge/oxy_ex-1/topics/d12xUserManual-d13x.html

这个页面为例,显示器假设是1080P的,在浏览时上面的约1/3是不可动的,导致主要的内容看起来很很费力。

收到,我们改进下

#78 Re: 工业芯 匠芯创 » 关于D133 PWMCS模块的脉冲输出功能,找不到PUL_OUT_NUM和EPWM_PUL_OUT_EN相关的寄存器定义和信息 » 2024-04-19 00:20:24

#79 Re: 工业芯 匠芯创 » 入坑D133 » 2024-04-19 00:17:32

#80 Re: 工业芯 匠芯创 » luban-lite新发布的# V1.0.4 #变慢了 » 2024-04-18 00:00:13

#81 Re: 工业芯 匠芯创 » f1c200s 和 D213 图形性能对比 » 2024-04-16 09:09:33

#82 Re: 工业芯 匠芯创 » 可否在vscode环境下只打开构建后的project目录 » 2024-04-14 00:39:47

#83 Re: 工业芯 匠芯创 » 关于D133 PWMCS模块的脉冲输出功能,找不到PUL_OUT_NUM和EPWM_PUL_OUT_EN相关的寄存器定义和信息 » 2024-04-13 08:53:18

m68000 wrote:

整整过去了一个月,只有一个收到,这效率,小客户真心伤不起,用不起啊

不好意思,着急的话可以在QQ群里面沟通,论坛上面回复慢了一些。

现在官网也更新了文档中心,欢迎随时查看

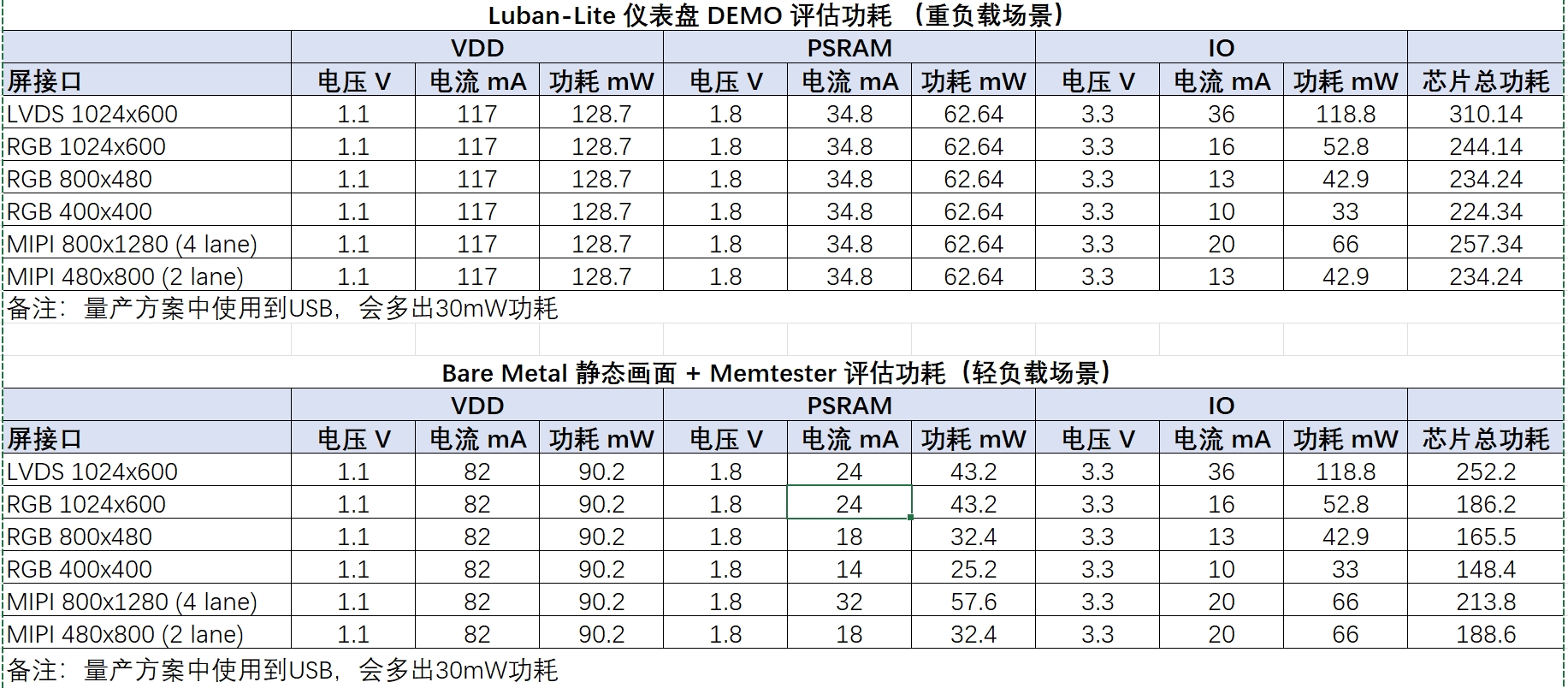

#84 Re: 工业芯 匠芯创 » 官网下的D12x规格书,连个功耗\工作电流说明都没 » 2024-04-10 09:12:45

sw773 wrote:

请问如果没操作时屏(以480*800计)显示固定内容,降低系统时钟可以减少多少功耗呢?

这个没测过,可以试试

#85 Re: 工业芯 匠芯创 » 官网下的D12x规格书,连个功耗\工作电流说明都没 » 2024-04-08 10:30:25

#87 Re: 工业芯 匠芯创 » D133 QFN88 官方参考图纸 » 2024-03-21 17:39:59

#88 Re: 工业芯 匠芯创 » 就很抽象,所有询问匠心扣扣群的帖子都没了 » 2024-03-19 21:49:31

#89 Re: 工业芯 匠芯创 » 关于D133 PWMCS模块的脉冲输出功能,找不到PUL_OUT_NUM和EPWM_PUL_OUT_EN相关的寄存器定义和信息 » 2024-03-12 09:15:03

#90 Re: 工业芯 匠芯创 » D213启动字符串能否去掉? » 2024-03-02 09:37:48

#91 Re: 工业芯 匠芯创 » D213启动字符串能否去掉? » 2024-03-02 09:37:02

#92 Re: 工业芯 匠芯创 » D13x有电机FOC硬件外设? » 2024-03-01 14:32:46

#93 Re: 工业芯 匠芯创 » D13x有电机FOC硬件外设? » 2024-03-01 09:44:46

#94 Re: 工业芯 匠芯创 » D213启动字符串能否去掉? » 2024-03-01 09:41:44

#95 Re: 工业芯 匠芯创 » D13x有电机FOC硬件外设? » 2024-02-29 09:21:26

海石生风 wrote:

这是贵司的图片源,看不见?

/files/members/1798/Screenshot_20240228_222912.png

这个是有的,D13x显控一体。定时器多达26个。

如果是伺服驱动器应用,建议选择M6800系列,SDK是分开的。

#96 Re: 工业芯 匠芯创 » D13x有电机FOC硬件外设? » 2024-02-28 21:17:02

海石生风 wrote:

看见贵司官网已更新,发现有下面这张图片。为何在目前的文档上没有体现?或者是未发布的新型号?

http://artinchip.com/upload/images/ueditor/20240125/17061491008787237.jpg

图片看不到啊

#97 Re: 工业芯 匠芯创 » 关于GUI工具的选型建议 » 2024-02-19 16:35:43

#98 Re: 工业芯 匠芯创 » 请问有D13X的usermanual吗? » 2024-02-18 14:57:31

#99 Re: 工业芯 匠芯创 » 评估板和样片购买方式说明,匠芯创ArtInChip » 2024-02-01 12:50:17

#100 Re: 工业芯 匠芯创 » 自己画的D213ECX-EVM » 2024-01-29 16:17:03

#101 Re: 工业芯 匠芯创 » D133EBS烧录失败问题 » 2024-01-25 09:51:16

#102 Re: 工业芯 匠芯创 » 匠芯创ArtInChip选型表更新,更多新型号加入,具体请咨询淘宝客服 » 2024-01-19 13:58:03

下周开放

#103 Re: 工业芯 匠芯创 » 匠芯创ArtInChip选型表更新,更多新型号加入,具体请咨询淘宝客服 » 2024-01-18 16:31:42

musich wrote:

ArtInChip wrote:

musich wrote:

是否支持 JPEG 解码呢? 这个选型表不支持, 但有的资料又介绍支持,

选型表写明了支持jpeg解码哦

列表原文:

Encode JPEG 8192x8192

Decode PNG 4096x4096以为只支持 JPEG编码, PNG解码的.

更新了一下,表述更清晰。

#106 Re: 工业芯 匠芯创 » 评估板和样片购买方式说明,匠芯创ArtInChip » 2024-01-15 15:08:23

pzh wrote:

ArtInChip wrote:

正在做4.3寸的开发板,以最低的价格给各位。

/files/members/13307/微信图片_20231114214515.png这个活动已经结束啦?:o

有时候没货就自动下架了。

#107 Re: 工业芯 匠芯创 » 评估板和样片购买方式说明,匠芯创ArtInChip » 2024-01-15 02:16:48

#108 Re: 工业芯 匠芯创 » 请问D133能否支持更大的mipi屏 » 2024-01-10 22:22:48

#109 Re: 工业芯 匠芯创 » D133EBS烧录失败问题 » 2024-01-08 14:49:20

#110 Re: 工业芯 匠芯创 » D133EBS烧录失败问题 » 2024-01-08 10:06:18

#111 Re: 工业芯 匠芯创 » 匠芯创ArtInChip Datasheet更新2023-12-14 » 2024-01-04 19:19:25

#112 Re: 工业芯 匠芯创 » f1c200s 和 D213 图形性能对比 » 2023-12-29 14:24:24

#113 Re: 工业芯 匠芯创 » 匠芯创ArtInChip QSPI双屏异显的应用 » 2023-12-29 14:23:01

#114 Re: 工业芯 匠芯创 » RISC-V工业级高性能通用计算MCU G73x系列Datasheet,内置大容量1MB SRAM和2MB FLASH » 2023-12-29 14:15:09

#115 Re: 工业芯 匠芯创 » D13x定时器可不可以做通用定时器 » 2023-12-29 14:13:35

#116 Re: 工业芯 匠芯创 » D13x定时器可不可以做通用定时器 » 2023-12-29 14:12:58

#117 Re: 工业芯 匠芯创 » D13x定时器可不可以做通用定时器 » 2023-12-29 14:09:53

#119 Re: 工业芯 匠芯创 » D133 烧录经常失败,怎么解决 » 2023-12-29 13:42:48

#120 Re: 工业芯 匠芯创 » D133EBS烧录失败问题 » 2023-12-23 21:30:38

#121 Re: 工业芯 匠芯创 » RISC-V工业级高性能通用计算MCU G73x系列Datasheet,内置大容量1MB SRAM和2MB FLASH » 2023-12-23 09:43:07

#122 Re: 工业芯 匠芯创 » 烧录失败问题 » 2023-12-21 21:21:41

#123 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2023-12-21 21:19:57

#124 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2023-12-21 21:18:55

#125 Re: 工业芯 匠芯创 » 入坑D133 » 2023-12-21 21:17:11

#126 Re: 工业芯 匠芯创 » 匠芯创ArtInChip QSPI双屏异显的应用 » 2023-12-21 21:15:53

#127 Re: 工业芯 匠芯创 » d133 RGB888 图形显示测试 » 2023-12-21 21:08:29

#128 Re: 工业芯 匠芯创 » 入坑D133 » 2023-12-21 14:40:19

#129 工业芯 匠芯创 » 匠芯创ArtInChip QSPI双屏异显的应用 » 2023-12-21 14:11:03

- ArtInChip

- 回复: 12

D21可以直接出1个QSPI加1个LCD QSPI

D13可以直接出2个QSPI加1个LCD QSPI

SPI (Serial Peripheral Interface) 是一种高速、全双工的同步通信总线。由于其实现比较简单,没有专利限制等,因此在各种器件中得到广泛的应用。 SPI 总线是一种行业事实标准,并没有统一的标准化组织,不同厂商在实际应用中演化出多种工作模式。

ArtInChip SPI 支持:

全双工、半双工模式

DMA 读写模式

CPU 读写模式

最高工作频率 100MHz

支持四线制模式:标准4线 SPI、DUAL SPI、QUAD SPI

支持三线制模式

数据位传输的模式可配置,CPOL 和 CPHA

#132 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2023-12-18 13:35:41

#133 Re: 工业芯 匠芯创 » 工业级芯片之三问三答:可靠性和稳定性是匠芯创产品在软件端的核心指标 » 2023-12-18 11:01:58

#134 Re: 工业芯 匠芯创 » 工业级芯片之三问三答:可靠性和稳定性是匠芯创产品在软件端的核心指标 » 2023-12-17 20:47:30

#135 Re: 工业芯 匠芯创 » 工业级芯片之三问三答:可靠性和稳定性是匠芯创产品在软件端的核心指标 » 2023-12-17 09:56:52

#136 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2023-12-17 09:54:41

#137 Re: 工业芯 匠芯创 » D213 刷官方LVGL » 2023-12-16 13:02:41

#138 工业芯 匠芯创 » 工业级芯片之三问三答:可靠性和稳定性是匠芯创产品在软件端的核心指标 » 2023-12-16 12:56:34

- ArtInChip

- 回复: 11

导读

芯片是电子产品的核心,其质量和可靠性直接影响着产品的性能和稳定性。为了满足不同应用领域的需求,芯片被分为不同的等级。其中,工业级芯片适用于工业自动化、控制系统和仪器仪表等领域,对芯片的可靠性和稳定性要求较高。这些芯片通常具有更宽的工作温度范围(-40°C至85°C),能够在恶劣的工作环境下正常运行,如高温、低温、湿度和振动等。本篇,将从软件端入手,解答ArtInChip芯片如何全方位实现“工业级”要求。

用敏捷开发撬动工业级应用地图

工业级产品对其软件性能——如可靠性、稳定性、一致性、可维护性等具有更严格的要求,为了满足这些特性需求,匠芯创科技团队将敏捷软件的一些理念和方法融入到日常开发中,为工业级应用埋下深厚的技术种子。

敏捷开发不是单独一个工具、当然也不限于某一个环节,而是一组贯穿始末的方法论。如果非要一言以蔽之的话,它有两个核心原则——快速迭代和持续交付。

1。快速迭代

相对于传统的瀑布式开发模式来说,快速迭代给团队及产品都带来极大的灵活性,以“用户故事”(相当于常说的“用户需求”)为粒度形成pipeline的开发模式、以“测试驱动开发”为每一次变更提供品质保障。

2。持续交付

工业类产品的特点是研发周期相对较长,另一大特点是需求的碎片化,这些特点体现到软件的要求就是:高品质的软件版本、细分的应用场景,简单的说就是既要稳定、又要灵活。这就要求我们能够随时可以给客户提供一份可用可靠的软件,只有基于上述快速迭代的基础建设,才能在客户面前做到持续交付的能力。

用系统思维赋能高质量软件品质

ArtInChip匠芯创科技经过三年多的持续努力,打造了一整套的CI/CD(持续集成/持续交付)系统。该系统覆盖了从软件编码到测试验收、再到打包交付的各个环节,全流程实现了自动化,将设计的规范性和工程师的创造性有机结合起来,有效提升了团队开发效率和软件品质。

匠芯创软件团队的敏捷软件开发模型

如图所示,蓝色部分都属于自动化执行的部分,只有“代码设计”、“代码评审”需要人工参与,而其中的“代码评审”环节至关重要。这个开发模型也符合我们内部一直在强调的几个理念:

1)质量的源头是设计,而编码也是设计

大家都承认“高质量是设计出来的”,但有意思的是很多团队在“设计”阶段投入却较少,尤其是将“代码评审”流于形式,结果是将大量精力投入在后期的维护和变更中,最可怕的是陷入救火的忙碌中且将此视为常态。

所以,匠芯创科技坚持执行严格的代码审查,将问题尽量暴露在设计阶段,包括人工同行审查、以及各种代码静态检查工具。就在今年还部署了MISRA(汽车工业软件可靠性协会) C语言规范检查工具,以确保代码遵循行业最佳实践。

2)把复杂留给自己,把简单留给客户

实际上,把匠芯创科技的研发理念用更简单易懂的话说,即是——回到用户场景,用户好用才算好用。

用户的使用环境多种多样,要在尽量少假设的前提下,让用户顺利用起来我们的SDK,这个也叫做依赖性管理。团队在CI/CD系统中增加了自动化部署验证,能够在一个空白的运行环境中顺利建立对于SDK的开发依赖,并以此验证我们的软件可用性。

“回到用户场景”也体现在需求的验收环节,匠芯创科技软件团队尽量重现客户的使用环境、使用习惯、甚至模拟一些无序操作,这些给团队测试验收带来很多工作量,但回过头看都是值得的。

3)能让工具完成的,都交给工具

作为IC原厂,匠芯创科技提供的SDK必然是要跨芯片的平台化SDK,针对一个SoC平台会衍生出多种板卡配置。跨平台意味着代码改动频繁,也意味着必须全量覆盖,因此导致测试工作量倍增,这对团队来说是一个非常严峻的挑战。

经过讨论、优化,团队将能让工具完成的都交给工具——用自动化测试完成全量覆盖的嵌入式设备测试。这个答案理解起来并不难,难的是如何攻克技术难关,切实实现全测试环节自动化。

目前业内在嵌入式自动化测试方面并没有通用的做法,匠芯创科技根据自己产品特点和应用需求,自主研发了一套全自动化的测试软硬件系统,可以做到分布式设备管理、项目化测试计划管理、单元/集成/系统/稳定性测试全覆盖,这套系统为代码重构和版本发布保驾护航。

我们“交给工具”的远不止自动化测试,还有OneStep增强命令行、一键部署OneClick、一键发布、GPIO冲突检测、在线调屏工具等,这些工具已经在为团队和为客户带来了切实的便利和效率的提高。

敏捷求索之路行之漫长,匠芯创科技软件端将赓续“让使用更简单”的企业使命,将客户价值作为软件开发指南针,充分发挥工业级芯片高稳定、高可靠性的技术优势与市场价值,推动国产工业级MPU&MCU行稳致远。

#139 Re: 工业芯 匠芯创 » D13x ADC精度 » 2023-12-15 11:08:51

#140 Re: 工业芯 匠芯创 » 匠芯创ArtInChip Datasheet更新2023-12-14 » 2023-12-15 11:01:15

#141 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2023-12-14 12:33:33

#143 Re: 工业芯 匠芯创 » f1c200s 和 D213 图形性能对比 » 2023-12-13 18:18:56

#144 Re: 工业芯 匠芯创 » D133/D213有IAR可用的开发包吗? » 2023-12-11 18:51:07

#145 Re: 工业芯 匠芯创 » d13x系列封装 » 2023-12-11 18:49:39

#146 Re: 工业芯 匠芯创 » D13x ADC精度 » 2023-12-11 13:31:07

#147 Re: 工业芯 匠芯创 » D13x ADC精度 » 2023-12-11 13:30:04

#148 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2023-12-10 14:00:15

#149 Re: 工业芯 匠芯创 » D133EBS 核心板设计好了,待验证 » 2023-12-10 13:59:15

#153 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2023-12-09 11:10:12

#154 Re: 工业芯 匠芯创 » D213 刷官方LVGL » 2023-12-09 11:06:12

#156 Re: 工业芯 匠芯创 » D213 刷官方LVGL » 2023-12-08 09:07:01

#157 Re: 工业芯 匠芯创 » 第一块D133CBS 烧录并运行成功 » 2023-12-07 20:00:08

#159 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2023-12-07 19:58:21

#160 Re: 工业芯 匠芯创 » D13x ADC精度 » 2023-12-05 19:12:07

#162 Re: 工业芯 匠芯创 » USB 控制器中关于5对 endpoint的说明 » 2023-12-05 13:14:01

#164 Re: 工业芯 匠芯创 » 买开发板送“调试器”,限量20个。先到先得!!! » 2023-12-02 20:43:02

#166 Re: 工业芯 匠芯创 » MCU内存小怎么办?ArtInChip RTOS平台XIP技术揭秘 » 2023-12-01 13:16:15

#167 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2023-11-30 20:39:08

#168 Re: 工业芯 匠芯创 » 匠芯创RISC-V产品选型表更新V23-供选型参考 » 2023-11-30 20:32:38

#169 Re: 工业芯 匠芯创 » 匠芯创RISC-V产品选型表更新V23-供选型参考 » 2023-11-28 15:34:09

#170 Re: 工业芯 匠芯创 » 匠芯创RISC-V产品选型表更新V23-供选型参考 » 2023-11-28 15:33:16

#172 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2023-11-28 09:25:16

#174 Re: 工业芯 匠芯创 » 萌新来啦,匠芯创正式入驻WhyCan,第一波小福利正在准备中。。。。 » 2023-11-28 09:08:03

#175 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2023-11-28 09:04:30

#176 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2023-11-24 16:04:04

#177 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2023-11-22 11:17:22

#178 Re: 工业芯 匠芯创 » 评估板和样片购买方式说明,匠芯创ArtInChip » 2023-11-22 11:16:45

xfdr0805 wrote:

ArtInChip wrote:

正在做4.3寸的开发板,以最低的价格给各位。

/files/members/13307/微信图片_20231114214515.png原理图 pcb能放上来吗

具体可以联系淘宝店小二

#179 Re: 工业芯 匠芯创 » 萌新来啦,匠芯创正式入驻WhyCan,第一波小福利正在准备中。。。。 » 2023-11-21 18:19:35

#180 Re: 工业芯 匠芯创 » 萌新来啦,匠芯创正式入驻WhyCan,第一波小福利正在准备中。。。。 » 2023-11-21 11:36:26

#181 Re: 工业芯 匠芯创 » MCU内存小怎么办?ArtInChip RTOS平台XIP技术揭秘 » 2023-11-20 12:55:57

#182 Re: 工业芯 匠芯创 » 评估板和样片购买方式说明,匠芯创ArtInChip » 2023-11-19 23:13:45

#183 Re: 工业芯 匠芯创 » RISC-V工业级高性能通用计算MCU G73x系列Datasheet,内置大容量1MB SRAM和2MB FLASH » 2023-11-19 15:07:13

#184 Re: 工业芯 匠芯创 » RISC-V工业级高性能通用计算MCU G73x系列Datasheet,内置大容量1MB SRAM和2MB FLASH » 2023-11-19 14:59:56

#185 Re: 工业芯 匠芯创 » MCU内存小怎么办?ArtInChip RTOS平台XIP技术揭秘 » 2023-11-19 14:55:22

#186 Re: 工业芯 匠芯创 » MCU内存小怎么办?ArtInChip RTOS平台XIP技术揭秘 » 2023-11-19 00:01:35

#188 工业芯 匠芯创 » MCU内存小怎么办?ArtInChip RTOS平台XIP技术揭秘 » 2023-11-17 20:53:23

- ArtInChip

- 回复: 12

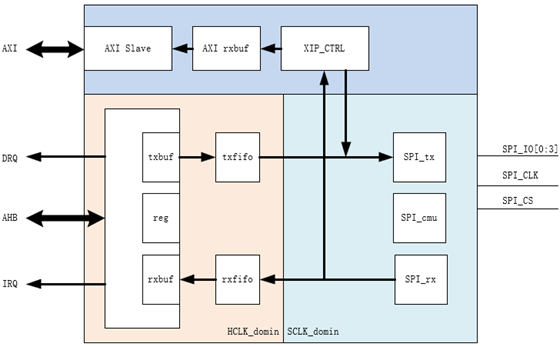

一、什么是XIP

XIP(eXecute In Place)技术是一种在嵌入式系统中执行代码的方法,它允许代码直接在存储器中执行,而无需将代码复制到RAM中。它通常用于嵌入式系统中,如微控制器、嵌入式Linux系统等。

二、实现XIP有哪些优势

节省内存空间:由于代码直接在存储器中执行,不需要将代码复制到RAM中,因此可以节省宝贵的内存空间。这对于资源受限的嵌入式系统尤为重要。

提高性能:XIP技术可以减少代码加载和执行的时间,从而提高系统的性能。因为代码直接在存储器中执行,无需复制到RAM中,减少了数据传输的时间和功耗。

简化系统设计:XIP技术可以简化系统设计,减少对RAM的需求。这意味着可以使用更小容量的RAM芯片,降低系统成本。

提高系统可靠性:由于XIP技术避免了代码复制的过程,减少了因为复制错误导致的系统崩溃的风险。此外,存储器中的代码通常是只读的,不容易被病毒或恶意软件修改,提高了系统的安全性和可靠性。

三、匠芯创ArtInChip芯片平台如何实现XIP(详细内容请参考开发手册)

拿ArtInChip D13x系列举例,先下载SDK,配置好开发环境。

一键配置编译,Luban-Lite 关于 Bootloader 和 RTOS 两部分固件的编译配置

XIP相关配置

Bootloader 阶段需要使能 XIP 启动指令,并配置 NOR Flash 的 XIP 相关命令。

RTOS 是在 NOR Flash 上运行的代码,其中包括

<span class="pre">.text</span>,<span class="pre">.data</span>,<span class="pre">.bss</span>,<span class="pre">.rodata</span>Section 需要在链接脚本中指定配置, 由于 XIP 模式下的 NOR Flash 是只读操作,因此<span class="pre">.data</span>Section 需要在编译制作 os.img 时,需要分段打包, 相关的编译打包脚本也需要做调整, 在 Luban-Lite 中,用户可通过 Menuconfig 来配置相关信息。

非XIP与XIP对比数据

| 测试项目 | 非XIP 模式 | XIP 模式 |

| --------------- | -------------- | ------------- |

| 启动速度(sec) | 0.433 | 0.481 |

| 显示帧率(FPS) | 29-46 (37) | 27-39(29)|

| CPU占用率(%) | 15-37 | 18-40 |

常见问题

问题:Winbond 颗粒,配置 XIP 模式后,马上通过 XIP 访问 Flash ,出现 32Bytes 数据是 0xcc

解决方法:需要加入延时,大概100ms.(Workaround,但不影响其他启动模式,问题只在 XIP 启动模式下存在)

功能特性:

支持 XIP 执行程序

支持 XIP 数据访问

原理框图

总结:ArtInChip RTOS平台XIP技术通过在存储器中执行代码,节省内存空间,提高性能,简化系统设计,提高系统可靠性等方面具有优势,特别适用于资源受限的嵌入式系统平台,譬如D13x系列和D12x系列微控制器MCU。

#189 Re: 工业芯 匠芯创 » RISC-V工业级高性能通用计算MCU G73x系列Datasheet,内置大容量1MB SRAM和2MB FLASH » 2023-11-17 19:33:19

#190 Re: 工业芯 匠芯创 » 萌新来啦,匠芯创正式入驻WhyCan,第一波小福利正在准备中。。。。 » 2023-11-17 18:47:23

jinlong631 wrote:

D211/D213这芯片强啊 从哪里能买到?

#191 Re: 工业芯 匠芯创 » RISC-V工业级高性能通用计算MCU G73x系列Datasheet,内置大容量1MB SRAM和2MB FLASH » 2023-11-17 16:41:23

#192 Re: 工业芯 匠芯创 » 关于GUI工具的选型建议 » 2023-11-17 13:44:06

#195 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2023-11-16 17:24:57

#196 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2023-11-16 16:53:39

#197 Re: 工业芯 匠芯创 » RISC-V工业级高性能通用计算MCU G73x系列Datasheet,内置大容量1MB SRAM和2MB FLASH » 2023-11-16 13:23:13

#200 Re: 工业芯 匠芯创 » RISC-V高性能显示控制跨界MCU D13x系列Datasheet » 2023-11-16 13:15:09

- 首页

- » 搜索

- » ArtInChip 发表的帖子

东莞哇酷科技有限公司开发