- 首页

- » 搜索

- » Jin劲 发表的帖子

#1 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » WhyCan赞助项目-SuperHUB工程师专用USB-HUB » 2020-06-01 08:03:28

#2 DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » WhyCan赞助项目-SuperHUB工程师专用USB-HUB » 2020-05-31 16:19:44

- Jin劲

- 回复: 32

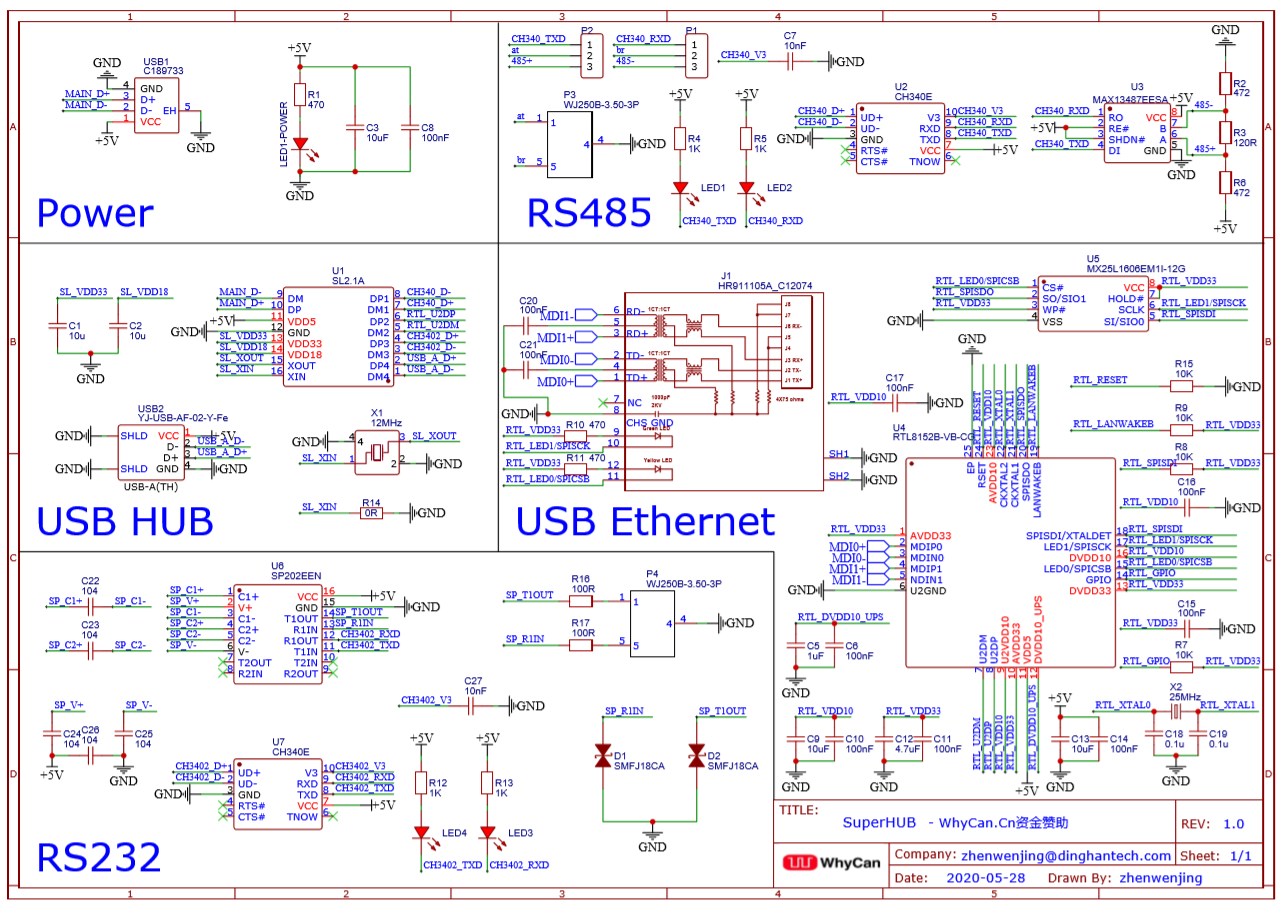

1.项目介绍:

本项目是基于本人工作环境,经常用到485、232、TTL、以太网口等工具。为了到现场调试方便(在轨道行业),节省电脑数量可怜的USB口,推出的一个项目。该项目利用USB-HUB,集成485、232、TTL、以太网等工具,并实现了USB用一还一的功能。

2.项目赞助:

本项目由WhyCan网进行资金赞助,也是WhyCan第一个该形式进行的项目。本人觉得该形式既可以节省自身的资金,又可以集思广益完善项目,大伙以后又相关需求也可以直接参考该项目,还能为论坛带来人气,可谓多赢!!!

项目完全开源,作者属于本人,进行商业用途请联系低调哥QQ: 516333132, 微信: whycan_cn 。

3.项目里程碑:

第一阶段:

需要做的:在本帖公布原理图源文件,劳烦各位少侠出谋划策,一起完善原理图。

达到的目标:对第一阶段的硬件进行调试,达到可用、无错、带外壳。

得出的成果:奉献前数名将获得第一阶段版本的实物。

第二阶段:

需要做的:讨论模块化、积木化,收集常用模块需求。

达到的目标:实现设备的模块化,需要用几个485,就插几个485,需要仿真器,就插仿真器。

得出的成果:对第二阶段的设计,有较为完善的设计思路与资料。

第三阶段:

需要做的:对第二阶段的硬件进行调试。

达到的目标:达到可用、无错、带外壳。

得出的成果:对第二、三阶段奉献前数名将获得第三阶段版本的实物。

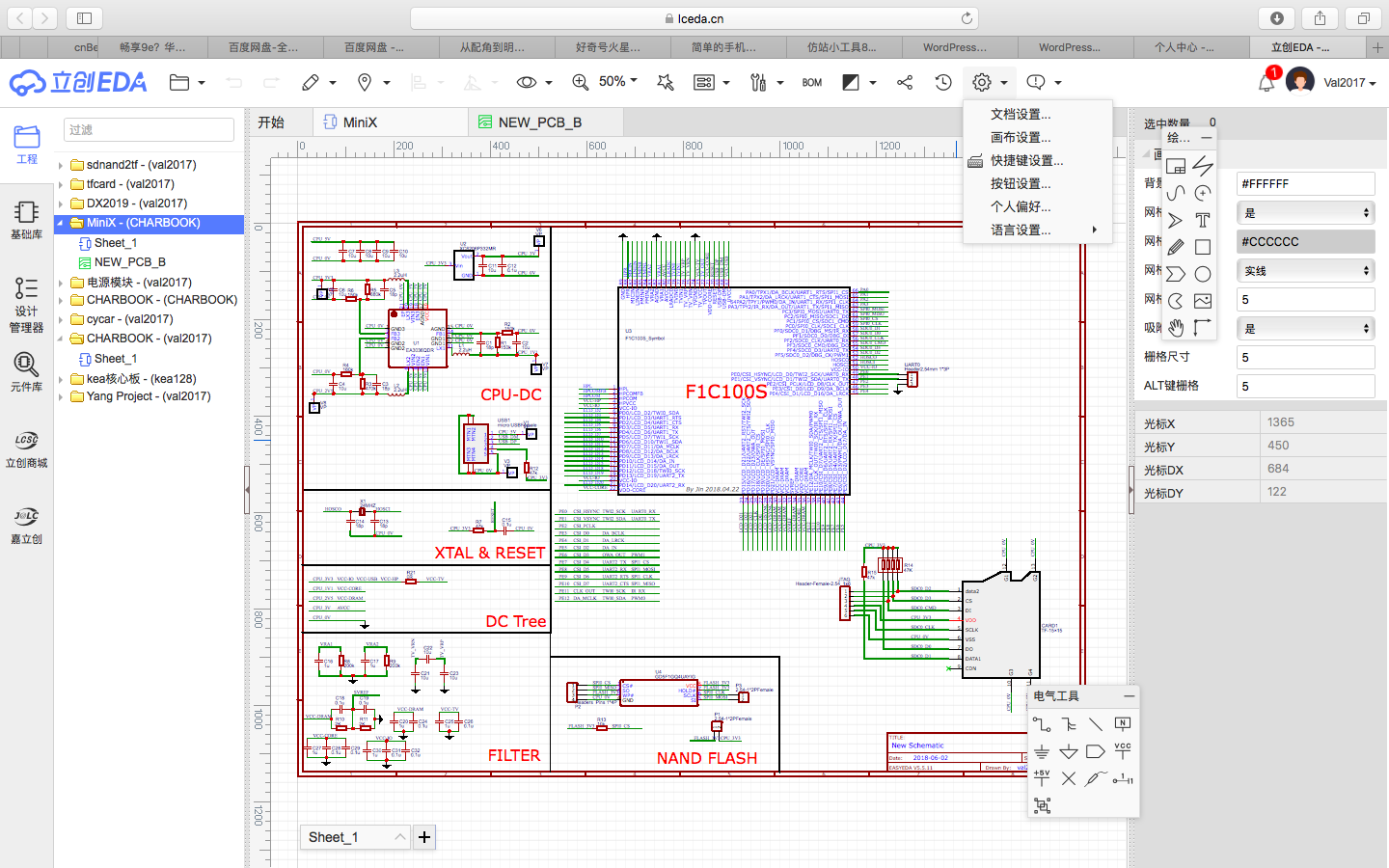

4.第一阶段20200528原理图:

SuperHUB_2020-05-28-08.zip

#3 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 请问大家这个很久没用的红外温度测量仪表面粘粘的, 还有救吗, 用什么可以洗掉? » 2019-10-31 09:34:28

#8 Re: 全志 SOC » 投屏仪,有搞过的么? » 2019-10-16 19:58:34

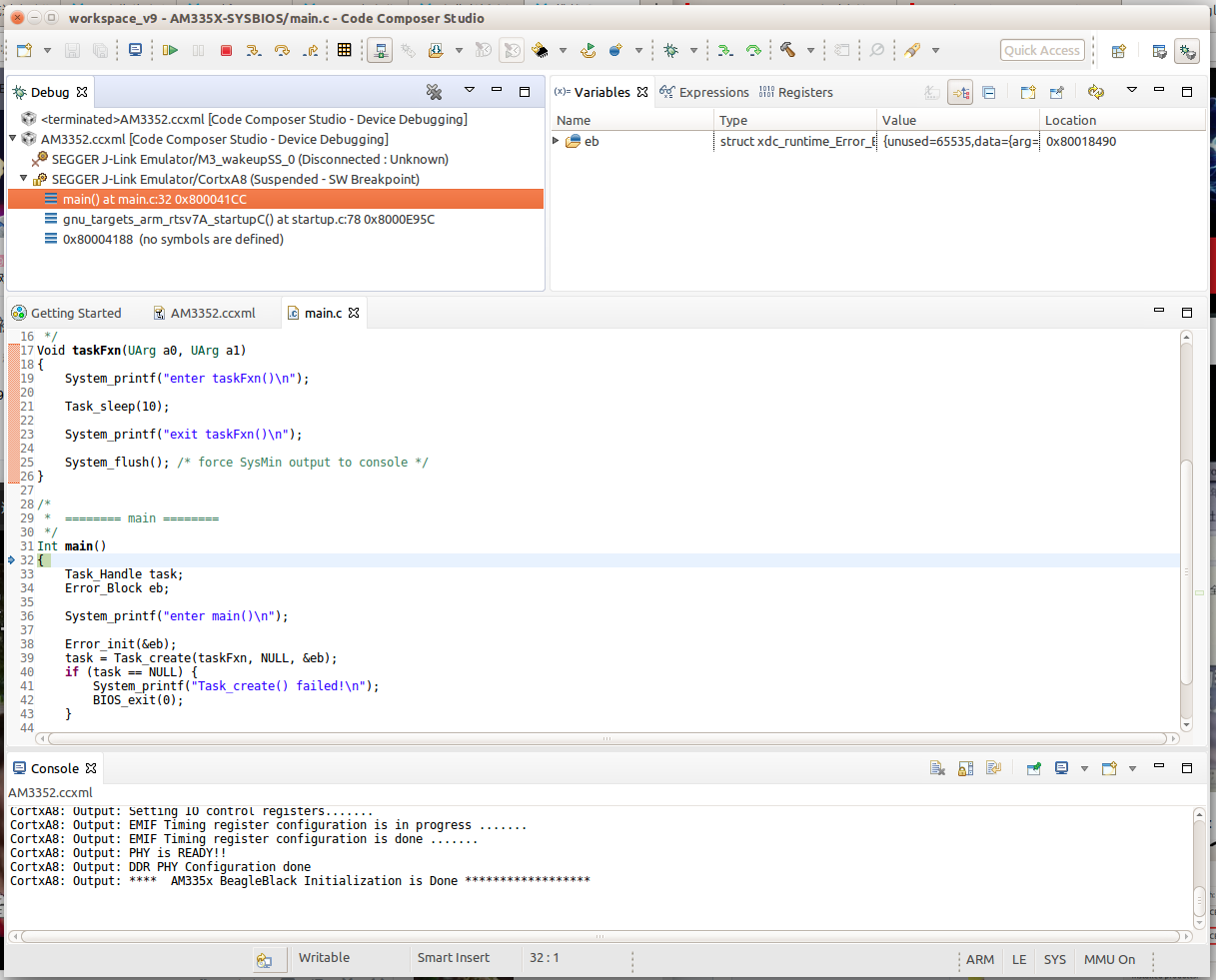

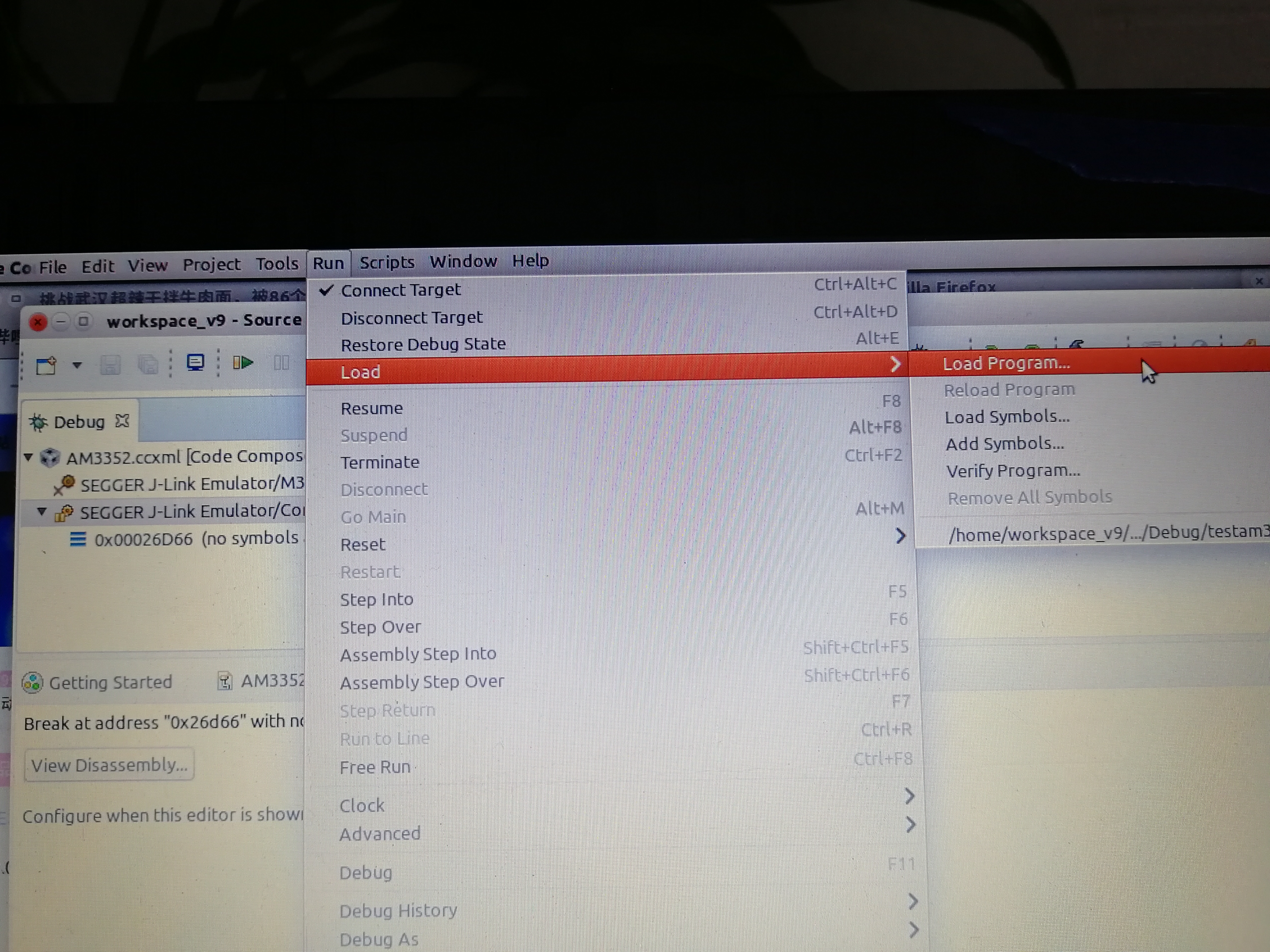

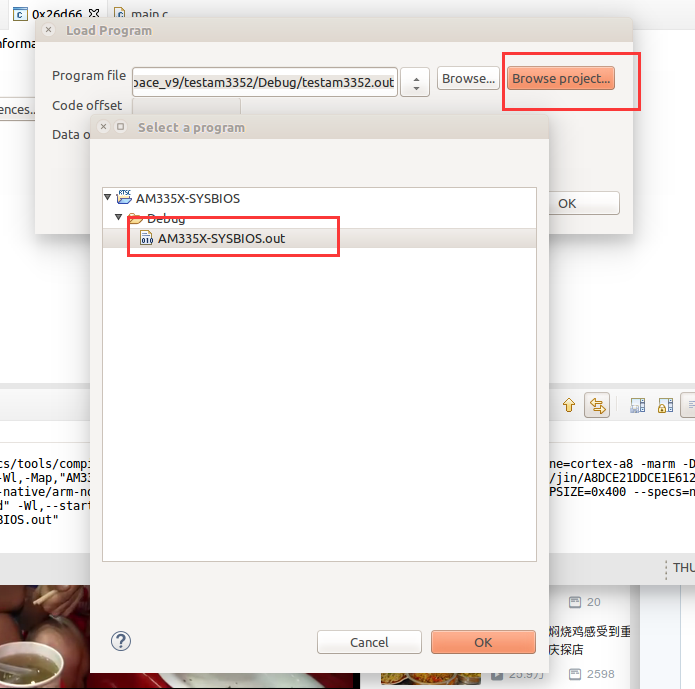

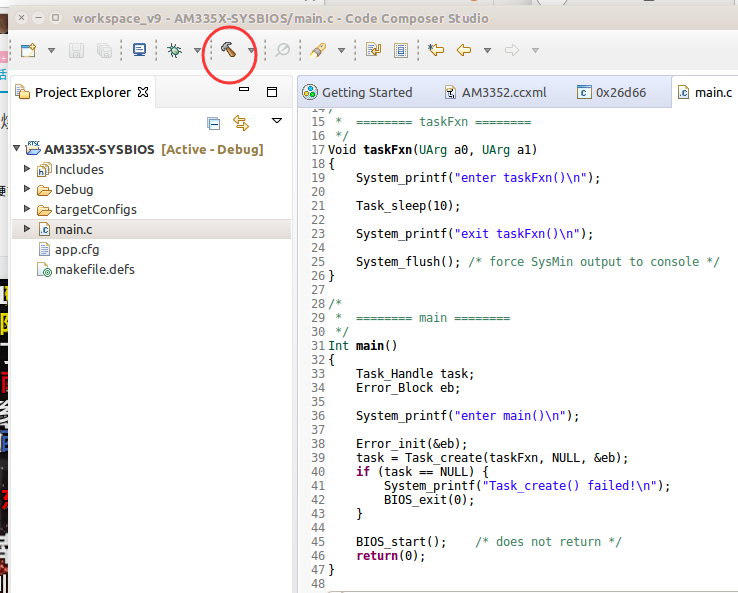

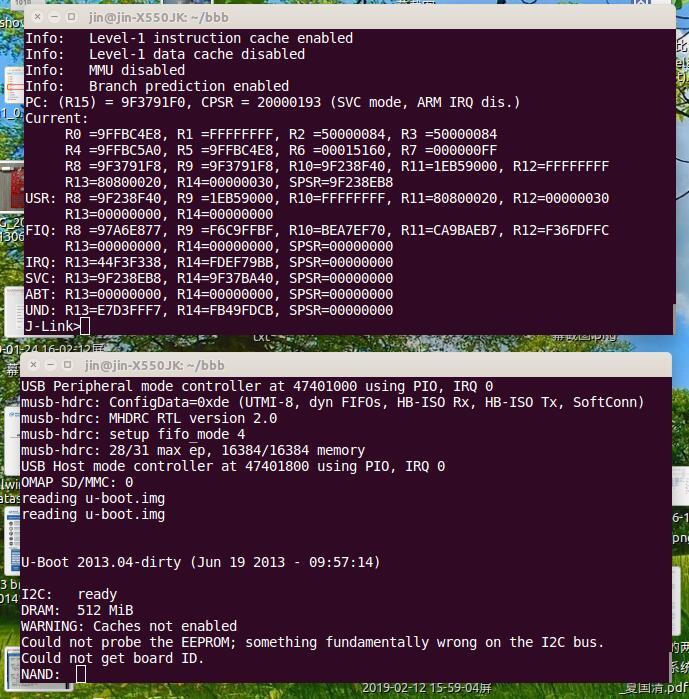

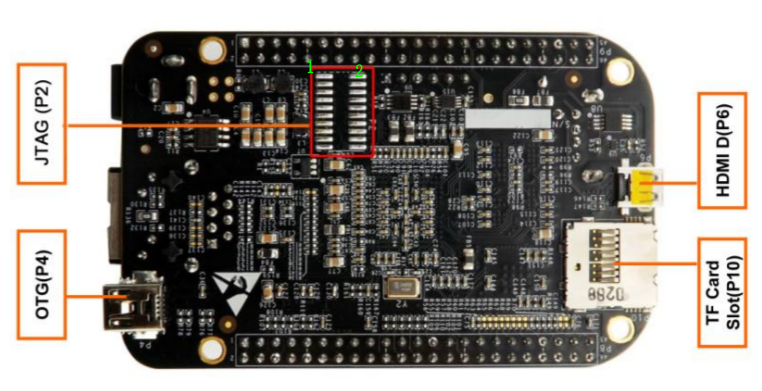

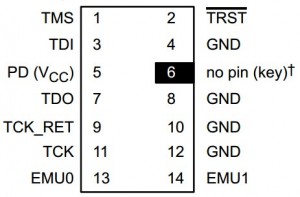

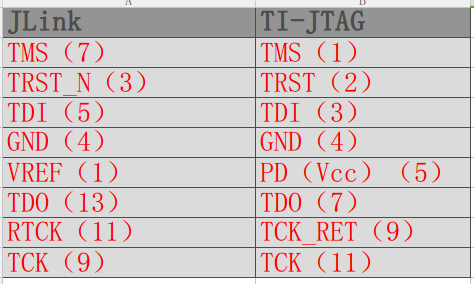

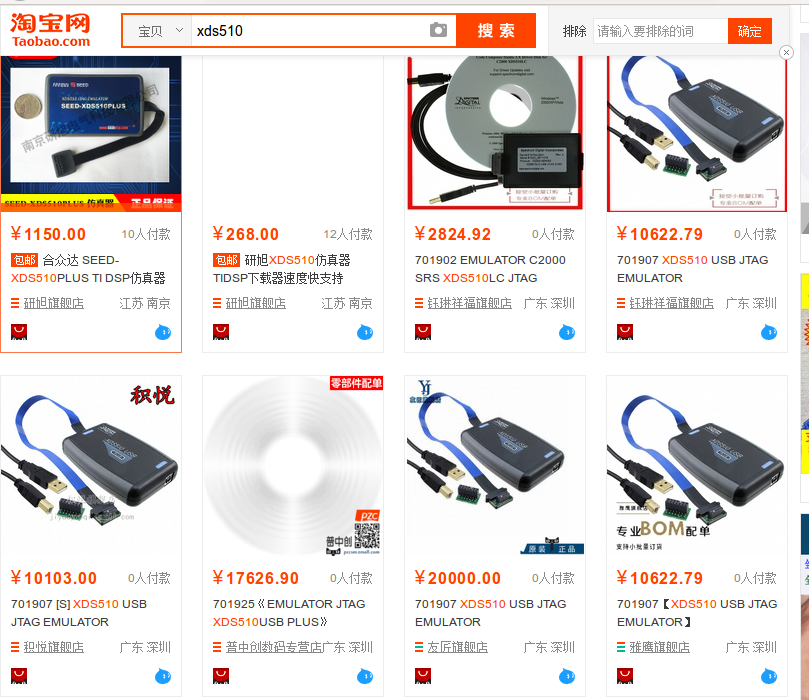

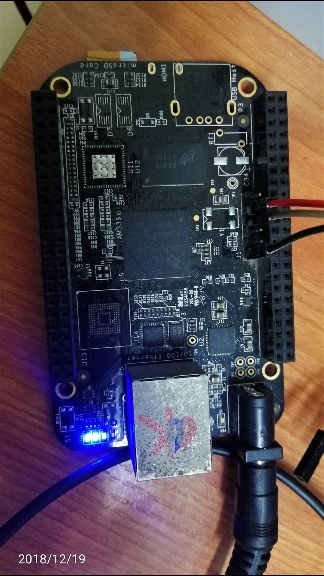

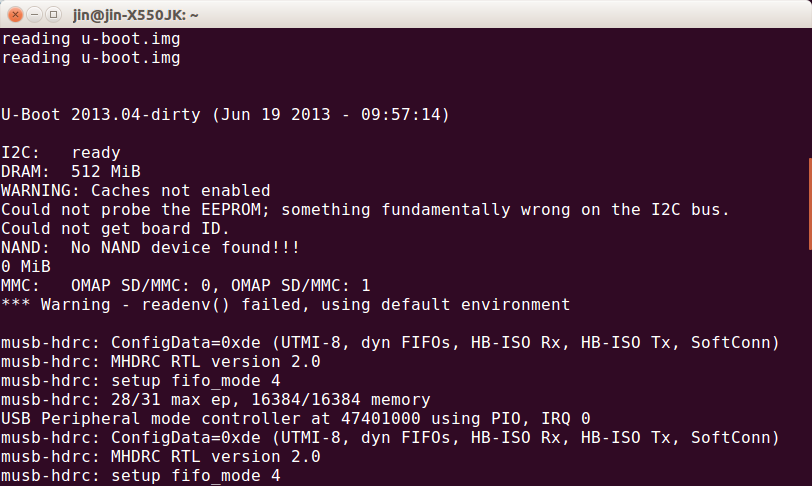

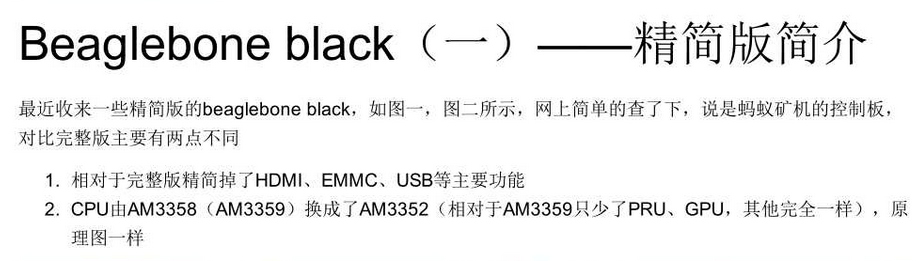

#20 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » AM335x-BeagleBoneBlack别样玩法 » 2019-08-06 10:58:57

SYS/BIOS 实时内核 资料:

http://www.ti.com.cn/tool/cn/SYSBIOS

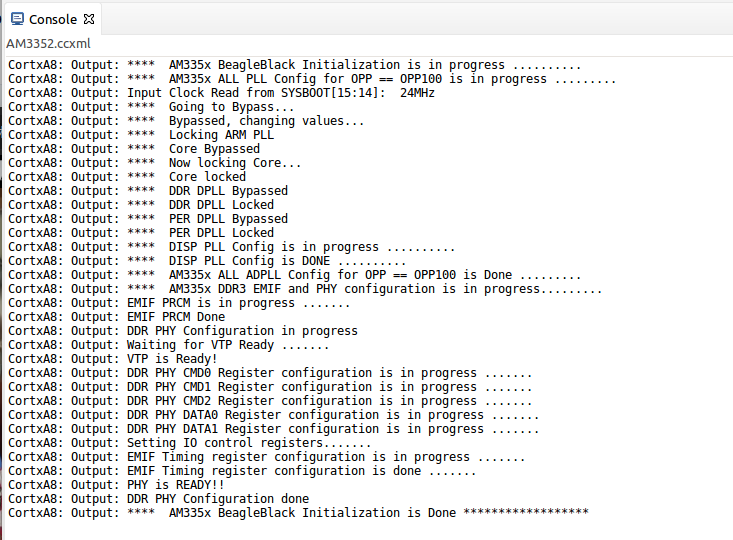

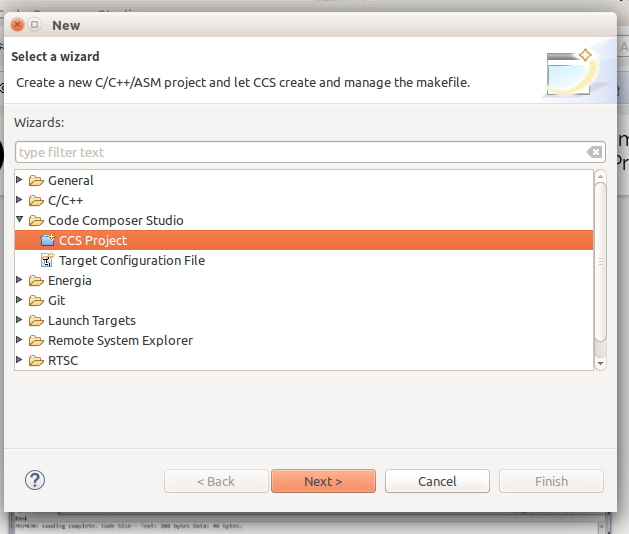

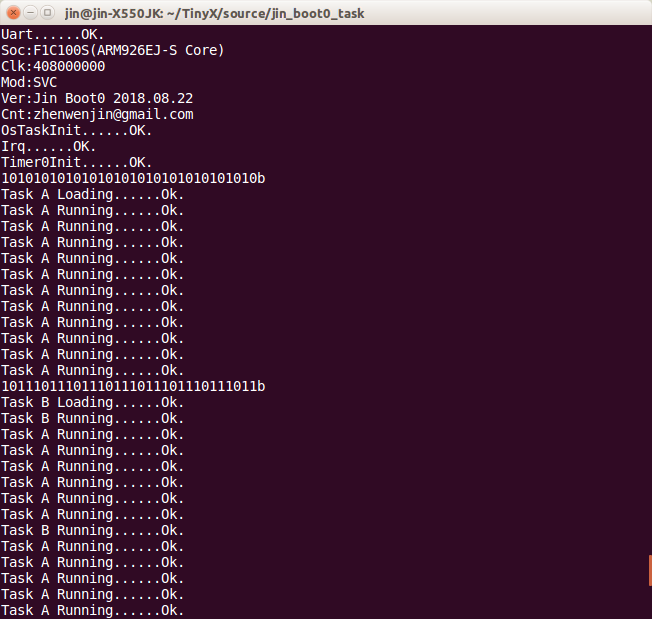

新建一个SYSBIOS工程:

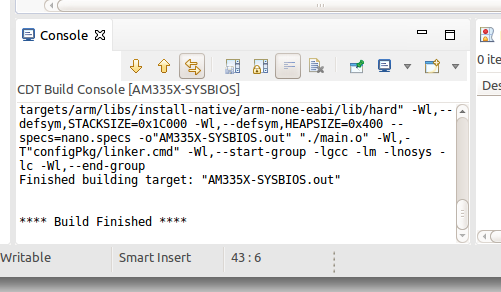

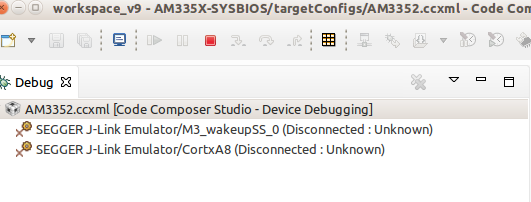

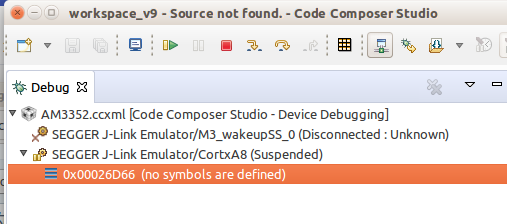

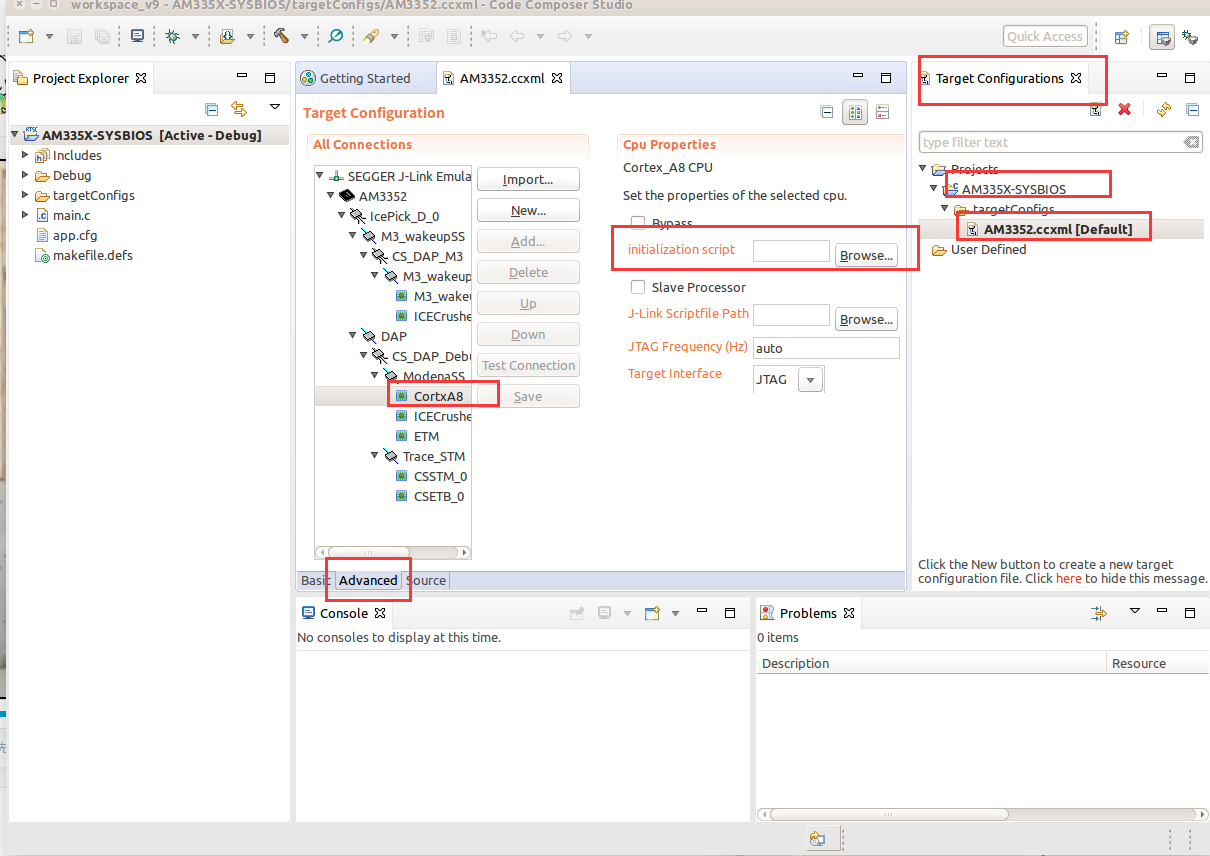

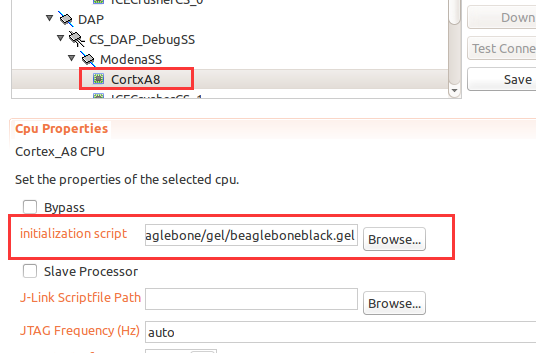

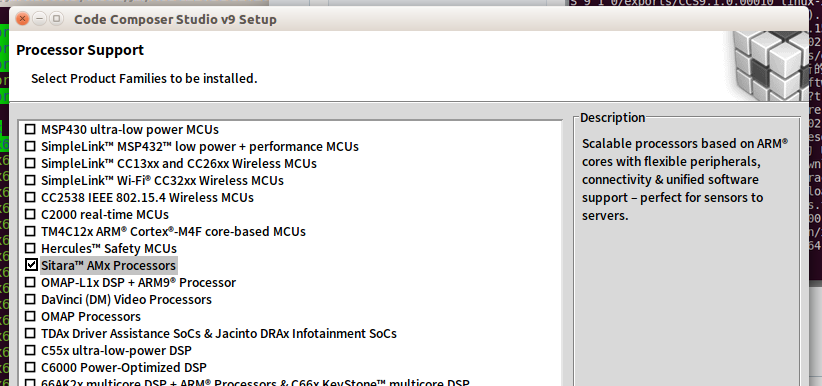

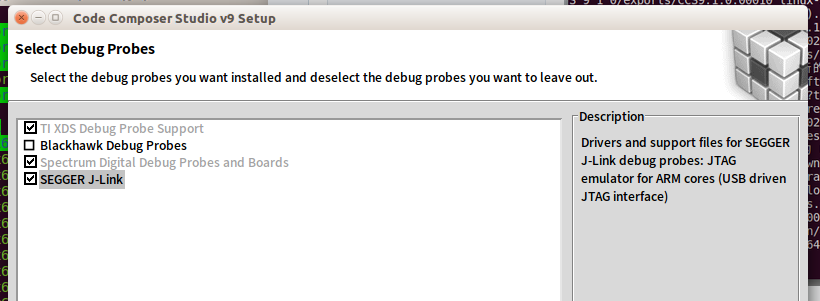

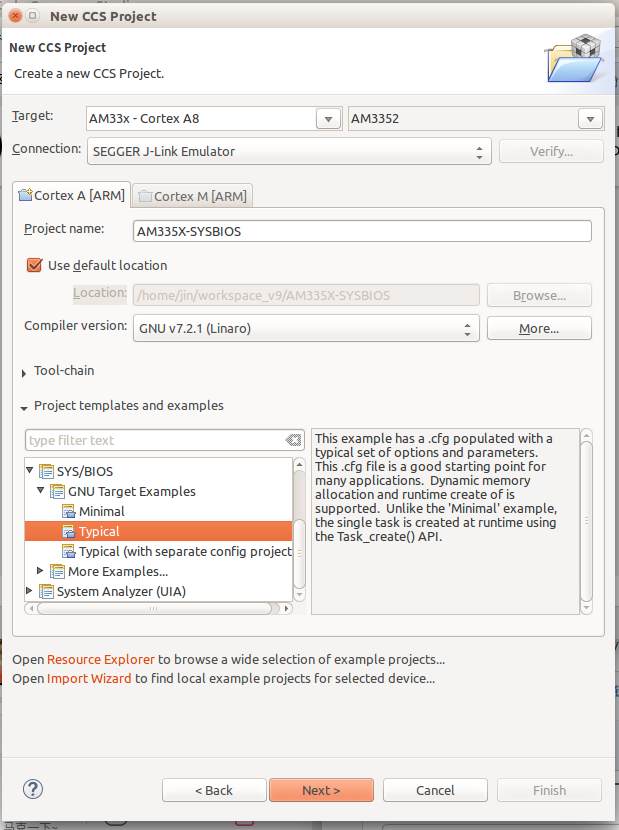

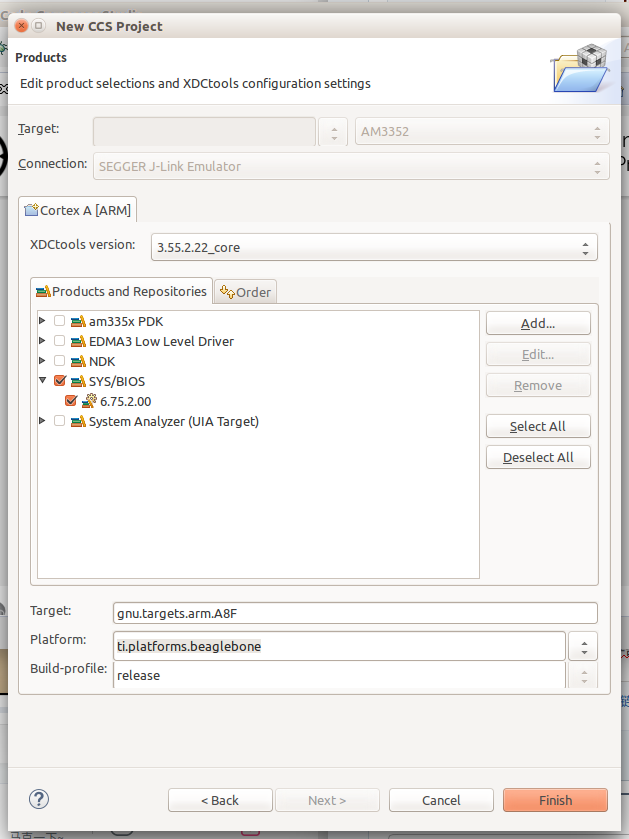

阉割版是AM3352,选择JLink调试,选择CortexA核,选择SYSBIOS:

选择ti.platforms.beaglebone平台,主要作用是内存分布,给工程的lds提供数据:

#22 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » AM335x-BeagleBoneBlack别样玩法 » 2019-08-06 10:35:15

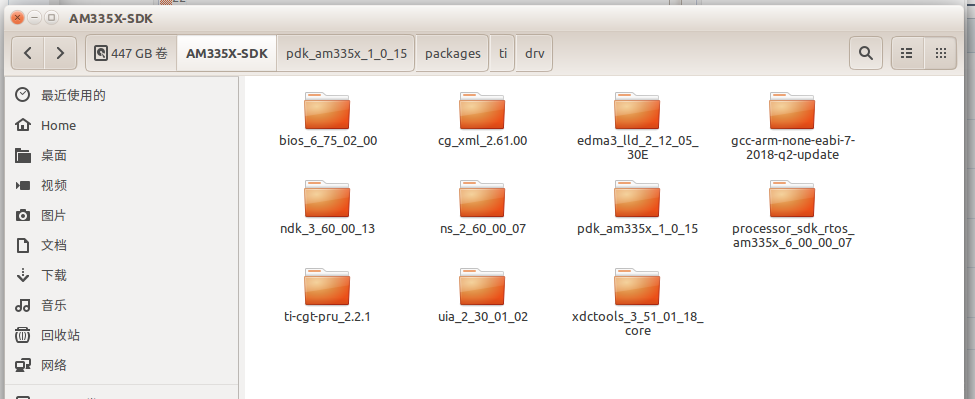

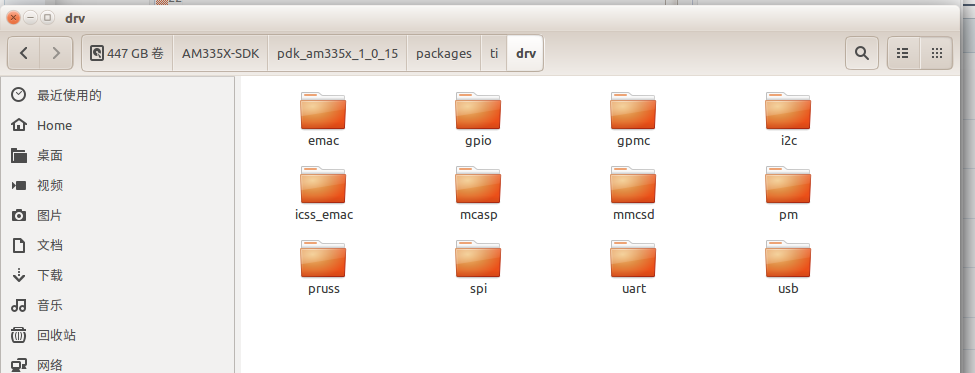

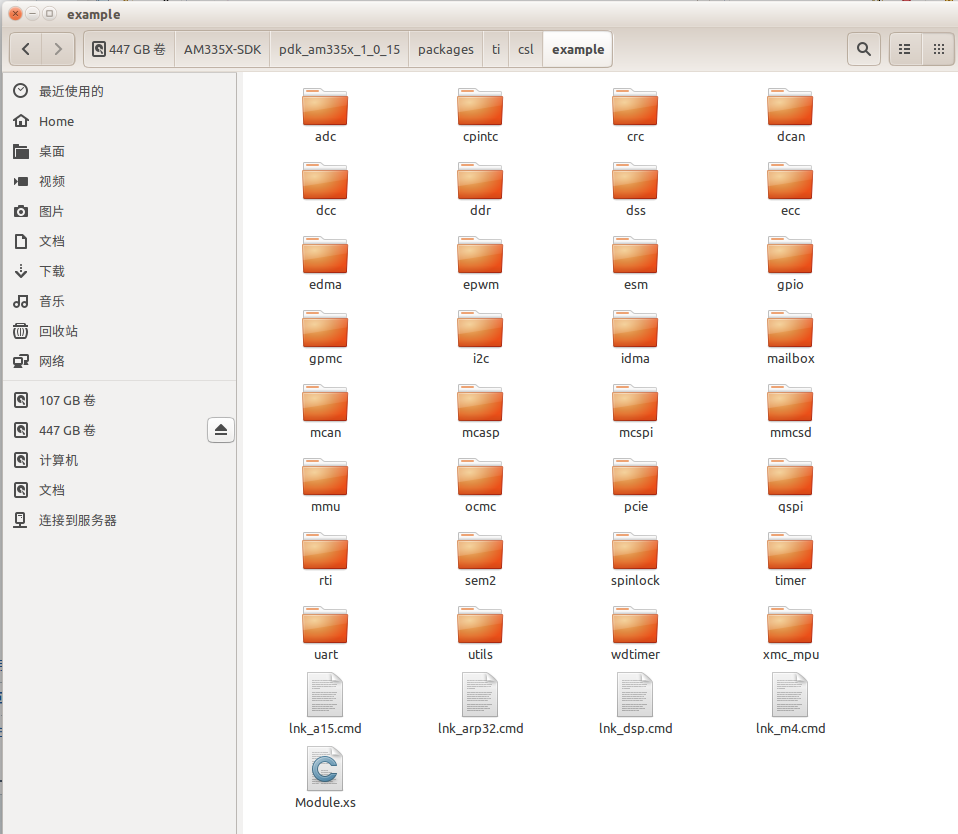

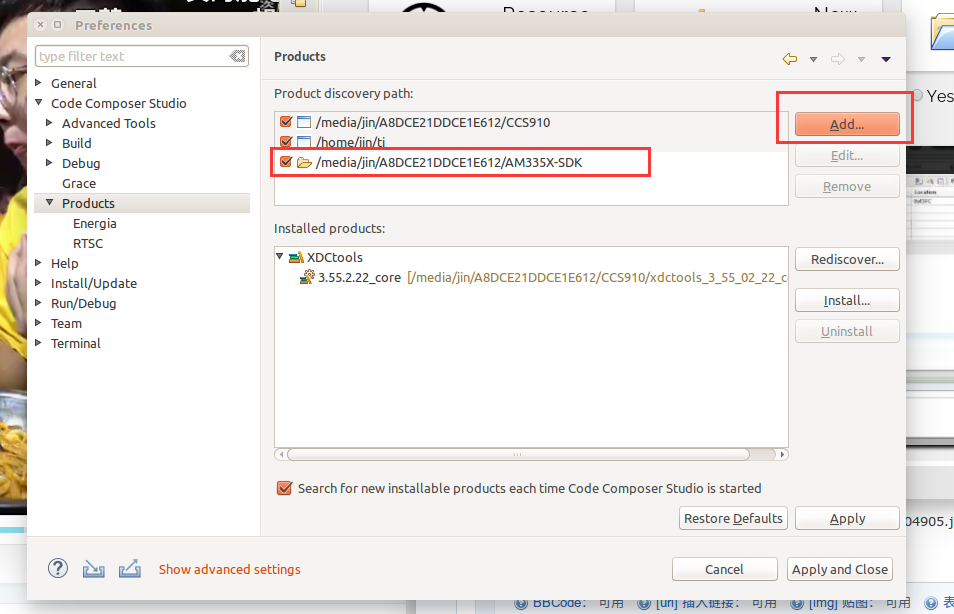

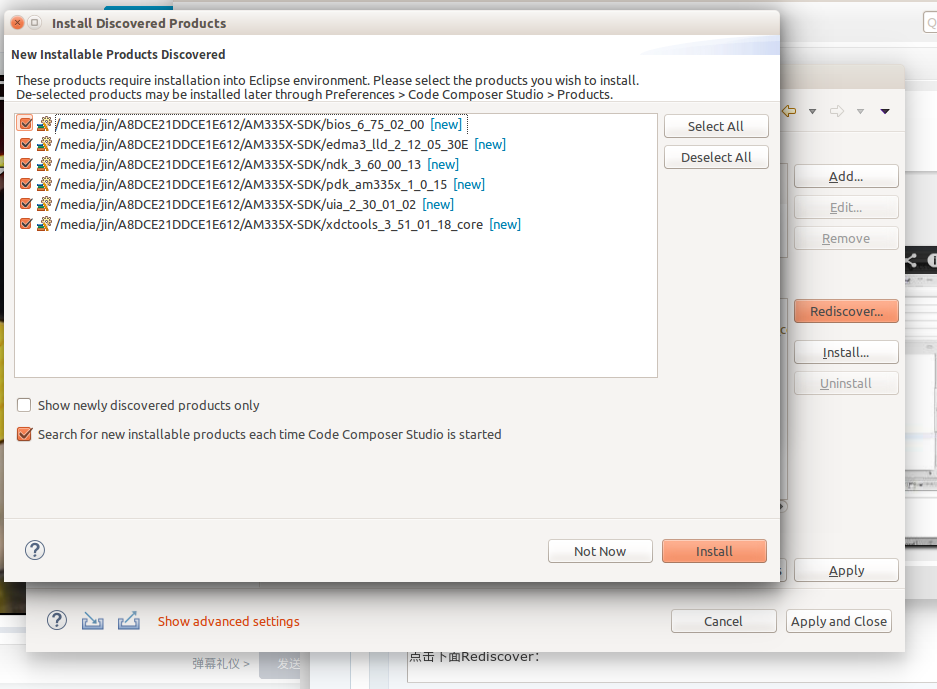

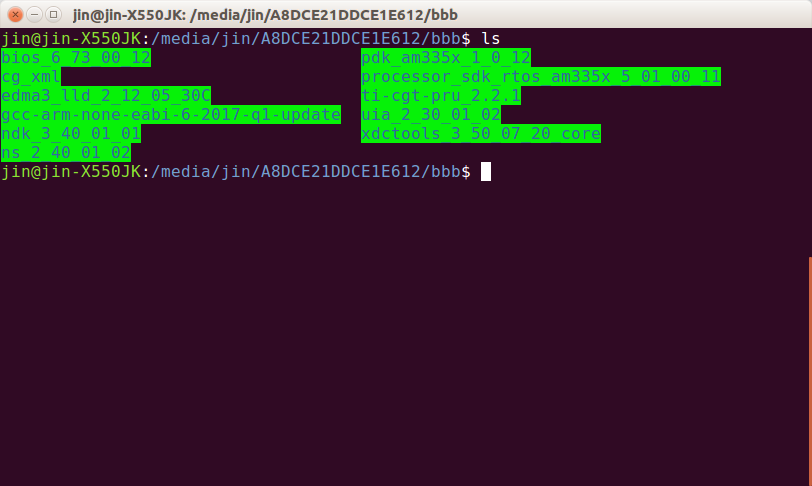

下载适用于 AM335X Sitara™ 处理器的处理器 SDK :

http://www.ti.com.cn/tool/cn/PROCESSOR-SDK-AM335X

下载PROCESSOR-SDK-RTOS-AM335X:

http://software-dl.ti.com/processor-sdk-rtos/esd/AM335X/latest/index_FDS.html

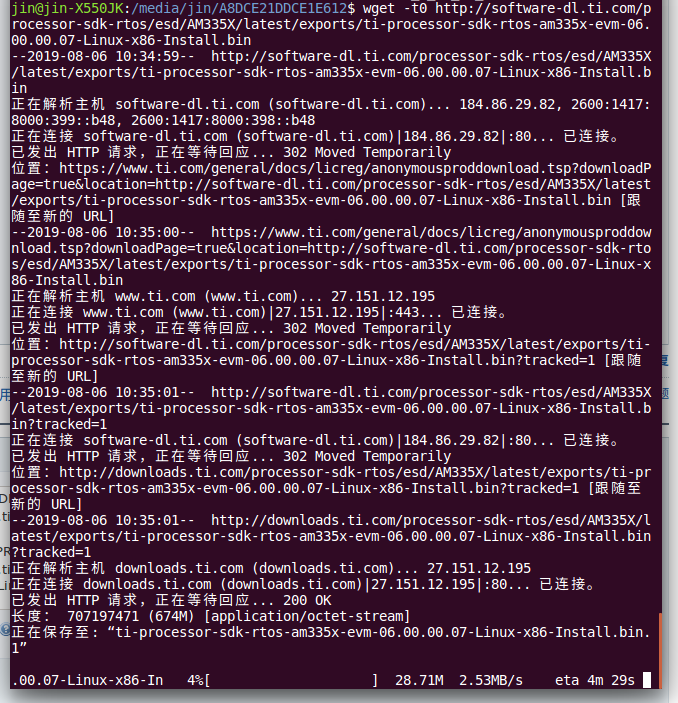

我下载的Linux版本 PROCESSOR-SDK-RTOS-AM335X 06_00_00_07:

http://software-dl.ti.com/processor-sdk-rtos/esd/AM335X/latest/exports/ti-processor-sdk-rtos-am335x-evm-06.00.00.07-Linux-x86-Install.bin

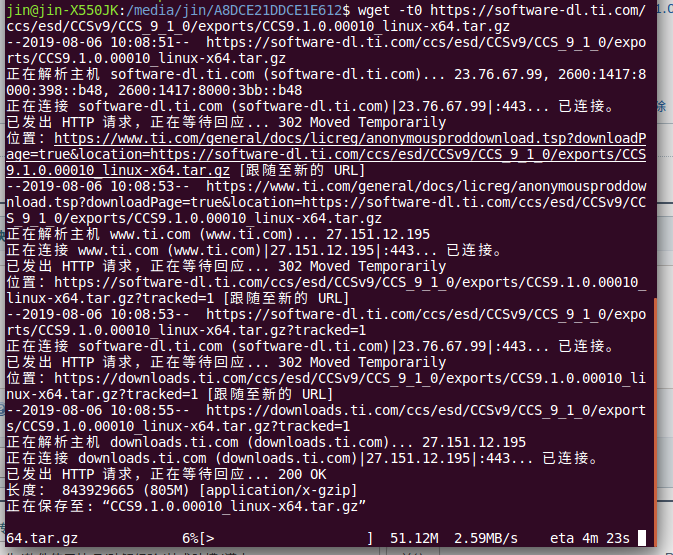

#24 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » AM335x-BeagleBoneBlack别样玩法 » 2019-08-06 10:07:23

#28 Re: 全志 SOC » F1C100S裸奔framebuffer+PWM+GPIO驱动 » 2019-06-14 21:19:42

达克罗德 wrote:

Jin劲 wrote:

达克罗德 wrote:

你把最终要的头信息都丢了

.global _start

_start:

/ Boot head information for BROM /

.long 0xea000016

.byte 'e', 'G', 'O', 'N', '.', 'B', 'T', '0'

.long 0, 0x2000

.byte 'S', 'P', 'L', 2

.long 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0 / 0x28 - boot type /

.long 0, 0, 0, 0, 0, 0, 0, 0 / 0x40 - boot params, 0x5c - dram size /

而且ld文件里

.obj/source/start.o (.text)一定要放到最开始最后还要用tools下面mksunxi对头信息处理一下

这么说 中断向量不放到0了? 中断向量首地址是不是要重新在cp15配置了

只是编译的时候放到文件的头,这样就放到flash的头,启动之后,ram或dram内容都是自己控制了。这个spl也就没用了

brom拷贝flash代码到sram,还拷贝这个头部吗?如果拷贝这个头部,是否brom拷贝到sram后,brom代码控制pc跳到0x1C(头部是0x0-0x018)?

#29 Re: 全志 SOC » F1C100S裸奔framebuffer+PWM+GPIO驱动 » 2019-06-14 18:07:28

达克罗德 wrote:

你把最终要的头信息都丢了

.global _start

_start:

/ Boot head information for BROM /

.long 0xea000016

.byte 'e', 'G', 'O', 'N', '.', 'B', 'T', '0'

.long 0, 0x2000

.byte 'S', 'P', 'L', 2

.long 0, 0

.long 0, 0, 0, 0, 0, 0, 0, 0 / 0x28 - boot type /

.long 0, 0, 0, 0, 0, 0, 0, 0 / 0x40 - boot params, 0x5c - dram size /

而且ld文件里

.obj/source/start.o (.text)一定要放到最开始最后还要用tools下面mksunxi对头信息处理一下

这么说 中断向量不放到0了? 中断向量首地址是不是要重新在cp15配置了

#32 全志 SOC » 100s自己写的boot程序fel加载到sram正常运行,烧到flash不正常 » 2019-06-11 23:58:53

- Jin劲

- 回复: 11

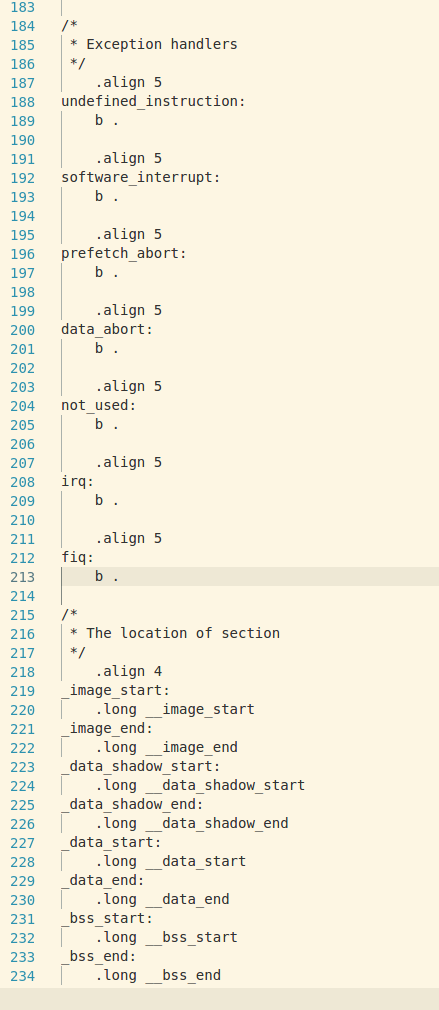

这是我的链接脚本

OUTPUT_FORMAT("elf32-littlearm", "elf32-littlearm", "elf32-littlearm")

OUTPUT_ARCH(arm)

STACK_FIQ_SIZE = 1K;

STACK_IRQ_SIZE = 1K;

STACK_SVC_SIZE = 1K;

STACK_ABT_SIZE = 1K;

STACK_UDF_SIZE = 1K;

STACK_SYS_SIZE = 1K;

MEMORY

{

sram_stack_fiq : org = 40K-1K, len = 1K

sram_stack_irq : org = 40K-2K, len = 1K

sram_stack_svc : org = 40K-3K, len = 1K

sram_stack_abt : org = 40K-4K, len = 1K

sram_stack_udf : org = 40K-5K, len = 1K

sram_stack_sys : org = 40K-6K, len = 1K

sram : org = 0x00000000, len = 40K-6K

}

SECTIONS

{

.text : {

* (.vector)

jin_boot0_start.o (.text)

* (.text)

} > sram

. = ALIGN(4);

.data : {

* (.data)

} > sram

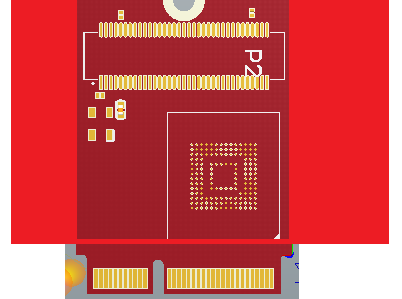

. = ALIGN(4);

.bss : {

* (.bss)

} > sram

. = ALIGN(4);

.sram_stack_fiq : {

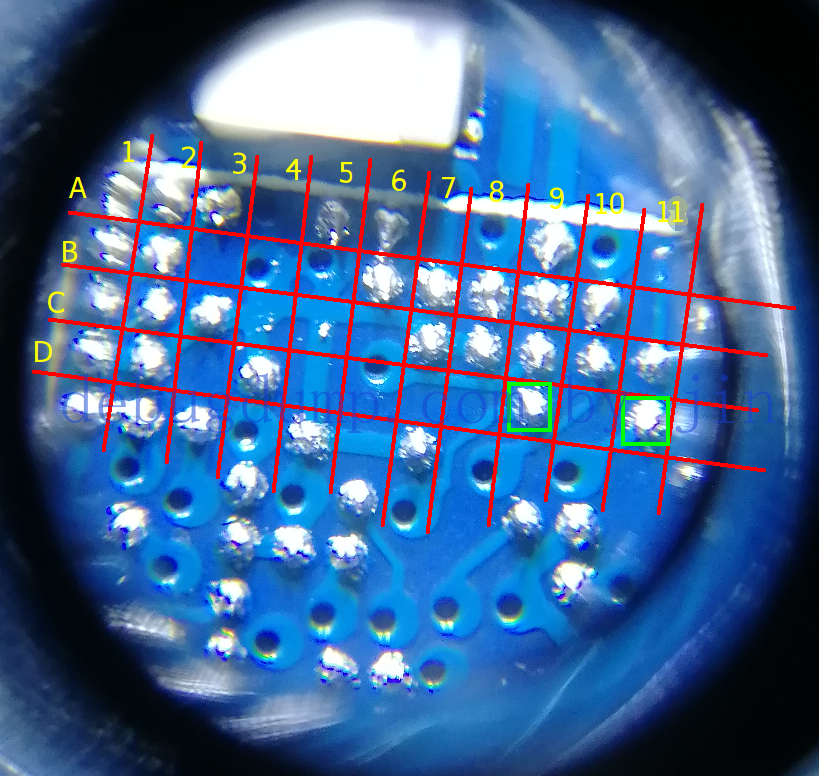

. += STACK_FIQ_SIZE;

PROVIDE(stack_fiq_start = .);

} > sram_stack_fiq

. = ALIGN(4);

.sram_stack_irq : {

. += STACK_IRQ_SIZE;

PROVIDE(stack_irq_start = .);

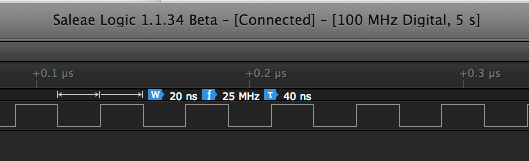

} > sram_stack_irq

. = ALIGN(4);

.sram_stack_svc : {

. += STACK_SVC_SIZE;

PROVIDE(stack_svc_start = .);

} > sram_stack_svc

. = ALIGN(4);

.sram_stack_abt : {

. += STACK_ABT_SIZE;

PROVIDE(stack_abt_start = .);

} > sram_stack_abt

. = ALIGN(4);

.sram_stack_udf : {

. += STACK_UDF_SIZE;

PROVIDE(stack_udf_start = .);

} > sram_stack_udf

. = ALIGN(4);

.sram_stack_sys : {

. += STACK_SYS_SIZE;

PROVIDE(stack_sys_start = .);

} > sram_stack_sys

}利用下面fel命令或者jlink加载到sram正常运行:

sudo sunxi-fel -p write 0 jin_boot0.bin

sudo sunxi-fel exec 0x00000000loadbin jin_boot0.bin,0

setpc 0

然后利用mksunxi加入全志头部

mksunxi/mksunxi jin_boot0.bin

bootloader size= e59ff200

The bootloader head has been fixed烧写到flash

sunxi-fel -p spiflash-write 0 jin_boot0.bin

100% [================================================] 6 kB, 77.5 kB/s 重启brom跑到fel模式了

#33 Re: 全志 SOC » JTAG 调试 H3 » 2019-06-05 22:49:38

#34 Re: VMWare/Linux/Ubuntu/Fedora/CentOS/U-BOOT » 朋友公司有一个linux二进制程序只有一份,,以前别的公司留在服务器的,今天不小心删除了 » 2019-05-31 16:34:09

#36 Re: 全志 SOC » 有人试过在OpenOCD上对V3s裸机程序进行调试么 » 2019-05-31 00:00:50

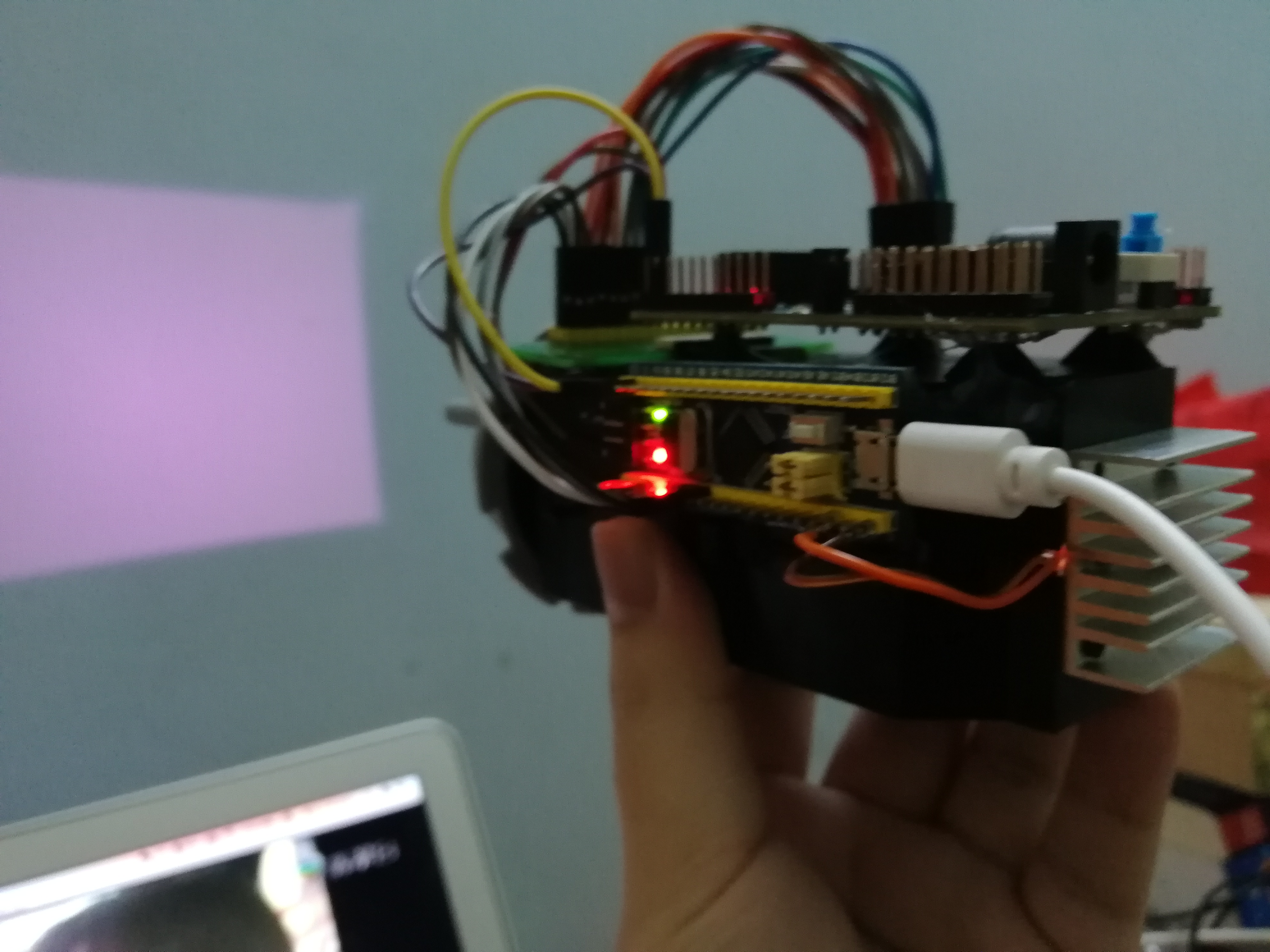

#40 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 纠结了三天169买了个广州花都产的投影仪,坐等测评 » 2019-05-12 11:20:40

- Jin劲

- 回复: 12

https://m.tb.cn/h.e2rxtaV?sm=10b9d9 点击链接,再选择浏览器咑閞;或復·制这段描述¥jcODYcLXQ57¥后到?淘♂寳♀?

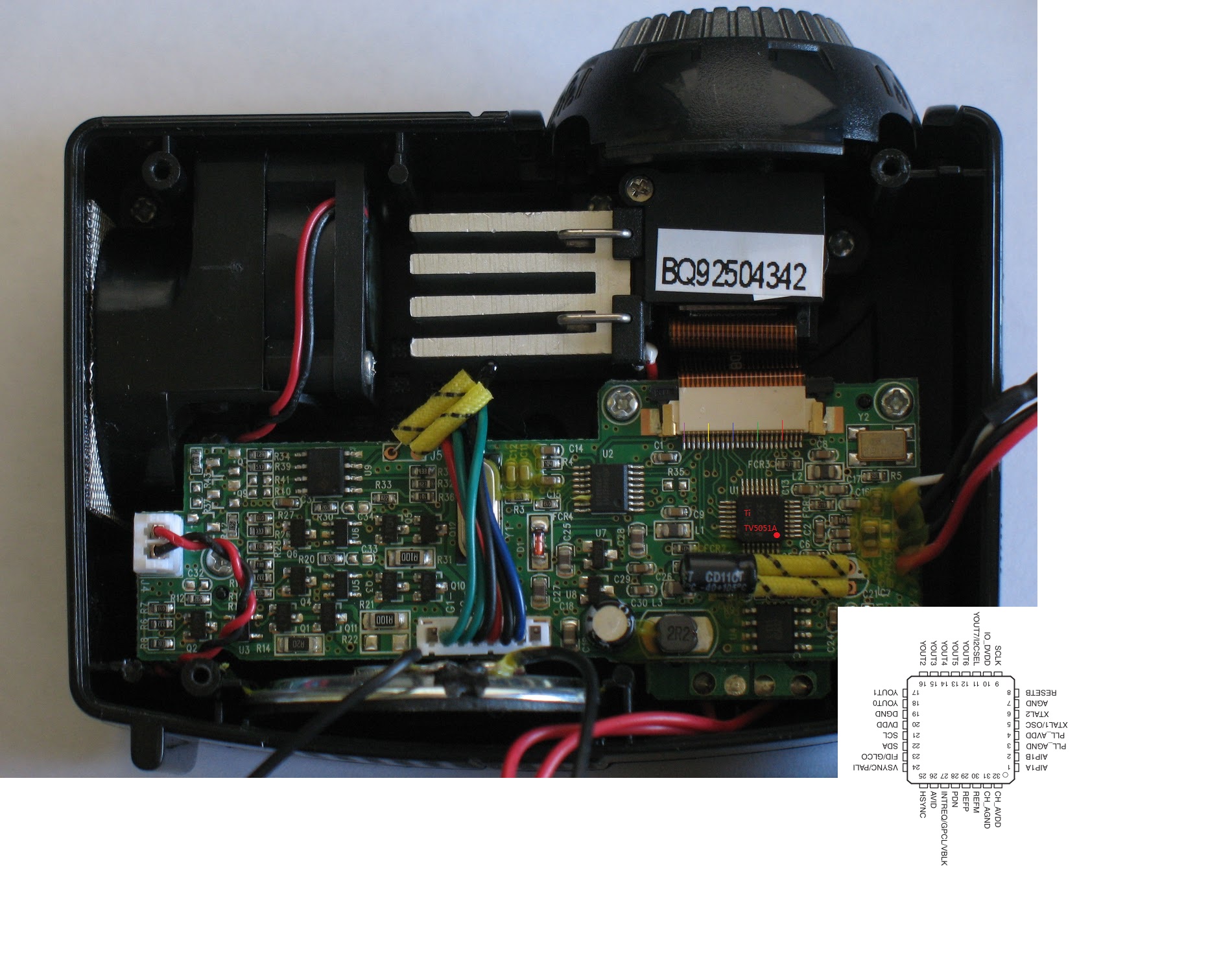

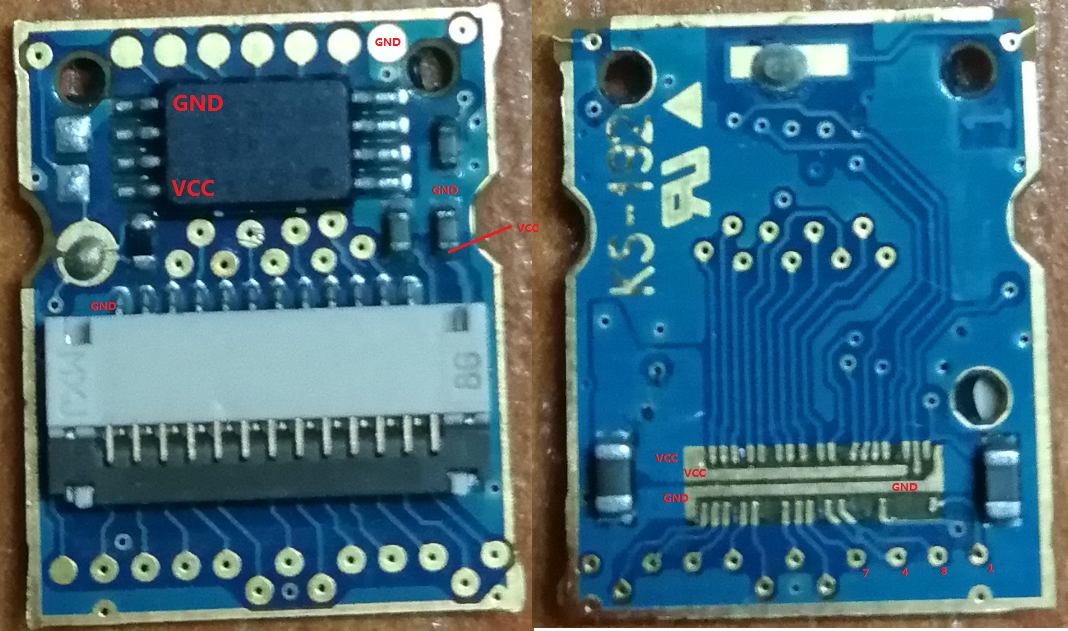

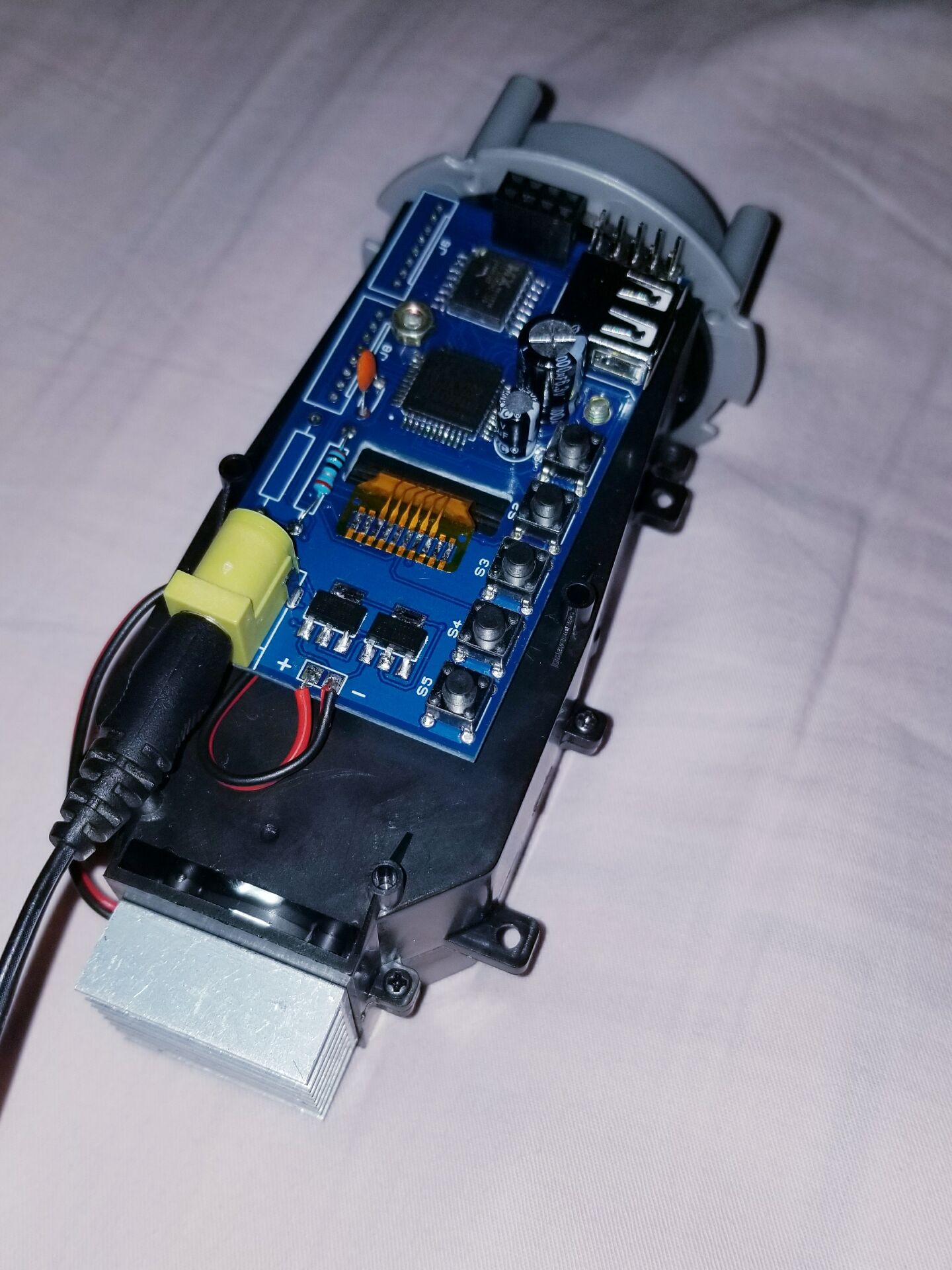

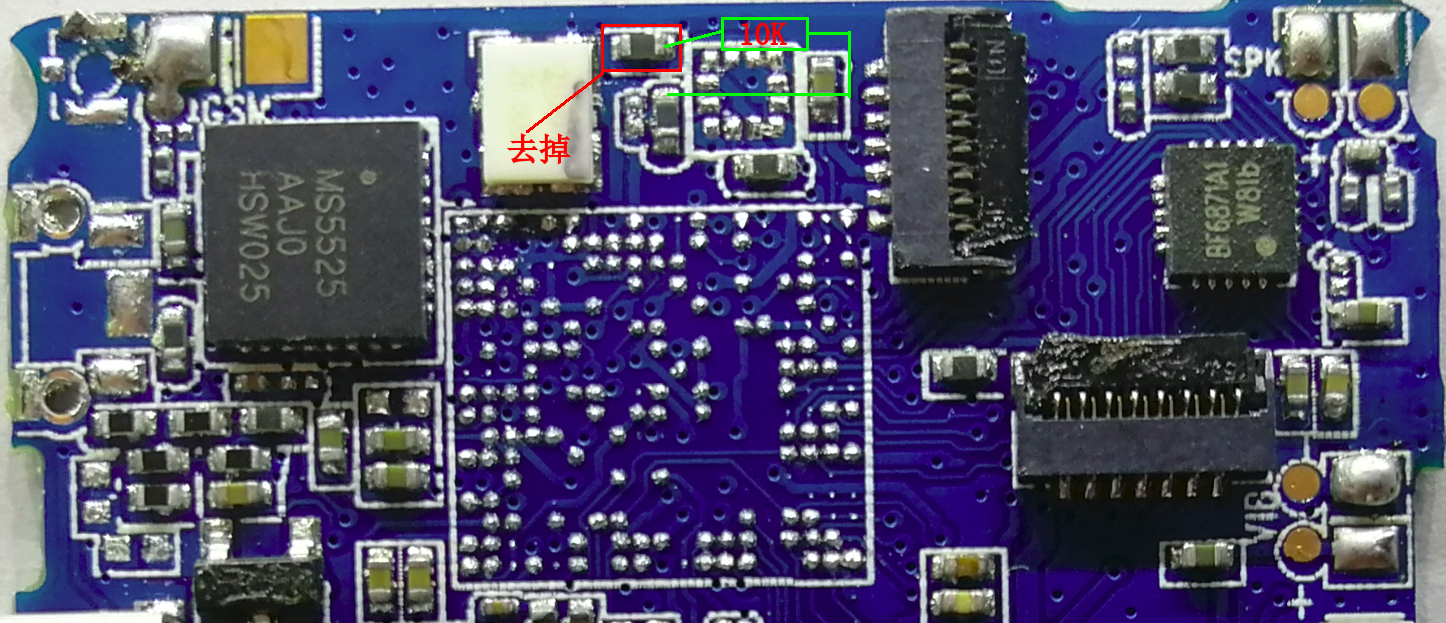

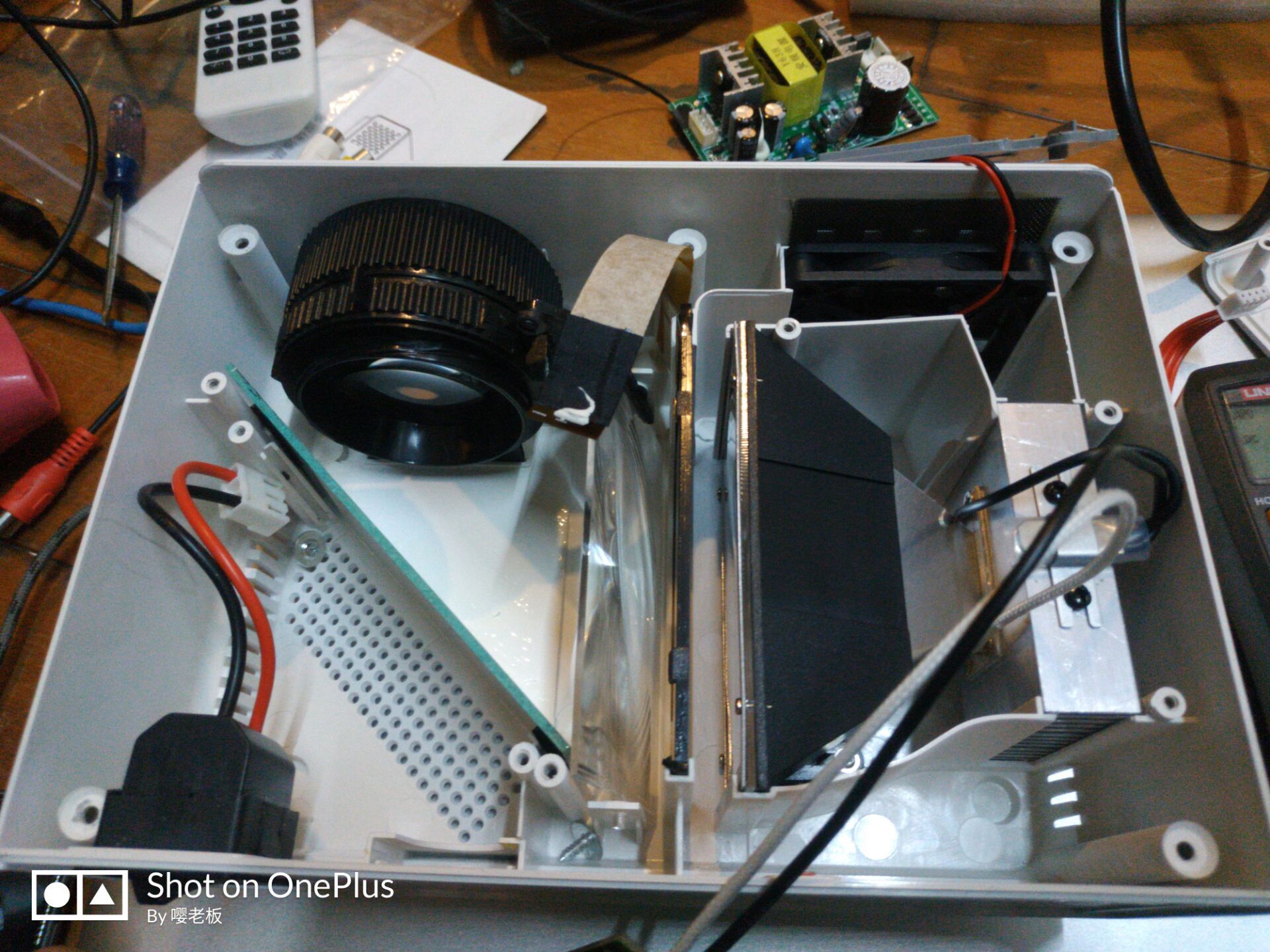

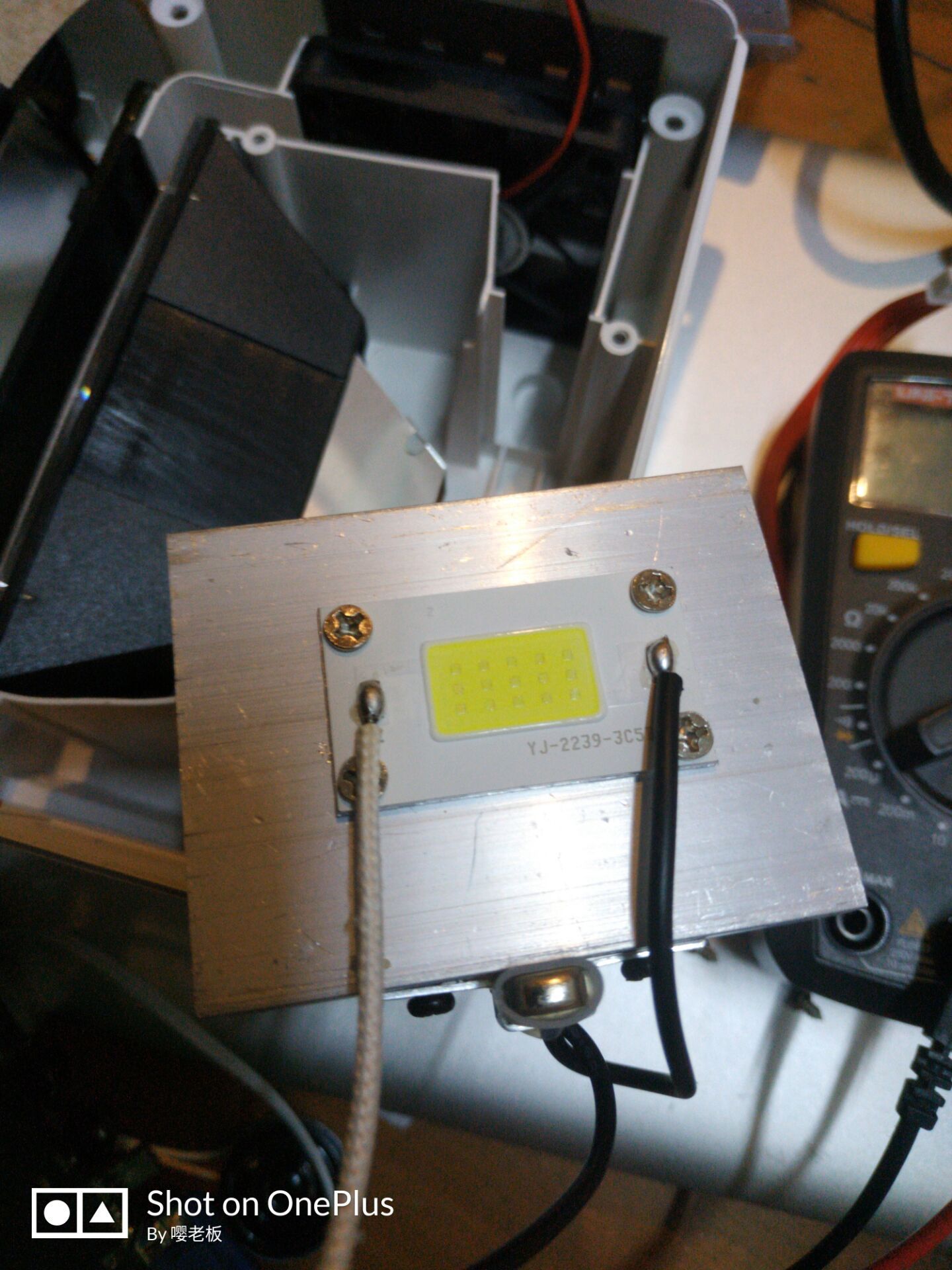

这是别人的拆机图

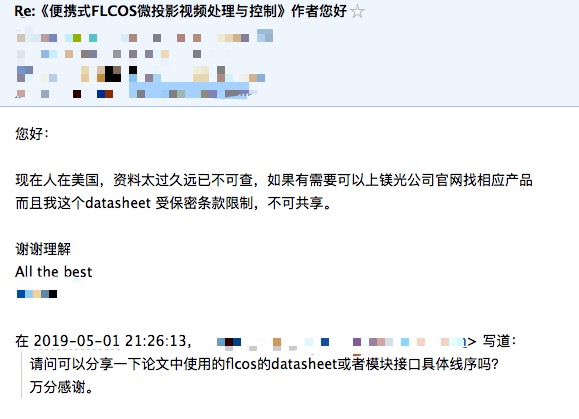

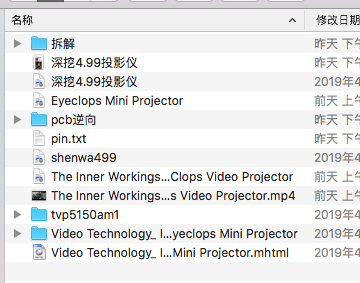

#53 DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 4.99迷你LCOS投影求挖坑 » 2019-04-28 14:13:08

- Jin劲

- 回复: 19

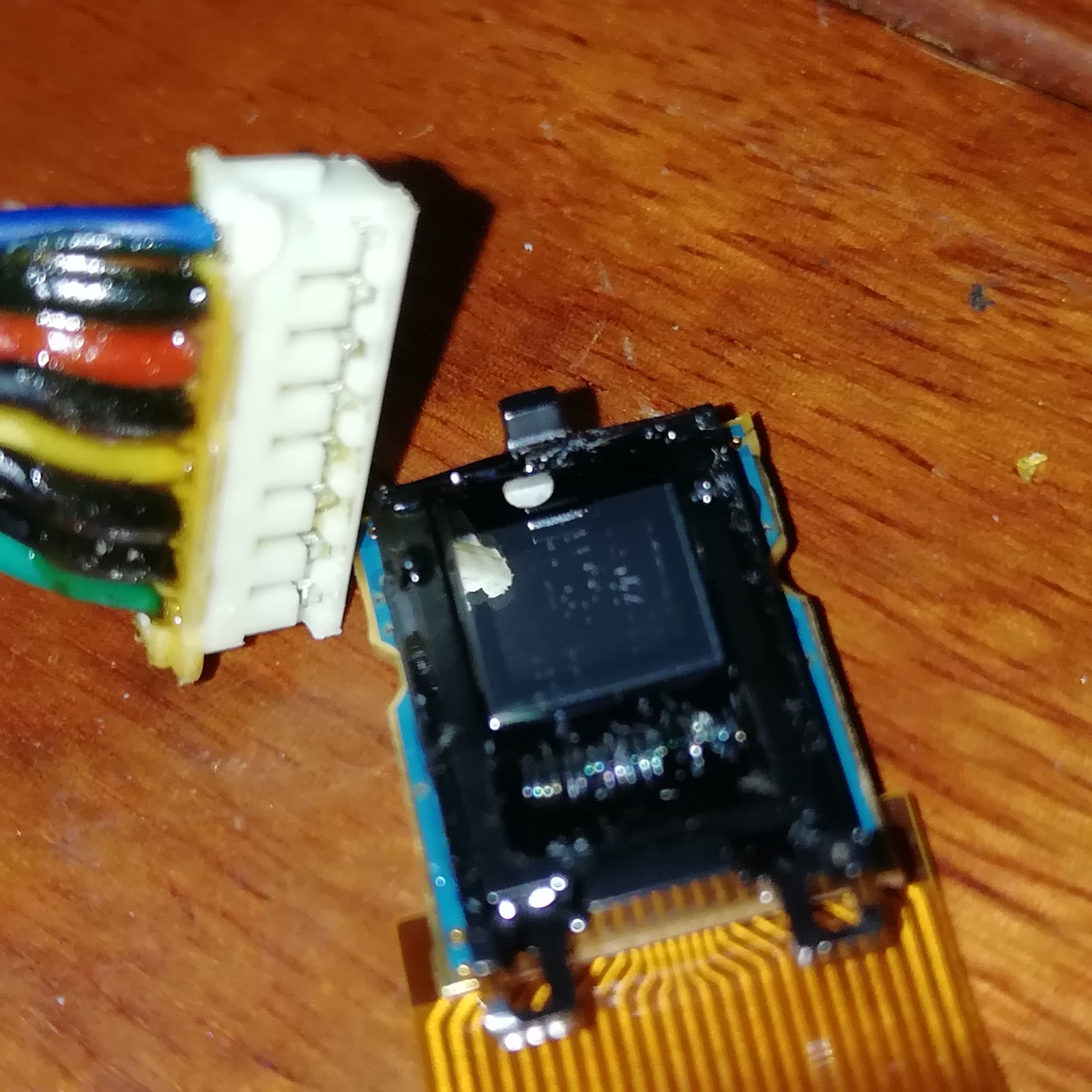

已经深挖原产品拆机图:

shenwa499_20190428-1428.pdf

#54 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 【全新原件】投影机镜头模组 1.5 TFT-LCD迷你小型投影机镜头模组 12元,有没有人玩? » 2019-04-28 10:28:46

视觉℡ wrote:

我找到一个和这个差不多的液晶,控制器用的是OTA5182A

OTA5182A-ORISE.pdf

但是这玩意像素点排列不好控制颜色啊,

/files/members/1430/QQ20190428101025.jpg

淘宝能买到全新的480*240 1.5寸的屏 都是这个主控,我这里还有商家分享的初始化配置代码:

void FY15001H_initial()

{

WriteDataSpi3_16Bit(0x000f);

WriteDataSpi3_16Bit(0x0005);

Delayms(50);

WriteDataSpi3_16Bit(0x000f);

WriteDataSpi3_16Bit(0x0005);

Delayms(50);

WriteDataSpi3_16Bit(0x000f);

Delayms(50);

WriteDataSpi3_16Bit(0x1064); GAMAH=4.5V

WriteDataSpi3_16Bit(0x504E); VCOM

WriteDataSpi3_16Bit(0xC001); VCAC=4.6V

WriteDataSpi3_16Bit(0xE013); GMASEL=2

WriteDataSpi3_16Bit(0xF546); Engineering mode

WriteDataSpi3_16Bit(0x9090); VGL=-7V, VGH=17V, VDD2=5.2V

Delayms(130);

WriteDataSpi3_16Bit(0x0003);GRB&STB="L"

Delayms(80);

}

但似乎统宝并不是这个主控。

#55 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 【全新原件】投影机镜头模组 1.5 TFT-LCD迷你小型投影机镜头模组 12元,有没有人玩? » 2019-04-27 23:35:08

视觉℡ wrote:

Jin劲 wrote:

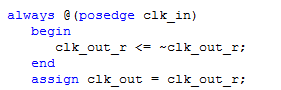

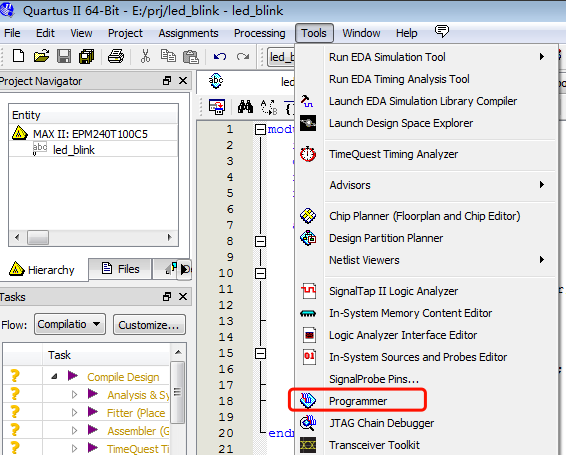

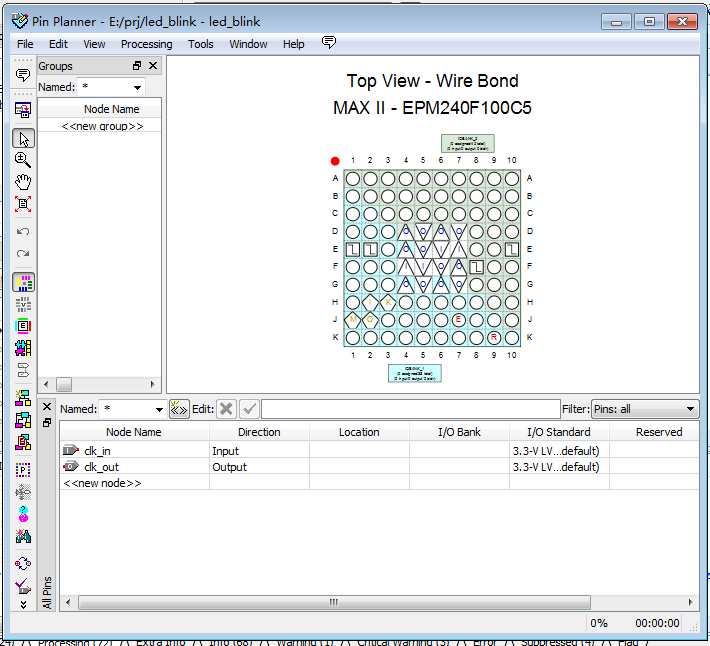

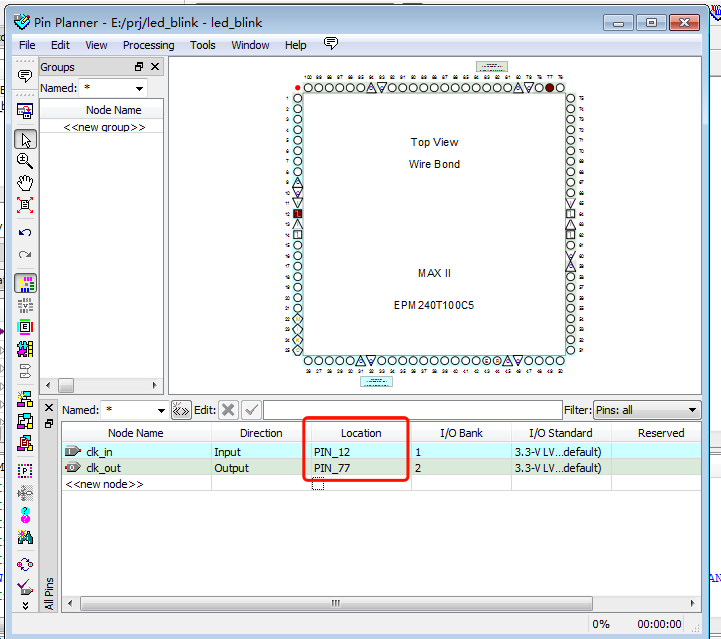

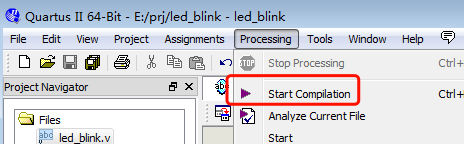

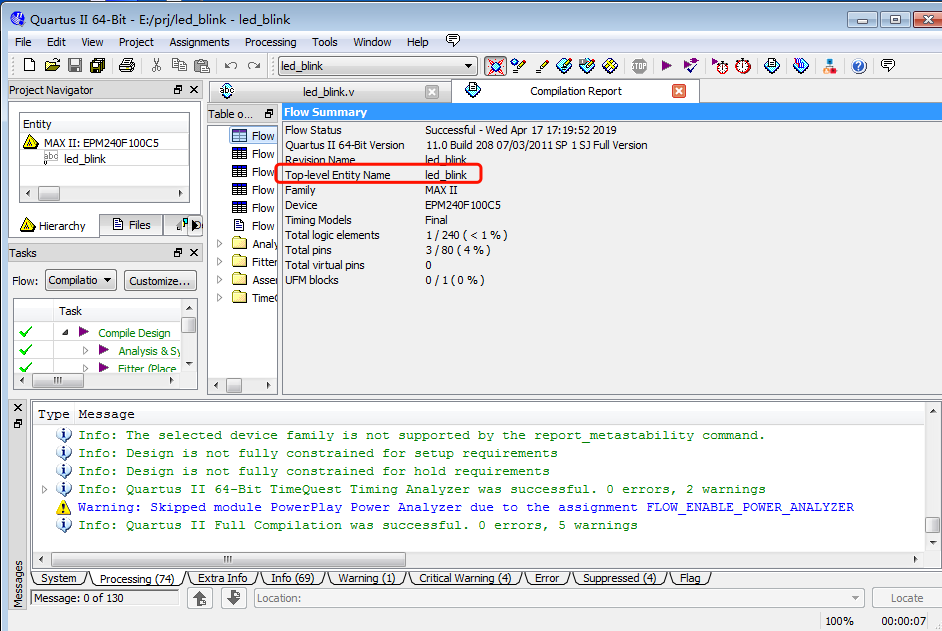

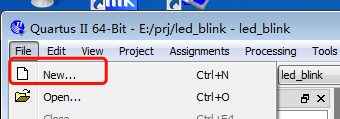

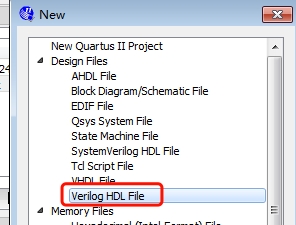

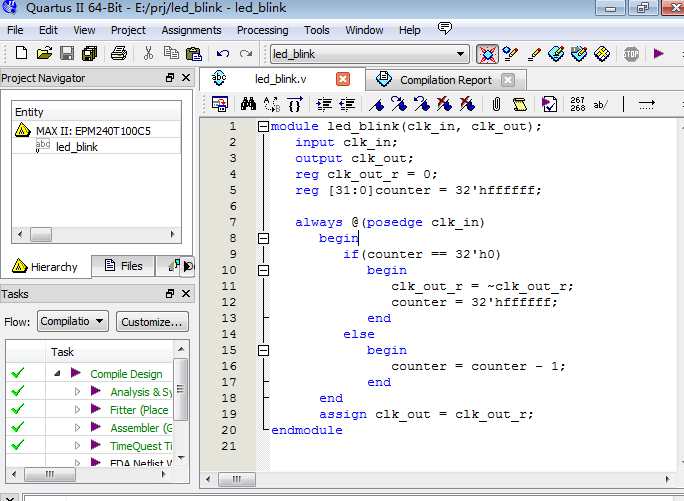

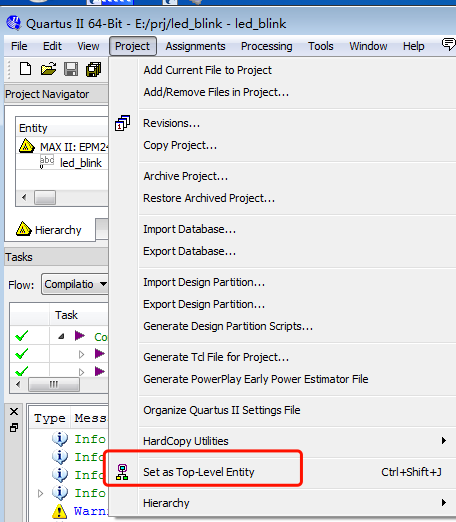

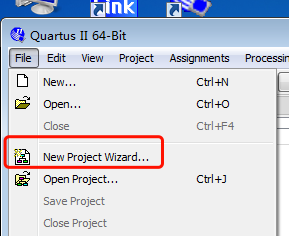

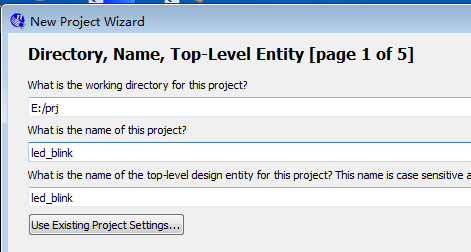

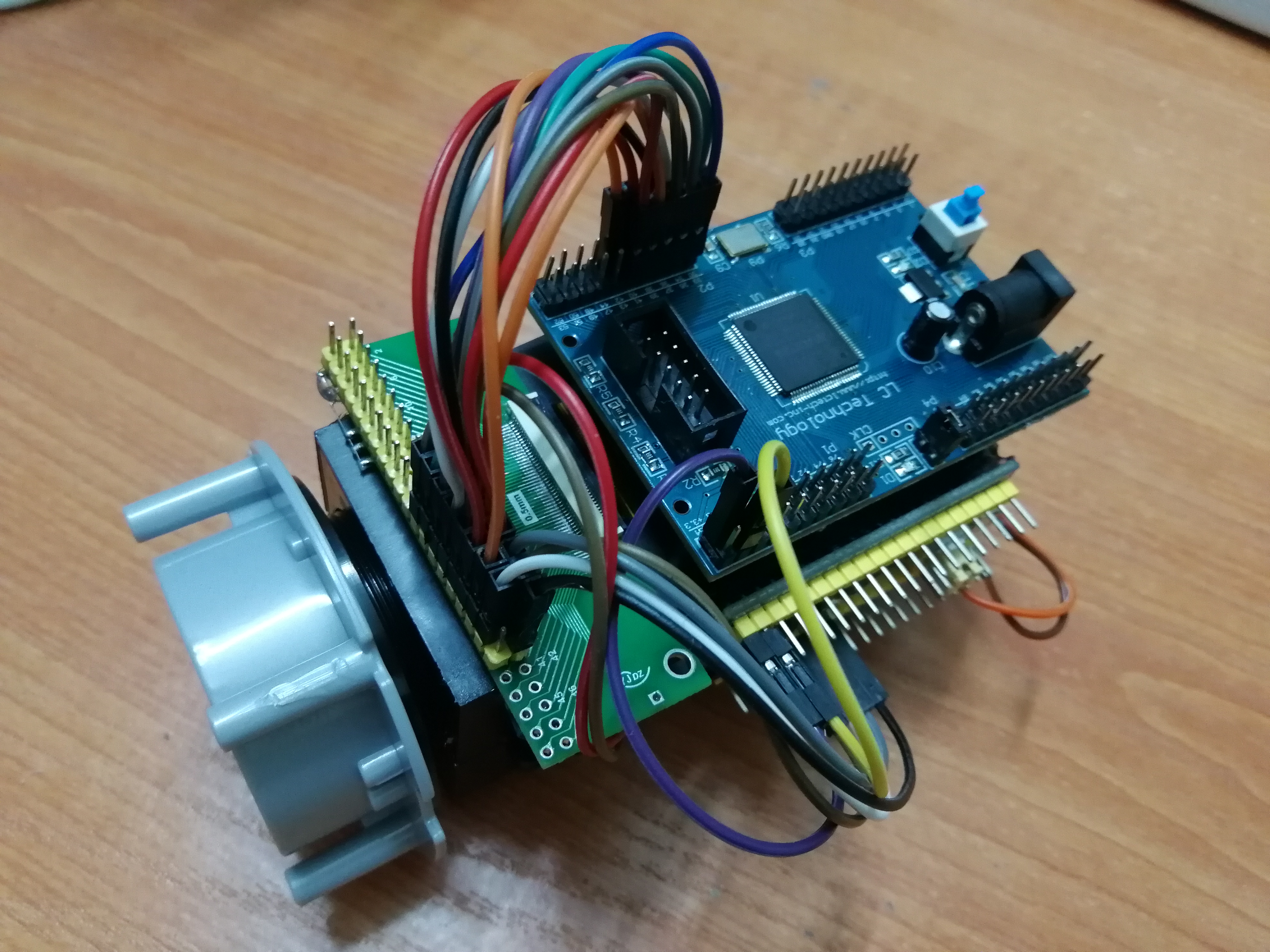

9.98投影工程(FPGAorCPLD联合STM32版)

9_98FPGAorCPLDSTM32.zip

/files/members/719/QQ20190426-1.jpg为什么不用STM32直接驱动,还要加FPGA

主题部分是写在fpga的(其实是cpld),然后我的cpld不够大,所以spi部分放到stm32了。

#56 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 【全新原件】投影机镜头模组 1.5 TFT-LCD迷你小型投影机镜头模组 12元,有没有人玩? » 2019-04-26 16:45:05

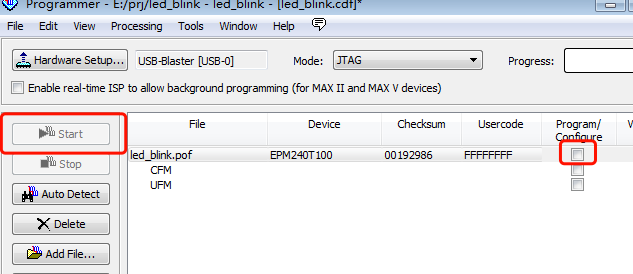

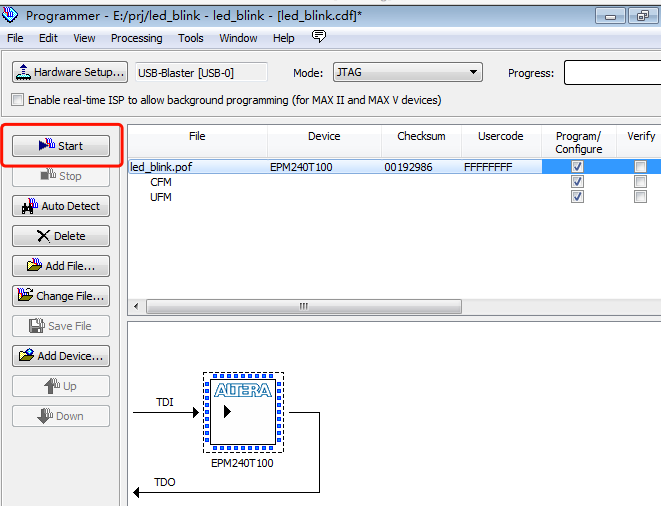

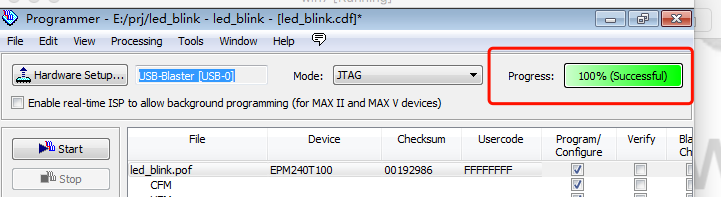

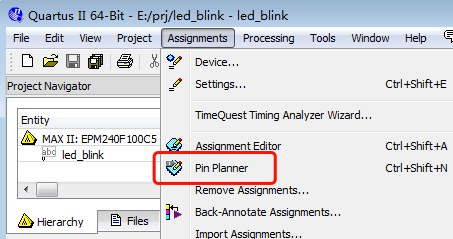

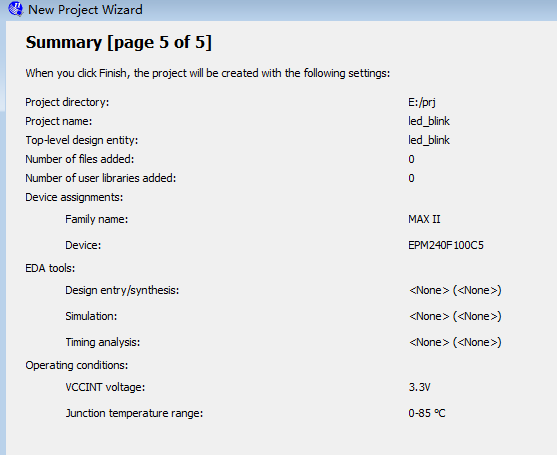

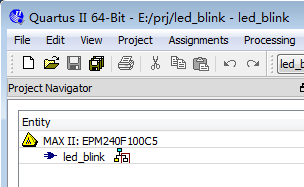

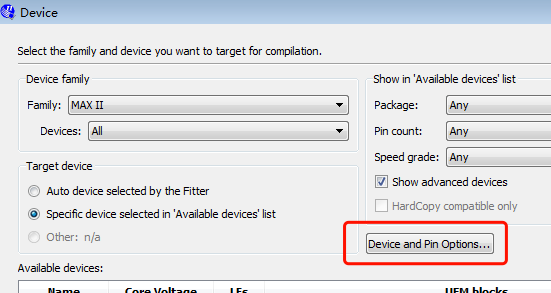

9.98投影工程(FPGAorCPLD联合STM32版)

9_98FPGAorCPLDSTM32.zip

#57 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 【全新原件】投影机镜头模组 1.5 TFT-LCD迷你小型投影机镜头模组 12元,有没有人玩? » 2019-04-25 14:58:42

#58 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 【全新原件】投影机镜头模组 1.5 TFT-LCD迷你小型投影机镜头模组 12元,有没有人玩? » 2019-04-25 14:42:43

#59 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 【全新原件】投影机镜头模组 1.5 TFT-LCD迷你小型投影机镜头模组 12元,有没有人玩? » 2019-04-25 14:38:42

#60 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 【全新原件】投影机镜头模组 1.5 TFT-LCD迷你小型投影机镜头模组 12元,有没有人玩? » 2019-04-25 14:28:55

ybbrdfxk0922 wrote:

TPG121-V1_7.pdf

这个是从别的网站上找的统宝屏的配置,大概试了下,只要配置寄存器2,模式选择 through模式,,寄存器3 ,non-interlace(时序相对简单),就可以正常点亮了。

问题:1.就是rgb delta的屏好像颜色排序不一样。奇行偶行不一样,需要区别对待。但是选择through模式后,好像横向只有480/3=160个点了。第一次玩屏,懵逼中,有懂的讲解下呗

2.参照上面的手册,好像可以直接输出YUV的方式。刚试了下,好像是可行的。但是第一次玩,只会用FPGA刷全色。/files/members/860/none.jpg

这个是通过SPI口回读的寄存器配置。

/files/members/860/RGB_Delta.jpg

rgb delta的问题

/files/members/860/none_20190413-1628.jpg

需要配置的值

感谢

#61 Re: 全志 SOC » F1C100s Nano使用一键烧录后出现的问题 » 2019-04-22 13:41:02

各版本arm-gcc区别与安装:

https://www.jianshu.com/p/fd0103d59d8e

#62 Re: 全志 SOC » F1C100s Nano使用一键烧录后出现的问题 » 2019-04-22 13:37:53

#63 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 学习fpga的妈妈cpld » 2019-04-22 13:22:17

posystorage wrote:

Jin劲 wrote:

posystorage wrote:

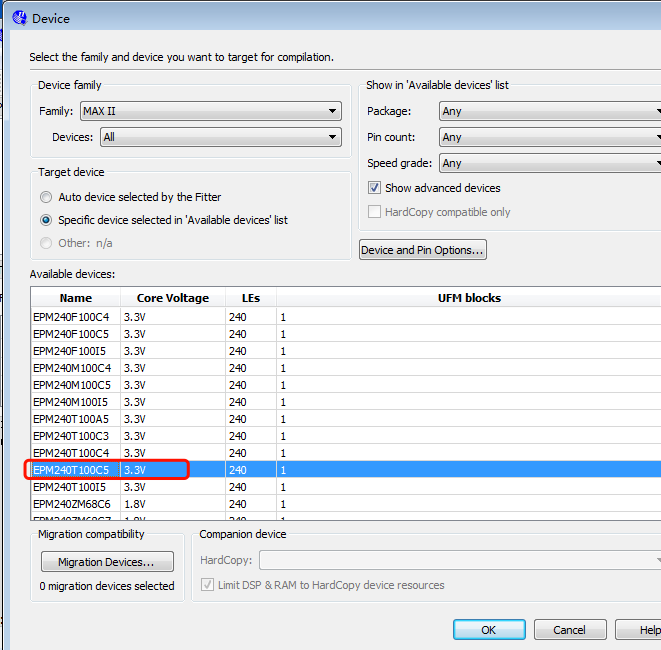

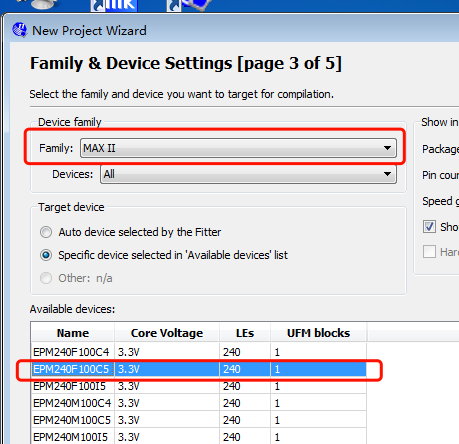

这个芯片我也在玩 还是挺不错的 便宜大碗

嗯嗯 学习成本不错,就是门有点不够,想做点大东西不行。

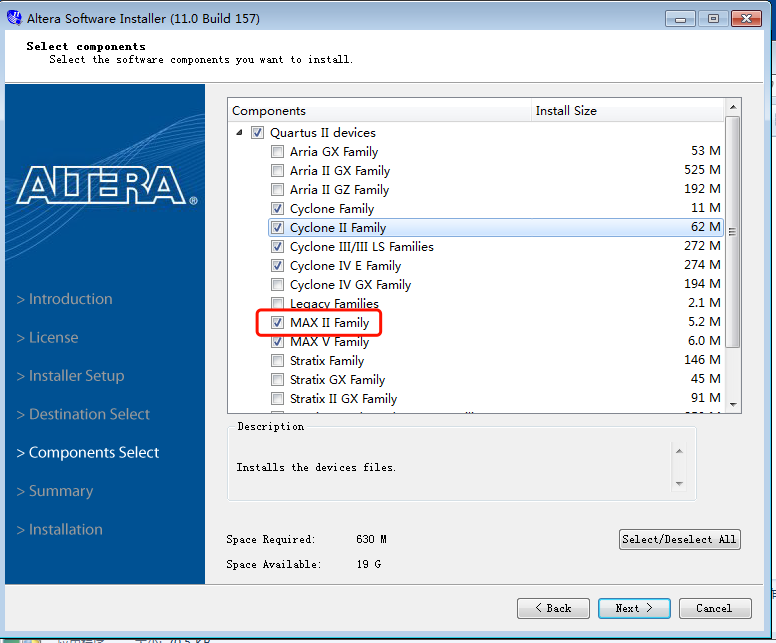

所以我想换一个老的芯片 epm3000a系列,好像停产了,quartus ii 11不支持了。

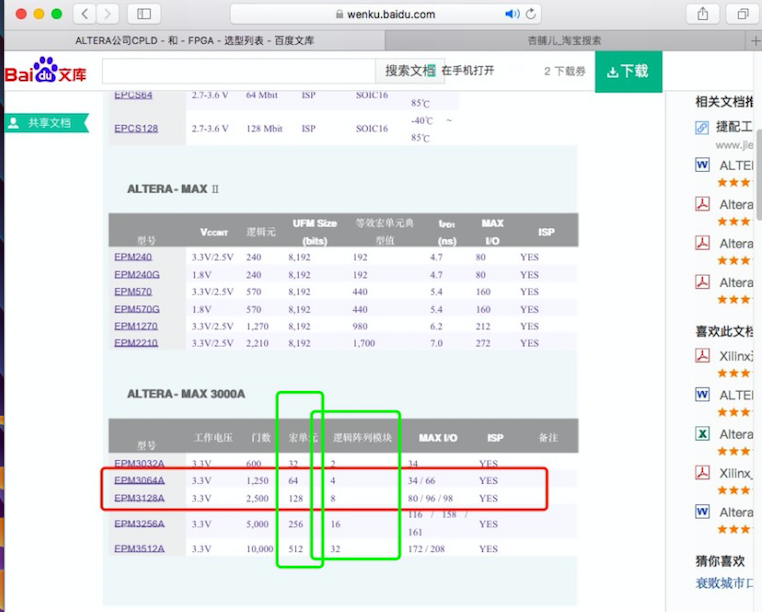

ALTERA公司CPLD_和_FPGA_选型列表(2012年):

但是淘宝有大量的货,价格也是几块钱,门很多。

https://wenku.baidu.com/view/1db565dfc1c708a1284a44de.html

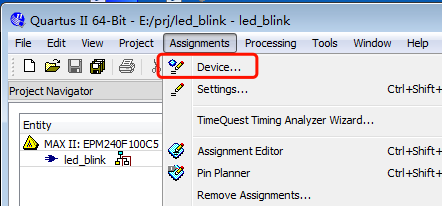

/files/members/719/WX20190422-090628.png你要看逻辑单元数量,门数量没用。epm240是240个,3032才32个,一下下就艹爆了

求科普项目开发评估选型流程。

是不是先用模拟器或者数量大的芯片开发完,再评估选取性价比最高,需求最接近的芯片?

#65 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 学习fpga的妈妈cpld » 2019-04-22 11:55:44

posystorage wrote:

Jin劲 wrote:

posystorage wrote:

这个芯片我也在玩 还是挺不错的 便宜大碗

嗯嗯 学习成本不错,就是门有点不够,想做点大东西不行。

所以我想换一个老的芯片 epm3000a系列,好像停产了,quartus ii 11不支持了。

ALTERA公司CPLD_和_FPGA_选型列表(2012年):

但是淘宝有大量的货,价格也是几块钱,门很多。

https://wenku.baidu.com/view/1db565dfc1c708a1284a44de.html

/files/members/719/WX20190422-090628.png你要看逻辑单元数量,门数量没用。epm240是240个,3032才32个,一下下就艹爆了

那么只能上更贵的芯片了

#66 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 学习fpga的妈妈cpld » 2019-04-22 09:08:00

posystorage wrote:

这个芯片我也在玩 还是挺不错的 便宜大碗

嗯嗯 学习成本不错,就是门有点不够,想做点大东西不行。

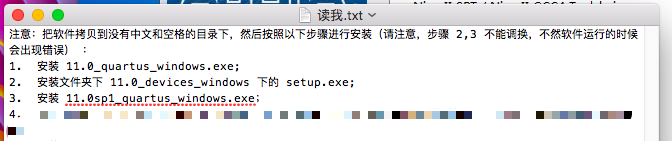

所以我想换一个老的芯片 epm3000a系列,好像停产了,quartus ii 11不支持了。

ALTERA公司CPLD_和_FPGA_选型列表(2012年):

但是淘宝有大量的货,价格也是几块钱,门很多。

https://wenku.baidu.com/view/1db565dfc1c708a1284a44de.html

#67 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 学习fpga的妈妈cpld » 2019-04-20 16:14:51

Jin劲 wrote:

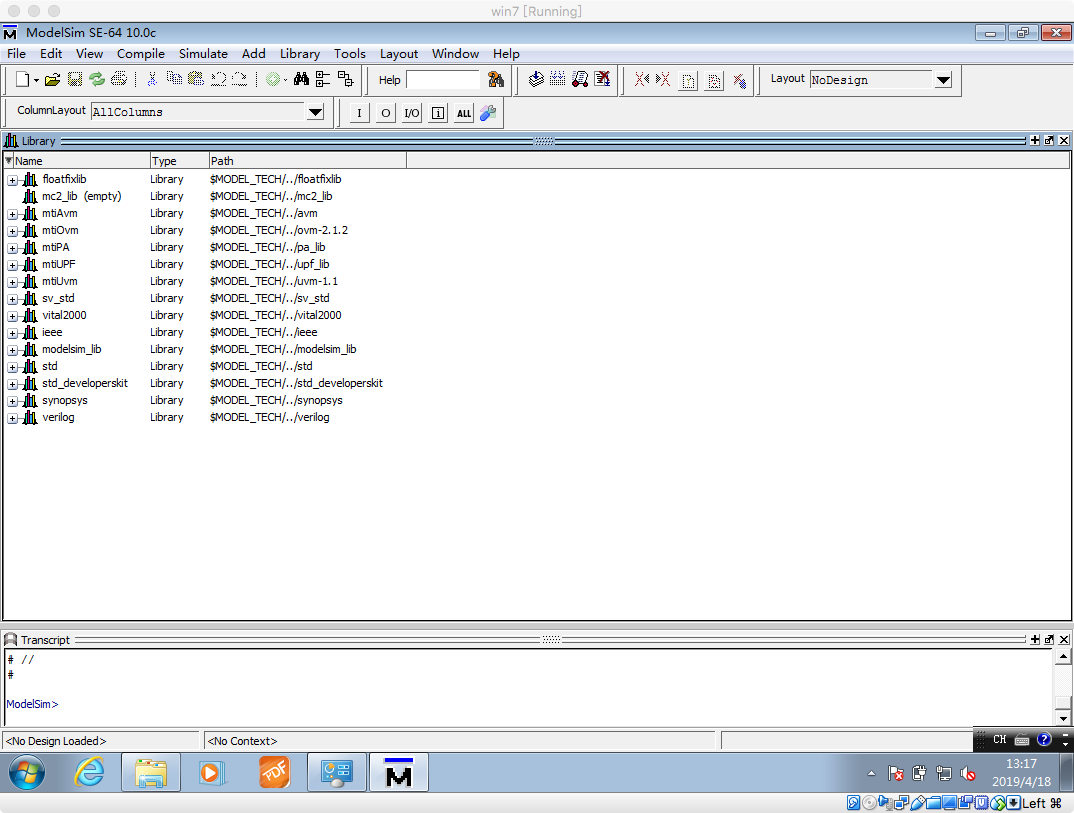

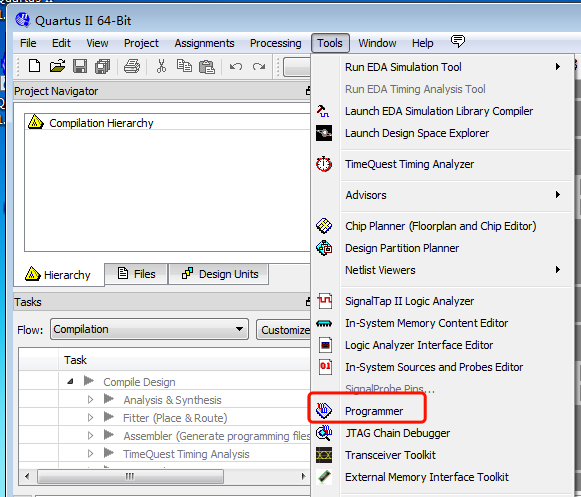

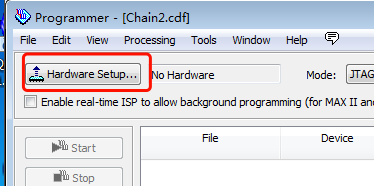

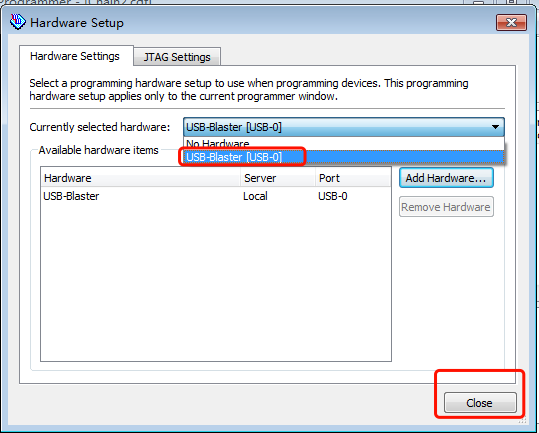

新版的quartus2删除了仿真功能,需要利用modelsim进行仿真:

/files/members/719/QQ20190418-130043.png

/files/members/719/QQ20190418-131709.png

https://wenku.baidu.com/view/d2cf37844afe04a1b071dee9.html 一个不错的教程

#76 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 学习fpga的妈妈cpld » 2019-04-17 15:40:24

找到个epm240实验书不错:

https://www.docin.com/p-702126460.html

#81 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 学习fpga的妈妈cpld » 2019-04-17 14:09:51

芯片手册:

MAX-.pdf

原理图:

epm240.pdf

#83 Re: 全志 SOC » v3s 接SPI 1602点阵液晶,有做过的朋友吗? » 2019-04-16 17:38:57

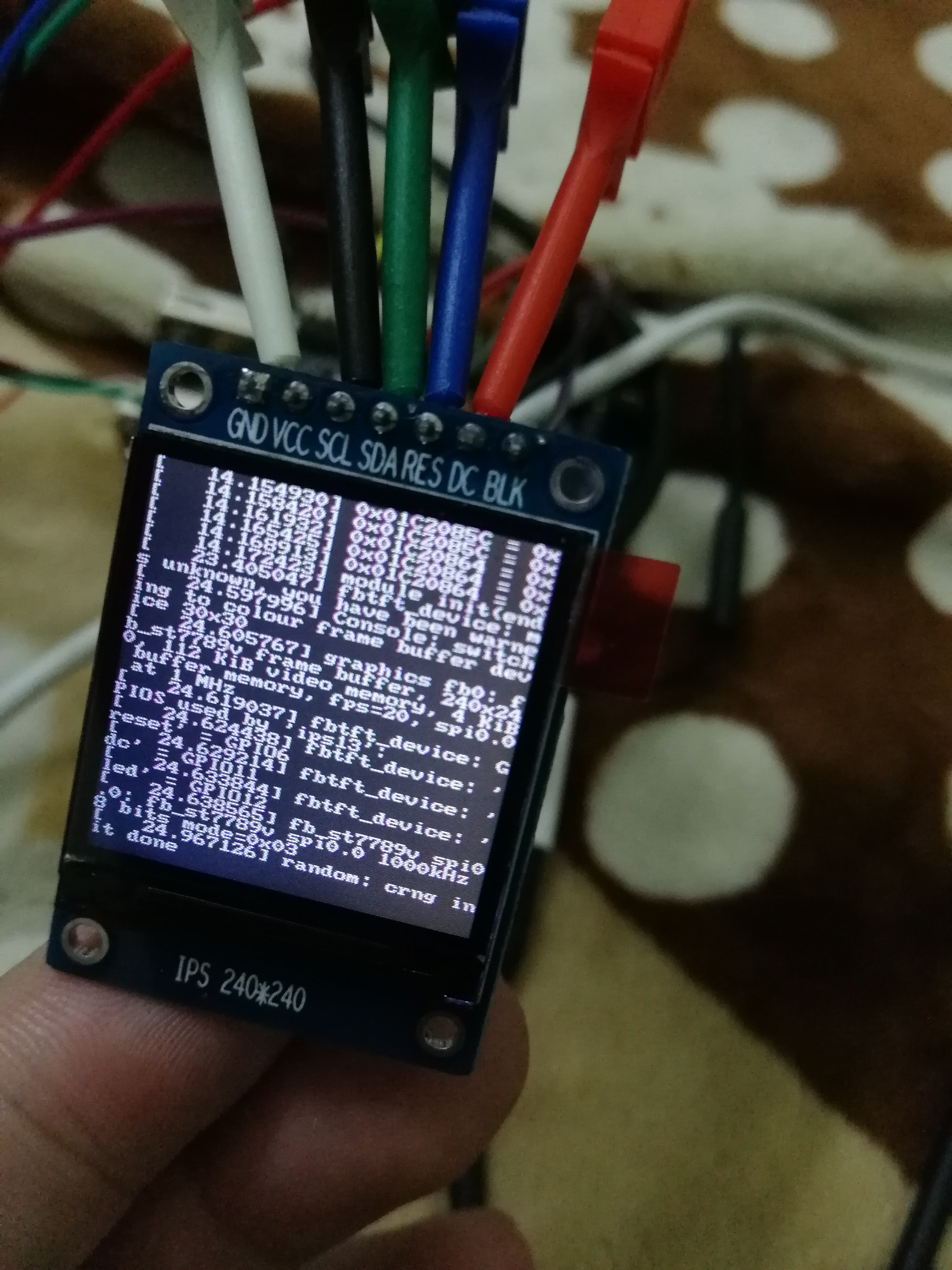

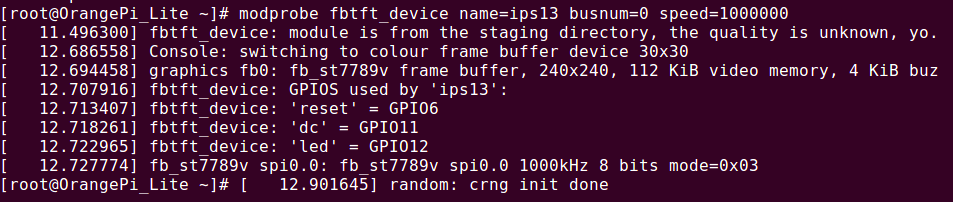

https://whycan.cn/t_2340.html 看看我这个对你有帮助不 fbtft

#86 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 【全新原件】投影机镜头模组 1.5 TFT-LCD迷你小型投影机镜头模组 12元,有没有人玩? » 2019-04-15 13:19:53

ybbrdfxk0922 wrote:

TPG121-V1_7.pdf

这个是从别的网站上找的统宝屏的配置,大概试了下,只要配置寄存器2,模式选择 through模式,,寄存器3 ,non-interlace(时序相对简单),就可以正常点亮了。

问题:1.就是rgb delta的屏好像颜色排序不一样。奇行偶行不一样,需要区别对待。但是选择through模式后,好像横向只有480/3=160个点了。第一次玩屏,懵逼中,有懂的讲解下呗

2.参照上面的手册,好像可以直接输出YUV的方式。刚试了下,好像是可行的。但是第一次玩,只会用FPGA刷全色。/files/members/860/none.jpg

这个是通过SPI口回读的寄存器配置。

/files/members/860/RGB_Delta.jpg

rgb delta的问题

/files/members/860/none_20190413-1628.jpg

需要配置的值

有接那些cp3-cp8等引脚的各种电容吗

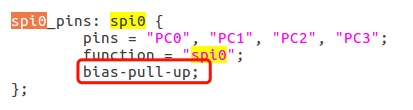

#87 Re: 全志 SOC » 使用h3跑linux上的fbtft,出现spi通信错误 » 2019-04-14 00:05:38

#89 Re: 全志 SOC » 使用h3跑linux上的fbtft,出现spi通信错误 » 2019-04-13 09:01:34

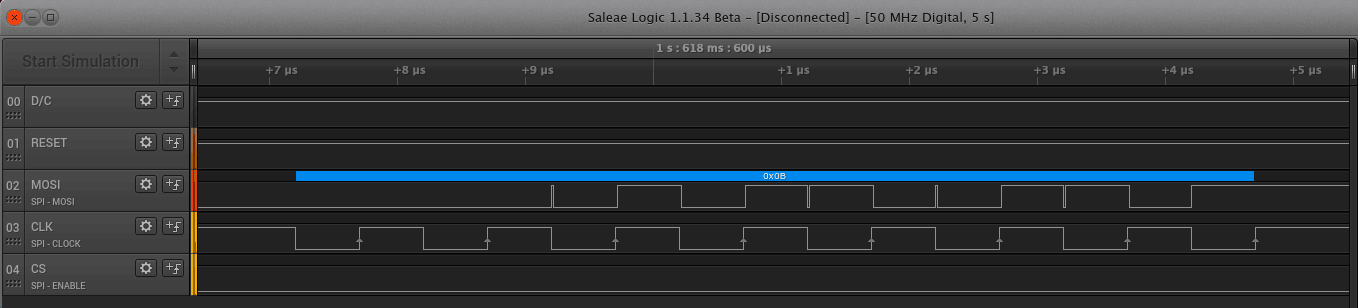

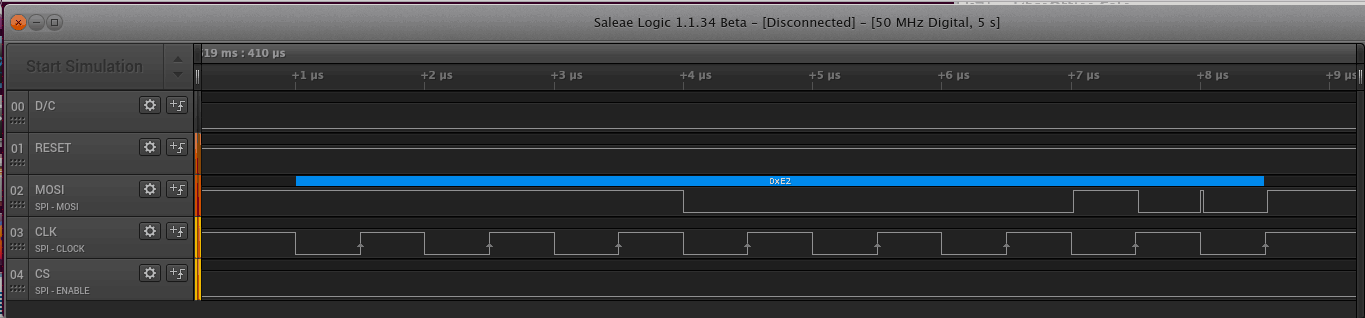

#91 全志 SOC » h3的硬件spi出现通信间隔时间很长的问题 » 2019-04-11 19:42:23

- Jin劲

- 回复: 2

#92 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 【全新原件】投影机镜头模组 1.5 TFT-LCD迷你小型投影机镜头模组 12元,有没有人玩? » 2019-02-19 21:37:01

#93 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 【全新原件】投影机镜头模组 1.5 TFT-LCD迷你小型投影机镜头模组 12元,有没有人玩? » 2019-02-19 20:53:02

#94 Re: Php/Nodejs/Web/HTML5/Javascript/微信开发/Python » Ubuntu 搭建Python Tk 开发平台 » 2019-02-12 17:23:10

山无棱 wrote:

Jin劲 wrote:

/files/members/719/2019-02-12-17-04-17.png

/files/members/719/2019-02-12-17-05-37.png

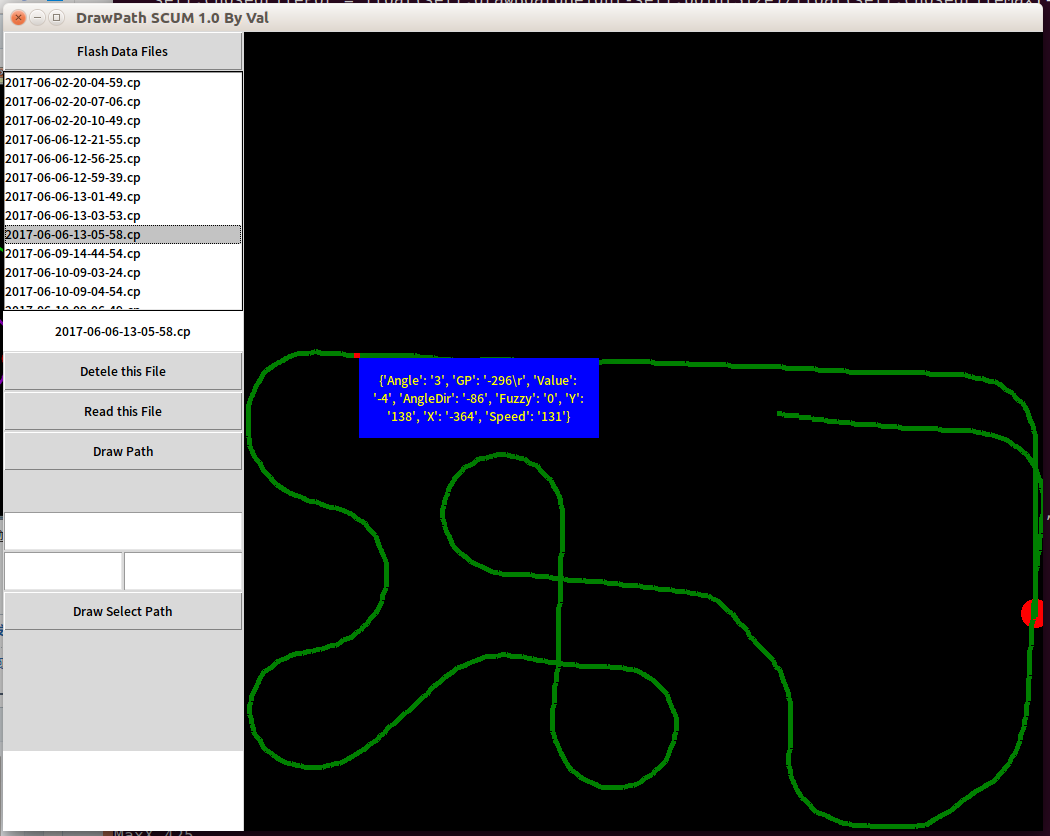

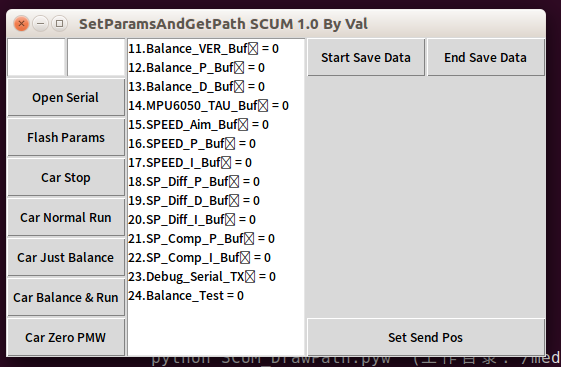

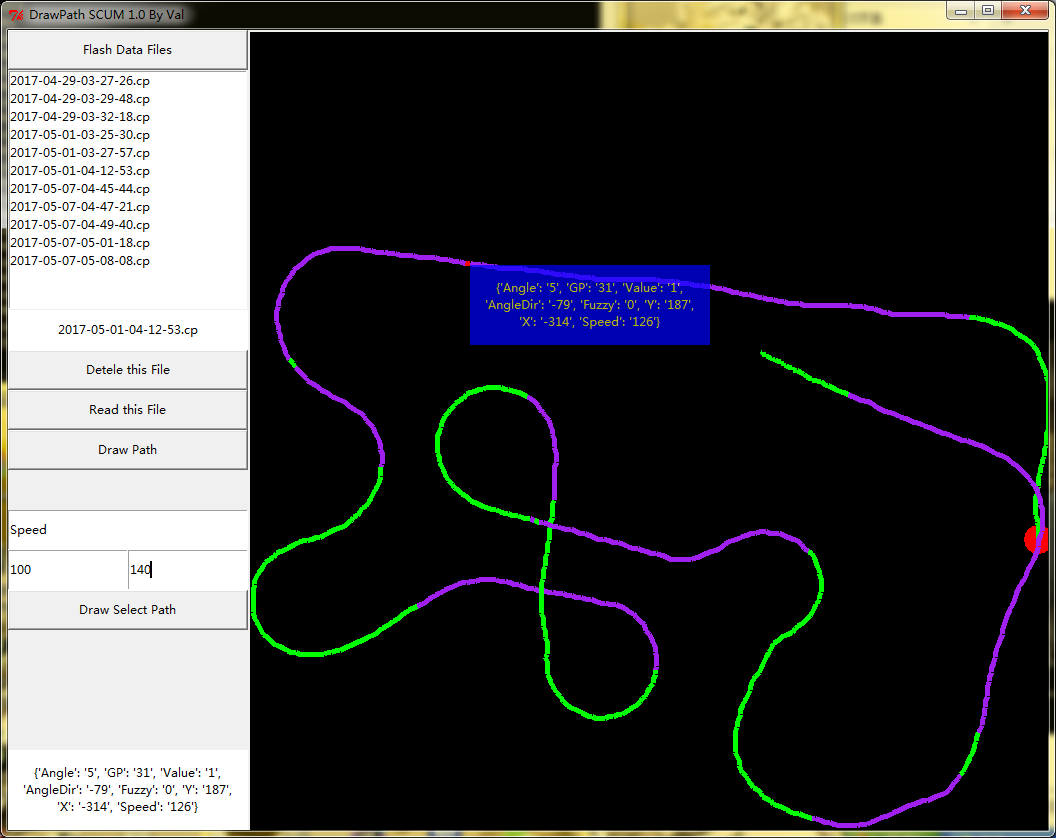

试了一下 还能打开 看到轨迹有点漂移

有漂移是正常,因为没有用电子罗盘修正航偏角,但是图上这么大的漂移其实是我的IMU融合搞得不好,我的师弟把我的融合改成四元素之后,漂移用这个上位机是看不出来的好厉害,

这是 GUI是 tkinter 组建做的?

就是python内置的tkinter

#98 Re: 全志 SOC » 刚买了荔枝nano,怎么入门。以前是一直搞单片机的。 » 2019-01-27 19:03:56

#100 Re: 全志 SOC » F1C100S原理图PCB可直接打样 » 2019-01-24 18:53:23

#101 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 占用一个位置 » 2019-01-24 17:23:17

晕哥 wrote:

/files/members/3/20190124172009.png

/files/members/3/20190124172022.png

chrome 版本 71.0.3578.98(正式版本) (32 位)

插件可以装上, 但是显示无法启动, 关闭那个按钮也是灰色的。

chrome没有开发者账号进行包发布,所以不能直接拖入安装(可见360等国产浏览器把chrome的安全部分去掉了),参照上面帖子加载已解压程序试试。

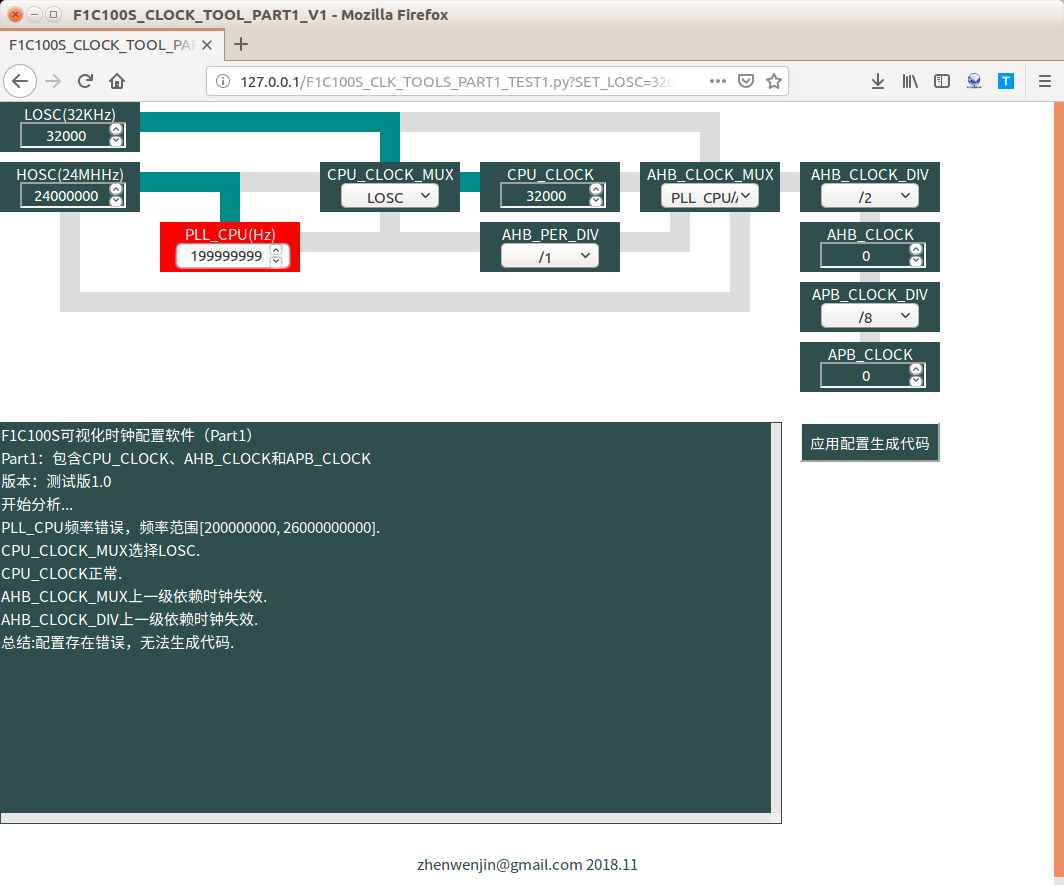

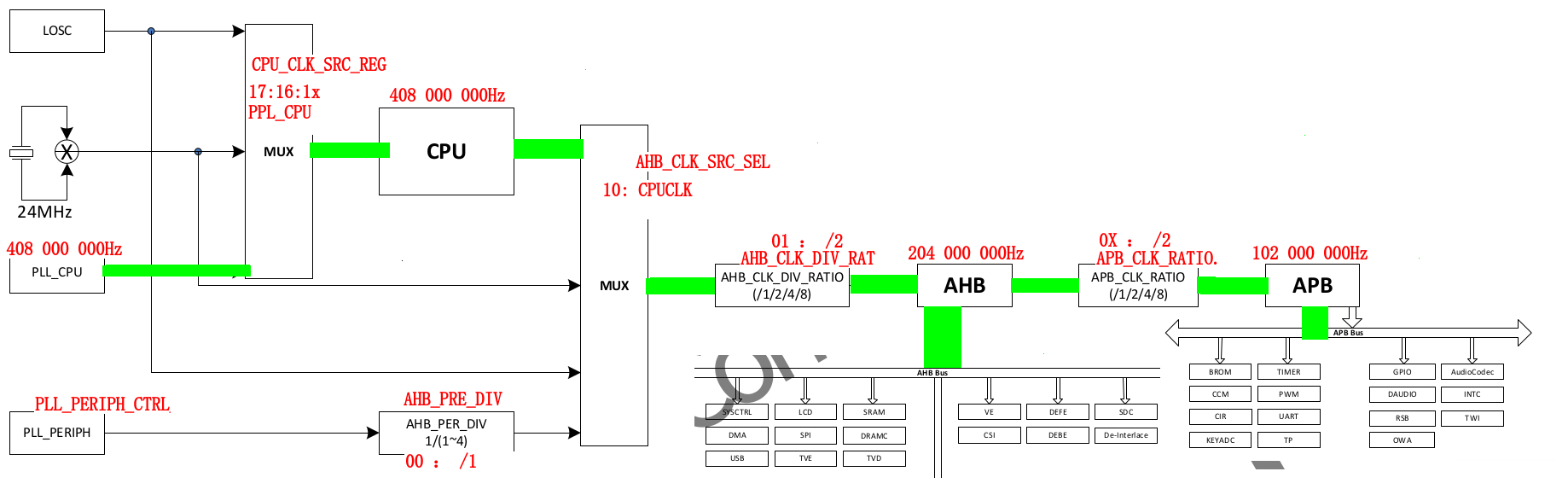

#102 Re: 全志 SOC » linux 主线内核荔枝派F1C100s 超频 » 2019-01-24 17:03:00

http://202.182.105.251:3721/

试试俺这个工具

#104 Re: 全志 SOC » F1c200s芯片也到了,晒晒 » 2019-01-24 12:01:43

#105 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 占用一个位置 » 2019-01-23 22:09:32

#106 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 占用一个位置 » 2019-01-23 22:05:30

#107 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 占用一个位置 » 2019-01-23 22:01:19

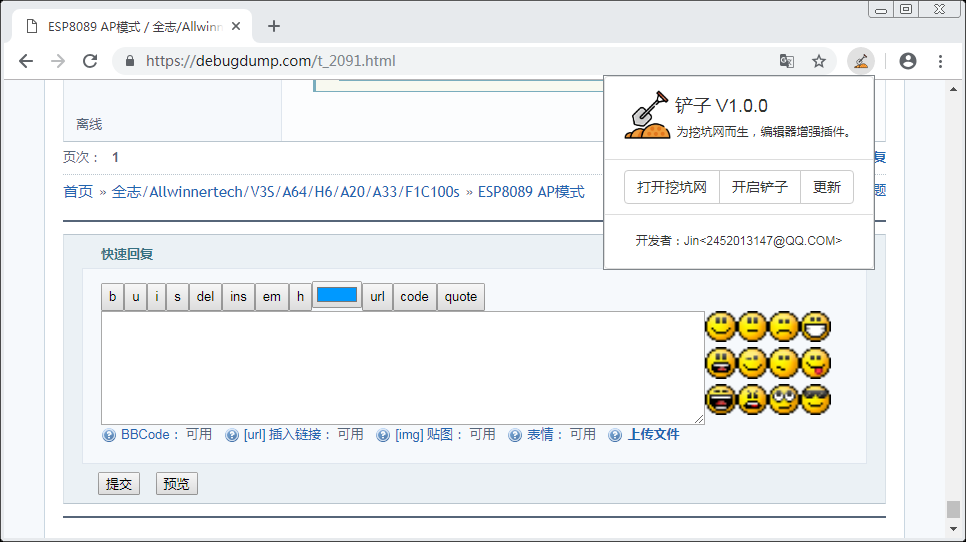

V1.0.0下载: shovel.zip

#108 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 占用一个位置 » 2019-01-23 21:51:44

铲子

挖坑网chrome内核浏览器增强插件

增强功能:

1.编辑器增强,再也不用手写代码,选中文本,点击按钮,自动插入;

2.表情功能,点击直接插入;

支持标签:

粗体文本 生成 粗体文本

下划线文本 生成 下划线文本

斜体文本 生成 斜体文本

中划线文本生成 中划线文本

删除的文本生成 删除的文本插入的文本 生成 插入的文本

强调的文本 生成 强调的文本

红色文本 生成 红色文本

蓝色文本 生成 蓝色文本

标题文本

生成

DebugDump Forum 生成 DebugDump Forum

此处是您准备引用的发言。

这里是一段源代码内容。

#110 Re: 全志 SOC » F1C100S裸奔framebuffer+PWM+GPIO驱动 » 2019-01-23 13:45:37

#111 Re: 全志 SOC » F1C100S原理图PCB可直接打样 » 2019-01-21 22:21:47

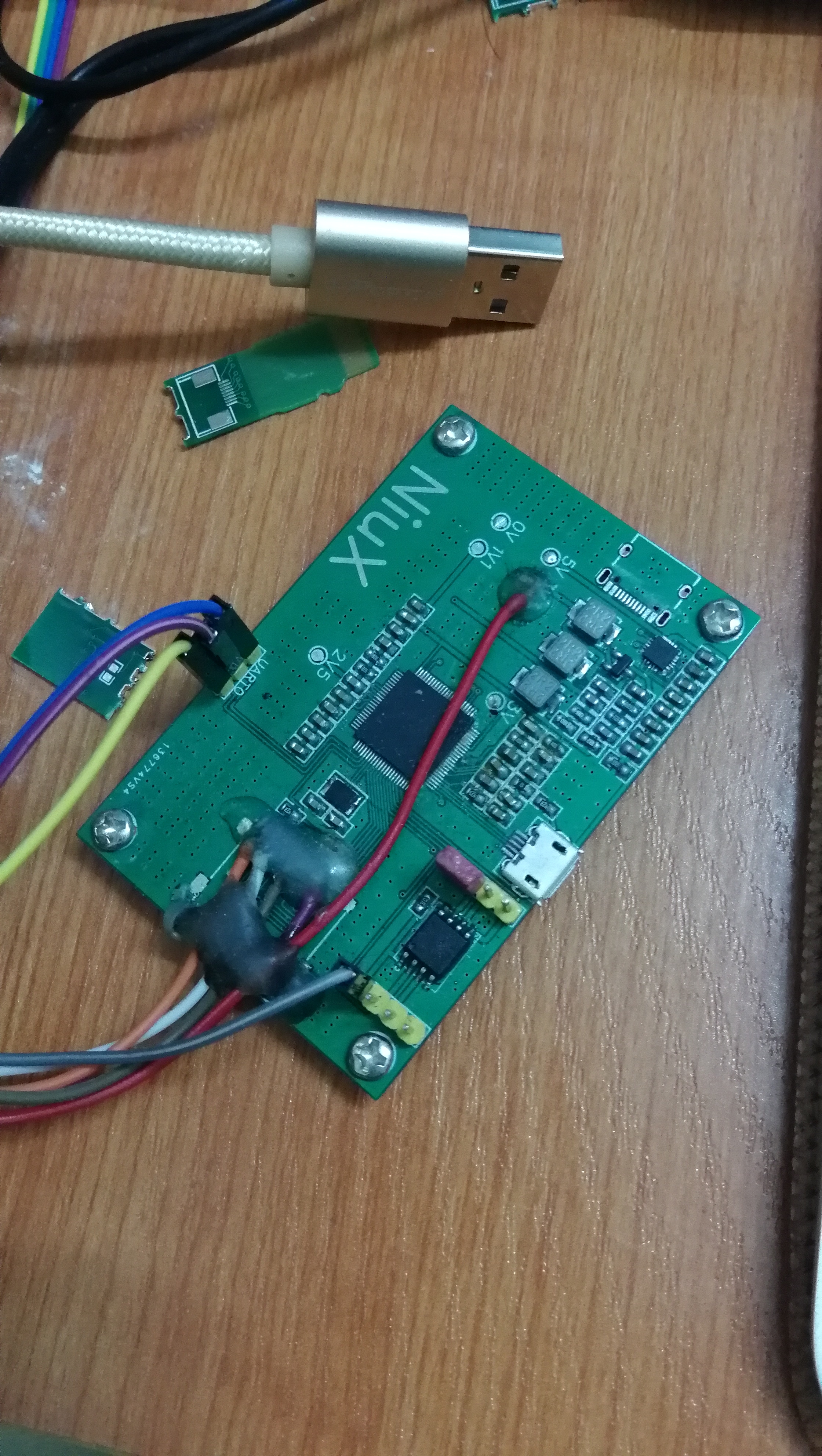

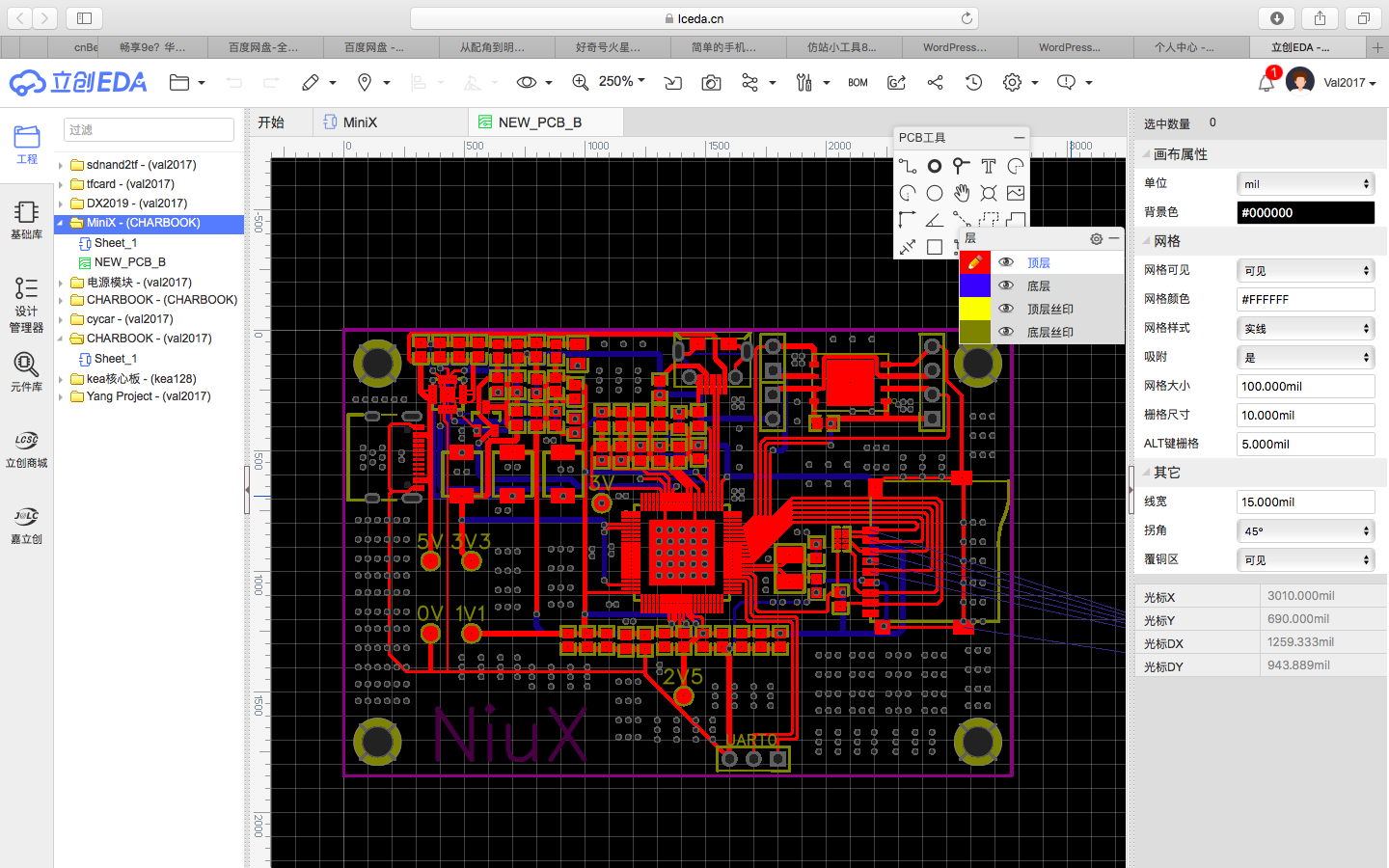

#112 全志 SOC » F1C100S原理图PCB可直接打样 » 2019-01-21 22:02:01

- Jin劲

- 回复: 55

#113 Re: 全志 SOC » 分享一个生死未卜的SDNAND2TF的PCB工程 » 2019-01-21 12:11:33

#114 Re: 全志 SOC » 分享一个生死未卜的SDNAND2TF的PCB工程 » 2019-01-17 08:51:40

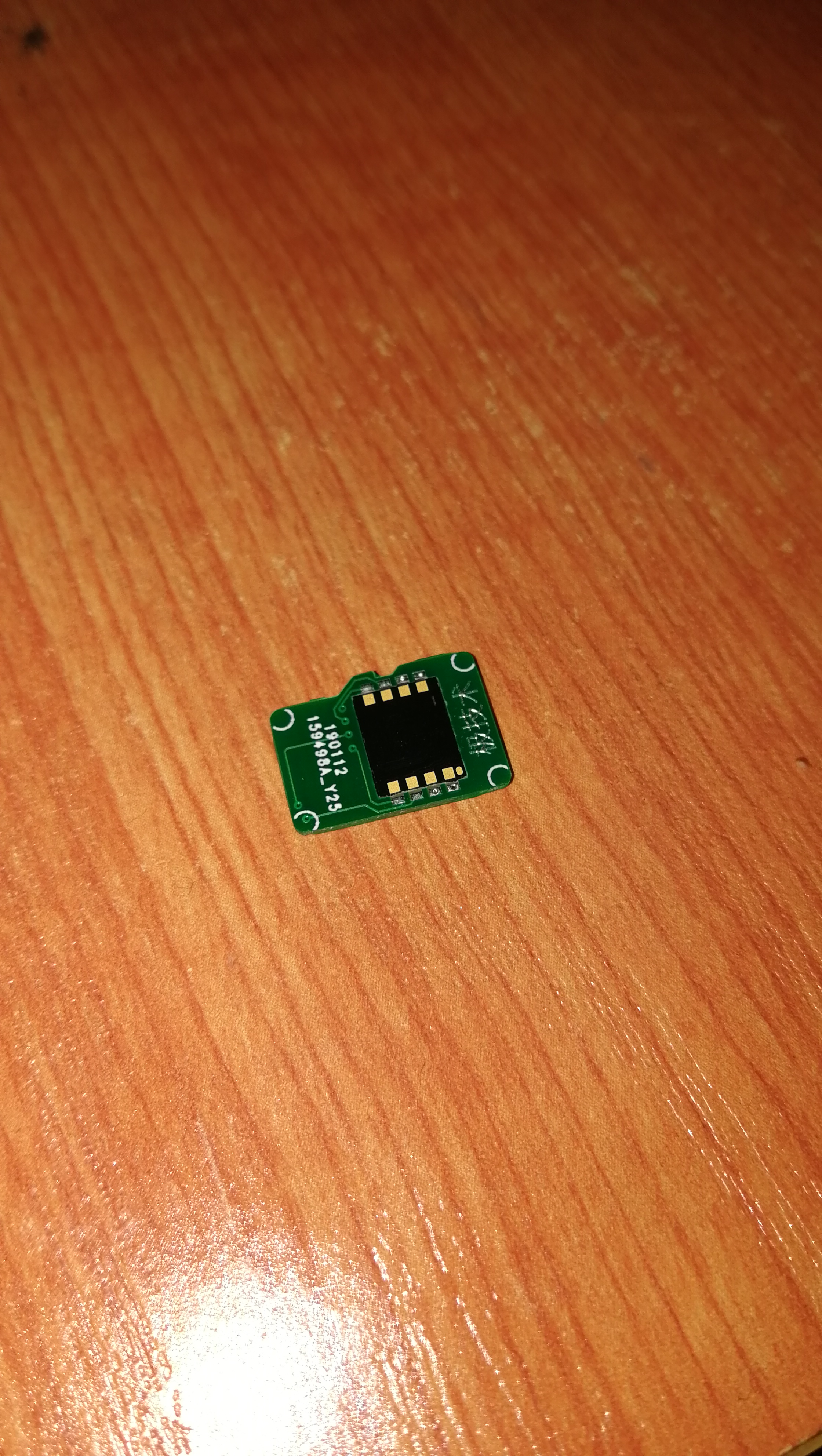

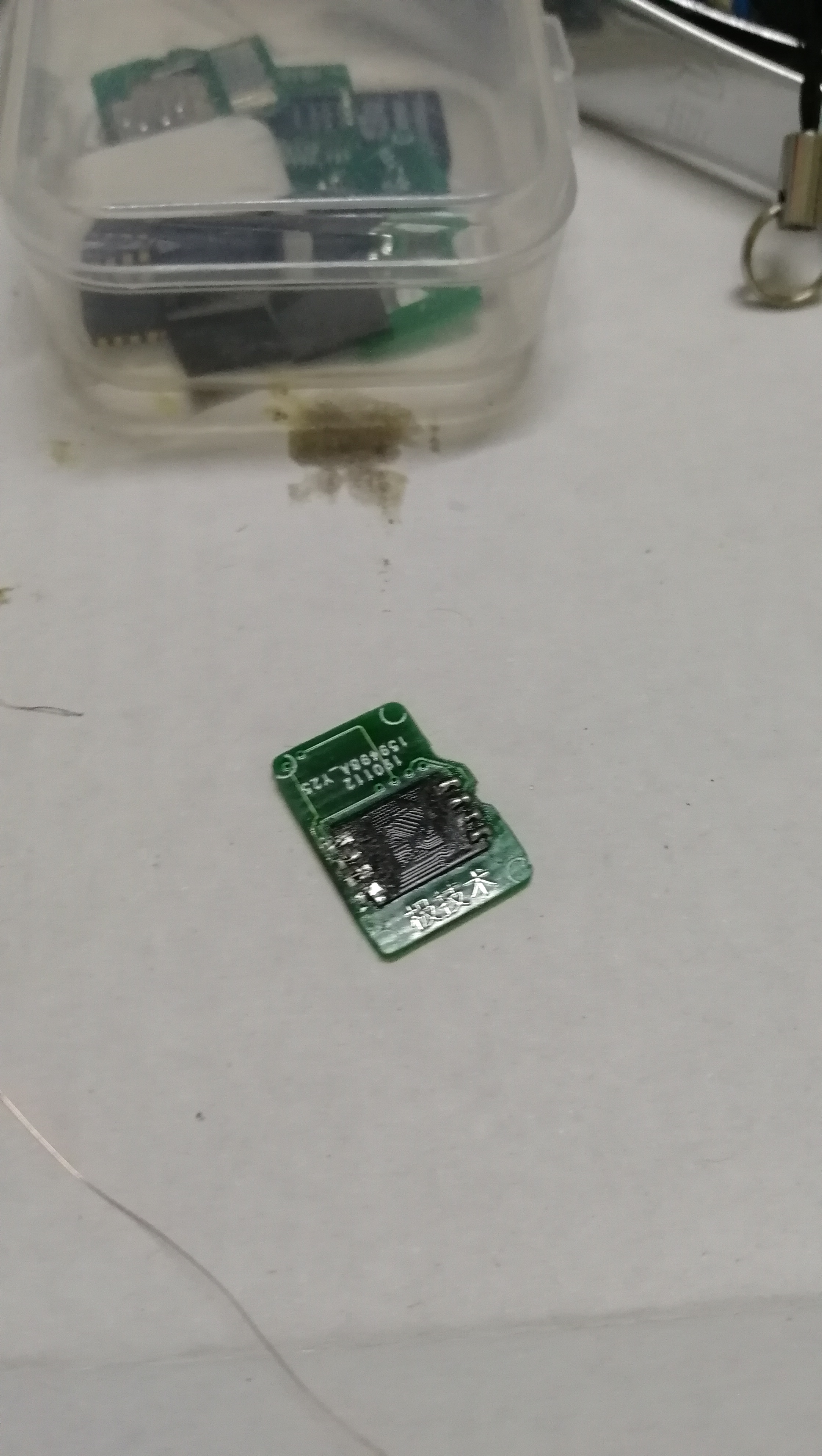

迪卡 wrote:

我可以转卖呀,嘻嘻,10元/片

你仔细看看俺的芯片 上面是不是有你的指纹[捂脸]

#115 Re: 全志 SOC » 分享一个生死未卜的SDNAND2TF的PCB工程 » 2019-01-16 13:55:54

雷龙发展q2852826868 wrote:

厉害,我们CS SD NAND 也有现成的转接板。

/files/members/1303/none.jpg

咱的芯片啥时候能淘宝零售啊

#116 Re: 全志 SOC » 分享一个生死未卜的SDNAND2TF的PCB工程 » 2019-01-16 09:38:18

#117 Re: 全志 SOC » 分享一个生死未卜的SDNAND2TF的PCB工程 » 2019-01-15 09:34:11

#118 全志 SOC » 分享一个生死未卜的SDNAND2TF的PCB工程 » 2019-01-15 09:16:37

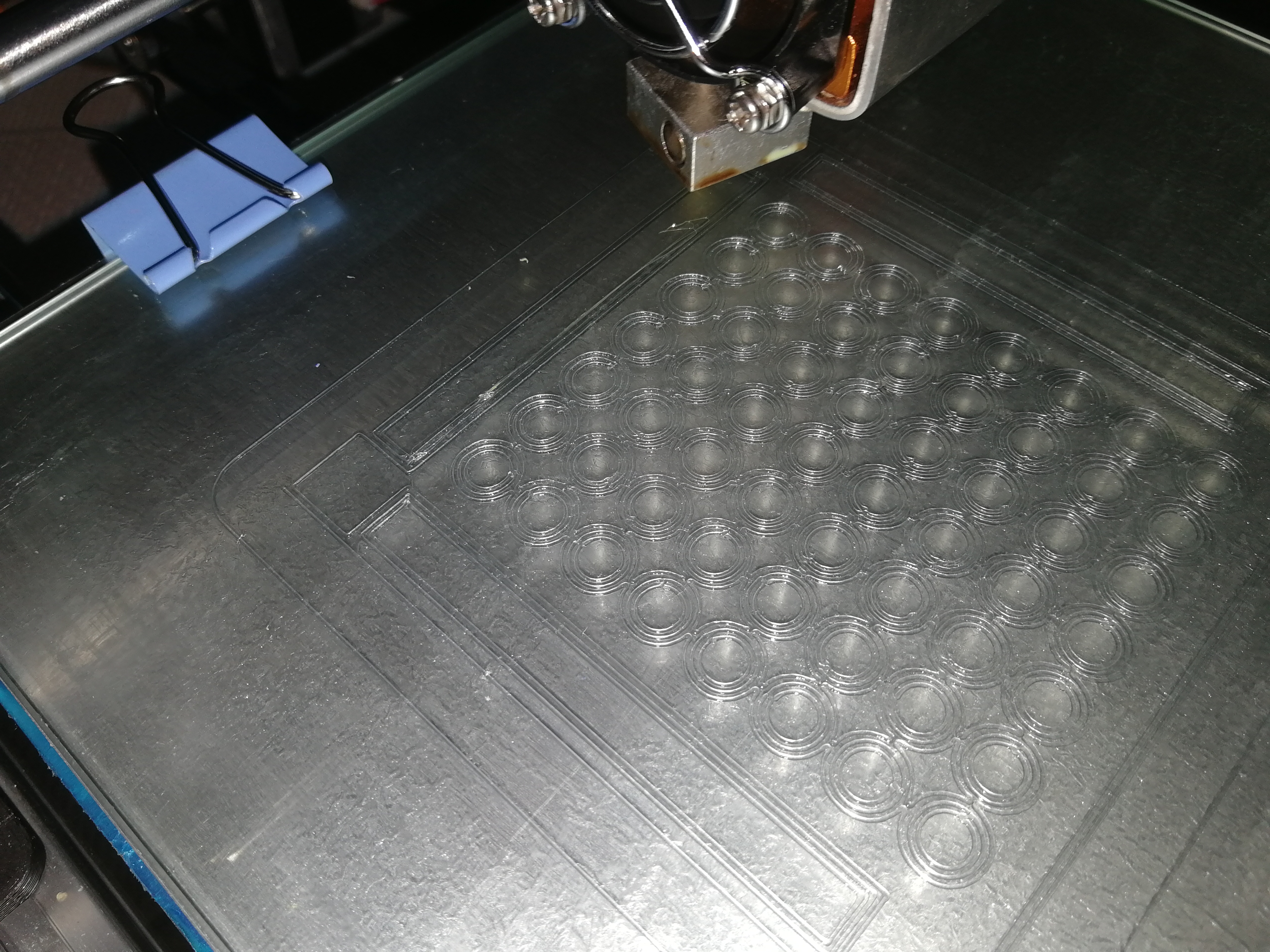

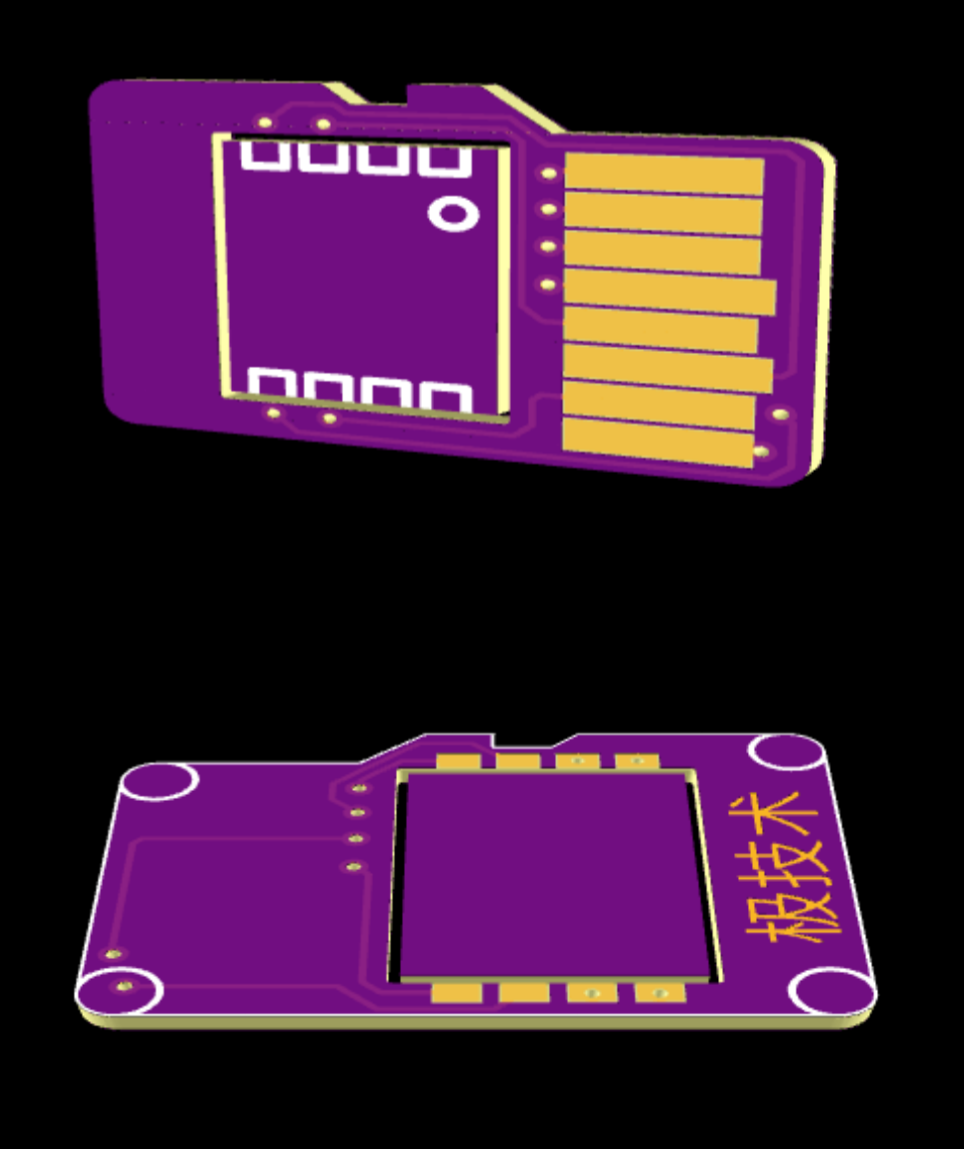

- Jin劲

- 回复: 15

!!!焊接问题,未验证!!!

尺寸都是对的,就是焊接问题暂时没法验证。

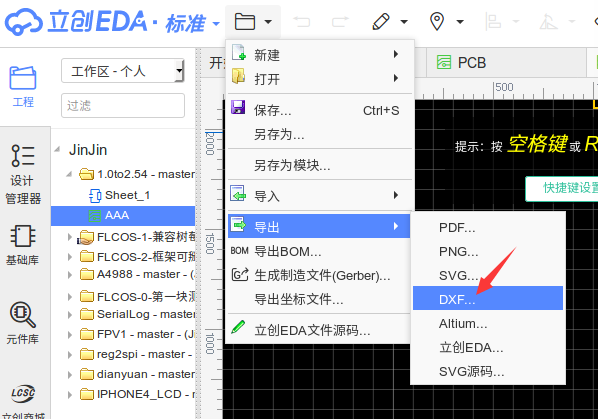

使用lceda画的导入就行。

下载: /files/members/719/Project_sdnand2tf_20190115090018.zip

#121 Re: ST/STM8/STM8S/STM8L » 第一次发现这个网站,这里做嵌入式的兄弟多吗 » 2019-01-07 19:32:05

#125 DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 请教一下中断延迟Interrupt Latency 测这个时间代码逻辑流程应该怎么写 » 2018-11-22 15:47:26

#126 Re: 全志 SOC » 在线配置F1C100S工具求测试 » 2018-11-14 09:35:38

#127 Re: 全志 SOC » 在线配置F1C100S工具求测试 » 2018-11-14 09:33:26

#128 Re: 全志 SOC » 在线配置F1C100S工具求测试 » 2018-11-14 09:21:01

#129 Re: 全志 SOC » F1C100S如何用晕哥的Keil裸机工程加载程序进DRAM » 2018-11-13 09:15:58

#130 Re: 全志 SOC » F1C100S如何用晕哥的Keil裸机工程加载程序进DRAM » 2018-11-13 08:51:10

#131 全志 SOC » 在线配置F1C100S工具求测试 » 2018-11-12 10:53:28

- Jin劲

- 回复: 10

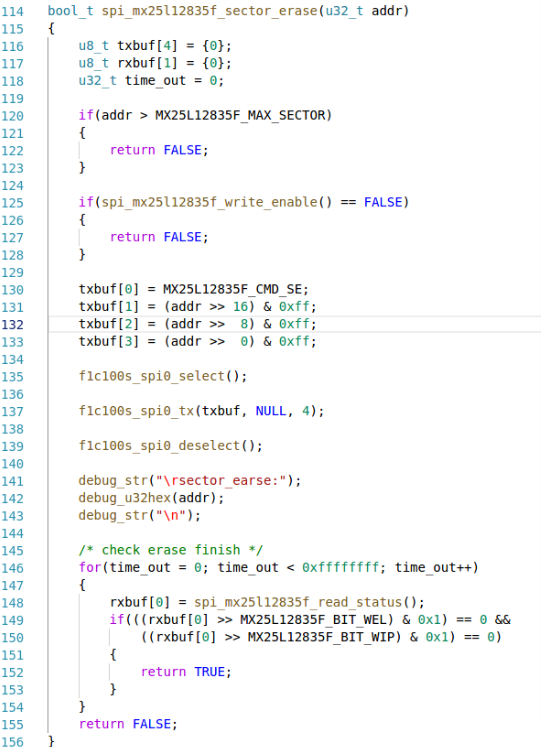

#133 Re: 全志 SOC » 为啥我只能擦nor的0和fff扇区 » 2018-11-08 10:33:30

#134 Re: 全志 SOC » 为啥我只能擦nor的0和fff扇区 » 2018-11-08 08:58:08

#135 Re: 全志 SOC » 为啥我只能擦nor的0和fff扇区 » 2018-11-07 11:49:30

#136 Re: 全志 SOC » 为啥我只能擦nor的0和fff扇区 » 2018-11-07 09:04:44

#137 全志 SOC » 为啥我只能擦nor的0和fff扇区 » 2018-11-07 09:02:24

#138 Re: Cortex M0/M3/M4/M7 » 关于6轴惯性模块的姿态解算问题请教 » 2018-10-23 13:48:27

#139 Re: Cortex M0/M3/M4/M7 » 关于6轴惯性模块的姿态解算问题请教 » 2018-10-23 11:09:16

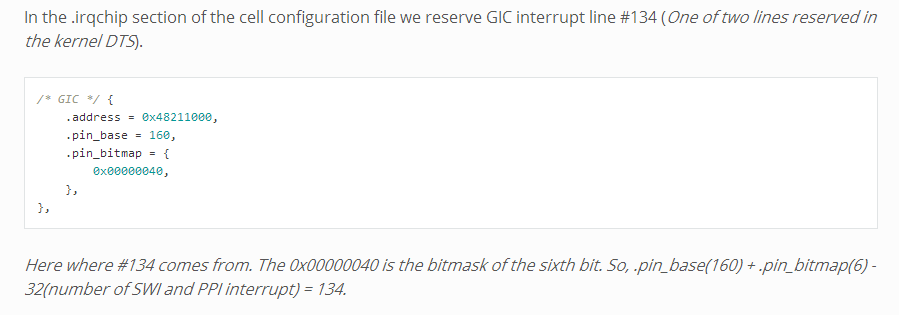

#141 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 请教一下这个ARM GIC怎么计算的 » 2018-10-09 14:56:40

Jin劲 wrote:

不知道发这个会不会和晕哥一起请去喝茶

#146 Re: RISC-V » 最权威的 RISC-V 汇编程序员手册 » 2018-09-18 13:54:32

#147 Re: RISC-V » 最权威的 RISC-V 汇编程序员手册 » 2018-09-18 09:58:52

#148 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 跟风拼多多买了一个手表,希望也是MT6260的. » 2018-09-13 23:27:59

#150 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 拼多多手表2(mt6260)目前进展与遇到一些困难 » 2018-09-09 17:55:13

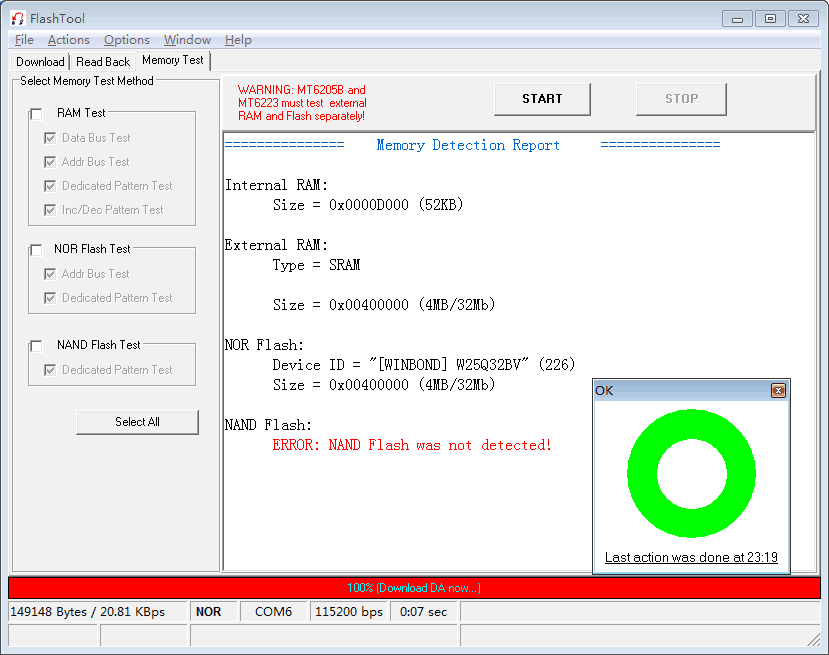

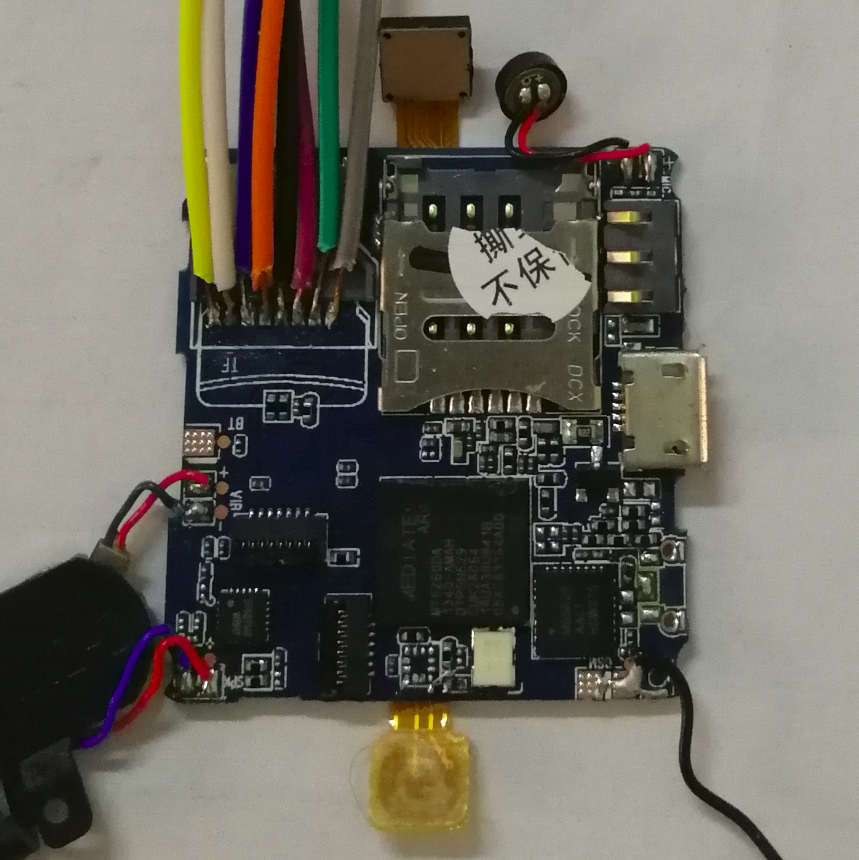

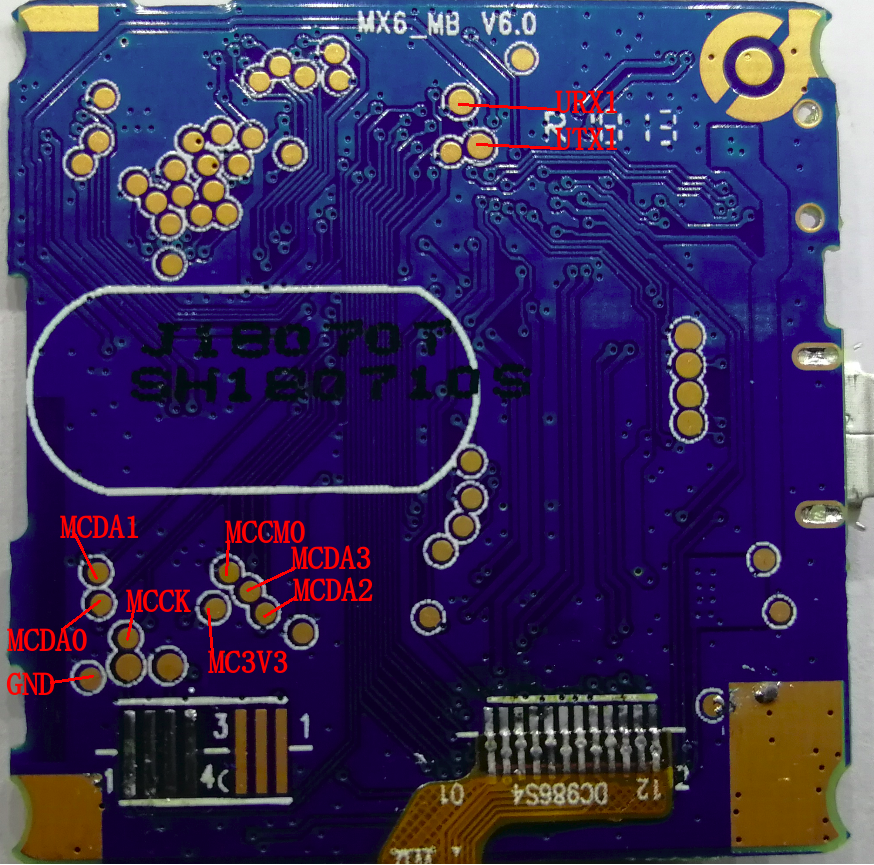

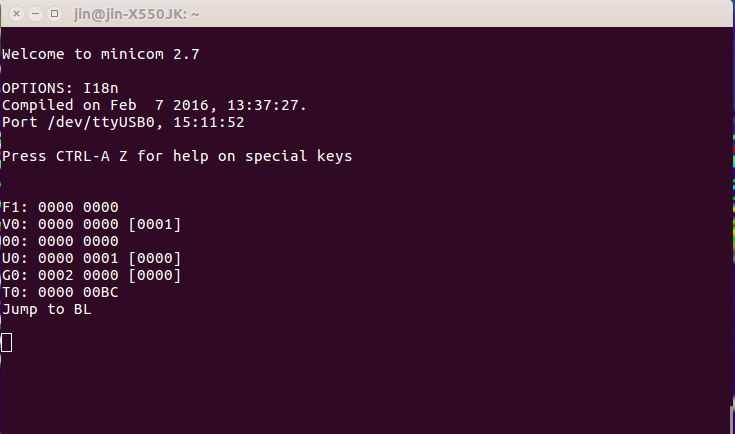

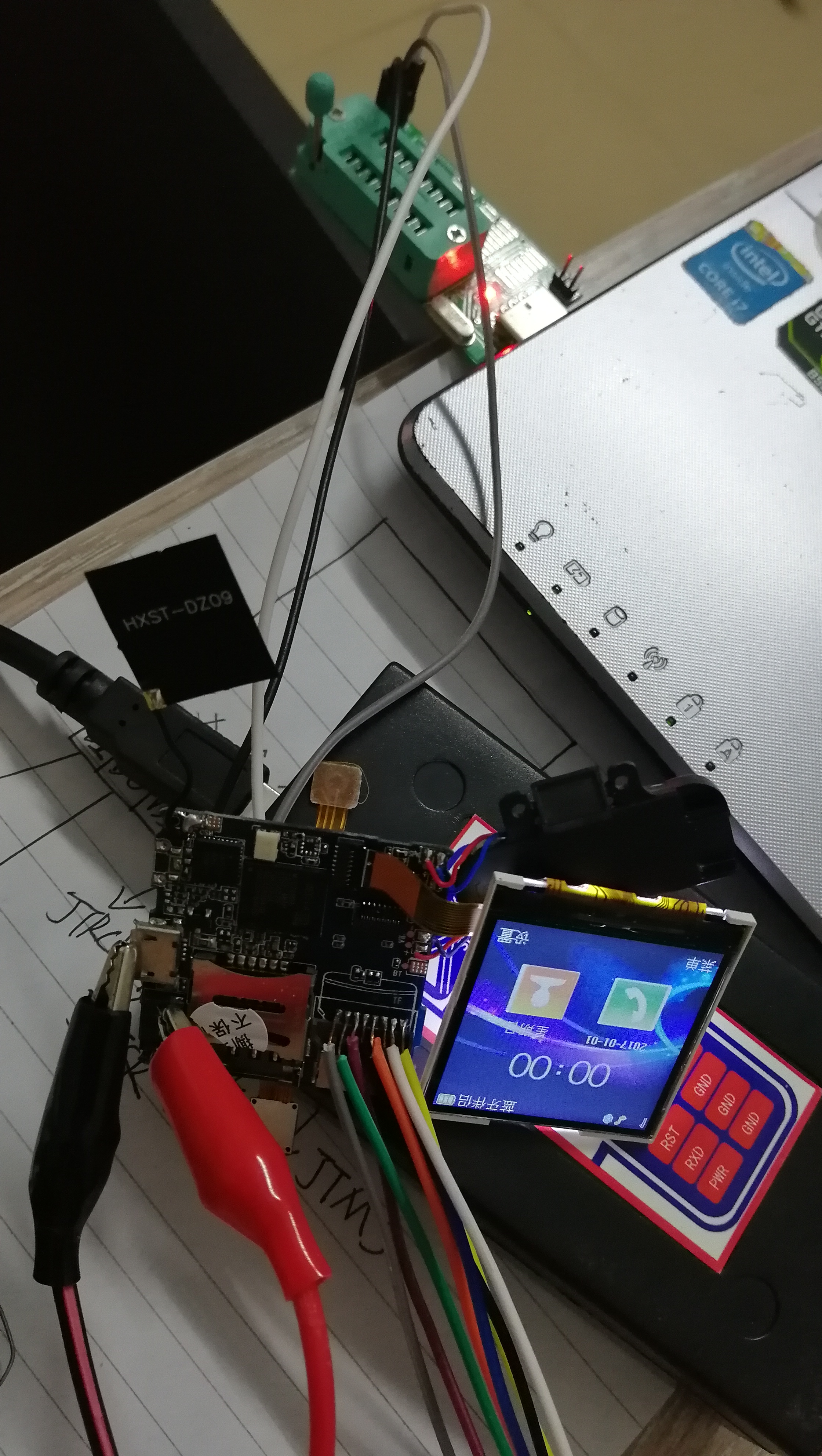

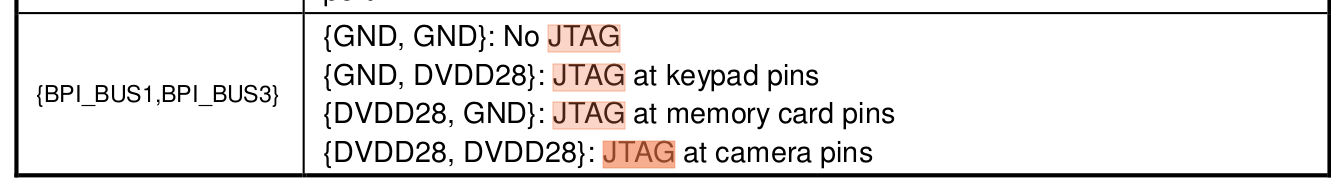

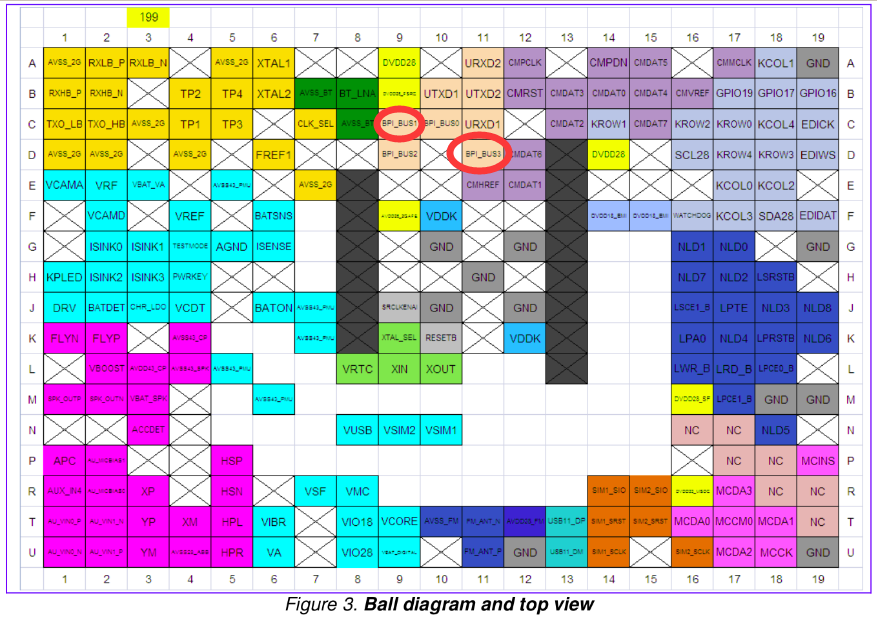

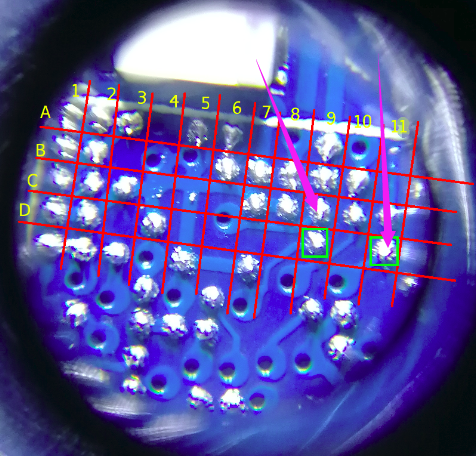

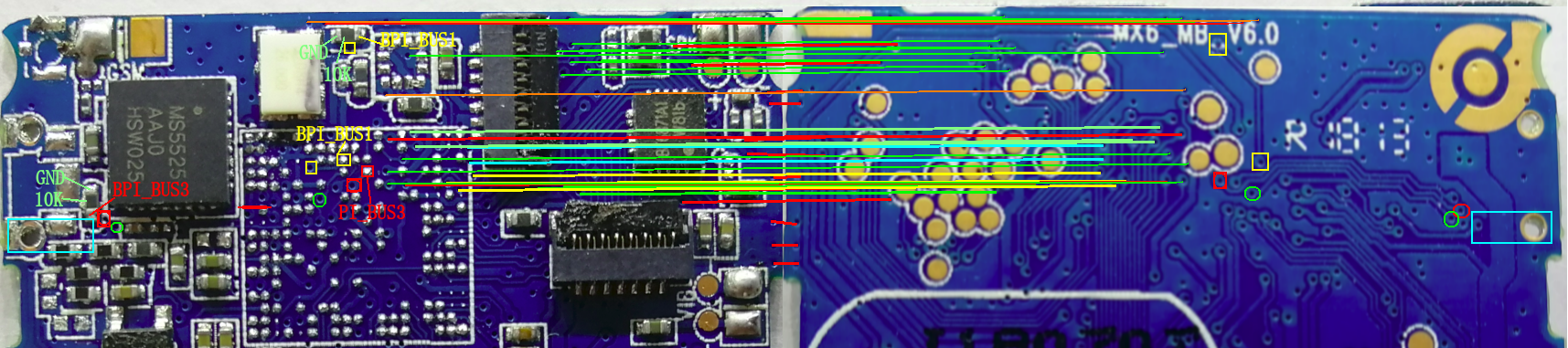

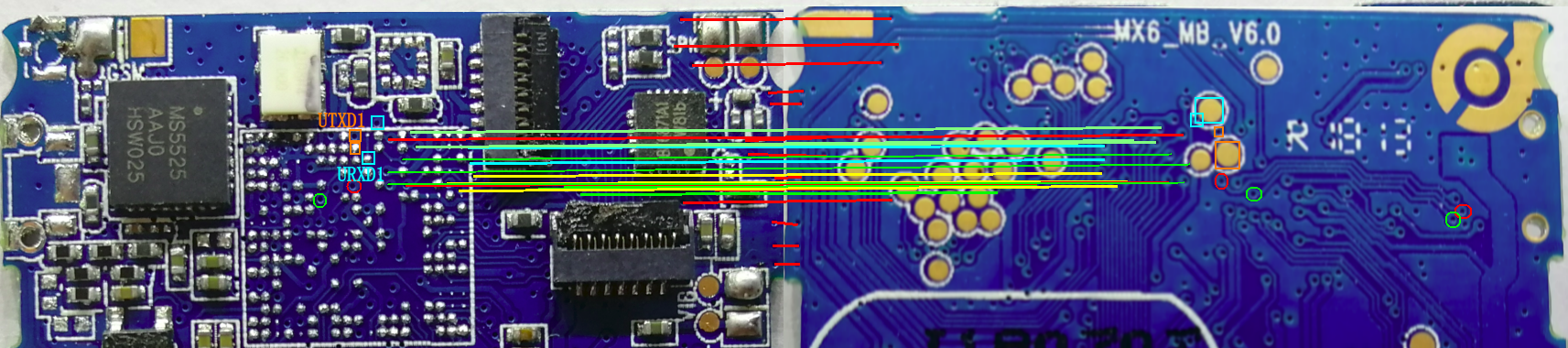

目前遇到的困难:

还没有拿下jtag

可能原因是datasheet写着,系统启动时,jtag的gpio的mode寄存器的默认值为0 也就是说没有配置为jtag引脚

可能需要编写一个引导程序烧写进去配置好引脚才能使用jtag

没有mtk方面的经验,不知道如何编译,最终需要生成什么样的文件,如何烧写等

我看教程好像直接用usb线连接windows装好驱动,就能出现一个“串口”的东西,然后利用FlashTools进行Flash的操着,读出写入,但是我的手表连接到windows后,装好驱动,并没有出现“串口”的东西,更谈不上连接到FlashTools。

还有cfg文件 好像是分区表,希望有mtk经验的坑友给予帮助。

#151 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 拼多多手表2(mt6260)目前进展与遇到一些困难 » 2018-09-09 17:52:28

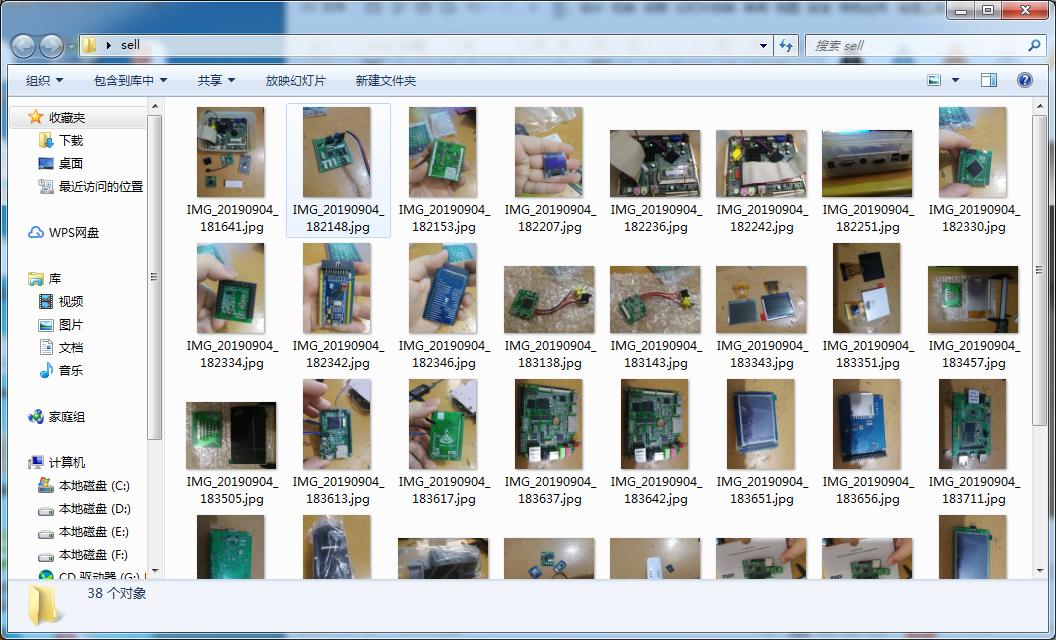

#152 DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 拼多多手表2(mt6260)目前进展与遇到一些困难 » 2018-09-09 17:50:22

#153 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2018-09-07 01:15:08

#154 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2018-09-07 00:00:07

#155 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2018-09-06 16:51:13

求转pdf 逼装大了 没有windows和这个画图软件

#156 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2018-09-06 16:27:35

#157 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2018-09-06 14:34:55

#158 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2018-09-06 13:37:43

#159 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 本站网友 劲哥 在【并夕夕】购买的 25.8 元联发科电话手表拆解,MT6260, ARM7EJ-S 内核. » 2018-09-06 10:50:50

#162 Re: 全志 SOC » F1C100S切换double buffer的显存时,会和帧同步吗? » 2018-08-29 10:57:12

#163 Re: 全志 SOC » 更便宜的F1C100s或V3S主板? » 2018-08-28 15:17:51

#164 Re: 全志 SOC » F1C100S切换double buffer的显存时,会和帧同步吗? » 2018-08-28 14:22:50

#165 Re: 全志 SOC » F1C100S切换double buffer的显存时,会和帧同步吗? » 2018-08-28 13:30:18

#166 Re: 全志 SOC » F1C100S切换double buffer的显存时,会和帧同步吗? » 2018-08-28 10:42:04

#167 Re: 全志 SOC » 买个全志arm9 F1C100s 方案的唱戏机回来拆一拆 » 2018-08-24 15:59:09

agnd wrote:

Jin劲 wrote:

晕哥 wrote:

据说热风枪 吹保修标签可以完整撕下 (逃

可以在tf卡位置怼一下jlink看一下芯片么

http://linux-sunxi.org/images/thumb/0/05/JTAG_MicroSD_UART-front.jpeg/180px-JTAG_MicroSD_UART-front.jpegRK2806也是ARM926EJ_s,外加一个DSP组成的双核,小心以假乱真啊

哇 异构多核

#168 Re: 全志 SOC » 买个全志arm9 F1C100s 方案的唱戏机回来拆一拆 » 2018-08-24 14:32:27

#169 Re: 全志 SOC » 大家希望S3模组使用什么接口引出?希望坛友脑爆一下 » 2018-08-23 15:16:13

mango wrote:

Jin劲 wrote:

可不可以这样呢(小白脑洞)

/files/members/719/-2018-08-21-5_25_22_20180821-0527.png达克罗德 wrote:

我倾向于原方案,少引三个脚算了

有思路了,感谢ing

板子扩宽1MM,正好可以装一个80PIN,将音频部分冗余引脚砍掉几个,应该可以解决了。

砍掉是不引出来了吗 弄几个没有阻焊的单面触点引出来不?

#170 Re: 全志 SOC » 大家希望S3模组使用什么接口引出?希望坛友脑爆一下 » 2018-08-23 11:54:41

#171 Re: Nuvoton N32905/N32926/NUC972/N9H20/N9H26/N9H30 » step by step 全志 f1c100s MDK 裸奔各种外设(参考N3290x) » 2018-08-22 17:08:31

#174 Re: ST/STM8/STM8S/STM8L » STM32F407换荔枝派 » 2018-08-21 16:53:57

#176 Re: 全志 SOC » f1c100s怎样才能timer产生并进入中断? » 2018-08-20 09:19:40

#178 Re: Nuvoton N32905/N32926/NUC972/N9H20/N9H26/N9H30 » 新唐的裸奔demo大全, 要是别的芯片都这么努力就好了! » 2018-08-18 18:23:32

#179 Re: 全志 SOC » 有一个疑惑了很久的问题 弱弱得问一下 » 2018-08-17 15:32:38

#180 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 今天打电话询问了腾讯和阿里,io和app后缀在国内无法备案 » 2018-08-17 11:39:28

mango wrote:

超级萌新 wrote:

.io为英国海外领地英属印度洋领地国家及地区顶级域(ccTLD)的域名。

IO既有“I/O”(输入/输出;Input/Output)的含义,

也可以作为“Internet Organization”(互联网组织)的缩写,

因此.io常被作为IT相关网站域名使用。作者:知乎用户

链接:https://www.zhihu.com/question/30090319/answer/118977446

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。估计是因为io属于别的国家/地区,所以不能备案.

是的,不管怎么说,IO的输入输出含义就是脑补,工信部不管这个。

搞活动,我用几十块钱注册10年的win域名,本来可以备案的,然后工信部出了公告,连org这种国际后缀的都不能备案了。

#181 Re: 全志 SOC » 有一个疑惑了很久的问题 弱弱得问一下 » 2018-08-17 10:26:45

#182 Re: 全志 SOC » 有一个疑惑了很久的问题 弱弱得问一下 » 2018-08-17 10:01:42

超级萌新 wrote:

https://whycan.cn/t_1003.html

这个就是 IAR f1c100s jlink调试的程序, 就是boot0吧。

看下有没有参考价值.

这个不是boot0 这个是已经执行了boot0初始化之后的代码 运行在dram的代码:

define symbol __ICFEDIT_intvec_start__ = 0x80000000;

和uboot主体是同一级别的

#183 Re: 全志 SOC » 有一个疑惑了很久的问题 弱弱得问一下 » 2018-08-17 09:46:58

#184 全志 SOC » 有一个疑惑了很久的问题 弱弱得问一下 » 2018-08-17 09:04:28

#185 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 不明白ti为什么这样做 » 2018-08-16 13:49:04

达克罗德 wrote:

Jin劲 wrote:

达克罗德 wrote:

结构体的声明只是声明,本身不占空间。

如果没有定义实例而是直接映射到寄存器空间,那么就不占空间,因为你寄存器本身就在那,把寄存器空间按照结构体来访问而已

如果是拷贝一份作为buffer,那是占空间,但有可能是方便软件维护typedef struct

{

uint8_t reg[4];

}reg_t;如果是这样的 映射到一个寄存器 可以按uint8_t大小访问吗 还是访问其中一个uint8_t内部实现是整个32位读出来 获取8位?

因为我看到有一些就是这样定义的 都是4字节对齐是的,ARM环境对uint8都是先读32位再取8位的

所以同理,定义变量时你用uint8_t, uint16_t效率是不高的,一般如果对省内存没要求的话,我都是定义32位变量。当然,因为你是映射寄存器,所以这样的reg_t是应该这样定义

定义变量时你用uint8_t, uint16_t效率是不高的 哇 又学到东西了

#186 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 不明白ti为什么这样做 » 2018-08-16 13:23:02

#187 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 不明白ti为什么这样做 » 2018-08-16 12:02:59

#188 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 不明白ti为什么这样做 » 2018-08-16 11:37:34

#189 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 不明白ti为什么这样做 » 2018-08-16 11:18:23

- Jin劲

- 回复: 10

在ti的CSL(chip support library 把ti所有chip都支持了)中把寄存器的分布都用结构体定义了一次,这样做不是很浪费空间么

/****

Register Overlay Structure for __ALL__

****/

typedef struct {

volatile Uint32 REVISION;

volatile Uint8 RSVD0[12];

volatile Uint32 SYSCONFIG;

volatile Uint8 RSVD1[12];

volatile Uint32 EOI;

volatile Uint32 IRQSTS_RAW_0;

volatile Uint32 IRQSTS_RAW_1;

volatile Uint32 IRQSTS_0;

volatile Uint32 IRQSTS_1;

volatile Uint32 IRQSTS_SET_0;

volatile Uint32 IRQSTS_SET_1;

volatile Uint32 IRQSTS_CLR_0;

volatile Uint32 IRQSTS_CLR_1;

volatile Uint32 IRQWAKEN_0;

volatile Uint32 IRQWAKEN_1;

volatile Uint8 RSVD2[200];

volatile Uint32 SYSSTS;

volatile Uint32 IRQSTS1;

volatile Uint32 IRQEN1;

volatile Uint32 WAKEUPEN;

volatile Uint8 RSVD3[4];

volatile Uint32 IRQSTS2;

volatile Uint32 IRQEN2;

volatile Uint32 CTRL;

volatile Uint32 OE;

volatile Uint32 DATAIN;

volatile Uint32 DATAOUT;

volatile Uint32 LEVELDETECT0;

volatile Uint32 LEVELDETECT1;

volatile Uint32 RISINGDETECT;

volatile Uint32 FALLINGDETECT;

volatile Uint32 DEBOUNCEN;

volatile Uint32 DEBOUNCINGTIME;

volatile Uint8 RSVD4[8];

volatile Uint32 CLRIRQEN1;

volatile Uint32 SETIRQEN1;

volatile Uint8 RSVD5[8];

volatile Uint32 CLRIRQEN2;

volatile Uint32 SETIRQEN2;

volatile Uint8 RSVD6[8];

volatile Uint32 CLRWKUPENA;

volatile Uint32 SETWKUENA;

volatile Uint8 RSVD7[8];

volatile Uint32 CLRDATAOUT;

volatile Uint32 SETDATAOUT;

} CSL_GpioRegs;

#190 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 买个渔网周末打发时间 » 2018-08-16 09:04:04

#193 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » 发现一个支持POSIX和多核的RTOS:RTEMS » 2018-08-15 15:41:31

#194 全志 SOC » 请教一下.align这条指令 » 2018-08-12 11:49:25

#196 Re: 全志 SOC » 小白求求挖坑填坑,f1c100s小小sram裸机 » 2018-07-10 11:05:26

#198 Re: 全志 SOC » 小白求求挖坑填坑,f1c100s小小sram裸机 » 2018-07-02 23:01:53

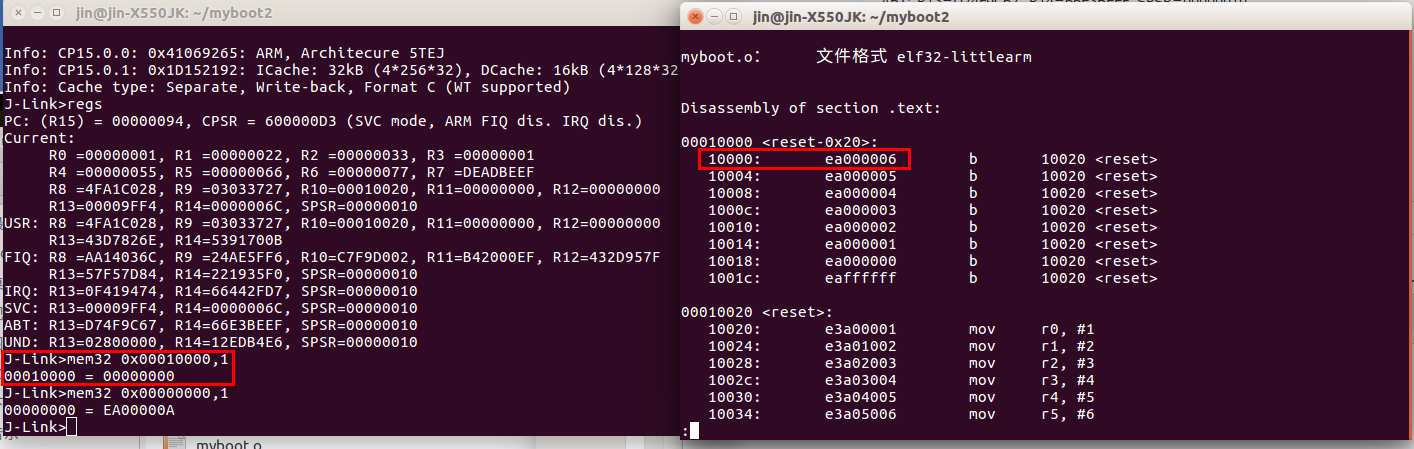

#199 Re: 全志 SOC » 小白求求挖坑填坑,f1c100s小小sram裸机 » 2018-07-02 22:26:58

使芯片进入fel模式,确保安装好fel工具,输入make write,写入spi flash

jin@jin-X550JK:~/myboot2$ sudo sunxi-fel list

[sudo] jin 的密码:

USB device 001:005 Allwinner F1C100s

jin@jin-X550JK:~/myboot2$ make write

sudo sunxi-fel -p spiflash-write 0 myboot_sram.bin

100% [================================================] 1 kB, 56.8 kB/s

重新上电,用JLink调试

jin@jin-X550JK:~/myboot2$ sudo JLinkExe

SEGGER J-Link Commander V5.00 ('?' for help)

Compiled Jun 8 2015 21:14:06

DLL version V5.00, compiled Jun 8 2015 21:14:03

Firmware: J-Link V9 compiled Jun 2 2222 22:22:22

Hardware: V9.40

S/N: 81480416

Feature(s): GDB, RDI, FlashBP, FlashDL, JFlash, RDDI

VTarget = 3.174V

Info: TotalIRLen = 4, IRPrint = 0x01

Info: CP15.0.0: 0x41069265: ARM, Architecure 5TEJ

Info: CP15.0.1: 0x1D152192: ICache: 32kB (425632), DCache: 16kB (412832)

Info: Cache type: Separate, Write-back, Format C (WT supported)

Found 1 JTAG device, Total IRLen = 4:

#0 Id: 0x07926F0F, IRLen: 04, IRPrint: 0x1, ARM926EJ-S Core

Found ARM with core Id 0x07926F0F (ARM9)

Target interface speed: 100 kHz

J-Link>r

Reset delay: 0 ms

Reset type NORMAL: Using RESET pin, halting CPU after Reset

Info: Core does not stop after Reset, setting WP to stop it.

WARNING: PC of target system has unexpected value of 0x00000094 after reset.

Info: CP15.0.0: 0x41069265: ARM, Architecure 5TEJ

Info: CP15.0.1: 0x1D152192: ICache: 32kB (425632), DCache: 16kB (412832)

Info: Cache type: Separate, Write-back, Format C (WT supported)

J-Link>regs

PC: (R15) = 00000094, CPSR = 600000D3 (SVC mode, ARM FIQ dis. IRQ dis.)

Current:

R0 =00000001, R1 =00000022, R2 =00000033, R3 =00000001

R4 =00000055, R5 =00000066, R6 =00000077, R7 =DEADBEEF

R8 =4FA1C028, R9 =03033727, R10=00010020, R11=00000000, R12=00000000

R13=00009FF4, R14=0000006C, SPSR=00000010

USR: R8 =4FA1C028, R9 =03033727, R10=00010020, R11=00000000, R12=00000000

R13=43D7826E, R14=5391700B

FIQ: R8 =AA14036C, R9 =24AE5FF6, R10=C7F9D002, R11=B42000EF, R12=432D957F

R13=57F57D84, R14=221935F0, SPSR=00000010

IRQ: R13=0F419474, R14=66442FD7, SPSR=00000010

SVC: R13=00009FF4, R14=0000006C, SPSR=00000010

ABT: R13=D74F9C67, R14=66E3BEEF, SPSR=00000010

UND: R13=02800000, R14=12EDB4E6, SPSR=00000010

J-Link>

R0 =00000001, R1 =00000022, R2 =00000033, R3 =00000001

R4 =00000055, R5 =00000066, R6 =00000077, R7 =DEADBEEF

#200 Re: 全志 SOC » 小白求求挖坑填坑,f1c100s小小sram裸机 » 2018-07-02 22:19:04

lds内存地址参考 Allwinner_F1C600_User_Manual_V1.0.pdf

jin@jin-X550JK:~/myboot2$ make clean

rm .o .bin

jin@jin-X550JK:~/myboot2$ ls

main.c Makefile mksunxiboot myboot.lds mystart.s

jin@jin-X550JK:~/myboot2$jin@jin-X550JK:~/myboot2$ make

arm-eabi-as mystart.s -o mystart.o

arm-eabi-gcc -c main.c -o main.o

arm-eabi-ld -Tmyboot.lds mystart.o main.o -o myboot.o

arm-eabi-objcopy -O binary myboot.o myboot.bin

./mksunxiboot/mksunxiboot myboot.bin myboot_sram.bin

File size: 0xb0

Load size: 0xb0

Read 0xb0 bytes

Write 0x200 bytes

jin@jin-X550JK:~/myboot2$ ls

main.c Makefile myboot.bin myboot.o mystart.o

main.o mksunxiboot myboot.lds myboot_sram.bin mystart.s

jin@jin-X550JK:~/myboot2$

//F1C100S上电从ROM启动,检测MMC、SPIFLASH等,./mksunxiboot/mksunxiboot myboot.bin myboot_sram.bin 就是给编译出的文件加入魔数,用于识别。

//mksunxiboot git地址: https://github.com/amery/mksunxiboot

- 首页

- » 搜索

- » Jin劲 发表的帖子

东莞哇酷科技有限公司开发