- 首页

- » 搜索

- » xiaohui 发表的帖子

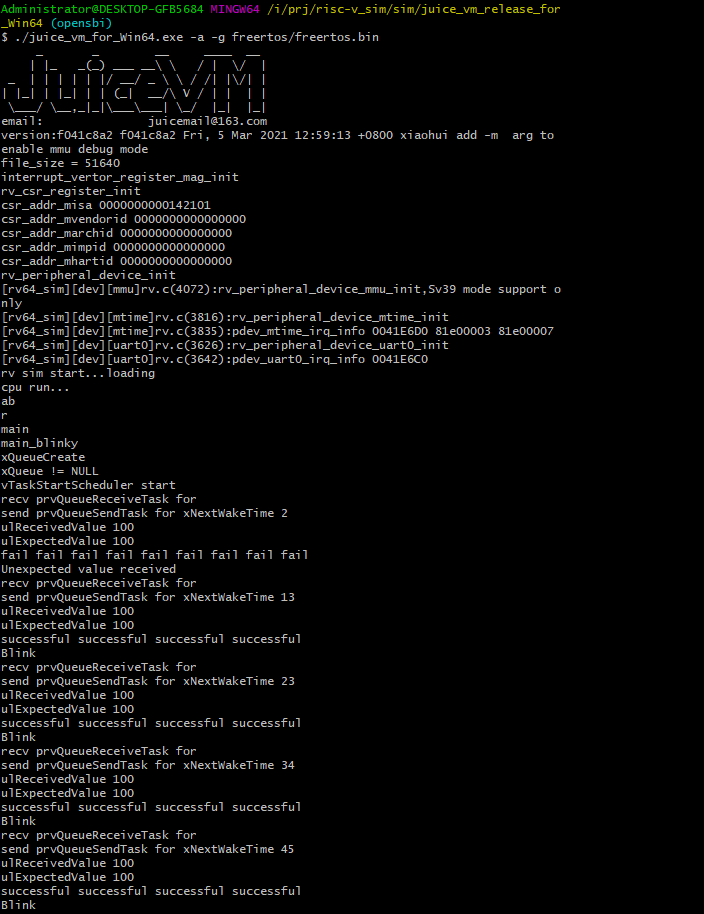

#1 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2024-03-28 17:40:13

juicevm的源代码真的没时间整理了。不嫌乱的话可以投票是否开源。

新项目,不过也是不怎么更新,但是开源: https://juicescript.com/

#3 Re: Cortex M0/M3/M4/M7 » 自制pico,rp2040烧录固件后么有正常启动 » 2023-11-06 11:53:43

擦除flash的固件: https://wws.lanzoui.com/ibwcRuo4hqb

ref: https://zhuanlan.zhihu.com/p/415306379

侵权的话叫晕哥来删。逃~

#5 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 单片机有8个信号输入,想通过上位机配置这8个信号与、或操作,该如何实现? » 2023-10-20 17:12:07

啥也不想说,直接看代码

#include <stdio.h>

#include <stdint.h>

#include <string.h>

#include <stdlib.h>

// str: x1&&(x2||x3)&&(x4||x5)

// planA

// ra0 = X3 || X2

// ra1 = ra0 && x1

// ra0 = x4 || x5

// ra1 = ra0 && ra1

// planB

// ra0 = X3 || X2

// ra1 = x4 || x5

// ra0 = ra0 && ra1

// ra0 = ra0 && x1

/*

x1&&(x2||(x3&&x4))&&(x5||x6)

ra1= x3 && x4

ra0=ra1 || x2

ra1= x5 || x6

ra0=ra1 && ra0

ra0=ra0 && x1

X1

X2

X3

POP -> X3

POP -> X2

X1

ra0

X5

POP -> X5

X1

ra0

I_LOAD X1

I_PUSH

I_LOAD X2

I_PUSH

I_LOAD X3

I_PUSH

I_LOAD X4

I_AND1

ra1 = x3 && x4

I_OR1

ra0 = ra1 || x2

I_PUSH

I_LOAD X5

I_PUSH

I_LOAD X6

I_OR1

ra1 = X5 || x6

I_AND1

ra0 = ra1 && ra0

I_AND1

ra0=ra0 && X1

I_PUSH

*/

#define is_letter(c) ((c >= 'a' && c <= 'z') || (c >= 'A' && c <= 'Z'))

#define is_num(c) (c >= '0' && c <= '9')

#define is_id(c) (is_letter(c) || )

enum{

STA_IDLE,

STA_ID,

STA_AND,

STA_OR,

STA_LPAR,

STA_RPAR,

STA_EOL,

}sta;

enum{

I_PUSH,

// I_POP,

I_ENTER,

I_EXIT,

I_LOAD_A0,

I_LOAD_A1,

I_AND1_A0,

I_AND1_A1,

I_OR1_A0,

I_OR1_A1,

I_AND2_RA0_X_X,

I_AND2_RA0_RA0_X,

I_AND2_RA0_RA1_X,

I_AND2_RA0_RA1_RA0,

I_AND2_RA0_RA0_RA1,

// I_AND2_RA0_RA1_RA1,

I_AND2_RA1_X_X,

I_AND2_RA1_RA0_X,

I_AND2_RA1_RA1_X,

I_AND2_RA1_RA1_RA0,

// I_AND2_RA1_RA0_RA1,

I_OR2_RA0_X_X,

I_OR2_RA0_RA0_X,

I_OR2_RA0_RA1_X,

I_OR2_RA0_RA1_RA0,

I_OR2_RA0_RA0_RA1,

// I_OR2_RA0_RA1_RA1,

I_OR2_RA1_X_X,

I_OR2_RA1_RA0_X,

I_OR2_RA1_RA1_X,

I_OR2_RA1_RA1_RA0,

I_OR2_RA1_RA0_RA1,

// I_OR2_RA1_RA1_RA1,

I_UIMP, // end

};

struct {

int t;

int i;

} lex_list[1024];

union{

uint32_t code;

struct{

unsigned char op;

unsigned char a0;

unsigned char a1;

}i;

}code_list[100];

union{

uint32_t code;

struct{

unsigned char op;

unsigned char a0;

unsigned char a1;

}i;

}opt_code_list[100];

int lex_list_i;

int code_list_i;

int opt_code_list_i;

int g_parse_i;

static void parse(void);

static void opt(int lev,int ra_i,int init);

static void prt(int lev,int ra_i);

static int vm(void);

int main(int argc,const char** argv){

int c;

uint32_t id;

int res = 0;

int size = 1024;

char* buff = (char*)malloc(size);

int tmp_c_i = 0;

lex_list_i = 0;

code_list_i = 0;

sta = STA_IDLE;

if(NULL == fgets(buff,size,stdin)){

return 0;

}

// sprintf(buff,"x1&&(x2||(x3&&x4))&&(x5||x6)\n");

printf("str: %s\n",buff);

// buff[strlen(buff)] = '\n';

while(tmp_c_i <= strlen(buff)){

c = buff[tmp_c_i];

tmp_c_i++;

// printf("c: %c(0x%x) sta: %d\n",c,c,sta);

// printf("c: %c(0x%x) sta: %d\n",c,c,sta);

retry:

if(c == '\r' || c == ' ' || c == '\t'){continue;}

switch(sta){

case STA_IDLE:

id = 0;

// if(is_letter(c)){

if(c == 'x'){

// id = c;

sta = STA_ID;

// }else if(is_num(c)){

// id = c;

// sta = STA_ID;

}else if(c == '&'){

sta = STA_AND;

}else if(c == '|'){

sta = STA_OR;

}else if(c == '('){

lex_list[lex_list_i].t = STA_LPAR;

lex_list[lex_list_i].i = 0;

lex_list_i++;

}else if(c == ')'){

lex_list[lex_list_i].t = STA_RPAR;

lex_list[lex_list_i].i = 0;

lex_list_i++;

}else if(c == '\n'){

goto input_ok;

}else{

// error

}

break;

case STA_ID:

// if(is_id(c)){

if(is_num(c)){

id = id * 10 + c - '0';

}else{

printf("sta: STA_ID lex_list_i: %d id: %d\n",lex_list_i,id);

lex_list[lex_list_i].t = STA_ID;

lex_list[lex_list_i].i = id;

lex_list_i++;

sta = STA_IDLE;

goto retry;

}

break;

case STA_AND:

if(c == '&'){

printf("sta: STA_AND\n");

lex_list[lex_list_i].t = STA_AND;

lex_list[lex_list_i].i = 0;

lex_list_i++;

sta = STA_IDLE;

}else{

// error

}

break;

case STA_OR:

if(c == '|'){

// printf("sta: STA_OR\n");

lex_list[lex_list_i].t = STA_OR;

lex_list[lex_list_i].i = 0;

lex_list_i++;

sta = STA_IDLE;

}else{

// error

}

break;

default:

break;

}

// refresh();

}

input_ok:

free(buff);

printf("parse lex_list_i:%d\n",lex_list_i);

g_parse_i = 0;

if(lex_list_i <= 0){

// error

return -1;

}

lex_list[lex_list_i].t = STA_EOL;

lex_list[lex_list_i].i = 0;

lex_list_i++;

printf("=parse==================================================================================\n");

parse();

printf("=prt==================================================================================\n");

prt(0,0);

// return 0;

printf("opt code_list_i:%d\n",code_list_i);

printf("=opt==================================================================================\n");

opt(0,0,1);

opt_code_list[opt_code_list_i].i.op = I_UIMP;

printf("set opt_code_list[%d] to I_UIMP\n",opt_code_list_i);

opt_code_list_i++;

printf("=vm==================================================================================\n");

res = vm();

printf("return %d\n",res);

// while(1);

return 0;

}

static void parse(void){

static int s_lpar_cnt = 0;

// printf("parse g_parse_i:%d lex_list[g_parse_i].t:%d lex_list_i: %d code_list_i:%d\n",g_parse_i,lex_list[g_parse_i].t,lex_list_i,code_list_i);

// refresh();

if(g_parse_i > lex_list_i){

return;

}

if(lex_list[g_parse_i].t == STA_EOL){

// printf("parse g_parse_i:%d lex_list[g_parse_i].t == STA_EOL code_list_i:%d\n",g_parse_i,code_list_i);

return;

}

if(lex_list[g_parse_i].t == STA_ID){

// printf("parse g_parse_i:%d lex_list[g_parse_i].t == STA_ID code_list_i:%d lex_list[g_parse_i].i:%d\n",g_parse_i,code_list_i,lex_list[g_parse_i].i);

// refresh();

code_list[code_list_i].i.op = I_LOAD_A0;

code_list[code_list_i].i.a0 = lex_list[g_parse_i].i;

code_list_i++;

g_parse_i++;

}else if(lex_list[g_parse_i].t == STA_AND){

// printf("parse g_parse_i:%d lex_list[g_parse_i].t == STA_AND code_list_i:%d\n",g_parse_i,code_list_i);

// refresh();

code_list[code_list_i].i.op = I_PUSH;

code_list_i++;

g_parse_i++;

parse();

// printf("parse g_parse_i:%d lex_list[g_parse_i].t == I_AND1 code_list_i:%d\n",g_parse_i,code_list_i);

code_list[code_list_i].i.op = I_AND1_A0;

code_list_i++;

}else if(lex_list[g_parse_i].t == STA_OR){

// printf("parse g_parse_i:%d lex_list[g_parse_i].t == STA_OR\n",g_parse_i);

// refresh();

code_list[code_list_i].i.op = I_PUSH;

code_list_i++;

g_parse_i++;

parse();

code_list[code_list_i].i.op = I_OR1_A0;

code_list_i++;

}else if(lex_list[g_parse_i].t == STA_LPAR){

// printf("parse g_parse_i:%d lex_list[g_parse_i].t == STA_LPAR\n",g_parse_i);

// refresh();

// code_list[code_list_i].i.op = I_PUSH;

// code_list_i++;

code_list[code_list_i].i.op = I_ENTER;

code_list_i++;

g_parse_i++;

s_lpar_cnt++;

parse();

if(lex_list[g_parse_i].t != STA_RPAR){

// error

}

code_list[code_list_i].i.op = I_EXIT;

code_list_i++;

return;

}else if(lex_list[g_parse_i].t == STA_RPAR){

// printf("parse g_parse_i:%d lex_list[g_parse_i].t == STA_RPAR\n",g_parse_i);

// refresh();

if(s_lpar_cnt == 0){

// error

}

s_lpar_cnt--;

// code_list[code_list_i].i.op = I_POP;

// code_list_i++;

g_parse_i++;

return;

}else{

// error

}

parse();

}

static void prt(int lev,int ra_i){

static int pc = 0;

while(1){

// printf("opt pc:%d code_list[pc].i.op: %d code_list_i: %d\n",pc,code_list[pc].i.op,code_list_i);

// refresh();

if(pc > code_list_i){

return;

}

switch(code_list[pc].i.op){

case I_PUSH:

printf("I_PUSH\n");

break;

// case I_ENTER:

// printf("I_ENTER\n");

// break;

// case I_EXIT:

// printf("I_EXIT\n");

// // return;

// break;

case I_LOAD_A0:

printf("I_LOAD X%d\n",code_list[pc].i.a0);

break;

case I_AND1_A0:

printf("I_AND1\n");

break;

case I_OR1_A0:

printf("I_OR1\n");

break;

// case I_AND2:

// break;

// case I_OR2:

// break;

case I_UIMP:

return;

break;

default:

break;

}

pc++;

}

}

static void opt(int lev,int ra_i,int init){

static int pc = 0;

static struct{

unsigned char is_ra;

unsigned char a0;

} stack[100],cur_ra={1,0};

static int ra0_isused=0;

static int ra1_isused=0;

static int stack_pos_start = (sizeof(stack)/sizeof(stack[0]));

static int stack_pos_i = (sizeof(stack)/sizeof(stack[0]));

if(init){

ra0_isused=0;

ra1_isused=0;

stack_pos_start = (sizeof(stack)/sizeof(stack[0]));

stack_pos_i = (sizeof(stack)/sizeof(stack[0]));

cur_ra.is_ra = 1;

cur_ra.a0 = 0;

opt_code_list_i = 0;

}

// cur_ra.is_ra = 1;

while(1){

// printf("opt ra0_isused: %d ra1_isused: %d stack_pos_start: %d stack_pos_i: %d\n",ra0_isused,ra1_isused,stack_pos_start,stack_pos_i);

// printf("opt pc:%d code_list[pc].i.op: %d code_list_i: %d\n",pc,code_list[pc].i.op,code_list_i);

if(pc > code_list_i){

return;

}

switch(code_list[pc].i.op){

case I_PUSH:

// printf("I_PUSH is_ra: %d a0: %d\n",cur_ra.is_ra,cur_ra.a0);

stack[stack_pos_i].is_ra = cur_ra.is_ra;

stack[stack_pos_i].a0 = cur_ra.a0;

stack_pos_i--;

break;

case I_ENTER:

// printf("I_ENTER ra0_isused: %d ra1_isused: %d\n",ra0_isused,ra1_isused);

pc++;

if(ra0_isused == 0){

ra0_isused=1;

ra1_isused=0;

opt(lev+1,0,0);

}else if(ra0_isused == 1){

ra0_isused=1;

ra1_isused=1;

opt(lev+1,1,0);

}else if(ra1_isused == 1){

printf("ra1_isused == 1\n");exit(-1);

}else{

printf("ra0_isused: %d ra1_isused: %d\n",ra0_isused,ra1_isused);exit(-1);

}

break;

case I_EXIT:

// printf("I_EXIT\n");

// stack_pos_i++;

// printf("I_EXIT is_ra:%d a0:%d\n",stack[stack_pos_i].is_ra,stack[stack_pos_i].a0);

// cur_ra.is_ra = stack[stack_pos_i].is_ra;

// cur_ra.a0 = stack[stack_pos_i].a0;

return;

break;

case I_LOAD_A0:

// printf("I_LOAD X%d\n",code_list[pc].i.a0);

cur_ra.is_ra = 0;

cur_ra.a0 = code_list[pc].i.a0;

break;

case I_AND1_A0:

stack_pos_i++;

// printf("I_AND1 cur_ra.is_ra: %d cur_ra.a0: %d stack_pos_i: %d stack[stack_pos_i].is_ra: %d\n",cur_ra.is_ra,cur_ra.a0,stack_pos_i,stack[stack_pos_i].is_ra);

if(cur_ra.is_ra == 0 && stack[stack_pos_i].is_ra == 0){

// a0 && a1

if(ra_i == 0){

opt_code_list[opt_code_list_i].i.op = I_AND2_RA0_X_X;

opt_code_list[opt_code_list_i].i.a0 = cur_ra.a0;

opt_code_list[opt_code_list_i].i.a1 = stack[stack_pos_i].a0;

printf("ra0 = X%d && X%d\n",cur_ra.a0,stack[stack_pos_i].a0);

} else if(ra_i == 1){

opt_code_list[opt_code_list_i].i.op = I_AND2_RA1_X_X;

opt_code_list[opt_code_list_i].i.a0 = cur_ra.a0;

opt_code_list[opt_code_list_i].i.a1 = stack[stack_pos_i].a0;

printf("ra1 = X%d && X%d\n",cur_ra.a0,stack[stack_pos_i].a0);

}

opt_code_list_i++;

}else if(cur_ra.is_ra == 1 && stack[stack_pos_i].is_ra == 0){

if(ra_i == 0){

if(cur_ra.a0 == 0){

opt_code_list[opt_code_list_i].i.op = I_AND2_RA0_RA0_X;

opt_code_list[opt_code_list_i].i.a1 = stack[stack_pos_i].a0;

printf("ra0 = ra0 && X%d\n",stack[stack_pos_i].a0);

}else if(cur_ra.a0 == 1){

opt_code_list[opt_code_list_i].i.op = I_AND2_RA0_RA1_X;

opt_code_list[opt_code_list_i].i.a1 = stack[stack_pos_i].a0;

printf("ra0 = ra1 && X%d\n",stack[stack_pos_i].a0);

}

} else if(ra_i == 1){

if(cur_ra.a0 == 0){

opt_code_list[opt_code_list_i].i.op = I_AND2_RA1_RA0_X;

opt_code_list[opt_code_list_i].i.a1 = stack[stack_pos_i].a0;

printf("ra1 = ra0 && X%d\n",stack[stack_pos_i].a0);

}else if(cur_ra.a0 == 1){

opt_code_list[opt_code_list_i].i.op = I_AND2_RA1_RA1_X;

opt_code_list[opt_code_list_i].i.a1 = stack[stack_pos_i].a0;

printf("ra1 = ra1 && X%d\n",stack[stack_pos_i].a0);

}

}

opt_code_list_i++;

}else if(cur_ra.is_ra == 1 && stack[stack_pos_i].is_ra == 1){

if(ra_i == 0){

if(cur_ra.a0 == 0){

if(stack[stack_pos_i].a0 == 0){

// opt_code_list[opt_code_list_i].i.op = I_AND2_RA0_RA0_RA0;

printf("ra0 = ra0 && ra0\n");exit(-1);

}else if(stack[stack_pos_i].a0 == 1){

opt_code_list[opt_code_list_i].i.op = I_AND2_RA0_RA0_RA1;

}

printf("ra0 = ra0 && ra%d\n",stack[stack_pos_i].a0);

}else if(cur_ra.a0 == 1){

if(stack[stack_pos_i].a0 == 1){

// opt_code_list[opt_code_list_i].i.op = I_AND2_RA0_RA0_RA0;

printf("ra0 = ra1 && ra1\n");exit(-1);

}else if(stack[stack_pos_i].a0 == 0){

opt_code_list[opt_code_list_i].i.op = I_AND2_RA0_RA1_RA0;

}

printf("ra0 = ra1 && ra%d\n",stack[stack_pos_i].a0);

}

opt_code_list_i++;

} else if(ra_i == 1){

if(cur_ra.a0 == 0){

opt_code_list[opt_code_list_i].i.op = I_AND2_RA1_RA0_X;

opt_code_list[opt_code_list_i].i.a1 = stack[stack_pos_i].a0;

printf("ra1 = ra0 && X%d\n",stack[stack_pos_i].a0);

}else if(cur_ra.a0 == 1){

opt_code_list[opt_code_list_i].i.op = I_AND2_RA1_RA1_X;

opt_code_list[opt_code_list_i].i.a1 = stack[stack_pos_i].a0;

printf("ra1 = ra1 && X%d\n",stack[stack_pos_i].a0);

}

opt_code_list_i++;

}

}

cur_ra.is_ra = 1;

cur_ra.a0 = ra_i;

break;

case I_OR1_A0:

stack_pos_i++;

// printf("I_OR1 cur_ra.is_ra: %d cur_ra.a0: %d stack_pos_i: %d stack[stack_pos_i].is_ra: %d\n",cur_ra.is_ra,cur_ra.a0,stack_pos_i,stack[stack_pos_i].is_ra);

if(cur_ra.is_ra == 0 && stack[stack_pos_i].is_ra == 0){

// a0 || a1

if(ra_i == 0){

opt_code_list[opt_code_list_i].i.op = I_OR2_RA0_X_X;

opt_code_list[opt_code_list_i].i.a0 = cur_ra.a0;

opt_code_list[opt_code_list_i].i.a1 = stack[stack_pos_i].a0;

printf("ra0 = X%d || X%d\n",cur_ra.a0,stack[stack_pos_i].a0);

} else if(ra_i == 1){

opt_code_list[opt_code_list_i].i.op = I_OR2_RA1_X_X;

opt_code_list[opt_code_list_i].i.a0 = cur_ra.a0;

opt_code_list[opt_code_list_i].i.a1 = stack[stack_pos_i].a0;

printf("ra1 = X%d || X%d\n",cur_ra.a0,stack[stack_pos_i].a0);

}

opt_code_list_i++;

}else if(cur_ra.is_ra == 1 && stack[stack_pos_i].is_ra == 0){

if(ra_i == 0){

if(cur_ra.a0 == 0){

opt_code_list[opt_code_list_i].i.op = I_OR2_RA0_RA0_X;

opt_code_list[opt_code_list_i].i.a1 = stack[stack_pos_i].a0;

printf("ra0 = ra0 || X%d\n",stack[stack_pos_i].a0);

}else if(cur_ra.a0 == 1){

opt_code_list[opt_code_list_i].i.op = I_OR2_RA0_RA1_X;

opt_code_list[opt_code_list_i].i.a1 = stack[stack_pos_i].a0;

printf("ra0 = ra1 || X%d\n",stack[stack_pos_i].a0);

}

opt_code_list_i++;

} else if(ra_i == 1){

if(cur_ra.a0 == 0){

opt_code_list[opt_code_list_i].i.op = I_OR2_RA1_RA0_X;

opt_code_list[opt_code_list_i].i.a1 = stack[stack_pos_i].a0;

printf("ra1 = ra0 || X%d\n",stack[stack_pos_i].a0);

}else if(cur_ra.a0 == 1){

opt_code_list[opt_code_list_i].i.op = I_OR2_RA1_RA1_X;

opt_code_list[opt_code_list_i].i.a1 = stack[stack_pos_i].a0;

printf("ra1 = ra1 || X%d\n",stack[stack_pos_i].a0);

}

opt_code_list_i++;

}

}else if(cur_ra.is_ra == 1 && stack[stack_pos_i].is_ra == 1){

if(ra_i == 0){

if(cur_ra.a0 == 0){

if(stack[stack_pos_i].a0 == 0){

// opt_code_list[opt_code_list_i].i.op = I_OR2_RA0_RA0_RA0;

printf("ra0 = ra0 || ra0\n");exit(-1);

}else if(stack[stack_pos_i].a0 == 1){

opt_code_list[opt_code_list_i].i.op = I_OR2_RA0_RA0_RA1;

}

printf("ra0 = ra0 || ra%d\n",stack[stack_pos_i].a0);

}else if(cur_ra.a0 == 1){

if(stack[stack_pos_i].a0 == 1){

// opt_code_list[opt_code_list_i].i.op = I_OR2_RA0_RA1_RA1;

printf("ra0 = ra1 || ra1\n");exit(-1);

}else if(stack[stack_pos_i].a0 == 0){

opt_code_list[opt_code_list_i].i.op = I_OR2_RA0_RA1_RA0;

}

printf("ra0 = ra1 || ra%d\n",stack[stack_pos_i].a0);

}

opt_code_list_i++;

} else if(ra_i == 1){

if(cur_ra.a0 == 0){

if(stack[stack_pos_i].a0 == 0){

// opt_code_list[opt_code_list_i].i.op = I_OR2_RA1_RA0_RA0;

printf("ra1 = ra0 || ra0\n");exit(-1);

}else if(stack[stack_pos_i].a0 == 1){

opt_code_list[opt_code_list_i].i.op = I_OR2_RA1_RA0_RA1;

}

printf("ra1 = ra0 || ra%d\n",stack[stack_pos_i].a0);

}else if(cur_ra.a0 == 1){

if(stack[stack_pos_i].a0 == 1){

// opt_code_list[opt_code_list_i].i.op = I_OR2_RA1_RA0_RA0;

printf("ra1 = ra1 || ra1\n");exit(-1);

}else if(stack[stack_pos_i].a0 == 0){

opt_code_list[opt_code_list_i].i.op = I_OR2_RA1_RA1_RA0;

}

printf("ra1 = ra1 || ra%d\n",stack[stack_pos_i].a0);

}

opt_code_list_i++;

}

}

cur_ra.is_ra = 1;

cur_ra.a0 = ra_i;

break;

case I_UIMP:

return;

break;

default:

break;

}

pc++;

}

}

// 只有vm需要存放在单片机里,只需要把opt_code_list数组从上位机传输到单片机里,vm函数只依赖opt_code_list数组。

static int vm(void){

int pc = 0;

int ra0 = 0;

int ra1 = 0;

static int x[6];

int run = 1;

x[0] = 0;

x[1] = 0;

x[2] = 2;

x[3] = 3;

x[4] = 4;

x[5] = 5;

x[6] = 6;

while(run){

printf("pc: %d ->",pc);

switch(opt_code_list[pc].i.op){

case I_PUSH:

case I_ENTER:

case I_EXIT:

case I_LOAD_A0:

case I_LOAD_A1:

case I_AND1_A0:

case I_AND1_A1:

case I_OR1_A0:

case I_OR1_A1:

printf("vm error\n");exit(-1);

break;

case I_AND2_RA0_X_X:

printf("RA0 = X%d && X%d\n",opt_code_list[pc].i.a0,opt_code_list[pc].i.a1);

ra0 = x[opt_code_list[pc].i.a0] && x[opt_code_list[pc].i.a1];

break;

case I_AND2_RA0_RA0_X:

printf("RA0 = RA0 && X%d\n",opt_code_list[pc].i.a1);

ra0 = ra0 && x[opt_code_list[pc].i.a1];

break;

case I_AND2_RA0_RA1_X:

printf("RA0 = RA1 && X%d\n",opt_code_list[pc].i.a1);

ra0 = ra1 && x[opt_code_list[pc].i.a1];

break;

case I_AND2_RA0_RA1_RA0:

printf("RA0 = RA1 && RA0\n");

ra0 = ra1 && ra0;

break;

case I_AND2_RA0_RA0_RA1:

printf("RA0 = RA0 && RA1\n");

ra0 = ra0 && ra1;

break;

case I_AND2_RA1_X_X:

printf("RA1 = X%d && X%d\n",opt_code_list[pc].i.a0,opt_code_list[pc].i.a1);

ra1 = x[opt_code_list[pc].i.a0] && x[opt_code_list[pc].i.a1];

break;

case I_AND2_RA1_RA0_X:

printf("RA1 = RA0 && X%d\n",opt_code_list[pc].i.a1);

ra1 = ra0 && x[opt_code_list[pc].i.a1];

break;

case I_AND2_RA1_RA1_X:

printf("RA1 = RA1 && X%d\n",opt_code_list[pc].i.a1);

ra1 = ra1 && x[opt_code_list[pc].i.a1];

break;

case I_AND2_RA1_RA1_RA0:

printf("RA1 = RA1 && RA0\n");

ra1 = ra1 && ra0;

break;

case I_OR2_RA0_X_X:

printf("RA0 = X%d || X%d\n",opt_code_list[pc].i.a0,opt_code_list[pc].i.a1);

ra0 = x[opt_code_list[pc].i.a0] || x[opt_code_list[pc].i.a1];

break;

case I_OR2_RA0_RA0_X:

printf("RA0 = RA0 || X%d\n",opt_code_list[pc].i.a1);

ra0 = ra0 || x[opt_code_list[pc].i.a1];

break;

case I_OR2_RA0_RA1_X:

printf("RA0 = RA1 || X%d\n",opt_code_list[pc].i.a1);

ra0 = ra1 || x[opt_code_list[pc].i.a1];

break;

case I_OR2_RA0_RA1_RA0:

printf("RA0 = RA1 || RA0\n");

ra0 = ra1 || ra0;

break;

case I_OR2_RA0_RA0_RA1:

printf("RA0 = RA0 || RA1\n");

ra0 = ra0 || ra1;

break;

case I_OR2_RA1_X_X:

printf("RA1 = X%d || X%d\n",opt_code_list[pc].i.a0,opt_code_list[pc].i.a1);

ra1 = x[opt_code_list[pc].i.a0] || x[opt_code_list[pc].i.a1];

break;

case I_OR2_RA1_RA0_X:

printf("RA1 = RA0 || X%d\n",opt_code_list[pc].i.a1);

ra1 = ra0 || x[opt_code_list[pc].i.a1];

break;

case I_OR2_RA1_RA1_X:

printf("RA1 = RA1 || X%d\n",opt_code_list[pc].i.a1);

ra1 = ra1 || x[opt_code_list[pc].i.a1];

break;

case I_OR2_RA1_RA1_RA0:

printf("RA1 = RA1 || RA0\n");

ra1 = ra1 || ra0;

break;

case I_OR2_RA1_RA0_RA1:

printf("RA1 = RA0 || RA1\n");

ra1 = ra0 || ra1;

break;

case I_UIMP:

printf("I_UIMP\n");

run = 0;

break;

default:

break;

}

pc++;

}

printf("RA0: %d RA1: %d\n",ra0,ra1);

return ra0;

}#8 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2022-07-13 09:14:31

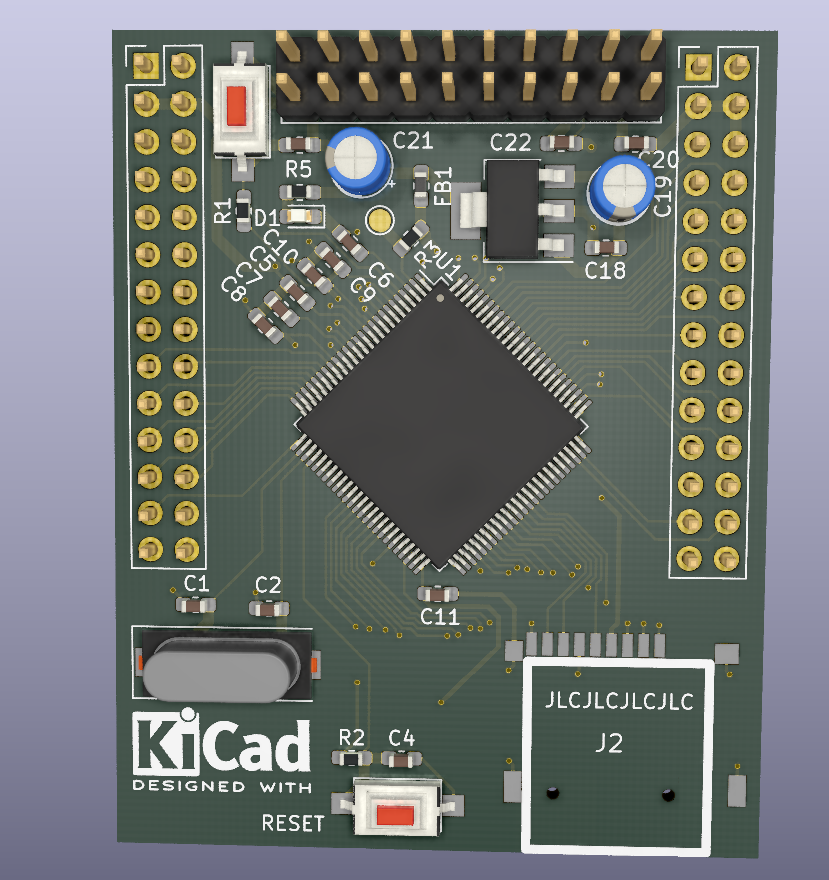

#10 硬件设计 KiCAD/Protel/DXP/PADS/ORCAD/EAGLE » 【微小小小小小小小"处理"器】超级超级超级小的一个处理器(瞎写的)开源,有电脑就可以仿真 » 2022-05-09 14:31:28

- xiaohui

- 回复: 2

JUICE LC3

Author: Li.XiongHui(juicemail@163.com)

1. clone this project

git clone https://gitee.com/xunxiaohuii/juice_lc-3

or

git clone https://github.com/xiaoxiaohuixxh/juice_lc-32. download and compile verilator simulator

2.1 download verilator source code , install the tools of dependence for compile verilator

# Prerequisites:

sudo apt-get install git perl python3 make autoconf g++ flex bison ccache

sudo apt-get install libgoogle-perftools-dev numactl perl-doc

sudo apt-get install libfl2 # Ubuntu only (ignore if gives error)

sudo apt-get install libfl-dev # Ubuntu only (ignore if gives error)

sudo apt-get install zlibc zlib1g zlib1g-dev # Ubuntu only (ignore if gives error)

cd juice_lc-3/juicelc3/tools

git clone https://github.com/verilator/verilator # Only first time

cd verilator

git pull # Make sure git repository is up-to-date

git tag # See what versions exist

git checkout aa86c777f4787db7d10fbbbb5019ed4d20a7fcfb # switch to v4.220 version2.2 compile the verilator source code

unset VERILATOR_ROOT # For bash

autoconf # Create ./configure script

./configure # Configure and create Makefile

make -j `nproc` # Build Verilator itself (if error, try just 'make')

./bin/verilator --versionthe version for my verilator is

Verilator 4.221 devel rev v4.220-35-g2b91d7643. design compile juicelc3 soc demo

pwd is xxx/juice_lc-3/juicelc3/tools/verilator

switch to juicelc3 soc demo directory

cd ../../sim/verilator/jlc3_soc

chmod +x ../../../tools/LC-3_Assembler/nglc3asmrun design compile

make run # will be automaticlly run dc,compile asm code and run demo➜ jlc3_soc git:(master) ✗ make run

../../../tools/LC-3_Assembler/nglc3asm ./rom/lc3.asm

Assembling "./rom/lc3.asm"

First Pass

----------

First Pass successful

Symbol table written to file "./rom/lc3.sym"

Second Pass

-----------

Second Pass successful

Binary file written to file "./rom/lc3.bin"

Hexadecimal file written to file "./rom/lc3_hex.bin"

echo '\n' >> ./rom/lc3.bin

verilator +incdir+../../../rtl/peripherals +incdir+../../../rtl/core/ --top-module jlc3_soc --trace -Wall -Wno-LATCH -Wno-EOFNEWLINE --cc jlc3_soc.v mem_ctrl.v ../../../rtl/core/pc.v ../../../rtl/core/id.v ../../../rtl/core/alu.v ../../../rtl/core/regs.v ../../../rtl/core/ctrl.v ../../../rtl/core/mux_1to2_16b.v ../../../rtl/core/mux_2to1_16b.v ../../../rtl/core/mux_3to1_16b.v ../../../rtl/peripherals/simple_uart_send.v --exe main.cpp

make -C obj_dir -f Vjlc3_soc.mk Vjlc3_soc

make[1]: Entering directory '/home/juice/prj/juice_lc-3/juicelc3/sim/verilator/jlc3_soc/obj_dir'

ccache g++ -I. -MMD -I/home/juice/prj/lc3_verilog/juicelc3/sim/verilator/sim/verilator/include -I/home/juice/prj/lc3_verilog/juicelc3/sim/verilator/sim/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TRACE=1 -DVM_TRACE_FST=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-sign-compare -Wno-uninitialized -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -Wno-shadow -std=gnu++14 -Os -c -o main.o ../main.cpp

ccache g++ -I. -MMD -I/home/juice/prj/lc3_verilog/juicelc3/sim/verilator/sim/verilator/include -I/home/juice/prj/lc3_verilog/juicelc3/sim/verilator/sim/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TRACE=1 -DVM_TRACE_FST=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-sign-compare -Wno-uninitialized -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -Wno-shadow -std=gnu++14 -Os -c -o verilated.o /home/juice/prj/lc3_verilog/juicelc3/sim/verilator/sim/verilator/include/verilated.cpp

ccache g++ -I. -MMD -I/home/juice/prj/lc3_verilog/juicelc3/sim/verilator/sim/verilator/include -I/home/juice/prj/lc3_verilog/juicelc3/sim/verilator/sim/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TRACE=1 -DVM_TRACE_FST=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-sign-compare -Wno-uninitialized -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -Wno-shadow -std=gnu++14 -Os -c -o verilated_vcd_c.o /home/juice/prj/lc3_verilog/juicelc3/sim/verilator/sim/verilator/include/verilated_vcd_c.cpp

/usr/bin/perl /home/juice/prj/lc3_verilog/juicelc3/sim/verilator/sim/verilator/bin/verilator_includer -DVL_INCLUDE_OPT=include Vjlc3_soc.cpp Vjlc3_soc___024root__DepSet_h4f076a71__0.cpp Vjlc3_soc__Trace__0.cpp Vjlc3_soc__ConstPool_0.cpp Vjlc3_soc___024root__Slow.cpp Vjlc3_soc___024root__DepSet_h4f076a71__0__Slow.cpp Vjlc3_soc__Syms.cpp Vjlc3_soc__Trace__0__Slow.cpp > Vjlc3_soc__ALL.cpp

ccache g++ -I. -MMD -I/home/juice/prj/lc3_verilog/juicelc3/sim/verilator/sim/verilator/include -I/home/juice/prj/lc3_verilog/juicelc3/sim/verilator/sim/verilator/include/vltstd -DVM_COVERAGE=0 -DVM_SC=0 -DVM_TRACE=1 -DVM_TRACE_FST=0 -faligned-new -fcf-protection=none -Wno-bool-operation -Wno-sign-compare -Wno-uninitialized -Wno-unused-but-set-variable -Wno-unused-parameter -Wno-unused-variable -Wno-shadow -std=gnu++14 -Os -c -o Vjlc3_soc__ALL.o Vjlc3_soc__ALL.cpp

echo "" > Vjlc3_soc__ALL.verilator_deplist.tmp

Archive ar -rcs Vjlc3_soc__ALL.a Vjlc3_soc__ALL.o

g++ main.o verilated.o verilated_vcd_c.o Vjlc3_soc__ALL.a -o Vjlc3_soc

rm Vjlc3_soc__ALL.verilator_deplist.tmp

make[1]: Leaving directory '/home/juice/prj/juice_lc-3/juicelc3/sim/verilator/jlc3_soc/obj_dir'

./obj_dir/Vjlc3_soc

Enabling waves...

uart0 write 0041 A

uart0 write 0031 1

uart0 uart0_seaddr 0

uart0 uart0_seaddr 1

uart0 uart0_seaddr 0

uart0 read stac 1

uart0 read stac 1

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0032 2

uart0 uart0_seaddr 0

uart0 uart0_seaddr 1

uart0 uart0_seaddr 0

uart0 read stac 1

uart0 read stac 1

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0033 3

uart0 uart0_seaddr 0

uart0 uart0_seaddr 1

uart0 uart0_seaddr 0

uart0 read stac 1

uart0 read stac 1

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0034 4

uart0 uart0_seaddr 0

uart0 uart0_seaddr 1

uart0 uart0_seaddr 0

uart0 read stac 1

uart0 read stac 1

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0035 5

uart0 uart0_seaddr 0

uart0 uart0_seaddr 1

uart0 uart0_seaddr 0

uart0 read stac 1

uart0 read stac 1

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0036 6

uart0 uart0_seaddr 0

uart0 uart0_seaddr 1

uart0 uart0_seaddr 0

uart0 read stac 1

uart0 read stac 1

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0037 7

uart0 uart0_seaddr 0

uart0 uart0_seaddr 1

uart0 uart0_seaddr 0

uart0 read stac 1

uart0 read stac 1

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0038 8

uart0 uart0_seaddr 0

uart0 uart0_seaddr 1

uart0 uart0_seaddr 0

uart0 read stac 1

uart0 read stac 1

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0041 A

uart0 write 0031 1

uart0 uart0_seaddr 0

uart0 uart0_seaddr 0

uart0 uart0_seaddr 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0032 2

uart0 uart0_seaddr 0

uart0 uart0_seaddr 0

uart0 uart0_seaddr 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0033 3

uart0 uart0_seaddr 0

uart0 uart0_seaddr 0

uart0 uart0_seaddr 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0034 4

uart0 uart0_seaddr 0

uart0 uart0_seaddr 0

uart0 uart0_seaddr 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0035 5

uart0 uart0_seaddr 0

uart0 uart0_seaddr 0

uart0 uart0_seaddr 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0036 6

uart0 uart0_seaddr 0

uart0 uart0_seaddr 0

uart0 uart0_seaddr 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0037 7

uart0 uart0_seaddr 0

uart0 uart0_seaddr 0

uart0 uart0_seaddr 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0038 8

uart0 uart0_seaddr 0

uart0 uart0_seaddr 0

uart0 uart0_seaddr 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0041 A

uart0 write 0031 1

uart0 uart0_seaddr 0

uart0 uart0_seaddr 1

uart0 uart0_seaddr 0

uart0 read stac 1

uart0 read stac 1

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0032 2

uart0 uart0_seaddr 0

uart0 uart0_seaddr 1

uart0 uart0_seaddr 0

uart0 read stac 1

uart0 read stac 1

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0033 3

uart0 uart0_seaddr 0

uart0 uart0_seaddr 1

uart0 uart0_seaddr 0

uart0 read stac 1

uart0 read stac 1

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0034 4

uart0 uart0_seaddr 0

uart0 uart0_seaddr 1

uart0 uart0_seaddr 0

uart0 read stac 1

uart0 read stac 1

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0035 5

uart0 uart0_seaddr 0

uart0 uart0_seaddr 1

uart0 uart0_seaddr 0

uart0 read stac 1

uart0 read stac 1

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0036 6

uart0 uart0_seaddr 0

uart0 uart0_seaddr 1

uart0 uart0_seaddr 0

uart0 read stac 1

uart0 read stac 1

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 read stac 0

uart0 write 0037 7

uart0 uart0_seaddr 0

uart0 uart0_seaddr 1

uart0 uart0_seaddr 0

---test jlc3_soc pass-----------------------------------------thx for try!!! --- Li.XiongHui(juicemail@163.com)

#13 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 【C18官方标准文档】Programming languages — C, Fourth Edition (ISO/IEC 9899:201 » 2022-05-09 10:28:15

- xiaohui

- 回复: 0

RT:非草案

International Standard: Information technology — Programming languages — C, Fourth Edition (ISO/IEC 9899:2018)

晕佬帮忙换下板块吧,不知道要丢哪里去了。。。

magnet:?xt=urn:btih:EB010AED0E34B3D31399D790128350BF98B6F8D5&tr=http%3A%2F%2Fbt2.t-ru.org%2Fann%3Fmagnet&dn=International%20Standard%3A%20Information%20technology%20%E2%80%94%20Programming%20languages%20%E2%80%94%20C%2C%20Fourth%20Edition%20(ISO%2FIEC%209899%3A2018)%20%5B2018%2C%20PDF%2C%20ENG%5D

防止版权问题,请用磁力链!!!

#14 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » [C11官方标准手册]Programming languages - C (INCITS/ISO/IEC 9899:2011[2012]) » 2022-05-09 10:26:53

- xiaohui

- 回复: 0

RT:非草案

American National Standard: Information Technology - Programming languages - C (INCITS/ISO/IEC 9899:2011[2012])

晕佬帮忙换下板块吧,不知道要丢哪里去了。。。

magnet:?xt=urn:btih:0B90C82939E98D39C66F15532331721A285D1A4D&tr=http%3A%2F%2Fbt4.t-ru.org%2Fann%3Fmagnet&dn=INCITS%2FISO%2FIEC%20-%20Programming%20languages%20-%20C%20(INCITS%2FISO%2FIEC%209899%3A2011%5B2012%5D)%20%5B2011%2F2012%2C%20PDF%2C%20ENG%5D

防止版权问题,请用磁力链!!!

#15 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-11-30 14:50:44

分享:不依赖时钟和os调度的uip例子

https://github.com/juiceRv/uip_test_for_juicevm

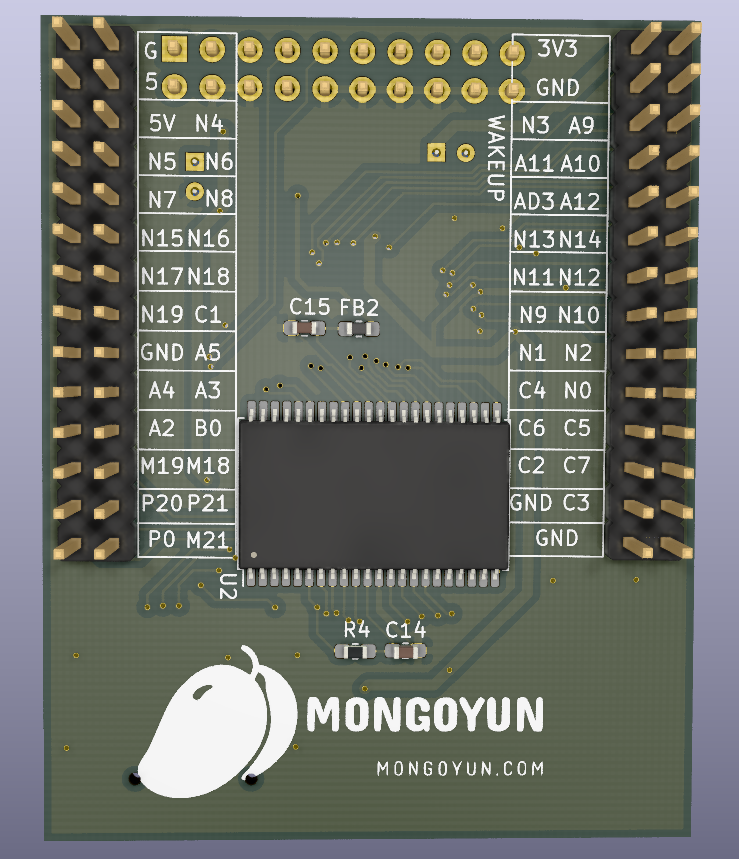

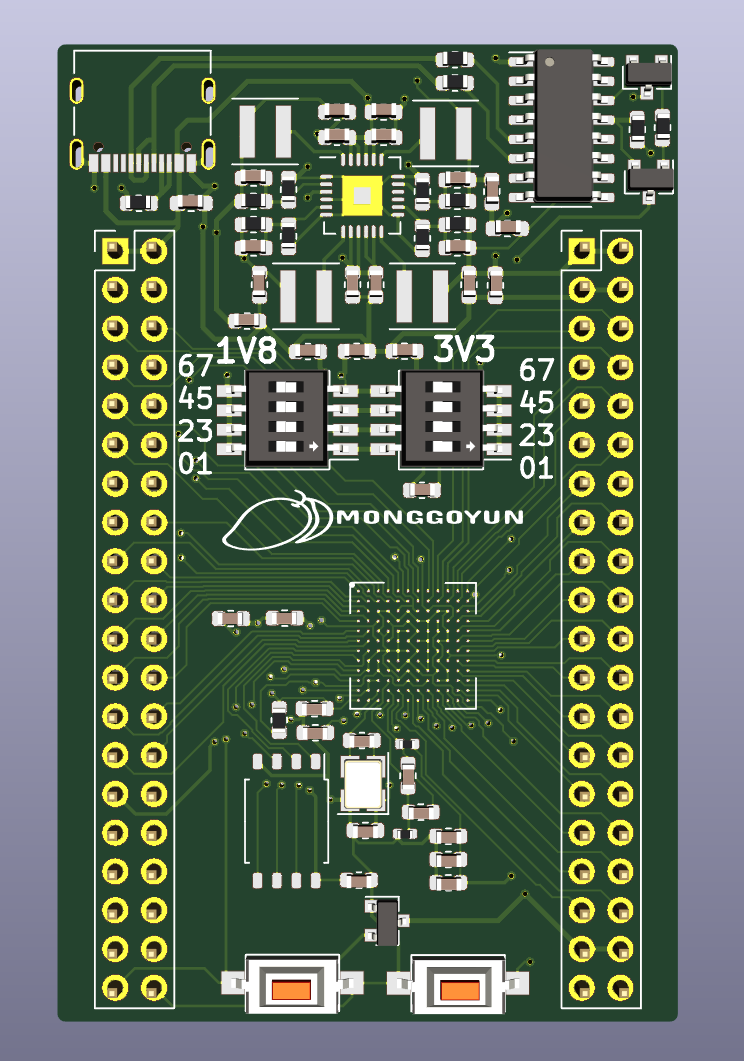

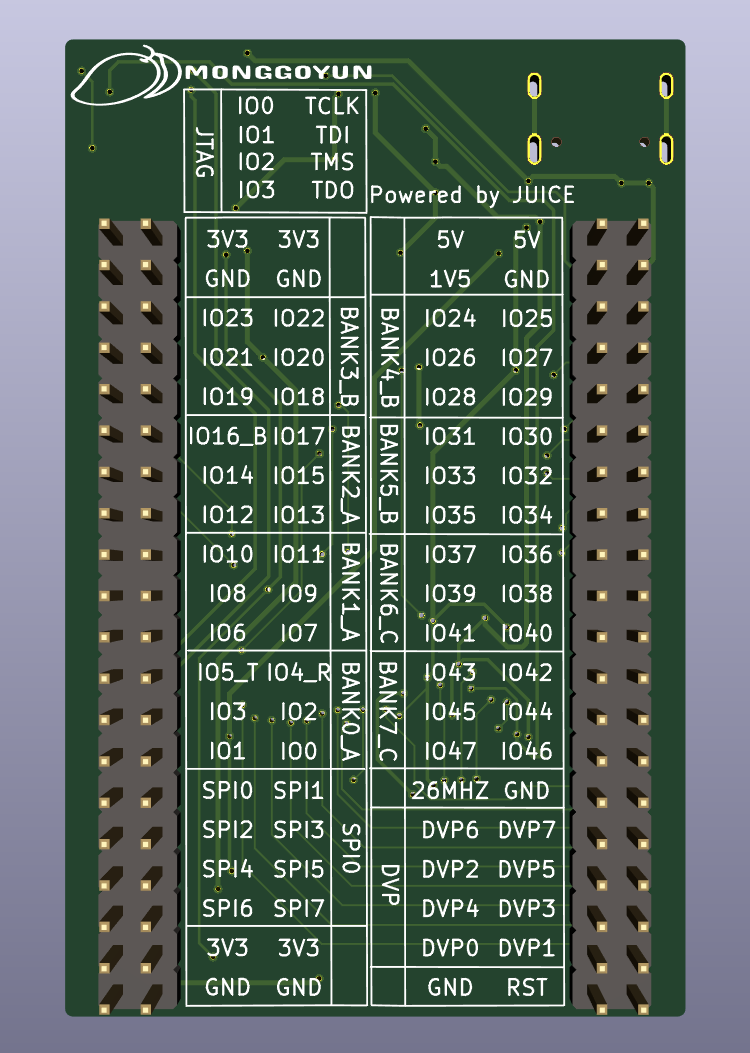

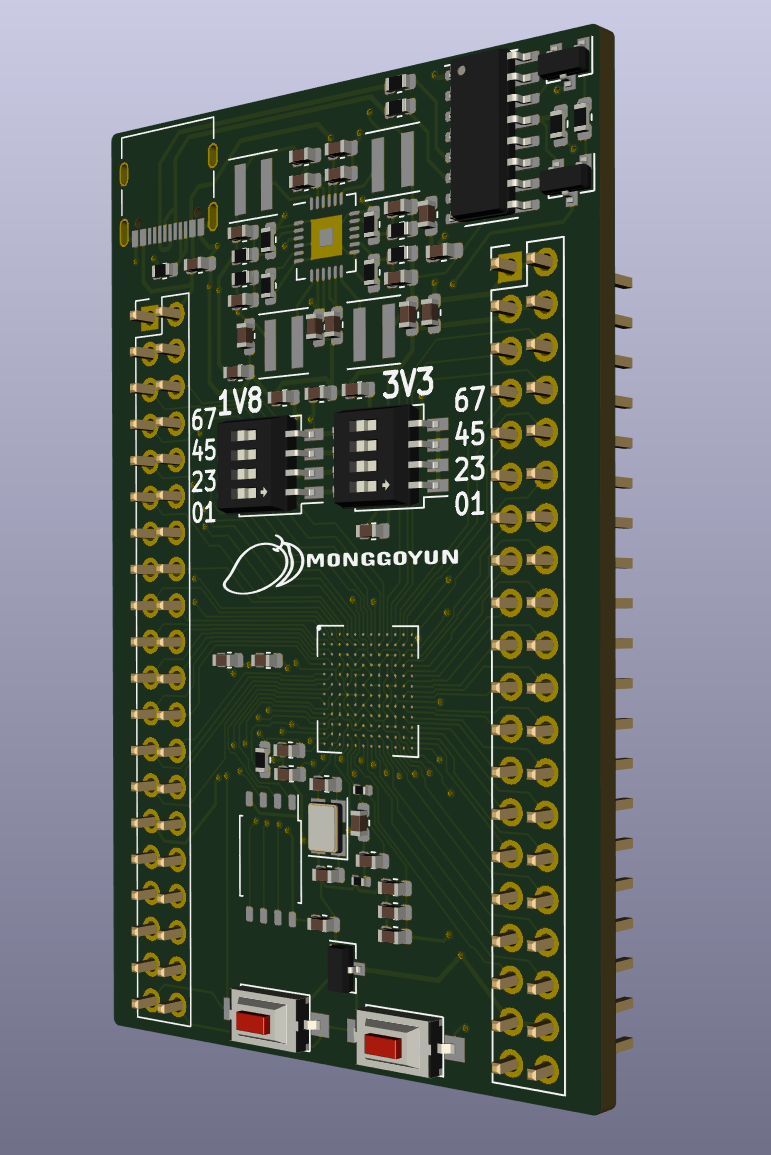

#18 RISC-V » [开源]kendry k210 开发板 » 2021-11-13 17:48:22

- xiaohui

- 回复: 2

#19 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-11-10 15:23:03

2021-11-12更新:

1.在linux平台和window下支持模拟显示器。

juice_vm_release_9bf0c4eb2.zip

加速后的效果

/*

*

* Automatically generated file; DO NOT EDIT.

* JuiceVm Compile Menu

*

*/

#define CONFIG_HAVE_FB_SDL_SUPPORT 1

#define CONFIG_FB_SDL_HEIGHT 480

#define CONFIG_FB_SDL_WIDTH 600/*

* Copyright (c) 2006-2021, JuiceVm Development Team

*

* SPDX-License-Identifier: Apache-2.0

*

* Change Logs:

* Date Author Notes

* 2021/04/22 Juice the first version

*/

#ifndef RV_MTVEC_MAP_INCLUDE

#define RV_MTVEC_MAP_INCLUDE

#include "rv_config.h"

#include <generated/autoconf.h>

#define JUICEVM_RELASE_VERSION 90

// #define mtvec_base_addr 0x5400 // 0x5400=21*1024 BYTE = 21KB

// #define mktime_irq_offet 0x2

#if (defined(JUICEVM_RELASE_VERSION) && (JUICEVM_RELASE_VERSION == 90))

#define rv_sim_pdev_base_addr (0x1000)

#else

#define rv_sim_pdev_base_addr (RV_CPU_SIM_RAM_START_ADDR+RV_CPU_SIM_RAM_SIZE)

#endif

#define rv_sim_pdev_uart0_base_addr (rv_sim_pdev_base_addr)

#define pdev_uart0_write_addr (rv_sim_pdev_uart0_base_addr)

#define pdev_uart0_read_addr (rv_sim_pdev_uart0_base_addr+1)

#define pdev_uart0_free_state 0x00

#define pdev_uart0_readbusy_state 0x01

#define pdev_uart0_state_addr (rv_sim_pdev_uart0_base_addr+2)

#define rv_sim_pdev_mtime_base_addr (rv_sim_pdev_base_addr+3)

#define pdev_mtime_mtime_addr (rv_sim_pdev_mtime_base_addr)

#define pdev_mtime_mtimecmp_addr (rv_sim_pdev_mtime_base_addr+4)

#if (defined(JUICEVM_RELASE_VERSION) && (JUICEVM_RELASE_VERSION == 90))

#define rv_sim_pdev_clint_base_addr (pdev_mtime_mtimecmp_addr+4)

#define rv_sim_pdev_clint_msip_addr (rv_sim_pdev_clint_base_addr) // machine mode software intterupt pending

#define rv_sim_pdev_clint_mtimecmp_addr (rv_sim_pdev_clint_base_addr+0x4000)

#define rv_sim_pdev_clint_mtime_addr (rv_sim_pdev_clint_base_addr+0xBFF8)

#define rv_sim_pdev_clint_max_addr (rv_sim_pdev_clint_mtime_addr)

#define rv_sim_pdev_clint_next_addr (rv_sim_pdev_clint_max_addr+4)

#endif

#ifdef UNIX_COMPILER

#if !defined(ESPIDF)

#define peripheral_device_netcard0 1

#endif // !defined(ESPIDF)

#endif // UNIX_COMPILER

// #if (peripheral_device_netcard0 == 1)

#if (defined(JUICEVM_RELASE_VERSION) && (JUICEVM_RELASE_VERSION == 90))

#define pdev_netcard0_base_addr (rv_sim_pdev_clint_next_addr)

#define pdev_netcard0_write_addr (pdev_netcard0_base_addr)

#define pdev_netcard0_write_end_addr (pdev_netcard0_base_addr+1500)

#define pdev_netcard0_write_cnt_H_addr (pdev_netcard0_write_end_addr+1)

#define pdev_netcard0_write_cnt_L_addr (pdev_netcard0_write_cnt_H_addr+2)

#define pdev_netcard0_write_start_addr (pdev_netcard0_write_cnt_L_addr+2)

#define pdev_netcard0_read_addr (pdev_netcard0_write_start_addr+1)

#define pdev_netcard0_read_end_addr (pdev_netcard0_read_addr+1500)

#define pdev_netcard0_readbuf_cnt_H_addr (pdev_netcard0_read_end_addr+1)

#define pdev_netcard0_readbuf_cnt_L_addr (pdev_netcard0_readbuf_cnt_H_addr+1)

#define pdev_netcard0_state_addr (pdev_netcard0_readbuf_cnt_L_addr+2)

#define pdev_netcard0_max_addr (pdev_netcard0_state_addr)

#define pdev_netcard0_next_addr (pdev_netcard0_state_addr+1)

#define pdev_netcard0_free_state 0x00

#define pdev_netcard0_readbusy_state 0x01

#else

#error("not support netcard yet");

#endif

// #endif // (peripheral_device_netcard0 == 1)

// #if (defined(CONFIG_HAVE_FB_SDL_SUPPORT))

#if (defined(JUICEVM_RELASE_VERSION) && (JUICEVM_RELASE_VERSION == 90))

#define pdev_fb0_base_addr (pdev_netcard0_next_addr)

#define pdev_fb0_write_x_H_addr (pdev_fb0_base_addr+1)

#define pdev_fb0_write_x_L_addr (pdev_fb0_base_addr+2)

#define pdev_fb0_write_y_H_addr (pdev_fb0_base_addr+3)

#define pdev_fb0_write_y_L_addr (pdev_fb0_base_addr+4)

#define pdev_fb0_write_r_addr (pdev_fb0_write_y_L_addr+1)

#define pdev_fb0_write_g_addr (pdev_fb0_write_y_L_addr+2)

#define pdev_fb0_write_b_addr (pdev_fb0_write_y_L_addr+3)

#define pdev_fb0_write_set_addr (pdev_fb0_write_y_L_addr+4)

#define pdev_fb0_write_render_addr (pdev_fb0_write_y_L_addr+5)

#define pdev_fb0_max_addr (pdev_fb0_write_render_addr)

#define pdev_fb0_next_addr (pdev_fb0_write_render_addr+1)

#else

#error("not support fb0 yet");

#endif

// #endif // (defined(CONFIG_HAVE_FB_SDL_SUPPORT))

#define uart0_irq_flag 1

#define uart0_irq_ecode 24

#define RV_exception_Instruction_address_misaligned_IFLAG 0

#define RV_exception_Instruction_address_misaligned_ECODE 0

#define RV_exception_Instruction_access_fault_IFLAG 0

#define RV_exception_Instruction_access_fault_ECODE 1

#define RV_exception_Illegal_Instruction_IFLAG 0

#define RV_exception_Illegal_Instruction_ECODE 2

#define RV_exception_Breakpoint_IFLAG 0

#define RV_exception_Breakpoint_ECODE 3

#define RV_exception_LoadAddress_Misaligned_IFLAG 0

#define RV_exception_LoadAddress_Misaligned_ECODE 4

#define RV_exception_Load_access_fault_IFLAG 0

#define RV_exception_Load_access_fault_ECODE 5

#define RV_exception_Store_or_AMO_Address_Misaligned_IFLAG 0

#define RV_exception_Store_or_AMO_Address_Misaligned_ECODE 6

#define RV_exception_Store_or_AMO_access_fault_IFLAG 0

#define RV_exception_Store_or_AMO_access_fault_ECODE 7

#define RV_exception_Environment_call_from_Umode_IFLAG 0

#define RV_exception_Environment_call_from_Umode_ECODE 8

#define RV_exception_Environment_call_from_Smode_IFLAG 0

#define RV_exception_Environment_call_from_Smode_ECODE 9

// https://zhuanlan.zhihu.com/p/164394603

#define RV_exception_Environment_Call_FromMachine_IFLAG 0

#define RV_exception_Environment_Call_FromMachine_ECODE 11

#define RV_exception_Environment_Call_FromUser_IFLAG 0

#define RV_exception_Environment_Call_FromUser_ECODE 8

#define RV_exception_Environment_Call_FromSupervisor_IFLAG 0

#define RV_exception_Environment_Call_FromSupervisor_ECODE 9

#define RV_exception_FloatingPoint_Disabled_IFLAG

#define RV_exception_FloatingPoint_Disabled_ECODE

#define RV_exception_Instruction_page_fault_IFLAG 0

#define RV_exception_Instruction_page_fault_ECODE 12

#define RV_exception_Load_page_fault_IFLAG 0

#define RV_exception_Load_page_fault_ECODE 13

#define RV_exception_Store_or_AMO_page_fault_IFLAG 0

#define RV_exception_Store_or_AMO_page_fault_ECODE 15

// Interrupt Exception Code Description

// 1 0 Reserved

// 1 1 Supervisor software interrupt not support

// 1 2 Reserved

// 1 3 Machine software interrupt not support

// 1 4 Reserved

// 1 5 Supervisor timer interrupt not support

// 1 6 Reserved

// 1 7 Machine timer interrupt support

// 1 8 Reserved

// 1 9 Supervisor external interrupt not support

// 1 10 Reserved

// 1 11 Machine external interrupt not support

// 1 12 Reserved

// 1 13 Reserved

// 1 14 Reserved

// 1 15 Reserved

// // 1 ≥16 Designated for platform use

// 0 0 Instruction address misaligned not support

// 0 1 Instruction access fault not support

// 0 2 Illegal instruction support

// 0 3 Breakpoint support

// 0 4 Load address misaligned support

// 0 5 Load access fault not support

// 0 6 Store/AMO address misaligned support

// 0 7 Store/AMO access fault not support

// 0 8 Environment call from U-mode not support

// 0 9 Environment call from S-mode not support

// 0 10 Reserved

// 0 11 Environment call from M-mode support

// 0 12 Instruction page fault not support

// 0 13 Load page fault not support

// 0 14 Reserved

// 0 15 Store/AMO page fault not support

// 0 16-23 Reserved

// // 0 24–31 Designated for custom use

// 0 32-47 Reserved

// // 0 48–63 Designated for custom use

// 0 ≥64 Reserved

// #define mtime_irq_flag 1

// #define mtime_irq_ecode 7

#define RV_Supervisor_software_interrupt_IFLAG 1

#define RV_Supervisor_software_interrupt_ECODE 1

#define RV_Machine_software_interrupt_IFLAG 1

#define RV_Machine_software_interrupt_ECODE 3

#define RV_User_timer_interrupt_IFLAG 1

#define RV_User_timer_interrupt_ECODE 4

#define RV_Supervisor_timer_interrupt_IFLAG 1

#define RV_Supervisor_timer_interrupt_ECODE 5

#define RV_Machine_timer_interrupt_IFLAG 1

#define RV_Machine_timer_interrupt_ECODE 7

#define RV_Supervisor_external_interrupt_IFLAG 1

#define RV_Supervisor_external_interrupt_ECODE 9

#define RV_Machine_external_interrupt_IFLAG 1

#define RV_Machine_external_interrupt_ECODE 10

#endif // RV_MTVEC_MAP_INCLUDE#20 Re: 全志 SOC » 试试用F1C100s来3D绘图 » 2021-11-01 12:50:52

[开源]tinygl的sdl后端,跨平台opengl的子集tinygl运行

https://whycan.com/t_7321.html

#21 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-11-01 12:49:35

大佬,什么时候会开源啊。非常好奇想学习一下的说

他的外设和组件已经在逐步开源了呢。

gdb组件开源:

https://github.com/juiceRv/gdb_stub_for_juicevm

fb组件开源:

https://github.com/juiceRv/tinygl_sdl_test

暂时不开源虚拟机的cpu部分。

cpu部分以为耦合性比较强,正在拆分成多级流水线的实现方式,使用内置的调度器进行并行处理。所以暂时没有开源时间公布。

#22 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » [开源]tinygl的sdl后端,跨平台opengl的子集tinygl运行 » 2021-11-01 12:31:06

- xiaohui

- 回复: 2

RT.

github: https://github.com/juicerv/tinygl_sdl_test

#23 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-10-25 12:07:22

uip_test:

uip_test.zip

/*

* Copyright (c) 2006-2021, JuiceVm Development Team

*

* SPDX-License-Identifier: Apache-2.0

*

* Change Logs:

* Date Author Notes

* 2021/04/22 Juice the first version

*/

#ifndef RV_MTVEC_MAP_INCLUDE

#define RV_MTVEC_MAP_INCLUDE

#include "rv_config.h"

#define JUICEVM_RELASE_VERSION 90

// #define mtvec_base_addr 0x5400 // 0x5400=21*1024 BYTE = 21KB

// #define mktime_irq_offet 0x2

#define RAM_SIZE_KB (1024)

#define RAM_SIZE_MB (1024*RAM_SIZE_KB)

#define RAM_SIZE_GB (1024*RAM_SIZE_MB)

#define RV_CPU_SIM_RAM_START_ADDR ((_cur_rv_uint)(0x80000000))

#define RV_CPU_SIM_RAM_SIZE ((_cur_rv_uint)(256 * RAM_SIZE_MB))

#if (defined(JUICEVM_RELASE_VERSION) && (JUICEVM_RELASE_VERSION == 90))

#define rv_sim_pdev_base_addr (0x1000)

#else

#define rv_sim_pdev_base_addr (RV_CPU_SIM_RAM_START_ADDR+RV_CPU_SIM_RAM_SIZE)

#endif

#define rv_sim_pdev_uart0_base_addr (rv_sim_pdev_base_addr)

#define pdev_uart0_write_addr (rv_sim_pdev_uart0_base_addr)

#define pdev_uart0_read_addr (rv_sim_pdev_uart0_base_addr+1)

#define pdev_uart0_free_state 0x00

#define pdev_uart0_readbusy_state 0x01

#define pdev_uart0_state_addr (rv_sim_pdev_uart0_base_addr+2)

#define rv_sim_pdev_mtime_base_addr (rv_sim_pdev_base_addr+3)

#define pdev_mtime_mtime_addr (rv_sim_pdev_mtime_base_addr)

#define pdev_mtime_mtimecmp_addr (rv_sim_pdev_mtime_base_addr+4)

#if (defined(JUICEVM_RELASE_VERSION) && (JUICEVM_RELASE_VERSION == 90))

#define rv_sim_pdev_clint_base_addr (pdev_mtime_mtimecmp_addr+4)

#define rv_sim_pdev_clint_msip_addr (rv_sim_pdev_clint_base_addr) // machine mode software intterupt pending

#define rv_sim_pdev_clint_mtimecmp_addr (rv_sim_pdev_clint_base_addr+0x4000)

#define rv_sim_pdev_clint_mtime_addr (rv_sim_pdev_clint_base_addr+0xBFF8)

#define rv_sim_pdev_clint_max_addr (rv_sim_pdev_clint_mtime_addr)

#define rv_sim_pdev_clint_next_addr (rv_sim_pdev_clint_max_addr+4)

#endif

#ifdef UNIX_COMPILER

#if !defined(ESPIDF)

#define peripheral_device_netcard0 1

#endif // !defined(ESPIDF)

#endif // UNIX_COMPILER

#if (peripheral_device_netcard0 == 1)

#if (defined(JUICEVM_RELASE_VERSION) && (JUICEVM_RELASE_VERSION == 90))

#define pdev_netcard0_base_addr (rv_sim_pdev_clint_next_addr)

#define pdev_netcard0_write_addr (pdev_netcard0_base_addr)

#define pdev_netcard0_write_end_addr (pdev_netcard0_base_addr+1500)

#define pdev_netcard0_write_cnt_H_addr (pdev_netcard0_write_end_addr+1)

#define pdev_netcard0_write_cnt_L_addr (pdev_netcard0_write_cnt_H_addr+2)

#define pdev_netcard0_write_start_addr (pdev_netcard0_write_cnt_L_addr+2)

#define pdev_netcard0_read_addr (pdev_netcard0_write_start_addr+1)

#define pdev_netcard0_read_end_addr (pdev_netcard0_read_addr+1500)

#define pdev_netcard0_readbuf_cnt_H_addr (pdev_netcard0_read_end_addr+1)

#define pdev_netcard0_readbuf_cnt_L_addr (pdev_netcard0_readbuf_cnt_H_addr+1)

#define pdev_netcard0_state_addr (pdev_netcard0_readbuf_cnt_L_addr+2)

#define pdev_netcard0_max_addr (pdev_netcard0_state_addr)

#define pdev_netcard0_next_addr (pdev_netcard0_state_addr+1)

#define pdev_netcard0_free_state 0x00

#define pdev_netcard0_readbusy_state 0x01

#else

#error("not support netcard yet");

#endif

#endif // (peripheral_device_netcard0 == 1)

#define uart0_irq_flag 1

#define uart0_irq_ecode 24

#define RV_exception_Instruction_address_misaligned_IFLAG 0

#define RV_exception_Instruction_address_misaligned_ECODE 0

#define RV_exception_Instruction_access_fault_IFLAG 0

#define RV_exception_Instruction_access_fault_ECODE 1

#define RV_exception_Illegal_Instruction_IFLAG 0

#define RV_exception_Illegal_Instruction_ECODE 2

#define RV_exception_Breakpoint_IFLAG 0

#define RV_exception_Breakpoint_ECODE 3

#define RV_exception_LoadAddress_Misaligned_IFLAG 0

#define RV_exception_LoadAddress_Misaligned_ECODE 4

#define RV_exception_Load_access_fault_IFLAG 0

#define RV_exception_Load_access_fault_ECODE 5

#define RV_exception_Store_or_AMO_Address_Misaligned_IFLAG 0

#define RV_exception_Store_or_AMO_Address_Misaligned_ECODE 6

#define RV_exception_Store_or_AMO_access_fault_IFLAG 0

#define RV_exception_Store_or_AMO_access_fault_ECODE 7

#define RV_exception_Environment_call_from_Umode_IFLAG 0

#define RV_exception_Environment_call_from_Umode_ECODE 8

#define RV_exception_Environment_call_from_Smode_IFLAG 0

#define RV_exception_Environment_call_from_Smode_ECODE 9

// https://zhuanlan.zhihu.com/p/164394603

#define RV_exception_Environment_Call_FromMachine_IFLAG 0

#define RV_exception_Environment_Call_FromMachine_ECODE 11

#define RV_exception_Environment_Call_FromUser_IFLAG 0

#define RV_exception_Environment_Call_FromUser_ECODE 8

#define RV_exception_Environment_Call_FromSupervisor_IFLAG 0

#define RV_exception_Environment_Call_FromSupervisor_ECODE 9

#define RV_exception_FloatingPoint_Disabled_IFLAG

#define RV_exception_FloatingPoint_Disabled_ECODE

#define RV_exception_Instruction_page_fault_IFLAG 0

#define RV_exception_Instruction_page_fault_ECODE 12

#define RV_exception_Load_page_fault_IFLAG 0

#define RV_exception_Load_page_fault_ECODE 13

#define RV_exception_Store_or_AMO_page_fault_IFLAG 0

#define RV_exception_Store_or_AMO_page_fault_ECODE 15

// Interrupt Exception Code Description

// 1 0 Reserved

// 1 1 Supervisor software interrupt not support

// 1 2 Reserved

// 1 3 Machine software interrupt not support

// 1 4 Reserved

// 1 5 Supervisor timer interrupt not support

// 1 6 Reserved

// 1 7 Machine timer interrupt support

// 1 8 Reserved

// 1 9 Supervisor external interrupt not support

// 1 10 Reserved

// 1 11 Machine external interrupt not support

// 1 12 Reserved

// 1 13 Reserved

// 1 14 Reserved

// 1 15 Reserved

// // 1 ≥16 Designated for platform use

// 0 0 Instruction address misaligned not support

// 0 1 Instruction access fault not support

// 0 2 Illegal instruction support

// 0 3 Breakpoint support

// 0 4 Load address misaligned support

// 0 5 Load access fault not support

// 0 6 Store/AMO address misaligned support

// 0 7 Store/AMO access fault not support

// 0 8 Environment call from U-mode not support

// 0 9 Environment call from S-mode not support

// 0 10 Reserved

// 0 11 Environment call from M-mode support

// 0 12 Instruction page fault not support

// 0 13 Load page fault not support

// 0 14 Reserved

// 0 15 Store/AMO page fault not support

// 0 16-23 Reserved

// // 0 24–31 Designated for custom use

// 0 32-47 Reserved

// // 0 48–63 Designated for custom use

// 0 ≥64 Reserved

// #define mtime_irq_flag 1

// #define mtime_irq_ecode 7

#define RV_Supervisor_software_interrupt_IFLAG 1

#define RV_Supervisor_software_interrupt_ECODE 1

#define RV_Machine_software_interrupt_IFLAG 1

#define RV_Machine_software_interrupt_ECODE 3

#define RV_User_timer_interrupt_IFLAG 1

#define RV_User_timer_interrupt_ECODE 4

#define RV_Supervisor_timer_interrupt_IFLAG 1

#define RV_Supervisor_timer_interrupt_ECODE 5

#define RV_Machine_timer_interrupt_IFLAG 1

#define RV_Machine_timer_interrupt_ECODE 7

#define RV_Supervisor_external_interrupt_IFLAG 1

#define RV_Supervisor_external_interrupt_ECODE 9

#define RV_Machine_external_interrupt_IFLAG 1

#define RV_Machine_external_interrupt_ECODE 10

#endif // RV_MTVEC_MAP_INCLUDE#24 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-10-25 12:01:54

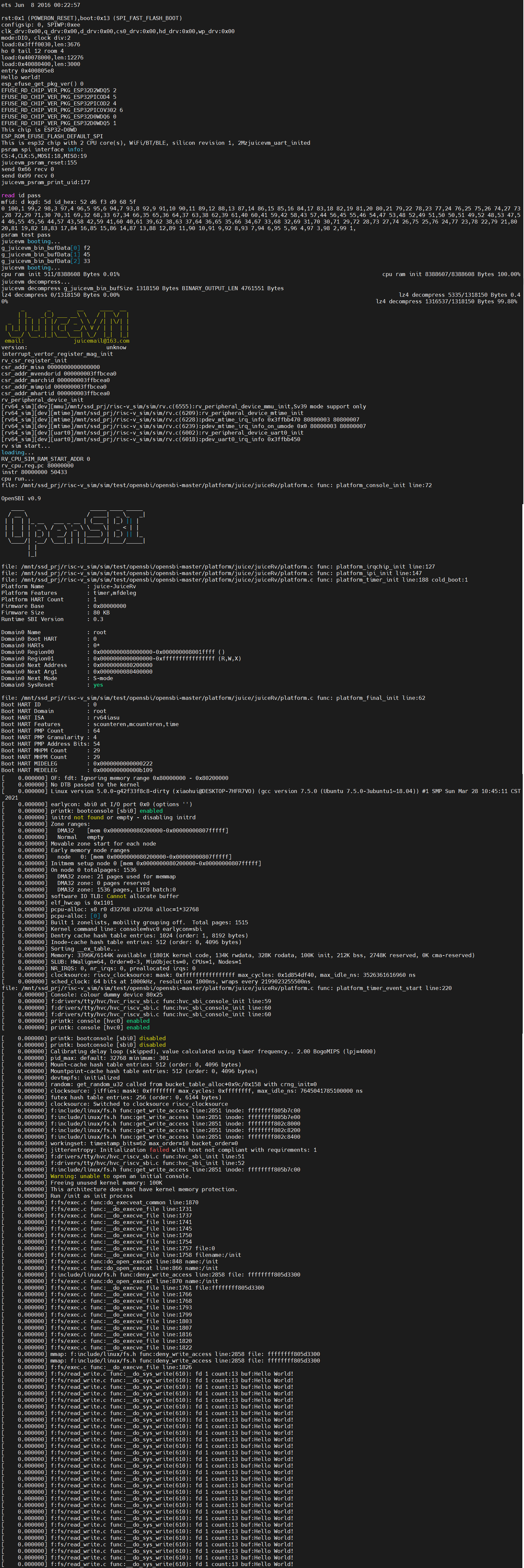

2021-10-24更新:

1.修复指令bug并通过risc-v官方指令集测试。

2.成功启动busybox。

3.在linux平台下支持模拟网卡。

juice_vm_release_f6bb27902.zip

linux运行固件:

fw_payload.zip

#25 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-09-16 13:25:26

20210916更新:

https://github.com/juiceRv/JuiceVm/blob/master/juice_vm_release_for_Linux_and_mingw64_laster.zip

feat(allwinner-d1): add allwinner d1 support

#26 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-09-02 19:59:47

#27 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-09-02 19:59:08

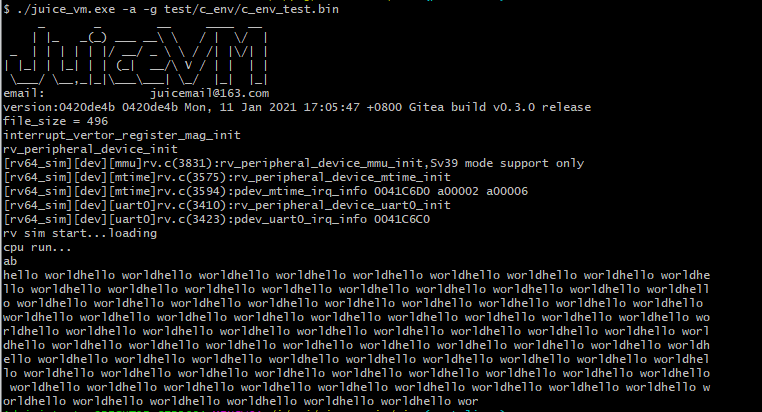

顺便给大家献上risc-v32下的测试代码:

rv32_test_c_env.zip

为了大家需要打字才可以运行,编译代码如下:

wget https://github.com/xpack-dev-tools/riscv-none-embed-gcc-xpack/releases/download/v8.3.0-2.1/xpack-riscv-none-embed-gcc-8.3.0-2.1-linux-x64.tar.gz

tar vxf xpack-riscv-none-embed-gcc-8.3.0-2.1-linux-x64.tar.gz

unzip rv32_test_c_env.zip

cd rv32_test_c_env

make CROSS_COMPILE=../xpack-riscv-none-embed-gcc-8.3.0-2.1/bin/riscv-none-embed-

./juicevm_rv32_for_Linux.out -a -g ./c_env_test.bin

运行效果:

global_vm_log_init juicevm_rv_output_mode_sel: 0 JUICE_VM_LOG_MAX_NUM:6000

_ _ __ ____ __

| |_ _(_) ___ __\ \ / | \/ |

_ | | | | | |/ __/ _ \ \ / /| |\/| |

| |_| | |_| | | (_| __/\ V / | | | |

\___/ \__,_|_|\___\___| \_/ |_| |_|

email: juicemail@163.com

version:f73bcb1c f73bcb1c Thu, 2 Sep 2021 19:39:22 +0800 xiaohui Merge branch 'master' of e.coding.net:xiaoxiaohuixxh/risc-v_vm/risc-v_sim

firm_addr:../../rv32_test/c_env/c_env_test.bin

fd = 3

file_size = 16928

[rv64_sim][dev][mem]main.c(280):RV_CPU_SIM_RAM_START_ADDR 7fbec83cce0b

[rv64_sim][dev][mem]main.c(284):RV_CPU_SIM_RAM_SIZE 8388608 Bytes 8.000000 MiB

interrupt_vertor_register_mag_init

rv_csr_register_init

csr_addr_misa 40140101

csr_addr_mvendorid 00000000

csr_addr_marchid 00000000

csr_addr_mimpid 00000000

csr_addr_mhartid 00000000

rv_peripheral_device_init

[rv64_sim][dev][mmu]rv_pdev.c(605):rv_peripheral_device_mmu_init,Sv39 mode support only

[rv64_sim][dev][mtime]rv_pdev.c(247):rv_peripheral_device_mtime_init

[rv64_sim][dev][mtime]rv_pdev.c(272):pdev_mtime_irq_info 0x7fffd20ac734 80800003 80800007

[rv64_sim][proc][err]rv.c[interrupt_vertor_register32](825){pc:0000000000000000}:interrupt_vertor_register err->irq info err irq_v 1 addr_min 4

[rv64_sim][dev][mtime]rv_pdev.c(283):pdev_mtime_irq_info_on_umode (nil) 80800003 80800007

[rv64_sim][dev][uart0]rv_pdev.c(32):rv_peripheral_device_uart0_init

[rv64_sim][dev][uart0]rv_pdev.c(48):pdev_uart0_irq_info 0x7fffd20ac724

[rv64_sim][dev][uart0]rv_pdev.c(49):pdev_uart0_write_addr 80800000

[rv64_sim][dev][uart0]rv_pdev.c(50):pdev_uart0_state_addr 80800002

[rv64_sim][dev][fb0]framebuffer.c(24):rv_peripheral_device_fb0_init

rv sim start...

loading...

RV_CPU_SIM_RAM_START_ADDR 80000000

rv_cpu->reg.pc 80000000

instr 80000000 100117

cpu run...

ab

hello world1

#28 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-09-02 19:53:28

20210902更新:

可能有小伙伴以为juicevm不更新了,打算做成TLS的,这次更新时间长是因为我把代码框架重构了,为后面的多核和多架构支持做好了准备。

这次更新除了框架重构外还添加了risc-v32 ima的支持(在rv32下暂不支持任何MMU,但是已经在TODO里啦,只要是RV32支持的将全都有),还即将支持用设备树来实现动态的寄存器地址和外设配置呢。下面我们下载下最新的支持体验下吧!!!

这次上传只打包了linux下的版本,window和macos的在路上了。

juice_vm_release_for_Linux_f73bcb1c.zip

#29 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-09-02 19:47:43

#30 Re: Cortex M0/M3/M4/M7 » 2.通过LWIP协议栈使用学习http,tcp,网卡之间的关系. » 2021-08-12 01:24:21

多年前写的一个超精简的协议栈: https://github.com/xiaoxiaohuixxh/McuInternet

#31 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-08-10 14:51:19

#32 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-08-10 12:22:35

#34 Re: RISC-V » juiceVm risc-v虚拟机在esp32上运行linux kernel » 2021-08-07 14:12:01

同样是WROVER-B,cpu ram init到99.60%的时候,速度突然变慢,而且卡在了下图:

https://whycan.com/files/members/1315/Screenshot121824.png

这里是在解压,压缩率有点高,解压有点慢。

#35 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-08-05 13:36:35

#36 Re: RISC-V » juiceVm risc-v虚拟机在esp32上运行linux kernel » 2021-08-02 19:14:26

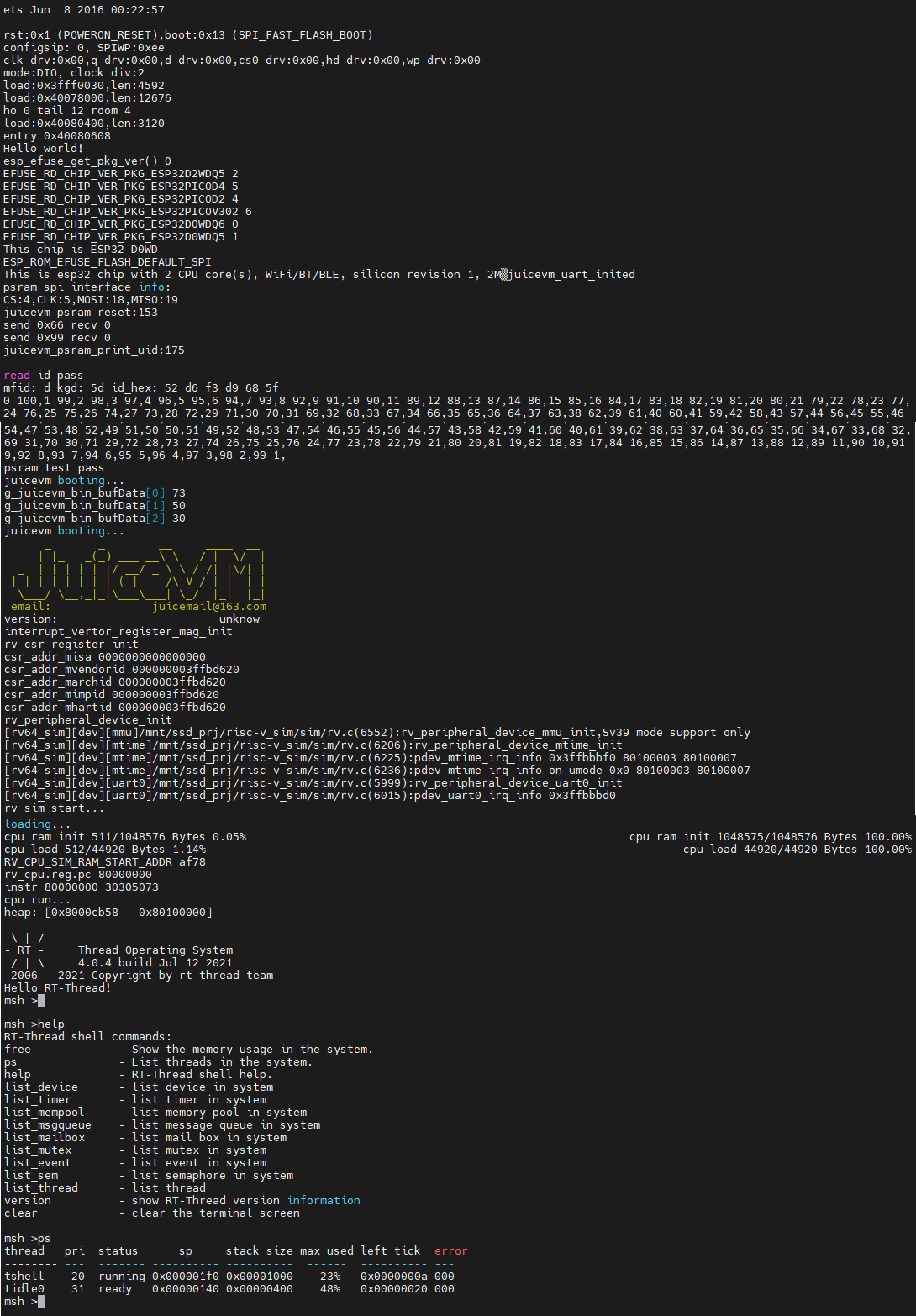

@findie

上传esp32 WROVER-B支持的固件

juicevm-risc-v_vm-for-esp32_wrover_20210812.zip

启动日志

ets Jun 8 2016 00:22:57

rst:0x1 (POWERON_RESET),boot:0x13 (SPI_FAST_FLASH_BOOT)

configsip: 0, SPIWP:0xee

clk_drv:0x00,q_drv:0x00,d_drv:0x00,cs0_drv:0x00,hd_drv:0x00,wp_drv:0x00

mode:DIO, clock div:2

load:0x3fff0030,len:3676

ho 0 tail 12 room 4

load:0x40078000,len:12276

load:0x40080400,len:3000

entry 0x400805e8

Thisjuicevm_uart_inited

psram size 8MiB

Himem has 4456448 B of memory, 4456448 B of which is free. Testing the free memory...

Himem has 4MiB of memory, 4MiB of which is free. Testing the free memory...

esp_himem_reserved_area_size is 262144MiB of memory

heap_caps_get_free_size: 3930007

heap_caps_get_free_size + memfree: 8386455

heap_caps_get_largest_free_block: 2097152

esp_get_minimum_free_heap_size: 4181999

tmp_addr 0 low_mem_p 3f80086c

tmp_addr 1 low_mem_p 3f808870

tmp_addr 2 low_mem_p 3f810874

tmp_addr 3 low_mem_p 3f818878

tmp_addr 4 low_mem_p 3f82087c

tmp_addr 5 low_mem_p 3f828880

tmp_addr 6 low_mem_p 3f830884

tmp_addr 7 low_mem_p 3f838888

tmp_addr 8 low_mem_p 3f84088c

tmp_addr 9 low_mem_p 3f848890

tmp_addr 10 low_mem_p 3f850894

tmp_addr 11 low_mem_p 3f858898

tmp_addr 12 low_mem_p 3f86089c

tmp_addr 13 low_mem_p 3f8688a0

tmp_addr 14 low_mem_p 3f8708a4

tmp_addr 15 low_mem_p 3f8788a8

tmp_addr 16 low_mem_p 3f8808ac

tmp_addr 17 low_mem_p 3f8888b0

tmp_addr 18 low_mem_p 3f8908b4

tmp_addr 19 low_mem_p 3f8988b8

tmp_addr 20 low_mem_p 3f8a08bc

tmp_addr 21 low_mem_p 3f8a88c0

tmp_addr 22 low_mem_p 3f8b08c4

tmp_addr 23 low_mem_p 3f8b88c8

tmp_addr 24 low_mem_p 3f8c08cc

tmp_addr 25 low_mem_p 3f8c88d0

tmp_addr 26 low_mem_p 3f8d08d4

tmp_addr 27 low_mem_p 3f8d88d8

tmp_addr 28 low_mem_p 3f8e08dc

tmp_addr 29 low_mem_p 3f8e88e0

tmp_addr 30 low_mem_p 3f8f08e4

tmp_addr 31 low_mem_p 3f8f88e8

tmp_addr 32 low_mem_p 3f9008ec

tmp_addr 33 low_mem_p 3f9088f0

tmp_addr 34 low_mem_p 3f9108f4

tmp_addr 35 low_mem_p 3f9188f8

tmp_addr 36 low_mem_p 3f9208fc

tmp_addr 37 low_mem_p 3f928900

tmp_addr 38 low_mem_p 3f930904

tmp_addr 39 low_mem_p 3f938908

tmp_addr 40 low_mem_p 3f94090c

tmp_addr 41 low_mem_p 3f948910

tmp_addr 42 low_mem_p 3f950914

tmp_addr 43 low_mem_p 3f958918

tmp_addr 44 low_mem_p 3f96091c

tmp_addr 45 low_mem_p 3f968920

tmp_addr 46 low_mem_p 3f970924

tmp_addr 47 low_mem_p 3f978928

tmp_addr 48 low_mem_p 3f98092c

tmp_addr 49 low_mem_p 3f988930

tmp_addr 50 low_mem_p 3f990934

tmp_addr 51 low_mem_p 3f998938

tmp_addr 52 low_mem_p 3f9a093c

tmp_addr 53 low_mem_p 3f9a8940

tmp_addr 55 low_mem_p 3f9b8948

tmp_addr 56 low_mem_p 3f9c094c

tmp_addr 57 low_mem_p 3f9c8950

tmp_addr 58 low_mem_p 3f9d0954

tmp_addr 59 low_mem_p 3f9d8958

tmp_addr 60 low_mem_p 3f9e095c

tmp_addr 61 low_mem_p 3f9e8960

tmp_addr 62 low_mem_p 3f9f0964

tmp_addr 63 low_mem_p 3f9f8968

tmp_addr 64 low_mem_p 3fa0096c

tmp_addr 65 low_mem_p 3fa08970

tmp_addr 66 low_mem_p 3fa10974

tmp_addr 67 low_mem_p 3fa18978

tmp_addr 68 low_mem_p 3fa2097c

tmp_addr 69 low_mem_p 3fa28980

tmp_addr 70 low_mem_p 3fa30984

tmp_addr 71 low_mem_p 3fa38988

tmp_addr 72 low_mem_p 3fa4098c

tmp_addr 73 low_mem_p 3fa48990

tmp_addr 74 low_mem_p 3fa50994

tmp_addr 75 low_mem_p 3fa58998

tmp_addr 76 low_mem_p 3fa6099c

tmp_addr 77 low_mem_p 3fa689a0

tmp_addr 78 low_mem_p 3fa709a4

tmp_addr 79 low_mem_p 3fa789a8

tmp_addr 80 low_mem_p 3fa809ac

tmp_addr 81 low_mem_p 3fa889b0

tmp_addr 82 low_mem_p 3fa909b4

tmp_addr 83 low_mem_p 3fa989b8

tmp_addr 84 low_mem_p 3faa09bc

tmp_addr 85 low_mem_p 3faa89c0

tmp_addr 86 low_mem_p 3fab09c4

tmp_addr 87 low_mem_p 3fab89c8

tmp_addr 88 low_mem_p 3fac09cc

tmp_addr 89 low_mem_p 3fac89d0

tmp_addr 90 low_mem_p 3fad09d4

tmp_addr 91 low_mem_p 3fad89d8

tmp_addr 92 low_mem_p 3fae09dc

tmp_addr 93 low_mem_p 3fae89e0

tmp_addr 94 low_mem_p 3faf09e4

tmp_addr 95 low_mem_p 3faf89e8

tmp_addr 96 low_mem_p 3fb009ec

tmp_addr 97 low_mem_p 3fb089f0

tmp_addr 98 low_mem_p 3fb109f4

tmp_addr 99 low_mem_p 3fb189f8

tmp_addr 100 low_mem_p 3fb209fc

tmp_addr 101 low_mem_p 3fb28a00

tmp_addr 102 low_mem_p 3fb30a04

tmp_addr 103 low_mem_p 3fb38a08

tmp_addr 104 low_mem_p 3fb40a0c

tmp_addr 105 low_mem_p 3fb48a10

tmp_addr 106 low_mem_p 3fb50a14

tmp_addr 107 low_mem_p 3fb58a18

tmp_addr 108 low_mem_p 3fb60a1c

tmp_addr 109 low_mem_p 3fb68a20

tmp_addr 110 low_mem_p 3fb70a24

tmp_addr 111 low_mem_p 3fb78a28

tmp_addr 112 low_mem_p 3fb80a2c

tmp_addr 113 low_mem_p 3fb88a30

tmp_addr 114 low_mem_p 3fb90a34

tmp_addr 115 low_mem_p 3fb98a38

tmp_addr 116 low_mem_p 3fba0a3c

tmp_addr 117 low_mem_p 3fba8a40

tmp_addr 118 low_mem_p 3fbb0a44

tmp_addr 119 low_mem_p 3ffc1080

low_mem_size 3932160 low_mem_p 3f80086c

hi_mem_size + low_mem_size 8388608

Done!

Done!

juicevm booting...

g_juicevm_bin_bufData[0] b0

g_juicevm_bin_bufData[1] 73

g_juicevm_bin_bufData[2] 50

juicevm booting...

cpu ram init 48519/8388608 Bytes 0.58%

...

cpu ram init 8388487/8388608 Bytes 100.00%

cpu ram init 8388607/8388608 Bytes 100.00%

juicevm decompress...

juicevm decompress g_juicevm_bin_bufSize 25119 Bytes BINARY_OUTPUT_LEN 45176 Bytes

lz4 decompress 0/25119 Bytes 0.00%

lz4 decompress 4801/25119 Bytes 19.11%

lz4 decompress 11789/25119 Bytes 46.93%

lz4 decompress 15262/25119 Bytes 60.76%

lz4 decompress 18424/25119 Bytes 73.35%

lz4 decompress 21379/25119 Bytes 85.11%

lz4 decompress 24130/25119 Bytes 96.06%

[0;33m _ _ __ ____ __

[0m[0;33m | |_ _(_) ___ __\ \ / | \/ |

[0m[0;33m _ | | | | | |/ __/ _ \ \ / /| |\/| |

[0m[0;33m | |_| | |_| | | (_| __/\ V / | | | |

[0m[0;33m \___/ \__,_|_|\___\___| \_/ |_| |_|

[0m[0;33m email: juicemail@163.com

[0mversion: unknow

interrupt_vertor_register_mag_init

rv_csr_register_init

csr_addr_misa 0000000000000000

csr_addr_mvendorid 000000003ffca248

csr_addr_marchid 000000003ffca248

csr_addr_mimpid 000000003ffca248

csr_addr_mhartid 000000003ffca248

rv_peripheral_device_init

[rv64_sim][dev][mmu]/mnt/ssd_prj/risc-v_sim/sim/rv.c(6599):rv_peripheral_device_mmu_init,Sv39 mode support only

[rv64_sim][dev][mtime]/mnt/ssd_prj/risc-v_sim/sim/rv.c(6253):rv_peripheral_device_mtime_init

[rv64_sim][dev][mtime]/mnt/ssd_prj/risc-v_sim/sim/rv.c(6272):pdev_mtime_irq_info 0x3ffbb678 80800003 80800007

[rv64_sim][dev][mtime]/mnt/ssd_prj/risc-v_sim/sim/rv.c(6283):pdev_mtime_irq_info_on_umode 0x0 80800003 80800007

[rv64_sim][dev][uart0]/mnt/ssd_prj/risc-v_sim/sim/rv.c(6046):rv_peripheral_device_uart0_init

[rv64_sim][dev][uart0]/mnt/ssd_prj/risc-v_sim/sim/rv.c(6062):pdev_uart0_irq_info 0x3ffbb658

rv sim start...

loading...

RV_CPU_SIM_RAM_START_ADDR 0

rv_cpu.reg.pc 80000000

nstr 80000000 30305073

cpu run...

heap: [0x8000cba8 - 0x80800000]

\ | /

- RT - Thread Operating System

/ | \ 4.0.4 build Jul 12 2021

2006 - 2021 Copyright by rt-thread team

Hello RT-Thread!

Hello RT-Thread! test_i = 0

Hello RT-Thread! test_i = 1

Hello RT-Thread! test_i = 2

Hello RT-Thread! test_i = 3

Hello RT-Thread! test_i = 4

Hello RT-Thread! test_i = 5

Hello RT-Thread! test_i = 6

Hello RT-Thread! test_i = 7

Hello RT-Thread! test_i = 8

Hello RT-Thread! test_i = 9

Hello RT-Thread! test_i = 10

Hello RT-Thread! test_i = 11

Hello RT-Thread! test_i = 12

Hello RT-Thread! test_i = 13

Hello RT-Thread! test_i = 14

Hello RT-Thread! test_i = 15

Hello RT-Thread! test_i = 16

Hello RT-Thread! test_i = 17

Hello RT-Thread! test_i = 18

Hello RT-Thread! test_i = 19

Hello RT-Thread! test_i = 20

Hello RT-Thread! test_i = 21

Hello RT-Thread! test_i = 22

Hello RT-Thread! test_i = 23

Hello RT-Thread! test_i = 24

Hello RT-Thread! test_i = 25

Hello RT-Thread! test_i = 26

Hello RT-Thread! test_i = 27

Hello RT-Thr#37 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-07-26 12:17:10

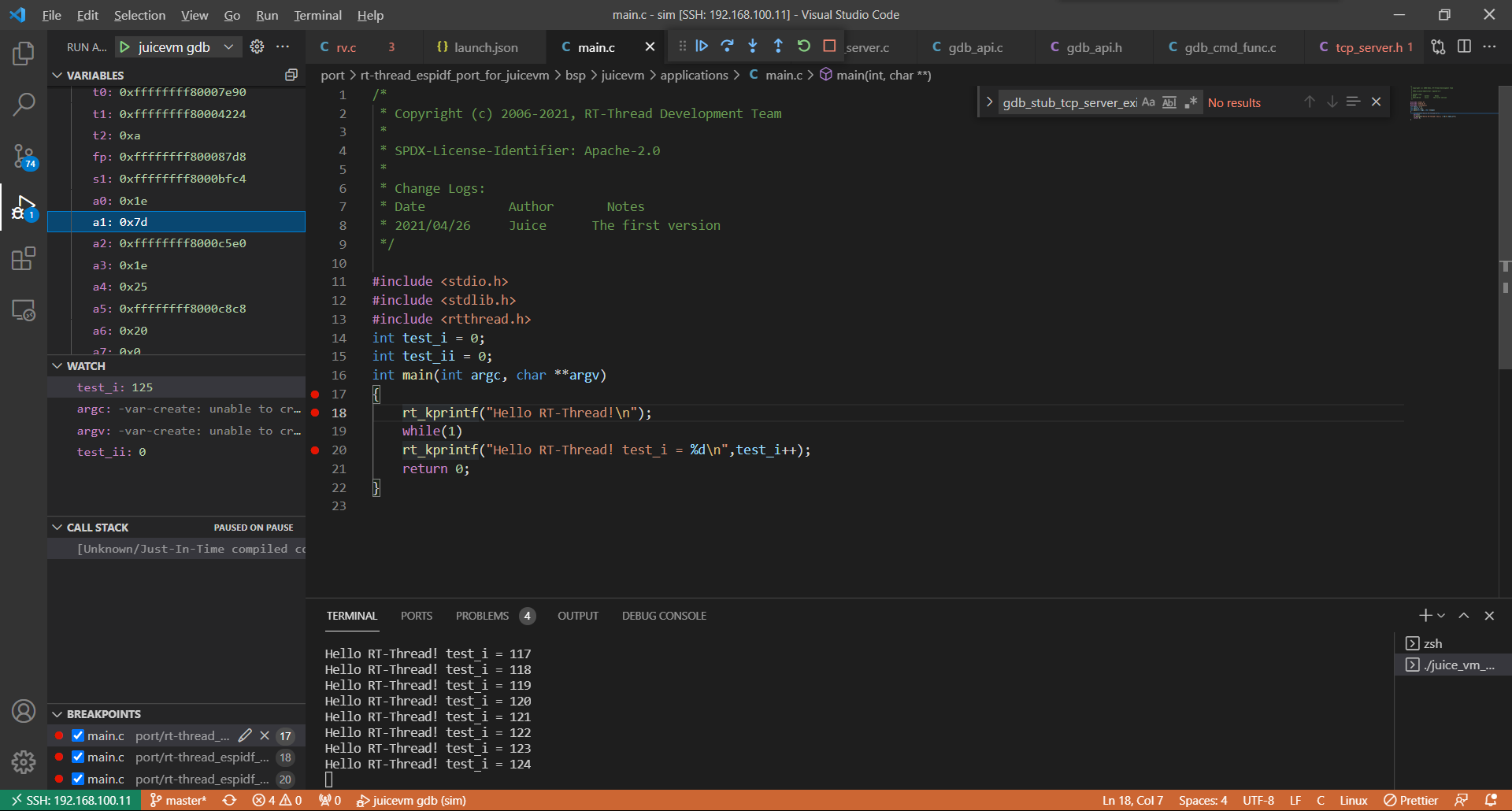

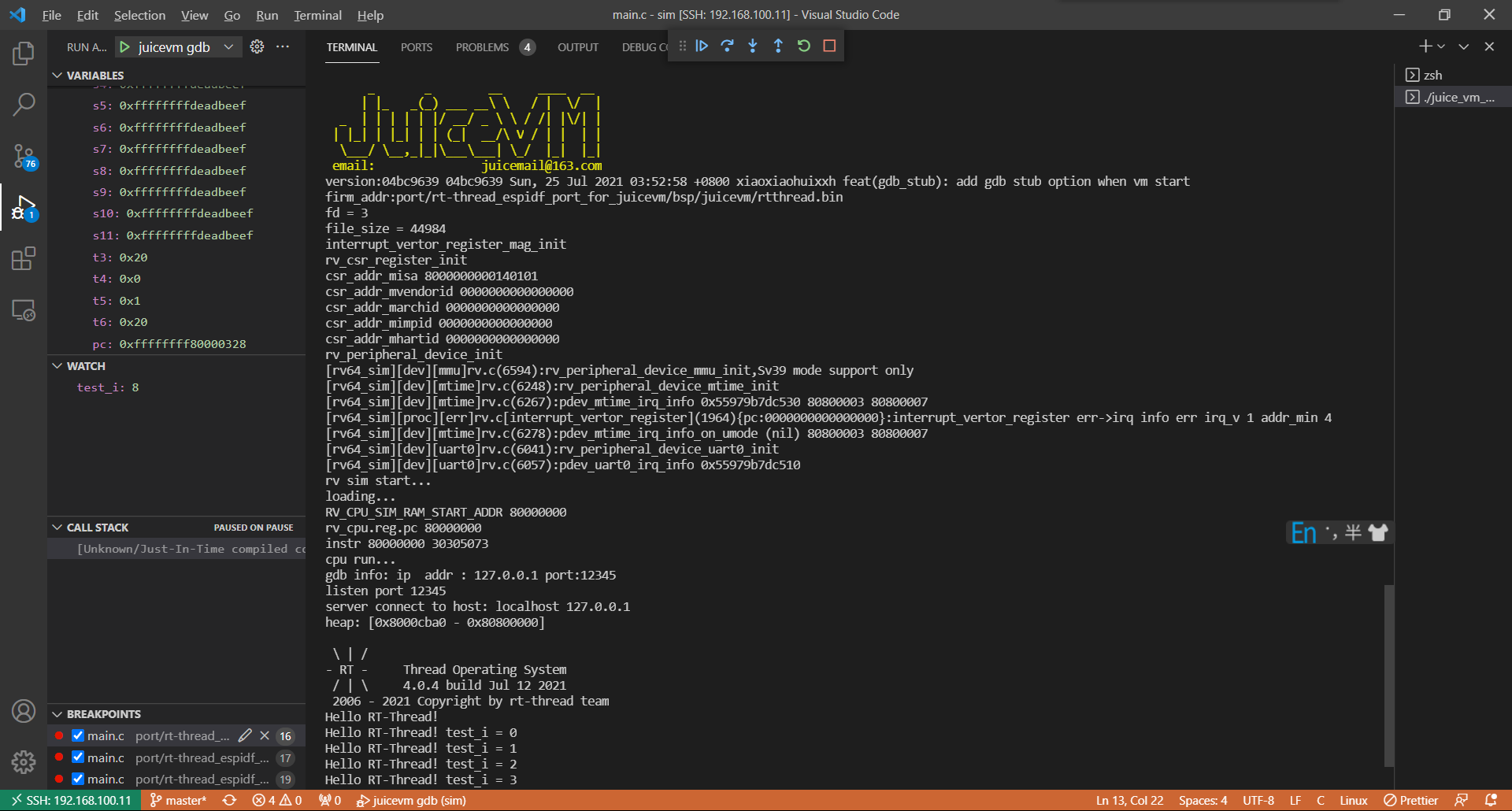

开源juicevm的gdb stub组件:https://github.com/juiceRv/gdb_stub_for_juicevm

#38 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-07-25 22:28:07

#40 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-07-19 19:28:58

#42 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-07-19 19:26:22

#45 Re: RISC-V » juiceVm risc-v虚拟机在esp32上运行linux kernel » 2021-07-17 15:55:58

#define JUICEVM_PSRAM_DMA_CHAN 2

#define JUICEVM_PSRAM_PIN_NUM_MISO 7

#define JUICEVM_PSRAM_PIN_NUM_MOSI 8

#define JUICEVM_PSRAM_PIN_NUM_CLK 17

#define JUICEVM_PSRAM_PIN_NUM_CS 16

#48 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-07-16 16:03:53

20210716更新:

esp32上运行juicevm。听说esp32和linux kernel更配哦

https://whycan.com/t_6899.html

#49 RISC-V » juiceVm risc-v虚拟机在esp32上运行linux kernel » 2021-07-16 16:02:45

- xiaohui

- 回复: 23

RT.

有图有真相,固件在文章末尾

运行环境:

esp32 devkit v1开发板:

外置 2MB flash.

外接 spi psram 8MB:

psram spi interface info:

CS:4,CLK:5,MOSI:18,MISO:19

固件下载信息:

Compressed 1583728 bytes to 1294532...

Wrote 1583728 bytes (1294532 compressed) at 0x00001000 in 33.1 seconds (effective 382.7 kbit/s)...

#50 Re: RISC-V » RISC-V代码密度相比Cortex-M差距明显 » 2021-07-16 15:38:27

#51 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-07-16 14:34:36

20210716更新:

请移步到https://whycan.com/t_6881.html

#52 Re: RISC-V » 用汇编学习risc-v指令集,并在线仿真,点亮led » 2021-07-16 14:32:36

#55 Re: RISC-V » esp32上运行juicevm psram可选 » 2021-07-14 18:16:02

#57 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-06-22 14:02:46

#58 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-06-10 16:08:36

#59 Re: 好钜润半导体(TIKY) » TKM32F499开坑 » 2021-05-31 14:48:07

#60 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-05-31 12:03:22

#61 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-05-27 02:22:14

更新私有软件源:

echo "deb http://xiaohui.mongoyun.com:3333/ trusty main" | sudo tee -a /etc/apt/sources.list

wget -O - http://xiaohui.mongoyun.com:3333/key/deb.gpg.key | sudo apt-key add -

sudo apt update

sudo apt install juicevm

#62 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-05-26 14:49:28

分享下软件的参数说明:

t: enable test mode

进入固件测试模式

当出现下面的状态会结束运行并且打印出通过还是失败的字样

x3_gp寄存器的值为1 和 x17_a7寄存器的值为93时,进入了ecall异常就会触发。x10_a0 寄存器的值为 0时打印pass字样,否则打印fail字样

-------------------------------------------------------------------------------

T: enable trap debug mode

使能异常调试模式,出现异常时会打印当前异常的调试信息

-------------------------------------------------------------------------------

d: enable debug mode

打开虚拟机内所有的调试选项,输出最详细的调试信息,包括指令译码,处理执行,当前寄存器列表,csr列表等

-------------------------------------------------------------------------------

c: print cst operation msg

打开虚拟机的csr寄存器读写调试信息。读写csr寄存器的时候都会打印对应的csr寄存器的值

-------------------------------------------------------------------------------

a: diable all debug msg

关闭所有调试选项,译码调试默认打开

-------------------------------------------------------------------------------

x: enable test mode for exception

打开异常测试模式,当出现异常时结束运行

-------------------------------------------------------------------------------

g: enable better readability printing

使用可读性更好的方式打印信息

-------------------------------------------------------------------------------

e: disable all error msg

关闭所有的错误信息打印

-------------------------------------------------------------------------------

i: enable all instr debug msg

打开所有指令调试信息打印

-------------------------------------------------------------------------------

m: enable mmu debug msg

打开mmu的遍历调试信息

-------------------------------------------------------------------------------

p: print mmu page 8 byte data

hexdump打印mmu页表里的8字节数据

-------------------------------------------------------------------------------

P: print mmu page 4K Byte data

hexdump打印mmu页表里的4K字节数据

-------------------------------------------------------------------------------

s: uart addr not use mmu translation

启用mmu翻译时,忽略uart的外设地址,在启用了mmu的时候也可以直接通过uart原始物理地址来操作uart外设

-------------------------------------------------------------------------------

S: switch mode debug info

打开切换mode时的调试信息,m-mode,s-mode和u-mode切换的时候都会打印调试信息

-------------------------------------------------------------------------------

M: disable mmu err msg

关闭mmu缺页异常,访问异常,加载异常的错误信息

-------------------------------------------------------------------------------

r: enable trap debug msg

打印更详细的进入中断的调试信息

-------------------------------------------------------------------------------

A: enable addr translation debug print

打印地址转换的调试打印

-------------------------------------------------------------------------------

L(n): output_mode_sel n = 0 -> stdout

1 -> log_buf UNIX SYS ONLY(buf_size:(2900))

2 -> none

选择虚拟机输出的方式,1,直接标准输出。2,使用一个buf先缓存,退出的时候再输出bug大小2900Byte。3,不输出。

-------------------------------------------------------------------------------

l: enable endless loop check (RV_ENDLESS_LOOP_CHECK_EXIT_CNT:(3))

启用死循环监测机制,当有连续3次出现同样的指令执行流程(包括寄存器和csr寄存器的值都没有改变),结束虚拟机的运行。可以搭配-L参数使用,方便调试固件。一般assert都是直接死循环。

-------------------------------------------------------------------------------

#64 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-05-25 13:39:45

opensbi和kernel的代码已发布到github!!!

https://github.com/juiceRv/kernel_juicevm_port

kernel的配置文件在arch/riscv/configs/juicevm_defconfig,make ARCH=riscv juicevm_defconfig

需要修改下arch/riscv/configs/juicevm_defconfig里的CONFIG_INITRAMFS_SOURCE="/mnt/ssd_prj/risc-v_sim/sim/test/opensbi/opensbi-master/rootfs"

修改为opensbi里的路径

opensbi仓库

https://github.com/juiceRv/opensbi_juicevm_port

toolchains

https://github.com/juiceRv/gcc-gnu-toolchains-for-juicevm

#65 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-05-25 00:42:04

20210524进展公布,发布包发布juice_vm_release_for_Linux_c21682d3.zip:

1,修复了mtime在m-mode,s-mode和u-mode下的中断处理漏洞。

2,修复了ecall在s-mode下的漏洞。

3,修复了在s-mode和u-mode下进入异常模式,更新csr寄存器的漏洞。

4,移植了linux。

juice_vm成功运行kernel主线5.0.0。

juice_vm成功运行kernel主线5.0.0。

juice_vm成功运行kernel主线5.0.0。

#66 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-05-24 18:43:18

#67 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-05-08 15:59:40

20210508更新:

1,上传一个ubuntu20.04上可以正常运行的发布包,感谢@XBOOT大佬的反馈。

2,添加了div指令支持。

3,修复了divuw,divw,remu,remw,amomin.w,amoswap.w的指令错误。

juice_vm_for_Linux_b58244f3.zip

#68 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-05-08 10:55:19

bellard的riscv&x86模拟器

https://bellard.org/tinyemu/

谢谢大佬分享,一直也有关注这个天才大佬的项目。

#69 Re: RISC-V » [juicevm] 只需要不到5000行代码实现一个risc-v虚拟机,纯c语言实现,无第三方库,支持ESP32 & GDB » 2021-05-07 18:44:21

global_vm_log_init output_mode_sel: 0 JUICE_VM_LOG_MAX_NUM:2900

gg ,ggg, gg ,a8a, ,gggg, ,ggggggg, ,ggg, ,g,ggg, ,ggg,_,ggg,

dP8dP Y8a 88 ,8 8, ,88 Y8b,dP Y8dP Y8a ,8dP Y8dP Y88P Y8b

dP YYb, `88 88 d8 8b d8 `Yd8' a YYb, `88 d8Yb, `88' `88' `88

,8 `8` 88 88 88 88d8' 8b d88 Y8P'` 88 88 ` 88 88 88

I8 Yb 88 88 88 8,8I Y88P`8baaaa 88 88 88 88 88

`8b, `8, 88 88 Y8 8I8' ,d8P I8 8I 88 88 88

` Y88888 88 88 `8, ,8d8 d8 `8, ,8' 88 88 88

Y8 88 888888 8,8 Y8, Y8, Y8, ,8P 88 88 88

,88,Y8b,____,d88`8b, ,d8b,`Yba,,_____`Yba,,_____, Yb,_,dP 88 88 Y8,

,ad88888 Y888888P Y8 Y88P Y8 ` Y8888888 ` Y8888888 Y8P 88 88 `Y8

,dP ' Yb

,8' I8

,8' I8

I8, ,8'

`Y8,___,d8'

Y888P

email: juicemail@163.com

version:f259ffe5 f259ffe5 Fri, 7 May 2021 16:31:18 +0800 xiaoxiaohuixxh feat(vm): pass ui ua si test but lrsc and scr test

firm_addr:build/platform/juice/juiceRv/firmware/fw_payload.bin

fd = 3

file_size = 6169144

interrupt_vertor_register_mag_init

rv_csr_register_init

csr_addr_misa 8000000000040101

csr_addr_mvendorid 0000000000000000

csr_addr_marchid 0000000000000000

csr_addr_mimpid 0000000000000000

csr_addr_mhartid 0000000000000000

rv_peripheral_device_init

[rv64_sim][dev][mmu]rv.c(6114):rv_peripheral_device_mmu_init,Sv39 mode support only

[rv64_sim][dev][mtime]rv.c(5773):rv_peripheral_device_mtime_init

[rv64_sim][dev][mtime]rv.c(5792):pdev_mtime_irq_info 0x55f859de9110 92c00003 92c00007

[rv64_sim][proc][err]rv.c[interrupt_vertor_register](1910){pc:0000000000000000}:interrupt_vertor_register err->irq info err irq_v 1 addr_min 4

[rv64_sim][dev][mtime]rv.c(5803):pdev_mtime_irq_info_on_umode (nil) 92c00003 92c00007

[rv64_sim][dev][uart0]rv.c(5580):rv_peripheral_device_uart0_init

[rv64_sim][dev][uart0]rv.c(5596):pdev_uart0_irq_info 0x55f859de90f0

rv sim start...loading

cpu run...

[juiceRv]set_rv_scr csr_addr 0000000000000180(csr_addr_satp) new_v 0000000000000000

get_MODE_xsatp(get_rv_csr(csr_addr_satp)) 0

OpenSBI v0.9

____ _____ ____ _____

/ __ \ / ____| _ \_ _|

| | | |_ __ ___ _ __ | (___ | |_) || |

| | | | '_ \ / _ \ '_ \ \___ \| _ < | |

| |__| | |_) | __/ | | |____) | |_) || |_

\____/| .__/ \___|_| |_|_____/|____/_____|

| |

|_|

Platform Name : juice-JuiceRv

Platform Features : timer,mfdeleg

Platform HART Count : 1

Firmware Base : 0x80000000

Firmware Size : 80 KB

Runtime SBI Version : 0.3

Domain0 Name : root

Domain0 Boot HART : 0

Domain0 HARTs : 0*

Domain0 Region00 : 0x0000000080000000-0x000000008001ffff ()

Domain0 Region01 : 0x0000000000000000-0xffffffffffffffff (R,W,X)

Domain0 Next Address : 0x0000000080200000

Domain0 Next Arg1 : 0x0000000082200000

Domain0 Next Mode : S-mode

Domain0 SysReset : yes

Boot HART ID : 0

Boot HART Domain : root

Boot HART ISA : rv64ias

Boot HART Features : scounteren,mcounteren,time

Boot HART PMP Count : 64

Boot HART PMP Granularity : 4

Boot HART PMP Address Bits: 54

Boot HART MHPM Count : 29

Boot HART MHPM Count : 29

Boot HART MIDELEG : 0x0000000000000222

Boot HART MEDELEG : 0x000000000000b109

[juiceRv]set_rv_scr csr_addr 0000000000000105(csr_addr_stvec) new_v 0000000080200000

[juiceRv]set_rv_scr csr_addr 0000000000000180(csr_addr_satp) new_v 0000000000000000

get_MODE_xsatp(get_rv_csr(csr_addr_satp)) 0

H

D

C

B

M

S

R

R1[juiceRv]set_rv_scr csr_addr 0000000000000105(csr_addr_stvec) new_v ffffffff800003a4

23[juiceRv]set_rv_scr csr_addr 0000000000000180(csr_addr_satp) new_v 800000000008021c

get_MODE_xsatp(get_rv_csr(csr_addr_satp)) 8

[rv64_sim][dev][mmu][err]rv.c(6220):V:0 R:0 W:0

[rv64_sim][dev][mmu][err]rv.c(6221):如果pte.v = 0,或者pte.r = 0且pte.w = 1,则停止并引发与原始访问类型相对应的页面错误异常。

[rv64_sim][dev][mmu][err]rv.c(6305):rv_peripheral_device_mmu_translation pc:0000000080200394 va 0000000080200394 pa 0000000000000000

[rv64_sim][proc][err]rv.c[RISCVTrap](1404){pc:0000000080200394}:RV_exception_Instruction_page_fault va 0000000080200394

[rv64_sim][dev][mmu][err]rv.c(6317):this addr not found

5

[juiceRv]set_rv_scr csr_addr 0000000000000105(csr_addr_stvec) new_v ffffffff800003f0

6[juiceRv]set_rv_scr csr_addr 0000000000000180(csr_addr_satp) new_v 80000000000805a7

get_MODE_xsatp(get_rv_csr(csr_addr_satp)) 8

I

Parse_dtb

start_kernel

[ 0.000000] OF: fdt: Ignoring memory range 0x80000000 - 0x80200000

[ 0.000000] memblock_add enter

[ 0.000000] No DTB passed to the kernel

[ 0.000000] func start_kernel ( 647 )

[ 0.000000] func start_kernel ( 651 )

[ 0.000000] func start_kernel ( 653 )

[ 0.000000] func start_kernel ( 656 )

[ 0.000000] func start_kernel ( 659 )