#1 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-21 14:50:58

jlau wrote:

XSTAR会开源吗

XSTAR还在开发中,后面会开源,先用来做做产品,顺便检验下,看是否能达到产品级。

#3 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-20 15:32:57

关于CRC初始化向量搞定了,借助AI的力量,找到了异或关键值0x35769521,原来APP通过0x18指令发出来的的key只需要跟0x35769521就可以得到初始化向量,验证了IOS以及ANDROID版本的APP,都是可以校验通过的,至此,通信协议的密钥坑已经填上。

uint32_t key = 0x35769521;

uint32_t raw;

//ios

raw = 0x4271a5b7;

printf("0x%08x -> 0x%08x\r\n", raw, raw^key);

raw = 0x3cc0d90a;

printf("0x%08x -> 0x%08x\r\n", raw, raw^key);

raw = 0xb87e98d4;

printf("0x%08x -> 0x%08x\r\n", raw, raw^key);

raw = 0x8dcb302e;

printf("0x%08x -> 0x%08x\r\n", raw, raw^key);

//android

raw = 0x35769521;

printf("0x%08x -> 0x%08x\r\n", raw, raw^key);0x4271a5b7 -> 0x77073096

0x3cc0d90a -> 0x09b64c2b

0xb87e98d4 -> 0x8d080df5

0x8dcb302e -> 0xb8bda50f

0x35769521 -> 0x00000000只剩唯一的一个问题,IOS平台连接蓝牙的问题,这个问题,要么是COD问题,要么是MFI问题。这个具体是哪方面的问题,现在手上没条件验证,就暂时告一段落了。

#4 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-20 14:03:28

海石生风 wrote:

加热时长为2mm即500Hz,那么如果用25kHz的PWM信号来控制加热的话,PWM的占空比就代表打印的灰度,这样的效果应该能做得更好。

有道理,核心是控制总加热功率,这里的非线性情况还是比较复杂,如果要做到极致,得需要通过精确的实验测定出加热时间与灰度的对应关系,当然灰度不仅仅跟加热时间有关,要考虑热扩散效因,甚至需要考虑下加热时的电源压降。

还有一个细节,要效果好的话,还必须做点抖动算法,当然这里的抖动,就不是二值化抖动了,而是256灰抖成16灰或者4灰,如果打印灰度能完美呈现,那么效果应该是可以接收的,类似与7色的那种电子纸,需要将RGB抖成7色后再去渲染。

#6 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-20 11:39:14

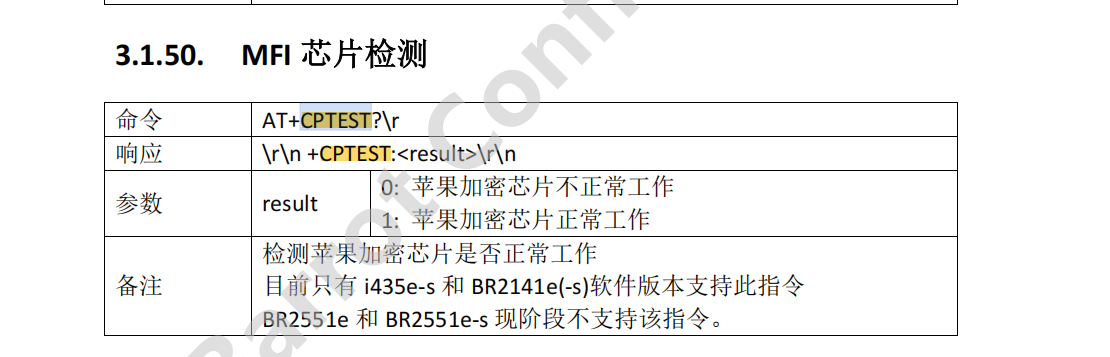

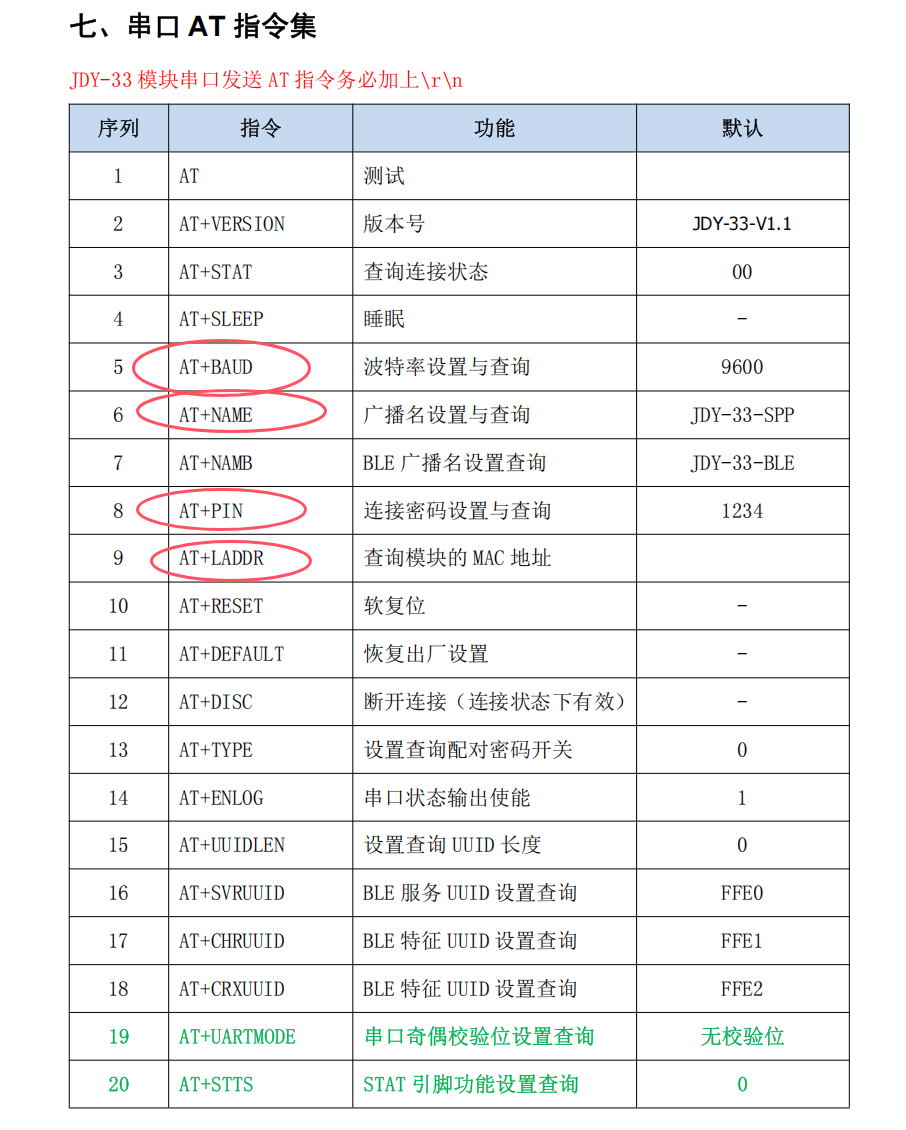

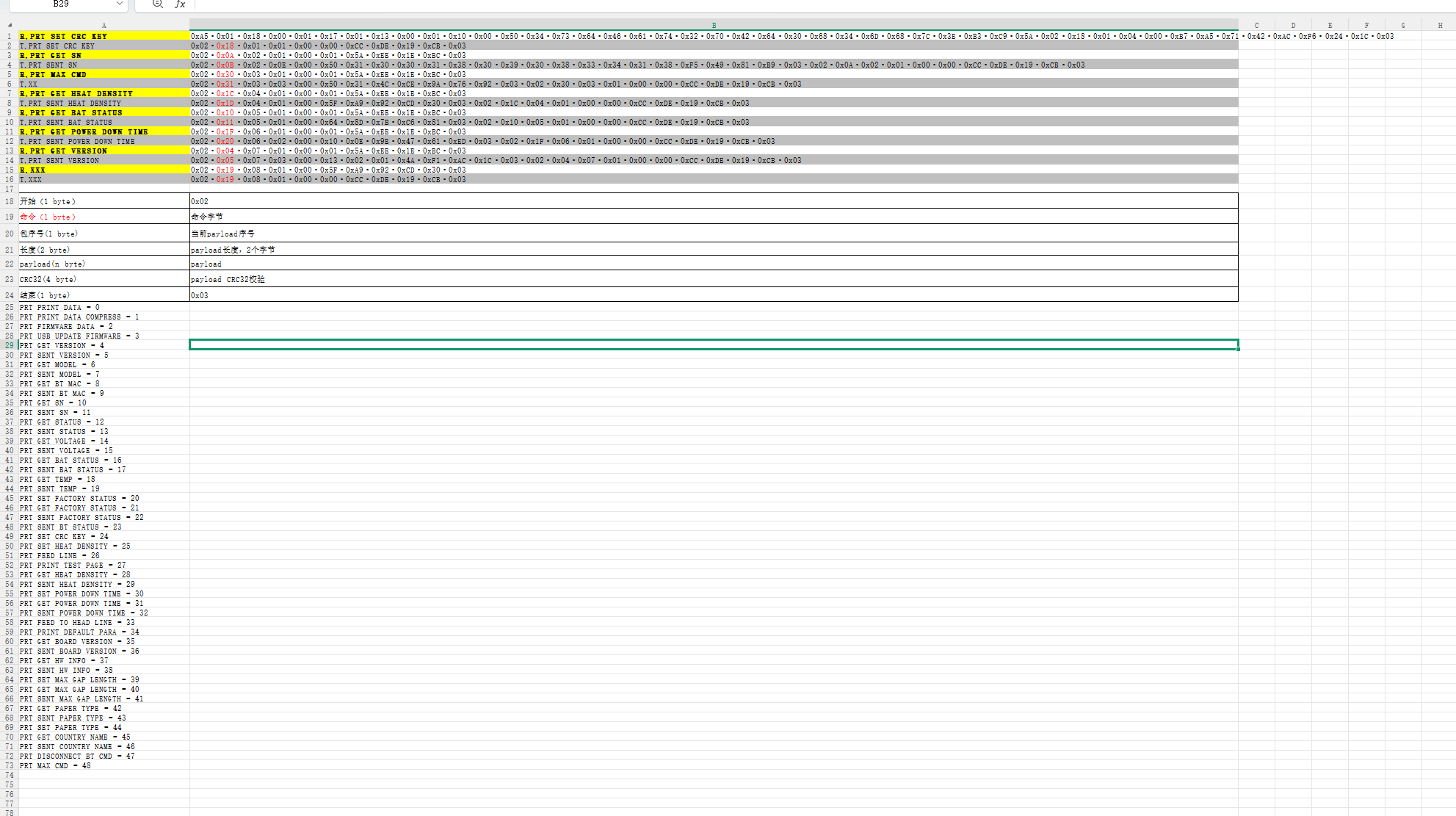

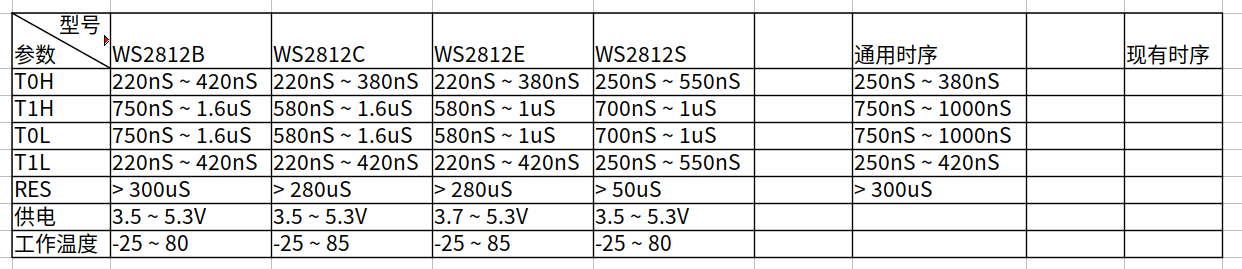

百瑞互联AI指令相关资料

BARROT_IoT双模模组_AT指令集_V2.8.pdf

#8 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-20 10:51:48

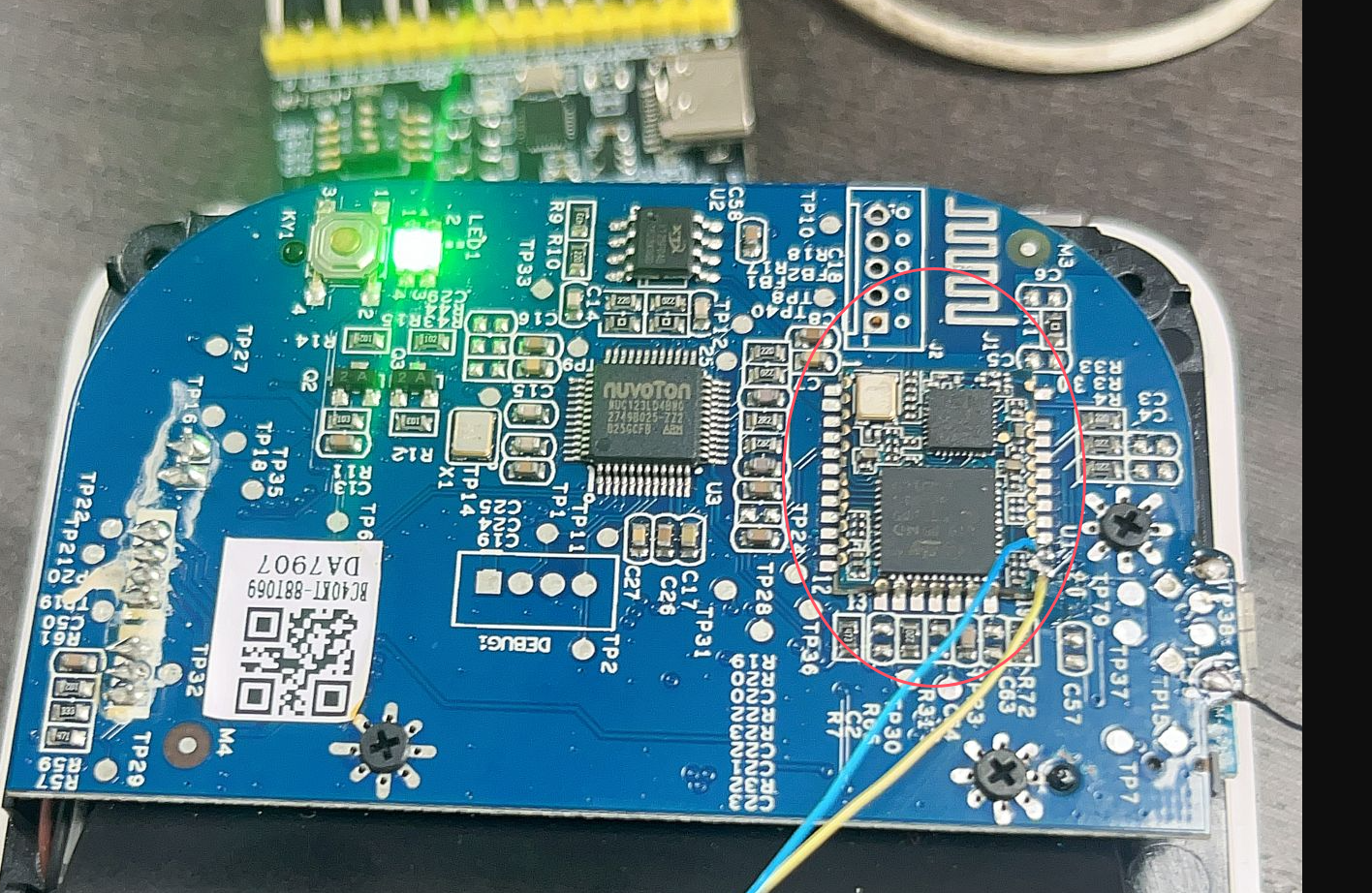

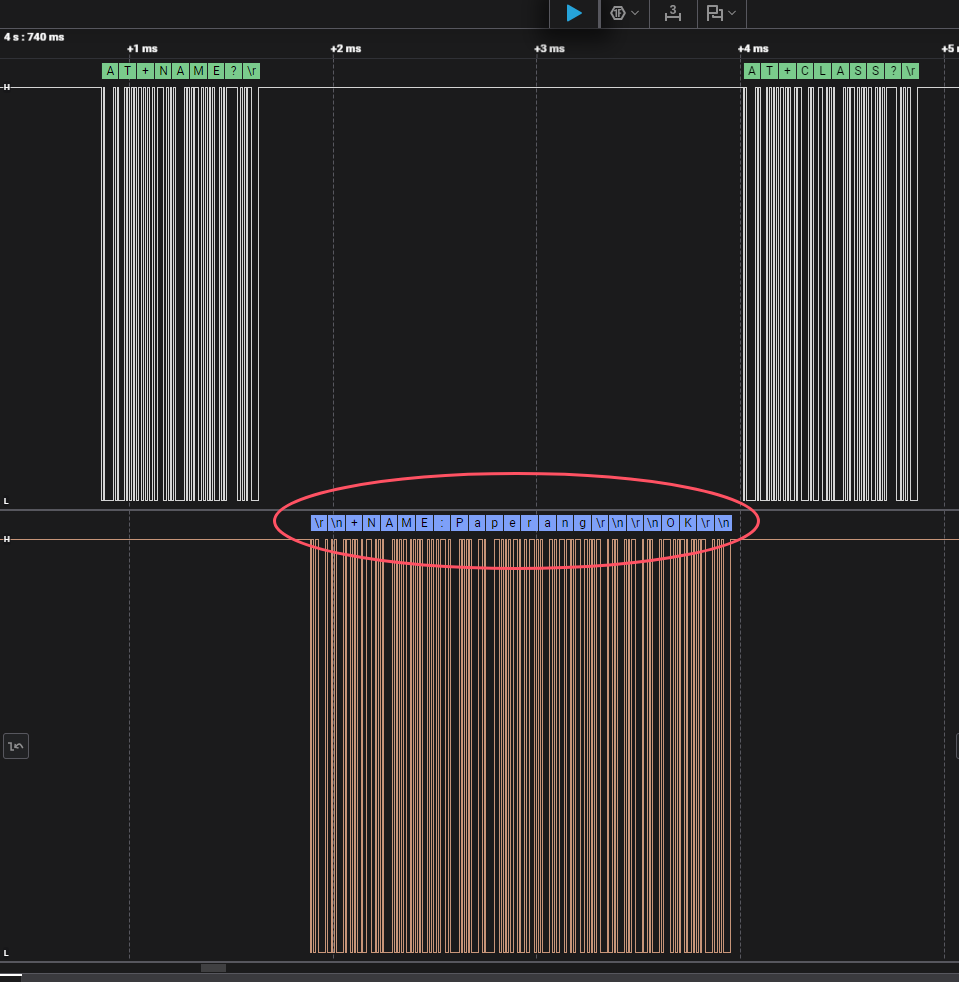

顺便再抓取了下,新塘MCU初始化蓝牙模块的过程。

AT+GVER?\r

\r\nIVT_IoT_i435e-sp_KT_20180424_r1492\r\n\r\nOK\r\n

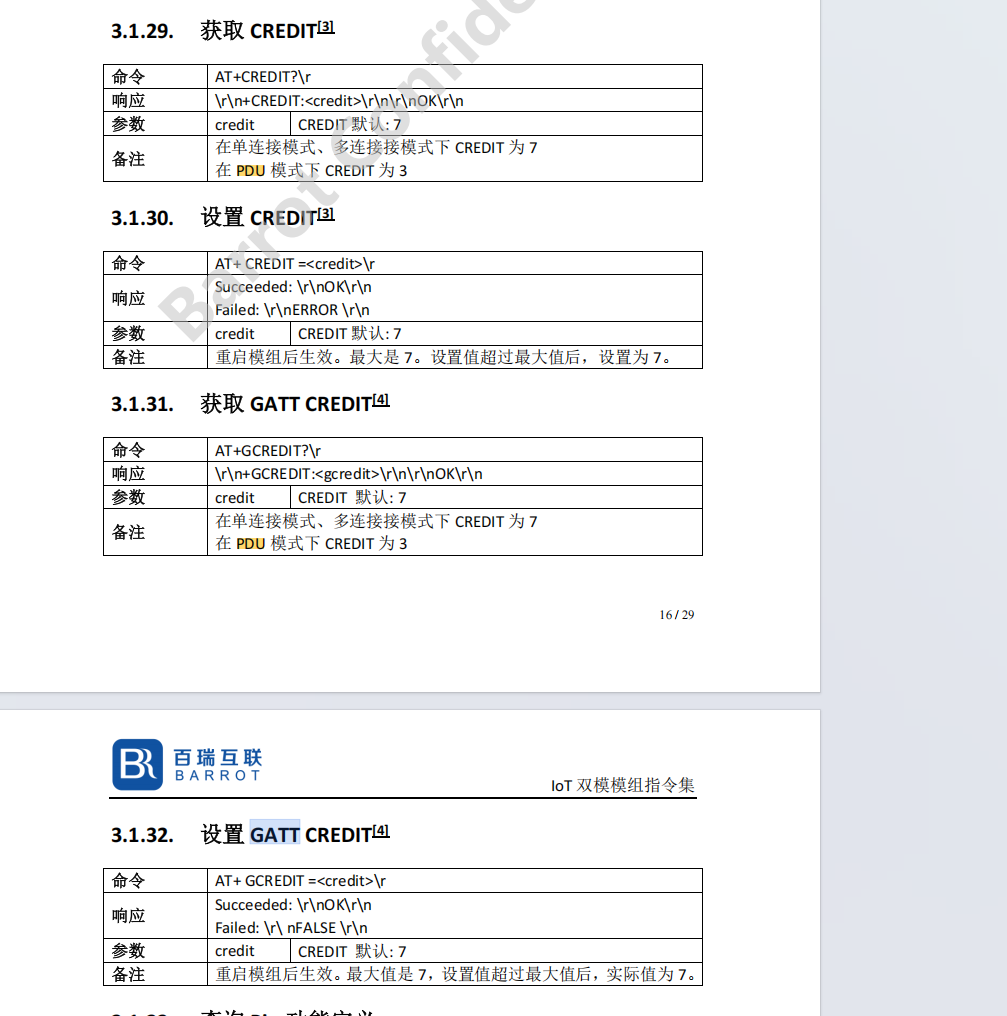

AT+CREDIT?\r

\r\n+CREDIT:1\r\n\r\nOK\r\n

AT+NAME?\r

\r\n+NAME:Paperang\r\n\r\nOK\r\n

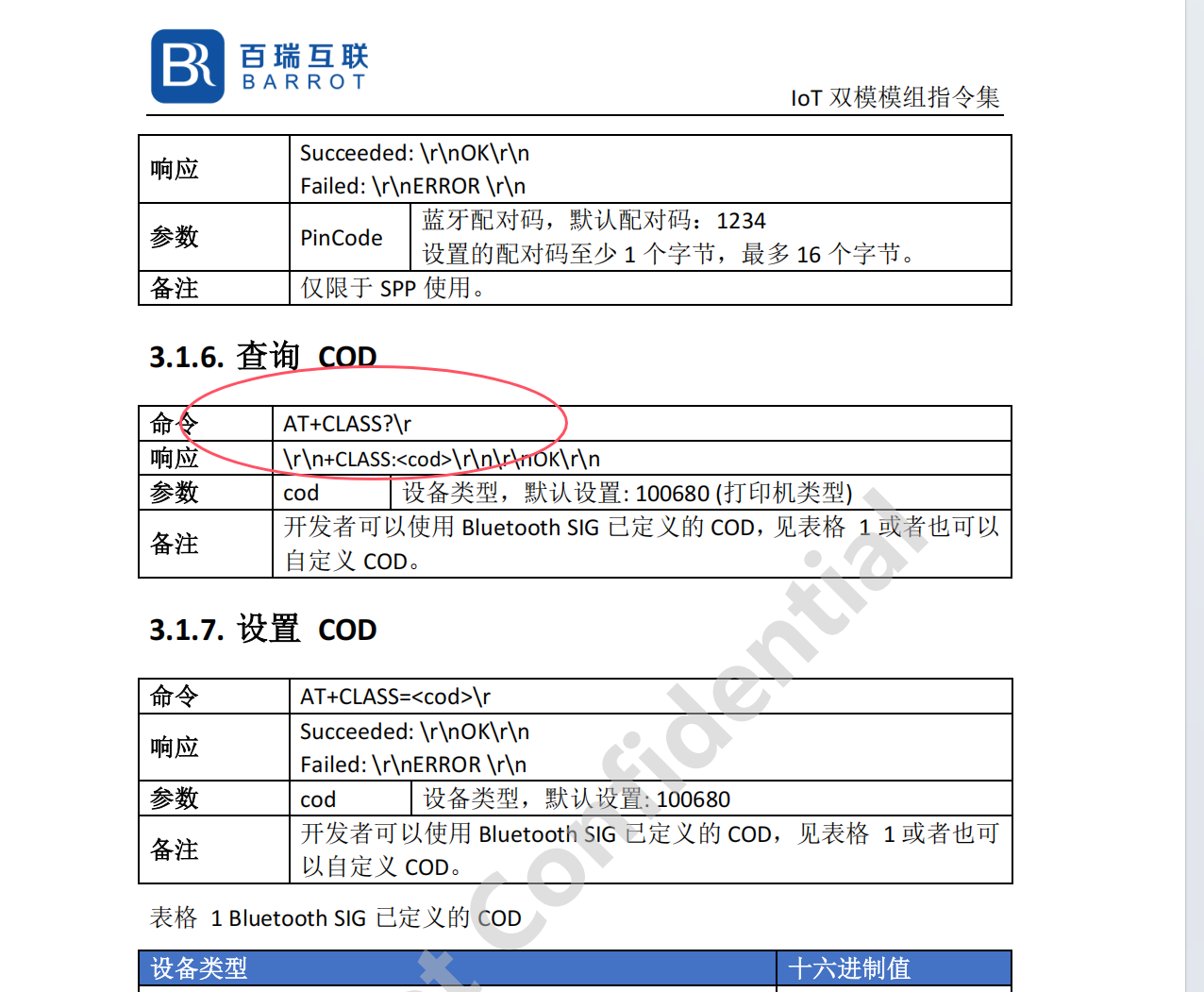

AT+CLASS?\r

\r\n+CLASS:000600\r\n\r\nOK\r\n

AT+LBDADDR?\r

\r\n+LBDADDR:001583DA7907\r\n\r\nOK\r\n

AT+SSP?\r

\r\n+SSP:1\r\n\r\nOK\r\n

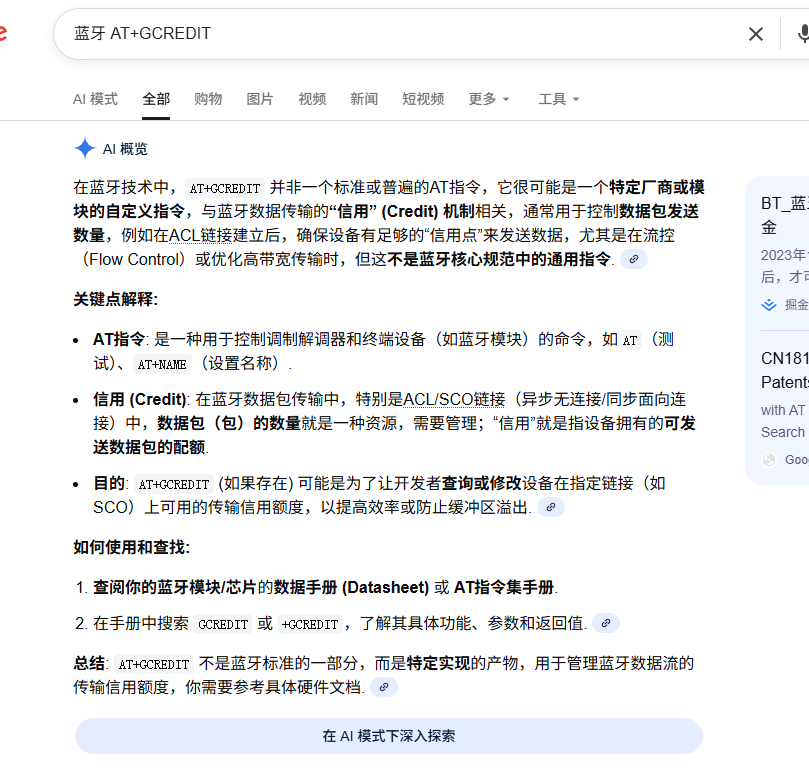

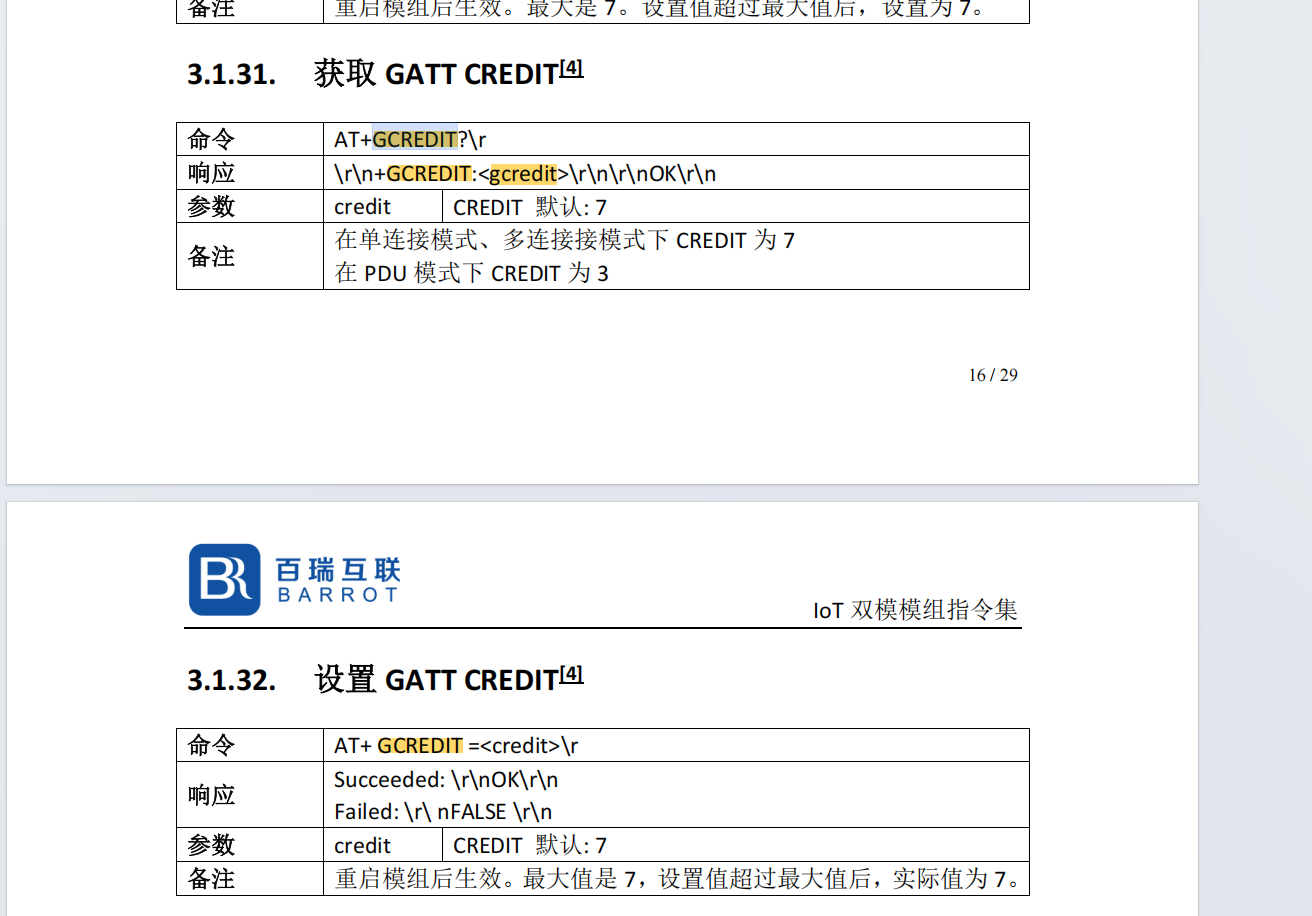

AT+GCREDIT?\r

\r\n+GCREDIT:3\r\n\r\nOK\r\n

AT+GCREDIT=3\r

\r\nOK\r\n我之前认为的IOS模式下走的是BLE,看来是错误,还是走的SSP模式,那问题来了,苹果可以支持SSP么,我现在的模块,在IOS版的作业帮是发现不了了。

这里有两条设定我认为比较关键一个是AT+CLASS,应该就是蓝牙的COD设定,我现在的模块不支持调整,没法试验,还有一个是AT+GCREDIT,这个就不知道是啥指令了

#9 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-20 10:36:07

通过作业帮的IOS版APP,又重新抓了下CRC初始化向量问题,发现这个向量在APP版本确定时是会变化的,经试验,只要作业帮APP杀掉再启动,CRC初始化向量就会变化一次,所以这个初始化向量应该是随机生成的,如何解密出初始化向量,这个就留给有心人了,我这里做个记录,抓取了4条初始化向量的通信过程,并暴力计算出真实的CRCIV,看有谁能找出计算规律。

0xA5·0x01·0x18·0x00·0x01·0x17·0x01·0x13·0x00·0x01·0x10·0x00·0x50·0x34·0x73·0x64·0x46·0x61·0x74·0x32·0x70·0x42·0x64·0x30·0x68·0x34·0x6D·0x68·0x7C·0x3E·0xB3·0xC9·0x5A·

0x02·0x18·0x01·0x04·0x00·0xB7·0xA5·0x71·0x42·0xAC·0xF6·0x24·0x1C·0x03

crciv = 0x77073096

爆破样本0x02·0x18·0x01·0x01·0x00·0x00·0xCC·0xDE·0x19·0xCB·0x03

========================================================================

0xA5·0x01·0x18·0x00·0x01·0x17·0x01·0x13·0x00·0x01·0x10·0x00·0x57·0x4B·0x50·0x4A·0x62·0x52·0x4D·0x57·0x42·0x69·0x44·0x38·0x46·0x58·0x6A·0x6B·0x58·0x3F·0x48·0x5C·0x5A·

0x02·0x18·0x01·0x04·0x00·0x0A·0xD9·0xC0·0x3C·0x1D·0x32·0xB4·0xE4·0x03

crciv = 0x09b64c2b

爆破样本0x02·0x18·0x01·0x01·0x00·0x00·0x81·0xA0·0xB7·0x7E·0x03

========================================================================

0xA5·0x01·0x18·0x00·0x01·0x17·0x01·0x13·0x00·0x01·0x10·0x00·0x73·0x78·0x49·0x37·0x31·0x6C·0x76·0x54·0x67·0x79·0x4A·0x52·0x76·0x51·0x45·0x6F·0x0A·0x70·0x8C·0x3A·0x5A·

0x02·0x18·0x01·0x04·0x00·0xD4·0x98·0x7E·0xB8·0x4F·0xDF·0xF4·0xC3·0x03

crciv = 0x8d080df5

爆破样本0x02·0x18·0x01·0x01·0x00·0x00·0x13·0xE1·0x58·0x1F·0x03

========================================================================

0xA5·0x01·0x18·0x00·0x01·0x17·0x01·0x13·0x00·0x01·0x10·0x00·0x63·0x74·0x36·0x36·0x44·0x41·0x4D·0x73·0x42·0x54·0x36·0x77·0x30·0x43·0x57·0x47·0xA1·0x6A·0xF0·0xF9·0x5A·

0x02·0x18·0x01·0x04·0x00·0x2E·0x30·0xCB·0x8D·0x8A·0xBB·0x45·0x32·0x03

crciv = 0xb8bda50f

爆破样本0x02·0x18·0x01·0x01·0x00·0x00·0xB9·0x4F·0x05·0x42·0x03

========================================================================这里补充说明下,0x18命令代码设置CRC初始化向量,正常帧都是0x02打头,0x03结尾,刚开始时的0xA5,结束时的0x5A很惹眼,要么就是烟雾弹,要么里面还有关键解密信息。

以第一条记录为例,如果是明文的话,CRCIV就是0xB7·0xA5·0x71·0x42,但实际是0x77073096,之间怎么运算的,就不得而知了,除非去逆向下新塘的那个MCU固件。

#10 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-19 18:56:50

#11 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-19 18:52:05

#12 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-19 18:37:35

有了数据,结合前人研究的协议,我这里分析到问题点了,最新的app不支持,就是因为CRC32的初始化向量变化了,作业帮APP的CRC32初始化向量是随APP走的,理论上要通信成功,需要作业帮APP先发送初始化向量,然后机器接收到后,后面都按此向量来校验以及生成相关数据帧,如果向量不正确,那么你肯定无法生成有效信息,所以APP也不认了。

那APP是如何发送初始化向量的呢,明文吗?这个大概率不是的,那如何解密出初始化向量呢,这个说实话,是有点困难的,特别是在特征信息很少时,根本无法正向解密出来,尽然来不了正向,那就来暴力,CRC32我从0x00000000试验到0xffffffff,只需要几秒钟,暴力代码如下,基于ios数据编写的,仅供参考。

/*

* start = 0x88f8cf69, crc= 0xbc1eee5a

*/

static int do_test(int argc, char ** argv)

{

uint8_t buf = 0x01;

for(uint32_t start = 0; start < 0xffffffff; start++)

{

uint32_t crc = xcrc32_sum(start, &buf, 1);

if((crc == 0xbc1eee5a)/* || (crc == 0x5aee1ebc)*/)

{

shell_printf("start = 0x%08x, crc= 0x%08x\r\n", start, crc);

}

else

{

if((start & 0xffff) == 0xffff)

{

//shell_printf("not found start = 0x%08x\r\n", start);

}

}

}

return 0;

}可以顺利输出当前CRC初始化向量,而且这个向量是不变化的,是固化在APP里。后面重点在攻克Android系统的APP,暴力出来后,CRC初始化向量是0,不知道是不是因为我的机器是P1,最老款的,进行特殊对待了,不管怎么样,我就模拟P1,当最老款的,也不是未尝不可。

好了,基础工作研究到位了,下面就开始编码验证,App绑定验证了。

需要先购买一个蓝牙透传模拟,支持SPP以及BLE的,然后做一些设定,稍后补充,下面是具体的APP绑定过程。

#13 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-19 18:21:41

#14 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-19 18:10:50

#15 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-19 18:03:55

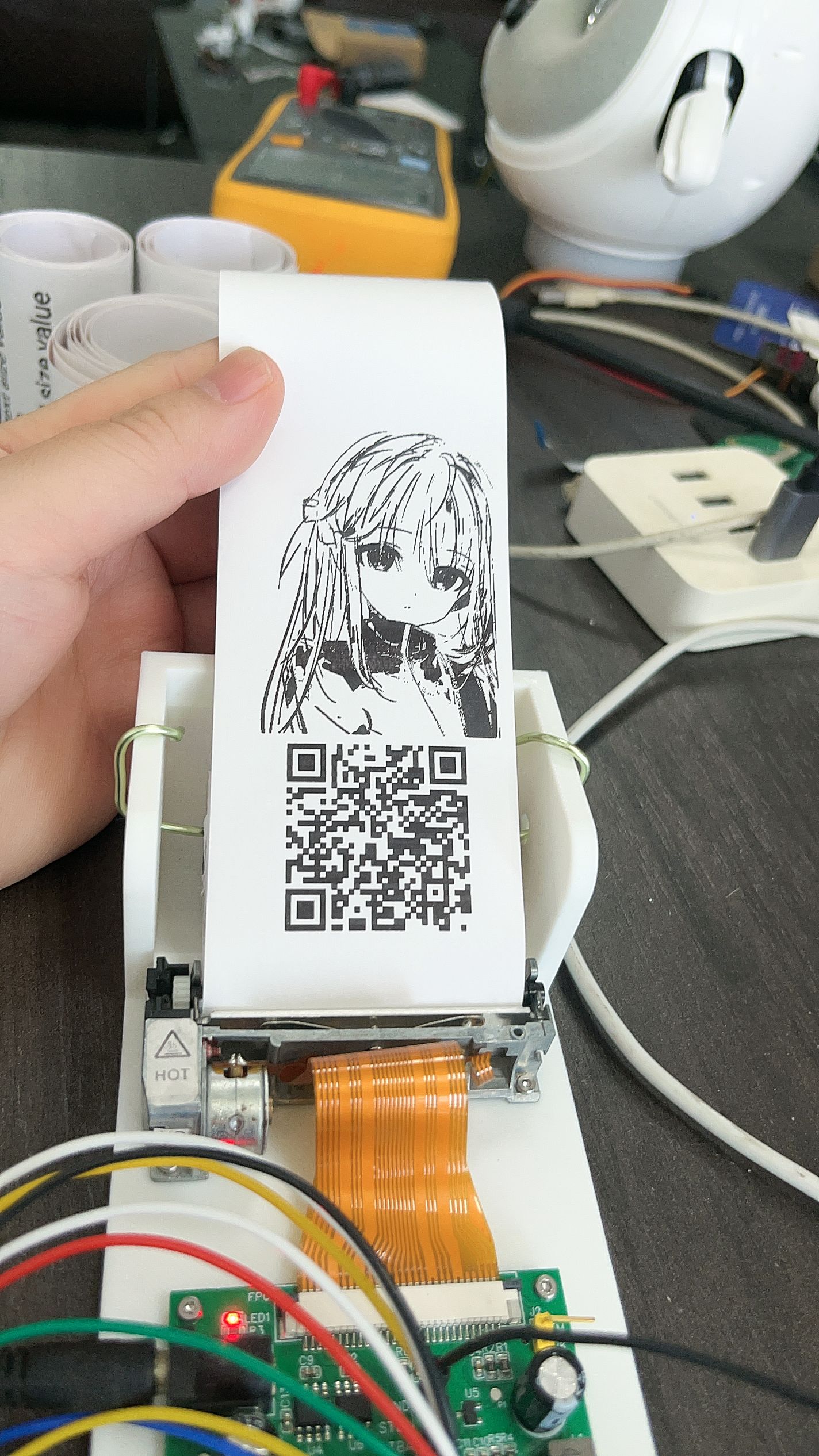

关于抖动算法,常用的有floyd-steinberg,jarvis-judice-ninke,stucki,atkinson,这里采用atkinson,这个算法会大面积留白,有点艺术性,适合打印场景。

对于这种普通的热敏打印机是否能灰度化打印,理论上是可行,原理也不复杂,就是将加热时间进行分片,比如需要实现16灰度打印,原始图像数据位8bit灰度图,只需将总时间除以16用于基本加热时间片,然后加加热一次,对应的灰度值减去16,直到减至0,就不再加热。这里假设了打印灰度跟加热时间是线性关系。

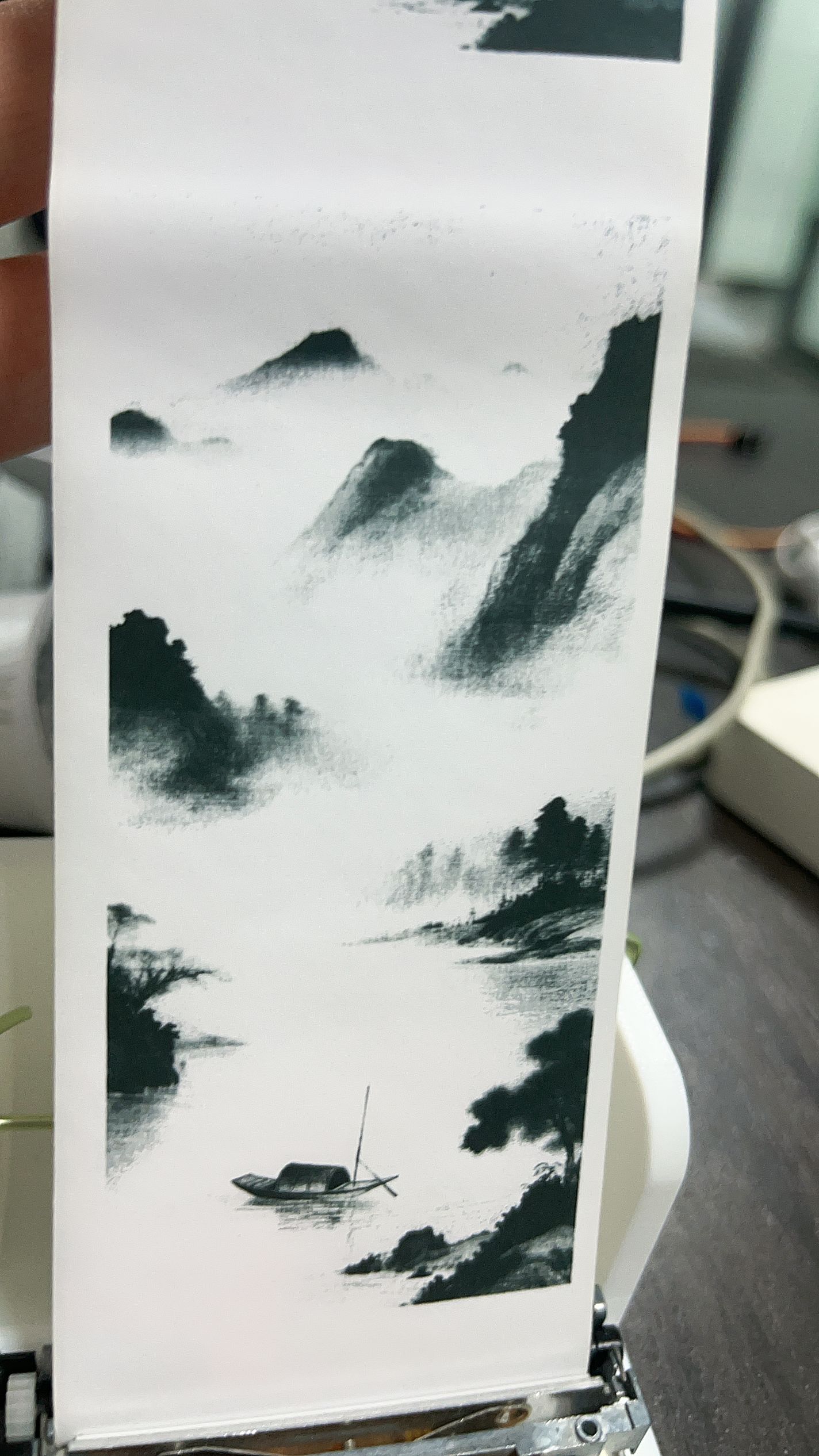

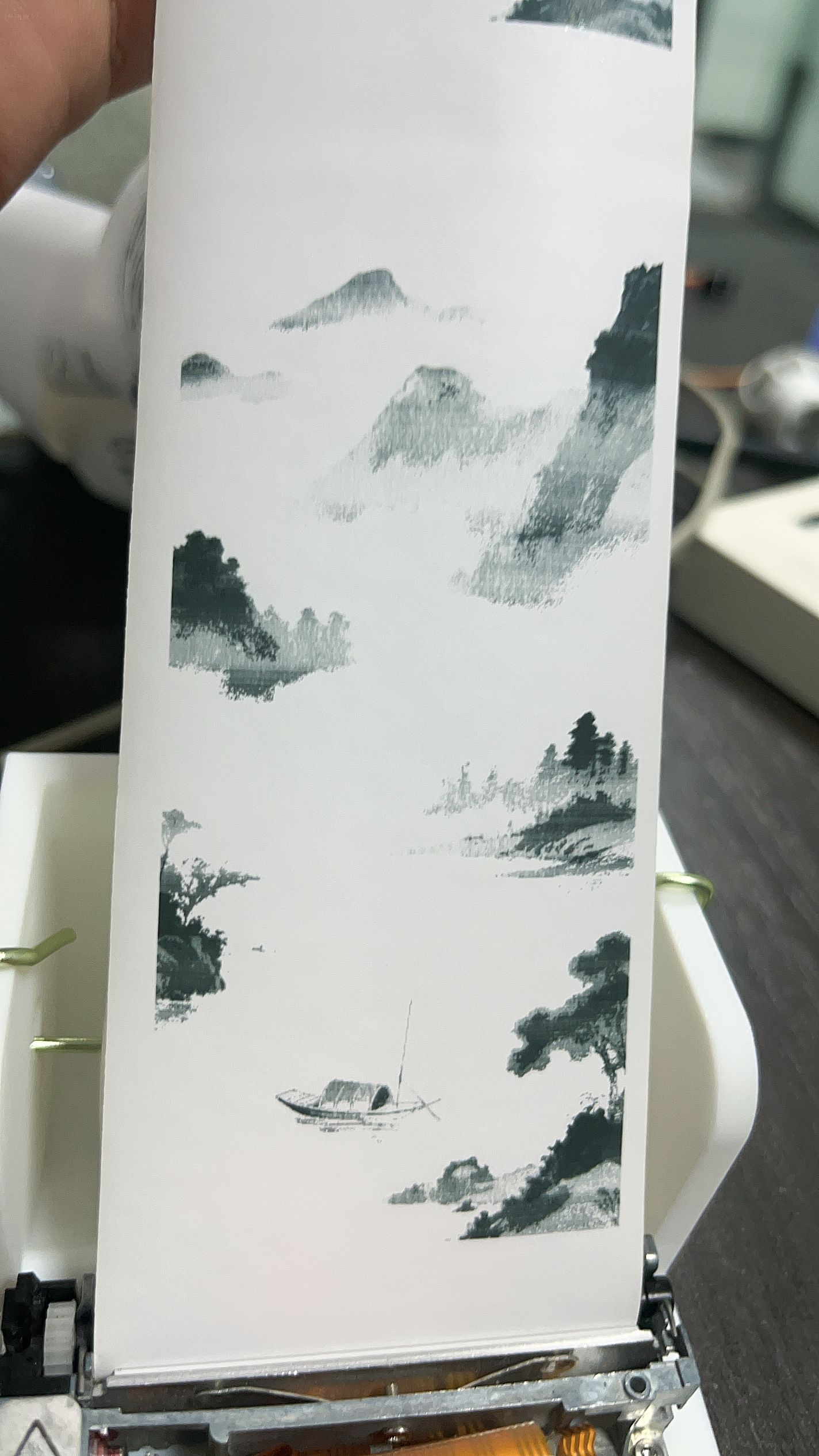

实际测试下来,靠加热时间控制很难实现16灰度等级的打印,即使理论上的16灰度等级,实际上最多也就4灰度等级,这个结论仅限于我当前的实验条件,线性化假设,以及这种国产的普通热敏打印机。

上面是卡通图像是抖动算法,下面的是灰度打印,可以看出是能表现出一些灰度来的。

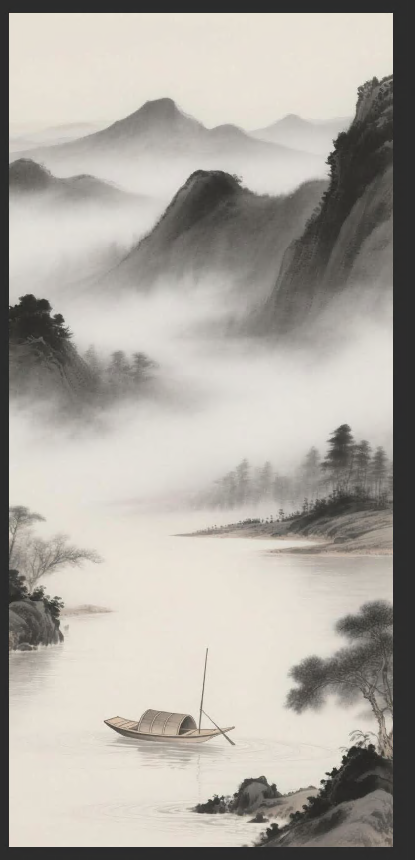

为了展现出灰度打印的实际效果,我这里选择了中国传统山水画,再来进一步实验。首图是原始绘图度,下面都是不同打印热密度下的表现。

最终结论,普通热敏打印机是可以实现灰度打印的,但是效果不敢恭维,基本没有很强的表现力,只能用于赚吆喝,堆参数而已,所有最终还是决定放弃此特性。

#16 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-19 17:44:32

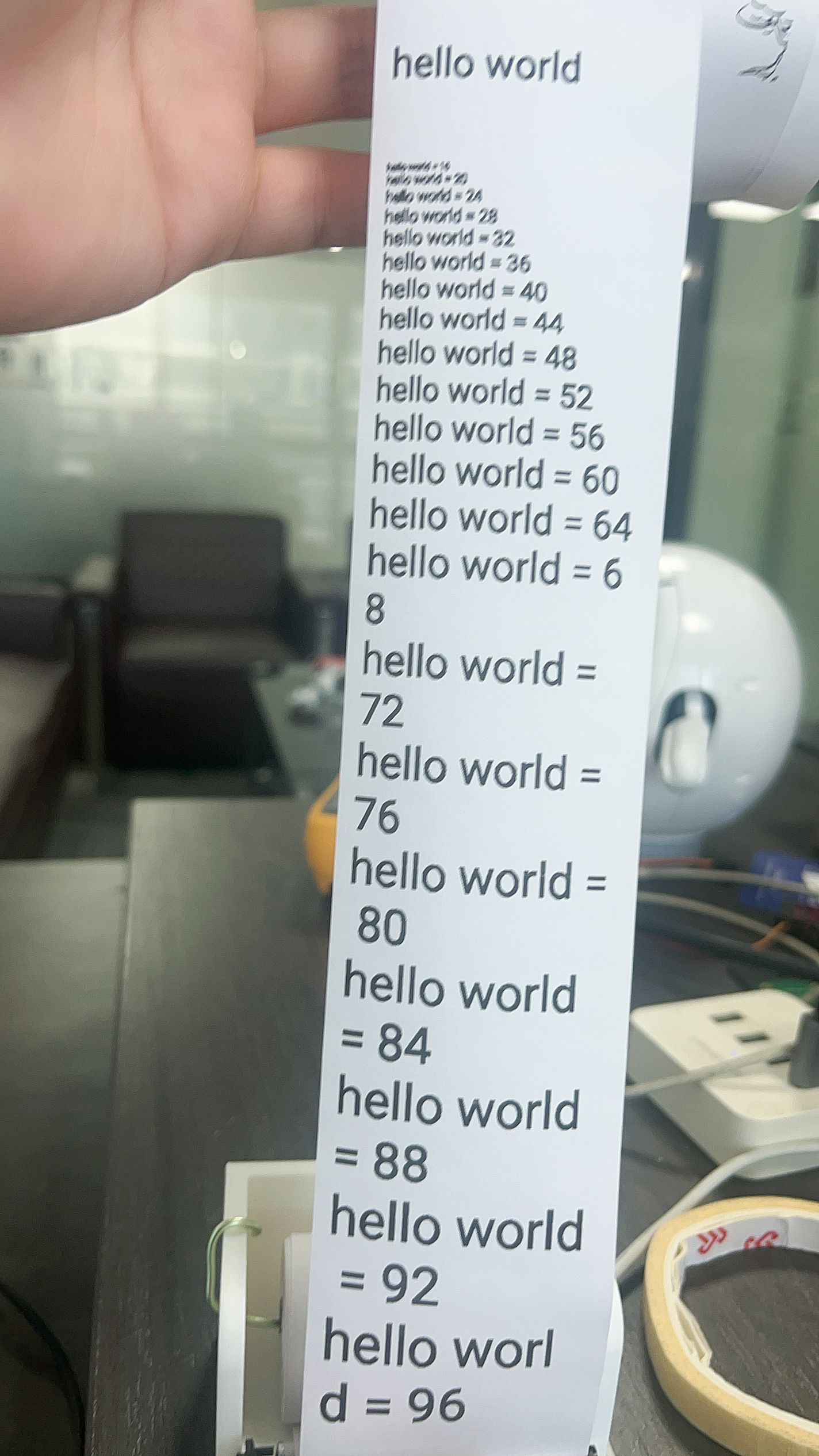

有了文字打印,当然少不了图片打印,以及二维码打印,这些都是轻车熟路,简单拓展下api就可以了。

下面是打印接口函数,既支持低阶接口也支持高阶打印接口,其中文字支持多语言混排,图片也支持抖动算法,自动二值化。

void printer_print(struct printer_t * p, unsigned char * buf, unsigned int len);

void printer_feed(struct printer_t * p, int lines);

void printer_cut(struct printer_t * p);

void printer_standby(struct printer_t * p);

void printer_print_hr(struct printer_t * p, int black, int white);

void printer_print_text(struct printer_t * p, enum printer_align_t align, const char * family, enum font_style_t style, int size, const char * fmt, ...);

void printer_print_qrcode(struct printer_t * p, enum printer_align_t align, int pixsz, const char * fmt, ...);

void printer_print_vision(struct printer_t * p, enum printer_align_t align, struct vision_t * v);

void printer_print_surface(struct printer_t * p, enum printer_align_t align, struct surface_t * s);

#17 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-19 17:39:24

#18 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-19 17:33:02

关于字体渲染,这里走了点弯路,开始研究的是MSDF技术,这种技术由SDF扩展而来,就是多通道有符号距离场,其优势是高质量缩放,很容易实现发光,阴影,空心字等特效,其存储方式类似于传统的点阵字体,但表现能力要强很多,这种技术主要是用在3D游戏领域,本以为应该也适合嵌入式,但综合评估下来,还是不太适合。

1,字库偏大,一个3000字的中文字库,在24像素大小时需要仅10MB

2,为了达到高质量缩放,必须采用更大像素尺寸的字库,这里字库体积会急剧膨胀

3,渲染效率这一块,虽然渲染代码不多,仅需10来行,但需要实现浮点型双线性插值,对于纯CPU渲染来说,代价偏大

研究成果我打个包丢这里,敢兴趣的可以研究研究,备注,对于嵌入式而言,此方案是歧路。

# MSDF字体生成工具

这是一个用于生成MSDF(多通道有符号距离场)字体的工具集,包含字体纹理生成和C代码转换功能。

## 使用方法

### 1. 生成MSDF字体纹理

使用 `msdf-atlas-gen.exe` 从TTF字体文件生成MSDF纹理:

#### Windows环境:

```bash

# 生成PNG格式纹理

.\msdf-atlas-gen.exe -font Roboto-Regular.ttf -type mtsdf -minsize 24 -emrange 0.2 -yorigin top -format png -imageout roboto_regular.png -json roboto_regular.json

```

#### Linux环境(使用Wine):

```bash

# 生成PNG格式纹理

wine msdf-atlas-gen.exe -font Roboto-Regular.ttf -type mtsdf -minsize 24 -emrange 0.2 -yorigin top -format png -imageout roboto_regular.png -json roboto_regular.json

```

#### 备注:

- **Kerning 支持**:如果TTF字体未能导出kerning信息,需要通过FontForge重新导出支持kern的字体。使用FontForge打开字体文件,确保包含kerning表,然后重新导出为TTF格式。

- **字体规范**:字体必须满足OpenType规范,无异常交集(overlapping contours)。可以使用FontForge检查和修复字体中的轮廓交集问题,确保字形路径正确且无自交。

- **字符集**:如果需要按需来生成字符,请使用-charset参数,所需字体存储在一个txt文本里,用双引号括起来,也在文件里指定unicode范围,用方括号描述,具体请参考chinese目录的中文字符集。

### 2. 转换为C头文件

使用Python脚本将生成的纹理和元数据转换为C头文件:

```bash

python3 msdfgenc.py <png_file> <json_file> <font_name>

```

#### 参数说明:

- `png_file`: 输入的PNG纹理文件

- `json_file`: 输入的JSON元数据文件

- `font_name`: 输出字体名称(用于生成的文件名和变量名)

#### 示例:

```bash

python3 msdfgenc.py roboto_regular.png roboto_regular.json roboto

```

## 依赖要求

- msdf-atlas-gen.exe

- Python 3.x

- wine (Linux平台)#19 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-19 17:17:14

打印机驱动本身,并不复杂,一个2相4线步进电机,每走两步,算一个像素,两根串行数据传输线,就是SPI里面的MOSI以及CLK,还有锁存线,以及至少1根加热控制线,加热控制线的加热时间通常是2ms左右,这里需要考虑热扩散效应,最好建立一个跟历史数据,并跟当前打印黑点数相关联的模型,动态调整加热时间,以达到最优加热效果。

这里在控制加热时有个坑,还得注意,从省事的角度,384个点一股脑传输进来再一起加热是最简单的,但是,但是,就怕但是,如果这384个点里面绝大部分是黑色,也就是需要加热,那么第一你的电源顶不住,第二,即使你的电源顶得住,打印头也顶不住,一般最多同时打印点数在128点左右,不然,你期望的黑色线条变成白茫茫一片,所以这里需要做点处理,当然也不复杂,超过了极限分批次处理就可以了。

还有一个影响体验的就是IO速度了,之前因为用的纯gpio模拟,打印速度太慢了,慢得无法忍受。这里在数据传输时需要上纯硬件SPI接口,来个10MHZ基本就快起来了,当然GPIO模拟慢,这里要批评一下沁恒微,I2C连续读写之间有固定的的延迟,这个延迟严重制约GPIO的速度,这里还看官方是否能改进吧,不然这些桥接芯片在高速场景就无法满足需求了。

#20 Re: 全志 SOC » 我来玩玩热敏打印机,先实现AI打印机,再顺带赋能作业帮APP » 2026-01-19 17:02:10

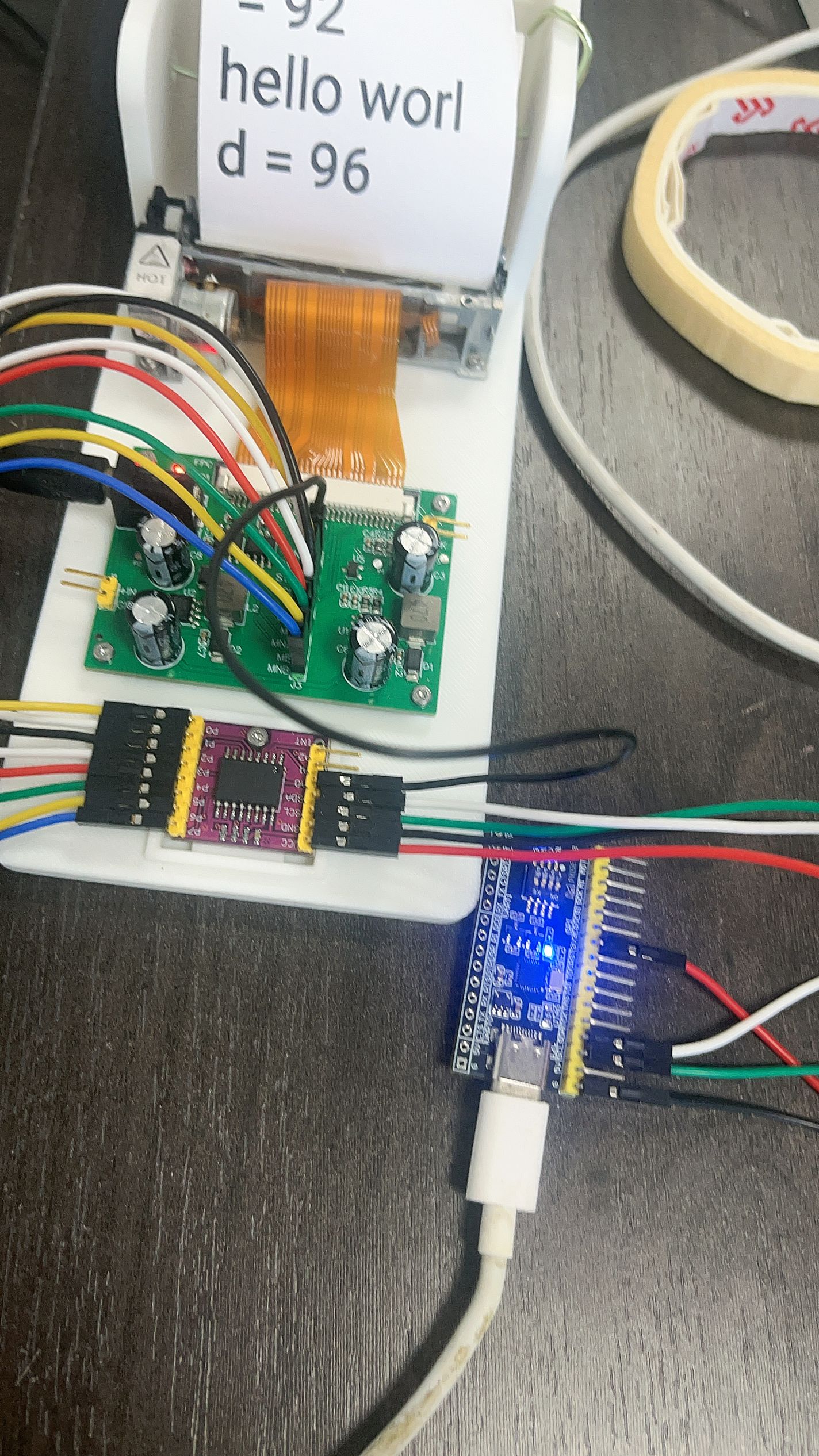

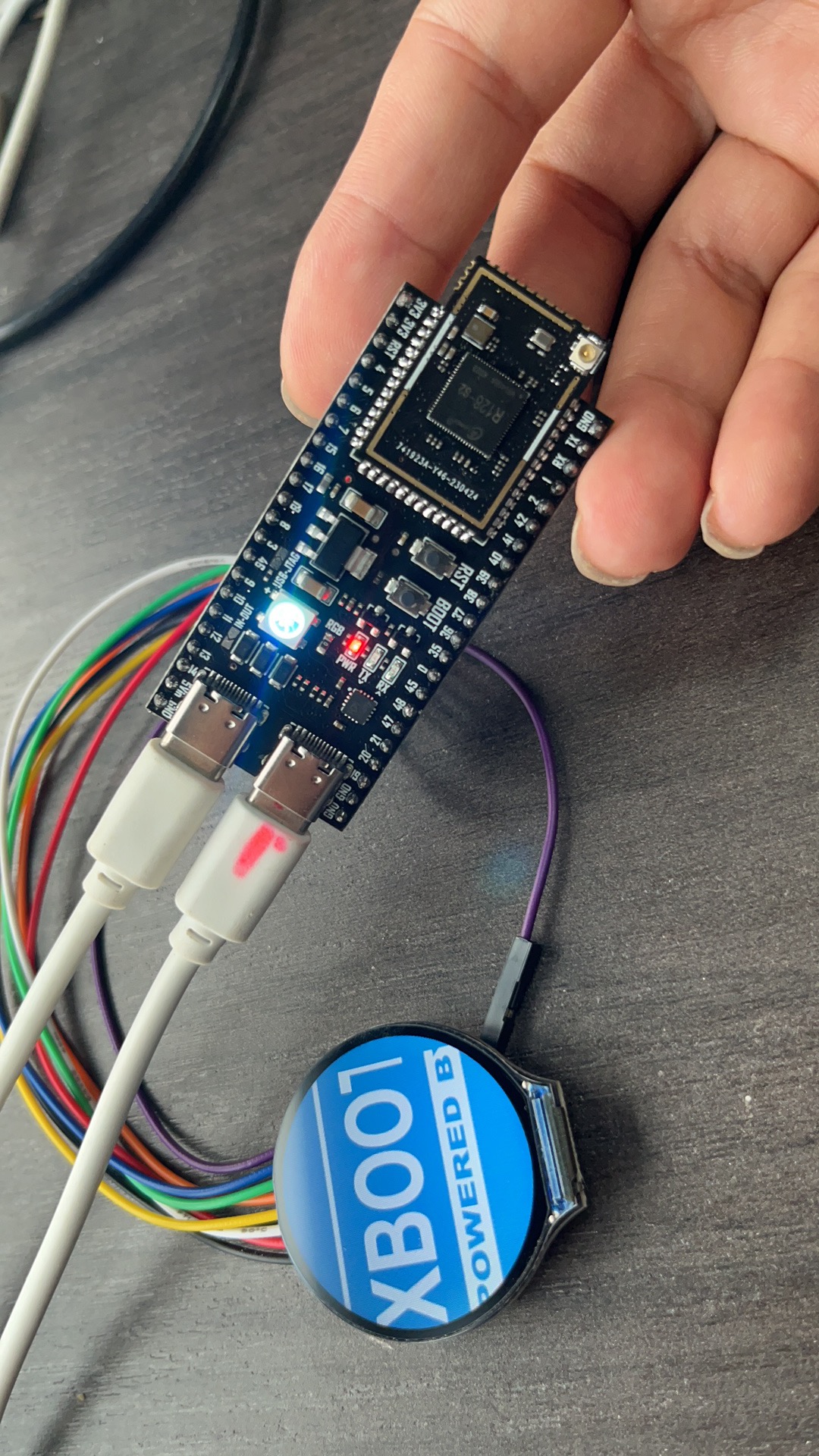

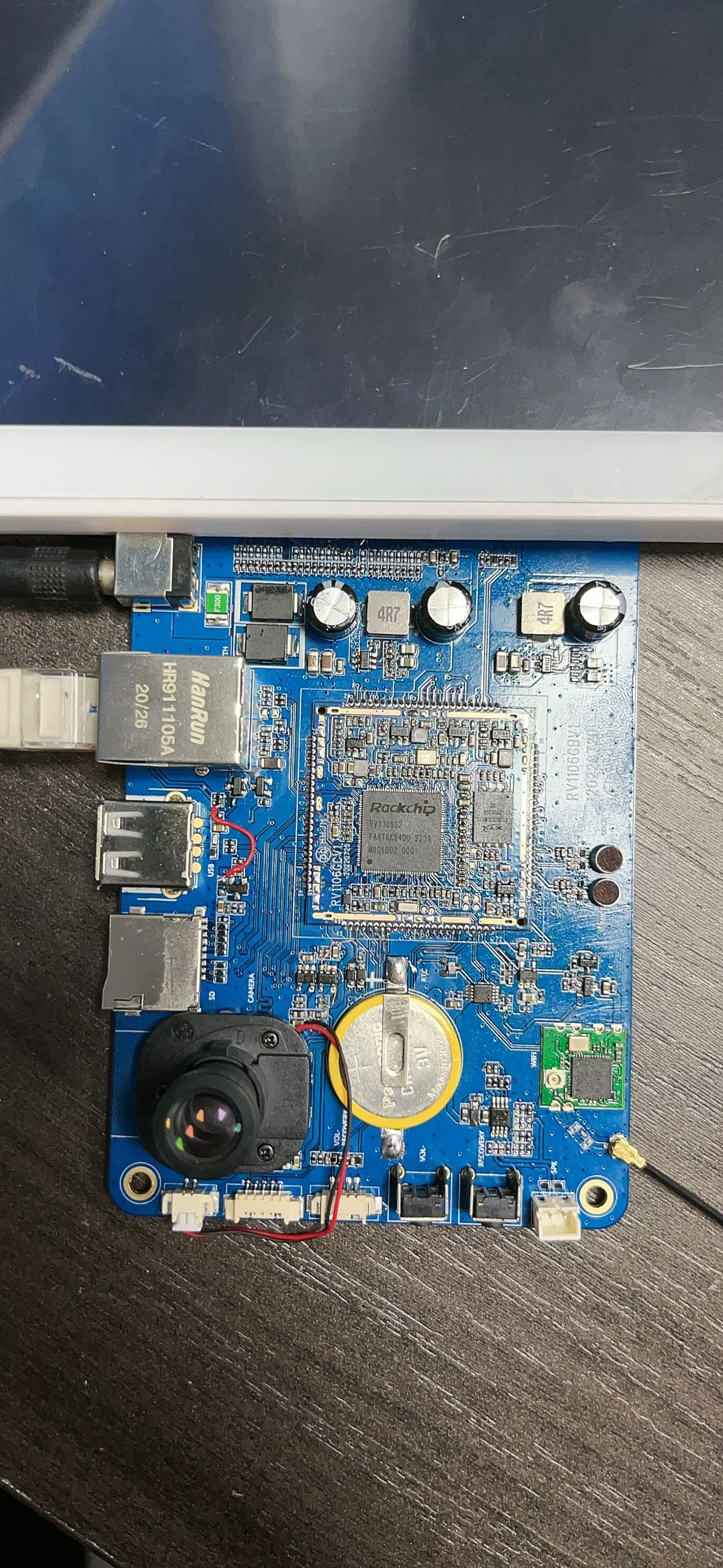

先介绍下当前的实验环境:

软件环境:

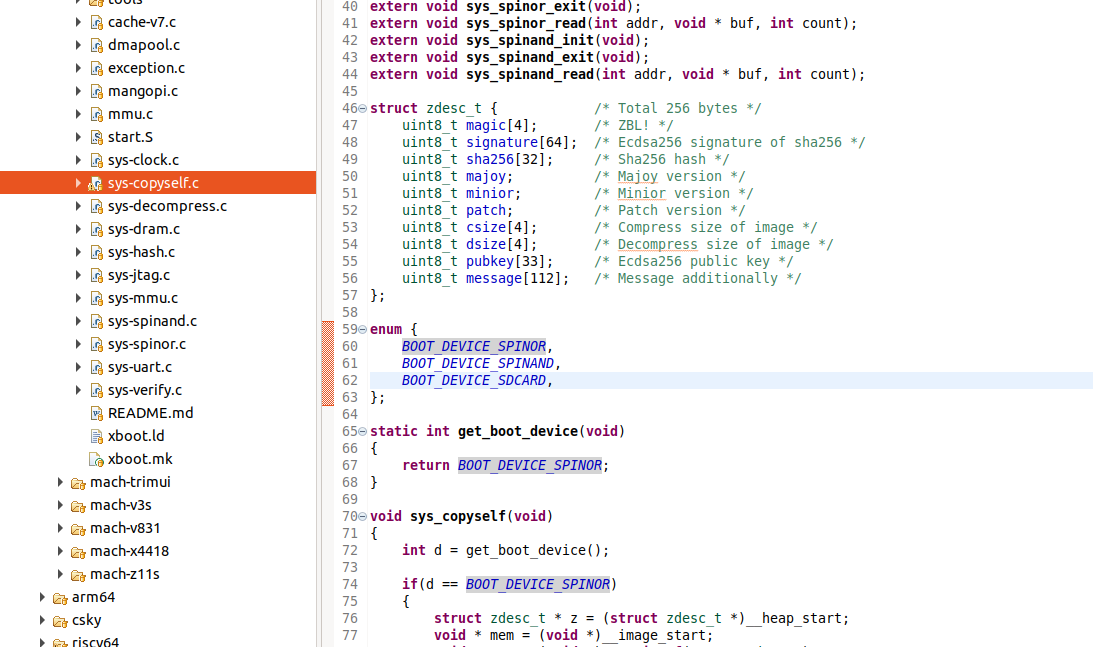

XSTAR开发环境,由原先的XBOOT分离而来.。XBOOT计划分离出两个独立项目,一个XSPARK,聚焦bootloader;另一个就是XSTAR,跨操作系统纯C版APP开发框架。

硬件环境:

因为有了XSTAR加持,所以就可以不上任何SOC了,直接用PC搞定,为了让PC拥有控制IO的能力,这里用沁恒微的CH347F这款USB口扩展芯片,其可以扩展出I2C,SPI,GPIO,UART,JTAG功能

打印机直接采用常用的384点,57mm的普通热敏打印机,因为打印机所需IO较多,这里采用了PCF8574这款I2C接口的芯片来扩展GPIO,一颗PCF8574可以扩展8个GPIO口,可以满足打印机模块的核心功能驱动,辅助性的功能,就需额外扩展了,比如温度检测,纸张检测,切刀等等。

#22 Re: 全志 SOC » libxnes开源了,这是一款纯C99标准拥有超强的可移植性,可读性,可玩性的高精度NES模拟器库,纯手写打造,感兴趣的可以在这帖子里恰饭。 » 2024-10-14 09:29:52

#23 Re: 全志 SOC » libxnes开源了,这是一款纯C99标准拥有超强的可移植性,可读性,可玩性的高精度NES模拟器库,纯手写打造,感兴趣的可以在这帖子里恰饭。 » 2024-10-11 20:38:14

#24 Re: 全志 SOC » libxnes开源了,这是一款纯C99标准拥有超强的可移植性,可读性,可玩性的高精度NES模拟器库,纯手写打造,感兴趣的可以在这帖子里恰饭。 » 2024-10-11 09:43:18

为了增强代码的可读性,将卡带的读写接口进行拆分,拆分成完全独立的cpu总线读写以及完全独立的ppu总线读写,新接口如下:

uint8_t (*cpu_read)(struct xnes_ctx_t * ctx, uint16_t addr);

void (*cpu_write)(struct xnes_ctx_t * ctx, uint16_t addr, uint8_t val);

uint8_t (*ppu_read)(struct xnes_ctx_t * ctx, uint16_t addr);

void (*ppu_write)(struct xnes_ctx_t * ctx, uint16_t addr, uint8_t val);

void (*ppu_step)(struct xnes_ctx_t * ctx);

void (*apu_step)(struct xnes_ctx_t * ctx);红白机系统里面有两条总线,一条是CPU总线,另一条是PPU总线,两者完全独立,CPU是无法直接访问PPU总线上的内容的,必须通过PPU的寄存器来间接访,因为PPU寄存器才8个,只靠这8个来通信效率肯定不太高,所有这8个寄存器里面又有个OAM DMA,可以通过DMA来提供通信效率。

顺便再导出一个ppu step接口,以及apu step接口,某些卡带里面带有音频扩展能力,虽然现在没实现,但先预留接口,增强扩展能力。

#25 Re: 全志 SOC » libxnes开源了,这是一款纯C99标准拥有超强的可移植性,可读性,可玩性的高精度NES模拟器库,纯手写打造,感兴趣的可以在这帖子里恰饭。 » 2024-10-11 09:16:08

现在的实现,虽说是精确到每一个指令的准确周期,但每一条指令都是原子化的,这就意味着,要么不干活,要干就干完,但实际情况,并不是这样,比如一条指令需要多个周期,取指周期,译码周期,执行周期,访问内存周期,跨页周期,条件跳转判断周期,每个周期都需要干特别的事情,说白了点,就是现在的实现粒度不够细,(当然对于模拟器也没必要特别细,比如精确到电路的电平及时序这种级别)。之所以会思考粒度问题,就是因为测试发现,nesdev网站上的那些刁钻的测试rom,就专门针对这种情况而设计的,要想通过测试,就必须将原子化的指令拆分出各种过程,这个任务是当前的重点任务了,比起支持更多的mapper这些来说,显得更关键了点。

网上有完全精确的模拟器实现,但是效率太低,不太实用,这个粒度的细分就需要好好考究了,要分但又不能太细,需要做好折中。估计接下来一段时间会优先考虑这些问题,估计结构上会做较大变化了。

#26 Re: 全志 SOC » libxnes开源了,这是一款纯C99标准拥有超强的可移植性,可读性,可玩性的高精度NES模拟器库,纯手写打造,感兴趣的可以在这帖子里恰饭。 » 2024-10-09 18:01:18

#27 Re: 全志 SOC » libxnes开源了,这是一款纯C99标准拥有超强的可移植性,可读性,可玩性的高精度NES模拟器库,纯手写打造,感兴趣的可以在这帖子里恰饭。 » 2024-10-09 17:54:36

#28 Re: 全志 SOC » libxnes开源了,这是一款纯C99标准拥有超强的可移植性,可读性,可玩性的高精度NES模拟器库,纯手写打造,感兴趣的可以在这帖子里恰饭。 » 2024-10-09 09:15:44

添加对mapper 66的支持,因140跟66比较接近,也顺便一起支持了

https://gitee.com/xboot/libxnes/blob/master/src/mapper66.c

https://gitee.com/xboot/libxnes/blob/master/src/mapper140.c

#29 Re: 全志 SOC » libxnes开源了,这是一款纯C99标准拥有超强的可移植性,可读性,可玩性的高精度NES模拟器库,纯手写打造,感兴趣的可以在这帖子里恰饭。 » 2024-10-08 11:42:21

#30 全志 SOC » libxnes开源了,这是一款纯C99标准拥有超强的可移植性,可读性,可玩性的高精度NES模拟器库,纯手写打造,感兴趣的可以在这帖子里恰饭。 » 2024-10-08 09:43:59

- xboot

- 回复: 33

开源网址:

https://github.com/xboot/libxnes

https://gitee.com/xboot/libxnes

编译了一个windows版,可以命令行执行,或者直接将rom拖到xnes即可运行

xnes.7z

#31 Re: 全志 SOC » 45块顺丰包邮买到的10.1寸保资LCD价签F1C200S 值不值 » 2024-09-26 01:08:17

11, SPI NAND Flash 128MB

xfel spinand

Found spi nand flash 'MX35LF1GE4AB' with 134217728 bytes12,上传一个dump固件,从0地址dump到0x03140000,后面UDISK分区没必要dump了。

blozi_0x0_0x3140000.7z

花了几个小时的初步研究成果,先贴出来,期待大家再接再厉!

#32 Re: 全志 SOC » 45块顺丰包邮买到的10.1寸保资LCD价签F1C200S 值不值 » 2024-09-26 01:01:51

补充一些有用的信息:

1,供电12V

2,调试串口uart1

3,ssd2828使用spi1来初始化

4,一些gpio

GPIOs 0-191, platform/pio, pio:

gpio-1 (lcd_reset ) out hi

gpio-130 (wlan_regon ) out hi

gpio-131 (wlan_hostwake ) in lo

gpio-133 (? ) out hiplatform/1c21000.pwm, 2 PWM devices

pwm-0 (lcd ): requested enabled

pwm-1 ((null) ):5,分区表

-total partitions:9-

-name- -start- -size-

bootlogo : 400000 80000

env : 480000 40000

boot : 4c0000 600000

rootfs : ac0000 f00000

rootfs_data : 19c0000 f00000

recovery : 28c0000 800000

misc : 30c0000 40000

private : 3100000 40000

UDISK : 3140000 0 6,LCD屏参,只跑38帧,估计怕性能不够吧

[ 0.223950] ***

[ 0.223961] *** Interface:

[ 0.223972] *** Parallel HV Panel

[ 0.223983] *** Lcd Frm to RGB666

[ 0.223992] ***

[ 0.224002] *** Timing:

[ 0.224013] *** lcd_x: 800

[ 0.224025] *** lcd_y: 1280

[ 0.224036] *** lcd_ht: 1220

[ 0.224047] *** lcd_hbp: 70

[ 0.224058] *** lcd_vt: 1315

[ 0.224069] *** lcd_vbp: 22

[ 0.224081] *** lcd_hspw: 20

[ 0.224092] *** lcd_vspw: 6

[ 0.224103] *** lcd_frame_frq: 38Hz

[ 0.224112] ***

[ 0.224125] *** WRN03: Recommend "lcd_dclk_frq = 96"

[ 0.224135] ***

[ 0.224145] *** LCD Panel Parameter Check End7.内核入口点0x80008000

8,设备树内存地址0x81000000

9,sd2828 RGB转MIPI初始化代码,可以从内核里逆向,或者直接上逻辑分析仪

[ 2.944530] ssd2828 spi1.0: ssd2828_probe

[ 2.949253] ssd2828 spi1.0: reg_value = 0x2828

[ 2.954267] ssd2828 spi1.0: ssd2828_init START

[ 3.312945] ssd2828 spi1.0: ssd2828_init SUCCESS!10, pinctrl-maps

Pinctrl maps:

device twi0

state default

type MUX_GROUP (2)

controlling device pio

group PD12

function twi0

device twi0

state default

type CONFIGS_GROUP (4)

controlling device pio

group PD12

config 00000000

config 00000000

config 00000000

device twi0

state default

type MUX_GROUP (2)

controlling device pio

group PD0

function twi0

device twi0

state default

type CONFIGS_GROUP (4)

controlling device pio

group PD0

config 00000000

config 00000000

config 00000000

device twi0

state sleep

type MUX_GROUP (2)

controlling device pio

group PD12

function io_disabled

device twi0

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PD12

config 00140009

config 00000005

device twi0

state sleep

type MUX_GROUP (2)

controlling device pio

group PD0

function io_disabled

device twi0

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PD0

config 00140009

config 00000005

device uart1

state default

type MUX_GROUP (2)

controlling device pio

group PA2

function uart1

device uart1

state default

type CONFIGS_GROUP (4)

controlling device pio

group PA2

config 00000003

config 00000000

config 00000000

device uart1

state default

type MUX_GROUP (2)

controlling device pio

group PA3

function uart1

device uart1

state default

type CONFIGS_GROUP (4)

controlling device pio

group PA3

config 00000003

config 00000000

config 00000000

device uart1

state sleep

type MUX_GROUP (2)

controlling device pio

group PA3

function io_disabled

device uart1

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PA3

config 00140009

config 00000003

device uart1

state sleep

type MUX_GROUP (2)

controlling device pio

group PA2

function io_disabled

device uart1

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PA2

config 00140009

config 00000003

device spinand

state default

type MUX_GROUP (2)

controlling device pio

group PC1

function spi0

device spinand

state default

type CONFIGS_GROUP (4)

controlling device pio

group PC1

config 00000003

config 00000000

config 00000000

device spinand

state default

type MUX_GROUP (2)

controlling device pio

group PC0

function spi0

device spinand

state default

type CONFIGS_GROUP (4)

controlling device pio

group PC0

config 00000000

config 00000000

config 00000000

device spinand

state default

type MUX_GROUP (2)

controlling device pio

group PC3

function spi0

device spinand

state default

type CONFIGS_GROUP (4)

controlling device pio

group PC3

config 00000000

config 00000000

config 00000000

device spinand

state default

type MUX_GROUP (2)

controlling device pio

group PC2

function spi0

device spinand

state default

type CONFIGS_GROUP (4)

controlling device pio

group PC2

config 00000000

config 00000000

config 00000000

device spinand

state sleep

type MUX_GROUP (2)

controlling device pio

group PC0

function io_disabled

device spinand

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PC0

config 00140009

config 00000005

device spinand

state sleep

type MUX_GROUP (2)

controlling device pio

group PC1

function io_disabled

device spinand

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PC1

config 00140009

config 00000005

device spinand

state sleep

type MUX_GROUP (2)

controlling device pio

group PC2

function io_disabled

device spinand

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PC2

config 00140009

config 00000005

device spinand

state sleep

type MUX_GROUP (2)

controlling device pio

group PC3

function io_disabled

device spinand

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PC3

config 00140009

config 00000005

device spi1

state default

type MUX_GROUP (2)

controlling device pio

group PE7

function spi1

device spi1

state default

type CONFIGS_GROUP (4)

controlling device pio

group PE7

config 00000003

config 00000000

config 00000000

device spi1

state default

type MUX_GROUP (2)

controlling device pio

group PE9

function spi1

device spi1

state default

type CONFIGS_GROUP (4)

controlling device pio

group PE9

config 00000000

config 00000000

config 00000000

device spi1

state default

type MUX_GROUP (2)

controlling device pio

group PE8

function spi1

device spi1

state default

type CONFIGS_GROUP (4)

controlling device pio

group PE8

config 00000000

config 00000000

config 00000000

device spi1

state default

type MUX_GROUP (2)

controlling device pio

group PE10

function spi1

device spi1

state default

type CONFIGS_GROUP (4)

controlling device pio

group PE10

config 00000000

config 00000000

config 00000000

device spi1

state sleep

type MUX_GROUP (2)

controlling device pio

group PE7

function io_disabled

device spi1

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PE7

config 00140009

config 00000005

device spi1

state sleep

type MUX_GROUP (2)

controlling device pio

group PE8

function io_disabled

device spi1

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PE8

config 00140009

config 00000005

device spi1

state sleep

type MUX_GROUP (2)

controlling device pio

group PE9

function io_disabled

device spi1

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PE9

config 00140009

config 00000005

device spi1

state sleep

type MUX_GROUP (2)

controlling device pio

group PE10

function io_disabled

device spi1

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PE10

config 00140009

config 00000005

device sdc0

state default

type MUX_GROUP (2)

controlling device pio

group PF0

function sdc0

device sdc0

state default

type CONFIGS_GROUP (4)

controlling device pio

group PF0

config 00280009

config 00000003

config 00000000

device sdc0

state default

type MUX_GROUP (2)

controlling device pio

group PF1

function sdc0

device sdc0

state default

type CONFIGS_GROUP (4)

controlling device pio

group PF1

config 00280009

config 00000003

config 00000000

device sdc0

state default

type MUX_GROUP (2)

controlling device pio

group PF2

function sdc0

device sdc0

state default

type CONFIGS_GROUP (4)

controlling device pio

group PF2

config 00280009

config 00000003

config 00000000

device sdc0

state default

type MUX_GROUP (2)

controlling device pio

group PF3

function sdc0

device sdc0

state default

type CONFIGS_GROUP (4)

controlling device pio

group PF3

config 00280009

config 00000003

config 00000000

device sdc0

state default

type MUX_GROUP (2)

controlling device pio

group PF4

function sdc0

device sdc0

state default

type CONFIGS_GROUP (4)

controlling device pio

group PF4

config 00280009

config 00000003

config 00000000

device sdc0

state default

type MUX_GROUP (2)

controlling device pio

group PF5

function sdc0

device sdc0

state default

type CONFIGS_GROUP (4)

controlling device pio

group PF5

config 00280009

config 00000003

config 00000000

device sdc0

state sleep

type MUX_GROUP (2)

controlling device pio

group PF0

function io_disabled

device sdc0

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PF0

config 00140009

config 00000003

device sdc0

state sleep

type MUX_GROUP (2)

controlling device pio

group PF1

function io_disabled

device sdc0

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PF1

config 00140009

config 00000003

device sdc0

state sleep

type MUX_GROUP (2)

controlling device pio

group PF2

function io_disabled

device sdc0

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PF2

config 00140009

config 00000003

device sdc0

state sleep

type MUX_GROUP (2)

controlling device pio

group PF3

function io_disabled

device sdc0

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PF3

config 00140009

config 00000003

device sdc0

state sleep

type MUX_GROUP (2)

controlling device pio

group PF4

function io_disabled

device sdc0

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PF4

config 00140009

config 00000003

device sdc0

state sleep

type MUX_GROUP (2)

controlling device pio

group PF5

function io_disabled

device sdc0

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PF5

config 00140009

config 00000003

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD1

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD1

config 00000005

config 00000000

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD2

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD2

config 00000005

config 00000000

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD3

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD3

config 00000005

config 00000000

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD4

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD4

config 00000005

config 00000000

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD5

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD5

config 00000005

config 00000000

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD6

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD6

config 00000005

config 00000000

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD7

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD7

config 00000005

config 00000000

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD8

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD8

config 00000005

config 00000000

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD9

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD9

config 00000005

config 00000000

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD10

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD10

config 00000005

config 00000000

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD11

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD11

config 00000005

config 00000000

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD13

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD13

config 00000005

config 00000000

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD14

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD14

config 00000005

config 00000000

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD15

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD15

config 00000005

config 00000000

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD16

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD16

config 00000005

config 00000000

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD17

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD17

config 00000005

config 00000000

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD18

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD18

config 00280009

config 00000005

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD19

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD19

config 00280009

config 00000005

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD20

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD20

config 00280009

config 00000005

config 00000000

device lcd0

state active

type MUX_GROUP (2)

controlling device pio

group PD21

function lcd0

device lcd0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PD21

config 00280009

config 00000005

config 00000000

device pwm0.0

state active

type MUX_GROUP (2)

controlling device pio

group PE12

function pwm0

device pwm0.0

state active

type CONFIGS_GROUP (4)

controlling device pio

group PE12

config 00140009

config 00000005

device pwm0.0

state sleep

type MUX_GROUP (2)

controlling device pio

group PE12

function io_disabled

device pwm0.0

state sleep

type CONFIGS_GROUP (4)

controlling device pio

group PE12

config 00140009

config 00000005#33 Re: 全志 SOC » 45块顺丰包邮买到的10.1寸保资LCD价签F1C200S 值不值 » 2024-09-26 00:47:15

我来贴个dts

/memreserve/ 0x81000000 0x10000;

/ {

model = "sun3iw1p1";

compatible = "arm,sun3iw1p1", "arm,sun3iw1p1";

interrupt-parent = <0x00000001>;

#address-cells = <0x00000002>;

#size-cells = <0x00000002>;

clocks {

compatible = "allwinner,sunxi-clk-init";

device_type = "clocks";

#address-cells = <0x00000002>;

#size-cells = <0x00000002>;

ranges;

reg = <0x00000000 0x01c20000 0x00000000 0x000002d0>;

losc {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-clock";

clock-frequency = <0x00008000>;

clock-output-names = "losc";

};

hosc {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-clock";

clock-frequency = <0x016e3600>;

clock-output-names = "hosc";

linux,phandle = <0x00000008>;

phandle = <0x00000008>;

};

pll_cpu {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-pll-clock";

lock-mode = "none";

assigned-clock-rates = <0x20e6da00>;

clock-output-names = "pll_cpu";

};

pll_audio {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-pll-clock";

lock-mode = "none";

clock-output-names = "pll_audio";

linux,phandle = <0x00000002>;

phandle = <0x00000002>;

};

pll_video {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-pll-clock";

lock-mode = "none";

assigned-clock-rates = <0x11b3dc40>;

clock-output-names = "pll_video";

linux,phandle = <0x00000003>;

phandle = <0x00000003>;

};

pll_ve {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-pll-clock";

lock-mode = "none";

clock-output-names = "pll_ve";

linux,phandle = <0x0000000a>;

phandle = <0x0000000a>;

};

pll_ddr {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-pll-clock";

lock-mode = "none";

assigned-clock-rates = <0x1298be00>;

clock-output-names = "pll_ddr";

};

pll_periph {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-pll-clock";

lock-mode = "none";

clock-output-names = "pll_periph";

linux,phandle = <0x00000004>;

phandle = <0x00000004>;

};

pll_audiox8 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000002>;

clock-mult = <0x00000008>;

clock-div = <0x00000001>;

clock-output-names = "pll_audiox8";

};

pll_audiox4 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000002>;

clock-mult = <0x00000008>;

clock-div = <0x00000002>;

clock-output-names = "pll_audiox4";

};

pll_audiox2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000002>;

clock-mult = <0x00000008>;

clock-div = <0x00000004>;

clock-output-names = "pll_audiox2";

};

pll_videox2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000003>;

clock-mult = <0x00000002>;

clock-div = <0x00000001>;

clock-output-names = "pll_videox2";

};

pll_periphx2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,fixed-factor-clock";

clocks = <0x00000004>;

clock-mult = <0x00000002>;

clock-div = <0x00000001>;

clock-output-names = "pll_periphx2";

};

cpu {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "cpu";

};

pll_periphahb {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "pll_periphahb";

};

ahb1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "ahb1";

linux,phandle = <0x0000001e>;

phandle = <0x0000001e>;

};

apb1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "apb1";

};

sdmmc0_mod {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "sdmmc0_mod";

linux,phandle = <0x0000002a>;

phandle = <0x0000002a>;

};

sdmmc0_bus {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "sdmmc0_bus";

linux,phandle = <0x0000002b>;

phandle = <0x0000002b>;

};

sdmmc0_rst {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "sdmmc0_rst";

linux,phandle = <0x0000002c>;

phandle = <0x0000002c>;

};

sdmmc1_mod {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "sdmmc1_mod";

linux,phandle = <0x0000002f>;

phandle = <0x0000002f>;

};

sdmmc1_bus {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "sdmmc1_bus";

linux,phandle = <0x00000030>;

phandle = <0x00000030>;

};

sdmmc1_rst {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "sdmmc1_rst";

linux,phandle = <0x00000031>;

phandle = <0x00000031>;

};

spi0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "spi0";

linux,phandle = <0x0000001f>;

phandle = <0x0000001f>;

};

spi1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "spi1";

linux,phandle = <0x00000026>;

phandle = <0x00000026>;

};

usbphy0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "usbphy0";

linux,phandle = <0x00000043>;

phandle = <0x00000043>;

};

usbotg {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "usbotg";

linux,phandle = <0x00000044>;

phandle = <0x00000044>;

};

audio {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "audio";

linux,phandle = <0x00000045>;

phandle = <0x00000045>;

};

avs {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "avs";

};

codec {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "codec";

linux,phandle = <0x0000004b>;

phandle = <0x0000004b>;

};

spdif {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "spdif";

linux,phandle = <0x00000048>;

phandle = <0x00000048>;

};

debe {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "debe";

linux,phandle = <0x00000034>;

phandle = <0x00000034>;

};

defe {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "defe";

linux,phandle = <0x00000035>;

phandle = <0x00000035>;

};

tcon {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "tcon";

linux,phandle = <0x00000036>;

phandle = <0x00000036>;

};

deinterlace {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "deinterlace";

linux,phandle = <0x00000038>;

phandle = <0x00000038>;

};

tve_clk2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "tve_clk2";

linux,phandle = <0x00000037>;

phandle = <0x00000037>;

};

tve_clk1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "tve_clk1";

};

tvd {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "tvd";

linux,phandle = <0x00000039>;

phandle = <0x00000039>;

};

csi_m {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "csi_m";

linux,phandle = <0x00000040>;

phandle = <0x00000040>;

};

ve {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "ve";

linux,phandle = <0x0000000b>;

phandle = <0x0000000b>;

};

sdram {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "sdram";

};

dma {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "dma";

linux,phandle = <0x00000006>;

phandle = <0x00000006>;

};

pio {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "pio";

linux,phandle = <0x00000005>;

phandle = <0x00000005>;

};

uart0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "uart0";

linux,phandle = <0x0000000c>;

phandle = <0x0000000c>;

};

uart1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "uart1";

linux,phandle = <0x0000000f>;

phandle = <0x0000000f>;

};

uart2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "uart2";

linux,phandle = <0x00000012>;

phandle = <0x00000012>;

};

twi0 {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "twi0";

linux,phandle = <0x00000015>;

phandle = <0x00000015>;

};

twi1 {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "twi1";

linux,phandle = <0x00000018>;

phandle = <0x00000018>;

};

twi2 {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "twi2";

linux,phandle = <0x0000001b>;

phandle = <0x0000001b>;

};

rsb {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "rsb";

};

cir {

#clock-cells = <0x00000000>;

compatible = "allwinner,sunxi-periph-clock";

clock-output-names = "cir";

linux,phandle = <0x00000009>;

phandle = <0x00000009>;

};

};

soc {

compatible = "simple-bus";

#address-cells = <0x00000002>;

#size-cells = <0x00000002>;

device_type = "soc";

ranges;

pinctrl@01c20800 {

compatible = "allwinner,sun3iw1p1-pinctrl";

reg = <0x00000000 0x01c20800 0x00000000 0x00000400>;

interrupts = <0x00000026 0x00000027 0x00000028>;

device_type = "pio";

clocks = <0x00000005>;

gpio-controller;

interrupt-controller;

#interrupt-cells = <0x00000002>;

#size-cells = <0x00000000>;

#gpio-cells = <0x00000006>;

linux,phandle = <0x00000024>;

phandle = <0x00000024>;

ir@0 {

allwinner,function = "ir";

allwinner,muxsel = <0x00000004>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000001>;

linux,phandle = <0x00000007>;

phandle = <0x00000007>;

};

uart0@1 {

allwinner,pins = "PF2", "PF4";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x00000007>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000001>;

linux,phandle = <0x0000000e>;

phandle = <0x0000000e>;

};

uart1@1 {

allwinner,pins = "PA3", "PA2";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x00000007>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000001>;

linux,phandle = <0x00000011>;

phandle = <0x00000011>;

};

uart2@0 {

allwinner,pname = "uart2_tx", "uart2_rx";

allwinner,function = "uart2";

allwinner,muxsel = <0x00000003>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000001>;

linux,phandle = <0x00000013>;

phandle = <0x00000013>;

};

uart2@1 {

allwinner,function = "io_disabled";

allwinner,muxsel = <0x00000007>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000001>;

linux,phandle = <0x00000014>;

phandle = <0x00000014>;

};

twi0@1 {

allwinner,pins = "PD12", "PD0";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x00000007>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

linux,phandle = <0x00000017>;

phandle = <0x00000017>;

};

twi1@1 {

allwinner,pins = "PB0", "PB1";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x00000007>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

linux,phandle = <0x0000001a>;

phandle = <0x0000001a>;

};

twi2@1 {

allwinner,function = "io_disabled";

allwinner,muxsel = <0x00000007>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

linux,phandle = <0x0000001d>;

phandle = <0x0000001d>;

};

spi0@2 {

allwinner,pins = "PC0", "PC1", "PC2";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x00000007>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

linux,phandle = <0x00000022>;

phandle = <0x00000022>;

};

spi0@3 {

allwinner,pins = "PC3";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x00000007>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

linux,phandle = <0x00000023>;

phandle = <0x00000023>;

};

spi1@2 {

allwinner,pins = "PE7", "PE8", "PE9", "PE10";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x00000007>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

linux,phandle = <0x00000029>;

phandle = <0x00000029>;

};

csi0@0 {

allwinner,pins = "PE0", "PE1", "PE2", "PE3", "PE4", "PE5", "PE6", "PE7", "PE8", "PE9", "PE10";

allwinner,pname = "csi0_hsync", "csi0_vsync", "csi0_pck", "csi0_d0", "csi0_d1", "csi0_d2", "csi0_d3", "csi0_d4", "csi0_d5", "csi0_d6", "csi0_d7";

allwinner,function = "csi0";

allwinner,muxsel = <0x00000002>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

allwinner,data = <0x00000000>;

linux,phandle = <0x00000041>;

phandle = <0x00000041>;

};

csi0_sleep@0 {

allwinner,pins = "PE0", "PE1", "PE2", "PE3", "PE4", "PE5", "PE6", "PE7", "PE8", "PE9", "PE10";

allwinner,pname = "csi0_hsync", "csi0_vsync", "csi0_pck", "csi0_d0", "csi0_d1", "csi0_d2", "csi0_d3", "csi0_d4", "csi0_d5", "csi0_d6", "csi0_d7";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x00000007>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

allwinner,data = <0x00000000>;

linux,phandle = <0x00000042>;

phandle = <0x00000042>;

};

pwm0@0 {

allwinner,pins = "PE12";

allwinner,function = "pwm0";

allwinner,muxsel = <0x00000004>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

linux,phandle = <0x0000003c>;

phandle = <0x0000003c>;

};

pwm0@1 {

allwinner,pins = "PE12";

allwinner,function = "pwm0";

allwinner,muxsel = <0x00000007>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

linux,phandle = <0x0000003d>;

phandle = <0x0000003d>;

};

pwm1@0 {

allwinner,function = "pwm1";

allwinner,muxsel = <0x00000003>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

linux,phandle = <0x0000003e>;

phandle = <0x0000003e>;

};

pwm1@1 {

allwinner,function = "pwm1";

allwinner,muxsel = <0x00000007>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

linux,phandle = <0x0000003f>;

phandle = <0x0000003f>;

};

sdc0@1 {

allwinner,pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x00000007>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000001>;

linux,phandle = <0x0000002e>;

phandle = <0x0000002e>;

};

sdc1@1 {

allwinner,pins = "PC0", "PC1", "PC2";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x00000007>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000001>;

linux,phandle = <0x00000033>;

phandle = <0x00000033>;

};

daudio0@0 {

allwinner,function = "iis0";

allwinner,muxsel = <0x00000004>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

linux,phandle = <0x00000046>;

phandle = <0x00000046>;

};

daudio0_sleep@0 {

allwinner,function = "io_disabled";

allwinner,muxsel = <0x00000007>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

linux,phandle = <0x00000047>;

phandle = <0x00000047>;

};

daudio0@1 {

allwinner,function = "iis0";

allwinner,muxsel = <0x00000002>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

};

spdif@0 {

allwinner,pins = "PD17";

allwinner,function = "spdif0";

allwinner,muxsel = <0x00000003>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

linux,phandle = <0x00000049>;

phandle = <0x00000049>;

};

spdif_sleep@0 {

allwinner,pins = "PD17";

allwinner,function = "io_disabled";

allwinner,muxsel = <0x00000007>;

allwinner,drive = <0x00000001>;

allwinner,pull = <0x00000000>;

linux,phandle = <0x0000004a>;

phandle = <0x0000004a>;

};

card0_boot_para@0 {

linux,phandle = <0x00000051>;

phandle = <0x00000051>;

allwinner,pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5";

allwinner,function = "card0_boot_para";

allwinner,pname = "sdc_d1", "sdc_d0", "sdc_clk", "sdc_cmd", "sdc_d3", "sdc_d2";

allwinner,muxsel = <0x00000002>;

allwinner,pull = <0x00000001>;

allwinner,drive = <0x00000002>;

allwinner,data = <0xffffffff>;

};

card2_boot_para@0 {

linux,phandle = <0x00000052>;

phandle = <0x00000052>;

allwinner,pins = "PC5", "PC6", "PC8", "PC9", "PC10", "PC11", "PC12", "PC13", "PC14", "PC15", "PC16", "PC1";

allwinner,function = "card2_boot_para";

allwinner,pname = "sdc_clk", "sdc_cmd", "sdc_d0", "sdc_d1", "sdc_d2", "sdc_d3", "sdc_d4", "sdc_d5", "sdc_d6", "sdc_d7", "sdc_emmc_rst", "sdc_ds";

allwinner,muxsel = <0x00000003>;

allwinner,pull = <0x00000001>;

allwinner,drive = <0x00000003>;

allwinner,data = <0xffffffff>;

};

card1_boot_para@0 {

linux,phandle = <0x00000053>;

phandle = <0x00000053>;

allwinner,pins = "PC0", "PC1", "PC2";

allwinner,function = "card1_boot_para";

allwinner,pname = "sdc_clk", "sdc_cmd", "sdc_d0";

allwinner,muxsel = <0x00000003>;

allwinner,pull = <0x00000001>;

allwinner,drive = <0x00000003>;

allwinner,data = <0xffffffff>;

};

twi_para@0 {

linux,phandle = <0x00000054>;

phandle = <0x00000054>;

allwinner,pins = "PD12", "PD0";

allwinner,function = "twi_para";

allwinner,pname = "twi_scl", "twi_sda";

allwinner,muxsel = <0x00000003>;

allwinner,pull = <0xffffffff>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

uart_para@0 {

linux,phandle = <0x00000055>;

phandle = <0x00000055>;

allwinner,pins = "PA2", "PA3";

allwinner,function = "uart_para";

allwinner,pname = "uart_debug_tx", "uart_debug_rx";

allwinner,muxsel = <0x00000005>;

allwinner,pull = <0x00000001>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

jtag_para@0 {

linux,phandle = <0x00000056>;

phandle = <0x00000056>;

allwinner,pins = "PH9", "PH10", "PH11", "PH12";

allwinner,function = "jtag_para";

allwinner,pname = "jtag_ms", "jtag_ck", "jtag_do", "jtag_di";

allwinner,muxsel = <0x00000003>;

allwinner,pull = <0xffffffff>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

twi0@0 {

linux,phandle = <0x00000057>;

phandle = <0x00000057>;

allwinner,pins = "PD12", "PD0";

allwinner,function = "twi0";

allwinner,pname = "twi0_scl", "twi0_sda";

allwinner,muxsel = <0x00000003>;

allwinner,pull = <0xffffffff>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

twi1@0 {

linux,phandle = <0x00000058>;

phandle = <0x00000058>;

allwinner,pins = "PB0", "PB1";

allwinner,function = "twi1";

allwinner,pname = "twi1_scl", "twi1_sda";

allwinner,muxsel = <0x00000002>;

allwinner,pull = <0xffffffff>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

twi2@0 {

linux,phandle = <0x00000059>;

phandle = <0x00000059>;

allwinner,pins = "PD15", "PD16";

allwinner,function = "twi2";

allwinner,pname = "twi2_scl", "twi2_sda";

allwinner,muxsel = <0x00000004>;

allwinner,pull = <0xffffffff>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

uart0@0 {

linux,phandle = <0x0000005a>;

phandle = <0x0000005a>;

allwinner,pins = "PF2", "PF4";

allwinner,function = "uart0";

allwinner,pname = "uart0_tx", "uart0_rx";

allwinner,muxsel = <0x00000003>;

allwinner,pull = <0x00000001>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

uart1@0 {

linux,phandle = <0x0000005b>;

phandle = <0x0000005b>;

allwinner,pins = "PA2", "PA3";

allwinner,function = "uart1";

allwinner,pname = "uart1_tx", "uart1_rx";

allwinner,muxsel = <0x00000005>;

allwinner,pull = <0x00000001>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

spi0@0 {

linux,phandle = <0x0000005c>;

phandle = <0x0000005c>;

allwinner,pins = "PC1";

allwinner,function = "spi0";

allwinner,pname = "spi0_cs0";

allwinner,muxsel = <0x00000002>;

allwinner,pull = <0x00000001>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

spi0@1 {

linux,phandle = <0x0000005d>;

phandle = <0x0000005d>;

allwinner,pins = "PC0", "PC3", "PC2";

allwinner,function = "spi0";

allwinner,pname = "spi0_sclk", "spi0_mosi", "spi0_miso";

allwinner,muxsel = <0x00000002>;

allwinner,pull = <0xffffffff>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

spi1@0 {

linux,phandle = <0x0000005e>;

phandle = <0x0000005e>;

allwinner,pins = "PE7";

allwinner,function = "spi1";

allwinner,pname = "spi1_cs0";

allwinner,muxsel = <0x00000004>;

allwinner,pull = <0x00000001>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

spi1@1 {

linux,phandle = <0x0000005f>;

phandle = <0x0000005f>;

allwinner,pins = "PE9", "PE8", "PE10";

allwinner,function = "spi1";

allwinner,pname = "spi1_sclk", "spi1_mosi", "spi1_miso";

allwinner,muxsel = <0x00000004>;

allwinner,pull = <0xffffffff>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

nand0@0 {

linux,phandle = <0x00000060>;

phandle = <0x00000060>;

allwinner,pins = "PC0", "PC1", "PC2", "PC4", "PC6", "PC7", "PC8", "PC9", "PC10", "PC11", "PC12", "PC13", "PC14";

allwinner,function = "nand0";

allwinner,pname = "nand0_we", "nand0_ale", "nand0_cle", "nand0_nre", "nand0_d0", "nand0_d1", "nand0_d2", "nand0_d3", "nand0_d4", "nand0_d5", "nand0_d6", "nand0_d7", "nand0_ndqs";

allwinner,muxsel = <0x00000002>;

allwinner,pull = <0x00000000>;

allwinner,drive = <0x00000001>;

allwinner,data = <0xffffffff>;

};

nand0@1 {

linux,phandle = <0x00000061>;

phandle = <0x00000061>;

allwinner,pins = "PC3", "PC5";

allwinner,function = "nand0";

allwinner,pname = "nand0_ce0", "nand0_rb0";

allwinner,muxsel = <0x00000002>;

allwinner,pull = <0x00000001>;

allwinner,drive = <0x00000001>;

allwinner,data = <0xffffffff>;

};

lcd0@0 {

linux,phandle = <0x00000062>;

phandle = <0x00000062>;

allwinner,pins = "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD8", "PD9", "PD10", "PD11", "PD13", "PD14", "PD15", "PD16", "PD17";

allwinner,function = "lcd0";

allwinner,pname = "lcdd3", "lcdd4", "lcdd5", "lcdd6", "lcdd7", "lcdd10", "lcdd11", "lcdd12", "lcdd13", "lcdd14", "lcdd15", "lcdd19", "lcdd20", "lcdd21", "lcdd22", "lcdd23";

allwinner,muxsel = <0x00000002>;

allwinner,pull = <0x00000000>;

allwinner,drive = <0xffffffff>;

allwinner,data = <0xffffffff>;

};

lcd0@1 {

linux,phandle = <0x00000063>;

phandle = <0x00000063>;

allwinner,pins = "PD18", "PD19", "PD20", "PD21";

allwinner,function = "lcd0";

allwinner,pname = "lcdclk", "lcdde", "lcdhsync", "lcdvsync";

allwinner,muxsel = <0x00000002>;

allwinner,pull = <0x00000000>;

allwinner,drive = <0x00000003>;

allwinner,data = <0xffffffff>;

};

sdc0@0 {

linux,phandle = <0x00000064>;

phandle = <0x00000064>;

allwinner,pins = "PF0", "PF1", "PF2", "PF3", "PF4", "PF5";

allwinner,function = "sdc0";

allwinner,pname = "sdc0_d1", "sdc0_d0", "sdc0_clk", "sdc0_cmd", "sdc0_d3", "sdc0_d2";

allwinner,muxsel = <0x00000002>;

allwinner,pull = <0x00000001>;

allwinner,drive = <0x00000003>;

allwinner,data = <0xffffffff>;

};

sdc1@0 {

linux,phandle = <0x00000065>;

phandle = <0x00000065>;

allwinner,pins = "PC0", "PC1", "PC2";

allwinner,function = "sdc1";

allwinner,pname = "sdc1_clk", "sdc1_cmd", "sdc1_d0";

allwinner,muxsel = <0x00000003>;

allwinner,pull = <0x00000001>;

allwinner,drive = <0x00000002>;

allwinner,data = <0xffffffff>;

};

Vdevice@0 {

linux,phandle = <0x00000066>;

phandle = <0x00000066>;

allwinner,pins = "PC0", "PC1";

allwinner,function = "Vdevice";

allwinner,pname = "Vdevice_0", "Vdevice_1";

allwinner,muxsel = <0x00000004>;

allwinner,pull = <0x00000001>;

allwinner,drive = <0x00000002>;

allwinner,data = <0xffffffff>;

};

};

dma-controller@01c02000 {

compatible = "allwinner,sun3i-dma";

reg = <0x00000000 0x01c02000 0x00000000 0x00001000>;

interrupts = <0x00000012>;

clocks = <0x00000006>;

#dma-cells = <0x00000002>;

linux,phandle = <0x00000025>;

phandle = <0x00000025>;

};

timer@1c20c00 {

compatible = "allwinner,sunxi-timer";

device_type = "timer";

reg = <0x00000000 0x01c20c00 0x00000000 0x00000090>;

interrupts = <0x0000000d>;

clock-frequency = <0x016e3600>;

timer-prescale = <0x00000010>;

};

ir@01c22c00 {

compatible = "allwinner,ir";

reg = <0x00000000 0x01c22c00 0x00000000 0x00000400>;

interrupts = <0x00000006>;

pinctrl-names = "default";

pinctrl-0 = <0x00000007>;

clocks = <0x00000008 0x00000009>;

status = "okay";

};

ve@01c0e000 {

compatible = "allwinner,sunxi-cedar-ve";

reg = <0x00000000 0x01c0e000 0x00000000 0x00001000 0x00000000 0x01c00000 0x00000000 0x00003000 0x00000000 0x01c20000 0x00000000 0x00000800>;

interrupts = <0x00000022>;

clocks = <0x0000000a 0x0000000b>;

};

uart@01c25000 {

compatible = "allwinner,sun3i-uart";

device_type = "uart0";

reg = <0x00000000 0x01c25000 0x00000000 0x00000400>;

interrupts = <0x00000001>;

clocks = <0x0000000c>;

pinctrl-names = "default", "sleep";

pinctrl-1 = <0x0000000e>;

uart0_port = <0x00000000>;

uart0_type = <0x00000002>;

status = "disabled";

pinctrl-0 = <0x0000005a>;

};

uart@01c25400 {

compatible = "allwinner,sun3i-uart";

device_type = "uart1";

reg = <0x00000000 0x01c25400 0x00000000 0x00000400>;

interrupts = <0x00000002>;

clocks = <0x0000000f>;

pinctrl-names = "default", "sleep";

pinctrl-1 = <0x00000011>;

uart1_port = <0x00000001>;

uart1_type = <0x00000002>;

status = "okay";

pinctrl-0 = <0x0000005b>;

};

uart@01c25800 {

compatible = "allwinner,sun3i-uart";

device_type = "uart2";

reg = <0x00000000 0x01c25800 0x00000000 0x00000400>;

interrupts = <0x00000003>;

clocks = <0x00000012>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x00000013>;

pinctrl-1 = <0x00000014>;

uart2_port = <0x00000002>;

uart2_type = <0x00000004>;

status = "disabled";

};

twi@0x01c27000 {

#address-cells = <0x00000001>;

#size-cells = <0x00000000>;

compatible = "allwinner,sun3i-twi";

device_type = "twi0";

reg = <0x00000000 0x01c27000 0x00000000 0x00000400>;

interrupts = <0x00000007>;

clocks = <0x00000015>;

clock-frequency = <0x000186a0>;

pinctrl-names = "default", "sleep";

pinctrl-1 = <0x00000017>;

status = "okay";

pinctrl-0 = <0x00000057>;

io_expand@0x38 {

compatible = "nxp,pcf8574a";

i2c-max-frequency = <0x000186a0>;

reg = <0x00000038>;

device_type = "io_expand";

};

touchscreen0@0x4A {

compatible = "atmel,mxt336t";

reg = <0x0000004a>;

atmel,suspend_mode = <0x00000000>;

};

touchscreen1@0x48 {

compatible = "ctp_icn85xx";

reg = <0x00000048>;

device_type = "touchscreen1";

};

rtc@0x51 {

compatible = "nxp,pcf8563";

i2c-max-frequency = <0x000186a0>;

reg = <0x00000051>;

};

sensor_gc0308@0x42 {

compatible = "allwinner,sensor_gc0308";

i2c-max-frequency = <0x000186a0>;

reg = <0x00000042>;

status = "okay";

};

};

twi@0x01c27400 {

#address-cells = <0x00000001>;

#size-cells = <0x00000000>;

compatible = "allwinner,sun3i-twi";

device_type = "twi1";

reg = <0x00000000 0x01c27400 0x00000000 0x00000400>;

interrupts = <0x00000008>;

clocks = <0x00000018>;

clock-frequency = <0x00030d40>;

pinctrl-names = "default", "sleep";

pinctrl-1 = <0x0000001a>;

status = "disabled";

pinctrl-0 = <0x00000058>;

};

twi@0x01c27800 {

#address-cells = <0x00000001>;

#size-cells = <0x00000000>;

compatible = "allwinner,sun3i-twi";

device_type = "twi2";

reg = <0x00000000 0x01c27800 0x00000000 0x00000400>;

interrupts = <0x00000009>;

clocks = <0x0000001b>;

clock-frequency = <0x000186a0>;

pinctrl-names = "default", "sleep";

pinctrl-1 = <0x0000001d>;

status = "disabled";

pinctrl-0 = <0x00000059>;

};

spi@01c05000 {

#address-cells = <0x00000001>;

#size-cells = <0x00000000>;

compatible = "allwinner,sun8i-spi";

device_type = "spi0";

reg = <0x00000000 0x01c05000 0x00000000 0x00001000>;

interrupts = <0x0000000a>;

clocks = <0x0000001e 0x0000001f>;

clock-frequency = <0x05f5e100>;

pinctrl-names = "default", "sleep";

pinctrl-1 = <0x00000022 0x00000023>;

spi0_cs_number = <0x00000001>;

spi0_cs_bitmap = <0x00000001>;

sd-spi-sel = <0x00000024 0x00000000 0x00000001 0x00000001 0x00000001 0x00000000 0x00000000>;

sd-spi-act = <0x00000001>;

dmas = <0x00000025 0x00000000 0x00000004 0x00000025 0x00000000 0x00000004>;

dma-names = "rx", "tx";

status = "okay";

pinctrl-0 = <0x0000005c 0x0000005d>;

nor_flash@0 {

#address-cells = <0x00000001>;

#size-cells = <0x00000001>;

compatible = "st,m25p64";

spi-max-frequency = <0x02faf080>;

reg = <0x00000000>;

};

};

spinand@01c05000 {

compatible = "allwinner,sunxi-spinand";

device_type = "spinand";

reg = <0x00000000 0x01c05000 0x00000000 0x00001000>;

interrupts = <0x0000000a>;

clocks = <0x0000001e 0x0000001f>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x0000005c 0x0000005d>;

pinctrl-1 = <0x00000022 0x00000023>;

nand0_regulator1 = "vcc-nand";

nand0_regulator2 = "none";

nand0_cache_level = <0x55aaaa55>;

nand0_flush_cache_num = <0x55aaaa55>;

nand0_capacity_level = <0x55aaaa55>;

nand0_id_number_ctl = <0x55aaaa55>;

nand0_print_level = <0x55aaaa55>;

nand0_p0 = <0x55aaaa55>;

nand0_p1 = <0x55aaaa55>;

nand0_p2 = <0x55aaaa55>;

nand0_p3 = <0x55aaaa55>;

status = "okay";

};

spi@01c06000 {

#address-cells = <0x00000001>;

#size-cells = <0x00000000>;

compatible = "allwinner,sun8i-spi";

device_type = "spi1";

reg = <0x00000000 0x01c06000 0x00000000 0x00001000>;

interrupts = <0x0000000b>;

clocks = <0x0000001e 0x00000026>;

clock-frequency = <0x05f5e100>;

pinctrl-names = "default", "sleep";

pinctrl-1 = <0x00000029>;

spi1_cs_number = <0x00000001>;

spi1_cs_bitmap = <0x00000001>;

status = "okay";

pinctrl-0 = <0x0000005e 0x0000005f>;

ssd2828@0 {

compatible = "ss,ssd2828";

spi-max-frequency = <0x017d7840>;

gpios = <0x00000024 0x00000000 0x00000001 0x00000000 0x00000001 0x00000001 0x00000001>;

reg = <0x00000000>;

};

};

sdmmc@01c0f000 {

compatible = "allwinner,sun3iw1p1-sdmmc0";

device_type = "sdc0";

reg = <0x00000000 0x01c0f000 0x00000000 0x00001000>;

interrupts = <0x00000017>;

clocks = <0x00000008 0x00000004 0x0000002a 0x0000002b 0x0000002c>;

clock-names = "osc24m", "pll_periph", "mmc", "ahb", "rst";

pinctrl-names = "default", "sleep";

pinctrl-1 = <0x0000002e>;

max-frequency = <0x02faf080>;

bus-width = <0x00000004>;

cap-sdio-irq;

keep-power-in-suspend;

ignore-pm-notify;

status = "okay";

sdc0_buswidth = <0x00000004>;

pinctrl-0 = <0x00000064>;

sdc0_det = <0x00000024 0x00000000 0x00000001 0x00000000 0x00000001 0x00000003 0xffffffff>;

sdc0_use_wp = <0x00000000>;

sdc0_wp;

sdc0_isio = <0x00000000>;

sdc0_regulator = "none";

};

sdmmc@01c10000 {

compatible = "allwinner,sun3iw1p1-sdmmc1";

device_type = "sdc1";

reg = <0x00000000 0x01c10000 0x00000000 0x00001000>;

interrupts = <0x00000018>;

clocks = <0x00000008 0x00000004 0x0000002f 0x00000030 0x00000031>;

clock-names = "osc24m", "pll_periph", "mmc", "ahb", "rst";

pinctrl-names = "default", "sleep";

pinctrl-1 = <0x00000033>;

max-frequency = <0x02faf080>;

bus-width = <0x00000001>;

no-sdio;

no-sd;

non-removable;

cap-sdio-irq;

keep-power-in-suspend;

ignore-pm-notify;

sunxi-dly-52M-ddr4 = <0x00000001 0x00000000 0x00000000 0x00000000 0x00000002>;

sunxi-dly-104M = <0x00000001 0x00000000 0x00000000 0x00000000 0x00000001>;

sunxi-dly-208M = <0x00000001 0x00000000 0x00000000 0x00000000 0x00000001>;

status = "disabled";

sdc1_detmode = <0x00000004>;

sdc1_buswidth = <0x00000001>;

pinctrl-0 = <0x00000065>;

sdc1_det;

sdc1_use_wp = <0x00000000>;

sdc1_wp;

sdc1_isio = <0x00000001>;

sdc1_regulator = "none";

};

disp@0x01e00000 {

compatible = "allwinner,sunxi-disp";

reg = <0x00000000 0x01e00000 0x00000000 0x00020000 0x00000000 0x01c0c000 0x00000000 0x00001000 0x00000000 0x01e70000 0x00000000 0x00010000>;

interrupts = <0x0000001d 0x0000001f 0x0000001e 0x00000021>;

clocks = <0x00000034 0x00000035 0x00000036 0x00000037 0x00000038>;

status = "okay";

device_type = "disp";

disp_init_enable = <0x00000001>;

disp_mode = <0x00000000>;

screen0_output_type = <0x00000001>;

screen0_output_mode = <0x00000004>;

screen1_output_type = <0x00000001>;

screen1_output_mode = <0x00000004>;

fb0_framebuffer_num = <0x00000002>;

fb0_pixel_sequence = <0x00000000>;

fb0_scaler_mode_enable = <0x00000000>;

fb0_format = <0x00000000>;

fb0_width = <0x00000000>;

fb0_height = <0x00000000>;

fb1_framebuffer_num = <0x00000000>;

fb1_pixel_sequence = <0x00000000>;

fb1_scaler_mode_enable = <0x00000000>;

fb1_format = <0x00000000>;

fb1_width = <0x00000000>;

fb1_height = <0x00000000>;

lcd0_backlight = <0x00000032>;

lcd1_backlight = <0x00000032>;

lcd0_bright = <0x00000032>;

lcd0_contrast = <0x00000032>;

lcd0_saturation = <0x00000039>;

lcd0_hue = <0x00000032>;

lcd1_bright = <0x00000032>;

lcd1_contrast = <0x00000032>;

lcd1_saturation = <0x00000039>;

lcd1_hue = <0x00000032>;

};

tvd0@01c0b000 {

compatible = "allwinner,sunxi-tvd";

reg = <0x00000000 0x01c0b000 0x00000000 0x00001000>;

interrupts = <0x0000001b>;

clocks = <0x00000039>;

tvd_used = <0x00000001>;

tvd_if = <0x00000000>;

status = "okay";

};

lcd0@01c0c000 {

compatible = "allwinner,sunxi-lcd0";

pinctrl-names = "active", "sleep";

status = "okay";

device_type = "lcd0";

lcd_used = <0x00000001>;

lcd_driver_name = "ili6122_800x480";

lcd_if = <0x00000000>;

lcd_x = <0x00000320>;

lcd_y = <0x00000500>;

lcd_width = <0x00000087>;

lcd_height = <0x000000d8>;

lcd_dclk_freq = <0x0000003e>;

lcd_pwm_used = <0x00000001>;

lcd_pwm_ch = <0x00000000>;

lcd_pwm_freq = <0x0000c350>;

lcd_pwm_pol = <0x00000001>;

lcd_hbp = <0x00000046>;

lcd_ht = <0x000004c4>;

lcd_hspw = <0x00000014>;

lcd_vbp = <0x00000016>;

lcd_vt = <0x00000523>;

lcd_vspw = <0x00000006>;

lcd_hv_if = <0x00000000>;

lcd_hv_smode = <0x00000000>;

lcd_hv_s888_if = <0x00000000>;

lcd_hv_syuv_if = <0x00000000>;

lcd_hv_vspw = <0x00000006>;

lcd_hv_hspw = <0x00000014>;

lcd_hv_sync_polarity = <0x00000001>;

lcd_deu_mode = <0x00000001>;

lcd_lvds_if = <0x00000000>;

lcd_lvds_colordepth = <0x00000001>;

lcd_lvds_mode = <0x00000000>;

lcd_lvds_ch = <0x00000000>;

lcd_lvds_bitwidth = <0x00000000>;

lcd_lvds_io_cross = <0x00000000>;

lcd_cpu_if = <0x00000000>;

lcd_frm = <0x00000001>;

lcd_rb_swap = <0x00000001>;

lcd_io_phase = <0x00000000>;

lcd_gamma_en = <0x00000000>;

lcd_bright_curve_en = <0x00000000>;

lcd_cmap_en = <0x00000000>;

deu_mode = <0x00000000>;

lcdgamma4iep = <0x00000016>;

lcd_io_cfg0 = <0x00000000>;

smart_color = <0x0000005a>;

lcd_gpio_0 = <0x00000024 0x00000004 0x00000005 0x00000001 0x00000000 0xffffffff 0x00000000>;

pinctrl-0 = <0x00000062 0x00000063>;

};

pwm@01c21000 {

compatible = "allwinner,sunxi-pwm";

reg = <0x00000000 0x01c21000 0x00000000 0x00000008>;

pwm-number = <0x00000002>;

pwm-base = <0x00000000>;

pwms = <0x0000003a 0x0000003b>;

};

pwm0@01c21000 {

compatible = "allwinner,sunxi-pwm0";

pinctrl-names = "active", "sleep";

pinctrl-0 = <0x0000003c>;

pinctrl-1 = <0x0000003d>;

reg_base = <0x01c21000>;

reg_busy_offset = <0x00000000>;

reg_busy_shift = <0x0000001c>;

reg_enable_offset = <0x00000000>;

reg_enable_shift = <0x00000004>;

reg_clk_gating_offset = <0x00000000>;

reg_clk_gating_shift = <0x00000006>;

reg_bypass_offset = <0x00000000>;

reg_bypass_shift = <0x00000009>;

reg_pulse_start_offset = <0x00000000>;

reg_pulse_start_shift = <0x00000008>;

reg_mode_offset = <0x00000000>;

reg_mode_shift = <0x00000007>;

reg_polarity_offset = <0x00000000>;

reg_polarity_shift = <0x00000005>;

reg_period_offset = <0x00000004>;

reg_period_shift = <0x00000010>;

reg_period_width = <0x00000010>;

reg_active_offset = <0x00000004>;

reg_active_shift = <0x00000000>;

reg_active_width = <0x00000010>;

reg_prescal_offset = <0x00000000>;

reg_prescal_shift = <0x00000000>;

reg_prescal_width = <0x00000004>;

linux,phandle = <0x0000003a>;

phandle = <0x0000003a>;

};

pwm1@01c21000 {

compatible = "allwinner,sunxi-pwm1";

pinctrl-names = "active", "sleep";

pinctrl-0 = <0x0000003e>;

pinctrl-1 = <0x0000003f>;

reg_base = <0x01c21000>;

reg_busy_offset = <0x00000000>;

reg_busy_shift = <0x0000001d>;

reg_enable_offset = <0x00000000>;

reg_enable_shift = <0x00000013>;

reg_clk_gating_offset = <0x00000000>;

reg_clk_gating_shift = <0x00000015>;

reg_bypass_offset = <0x00000000>;

reg_bypass_shift = <0x00000018>;

reg_pulse_start_offset = <0x00000000>;

reg_pulse_start_shift = <0x00000017>;

reg_mode_offset = <0x00000000>;

reg_mode_shift = <0x00000016>;

reg_polarity_offset = <0x00000000>;

reg_polarity_shift = <0x00000014>;

reg_period_offset = <0x00000008>;

reg_period_shift = <0x00000010>;

reg_period_width = <0x00000010>;

reg_active_offset = <0x00000008>;

reg_active_shift = <0x00000000>;

reg_active_width = <0x00000010>;

reg_prescal_offset = <0x00000000>;

reg_prescal_shift = <0x0000000f>;

reg_prescal_width = <0x00000004>;

linux,phandle = <0x0000003b>;

phandle = <0x0000003b>;

};

deinterlace@01e70000 {

compatible = "allwinner,sunxi-deinterlace";

reg = <0x00000000 0x01e70000 0x00000000 0x00000080>;

interrupts = <0x00000021>;

clocks = <0x00000038 0x00000003>;

status = "okay";

};

csi_res@0x01cb0000 {

compatible = "allwinner,sunxi-csi";

reg = <0x00000000 0x01cb0000 0x00000000 0x00001000>;

clocks = <0x00000040 0x00000003 0x00000008>;

clocks-index = <0x00000000 0x00000001 0x00000002>;

status = "okay";

};

vfe@0 {

device_type = "csi0";

compatible = "allwinner,sunxi-vfe";

interrupts = <0x00000020>;

pinctrl-names = "default", "sleep";

pinctrl-0 = <0x00000041>;

pinctrl-1 = <0x00000042>;

csi_sel = <0x00000000>;

csi0_sensor_list = <0x00000000>;

csi0_mck = <0x00000024 0x00000004 0x0000000b 0x00000002 0x00000001 0x00000003 0x00000000>;

status = "okay";

dev@1 {

csi0_dev0_mname = "gc0308";

csi0_dev0_twi_addr = <0x00000042>;

csi0_dev0_twi_id = <0x00000000>;

csi0_dev0_pos = "rear";

csi0_dev0_isp_used = <0x00000000>;

csi0_dev0_fmt = <0x00000000>;

csi0_dev0_stby_mode = <0x00000000>;

csi0_dev0_vflip = <0x00000000>;

csi0_dev0_hflip = <0x00000000>;

csi0_dev0_iovdd = <0x00000000>;

csi0_dev0_iovdd_vol = <0x00000000>;

csi0_dev0_avdd = <0x00000000>;

csi0_dev0_avdd_vol = <0x00000000>;

csi0_dev0_dvdd = <0x00000000>;

csi0_dev0_dvdd_vol = <0x00000000>;

csi0_dev0_afvdd = <0x00000000>;

csi0_dev0_afvdd_vol = <0x00000000>;

csi0_dev0_power_en;

csi0_dev0_reset = <0x000007fc>;

csi0_dev0_pwdn;

csi0_dev0_flash_en;

csi0_dev0_flash_mode;

csi0_dev0_af_pwdn;

csi0_dev0_act_used = <0x00000000>;

csi0_dev0_act_name = <0x00000000>;

csi0_dev0_act_slave = <0x00000000>;

status = "okay";

};

};

usbc0@0 {

device_type = "usbc0";

compatible = "allwinner,sunxi-otg-manager";

usb_port_type = <0x00000000>;

usb_detect_type = <0x00000001>;

usb_detect_mode = <0x00000000>;

usb_drv_vbus_gpio = <0x000007ff>;

usb_host_init_state = <0x00000000>;

usb_regulator_io = "nocare";

usb_wakeup_suspend = <0x00000000>;

usb_luns = <0x00000003>;

usb_serial_unique = <0x00000000>;

usb_serial_number = "20080411";

rndis_wceis = <0x00000001>;

status = "okay";

usb_id_gpio;

usb_det_vbus_gpio;

usb_board_sel = <0x00000001>;

usb_regulator_vol = <0x00000000>;

};

udc-controller@0x01c13000 {

compatible = "allwinner,sunxi-udc";

reg = <0x00000000 0x01c13000 0x00000000 0x00001000 0x00000000 0x01c00000 0x00000000 0x00000100>;

interrupts = <0x0000001a>;

clocks = <0x00000043 0x00000044>;

status = "okay";

};

otghci0-controller@0x01c13000 {

compatible = "allwinner,sunxi-hcd0";

reg = <0x00000000 0x01c13000 0x00000000 0x00001000 0x00000000 0x01c00000 0x00000000 0x00000100>;

interrupts = <0x0000001a>;