#1 Re: 全志 SOC » 怎么理解设备树文件 » 2022-03-03 10:38:06

#2 Re: 全志 SOC » 小白新人求教uboot中怎么开启logo显示 » 2022-01-26 16:39:32

#3 Re: 全志 SOC » No Spidev device » 2022-01-26 16:33:47

#4 Re: 全志 SOC » [V3x] u-boot 支持 » 2021-08-06 20:09:42

比较了以下 ddr3 和 ddr2 初始化:

https://github.com/u-boot/u-boot/blob/master/arch/arm/mach-sunxi/dram_timings/ddr3_1333.c

#include <common.h>

#include <asm/arch/dram.h>

#include <asm/arch/cpu.h>

void mctl_set_timing_params(uint16_t socid, struct dram_para *para)

{

struct sunxi_mctl_ctl_reg * const mctl_ctl =

(struct sunxi_mctl_ctl_reg *)SUNXI_DRAM_CTL0_BASE;

u8 tccd = 2;

u8 tfaw = ns_to_t(50);

u8 trrd = max(ns_to_t(10), 4);

u8 trcd = ns_to_t(15);

u8 trc = ns_to_t(53);

u8 txp = max(ns_to_t(8), 3);

u8 twtr = max(ns_to_t(8), 4);

u8 trtp = max(ns_to_t(8), 4);

u8 twr = max(ns_to_t(15), 3);

u8 trp = ns_to_t(15);

u8 tras = ns_to_t(38);

u16 trefi = ns_to_t(7800) / 32;

u16 trfc = ns_to_t(350);

u8 tmrw = 0;

u8 tmrd = 4;

u8 tmod = 12;

u8 tcke = 3;

u8 tcksrx = 5;

u8 tcksre = 5;

u8 tckesr = 4;

u8 trasmax = 24;

u8 tcl = 6; /* CL 12 */

u8 tcwl = 4; /* CWL 8 */

u8 t_rdata_en = 4;

u8 wr_latency = 2;

u32 tdinit0 = (500 * CONFIG_DRAM_CLK) + 1; /* 500us */

u32 tdinit1 = (360 * CONFIG_DRAM_CLK) / 1000 + 1; /* 360ns */

u32 tdinit2 = (200 * CONFIG_DRAM_CLK) + 1; /* 200us */

u32 tdinit3 = (1 * CONFIG_DRAM_CLK) + 1; /* 1us */

u8 twtp = tcwl + 2 + twr; /* WL + BL / 2 + tWR */

u8 twr2rd = tcwl + 2 + twtr; /* WL + BL / 2 + tWTR */

u8 trd2wr = tcl + 2 + 1 - tcwl; /* RL + BL / 2 + 2 - WL */

/* set mode register */

writel(0x1c70, &mctl_ctl->mr[0]); /* CL=11, WR=12 */

writel(0x40, &mctl_ctl->mr[1]);

writel(0x18, &mctl_ctl->mr[2]); /* CWL=8 */

writel(0x0, &mctl_ctl->mr[3]);

if (socid == SOCID_R40)

writel(0x3, &mctl_ctl->lp3mr11); /* odt_en[7:4] */

/* set DRAM timing */

writel(DRAMTMG0_TWTP(twtp) | DRAMTMG0_TFAW(tfaw) |

DRAMTMG0_TRAS_MAX(trasmax) | DRAMTMG0_TRAS(tras),

&mctl_ctl->dramtmg[0]);

writel(DRAMTMG1_TXP(txp) | DRAMTMG1_TRTP(trtp) | DRAMTMG1_TRC(trc),

&mctl_ctl->dramtmg[1]);

writel(DRAMTMG2_TCWL(tcwl) | DRAMTMG2_TCL(tcl) |

DRAMTMG2_TRD2WR(trd2wr) | DRAMTMG2_TWR2RD(twr2rd),

&mctl_ctl->dramtmg[2]);

writel(DRAMTMG3_TMRW(tmrw) | DRAMTMG3_TMRD(tmrd) | DRAMTMG3_TMOD(tmod),

&mctl_ctl->dramtmg[3]);

writel(DRAMTMG4_TRCD(trcd) | DRAMTMG4_TCCD(tccd) | DRAMTMG4_TRRD(trrd) |

DRAMTMG4_TRP(trp), &mctl_ctl->dramtmg[4]);

writel(DRAMTMG5_TCKSRX(tcksrx) | DRAMTMG5_TCKSRE(tcksre) |

DRAMTMG5_TCKESR(tckesr) | DRAMTMG5_TCKE(tcke),

&mctl_ctl->dramtmg[5]);

/* set two rank timing */

clrsetbits_le32(&mctl_ctl->dramtmg[8], (0xff << 8) | (0xff << 0),

((socid == SOCID_H5 ? 0x33 : 0x66) << 8) | (0x10 << 0));

/* set PHY interface timing, write latency and read latency configure */

writel((0x2 << 24) | (t_rdata_en << 16) | (0x1 << 8) |

(wr_latency << 0), &mctl_ctl->pitmg[0]);

/* set PHY timing, PTR0-2 use default */

writel(PTR3_TDINIT0(tdinit0) | PTR3_TDINIT1(tdinit1), &mctl_ctl->ptr[3]);

writel(PTR4_TDINIT2(tdinit2) | PTR4_TDINIT3(tdinit3), &mctl_ctl->ptr[4]);

/* set refresh timing */

writel(RFSHTMG_TREFI(trefi) | RFSHTMG_TRFC(trfc), &mctl_ctl->rfshtmg);

}https://github.com/u-boot/u-boot/blob/master/arch/arm/mach-sunxi/dram_timings/ddr2_v3s.c

#include <common.h>

#include <asm/arch/dram.h>

#include <asm/arch/cpu.h>

void mctl_set_timing_params(uint16_t socid, struct dram_para *para)

{

struct sunxi_mctl_ctl_reg * const mctl_ctl =

(struct sunxi_mctl_ctl_reg *)SUNXI_DRAM_CTL0_BASE;

u8 tccd = 1;

u8 tfaw = ns_to_t(50);

u8 trrd = max(ns_to_t(10), 2);

u8 trcd = ns_to_t(20);

u8 trc = ns_to_t(65);

u8 txp = 2;

u8 twtr = max(ns_to_t(8), 2);

u8 trtp = max(ns_to_t(8), 2);

u8 twr = max(ns_to_t(15), 3);

u8 trp = ns_to_t(15);

u8 tras = ns_to_t(45);

u16 trefi = ns_to_t(7800) / 32;

u16 trfc = ns_to_t(328);

u8 tmrw = 0;

u8 tmrd = 2;

u8 tmod = 12;

u8 tcke = 3;

u8 tcksrx = 5;

u8 tcksre = 5;

u8 tckesr = 4;

u8 trasmax = 27;

u8 tcl = 3; /* CL 6 */

u8 tcwl = 3; /* CWL 6 */

u8 t_rdata_en = 1;

u8 wr_latency = 1;

u32 tdinit0 = (400 * CONFIG_DRAM_CLK) + 1; /* 400us */

u32 tdinit1 = (500 * CONFIG_DRAM_CLK) / 1000 + 1; /* 500ns */

u32 tdinit2 = (200 * CONFIG_DRAM_CLK) + 1; /* 200us */

u32 tdinit3 = (1 * CONFIG_DRAM_CLK) + 1; /* 1us */

u8 twtp = tcwl + 2 + twr; /* WL + BL / 2 + tWR */

u8 twr2rd = tcwl + 2 + twtr; /* WL + BL / 2 + tWTR */

u8 trd2wr = tcl + 2 + 1 - tcwl; /* RL + BL / 2 + 2 - WL */

/* set mode register */

writel(0x263, &mctl_ctl->mr[0]);

writel(0x4, &mctl_ctl->mr[1]);

writel(0x0, &mctl_ctl->mr[2]);

writel(0x0, &mctl_ctl->mr[3]);

/* set DRAM timing */

writel(DRAMTMG0_TWTP(twtp) | DRAMTMG0_TFAW(tfaw) |

DRAMTMG0_TRAS_MAX(trasmax) | DRAMTMG0_TRAS(tras),

&mctl_ctl->dramtmg[0]);

writel(DRAMTMG1_TXP(txp) | DRAMTMG1_TRTP(trtp) | DRAMTMG1_TRC(trc),

&mctl_ctl->dramtmg[1]);

writel(DRAMTMG2_TCWL(tcwl) | DRAMTMG2_TCL(tcl) |

DRAMTMG2_TRD2WR(trd2wr) | DRAMTMG2_TWR2RD(twr2rd),

&mctl_ctl->dramtmg[2]);

writel(DRAMTMG3_TMRW(tmrw) | DRAMTMG3_TMRD(tmrd) | DRAMTMG3_TMOD(tmod),

&mctl_ctl->dramtmg[3]);

writel(DRAMTMG4_TRCD(trcd) | DRAMTMG4_TCCD(tccd) | DRAMTMG4_TRRD(trrd) |

DRAMTMG4_TRP(trp), &mctl_ctl->dramtmg[4]);

writel(DRAMTMG5_TCKSRX(tcksrx) | DRAMTMG5_TCKSRE(tcksre) |

DRAMTMG5_TCKESR(tckesr) | DRAMTMG5_TCKE(tcke),

&mctl_ctl->dramtmg[5]);

/* set two rank timing */

clrsetbits_le32(&mctl_ctl->dramtmg[8], (0xff << 8) | (0xff << 0),

(0x66 << 8) | (0x10 << 0));

/* set PHY interface timing, write latency and read latency configure */

writel((0x2 << 24) | (t_rdata_en << 16) | (0x1 << 8) |

(wr_latency << 0), &mctl_ctl->pitmg[0]);

/* set PHY timing, PTR0-2 use default */

writel(PTR3_TDINIT0(tdinit0) | PTR3_TDINIT1(tdinit1), &mctl_ctl->ptr[3]);

writel(PTR4_TDINIT2(tdinit2) | PTR4_TDINIT3(tdinit3), &mctl_ctl->ptr[4]);

/* set refresh timing */

writel(RFSHTMG_TREFI(trefi) | RFSHTMG_TRFC(trfc), &mctl_ctl->rfshtmg);

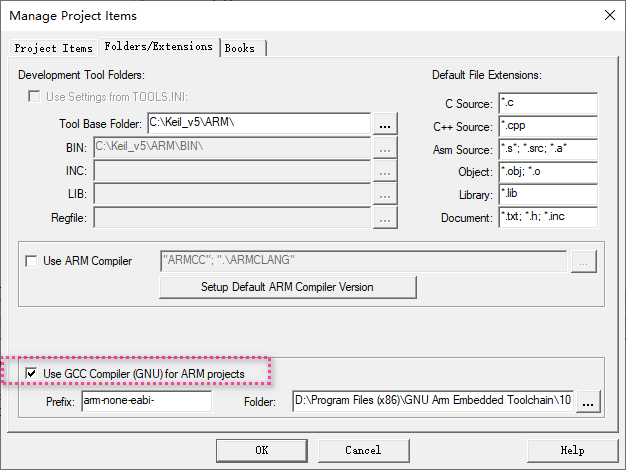

}#5 DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 我朋友做的ARM A7 IDE集成开发环境, 基于 STM32MP157 » 2021-08-06 20:02:48

- 孤星泪

- 回复: 0

IDE(AHL-STM32MP157-20210221.zip)下载地址: http://sumcu.suda.edu.cn/AHLwSTM32MP157/list.htm

STM32MP157快速指南: AHL-STM32MP157快速指南-20210317.pdf

#6 Re: 全志 SOC » 终于搞清楚汇编代码的重定位判断语句是怎么实现的了 » 2021-06-14 20:19:41

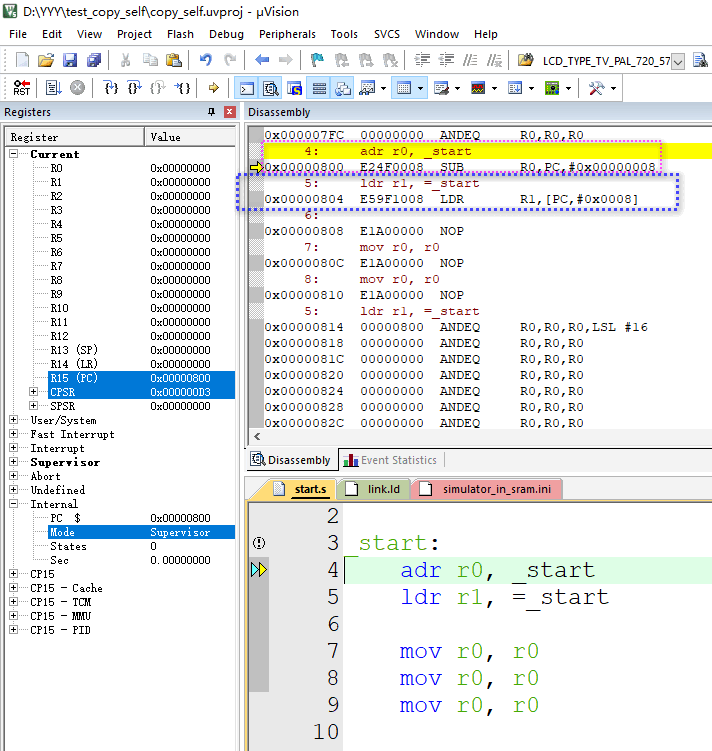

#8 全志 SOC » 终于搞清楚汇编代码的重定位判断语句是怎么实现的了 » 2021-06-14 20:12:29

- 孤星泪

- 回复: 3

比如 xboot 这个代码段重定位 https://github.com/xboot/xboot/blob/master/src/arch/arm32/mach-f1c100s/start.S

_speedup:

nop

/* Copyself to link address */

adr r0, _start

ldr r1, =_start

cmp r0, r1

beq 1f

bl sys_copyself第一条语句 adr r0, _start 编译后是 基于PC指针把 _start 的位置读到 r0 寄存器,

在哪个位置运行, r0 值就是多少. 比如程序在 0x800 运行, 那么 _start 就是 0x800

第二条语句 ldr r1, =_start 是取 _start 的链接地址, 也就是重定位地址.

如果 r1 与 r0 寄存器不相等, 他们肯定要进行重定位 (代码段复制)

为了证明这个问题, 我用MDK反汇编看了一下:

#11 Re: SigmaStar/SSD201/SSD202/SSD212 » 自己做SSD201内核和文件系统的时候,打包了一个USB升级固件的bin文件,一直进不去系统 » 2021-03-29 10:38:40

#12 Re: 全志 SOC » 请问 u-boot的sf 操作flash命令,如何校验flash烧录成功或者失败? » 2021-03-24 17:10:35

https://www.denx.de/wiki/publish/DULG/to-delete/UBootCmdGroupMemory.html

① 都读到内存,用cmp命令比较

② 都读到内存,比较crc值

有道理,感谢版主!

#15 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 长按若干秒强制重启的电路怎么做? » 2021-03-10 11:11:15

这么多元件不如加个两毛钱的单片机靠谱

#19 Re: 全志 SOC » 荔枝派nano Linux系统电阻屏触摸驱动的具体配置文件是怎样的? » 2021-01-21 21:26:24

因为荔枝派nano的ns2009没有接中断引脚, 所以把下面的轮询驱动:

https://github.com/Lichee-Pi/linux/blob/zero-4.13.y/drivers/input/touchscreen/ns2009.c

https://github.com/Lichee-Pi/linux/blob/zero-4.13.y/drivers/input/touchscreen/Makefile

https://github.com/Lichee-Pi/linux/blob/zero-4.13.y/drivers/input/touchscreen/Kconfig

添加到:

https://github.com/Lichee-Pi/linux/tree/nano-5.2-tf/drivers/input/touchscreen

设备树添加 ns2009:

https://github.com/Lichee-Pi/linux/blob/zero-4.13.y/arch/arm/boot/dts/sun8i-v3s-licheepi-zero.dts

&i2c0 {

status = "okay";

ns2009: ns2009@48 {

compatible = "nsiway,ns2009";

reg = <0x48>;

};

};#20 Re: 全志 SOC » 发一个能用win32diskimager 烧 A33/X3 SPI FLASH(MX25/W25)的TF卡固件 » 2021-01-20 08:33:16

本站下载: smallwit_x3_tfcard_20201203155930.tgz

1. 解压缩, 用 win32diskimager 把 smallwit_x3_tfcard_20201203155930.img 烧录到 TF卡

2. 把TF卡插入 小智X3开发板, USB插入OTG线启动, 电脑会出现一个U盘, 不要格式化.

3. 用 win32diskimager 把你的 flash img 烧录到 那个U盘即可。

昨天试了一下小智的X3开发板,确实可以用,一开始很快,后面就很慢了,估计是windows缓冲文件系统,加上flash擦写慢引起。最后自己再手动校验一下。

#21 Re: Qt/MSVC/MINGW/C++/MFC/GTK+/Delphi/BCB » 请问Qt可以在运行中打印调用栈吗?调试中的代码无故调用了很多次,不知道为啥 » 2021-01-19 19:11:21

#22 Qt/MSVC/MINGW/C++/MFC/GTK+/Delphi/BCB » 请问Qt可以在运行中打印调用栈吗?调试中的代码无故调用了很多次,不知道为啥 » 2021-01-19 11:16:06

#24 Re: 全志 SOC » cortex A7 支持 jlink 后台方式查看变量吗? » 2021-01-19 08:46:19

#26 Re: Nuvoton N32905/N32926/NUC972/N9H20/N9H26/N9H30 » 请教各位大侠,挂载时,输入ubiattach /dev/ubi_ctrl -p /dev/mtd0时报错: » 2021-01-13 08:10:47

#27 Re: 全志 SOC » 自制F1C100S核心板 (开源PCB) » 2021-01-13 08:09:23

#28 Re: 全志 SOC » f1c100s成功运行jpeg硬解码demo,但输出还是有问题 » 2021-01-13 08:06:35

F1C200s主线gstreamer使用openmax调用cedar硬解码

http://whycan.com/t_5824.html

(出处:哇酷开发者社区【全志 V3S/F1C100s/X3】)

和这个帖子配合一起看,更有参考意义,感谢楼主!

#29 Re: Nuvoton N32905/N32926/NUC972/N9H20/N9H26/N9H30 » 请教各位大侠,挂载时,输入ubiattach /dev/ubi_ctrl -p /dev/mtd0时报错: » 2021-01-12 22:56:36

#31 Re: 全志 SOC » [慢更]小白探索如何使用V3s播放音乐 » 2021-01-04 22:22:32

#32 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 嵌入式系统显示一个二维码,微信扫码登录,然后可以通过公众号/小程序 同步信息到这个嵌入式系统,请问这样可行吗? » 2021-01-01 18:31:59

#34 Re: 全志 SOC » tiny200 framebuffer配置问题 » 2020-11-29 19:56:35

#37 Re: 全志 SOC » 请问大佬们关于tiny200 r3的小问题!! » 2020-11-26 22:59:45

#39 Re: 全志 SOC » 请问大佬们关于tiny200 r3的小问题!! » 2020-11-26 22:11:23

#40 Re: 全志 SOC » 请问Linux kernel空间和User空间的两个复合 usb gadget 功能怎么玩呢? » 2020-11-26 21:56:27

好奇搜了一下, 还真有这玩意: http://www.trivialfeat.com/home/2016/11/17/media-transfer-protocol-in-a-usb-composite-gadget

/etc/init.d/S99-gadget

#!/bin/sh

CONFIGFS="/sys/kernel/config"

GADGET="$CONFIGFS/usb_gadget"

VID="0x0000"

PID="0x0000"

SERIAL="0123456789"

MANUF="Me"

PRODUCT="Radget"

case "$1" in

start)

echo "Creating the USB gadget"

echo "Loading composite module"

modprobe libcomposite

echo "Mounting ConfigFS"

mount -t configfs none $CONFIGFS

cd $GADGET

if [ $? -ne 0 ]; then

echo "Error setting up configfs"

exit 1;

fi

echo "Creating gadget directory"

mkdir gadget

cd gadget

if [ $? -ne 0 ]; then

echo "Error creating usb gadget in configfs"

exit 1;

fi

echo "Setting Vendor and Product ID's"

echo $VID > idVendor

echo $PID > idProduct

echo "Setting English strings"

mkdir strings/0x409

echo $SERIAL > strings/0x409/serialnumber

echo $MANUF > strings/0x409/manufacturer

echo $PRODUCT > strings/0x409/product

echo "Setting configuration"

mkdir configs/c.1

mkdir configs/c.1/strings/0x409

echo "CDC ACM + MTP + Mass Storage" > configs/c.1/strings/0x409/configuration

echo 120 > configs/c.1/MaxPower

echo "Creating ACM interface"

mkdir functions/acm.GS0

ln -s functions/acm.GS0 configs/c.1

echo "Creating MTP interface"

mkdir functions/mtp.mtp

ln -s functions/mtp.mtp configs/c.1

mkdir /dev/mtp

mount -t functionfs mtp /dev/mtp

echo "Creating Mass Storage interface"

mkdir functions/mass_storage.ms0

echo "/dev/mmcblk0" > functions/mass_storage.ms0/lun.0/file

echo "1" > functions/mass_storage.ms0/lun.0/removable

ln -s functions/mass_storage.ms0 configs/c.1/mass_storage.ms0

echo "Binding USB Device Controller"

echo `ls /sys/class/udc` > UDC

echo "Starting the MTP responder daemon"

mtp-server &

;;

stop)

echo "Stopping the USB gadget"

echo "Killing MTP responder daemon"

killall mtp-server

cd $GADGET/gadget

if [ $? -ne 0 ]; then

echo "Error: no configfs gadget found"

exit 1;

fi

echo "Unbinding USB Device Controller"

echo "" > UDC

echo "Removing Mass Storage interface"

rm configs/c.1/mass_storage.ms0

rmdir functions/mass_storage.ms0

echo "Removing MTP interface"

umount /dev/mtp

rmdir /dev/mtp

rm configs/c.1/mtp.mtp

rmdir functions/mtp.mtp

echo "Removing ACM interface"

rm configs/c.1/acm.GS0

rmdir functions/acm.GS0

echo "Clearing English strings"

rmdir strings/0x409

echo "Cleaning up configuration"

rmdir configs/c.1/strings/0x409

rmdir configs/c.1

echo "Removing gadget directory"

cd $GADGET

rmdir gadget

cd /

echo "Unmounting ConfigFS"

umount $CONFIGFS

;;

esac#42 Re: 全志 SOC » 【分享】V3s Licheepi上控制LED灯的方法 » 2020-11-22 22:26:33

#43 Re: 全志 SOC » F1C600和F1c100s » 2020-11-22 15:35:05

#44 Re: 全志 SOC » S3 I2S问题逐步排查 » 2020-11-22 15:34:12

#48 Re: 全志 SOC » 主线kernel测试----S3平台 » 2020-11-19 22:40:59

请问全志V3s使用荔枝派最新的 linux 4.13-y 分支,如何支持声卡?

http://whycan.com/t_489.html#p1595

(出处:哇酷开发者社区【全志 V3S/F1C100s/X3】)

#49 Re: 全志 SOC » 主线kernel测试----S3平台 » 2020-11-19 19:20:00

#50 Re: 全志 SOC » 移植eMMC驱动遇到一些问题 » 2020-11-19 09:34:31

#51 Re: 全志 SOC » 荔枝派zero v4l2使用问题 » 2020-11-18 18:09:39

#53 Re: 全志 SOC » 关于 V3S 加密 的问题 » 2020-11-17 15:20:36

#54 Re: 全志 SOC » 关于 V3S 加密 的问题 » 2020-11-17 14:26:27

#55 Re: VMWare/Linux/Ubuntu/Fedora/CentOS/U-BOOT » Ubuntu18.04 安装微软 vscode / visual code » 2020-11-15 23:53:19

#56 Re: 全志 SOC » buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *,支持SPI NAND » 2020-11-15 23:52:31

#57 Re: 全志 SOC » fel模式下usb启动问题 » 2020-11-15 23:06:39

#58 Re: 全志 SOC » V3S 新手入门练手 » 2020-11-15 23:04:06

#60 Re: 全志 SOC » buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *,支持SPI NAND » 2020-11-12 14:54:48

#62 Re: 全志 SOC » 全志主线Linux UART串口使用8250驱动程序,但是没有实现RS485控制,有没有哪位打上了patch? » 2020-11-11 21:13:45

楼主, 给你关键字和链接: SER_RS485_RTS_AFTER_SEND SER_RS485_ENABLED

https://elixir.bootlin.com/linux/v5.4.77/source/drivers/tty/serial/imx.c#L445

https://elixir.bootlin.com/linux/v5.4.77/source/drivers/tty/serial/omap-serial.c#L310

全志的uart驱动修改这个文件就可以了:

https://elixir.bootlin.com/linux/v5.4.77/source/drivers/tty/serial/8250/8250_port.c#L1488

https://elixir.bootlin.com/linux/v5.4.77/source/include/linux/serial_8250.h#L101

照猫画虎, 在这里面实现控制即可:

serial8250_start_tx( )

serial8250_stop_tx( )

https://www.cnblogs.com/leisure_chn/p/10381616.html

https://cloud.tencent.com/developer/article/1409518

#63 Re: 全志 SOC » 关于V3s display-engine/display_clocks /mixer0和tcon0 有关lcd时钟配置的一些问题 » 2020-11-11 09:52:41

#64 Re: 全志 SOC » emmc 烧录问题 » 2020-11-10 17:30:19

#65 Re: 全志 SOC » 求助, Matrix Keypad,配置后无设备 » 2020-11-10 16:04:42

#66 Re: 全志 SOC » 求助, Matrix Keypad,配置后无设备 » 2020-11-10 15:38:37

#67 Re: 全志 SOC » 求助, Matrix Keypad,配置后无设备 » 2020-11-10 11:37:34

#68 Re: 全志 SOC » 求助, Matrix Keypad,配置后无设备 » 2020-11-10 11:30:26

dts配置了吗?

最近做个8X11行列键盘,我测试都很好,但是客户说有漏按键的。各位有什么经验介绍一下?

http://whycan.com/t_645.html#p14763

(出处:哇酷开发者社区【Cortex M0/M3/M4/M7】)

#69 Re: 全志 SOC » 链接一个库诡异链接失败,库明明存在 » 2020-11-08 07:39:11

#70 Re: 全志 SOC » 请教荔枝派 ZERO V3S的RGB LED是在哪里控制的? » 2020-11-07 19:23:16

#72 Re: 全志 SOC » licheepi v3s 4.10 内核 有线网口无法驱动 » 2020-11-05 17:02:27

#73 Re: 全志 SOC » 为啥MangoPi V3S PhoenixSuit烧录不成功 » 2020-11-05 10:10:29

#75 Re: 全志 SOC » licheepi v3s 4.10 内核 有线网口无法驱动 » 2020-11-05 10:08:37

#77 Re: 全志 SOC » V3S Lichee Pi ESP8089 WIFI SDIO Based Not working- No scan results » 2020-11-03 17:08:33

#78 Re: 全志 SOC » V3S主线驱动wifi-esp8089 » 2020-11-03 17:07:25

#83 Re: 全志 SOC » V3S官方SDK,console 串口打印怎样彻底关闭 » 2020-11-01 13:14:34

#84 Re: 全志 SOC » V3S官方SDK,console 串口打印怎样彻底关闭 » 2020-11-01 11:23:38

#85 Re: 全志 SOC » 请问F1C100S分辨率可以1366*768吗 » 2020-10-31 14:47:02

#87 Re: 全志 SOC » V3s GT911驱动问题 » 2020-10-30 15:55:44

buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *

http://whycan.com/t_5221.html

(出处:哇酷开发者社区【全志 V3S/F1C100s/X3】)

#88 Re: 全志 SOC » 请教v3s gt911驱动的问题。 dts里面iic配置,驱动触摸屏,io口和中断的配置 » 2020-10-30 15:55:23

buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *

http://whycan.com/t_5221.html

(出处:哇酷开发者社区【全志 V3S/F1C100s/X3】)

#90 Re: 全志 SOC » 闲鱼30元广告机板填坑主线uboot+主线linux » 2020-10-30 12:53:31

#91 Re: 全志 SOC » X3的656时分复用输入 » 2020-10-29 12:52:32

#92 Re: 全志 SOC » 淘了一个a20行车记录仪主板,并编译lichee » 2020-10-29 10:42:31

#93 Re: 全志 SOC » 根文件系统通过网络NFS挂载不成功,求助 » 2020-10-27 21:14:08

#96 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » 这种数码管字体 littlevgl / lvgl 计时器/倒计时器 界面如何? » 2020-10-25 20:38:39

#97 Php/Nodejs/Web/HTML5/Javascript/微信开发/Python » 发现一个好用的一个正则表达式可视化网站 https://regexper.com/ » 2020-10-25 00:37:30

- 孤星泪

- 回复: 8

发现一个好用的一个正则表达式可视化网站 https://regexper.com/

#98 Re: 全志 SOC » 无数次启动u-boot, 原因何在? » 2020-10-23 18:48:30

#99 Re: 全志 SOC » 无数次启动u-boot, 原因何在? » 2020-10-23 15:43:24

#100 Re: 全志 SOC » 无数次启动u-boot, 原因何在? » 2020-10-23 15:34:13

aodzip的sdk不香吗?

buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *

http://whycan.com/t_5221.html

(出处:哇酷开发者社区【全志 V3S/F1C100s/X3】)

#101 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 我用一条命令就把哇酷网备份了, web.archive.org 时光机(wayback)你值得拥有. » 2020-10-23 08:37:54

#102 Re: 全志 SOC » A33主线Linux跑起OpenGL/ES » 2020-10-22 16:46:26

#103 Re: 全志 SOC » buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *,支持SPI NAND » 2020-10-22 16:44:51

#104 Re: 全志 SOC » buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *,支持SPI NAND » 2020-10-22 16:19:35

#106 Re: 全志 SOC » F1C100S裸跑实现硬件多图层叠加和Alpha » 2020-10-22 12:54:52

#109 Re: 全志 SOC » buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *,支持SPI NAND » 2020-10-21 17:12:03

#110 Re: 全志 SOC » 分享个licheepi nano镜像,支持adb调试 » 2020-10-19 21:56:03

#113 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 树莓派图传核心技术和WiFi图传大PK! » 2020-10-17 12:15:22

#114 Re: 全志 SOC » codesourcery的gcc toolchain停更了,linaro的gcc工具链没有arm926ej-s/armv5te的版本 » 2020-10-16 13:50:09

#115 Re: 全志 SOC » 怎么烧录Tiny200 r3的SPI NAND » 2020-10-16 10:24:13

#118 Re: SigmaStar/SSD201/SSD202/SSD212 » 有没有人用过SigmaStar SSD201这颗芯片,感觉挺不错的啊 » 2020-10-13 19:54:55

关于Ubuntu 18.04下编译 SSD202D(卖家给的SDK)的文件无法通过uboot更新到nand上的问题

http://whycan.com/t_5370.html

(出处:哇酷开发者社区【DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/】)

有网友已经玩起来了

#121 Re: 全志 SOC » buildroot 为什么不能 make ,都是错误 » 2020-10-09 22:15:05

buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *

http://whycan.com/t_5221.html

(出处:哇酷开发者社区【全志 V3S/F1C100s/X3】)

用这个,然后勾选Qt就可以生成烧写镜像了。

#123 Re: 全志 SOC » codesourcery的gcc toolchain停更了,linaro的gcc工具链没有arm926ej-s/armv5te的版本 » 2020-10-09 10:23:31

#124 Re: 全志 SOC » f1c100s自制电路板程序下载和读取失败 » 2020-10-09 10:22:40

底部的GND焊了,PCB上特地挖了个大的过孔。

今天坑网似乎有问题,原理图一直没上传成功。

如何在本站发图片, 顺便吐槽功能弱智的phpbb半自动步木仑

http://whycan.com/t_588.html#p16351

(出处:哇酷开发者社区【站务公告/网站建设】)

可能上传成功了,要点插入才行。

#125 VMWare/Linux/Ubuntu/Fedora/CentOS/U-BOOT » buildroot 生成的镜像文件和target文件夹都缺少 libstdc++.so,手动复制才行,有什么办法彻底解决吗? » 2020-10-08 16:59:58

#126 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 大家快来看我的笑话! » 2020-10-07 10:52:18

#128 Re: 全志 SOC » 编译、安装Windows版本sunxi-fel步骤 (32M spi flash补丁,支持W25Q256/MX25L256) » 2020-09-30 17:13:47

#129 Re: 全志 SOC » 编译、安装Windows版本sunxi-fel步骤 (32M spi flash补丁,支持W25Q256/MX25L256) » 2020-09-30 17:00:08

#130 Re: 全志 SOC » 荔枝派Zero根据晕哥的USB线刷做的ubuntu下生成固件img » 2020-09-30 00:05:15

分享全志主线u-boot/linux 打包 TF/SD/SDNAND 镜像脚本

http://whycan.com/t_4008.html

(出处:哇酷开发者社区【全志 V3S/F1C100s/X3】)

#131 Re: 全志 SOC » buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *,支持SPI NAND » 2020-09-29 14:51:41

#132 Re: VMWare/Linux/Ubuntu/Fedora/CentOS/U-BOOT » 请问uboot的bootargs参数如何传递给linux app? » 2020-09-28 15:17:53

#133 Re: 全志 SOC » v3s TF卡烧录问题-无限重启 日志! » 2020-09-27 11:12:34

#134 Re: 硬件设计 KiCAD/Protel/DXP/PADS/ORCAD/EAGLE » pads破解版本有木马?怎么感觉我玩什么都有人知道的样子! » 2020-09-25 19:26:26

#135 Re: 全志 SOC » 请教一下,已经使用spi驱动的屏幕,需要怎么操作,可以让自己写的驱动使用该屏幕 » 2020-09-25 18:50:04

分享一个2011年在魅族M9上跑的一个framebuffer plasma 测试程序

http://whycan.com/t_3492.html

(出处:哇酷开发者社区【DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/】)

#136 Re: 全志 SOC » 大佬发的硬解码cedar如何使用 » 2020-09-25 18:31:01

buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *

http://whycan.com/t_5221.html

(出处:哇酷开发者社区【全志 V3S/F1C100s/X3】)

最新的tiny200 sdk已经包含了上面的cedarc

#138 Re: 全志 SOC » 大神能看一下吗,f1c100s 修改DDR主频和cpu主频?? » 2020-09-23 11:03:43

#139 Re: 全志 SOC » QSPI nor flash相关驱动代码 【转】 » 2020-09-23 07:04:28

#141 Re: 全志 SOC » V3s/S3/f1c100s通过USB启动Linux,并把SD NAND/TF卡挂载为U盘, 可以dd或Win32DiskImager任烧写 » 2020-09-22 13:51:12

#142 Re: 全志 SOC » emwin貌似是收费的,如果全志的芯片用emwin做界面会有问题吗 » 2020-09-22 13:49:56

#143 Re: 全志 SOC » W25N01G FLASH底部的焊盘需要焊接吗? » 2020-09-22 13:48:59

#144 Re: 全志 SOC » F1C200s 驱动 SPI+RGB 屏的接线问题 » 2020-09-22 13:48:19

三木同子 说:另外还想请教你一个问题,DB0-DB17怎么知道哪个是分别对应R,G,B?

本站不知道哪个帖子(找不到了)里有份全志A10 LCD的文档,有列出来。

v3s和LCD通过i8080总线模式

http://whycan.com/t_900.html#p3678

(出处:哇酷开发者社区【全志 V3S/F1C100s/X3】)

是这个吗?

#145 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 请问公共场所这种共享WIFI热点是什么原理?在小米手机的WIFI连接页面可以看到是否需要登录,是否已登录 » 2020-09-22 11:03:51

#146 Re: 全志 SOC » F1C100S显示屏颜色失真 » 2020-09-22 09:35:46

#148 Re: Openwrt/LEDE/AR9331/MT7688/RT5350 » 请问有大神会不会widora MT7688 驱动 NS4168 I2S声卡驱动, 用widora的固件库SDK » 2020-09-21 17:26:42

我做过驱动MT7688 (widora neo 开发板) 驱动 PCM5102A 声卡的,也是没有I2C控制的, 直接I2S输入输出.

https://whycan.cn/files/members/3/QQ20180407173256.jpg

https://whycan.cn/files/members/3/QQ20180407173253.jpg

https://whycan.cn/files/members/3/QQ20180407173247.jpg

https://whycan.cn/files/members/3/QQ20180407173258.png

原理就是创建一张无需codec的虚拟声卡,然后把MT7688的i2s设置为master(非常重要!!!)

widora的代码驱动WM8960声卡, 声卡处于主模式, 时钟是WM8960提供给MT7688的,

如果用NS4168这种不能作为I2S master的声卡,一定要把mt7688改为master.

这操作够骚,学到了。

#149 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 请教大家,汽车转向灯那个提示音是机械声音还是电子合成的声音? » 2020-09-21 11:37:47

#150 DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 请教大家,汽车转向灯那个提示音是机械声音还是电子合成的声音? » 2020-09-21 11:29:40

#152 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » 用VS2013怎样移植LVGL,我现在用下载版本的是7.0 » 2020-09-19 14:40:45

#155 DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 超市货架上的墨水屏不停刷屏,是不是很快就报废了? » 2020-09-17 22:59:49

#157 Re: 全志 SOC » 发布一套V3S可用的BSP内核的完整包(含u-boot、BSP内核、buildroot、.config、sunxi-tools、lrzsz) » 2020-09-16 16:11:39

#159 Re: 全志 SOC » 无桌面根文件系统,需一摄像头应用,开机显示预览画面,求指教 » 2020-09-16 14:56:36

#160 Re: 硬件设计 KiCAD/Protel/DXP/PADS/ORCAD/EAGLE » ubuntu下安装cadence报错:bin/virtuoso: /bin/ksh: bad interpreter: No such fi » 2020-09-16 14:54:59

#162 Re: 全志 SOC » 我有个开发板,默认那个232串口作为调试,但没有232线,想linux输出选择其他ttl串口,uboot里启动参数怎写? » 2020-09-15 15:47:41

#163 Re: 全志 SOC » buildroot下编译mplayer等app,怎么修改一些参数。貌似默认直接就给下载解压编译了 » 2020-09-15 15:04:13

仿照aodzip给buildroot打补丁

buildroot-tiny200 (F1C100/200s) 开发包近期更新内容 * 已支持DVP摄像头 *

http://whycan.com/t_5221.html

(出处:哇酷开发者社区【全志 V3S/F1C100s/X3】)

#166 Re: 全志 SOC » 小智X3开发板,lvds驱动给大家参考一下!!! » 2020-09-15 08:08:13

#168 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 大家快来看我的笑话! » 2020-09-12 22:04:47

#169 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 请问这种叠加图片的二维码可以用代码生成吗,哪里有演示代码可以下载呢? » 2020-09-11 16:53:35

收到,感谢大佬分享,我先试一试看疗效。

#170 Re: 全志 SOC » F1C200s 驱动 SPI+RGB 屏的接线问题 » 2020-09-09 18:07:39

#171 Re: BLDC电机驱动 » 自己撸了个BLDC板 » 2020-09-09 14:06:18

#172 Re: 全志 SOC » F1C100S USB转以太网AX88772驱动编译 » 2020-09-09 08:08:35

#174 DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 请问这种叠加图片的二维码可以用代码生成吗,哪里有演示代码可以下载呢? » 2020-09-08 14:21:11

#176 Re: 全志 SOC » 玩过全志A64音频的童鞋看过来,还请不吝赐教~~~ » 2020-09-07 11:35:37

#177 Re: 计算机图形/GUI/RTOS/FileSystem/OpenGL/DirectX/SDL2 » 发一个取模工具 支持fontawsome图标字体 » 2020-09-05 14:28:52

#179 Re: VMWare/Linux/Ubuntu/Fedora/CentOS/U-BOOT » 刚刚VMWware Ubuntu18.04 挂了, 开机提示硬盘出错, 吓傻我了 » 2020-09-04 14:11:52

#180 Re: 全志 SOC » 解决f1c100s 主线Linux 升级到 4.19 之后的版本没有 framebuffer(fb0)设备问题(转转转)(Linux5.2) » 2020-09-03 15:25:33

#182 Re: 全志 SOC » 全志V5 tinaSDK overlayfs问题请教 » 2020-09-03 10:48:29

#183 Re: 全志 SOC » 请问一下,LVDS显示图片色泽是这样的是什么原因??? » 2020-09-03 10:46:11

#184 Re: VMWare/Linux/Ubuntu/Fedora/CentOS/U-BOOT » 【小技巧分享】在不退出vim的情况下使用sudo完成写入 » 2020-09-01 20:20:54

#185 Re: Php/Nodejs/Web/HTML5/Javascript/微信开发/Python » 跟上时代,记录一下刚刚看视频学会的 php + 微信公众号开发 » 2020-08-31 09:10:44

#187 Re: NXP i.MX6UL/6ULL » DART-6UL Evaluation Kits 板子到了,用buildroot编译好的系统不能从SD卡启动的问题 » 2020-07-31 11:03:48

#188 Re: 全志 SOC » 荔枝派开发板上的dropbear服务器,在vmware上的ubuntu连接时提示 Connection refused » 2020-07-31 11:02:16

密钥这样放就可以,没必要放/etc目录:

#189 Re: 全志 SOC » 也发一个荔枝派zero 全志V3s 32M spi flash 固件,800x480 LCD, 开机自动运行 Qt analogclock » 2020-07-15 23:00:53

感谢楼主分享宝贵教程,

说句实在话,PyQt5 真香: https://stackoverflow.com/questions/51828943/pyqt5-and-subprocess-popen

可以直接用串口登录X3就可以编程了,无需再烧录:

import sys

from PyQt5 import QtCore, QtGui, QtWidgets

class Console(QtWidgets.QWidget):

errorSignal = QtCore.pyqtSignal(str)

outputSignal = QtCore.pyqtSignal(str)

def __init__(self):

super().__init__()

self.editor = QtWidgets.QPlainTextEdit(self)

self.editor.setReadOnly(True)

self.font = QtGui.QFont()

# self.font.setFamily(editor["editorFont"])

self.font.setPointSize(12)

self.layout = QtWidgets.QVBoxLayout()

self.layout.addWidget(self.editor, 1)

self.setLayout(self.layout)

self.output = None

self.error = None

self.editor.setFont(self.font)

self.process = QtCore.QProcess()

self.process.readyReadStandardError.connect(self.onReadyReadStandardError)

self.process.readyReadStandardOutput.connect(self.onReadyReadStandardOutput)

def onReadyReadStandardError(self):

error = self.process.readAllStandardError().data().decode()

self.editor.appendPlainText(error)

self.errorSignal.emit(error)

def onReadyReadStandardOutput(self):

result = self.process.readAllStandardOutput().data().decode()

self.editor.appendPlainText(result)

self.outputSignal.emit(result)

def run(self, command):

"""Executes a system command."""

# clear previous text

self.editor.clear()

self.process.start(command)

if __name__ == '__main__':

app = QtWidgets.QApplication(sys.argv)

w = Console()

w.show()

w.errorSignal.connect(lambda error: print(error))

w.outputSignal.connect(lambda output: print(output))

w.run("ping 8.8.8.8 -c 100")

sys.exit(app.exec_())这是一个随意调用外部命令,输出日志随意显示到Qt5的例程.

#191 Re: 全志 SOC » 小智X3卡片电脑玩法第二弹,WEB服务器~ » 2020-06-06 17:22:09

#192 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 东莞某公司寻求充电桩软硬件全套解决方案, 价格面谈 » 2020-06-06 17:20:49

#193 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » 学习的意义??? » 2020-06-06 17:19:07

#194 Re: 全志 SOC » F1C100S运行RT_thread系统 » 2020-05-29 11:02:46

#195 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 吐槽一下,typec 还几种规格呀,6针的,16针的24针的,还有各种固定方式 » 2020-05-27 08:27:08

#196 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 吐槽一下,typec 还几种规格呀,6针的,16针的24针的,还有各种固定方式 » 2020-05-27 08:23:39

#197 Re: 技术人生/软件使用技巧/破解经验/技术吐槽/灌水 » MDK发现一个奇怪的现象,求解答 » 2020-05-21 17:06:47

#198 Re: DIY/综合/Arduino/写字机/3D打印机/智能小车/平衡车/四轴飞行/MQTT/物联网 » 16脚的单片机,8脚地,12脚电源,可能是什么型号? » 2020-05-20 14:57:16

#199 Re: 全志 SOC » 有一个u盘, s3c2416和电脑都可以读写, 但是用V3s不能读写 » 2020-05-15 18:30:14

太原小智科技有限责任公司 - 东莞哇酷科技有限公司联合开发